# LUND UNIVERSITY

### Multicarrier Faster-than-Nyguist Signaling Transceivers: From Theory to Practice

Dasalukunte, Deepak

2011

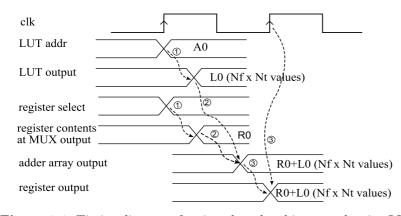

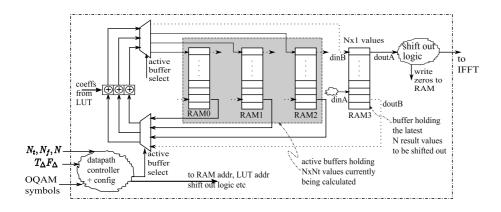

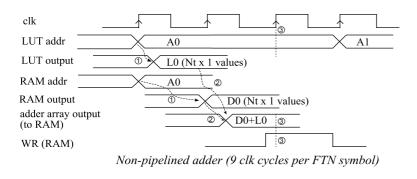

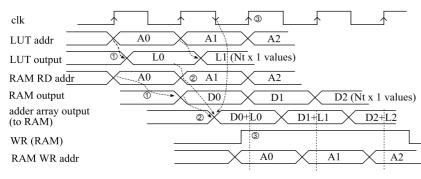

#### Link to publication

Citation for published version (APA): Dasalukunte, D. (2011). Multicarrier Faster-than-Nyquist Signaling Transceivers: From Theory to Practice. [Doctoral Thesis (monograph), Department of Electrical and Information Technology].

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

## Multicarrier Faster-than-Nyquist Signaling Transceivers

From Theory to Practice

Deepak Dasalukunte

Lund University

Ph.D Thesis, January 2012

Department of Electrical and Information Technology Lund University Box 118, SE-221 00 LUND SWEDEN

This thesis is set in Computer Modern 10pt with the  ${\rm IAT}_{\rm E}{\rm X}$  Documentation System

Series of licentiate and doctoral theses

ISBN 978-91-7473-223-8

ISSN 1654-790X

No. 36

© Deepak Dasalukunte

Printed in Sweden by *Tryckeriet i E-huset*, Lund.

December 2011.

# Abstract

The demand for spectrum resources in cellular systems worldwide has seen a tremendous escalation in the recent past. The mobile phones of today are capable of being cameras taking pictures and videos, able to browse the Internet, do video calling and much more than an yesteryear computer. Due to the variety and the amount of information that is being transmitted the demand for spectrum resources is continuously increasing. Efficient use of bandwidth resources has hence become a key parameter in the design and realization of wireless communication systems. Faster-than-Nyquist (FTN) signaling is one such technique that achieves bandwidth efficiency by making better use of the available spectrum resources at the expense of higher processing complexity in the transceiver.

This thesis addresses the challenges and design trade offs arising during the hardware realization of Faster-than-Nyquist signaling transceivers. The FTN system has been evaluated for its achievable performance compared to the processing overhead in the transmitter and the receiver. Coexistence with OFDM systems, a more popular multicarrier scheme in existing and upcoming wireless standards, has been considered by designing FTN specific processing blocks as add-ons to the conventional transceiver chain. A multicarrier system capable of operating under both orthogonal and FTN signaling has been developed. The performance of the receiver was evaluated for AWGN and fading channels. The FTN system was able to achieve 2x improvement in bandwidth usage with similar performance as that of an OFDM system. The extra processing in the receiver was in terms of an iterative decoder for the decoding of FTN modulated signals. An efficient hardware architecture for the iterative decoder reusing the FTN specific processing blocks and realize different functionality has been designed. An ASIC implementation of this decoder was implemented in a 65nm CMOS technology and the implemented chip has been successfully verified for its functionality.

iii

To my parents

# Preface

This thesis summarizes my research work carried out in the Digital ASIC group at the Department of Electrical and Information Technology for the Doctoral degree (Ph.D) in Circuit Design. The main contributions of the thesis are:

- D. Dasalukunte, F. Rusek, and V. Öwall, "Improved memory architecture for multicarrier faster-than-Nyquist iterative decoder," in *Proc. of IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, Chennai, Jul 2011.

- [2] D. Dasalukunte, F. Rusek, and V. Öwall, "Multicarrier faster-than-Nyquist signaling transceivers: Hardware architecture and performance analysis," *IEEE Transactions on Circuits and Systems-I (TCAS-I)*, vol. 58, no. 4, pp. 827-838, Apr 2011.

- [3] D. Dasalukunte, F. Rusek, and V. Öwall, "An iterative decoder for multicarrier faster-than-Nyquist signaling systems," in *Proc. of IEEE International Conference on Communications (ICC)*, Cape Town, May 2010.

- [4] D. Dasalukunte, K. Ananthanarayanan, M. Kandasamy, F. Rusek, and V. Öwall, "Hardware implementation of mapper for faster-than-Nyquist signaling transmitter," in *Proc. of IEEE NORCHIP*, Trondheim, Nov 2009.

- [5] D. Dasalukunte, F. Rusek, J. B. Anderson, and V. Öwall, "A transmitter architecture for faster-than-Nyquist signaling systems," in *Proc. IEEE International Symposium on Circuits and Systems (ISCAS)*, Taipei, May 2009.

- [6] S. Mehmood, D. Dasalukunte, and V. Öwall, "Hardware architecture of IOTA pulse shaping filters for multicarrier systems," under first revision in *IEEE Transactions on Circuits and Systems-I* Dec. 2011.

[7] D. Dasalukunte, S. Mehmood, and V. Öwall, "Complexity analysis of IOTA filter architectures in faster-than-Nyquist multicarrier systems," in *Proc. of IEEE NORCHIP*, Lund, Nov 2011.

I have also contributed to the following articles during my stint at the Department of EIT.

- [8] D. Noguet, M. Laugeois, X. Popon, P. Balamuralidhar, N. Sortur, M. Lobeira, D. Dasalukunte, Z. Bakirtzoglou and C. Dehos, "An MC-SS platform for short-range communications in the Personal Network context," in *EURASIP Journal on Wireless Communications and Networking*, 2008.

- [9] D. Dasalukunte, and V. Öwall, "A generic hardware MAC for wireless personal area network platforms," in *Proc. International Symposium on Wireless Personal Multimedia Communications (WPMC)*, Saariselka, Sep. 2008.

- [10] D. Dasalukunte, A. Pålsson, M. Kamuf, P. Persson, R. Veljanovski and V. Öwall, "Architectural optimization for low power in a reconfigurable UMTS filter," in *Proc. International Symposium on Wireless Personal Multimedia Communications (WPMC)*, San Diego, 2006.

### Contents

| Abstract            |       |                                                   | iii  |              |

|---------------------|-------|---------------------------------------------------|------|--------------|

| Preface<br>Contents |       |                                                   |      |              |

|                     |       |                                                   |      | $\mathbf{A}$ |

| $\mathbf{A}$        | crony | ms                                                | xv   |              |

| Sy                  | mbol  | s                                                 | xvii |              |

| 1                   | Intro | oduction                                          | 1    |              |

|                     | 1.1   | Motivation for FTN signaling                      | 2    |              |

|                     | 1.2   | Prior work and state-of-the-art                   | 4    |              |

|                     | 1.3   | Hardware implementation                           | 6    |              |

|                     | 1.4   | Thesis contributions                              | 10   |              |

| <b>2</b>            | FTN   | I theory                                          | 13   |              |

|                     | 2.1   | Transmission scheme                               | 13   |              |

|                     | 2.2   | Alternate transmission methods                    | 23   |              |

|                     | 2.3   | Decoding FTN modulated symbols                    | 25   |              |

|                     | 2.4   | Choice of Time-Frequency spacing in FTN signaling | 30   |              |

|                     | 2.5   | System setup                                      | 32   |              |

|                     | 2.6   | Receiver performance                              | 32   |              |

|                     | 2.7   | Gains from the FTN system                         | 37   |              |

|                     | 2.8   | Summary                                           | 40   |              |

ix

| 3        | FTN signaling in fading channels                                     | 41  |

|----------|----------------------------------------------------------------------|-----|

|          | 3.1 System model                                                     | 42  |

|          | 3.2 Receiver processing in presence of fading                        | 44  |

|          | 3.3 Adaptive FTN signaling                                           | 52  |

|          | 3.4 Summary                                                          | 56  |

| 4        | FTN Transmitter: Hardware Architecture and Implemen-                 |     |

|          | tation                                                               | 57  |

|          | 4.1 Look-Up Table based architecture                                 | 57  |

|          | 4.2 Implementation                                                   | 60  |

|          | 4.3 Results $\ldots$                                                 | 66  |

|          | 4.4 Summary                                                          | 68  |

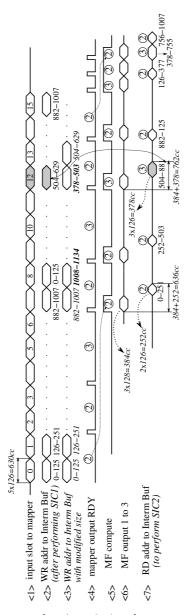

| <b>5</b> | FTN Receiver: Hardware Architecture and Implementa-                  |     |

|          | tion                                                                 | 69  |

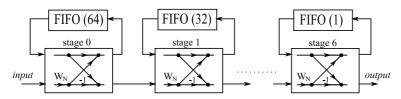

|          | 5.1 Matched Filter architecture                                      | 70  |

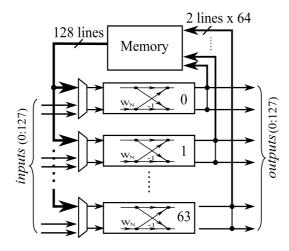

|          | 5.2 Inner Decoder architecture                                       | 72  |

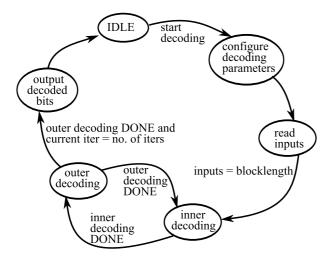

|          | 5.3 Outer Decoder                                                    | 77  |

|          | 5.4 Controller for the FTN decoder                                   | 77  |

|          | 5.5 Implementation results                                           | 78  |

|          | 5.6 Hardware overhead with FTN signaling                             | 81  |

|          | 5.7 Architectural optimizations to reduce area and power $\ldots$ .  | 83  |

|          | 5.8 Post-optimization results                                        | 91  |

|          | 5.9 RTL verification using MATLAB system model                       | 93  |

|          | 5.10 FTN signaling in transceivers                                   | 94  |

|          | 5.11 Summary                                                         | 96  |

| 6        | FTN decoder chip: Measurements and results                           | 97  |

|          | 6.1 Chip configurations                                              | 99  |

|          | 6.2 Measurement results                                              | 103 |

|          | 6.3 Summary                                                          | 106 |

| 7        | IOTA pulse shaping filter in FTN multi-carrier systems               | 107 |

|          | 7.1 Introduction                                                     | 107 |

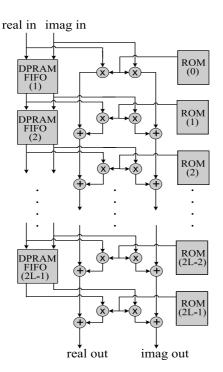

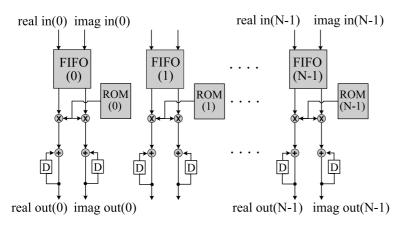

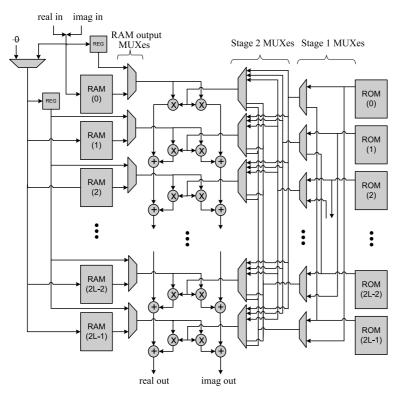

|          | 7.2 Functional description of transmit/receive IOTA filter $\ . \ .$ | 109 |

| <ul> <li>7.3 Hardware architecture</li></ul> | 111<br>121<br>127 |  |  |  |

|----------------------------------------------|-------------------|--|--|--|

| Conclusion                                   |                   |  |  |  |

| Future Directions                            |                   |  |  |  |

| Bibliography                                 | 134               |  |  |  |

# Acknowledgments

I would like to take this opportunity to thank those that have helped me during my years at the Department of Electrical and Information Technology as a PhD student.

First of all, my sincere gratitude and thanks to my supervisor Prof. Viktor Öwall for taking me as his PhD student, when I myself was not confident that I could come this far. Thanks for providing such a wonderful opportunity and for all your support and encouragement.

Thanks to my co-supervisor Dr. Fredrik Rusek who has been very helpful and patient in teaching me basics and advanced topics in Communication theory, I must admit, I still lack some. Also, special thanks to Prof. John B Anderson.

I have enjoyed my work and research in the Digital ASIC group and the Dept. of EIT. I would like to thank Johan, my contemporary, and current colleagues Joachim, Isael, Chenxin, Yasser, Reza, Oskar, Liang, Hemanth and Rakesh for all the constructive and interesting discussions I had in the group. It was a pleasure working with you all. Also, thanks to my former colleagues for their guidance when I started my PhD. I also thank my other colleagues and friends at the department for interesting coffee and lunch time discussions.

I would like to thank Prof. Borivoje Nikolic for hosting me at the Berkeley Wireless Research Center, UC Berkeley during Jan-Apr 2010. Thanks to Antonio Vicent from ST-Ericsson for his expert help during my chip tapeout.

xiii

My profound thanks to Pia for fixing almost everything on the administrative side for which I approached her, thanks to Erik and Stefan for support with the computers and CAD tools. Many thanks to Lars and rest of the administrative staff for getting things done and making sure things are in place so that I could focus better on my work.

Finally, I would like to express my utmost gratitude to my family. Thank you amma, daddy and Anu for your unconditional support and sacrifices that has made me what I am today!

3 / all

Deepak Dasalukunte

# Acronyms

**3GPP** 3<sup>rd</sup> Generation Partnership Project. **ASIC** Application Specific Integrated Circuit. AWGN Additive White Gaussian Noise. BCJR Bahl-Cocke-Jelenik-Raviv. **BER** Bit Error Rate. CMOS Complementary Metal Oxide Semiconductor. **DEMUX** De-Multiplexer **DFT** Discrete Fourier Transform. dp-RAM Dual Port RAM. **DVB** Digital Video Broadcasting. **FFT** Fast Fourier Transform. FPGA Field Programmable Gate Array. FTN Faster-than-Nyquist. **ICI** InterCarrier Interference. **IID** Independent, Identically Distributed. **IOTA** Isotropic Orthogonal Transform Algorithm. **ISI** InterSymbol Interference. **ITRS** International Technology Roadmap for Semiconductors.

XV

LLR Log-Likelihood Ratio.LR Likelihood Ratio.LTE Long Term Evolution.

LUT Look-Up Table.

MAP Maximum APosteriori.

MLM Max-Log-MAP.

$\mathbf{MCM}\xspace$  Multi-Carrier Modulation.

${\bf MF}\,$  Matched Filter.

MUX Multiplexer.

**OFDM** Orthogonal Frequency Division Multiplex.

${\bf OQAM}$  Offset-Quadrature Amplitude Modulation.

**OQPSK** Offset-Quadrature Phase Shift Keying.

${\bf PAPR}\,$  Peak-to-Average Power Ratio.

${\bf RAM}\,$  Random Access Memory.

${\bf RTL}\,$  Register Transfer Logic.

${\bf SNR}$ Signal-to-Noise Ratio.

${\bf SIC}\,$  Successive Interference Cancellation.

**sp-RAM** Single Port RAM.

VHDL VHSIC Hardware Description Language.

**VHSIC** Very High Speed Integrated Circuit.

**VLSI** Very Large Scale Integration.

WLAN Wireless Local Area Network.

# Symbols

- k Sub-carrier index of FTN symbols.

- $\ell\,$  Time index of FTN symbols.

- m Sub-carrier index of orthogonal symbols.

- n Time index of orthogonal symbols.

- N Number of sub-carriers in an orthogonal multicarrier system.

- M Number of time instances in a orthogonal multicarrier system.

- K Block size of transmitted/received information  $(= N \times M)$ .

- $N_{\rm FTN}\,$  Number of sub-carriers in a multicarrier FTN system.

- $M_{\rm FTN}\,$  Number of time instances in a multicarrier FTN system.

- *i* Imaginary number  $(=\sqrt{-1})$ .

- $N_t$  Number of projection points along time.

- $N_f$  Number of projection points sub-carriers.

- T Time period of a rectangular pulse carrying information in an orthogonal/OFDM system.

- $L_{\text{ext}}$  Extrinsic log-likelihood ratio.

- $T_{\Delta}\,$  Time spacing between two adjacent FTN symbols.

- $F_{\Delta}$  Frequency/sub-carrier spacing in the FTN system.

- $T_{\rm rep}$  Repetition rate in time.

- $F_{\rm rep}$  Repetition rate in frequency.

- $\check{x}_{k,\ell}\,$  Interference canceled symbols

- $\bar{x}_{k,\ell}$  Reconstructed FTN symbols are the receiver.

- $\hat{x}_{k,\ell}$  Soft symbol + Interference.

- $x_{m,n}^\prime\,$  Projected FTN symbol on the orthogonal basis function at sub-carrier m and time instance n.

- $x_{k,\ell}$  FTN information symbol.

$\tilde{x}_{k,\ell}$  Soft symbol.

### Chapter 1

## Introduction

This thesis deals with inter disciplinary work in wireless communication and VLSI, addressing challenges that arise when realizing wireless communication algorithms in hardware. The algorithms under study are those associated with improving the efficiency of the resources used for information transmission in a wireless system. One primary resource in the wireless system is the frequency band of operation. The frequencies are generally allocated by a gov-ernmental/regulatory bodies such as the Body of European Regulator for Electronic Communications (BEREC) [BER], Federal Communications Commission (FCC) [FCC], Telecom Regulatory Authority of India (TRAI) [TRA] to name a few. In this context, a wireless system primarily refers to a mobile phone or a handheld device capable of communicating wirelessly to another device or a base station.

Since its invention, the mobile phone has experienced explosive growth evolving from being a mere voice communicating device to more than a computer in the recent past. Ever since, there has been a rising demand for information transmission and reception. Though the amount of bandwidth available has also increased, the demand has infused severe competition amongst the mobile operators who are paying a very high premium to own spectrum resources. The recent 3G and broadband wireless spectrum auction in India in 2010 fetched USD 23.5 billion for the 5MHz nationwide spectrum in 20 circles [Wik]. In Spain, the 4G mobile licenses is expected to bring EUR 1.5 billion from the bidding of a total of 310MHz in different frequency bands [LG11]. At the same time, advances in semiconductor technology are pushing the limits of processing by cramming in more and more electronics into microchips. This means that the small sized chips can now accommodate more complex circuits. The main goal of this thesis is to realize architectures that are moderately more

1

complicated than existing ones and efficiently use the expensive bandwidth resources.

In the following sections an extended introduction to the two research topics, wireless communications and VLSI, are discussed. Section 1.1 provides the motivation and a brief background to FTN signaling. Section 1.2 briefs state-of-the-art research carried out in parallel to that presented in this thesis, also intended for improving bandwidth efficiency. Section 1.3 discusses various approaches/technologies available for hardware implementation. Depending on the application, different approaches prove to be suitable for different applications. Here, the focus is mostly on realizing the wireless algorithms in hardware and the choices are made on this basis.

### 1.1 Motivation for FTN signaling

Wireless communication dates back to late 1800's with pioneering contributions from G. Marconi, R. Fessenden, J.C. Bose, N. Tesla and many others. Since then it has come a long way in different forms as telegraphy, radio broadcasting, television, and in the most recent decades as mobile telephony. The mobile phone was primarily meant to be used for voice based communications, a portable and handheld version of the fixed telephone. The mobile telephony system later evolved into the second generation now popularly known as Global System for Mobile communication (GSM) [GSM]. Since then, the mobile phone has evolved rapidly with non-voice services overtaking the voice based communications. As a result, the mobile phone evolved into more just than a voice communicating device increasing the demand for broadband communication in order to cater for the next generation wireless technologies.

OFDM which stands for orthogonal frequency-division multiplexing is a multi-carrier scheme which is now the heart of several existing and upcoming broadband wireless access technologies such as LTE, WLAN, DVB, IMTadvanced. The sub-carriers carrying data can be seen as a channel transmitting information [Hir81, Cha66, Sal67] and they can vary from a few tens to thousands of sub-carriers. OFDM proved to be a very attractive solution due to its robustness and ease of decoding the modulated signals in a wireless environment. With more and more demand for broadband services such as the internet, video calls, and television, OFDM is being rapidly scaled to meet the demands for the upcoming standards. As a result, there is ever increasing need for improving the existing technologies to cope with the such rapid progress or envision newer schemes that scale with the demand. Though scaling the bandwidth of operation has been possible to a certain extent, it poses challenges in receiver processing and restrictions in terms of frequency usage as it

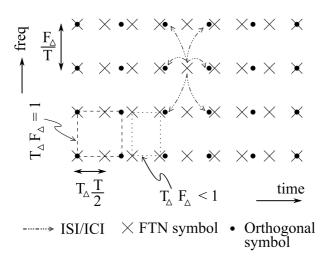

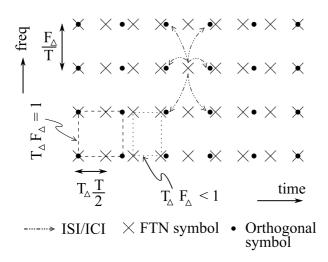

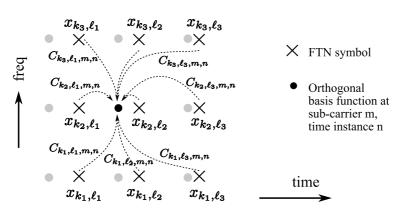

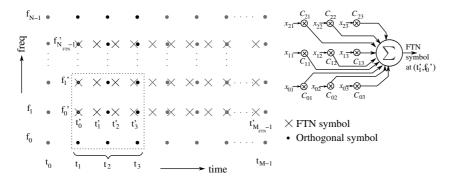

Figure 1.1: FTN and OFDM symbols on the time frequency grid.

is restricted by the regulatory bodies.

A more favorable solution is to make better use of the same available bandwidth in the existing multi-carrier systems. Faster-than-Nyquist (FTN) signaling is one such approach that trades bandwidth for processing complexity. Today bandwidth is a premium resource compared to the processing power that is at disposal in the state-of-the-art silicon technology. Therefore, methods like FTN that trade processing complexity for bandwidth efficiency needs to be investigated. FTN signaling has been theoretically proven to have advantages in single carrier system [RA09a]. However, since most modern wireless systems being multicarrier (mostly OFDM) the impact of FTN signaling in multicarrier environment needs to be evaluated. This especially refers to the algorithm-hardware tradeoff which is the main focus of this research project.

#### 1.1.1 FTN signaling: Background

The concept of FTN was first proposed by J.E. Mazo [Maz75] back in 1975. However, the transceiver involved in such a signaling scheme has a requirement of manifold processing complexity. This is similar to the trend of LDPC codes [Gal63] which were not used until lately due to their inherent implementation complexity. FTN is achieved by signaling information beyond Nyquist's criterion for transmission of symbols without any inter-symbol interference (ISI) [Nyq28]. In other words, to receive the symbols without any ISI, the information can be signaled no faster than the Nyquist rate [PS08, Rus07]. This is also usually referred to as orthogonal signaling, as there is no interference amongst the symbols.

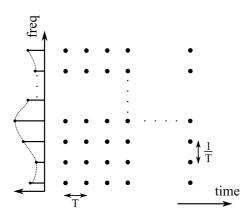

FTN signaling, on the other hand, packs more symbols than in a conventional orthogonal signaling scheme thus introducing inter-symbol and intercarrier interference (ISI and ICI). Figure 1.1 graphically shows how the information symbols appear on the time-frequency grid when signaled orthogonally or using FTN signaling. The •s correspond to orthogonal symbols and are separated in time and frequency satisfying Nyquist's condition, hence do not interfere with each other in time or frequency. This system is referred to as an orthogonal system, OFDM being one classic example. The symbols denoted as  $\times$ s, are signaled beyond Nyquist's criterion for ISI free transmission resulting in being able to transmit many more symbols than an orthogonal system. The effective improvement in bandwidth usage over the orthogonal system is dependent on the overall compression.

### **1.2** Prior work and state-of-the-art

Though FTN was developed in the 70's [Maz75], there had not been extensive work either with developing algorithms for FTN or realization on devices for practical usage until recently. A plausible reason is the complexity involved in the realization of such systems, a trend similar to that of the LDPC codes [Gal63]. In the past decade, FTN has received a lot more attention in the research communities worldwide. FTN has also been referred to by other names such as *Spectrally Efficient Frequency Division Multiplexing* (SEFDM), bandwidth efficiency improvement... etc. While most are theoretical studies developing algorithms or demonstrating the advantages of using FTN, only very recently there has been some architectural exploration other than the work presented in this thesis. The works listed below highlight what has been researched in each of the articles.

- In [LG03], the preservation of the minimum Euclidean distance for binary signaling in spite of small increase in signaling rate beyond Nyquist is extended to a family of raised-cosine pulses. Practical ways of achieving these gains through iterative joint equalization and decoding scheme is presented.

- [BFC09] investigates the spectral efficiency achievable by a low-complexity symbol-by-symbol receiver. It is shown that when using finite-order constellations, giving up the orthogonality condition can considerably improve the performance.

- [MS10] evaluates FTN transmission and reception in discrete time. A digital communication system with QPSK modulation and AWGN channel is assumed. It is shown that the symbol rate can be increased by 25% without significantly increasing the bit error rate and without requiring increased transmission bandwidth.

- Aspects of fading, Doppler and the robustness of FTN in dispersive channels is discussed in [HZ09].

- [HT04] defines bandwidth efficiency improvement as High Compaction Multi-Carrier Modulation (HC-MCM). It discusses DFT based transmitter and receiver, spectral efficiency and BER performance of the system.

- [YC10] discusses asymptotically achievable information rate of binary FTN signaling.

- [KB10] presents pre-coding of FTN signals and ways of preventing spectrum broadening due to pre-coding.

Under the alternative name of *Spectrally Efficient FDM* (SEFDM) the following works appear in literature:

- [KCRD09] discusses improving bandwidth efficiency by intentionally violating carrier orthogonality in a frequency division multiplexed system and at the expense of receiver complexity. It is shown that it is possible to detect optimally and efficiently FDM signals, with 25% bandwidth gain with respect to analogous OFDM signals.

- [ID11a] is about SEFDM receivers with relatively complex detectors to extract the signal from the ICI created by the loss of orthogonality. Fixed complexity Sphere Decoder (FSD), a hardware friendly approach for the detection of SEFDM signal is proposed.

- SEFDM is extended to time varying channels in [CKRD10]. However, 2 fixed channel realizations are considered in order to evaluate the performance.

- A hardware architecture to realize transmission of SEFDM signals is proposed in [WPID11] and the implementation in [PD11]. The realization is carried out using multiple IFFTs. This is also independently discussed in Section 2.2 together with the drawback in employing such an approach.

- [ID11b] discusses the peak-to-average power ratio (PAPR) reduction. Apart from investigating the standard PAPR reduction techniques, a novel PAPR reduction algorithm termed the Sliding Window PAPR reduction technique is proposed.

FTN related work [Rus07, RA09b] carried out within our department has been the motivation for hardware feasibility studies and also the foundation for the architectures proposed in this work. To the best of author's knowledge, no attempt of hardware implementation for decoding of FTN modulated signals has been made in the literature. An exception is the transmitter architecture in the most recently published work in [WPID11]. The proposed transmitter and receiver architectures in this work remains close to conventional architectures that exist in the standards. This is done in an attempt for seamless switching between an FTN and orthogonal signaling taking advantage of FTN signaling during good channel conditions. The approach in this work has resulted in simplified implementation of FTN signaling and its inclusion into existing systems by simply introducing FTN specific add-on processing blocks. We present an architecture and a successful silicon implementation of the FTN iterative decoder using a state-of-the-art CMOS ASIC process, also a first in the field. Faster-than-Nyquist signaling, having different nomenclatures, have started to gain popularity in the research community mainly because of increasing constraints in the spectrum and relaxing requirements in hardware processing complexity.

### **1.3** Hardware implementation

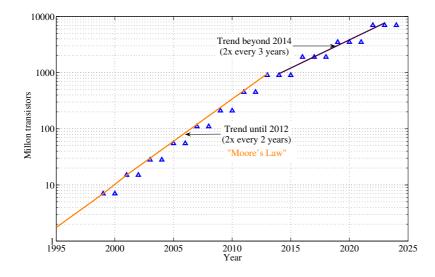

The Nobel prize winning invention of the Integrated Circuit (in the 1950's) revolutionized the electronics industry. It led to the realization of transistors, a fundamental building block of digital and analog circuits, in a highly compact manner. As a result electronic components could be manufactured on a small piece of silicon die, compared to those made from bulky vacuum tubes, thus resulting in smaller computers and other electronic devices. Over the last 50 years, the number of transistors that could be placed on a silicon die has risen exponentially, from a few to several thousands and today, billions. This trend came to be known as the Moore's law, named after the discoverer who observed and proposed in his paper [Moo65] that the number of transistors on a chip would double every year. The law has continued to be valid until very recently except that the transistor doubling happening every two years instead [ITR]. The International Technology Roadmap for Semiconductors (ITRS) comprises of experts from the semiconductor industry who periodically forecast the technology trends in silicon manufacturing related to microprocessors, memories etc. Figure 1.2 shows the trend from the data extracted from one such report released in 2009 with projections until the year 2025. The doubling of transistors will follow Moore until 2014, after which the trend slows down with the transistor doubling happening every 3 years, according to the ITRS forecast.

Figure 1.2: Semiconductor technology roadmap from ITRS [ITR].

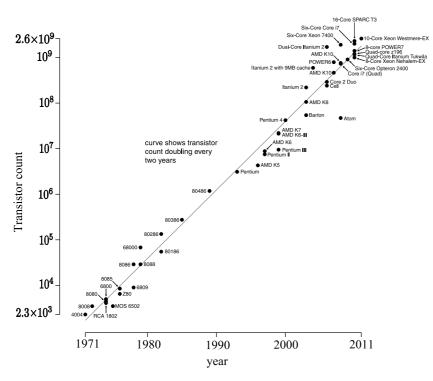

Figure 1.3 shows Moore's law in action, with data from specific chips from different manufacturers; from the first commercial microprocessor 4004 introduced by Intel [Int] to its latest (on the graph) the 10-core Xeon Westmere-EX.

As the semiconductor industry evolved, the silicon chips were designed to cater to a variety of applications. They could be broadly classified as general purpose processors (CPUs), Digital Signal Processors (DSPs), Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs). In principle, all the above solutions can be used to realize different target applications. However, certain constraints restrict their usage. For instance, applications that run on handheld devices are constrained for power as they run on batteries while desktop computers are more targeted for performance and does not have to be highly limited on the power. Certain other applications might be required to be capable of running different applications at different times bringing up the need for flexibility. Hence these solutions can be broadly classified on the basis of power consumption and flexibility of realizing different applications as they are considered as two important metrics when it comes to realization using hardware.

Figure 1.3: Moore's Law as a function of transistor count over the period of 1971-2011 (*Source: "Moore's law" Wikipedia*).

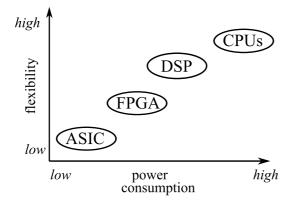

Figure 1.4 shows a general graph of how CPUs, DSPs, FPGAs, and ASICs fare in the flexibility vs. power consumption design space. It is to be noted that this classification has become increasingly obscure with advances in the semiconductor process technology and better tools that help in achieving low power designs. However, the argument of power and flexibility is still applicable in a general context. CPUs are highly programmable and are suitable for general purpose applications and hence are dominantly used in desktop computers, for example, the Intel core i5 processor. DSPs have specialized instructions that can speed up signal processing operations, hence suitable for realizing any signal processing algorithm and TMS320 is one such example of a family of DSPs from Texas Instruments [TI]. FPGAs have programmable logic and can be used to realize custom logic on the fly, but they are known to suffer from poor power performance. The Virtex<sup>TM</sup> series from Xilinx is a popular example for FPGAs. Finally, ASICs are custom integrated circuits that are

**Figure 1.4:** Flexibility vs. power consumption of various forms of digital integrated circuits.

fabricated for a particular application. Once manufactured the ASICs cannot be modified to have a different functionality altogether. However, in terms of power consumption, ASICs can be designed to have the best efficiency. These different possibilities discussed so far to realize an algorithm is to motivate the choice in the context of realizing FTN signaling using these solutions.

#### 1.3.1 Algorithm-hardware tradeoffs

Newer algorithms are devised to improve various aspects in wireless communications, for example, error performance and hence improve the overall efficiency of the system. However, for these algorithms to be applied in practice, they have to be architected and implemented on some device, be it a general purpose computer or a specialized chip. Thus, the algorithms are limited by the target platform on which it is implemented and hence have constraints such as:

- Finite wordlengths for number representation.

- Logic and memory defining the area and power consumption.

- Processing capability limitations on how extensively the algorithm can be run.

- Design specification constraints in order to meet speed and throughput rates.

In a wireless system, processing of signals received over a wireless channel involves signal detection, synchronization, demodulation, and decoding. All of these happens in a layer referred to as the physical layer (PHY), so named because it deals with the physical link connecting the devices (nodes in general) in the network. By 'link' in a wireless system we mean the propagation channel. FTN signaling being discussed in this work is also carried out in this layer of abstraction. The PHY layer has conventionally been implemented on custom hardware due to high demands for power and throughput. Since the hardware is application specific, the integrated circuits developed for this purpose are aptly called ASICs. Though there is also research carried out in this field, generally referred to as Software Defined Radio (SDR), most implementations still largely follows the conventional approach. Software defined radio in the FTN context is an interesting work that still needs to be researched but is not the focus of this work. The main aim of this work is to evaluate the actual overhead in processing one has to pay when adopting FTN to efficiently utilize the bandwidth resources. The CPUs, DSPs and FPGAs have their own overhead in terms of extra logic and other resource based overhead.

For example, with CPUs it is harder to evaluate the exact processing overhead as the processor is usually running several applications together with the one that is of interest to us. In case of FPGAs, the logic overhead cannot be determined accurately as the signal routing is also done using logic resources that are used for realizing the functionality at hand. An ASIC implementation provides an accurate overhead in terms of logic and power consumption as the logic purely corresponds to the functional blocks implemented and hence well motivated.

### **1.4** Thesis contributions

The contributions in the thesis (hereby referred to as work) is broadly classified as theory/algorithm design sections in Chapters 2 and 3. The hardware architecture, implementation and measurements of the chip is discussed in Chapters 4, 5 and 6. Chapter 7 discusses the hardware architecture and implementation of the IOTA pulse shaping filter.

On the theoretical front, FTN signaling can be improved in several different ways with algorithms that achieve performance close to the theoretic bounds. In this work, major focus is on the feasibility of FTN signaling for its use in practical applications, performance versus hardware complexity tradeoffs and achievable gains when actually implemented in hardware.

The following sub-sections highlight the chapter wise contributions under the two broad categories of theory and implementation.

#### Theory: FTN signaling in AWGN and fading channels

Chapter 2 (*FTN theory*) discusses the choice of orthogonal basis to be used for multicarrier modulation so as to reduce complexity in the transmitter. It also discusses transmission methods alternate to that proposed and its disadvantages. It has been shown that, operating at sub-optimal points for a particular time-frequency spacing will result in reduced storage complexity. The performance of the receiver for an AWGN channel and the actual gains achieved from the FTN system is elaborated.

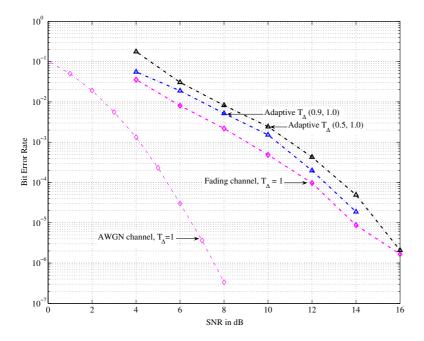

In Chapter 3 (*FTN signaling in fading channels*), the receiver processing is extended to combat fading. The modifications carried out to account for fading and steps taken to exploit the fading channel by adaptively using FTN signaling is explained. The achievable data rates while using FTN signaling in a fading environment is presented.

The contents of the chapters are based on the following articles:

- D. Dasalukunte, F. Rusek, J. B. Anderson, and V. Öwall, "A Transmitter Architecture for Faster-than-Nyquist Signaling Systems," in *Proc.IEEE International Symposium on Circuits and Systems*, Taipei, May 2009.

- D. Dasalukunte, F. Rusek, and V. Öwall, "An Iterative Decoder for Multicarrier Faster-than-Nyquist Signaling Systems," in *Proc. of IEEE International Conference on Communications*, Cape Town, May 2010.

## FTN transmitter, receiver: Hardware architecture, implementation and chip measurements

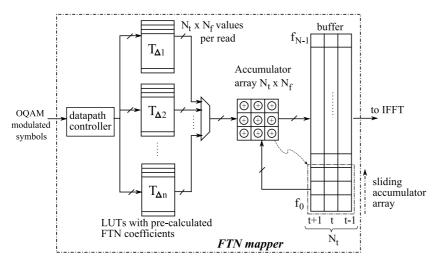

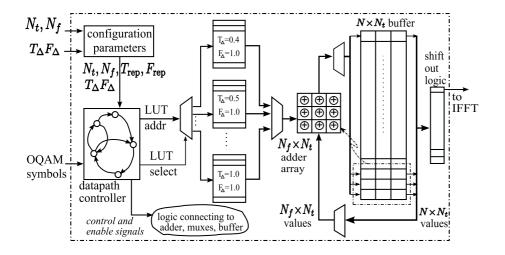

Chapter 4 (*FTN Transmitter: Hardware architecture and implementation*) details the hardware architecture and the implementation of the mapper used in the transmitter to realize FTN signaling. It also draws a comparison between the complexity in the mapper with respect to the IFFT block, generally considered as a significantly complex block in the transmitter.

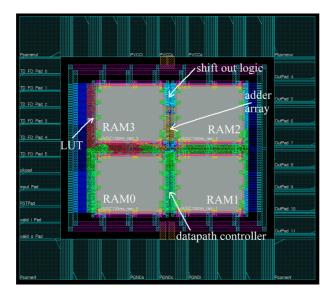

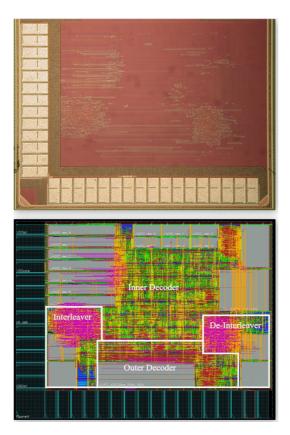

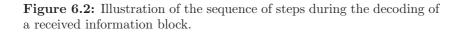

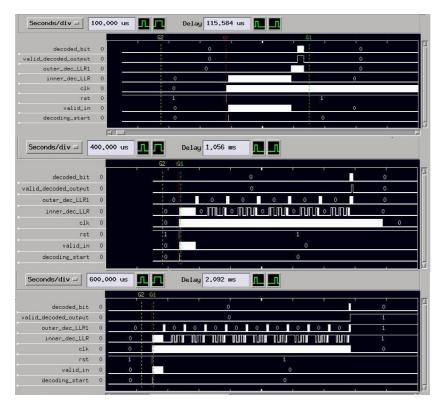

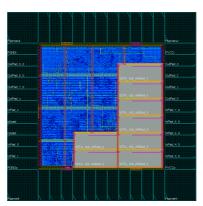

Chapter 5 (*FTN Receiver: Hardware architecture and implementation*) elaborates the architecture employed in the FTN decoder and also the re-use of processing blocks to realize different functionalities. Implementation results are provided for both FPGA and ASIC; a comparison in terms of complexity is made between the inner decoder (specific to FTN) and the outer decoder (which is a standard channel decoding approach). Memory optimizations to reduce silicon area and power is also carried out. The measurements from the FTN decoder chip implemented in ST 65nm CMOS is presented in Chapter 6 (*FTN decoder chip:Measurements and results*). The IOTA filter, hardware

architecture and its implementation is presented in Chapter 7 (*IOTA pulse shaping filter in FTN multi-carrier systems*). Though the IOTA pulse shaping is not directly related to the FTN signaling or its decoding, it has influenced in reducing hardware complexity and hence presented as a part of the thesis.

The contents of the chapters are based on the following articles:

- D. Dasalukunte, F. Rusek, J. B. Anderson, and V. Öwall, "A Transmitter Architecture for Faster-than-Nyquist Signaling Systems," in *Proc.IEEE International Symposium on Circuits and Systems*, Taipei, May 2009.

- D. Dasalukunte, K. Ananthanarayanan, M. Kandasamy, F. Rusek, and V. Öwall, "Hardware Implementation of Mapper for Faster-than-Nyquist Signaling Transmitter," in *Proc. of IEEE NORCHIP*, Trondheim, Nov 2009.

- D. Dasalukunte, F. Rusek, and V. Öwall, "Multicarrier Faster-than-Nyquist Signaling Transceivers: Hardware Architecture and Performance Analysis," *IEEE Transactions on Circuits and Systems-I*, vol. 58, no. 4, pp. 827-838, Apr 2011.

- D. Dasalukunte, F. Rusek, and V. Öwall, "Improved Memory Architecture for Multicarrier Faster-than-Nyquist Iterative Decoder," in *Proc. of IEEE Computer Society Annual Symposium on VLSI*, Chennai, Jul 2011.

- S. Mehmood, D. Dasalukunte, and V. Öwall, "Hardware architecture of IOTA pulse shaping filters for multicarrier systems," under first revision in *IEEE Transactions on Circuits and Systems-I* Dec. 2011.

### Chapter 2

# FTN theory

A signaling system is said to be faster-than-Nyquist if the pulses appear at a rate beyond the allowed Nyquist condition for ISI free transmission [Maz75]. Initially, this applied to a single carrier system with pulses overlapping with each other in time. Later this was extended for a multicarrier system (OFDM) [RA09b, Rus07] and in this case the pulses may violate the least required spacing in both time and frequency. As a result there is induced interference in both time and frequency, generally referred to as intersymbol (ISI) and intercarrier interference (ICI). Figure 2.1 shows the way orthogonal and multicarrier FTN symbols appear in the time-frequency lattice where the FTN system has symbols appearing more frequently in time. Though the FTN symbols can be signaled beyond the orthogonality limit in both time and frequency, for illustration the compression is shown only on the time axis. In any case the FTN symbols contribute both to ISI and ICI; the ISI/ICI is conceptually shown in Figure 2.1 for a single FTN symbol.

### 2.1 Transmission scheme

The information symbols are assumed to be independent and identically distributed (IID) with unit power and the power spectral density of the Additive White Gaussian Noise (AWGN) process is  $N_0/2$ . The modulation type chosen is offset-Quadrature Amplitude Modulation (OQAM) generally referred to as OFDM/OQAM in literature [Cha66, Sal67, BD74]. OFDM/OQAM allows the use of well localized pulses as pulse shaping filters resulting in transmission at high data rates through wireless channels [Bol03], while in the conventional method of OFDM/QAM it is not possible [LFAB95]. The use of pulse shaping

13

Figure 2.1: Illustration of FTN and Orthogonal symbols on the time-frequency axis.

filters in OFDM/OQAM also has advantages of reduced out-of-band emission and is more robust to carrier frequency offsets [Bol03, RH97]. An OQAM multicarrier modulated signal can be represented as

$$s(t) = \sum_{\ell=-\infty}^{\infty} \sum_{k=0}^{N-1} i^{k+\ell} x_{k,\ell} \ p\left(t-\ell\frac{T}{2}\right) e^{i\frac{2\pi}{T}kt},$$

(2.1)

where  $x_{k,\ell}$  refers to the real valued data symbols that are phase offset with the term  $i^{k+\ell}$  and varies depending on the sub-carrier k and time instance  $\ell$ . p(t) is generally a rectangular pulse with time period T in the case of conventional OFDM. In this work though only offset-QPSK is assumed, the results can be extended to higher order modulations. With offset-QPSK, the data symbols take the values of  $\pm 1$  which is not the case when higher order modulations are used.

In this work, the FTN system assumes data to be transmitted using Gaussian pulses g(t) as they have excellent time-frequency localization properties. The time period of the Gaussian pulse carrying an information symbol is assumed to be 3T for practical reasons, though in theory the pulse has infinite time support. In an FTN multicarrier system that uses Gaussian pulses for information transmission and OQAM modulation, the transmitted signal is written as

$$s(t) = \sum_{\ell = -\infty}^{\infty} \sum_{k=0}^{N-1} i^{k+\ell} x_{k,\ell} g\left(t - \ell T_{\Delta} \frac{T}{2}\right) e^{i2\pi \frac{F_{\Delta}}{T}kt},$$

(2.2)

where  $k, \ell$  refer to the sub-carrier and time indices respectively;  $T_{\Delta} \frac{T}{2}$  is the symbol period between two real valued data symbols  $(x_{k,\ell})$  and  $\frac{F_{\Delta}}{T}$  is the sub-carrier spacing. In an orthogonal system with OQAM modulation the time-frequency product would be

$$\left(T_{\Delta}\frac{T}{2}\right)\left(\frac{F_{\Delta}}{T}\right) = \frac{T_{\Delta}F_{\Delta}}{2}.$$

(2.3)

The modulated symbols are transmitted separately as real and complex parts, but at twice the rate of the complex valued symbols. The time frequency product of an orthogonal multicarrier modulation (MCM) with OQAM is  $\frac{1}{2}$ . That is, while  $T_{\Delta}F_{\Delta} = 1$  refers to an orthogonal system,  $T_{\Delta}F_{\Delta} < 1$  refers to a multicarrier system with FTN signaling. As a result,  $T_{\Delta}$  and  $F_{\Delta}$  can be viewed as compression factors in time and frequency respectively. We point out that although the product  $T_{\Delta}F_{\Delta}$  specifies the total time-bandwidth consumption of the system, the actual values of  $T_{\Delta}$  and  $F_{\Delta}$  are important and will be shown in later section. Henceforth, we refer to conventional data symbols being signaled at Nyquist's criterion for ISI free transmission as *orthogonal symbols* and those beyond Nyquist as *FTN symbols*.

There can be several approaches to realize transmission of FTN modulated symbols. One approach is by simply implementing Eqn. (2.2) as is. However, this is not an attractive option as it requires something similar to a Discrete Fourier Transform, but with fractional spacings. Efficient implementations for multicarrier modulations already exist in the form of IFFT, as used in OFDM-based systems. Hence an effort is made to retain this attractive option. However, using only the IFFT introduces complexity in a different dimension and the following section describe the impact of using rectangular windowed sinusoidal basis (basis functions for IFFT) on the overhead complexity. A feasible alternative solution is proposed and evaluated.

#### 2.1.1 Choice of orthogonal basis

In order to use IFFT for multicarrier modulation the Gaussian pulses are to be represented in an orthonormal set of basis functions. Each FTN symbol is represented on the basis functions spanning both time and frequency. The number of basis functions required in time is referred to as  $N_t$  and those in

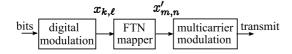

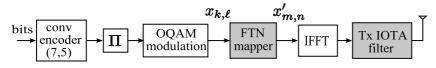

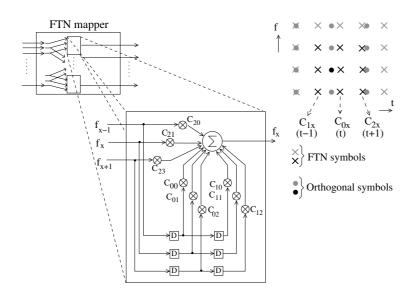

Figure 2.2: A general block diagram of the FTN transmitter using mapper.

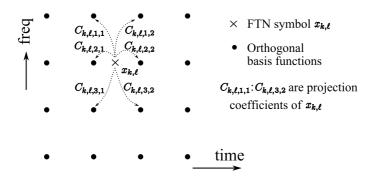

Figure 2.3: Illustration of FTN symbol projected on to an orthogonal basis.

frequency as  $N_f$ . Choosing  $N_t$  basis functions in time and  $N_f$  basis functions in frequency will require  $\mathcal{O}(N_t \times N_f)$  computations for each FTN symbol. Let  $\psi(t)$  be the basis pulse forming the orthonormal basis { $\psi_{m,n}(t)$ } defined as:

$$\psi_{m,n}(t) \triangleq i^{m+n} \ \psi\left(t - n\frac{T}{2}\right) \ e^{i2\pi \frac{1}{T}mt}.$$

(2.4)

The Gaussian pulses in an OQAM-based system are given by

$$g_{k,\ell}(t) \triangleq i^{k+\ell} g\left(t - \ell T_{\Delta} \frac{T}{2}\right) e^{i2\pi \frac{F_{\Delta}}{T}kt}, \qquad (2.5)$$

which allows us to write Eqn. (2.2) more compactly as

$$s(t) = \sum_{\ell=-\infty}^{\infty} \sum_{k=0}^{N-1} x_{k,\ell} g_{k,\ell}(t).$$

(2.6)

The representation of the Gaussian pulse in the basis will be the inner product between  $g_{k,\ell}(t)$  and  $\psi_{m,n}(t)$  as

$$C_{k,\ell,m,n} \triangleq \langle g_{k,l}(t), \psi_{m,n}(t) \rangle$$

=  $\Re \left\{ \int g_{k,\ell}(t) \psi_{m,n}^*(t) dt \right\},$  (2.7)

Figure 2.4: Illustration of mapping function on an orthogonal basis function at sub-carrier m and time instance n.

where  $C_{k,\ell,m,n}$  represents the projection coefficients of the Gaussian pulse on to the basis (This is also illustrated for one FTN symbol in Figure 2.3). In other words, the coefficients  $\{C_{k,\ell,m,n}\}$  represent the interference pattern of an FTN symbol at position  $(k,\ell)$  on a set of orthogonal basis functions in both time and frequency, and Eqn. (2.6) becomes

$$s(t) = \sum_{\ell=-\infty}^{\infty} \sum_{k=0}^{N-1} \sum_{m,n} x_{k,\ell} C_{k,\ell,m,n} \psi_{m,n}(t).$$

(2.8)

The process of representing the FTN symbols in the orthogonal basis is hereafter referred to as mapping and a block realizing it is referred to as a mapper. A general block diagram of the FTN transmitter using the mapper is shown in Figure 2.2. The mapper produces outputs  $x'_{m,n}$  by processing the incoming FTN symbols  $x_{k,\ell}$ . The number of symbols  $x'_{m,n}$  is  $T_{\Delta}F_{\Delta}$  times the number of symbols  $x_{k,\ell}$  for large blocklengths. For a given  $T_{\Delta}F_{\Delta}$ , the projection coefficients  $C_{k,\ell,m,n}$  correspond to a unique set of values that can be used to represent all the FTN symbols corresponding to that  $T_{\Delta}F_{\Delta}$ . The FTN mapper evaluates the output at each orthogonal sub-carrier m and time instance n for the incoming FTN symbols together with the help of pre-calculated projection coefficients. The FTN mapper output  $(x'_{m,n})$  can be written as

$$x'_{m,n} = x_{k_1,\ell_1} \cdot C_{k_1,\ell_1,m,n} + x_{k_2,\ell_2} C_{k_2,\ell_2,m,n} + x_{k_3,\ell_3} \cdot C_{k_3,\ell_3,m,n} + \dots,$$

=  $\sum_{p,q} x_{k_p,\ell_q} \cdot C_{k_p,\ell_q,m,n},$  (2.9)

where  $C_{k_p,\ell_q,m,n}$  correspond to the pre-calculated projection coefficients,  $x'_{m,n}$  is the value signaled at basis function  $\psi_{m,n}(t)$  and  $x_{k_p,\ell_q}$  are the FTN symbols. Eqn. (2.9) is illustrated in Figure 2.4 for one orthogonal sub-carrier and time instance (m, n).

#### Rectangular windowed sinusoidal basis

For the multicarrier modulation following the mapper, an immediate choice for  $\psi(t)$  in Eqn. (2.4) is the rectangular windowed sinusoidal basis (also referred to as rectangular basis for short in this work) in order to use IFFT for multicarrier modulation. The rectangular pulse is optimal in time. However, in frequency it is not very localized and its spectral decay is slow. As a consequence a large set of coefficients are required to represent every Gaussian pulse that carry information implying a significant impact on the FTN transmitter complexity. If just an IFFT is used for multicarrier modulation, we take  $\psi(t) = \operatorname{rect}(t)$  and the transmitted signal will be

$$s(t) = \sum_{n=-\infty}^{\infty} \sum_{m=0}^{N-1} i^{m+n} x'_{m,n} \cdot \operatorname{rect}\left(t - n\frac{T}{2}\right) e^{i\frac{2\pi}{T}mt}, \qquad (2.10)$$

where  $x'_{m,n}$  represents the projection of the transmission signal s(t) onto  $\psi_{m,n}(t)$ .

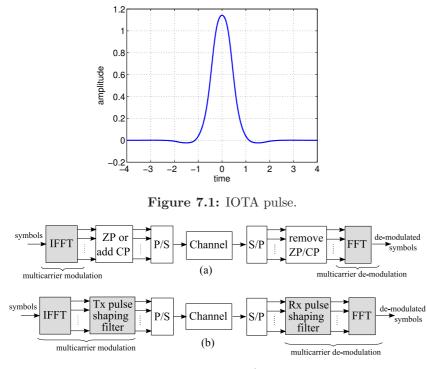

#### **IOTA** basis

It is important to identify a basis that is compact in both time and frequency. This will ensure fewer orthogonal basis functions required to represent an FTN symbol, reducing the computational complexity. A more suitable choice is a pulse such as the Isotropic Orthogonal Transform Algorithm (IOTA) [LFAB95] pulse (c.f Figure 7.1). The IOTA pulse retains the property of time-frequency compactness as it is derived from the Gaussian pulse and is a strong candidate for usage in FTN multicarrier systems. The orthogonal basis generated from the IOTA pulse can be written as

$$\mathfrak{S}_{m,n}(t) = i^{m+n} \cdot e^{i2\pi m f t} \cdot \mathfrak{S}\left(t - n\frac{T}{2}\right).$$

(2.11)

The IOTA pulse guarantees orthogonality only for real symbols, therefore OQAM systems are considered and the term  $i^{m+n}$  in Eqn. (2.11) is the phase offset factor. Eqn. (2.11) refers to multicarrier modulation using OQAM with

Figure 2.5: Block diagram of the proposed FTN transmitter.

IOTA as the orthogonal basis with time shift  $\frac{T}{2}$ . By using IOTA as the orthogonal basis, i.e.,  $\psi(t) = \Im(t)$ , the transmitted signal will be

$$s(t) = \sum_{n=-\infty}^{\infty} \sum_{m=0}^{N-1} i^{m+n} x'_{m,n} \cdot \Im\left(t - n\frac{T}{2}\right) e^{i\frac{2\pi}{T}mt}.$$

(2.12)

A block diagram of the FTN transmitter with the mapper and multicarrier modulation using IOTA is shown in Figure 2.5. An outer convolutional code is introduced prior to the FTN mapper to help in better decoding of the FTN modulated symbols at the receiver. The blocks highlighted in grey are those specific to the FTN system. Bypassing these during transmission will result in a multicarrier modulated signal corresponding to a conventional orthogonal (OFDM) system. IOTA in OFDM systems has previously been described in [SSL02, MJ05] where a pulse shaping filter is employed as a post processing block retaining the hardware efficient IFFT as a part of the IOTA multicarrier modulation. The realization of IOTA based multicarrier modulation using IFFT and a pulse shaping filter is derived from Eqn. (2.12) which can be re-written as

$$s(t) = \sum_{n=-\infty}^{\infty} i^n \Im\left(t - n\frac{T}{2}\right) \cdot \sum_{m=0}^{N-1} i^m x'_{m,n} e^{i\frac{2\pi}{T}mt}.$$

(2.13)

The term  $X_n''(t) \triangleq \sum_{m=0}^{N-1} i^m x'_{m,n} e^{i\frac{2\pi}{T}mt}$  refers to the inverse Fourier transform of the input  $i^m x'_{m,n}$ , hence

$$s(t) = \sum_{n=-\infty}^{\infty} i^n \Im\left(t - n\frac{T}{2}\right) \cdot X_n''(t)$$

$$= \sum_{n=-\infty}^{\infty} \Im\left(t - n\frac{T}{2}\right) \cdot X_n'(t), \qquad (2.14)$$

where  $X'_n(t) \triangleq i^n X''_n(t)$ . If  $X'_n(t)$  is to be represented as a discrete sequence, the inverse Fourier transform should be replaced by an Inverse Discrete Fourier Transform (IDFT). IDFT can be used instead of the inverse Fourier Transform

provided that the number of points of IDFT is equal to or greater than the number of samples of the discrete sequence  $x'_{m,n}$  in order to avoid aliasing [PM04]. If the sampling period  $T_s$  is related to T the duration of the discrete time sequence and N the number of points of IDFT as  $T_s = T/N$  then the transmitted discrete time sequence will be

$$s(pT_s) = \underbrace{\sum_{n=-\infty}^{\infty} \Im\left(pT_s - n\frac{T}{2}\right)}_{\text{IOTA pulse shaping}} \cdot \underbrace{X'_n(pT_s)}_{\text{IFFT}}.$$

(2.15)

It is also well known that an efficient implementation approach for the IDFT is the IFFT. This implies Eqn. (2.14), which corresponds to an IOTA based multicarrier modulation, can be realized as an IFFT followed by a post filtering operation as indicated in Eqn. (2.15) and Figure 2.5. Choosing IOTA based MCM results in reduced computational complexity. The hardware architecture and implementation of IOTA pulse shaping filter is discussed in greater detail in Chapter 7.

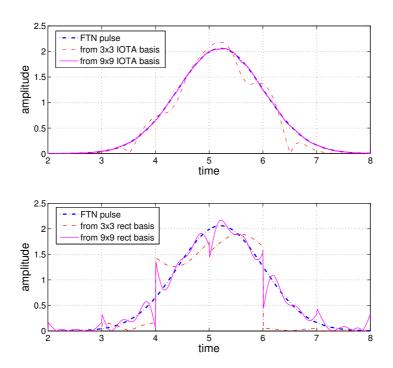

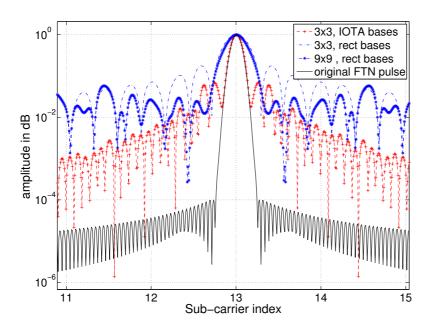

#### Rectangular vs. IOTA basis

In the following we will compare the IOTA and rectangular basis with respect to the requirements on the number of basis functions required across time  $(N_t)$  and frequency  $(N_f)$  to represent an FTN pulse. The aim is to obtain a reasonable number for  $N_t$  and  $N_f$  such that the representation is realized by a small set of basis functions and at the same time the reconstruction would be as close to the original FTN pulse as possible. The FTN pulse  $g_{k,\ell}(t)$  can be represented using  $N_t \times N_f$  projection coefficients  $C_{k,\ell,m,n}$  as

$$g_{k,\ell}(t) \approx \sum_{m} \sum_{n} C_{k,\ell,m,n} \ \psi_{m,n}(t).$$

$$(2.16)$$

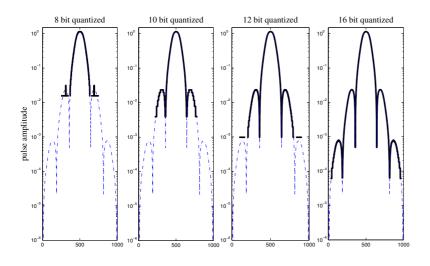

As  $N_t$  and  $N_f$  become large, the FTN pulse representation becomes more accurate but at the same time introduce higher computational complexity. The investigated combinations of  $N_t \times N_f$  are  $2 \times 2$ ,  $3 \times 3$ ,  $3 \times 2$ ,  $3 \times 4$ ,  $5 \times 5$  and  $9 \times 9$  for both IOTA and rectangular basis. Higher values of  $N_t \times N_f$  are not attractive for low complexity implementations. Furthermore,  $N_t$  and  $N_f$ are not dependent on  $T_{\Delta}F_{\Delta}$  but on the choice of the basis pulse. This is because, irrespective of the spacing between the adjacent pulses, each pulse in itself has to be represented with the best possible accuracy. Figure 2.6 shows a comparison between the FTN pulses reconstructed from both IOTA and rectangular windowed sinusoidal basis for two cases,  $N_t \times N_f = 3 \times 3$  and  $9 \times 9$ . The upper plot in Figure 2.6 shows the original and the reconstructed FTN

**Figure 2.6:** Comparison of FTN pulse (of time period 3T) reconstructed from IOTA and rectangular windowed sinusoidal basis.

pulse from an IOTA basis using  $3 \times 3$  and  $9 \times 9$  basis functions, while the lower plot shows the reconstruction using the same combination from the rectangular basis. The reconstruction using  $3 \times 3$  IOTA basis functions is fairly good while with  $9 \times 9$ , the reconstruction is indistinguishable as it overlaps on the original pulse. However, the reconstruction from  $3 \times 3$  rectangular windowed sinusoidal basis functions is not satisfactory, while the  $9 \times 9$  is better but is still worse than the  $3 \times 3$  IOTA. This argument is further supported from the frequency response plots of the reconstructed pulses. Figure 2.7 shows the spectrum of the pulses reconstructed from IOTA and rectangular basis on a particular subcarrier. The ICI introduced by representing the Gaussian pulse in the IOTA basis is far less compared to the rectangular basis. Further, the main lobe of the IOTA reconstruction is same as the original FTN pulse, while the one from rectangular basis has poor reconstruction as well as significant ICI. The other

Figure 2.7: Spectrum of reconstructed pulse on a certain sub-carrier.

evaluated combinations were discarded for the following reasons:

- i)  $2 \times 2$  projections were not satisfactory in either IOTA or rectangular windowed sinusoidal basis. The number being even did not distribute itself uniformly over the FTN symbol either in time or frequency. Hence one side of the FTN symbol energy was lost in most cases resulting in poor representation of the pulse.

- ii)  $3 \times 2$  projections produced fair reconstructions in a few cases, but failed in certain configurations.

- iii)  $3 \times 4$  projections gave satisfactory results but not considered due to the extra processing requirements compared to the  $3 \times 3$  configuration.

Furthermore, IOTA filtering has been used in orthogonal multicarrier systems to avoid the cyclic prefix [LFAB95, JL03] and is now a part of the 3GPP standard [3GP04]. The effective overhead due to FTN signaling is mainly due to the mapper. By using the IOTA, the number of projections for each pulse  $g_{k,\ell}(t)$ can be as low as  $3 \times 3$  [DRAO09]. Due to the fractional spacing, the FTN pulse may be represented by the  $N_t \times N_f$  basis functions at varying accuracies. With 3 sub-carriers and 3 time instances of the basis the best represented pulse retains up to 99.5% of the energy of an FTN pulse while the least accurate representation preserves 87% of the energy.

# 2.2 Alternate transmission methods

This section briefly mentions two other ways by which FTN signaling can be realized, and their disadvantages when considered for hardware realization.

#### Method1

Fractional fast Fourier transforms [BS91] can be used to realize Eqn. (2.2) as is by having  $T_{\Delta} = 1$  and  $F_{\Delta} < 1$ . In [BS91], the fractional Fourier transform of a sequence **x** is defined as

$$X_k(\mathbf{x},\alpha) = \sum_{n_{\rm frac}=0}^{N_{\rm frac}-1} x_{n_{\rm frac}} e^{i2\pi n_{\rm frac}k\alpha}, \qquad (2.17)$$

where the parameter  $\alpha$  defines the fractional spacing,  $N_{\rm frac}$  the length of the transform and all other variables having their conventional meaning as in a Fourier transform [PM04]. Apparently, it seems that a single module of fractional FFT will be sufficient. However, if one would like to have different  $T_{\Delta}F_{\Delta}$  in order to achieve varying bandwidth efficiencies, then the fractional FFT should be capable of carrying out the transform for different fractional spacings. Furthermore, if in a system the sub-carrier length varies the fractional FFT module should also be capable of such an adaptation. Thus, the fractional FFT should be reconfigurable in both number of points of the transform as well as the fractional spacing between the frequencies of the transform. Such a fractional FFT might not have the regularity that is found in conventional FFTs, using radix-2, radix-4 [PM04] etc., as the building blocks for the transform. Lastly, fractional FFTs brings up the requirement of a specialized multicarrier modulation scheme resulting in a system that requires drastic changes in design and implementation. Thus, it deviates significantly from conventional implementations limiting co-existence between FTN and orthogonal systems.

#### Method2

In the second alternative approach, multiple IFFTs can be used to obtain the FTN modulated signal. For example, an FTN modulated signal where  $T_{\Delta}F_{\Delta}=0.5$  with  $T_{\Delta}=\frac{1}{2}$  and  $F_{\Delta}=1$  can be evaluated as

$$s(t) = \mathcal{F}^{-1}\{X_1(f)\} + \mathcal{F}^{-1}\{X_2(f) \ e^{-i2\pi f \frac{T}{2}}\}$$

(2.18)

$$s(t) = x_1(t) + x_2\left(t - \frac{T}{2}\right),$$

(2.19)

and an FTN system with  $T_{\Delta}F_{\Delta} = \frac{1}{3}$  would require 3 IFFTs, evaluated as

$$s(t) = \mathcal{F}^{-1}\{X_1(f)\} + \mathcal{F}^{-1}\{X_2(f) \ e^{-i2\pi f \frac{T}{3}}\} + \mathcal{F}^{-1}\{X_3(f) \ e^{-i2\pi f \frac{2T}{3}}\}$$

$$s(t) = x_1(t) + x_2\left(t - \frac{T}{3}\right) + x_3\left(t - \frac{2T}{3}\right).$$

(2.20)

The above discussed alternative was proposed in [DRO11] and realizes FTN by signaling faster in time. A similar approach proposed in [WPID11] realizes FTN by squeezing the sub-carriers closer together with  $T_{\Delta} = 1$  and  $F_{\Delta} = \frac{1}{2}$ . In that case, the transmitted signal would be

$$s(t) = \mathcal{F}^{-1}\{X_1(f)\} + \mathcal{F}^{-1}\left\{X_2\left(f - \frac{1}{2T}\right)\right\}$$

(2.21)

$$(t) = x_1(t) + x_2(t) e^{i\pi t \frac{1}{T}}.$$

(2.22)

Eqns. (2.18) and (2.19) form the time shift property of the Fourier transform while Eqns. (2.21) and (2.22) correspond to the frequency shift/complex modulation property [PM04].

s

[WPID11] achieves FTN by having information carrying symbols closer in frequency as in Eqn. (2.21). This is achieved by the use of multiple IFFTs and some post-processing in the form of complex phase rotators. Further, the complex phase rotators that need to be multiplied in Eqn. (2.22) vary depending on the choice of frequency spacing.

The alternative proposed in [DRO11] achieves FTN by signaling faster in time and also requires multiple IFFTs. This approach needs pre-processing before carrying out the IFFTs as shown in Eqn. (2.18).

The multiple IFFTs approach suffer from some drawbacks when it comes to overhead complexity in realizing FTN signaling. Changing the FTN parameters, such as time-frequency spacing, requires substantial changes in hardware such as the requirement of several FFTs that take up significant hardware resources. Further, varying number of sub-carriers in the system brings in

Figure 2.8: Block diagram of the FTN receiver.

additional complexity. Though these factors can be accounted by realizing the worst case scenario for the system, it poses a risk of very large hardware overhead.

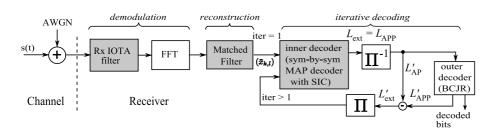

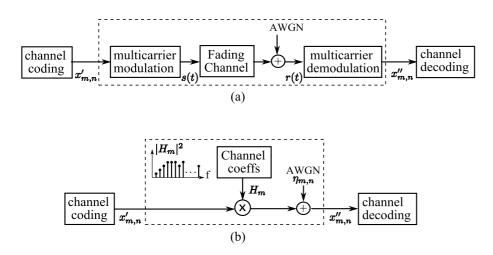

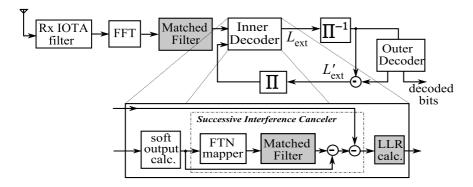

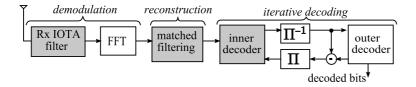

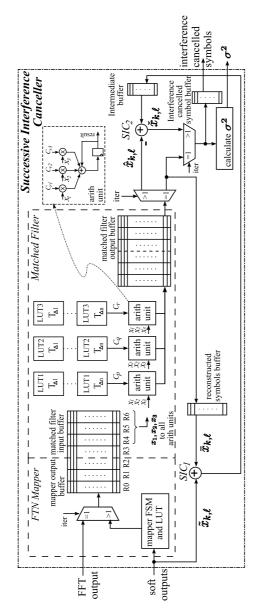

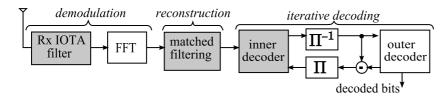

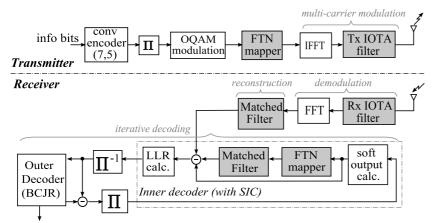

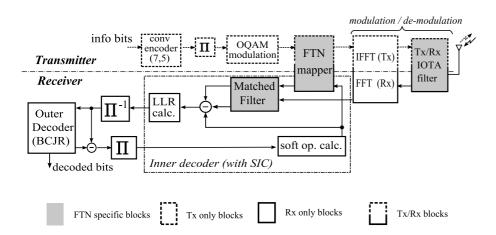

# 2.3 Decoding FTN modulated symbols

The decoding scheme proposed in this article is comprised of an iterative detector with Matched Filter (MF) and Successive Interference Cancellation (SIC). The decoding algorithm is primarily conceived in [RA09b] but has been modified for hardware efficient implementation in this work by re-use of processing blocks in different scenarios. Figure 2.8 shows the block diagram of the receiver and custom blocks specific to FTN signaling are highlighted in grey. The subsections described henceforth are ordered in the way the received signals are processed. The modulated signal s(t) is assumed to be transmitted through an AWGN channel as shown in Figure 2.8. The multicarrier demodulation is assumed to be carried out in the same way as the two step approach of multicarrier modulation in the transmitter discussed in Section 2.1.1 under '**IOTA basis**'.

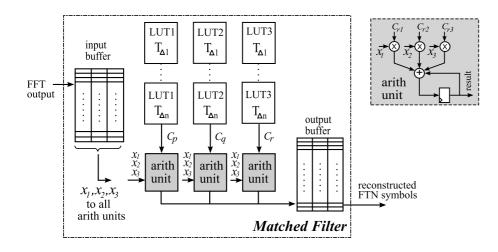

## 2.3.1 Matched Filtering for FTN symbol reconstruction

The multicarrier demodulated signal represents the transmitted projections of FTN symbols affected by an AWGN channel  $\eta_{m,n}$ . In order to decode the received FTN modulated block into binary information, it has to be reconstructed back from the projections. The approximation of the original FTN symbol is obtained from the received symbols and the pre-computed unique projection coefficients for that FTN symbol (interference pattern  $C_{k,\ell,m,n}$ ) using an MF.

The MF in Figure 2.8 reconstructs the FTN symbols as

$$\bar{x}_{k,\ell} = \sum_{m,n} C_{k,\ell,m,n} \quad (x'_{m,n} + \eta_{m,n}), \qquad (2.23)$$

where  $x'_{m,n}$  are the accumulated projections of FTN symbols transmitted over an AWGN channel.  $C_{k,\ell,m,n}$  correspond to the same pre-computed projection coefficients that is used in the transmitter. The so reconstructed FTN symbols,  $\bar{x}_{k,\ell}$ , are not free from ISI/ICI as they were originally non-orthogonal when transmitted. As a result, the reconstructions comprise information of the symbol of interest, interference (both ISI and ICI) together with a noise component. The process of matched filtering results in the noise being colored and is denoted as  $\eta'_{k,\ell}$ . Eqn. (2.23) becomes

$$\bar{x}_{k,\ell} = \sum_{m,n} C_{k,\ell,m,n} x'_{m,n} + \eta'_{k,\ell}.$$

(2.24)

Substituting Eqn. (2.9) for  $x'_{m,n}$  in Eqn. (2.24) we get

$$\bar{x}_{k_{1},\ell_{1}} = \sum_{m,n} C_{k_{1},\ell_{1},m,n} \cdot \left( \underbrace{x_{k_{1},\ell_{1}} C_{k_{1},\ell_{1},m,n}}_{\text{signal component at }k_{1},\ell_{1}} + \underbrace{\sum_{(k_{p},\ell_{q})\neq(k_{1},\ell_{1})} x_{k_{p},\ell_{q}} C_{k_{p},\ell_{q},m,n}}_{(2.25)} + \eta_{k_{1},\ell_{1}}' \right)$$

interference+noise at index  $k_1, \ell_1$

From Eqn. (2.25), it can be seen that the reconstructed FTN symbol  $\bar{x}_{k_1,\ell_1}$  at sub-carrier  $k_1$  and time instance  $\ell_1$ , has signal component  $x_{k_1,\ell_1}$  as well as interferences from neighboring symbols  $x_{k_2,\ell_2}, x_{k_3,\ell_3}, \ldots$ , and colored noise  $\eta'_{k_1,\ell_1}$ . The signal component from the reconstructed symbols can be obtained through iterative decoding. The proposed decoder consists of symbol-by-symbol sub-optimal maximum aposteriori (MAP) decoding with successive interference cancellation as the inner decoder and a standard BCJR for the convolutional encoder<sup>1</sup> as shown in Figure 2.8.

<sup>&</sup>lt;sup>1</sup>The codes used in this paper are low memory codes so that the BCJR is of practical complexity.

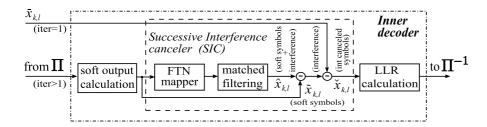

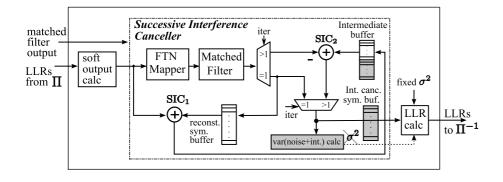

# 2.3.2 Inner Decoder

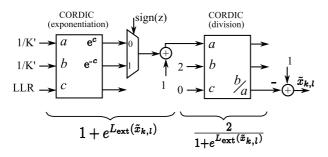

The inner decoder consists of soft output calculation, SIC and LLR calculation blocks as shown in Figure 2.9. The blocks within the inner decoder are described in the following subsections in the order of their processing.

#### Soft Output Calculation

The soft output calculation block evaluates the soft symbols from the loglikelihood ratios (LLRs) received from the outer decoder as

$$\tilde{x}_{k,\ell} = \{+1 \cdot P(x_{k,\ell} = +1)\} + \{-1 \cdot P(x_{k,\ell} = -1)\},\$$

$$= P(x_{k,\ell} = +1) - P(x_{k,\ell} = -1),\$$

$$= (1 - P(x_{k,\ell} = -1)) - P(x_{k,\ell} = -1),\$$

$$= 1 - \frac{2}{1 + e^{\text{LLR}(x_{k,\ell})}},$$

(2.26)

where  $x_{k,\ell}$  are OQAM modulated symbols. The Likelihood ratio (LR) and LLR are assumed to have the following definitions:

Likelihood Ratio

$$(x_{k,\ell}) = \frac{\mathrm{P}(x_{k,\ell} = +1|\mathbf{x})}{\mathrm{P}(x_{k,\ell} = -1|\mathbf{x})},$$

(2.27)

and

$$LLR(x_{k,\ell}) = \ln\left(\frac{P(x_{k,\ell} = +1|\mathbf{x})}{P(x_{k,\ell} = -1|\mathbf{x})}\right),$$

(2.28)

where  $\mathbf{x}$  represents the received sequence. From Eqn. (2.28) it can be deduced that

$$P(x_{k,\ell} = -1|\mathbf{x}) = \frac{1}{1 + e^{\text{LLR}(x_{k,\ell})}}.$$

(2.29)

#### Successive Interference Cancellation

The concept of SIC is well known and widely used in the field of communications and is applicable to a broad class of problems in the field. In a multiuser system, it can used to extract individual user data [Ver98, RSAA98, WP99]. In the present context of FTN, SIC is used to repeatedly cancel out the induced ISI and ICI arising due to FTN signaling.

The processing blocks in SIC for FTN signaling are shown inside the dashed box in Figure 2.9. The SIC blocks are re-used from those designed specifically

Figure 2.9: Inner decoder and its component processing blocks.

for FTN signaling, i.e., FTN mapper and MF. The symbols  $\hat{x}_{k,\ell}$  at the output of the mapper—MF cascade (Figure 2.9) represents the amount of information the soft symbol holds and the interference it experiences from the neighboring symbols (Eqn. (2.25)) due to FTN signaling. Eqn. (2.25) can be expressed more generally as

$$\hat{x}_{k,\ell} = \underbrace{\widetilde{x}_{k,\ell}}_{\text{(p,q)} \neq (k,\ell)} + \underbrace{\sum_{(p,q) \neq (k,\ell)}}_{(p,q) \neq (k,\ell)} \tilde{x}_{p,q} + \eta'_{k,\ell}, \qquad (2.30)$$

where  $\tilde{x}_{k,\ell}$  is the signal component and  $\tilde{x}_{p,q}$  is the interference component. The soft outputs  $(\tilde{x}_{k,\ell})$  when subtracted from its corresponding output at the mapper-matched filter cascade (Eqn. (2.30)) leaves behind the total interference plus noise that the soft symbol experiences and is given as

$$\hat{x}_{k,\ell} - \tilde{x}_{k,\ell} = \sum_{(p,q) \neq (k,\ell)} \tilde{x}_{p,q} + \eta'_{k,\ell}.$$

(2.31)

Once an estimate of the interference plus noise is calculated, it can be readily canceled out from the received symbols to leave behind a cleaner signal component and is given as

nt. canc. symbol reconst. symbol estimate of int.+noise

$$\overbrace{\check{x}_{k,\ell}}^{\text{reconst. symbol}} = \overbrace{\bar{x}_{k,\ell}}^{\text{reconst. symbol}} - \overbrace{\{\hat{x}_{k,\ell} - \tilde{x}_{k,\ell}\}}^{\text{estimate of int.+noise}},$$

(2.32)

where  $\check{x}_{k,\ell}$  represents the interference canceled symbols and  $\{\hat{x}_{k,\ell} - \tilde{x}_{k,\ell}\}$  the estimate of the interference plus noise.  $\bar{x}_{k,\ell}$  represents the received symbols at the output of the first MF after the FFT (in Figure 2.8). The interference canceled symbols  $(\check{x}_{k,\ell})$  are now used as the new set of received symbols to calculate the LLRs in the inner decoder. During each new iteration of decoding in the inner decoder, the interference estimates improve and SIC cleans the reconstructed FTN symbols of noise and interference resulting in better decoding performance.

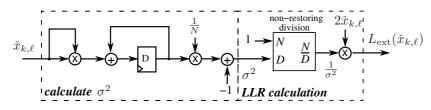

#### LLR calculation

The calculation of the LLRs in the inner decoder is derived with the assumption of additive white Gaussian noise. It turns out that the equation to calculate LLRs is very simple for the symbol-by-symbol MAP decoding (and can also be found in [LC04]). The LLRs are calculated as

$$\mathcal{L}_{\text{ext}}\{\check{x}_{k,\ell}\} = \ln\left\{\frac{\mathcal{P}(\check{x}_{k,\ell} = +1|\mathbf{x})}{\mathcal{P}(\check{x}_{k,\ell} = -1|\mathbf{x})}\right\},\tag{2.33}$$

which simplifies to

$$\mathcal{L}_{\text{ext}}\{\check{x}_{k,\ell}\} = \frac{2\;\check{x}_{k,\ell}}{\sigma_{N+I}^2},\tag{2.34}$$

where  $\check{x}_{k,\ell}$  refers to the interference canceled symbols of block size  $K(=M \times N)$ . The variance estimate of the noise plus interference  $(\sigma_{N+I}^2)$  from FTN signaling is calculated as

$$\sigma_{N+I}^{2} = \operatorname{var}(\check{x}_{k,\ell}) - \operatorname{var}(x_{k,\ell})$$

$$\approx \frac{1}{K} \sum_{k,\ell} \check{x}_{k,\ell}^{2} - \frac{1}{K} \sum_{0}^{K-1} 1$$

$$= \frac{1}{K} \sum_{k,\ell} \check{x}_{k,\ell}^{2} - 1. \qquad (2.35)$$

In the first iteration, the inner decoder calculates the LLRs using the symbols reconstructed from matched filtering as there is no estimate of the interference. In subsequent iterations it is done on the interference canceled symbols. The inner decoder block directly calculates the extrinsic LLRs from the input LLRs. As a result, apriori LLRs need not be subtracted at the output of the inner decoder (see Figure 2.8).

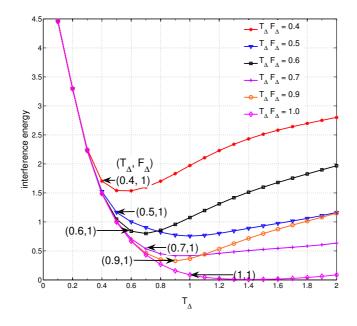

Figure 2.10: Plot showing the interference energy curves for different time-frequency spacings  $T_{\Delta}F_{\Delta}$ .

# 2.4 Choice of Time-Frequency spacing in FTN signaling

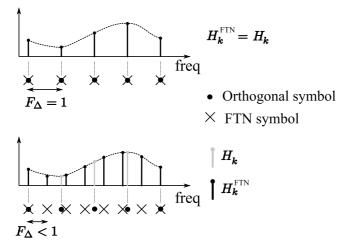

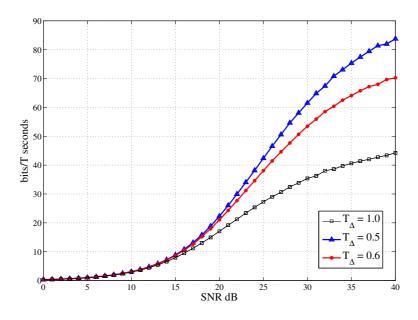

Prior to presenting the performance of the proposed receiver, we establish the reason for choosing a particular time and frequency spacing  $(T_{\Delta}, F_{\Delta})$ . Strictly speaking, though individual values of  $T_{\Delta}$  or  $F_{\Delta}$  are important, it is the product  $T_{\Delta}F_{\Delta}$  that defines the effective improvement in bandwidth usage. As a result, for any given product that attains a certain amount of bandwidth efficiency,  $T_{\Delta}$  and  $F_{\Delta}$  can theoretically take infinite number of values. However, it is important to choose the spacing such that the interference by the FTN symbols to its neighbors is minimal compared to the rest of the possible spacing alternatives. Figure 2.10 shows the plots of interference energy of FTN symbols to its neighbors as a function of the time spacing  $T_{\Delta}$ . The interference energy  $(E_{\text{int}})$ , on an FTN pulse at a certain index  $(k_1, \ell_1)$  from a set of surrounding

FTN pulses  $g_{k,\ell}(t)$ , as a function of  $T_{\Delta}$  for a given product  $T_{\Delta}F_{\Delta}$  is given by

$$E_{\text{int}}(T_{\Delta})|_{T_{\Delta}F_{\Delta}=P} = \underbrace{\sum_{k,\ell} |\langle g_{k,\ell}(t), g_{k_1,\ell_1}(t) \rangle|^2}_{\text{total energy at } (k_1,\ell_1)} - \underbrace{|\langle g_{k_1,\ell_1}(t), g_{k_1,\ell_1}(t) \rangle|^2}_{\text{energy of symbol at } (k_1,\ell_1)},$$

(2.36)

where  $P = \{0.4, 0.5, 0.6, 0.7, 0.9, 1.0\}$  and  $g_{k,\ell}(t)$  refers to a Gaussian pulse g(t)at sub-carrier k and time instance  $\ell^2$ . The first term on the right hand side of Eqn. (2.36) gives the total interference of all FTN pulses,  $g_{k,\ell}(t)$ , on the FTN pulse at  $(k_1, \ell_1)$ . From this the second term, which represents the energy on the FTN pulse at  $(k_1, \ell_1)$ , is subtracted to obtain the total interference. Each curve represents a fixed time-frequency spacing  $(T_{\Delta}F_{\Delta} \leq 1)$  with interference energy along y-axis, as we vary  $T_{\Delta}$  along the x-axis. From the figure it is evident that when spacing  $T_{\Delta}$  is very small implying that the symbols are very close to each other the total interference on any symbol from its neighbors is very high. Similar is the case when  $T_{\Delta}$  is large (because  $F_{\Delta}$  turns out to be very small). These extreme values can be ignored outright as a large amount of induced interference will have an impact on the decoding performance. The optimal operating points would be those where the interference energy is at its least. At these optimal points, the induced ISI and ICI due to FTN signaling will be minimal for the given product  $T_{\Delta}F_{\Delta}$  and helps in better decoding at the receiver. We strongly believe that this optimizes the system. However, the system is operated slightly away from the optimal operating points such that  $F_{\Delta} = 1$  always<sup>3</sup>, as indicated in Figure 2.10. With this, by simply changing the parameter  $T_{\Delta}$ , different  $T_{\Delta}F_{\Delta}$  can be accomplished.

For the  $T_{\Delta}F_{\Delta} = 0.5$  curve, an operating point at  $T_{\Delta} = 1$  is a more appropriate choice in the context of minimal interference than the chosen point at  $T_{\Delta} = 0.5$ . However, this has not been considered keeping in mind the hardware implementation. A homogeneous choice of  $T_{\Delta}$  and  $F_{\Delta}$  results in simplified computational units as well as the control unit that manages the data flow. It will also be shown later that the chosen operating points result in a more efficient hardware implementation inspite of the higher interference.

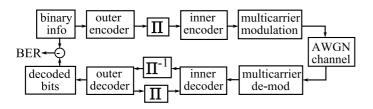

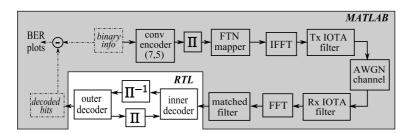

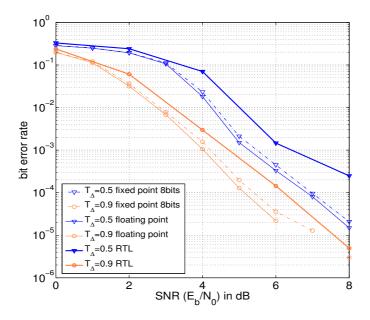

**Figure 2.11:** System setup of FTN transceiver to evaluate the decoder performance.

# 2.5 System setup

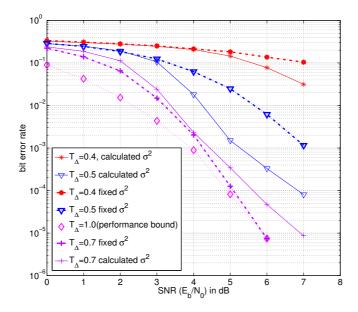

The performance of the FTN decoder is evaluated in MATLAB by using the system setup shown in Figure 2.11. The sequence of blocks **outer encoder interleaver - inner encoder - multicarrier modulation** correspond to the FTN transmitter shown in Figure 2.5. The so generated symbols are transmitted through an AWGN channel. The receiver chain is a generalization of Figure 2.8. We measure the performance in terms of the SNR, average energy per bit over  $N_0$  ( $E_b/N_0$ ). Random interleaving is assumed during the simulations. The information block size is chosen by specifying the number of sub-carriers N and time instances M. For simulations, a system with 1000 sub-carriers for 20 time instances was chosen as the block size. A total of about 1M information bits are decoded for each SNR and per FTN configuration ( $T_{\Delta}$ ). The number of decoding iterations in the setup is also parameterizable but is fixed at 8.

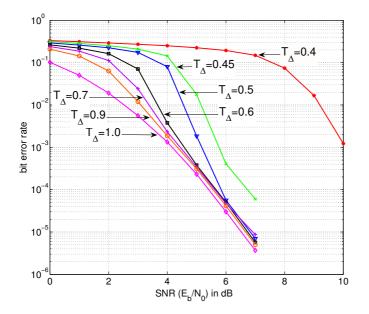

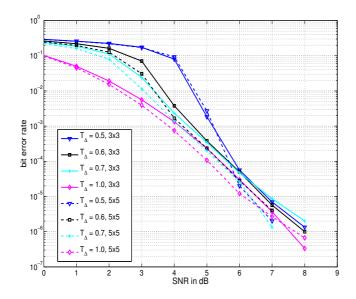

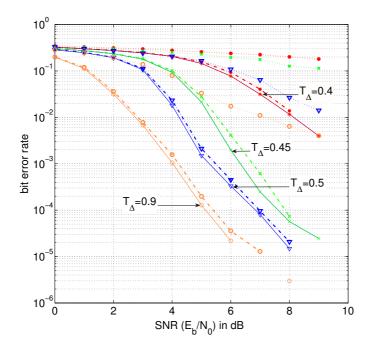

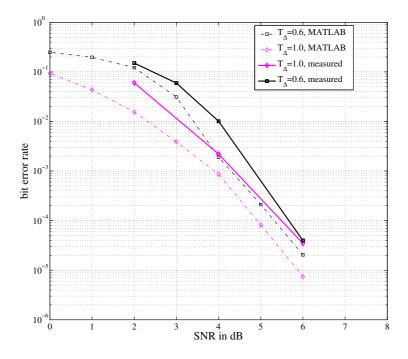

# 2.6 Receiver performance