| Field Frogrammable Gate Arrays and Recomigurable Computing in Automatic Com | liOi |

|-----------------------------------------------------------------------------|------|

| Wilhelmsson, Carl                                                           |      |

| 2007                                                                        |      |

#### Link to publication

Citation for published version (APA): Wilhelmsson, C. (2007). Field Programmable Gate Arrays and Reconfigurable Computing in Automatic Control. [Licentiate Thesis, Combustion Engines].

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or recognise.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

**PO Box 117** 221 00 Lund +46 46-222 00 00

# Field Programmable Gate Arrays and Reconfigurable Computing in Automatic Control

#### Carl Wilhelmsson

Thesis for the Degree of Licentiate in Engineering

Division of Combustion Engines Department of Energy Sciences Lund University

## Field Programmable Gate Arrays and Reconfigurable Computing in Automatic Control

## Field Programmable Gate Arrays and Reconfigurable Computing in Automatic Control

Carl Wilhelmsson

Division of Combustion Engines

Department of Energy Sciences

Lund University

Lund. December 2007

Till min Ella och min familj

Division of Combustion Engines Department of Energy Sciences Lund University Box 118 SE-221 00 LUND Sweden

ISSN 0282-1990 ISRN LUTMDN/TMHP--07/7050--SE

© 2007 by Carl Wilhelmsson. All rights reserved. Printed in Sweden by Media-Tryck. Lund 2007

## Acknowledgements

The first person I would like to thank for his support and understanding is Per Tunestål. Per has as my supervisor been an excellent mentor for me in the process of 'maturing' academically. I want to thank my love Ella for sharing her life with me, Ella has patience with me, my stubbornness, curiosity and restlessness in a way which I never hoped to find before I meet her. My brothers and parents, supporting me now and before are very important persons in my life, have always been and will always be. The rest of my family are also precious to me. Friends are important to have, in good times and in bad, I have good friends which deserves appreciation, you know who you are. The department has a lot of young employees and the atmosphere is open minded and good. I especially want to thank Thomas for good friendship on and off work, sharing a great interest in motorbikes. Andreas, Håkan, Leif and Jari have been very good friends at work before they moved on to new challenges. Professor Bengt Johansson deserves an acknowledgement for setting up an adequately founded and creative research environment, it is inspiring to work in collaboration with large and market leading companies. I also want to thank professor Rolf Johansson and professor Anders Rantzer for providing a lot of important automaticcontrol ideas and support. The help of Leif Andersson has been valuable while typesetting this thesis. The technicians have helped me a lot in the workshop keeping up my interest in workshop work in different ways. I want to thank my friends at Toyota, especially Moriya Hidenori for tutoring me both on and off work in Japan 2004, putting his own life in second hand sharing a fantastic half year with me in Susono. Yanagihara Hiromichi, also with Toyota, helped me to get to Japan and has maintained contact with me since, keeping an eye on me and my research. Finally to those not mentioned here I am not less grateful.

Carl

Acknowledgements

### **Preface**

#### **Publications**

#### Model based engine control using ASICs

Engine Control, Simulation and Modeling (E-COSM) - Rencontres Scientifiques de l'IFP

Carl Wilhelmsson, Per Tunestål, Bengt Johansson Division of Combustion Engines, Department of Energy Sciences, Faculty of Engineering, Lund University

Poster presented by the first author and Per Tunestål at the New Trends in Engine Control, Simulation and modeling, Rueil-Malmaison, France, October 2006

#### **FPGA Based Engine Feedback Control Algorithms**

Fédération Internationale des Sociétés d'Ingénieurs des Techniques de l'Automobile (FISITA) Technical paper F2006P039

Carl Wilhelmsson, Per Tunestål, Bengt Johansson Division of Combustion Engines, Department of Energy Sciences, Faculty of Engineering, Lund University

Presented by the first author at the 31st FISITA World Automotive Congress, Yokohama, Japan, October 2006

#### An Ultra High Bandwidth Automotive Rapid Prototype System

International Federation of Automatic Control (IFAC) Technical Paper AAC07-057

Carl Wilhelmsson, Per Tunestål, Bengt Johansson Division of Combustion Engines, Department of Energy Sciences, Faculty of Engineering, Lund University

Presented by the first author at the Fifth IFAC Symposium on Advances in Automotive Control, Aptos, CA, USA, August 2007

#### **Peripheral Publications**

## **Combustion Chamber Wall Temperature Measurement and Modeling During Transient HCCI Operation**

Society of Automotive Engineering (SAE) Technical Paper 2005-01-3731

*Carl Wilhelmsson*, Andreas Vressner, Per Tunestål and Bengt Johansson Division of Combustion Engines, Department of Energy Sciences, Faculty of Engineering, Lund University

Gustaf Särner, Marcus Aldén Division of Combustion Physics, Faculty of Engineering, Lund University

Presented by the first author at the Power train & Fluid Systems Conference & Exhibition, San Antonio, TX, USA, October 2005

## The Effect of Displacement on Air-Diluted Multi-Cylinder HCCl Engine Performance

Society of Automotive Engineering (SAE) Technical Paper 2006-01-0205

Jari Hyvönen, Carl Wilhelmsson, Bengt Johansson Division of Combustion Engines, Department of Energy Sciences, Faculty of Engineering, Lund University

Presented by Bengt Johansson at the SAE 2006 World Congress & Exhibition, Detroit, MI, USA, April 2006

#### Operation strategy of a Dual Fuel HCCI Engine with VGT

Japanese Society of Automotive Engineering (JSAE) Technical Paper 20077035, SAE Technical Paper 2007-01-1855

Carl Wilhelmsson, Per Tunestål, Bengt Johansson Division of Combustion Engines, Department of Energy Sciences, Faculty of Engineering, Lund University

Presented by the first author at the JSAE/SAE International Fuels & Lubricants Meeting, Kyoto, Japan, July 2007

#### **Outline**

This thesis has the form of a monograph meaning that no papers are included in the end. Never the less material from previous publications are covered by it, the covered publications are the ones listed under the title 'publications' above. The first section encountered by the reader would be the introduction, covering the motivation of this work, putting the work into its context and setting the focus of the thesis. Following the motivation are two sections which, very briefly, touch internal combustion engines as such and, a bit more in detail, how to carry out combustion engine feedback control.

The second chapter describes, in detail, the Field Programmable Gate Array (FPGA), the first section generally, the second it's history. The third section of the chapter describes architectural and design considerations, both the architecture of the actual device as well as different architectural considerations on the design level are discussed. Tools and design methods are described in the fourth section, covering topics as the basic steps carried out by a design tool, low level design, different high level design tools and their corresponding pros and cons. Second to last, to illustrate the power and applicability of the FPGA technology, a flavor of FPGA applications are offered the reader. The chapter is ended with a summary.

Implementing feedback-controllers in an FPGA environment takes special considerations devoted one chapter, Chapter three. Giving an introduction to the topic of FPGA implemented controllers, compared with microcontroller implemented ones. Continuing on to the second section presenting considerations to be made generally implementing digital control, including special considerations for the FPGA environment. Section three discusses the practical issue of internal word-length optimization, Section four handles the issues arising when implementing highly over-sampled control systems and Section five describes considerations which have to be made regarding parallelization and re-formulation of control algorithms in order to make them efficient in a FPGA implementation. A flavor of control applications implemented in FPGAs follows with the intention to give the topic legitimacy and engage the reader, lastly this chapter is ended with a chapter

#### summary.

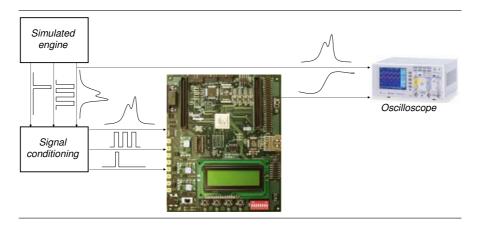

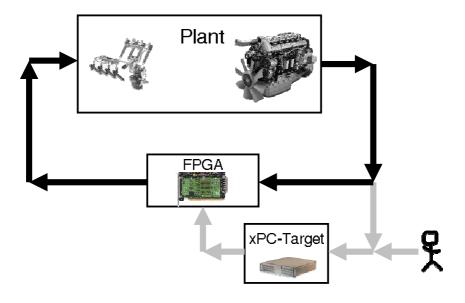

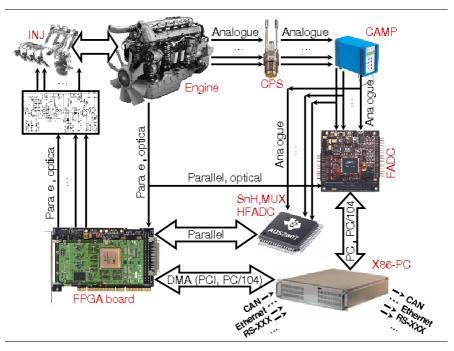

Chapter four deals with the work presented in the first and second paper covered by this thesis, namely an FPGA implementation of a heat release analysis algorithm. The chapter describes the experimental setup, the design tools used, the test environment as well as the algorithm used and its actual implementation on the FPGA. Finally, of course, the outcome meaning performance of the final system. This work was intended as a 'proof of concept'.

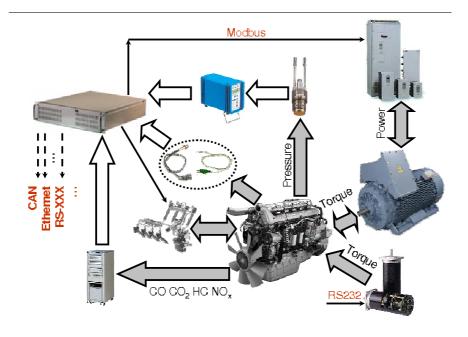

Approaching the end of this thesis, second to last, a chapter describing an intended 'rapid prototype' system, featuring FPGA hardware and with the capabilities of implementing controllers dealing with very fast feedback control loops. This system is mainly intended for combustion engine feedback control experiments, but the ideas can be reused for similar problems.

Some concluding remarks ends the thesis.

## Contents

| 1. | Intro      | duction                                                  | 1  |

|----|------------|----------------------------------------------------------|----|

|    | 1.1        | Motivation                                               | 1  |

|    | 1.2        | The Application, the Internal Combustion Engine          | 2  |

|    | 1.3        | Combustion Engine Feedback Control                       | 3  |

| 2. | The l      | Field Programmable Gate Array (FPGA)                     | 9  |

|    | 2.1        | FPGA Fundamental Description and its Processor Com-      |    |

|    |            | parison                                                  | 9  |

|    | 2.2        | FPGA history                                             | 10 |

|    | 2.3        | FPGA Architecture and Design Considerations              | 11 |

|    | 2.4        | FPGA Design Tools and Methods                            | 16 |

|    | 2.5        | A Flavor of Application                                  | 24 |

|    | 2.6        | Chapter Summary                                          | 24 |

| 3. | FPG        | As in Feedback Control Applications                      | 27 |

|    | 3.1        | Introduction                                             | 27 |

|    | 3.2        | Implementation of Digital Controllers                    | 29 |

|    | 3.3        | Word-length Optimization, Internal Number Representa-    |    |

|    |            | tion and Parameter Conditioning                          | 32 |

|    | 3.4        | Over-Sampling and Limited Precision, Digital Control us- |    |

|    |            | ing the $\delta$ -transform                              | 35 |

|    | 3.5        | Parallelization and Algorithm Reformulation              | 39 |

|    | 3.6        | A Flavor of Application                                  | 42 |

|    | 3.7        | Chapter Summary                                          | 46 |

| 4. | An F       | PGA Implemented Heat Release Model                       | 51 |

|    | 4.1        | Experimental Setup                                       | 52 |

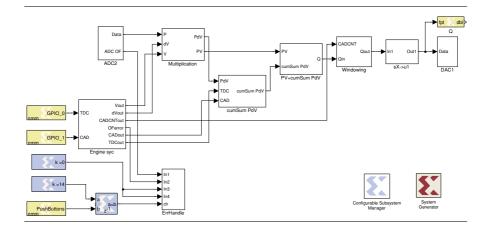

|    | 4.2        | FPGA Layout                                              | 54 |

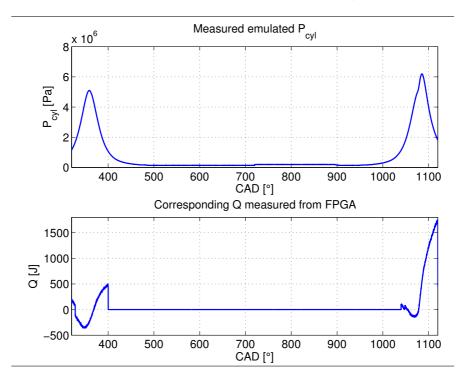

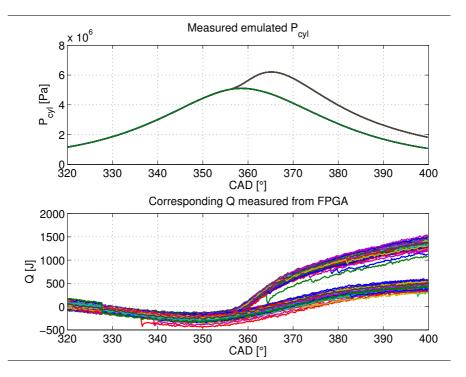

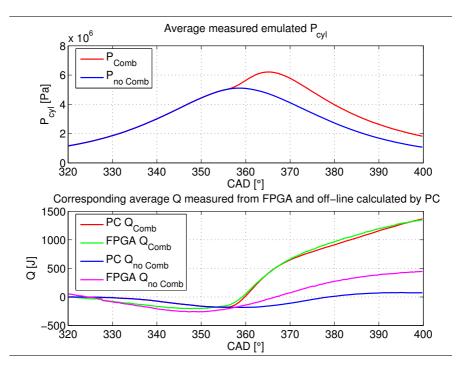

|    | 4.3        | Experimental Results                                     | 58 |

|    | 4.4        | Discussion                                               | 60 |

|    | 4.5        | Chapter Summary                                          | 62 |

| 5. | <b>FPG</b> | A Based Rapid Prototype System – a Suggestion            | 63 |

#### Contents

|    | 5.1                         | Automotive Control Rapid Prototyping | 64       |

|----|-----------------------------|--------------------------------------|----------|

|    | 5.2                         | The Setup                            | 64       |

|    | 5.3                         | Loop Overview                        | 66       |

|    | 5.4                         | Loop Bandwidth                       | 67       |

|    | 5.5                         | Suitable EDC Hardware                | 70       |

|    | 5.6                         | Software/Hardware Configuration      | 72       |

|    | 5.7                         | Chapter Summary                      | 73       |

|    |                             | 1                                    |          |

| 6. | Concl                       | uding Remarks                        | 75       |

| 6. | Conclude 6.1                | *                                    | 75<br>75 |

| 6. |                             | uding Remarks                        |          |

|    | 6.1<br>6.2                  | uding Remarks                        | 75       |

|    | 6.1<br>6.2<br><b>Biblio</b> | Summary                              | 75<br>76 |

1

### Introduction

#### 1.1 Motivation

As the reader may know internal combustion engines have been the main energy source in mobile applications for something like a century. The reader is probably also familiar with the great threat to the environment of our planet which are posed by mankind's wasteful use of energy. Internal combustion engines are a part of this energy waste and their contribution to the environmental harm is worsened by the fact that most normal types of combustion engines emit both carbon-dioxide ( $CO_2$ ) and other harmful compounds like oxides of nitrogen( $NO_x$ ), hydrocarbon (HC), and carbon-monoxide (CO). Due to environmental issues, the green house effect and increasing fuel prices, there is of course a strong urge to improve the internal combustion engine. One part which is regarded as an important factor for improving the environmental and economical performance of engines is feedback control of various engine parameters.

The author makes no claims of writing an exhaustive description of combustion engines as such. Even so they have to be briefly discussed in order to give the reader an idea of the frame within which this work has been undertaken. It is also important to introduce the reader to the topic, enabling understanding of the relevance of this work.

Instead of an exhaustive description of combustion engines the Field Programmable Gate Array (FPGA) is described. FPGA internals, design, benefits and drawbacks are described, with a feedback-control perspective in mind. The topic targeted with this thesis is how to use the FPGA as a potentially powerful tool for feedback control, both generally speaking and regarding its application in the combustion engine feedback control field.

For most feedback control solutions the capabilities of 'normal' processor systems are more than enough and the price performance ratio of processors

is good. Even so there are potential benefits in using Field Programmable Gate Arrays for feedback control and especially feedback control of internal combustion engines. The benefits could be implementation of feedback control loops in timescales not yet possible, and not expected to be possible in a very long time. Potential benefits could also be the possibility to use models more complex than possible with conventional techniques in feedback control loops. Economically speaking FPGAs have the potential to outperform conventional techniques. FPGA systems can hence potentially serve as powerful tools for feedback control of, among other the internal combustion engine.

#### 1.2 The Application, the Internal Combustion Engine

Traditionally there have been two different kinds of engines, the Otto engine (the normal gasoline engine) and the Diesel engine. Obviously there are enormous amounts of results and written publications regarding these two engine types and the best place in literature to start for the interested reader would be [Heywood, 1988]. Instead of the Otto or Diesel engine a third type of internal combustion engine principle will be discussed below. This third engine type is called Homogeneous Charge Compression Ignition (HCCI) and was first suggested by [Onishi et al., 1979]. The HCCI engine can best be understood as a hybrid between the traditional Otto and Diesel engines. Pure HCCI engines are operated with a homogeneous mixture of fuel and air, as an Otto engine. However as opposed to Otto engines, there is no throttling of the intake air, and there are no spark plugs. The fuel mixture is instead ignited by the increased temperature originating from compression of the intake charge, as in a Diesel engine. In theory this operation principle combines the high efficiency originating from Diesel engines with the low emissions originating from Otto engines. In practice HCCI combustion can be obtained in a large number of ways, each with different benefits/drawbacks compared to traditional Otto and Diesel engines.

#### The HCCI Engine

Despite intense research efforts in recent years the HCCI engine is still less known than its relatives the Otto and the Diesel engine. Nevertheless it seems to be one of the more promising engine concepts of the future, combining high efficiency with ultra-low emissions of nitrogen oxides. When the concept of HCCI was first reported by [Onishi *et al.*, 1979] is was primarily an attempt to reduce emissions of unburned hydrocarbons (HC) and improve part load efficiency of two stroke engines. After Onishi et al. published their results it took a while before further HCCI publications emerged,

when they did the publication rate increased. Important early publications are for example [Najt and Foster, 1983], [Thring, 1989] and [Stockinger *et al.*, 1992].

The operation principle of the HCCI engine makes it possible to increase the efficiency compared to the Otto engine due to the avoidance of throttling losses. At the same time the high soot and nitrogen oxide emissions of the diesel engine are avoided. Soot emission is avoided because of the homogeneity of the mixture and the absence of locally rich combustion zones. Nitrogen oxide emission is avoided because of the decreased peak in-cylinder temperature due to the diluted operation of the engine and the absence of stoichiometric undiluted zones.

HCCI combustion can be achieved in numerous ways, both in two and four stroke engines. High compression ratio can be applied [Haraldsson et al., 2002], the inlet air can be pre heated [Martinez-Frias et al., 2000]. HCCI combustion can be induced by unconventional valve strategies that retain hot residuals [Milovanovic et al., 2004] and the octane number of the fuel can be altered [Olsson et al., 2001] to modulate the ignition temperature. Since the HCCI combustion process in many operating points is unstable, feedback combustion control is needed to operate an HCCI engine in parts of its operating range. Such combustion control can be performed in numerous ways using different actuators and sensors.

Even though it has many good features, the HCCI engine also has some limitations besides the, just described, need for feedback combustion control. The operational principle unfortunately suffers from very high combustion rates, causing noise as well as wear of engine hardware. Another issue with the HCCI principle is low combustion efficiency at low load. This causes high emissions of unburned hydrocarbons and carbon monoxide.

#### 1.3 Combustion Engine Feedback Control

Internal combustion engines have, every since they were first developed been under control/feedback-control. In fact control/feedback-control of combustion engines is an 'enabler' for the success of the entire engine technique. An engine which can not deliver a controlled amount of energy at a controlled engine speed is of no use. The control tasks to be carried out by the engine controller depends greatly on the engine type and the performance requirements of the engine. This very brief section will mainly be devoted to what is considered state-of-the art control technology in the HCCI field, being a more challenging control task than state-of-the art gasoline or Diesel engine control. An early view of state-of-the art gasoline engine control was provided by [Powell, 1993]. For the Diesel engine however similar publications are sparse or completely lacking, such work has just recently been

undertaken. [Kiencke and Nielsen, 2000] provides a very interesting view for readers mainly interested in more production near combustion engine feedback control, as well as feedback control within other parts of the automotive domain (suspension, steering, breaking and driveline).

#### **HCCI Engine Control**

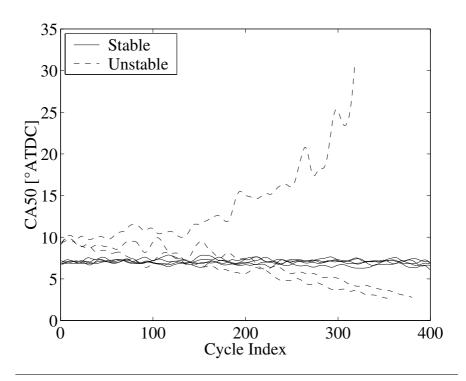

Besides development of the actual HCCI principle much work has been carried out addressing the great task of developing feedback combustion control systems for the HCCI engine. The highly non-linear nature of HCCI combustion together with the fact that actuators with high control authority are lacking poses a great challenge to researchers in the field. Furthermore, as indicated by Figure 1.1, the HCCI engine represents an unstable system which needs feedback control for successful operation. The two most important variables to control in an HCCI engine are combustion phasing and engine load. Combustion phasing is simply a number describing when during the engine cycle combustion takes place and engine load is a number describing how much work the engine develops.

Many interesting results, starting with [Olsson et al., 2001], have been published attempting HCCI control using various feedback control techniques. Some of these attempts to utilize model assisted controllers, meaning that mathematical models of the combustion process and/or other sub phenomena in the engine system are contained in the control system being continuously updated to reflect the current state the engine system. Interesting results has been published, for example by [Shaver et al., 2004] who utilizes a physically based model for HCCI control (meaning combustion phasing and output work). Results using identified instead of physically based models for HCCI control have for example been published by [Bengtsson et al., 2006] using Model Predictive Control (MPC) with an identified model for HCCI control (Bengtsson et al. also covers other interesting topics in the area of HCCI control). The point being that mathematical models contained in the control system are playing an increasingly important role in the attempts of tackling the difficult HCCI control problem. A fact which also is true in the attempts of improving control and performance of the Otto and Diesel engines.

#### **Cylinder Pressure Measurements**

Cylinder pressure is a very powerful measurement signal when conducting engine feedback control, [Tunestål, 2000] quotes Professor A. K. Oppenheim who said that the cylinder pressure is like "the heartbeat of the engine" and measuring it is like carrying out 'engine cardiology'. The author recognizes this to be an excellent explanation of the importance of the cylinder pressure signal. From the cylinder pressure both combustion phasing and

**Figure 1.1** HCCI combustion instability, combustion phasing is shown as function of cycle-number for different cases. Combustion-phasing feedback-controllers are switched off at cycle zero, note that some cases are stable (combustion phasing is maintained) while others change combustion phasing spontaneously. Figure found in [Olsson *et al.*, 2002]

engine load can be calculated, as well as other important parameters. Cylinder pressure is typically measured using a piezoelectric pressure transducer. The piezoelectric effect causes a quartz crystal to give away a small charge when exposed to an external force. Such a pressure transducer is typically connected to a charge amplifier which converts the small charge generated by the piezo-effect to a measurable voltage. A charge amplifier however can not be constructed without some leakage current, the leakage current will cause a drift in the DC level of the pressure signal. Due to this drift the output signal from the charge amplifier has to be treated in order to obtain the correct absolute level of the pressure. Several methods can be used to calculate the correct absolute pressure, [Randolph, 1990] accounts for three different ways;

- The cylinder pressure at bottom dead center of the intake stroke of the engine equals the pressure of the intake manifold.

- The average cylinder pressure during the exhaust stroke is equal to the back pressure in the exhaust system.

- The compression is poly-tropic and the poly tropic exponent is known and fixed.

Tunestål offers a far more detailed explanation of how to treat the signal from a cylinder pressure transducer, both in general and specifically using the third method above. In [Tunestål, 2007] the same author shows a heuristic approach which, using non linear least-squares estimation, finds both the poly tropic exponent and the DC level of the pressure signal simultaneously.

#### **Heat Release Analysis**

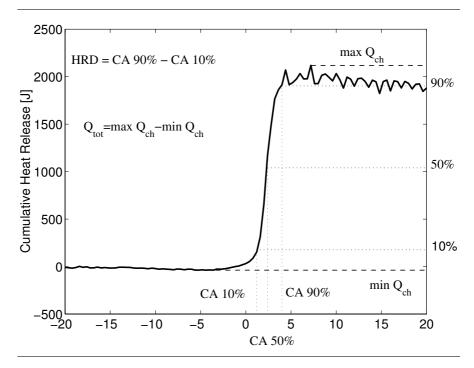

If the pressure within a cylinder is known it is possible to calculate the released heat within that cylinder after each engine cycle using thermodynamic equations as shown by [Gatowski et al., 1984], performing a Heat Release (HR) analysis. The HR model of Gatowski et al. accounts for losses as well, losses included are losses through heat transfer to the combustion chamber walls and losses originating from mass loss caused by leakage past the piston rings. Heat transfer losses are calculated based on the results presented by [Woschni, 1967] while the model for crevice losses is developed by Gatowski et al. For feedback control purposes the different losses are often neglected as discussed by [Bengtsson et al., 2004], the reason being that combustion phasing (see Figure 1.2) which is the most important feedback control candidate calculated using HR analysis can be calculated with enough accuracy even neglecting these losses. Controller complexity and hence execution time can in this way be reduced. This 'simplified' calculation is visible in Equation 1.1 which is a version of Equation 9 in Gatowski et al., neglecting losses.

$$\frac{dQ}{d\theta} = \frac{\gamma}{\gamma - 1} p \frac{dV}{d\theta} + \frac{1}{\gamma - 1} V \frac{dp}{d\theta}$$

(1.1)

Furthermore [Tunestål, 2007] has recently expanded his work, as previously noted. The benefit from Tunestål is that the explicit heat transfer model and model for losses over the piston rings used by Gatowski et al. no longer are needed since the method of Tunestål includes these effects implicitly. The main drawback with the approach taken by Gatowski et al., which is parameter tuning, is in this way avoided. The models included in Gatowski et al. and Woschni need to be parametrically tuned to fit every specific application. Using the method of Tunestål it is possible to avoid the non-heuristic

**Figure 1.2** A typical heat-release curve (the integration of Equation 1.1) with the important combustion phasing, defined as the instance when half of the total heat has been released (half of the combustion has taken place), indicated (CA50%). Bottom axis in the figure has the unit Crank Angle Degree meaning that CA50% has the same unit. Figure found in [Tunestål, 2000].

#### Chapter 1. Introduction

## The Field Programmable Gate Array (FPGA)

## 2.1 FPGA Fundamental Description and its Processor Comparison

The 'normal' processor technology is well known to many people, if not through its internal operation it is know for being the 'heart' of a normal personal computer. The essence of 'normal' processor technology is not explained in detail here, but some generalizing statements are made in order to help the reader understand the difference between an FPGA and a processor.

A processor is a sequential device which executes a program consisting of a number of single instructions, the same unit must in this case be able to handle many different instructions. The 'power' of each instruction and the number of clock cycles it takes the processor to compute one instruction differ depending on the architecture. The 'best case' is one instruction per clock cycle but this is not the average rate of instruction completion. It should also be noted that a processor normally is programmed using a 'high level' programming language, each high level language instruction consists of several 'low level language' instructions hence of course a high level instruction would normally need many clock cycles to complete its operation on the processor. The benefits with this operational principle are that the processing device is very general and a large number of different programs, used to solve different problems can be run on the same device without modifications to the actual device.

An FPGA on the other hand does *not* execute instructions at all, an FPGA is an net of logic components which can be connected in a way so that the

device performs a specific operation of varying complexity. Inside the FPGA information is transferred to the different sub-nets by electric signals. If we compare the FPGA with the processor we find that no instructions are executed on the FPGA, instead the input is presented to the FPGA device through input signals. The input signals propagates through the FPGA using the internal connections of the device and finally the result is present on the outputs of the device. Normally, one result per clock cycle can be guaranteed on the output with an FPGA design. Another 'strength' of the FPGA technique compared to the processor is the inherited suitability for problems which are of parallel nature. To illustrate this with an example; if a specific computational problem consist of two different parts which first have to be calculated independently the two intermediate results are then summed before the final result is obtained. For simplicity it is also assumed that these two different parts are equally complex to calculate. The FPGA can in this case calculate the two different intermediate results simultaneously due to the fact that two independent signal paths will be implemented in the FPGA and the final result is obtained after a simple addition of the two results. The processor would in this case need to compute the intermediate results one at a time before it calculates the final sum, since the intermediate results are similarly complex the processor would in this case need at least twice the time of the FPGA to complete the calculation but probably more depending on which instructions are involved. This generalized simple example illustrates the benefits with the parallelism featured in the FPGAs and how it can be used.

The parallel nature of the FPGA in combination with the fact that the internals are customized completely for the application makes it a precious tool for systems where very high computational power is needed. Even if processors continue to evolve with the current rate they will fall short of performance. In many cases a, even state of the art, processor would not be enough and to make matters worse a state of the art processor is very expensive, power thirsty and is hence not an option.

#### 2.2 FPGA history

The FPGA was first invented in the mid 1980s by Ross Freeman, who also was one of the founders of the large FPGA company 'Xilinx'. Early FPGAs can be regarded as a, often larger, version of a similar device called Complex Programmable Logic Device (CPLD). The CPLD on the other hand is a larger and more modern version of the Programmable Array Logic (PAL) and the size 'ranking' from smallest to largest would be: PAL, CPLD, FPGA. Leaving the rudimentary PAL out of the picture it can be said that it is not only the size that differs between the FPGAs and the CPLDs, the architectures

Figure 2.1 An FPGA circuit.

differ as well. FPGAs have a more flexible architecture than CPLDs. FPGAs often feature a more complex interconnect between the internal units than CPLDs. Another difference might be that FPGAs often contain other components than pure logic functions e.g. distributed memory, adders, multipliers or other similar components, in many cases increasing the performance of the FPGA compared to the CPLD. FPGAs have evolved rapidly since the first ones. Modern FPGAs can host designs with an 'equivalent gate count' of many million gates. They now a days contain more and more complex peripheral devices, e.g. processor cores, Digital Signal Processing (DSP) blocks, even 'mixed-mode' FPGAs exist containing analog and partly analog parts for example Analog-to-Digital Converters (ADC) or analog filters. The FPGA have evolved to become a flexible, cost effective and high power device suitable for a wide variety of applications.

#### 2.3 FPGA Architecture and Design Considerations

[Todman et al., 2005] and [Compton and Hauck, 2002] have both published excellent surveys of FPGA design considerations, dealing with FPGA hardware, FPGA design, design tools, design flow and design architectures. There are a large number off different considerations to make when designing for FPGAs both regarding hardware selection, design tool selection as well as selecting an appropriate design architecture, an overview follows. Figures 2.2 and 2.3 were adapted from Todman et al. while Figure 2.4 was found in Compton and Hauck.

#### **Hardware Level Architecture**

The internals of an FPGA typically consist of a large number of different (more or less) configurable 'functional units' linked together by a net of configurable interconnect, together sometimes called a 'reconfigurable fabric'. The functional units is 'were it happens' meaning that the actual logics is implemented in the functional units, the reconfigurable interconnect is used to transport intermediate results between the different reconfigurable units. Different FPGAs have different architectures for their reconfigurable fabric, one can speak of either fine grained or coarse grained architectures, both in the case of the reconfigurable interconnect and in the case of the functional units. Selecting between fine grained and coarse grained interconnect/functional units essentially is a trade-off between flexibility (which gains from a fine grained architecture) and speed/overhead (gaining from a more coarse grained architecture). A fine grained fabric can better be adapted to different tasks as the configuration possibilities are more detailed. A more coarse grained fabric on the other hand is not as adaptable but will be much faster for the problems where they are well suited.

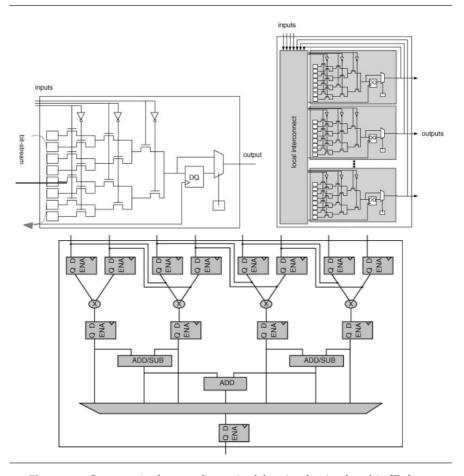

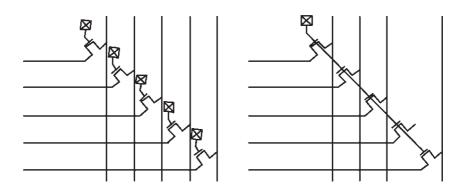

For an architecture with fine grained functional units a functional unit typically is a multiple input lookup table which can be configured to implement any logic function. These functional units are put together in clusters which in turn are interconnected via parallel connections between the closest neighbours of each cluster, and via the reconfigurable interconnect for signaling to clusters positioned in other parts of the FPGA circuit. For the coarse grained architecture the lookup table would be replaced by for example a multiplier block, and Arithmetic Logic Unit (ALU) or a memory blocks. These coarse grained blocks would perform considerably better on their specific task than the fine grained lookup tables would, but the coarse grained blocks might not be of any use for some applications. Modern FPGAs normally contain both fine grained and coarse grained blocks in the same circuit, the fine grained reconfigurable fabric is often complemented by for example an ALU or other more coarse grained components with the intention to increase the speed for some common operations. Figure 2.2 shows the structure of fine grained versus coarse grained functional units.

The reconfigurable interconnect connecting the different units within an FPGA can, as the functional units, either be fine or coarse grained. In a fine grained interconnect structure it is possible to control the routing 'wire by wire' but with a coarse grained structure it would only be possible to route a 'bundle' of wires per control bit see Figure 2.3 for visualisation. As before a coarse grained structure is less flexible but demands less overhead than the more flexible fine grained interconnect structure.

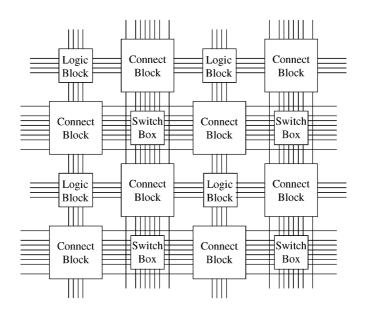

The interconnect together with the functional units forms the reconfig-

**Figure 2.2** Coarse-grained versus fine-grained functional units, found in [Todman *et al.*, 2005]. A fine grained three-input look-up table is shown above left, a cluster with fine grained look-up tables above right. A Altera DSP block is, being a coarse-grained unit, shown below.

urable fabric as shown in Figure 2.4. A reconfigurable fabric can be either homogeneous, meaning that the complete fabric consists of the same kind of functional units, or heterogeneous. A heterogeneous fabric typically contains different kinds of functional units instead of one type, a heterogeneous architecture can contain ALUs, multipliers, processor cores and of course distributed memory, all this to complement the basic functional units and to increase performance.

#### □ configuration bit

**Figure 2.3** Coarse-grained versus fine-grained routing structures, also found in [Todman *et al.*, 2005]. In coarse-grained structures, shown right, a number of signal-lines are controlled as a unit. In a fine-grained structure on the other hand a smaller number or even a single signal is configured individually as shown left.

**Figure 2.4** A typical generic reconfigurable fabric with switching units and functional-units or logic blocks. Figure found in [Compton and Hauck, 2002].

#### **Design Level Architectures**

Besides the architecture of the actual FPGA which is not so much a concern of the FPGA application designer, the architecture of the actual design is of great interest. It is of course possible to design a complete full hardware system residing only using the reconfigurable fabric of the FPGA (no type of processor core is present in the system). In many systems however some sort of processor core might well be present. Several different motivations exist for mixing processor(s) and FPGA(s) in a single system. The FPGA is not well suited for all types of tasks, iterative tasks with variable length, e.g. loops or control of dataflow, are difficult to implement efficiently in an FPGA. Such tasks are preferably implemented on a processor while computationally expensive, time critical and/or parallel tasks benefit greatly from an FPGA implementation.

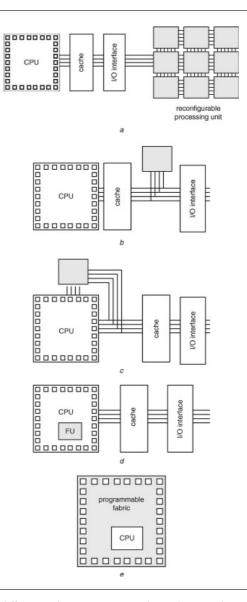

There are five different ways of integrating a processor core with the reconfigurable fabric of an FPGA, Figure 2.5 shows the five methods, four of them identified by [Compton and Hauck, 2002] and the last one (number five in the figure) added by [Todman et al., 2005]. Architecture one features communications between the processor and the reconfigurable fabric through the standard Input/Output (I/O) units of the processor. Architecture two and three show intermediate structures, meaning that the processor can access the reconfigurable fabric without having to use the standard I/O units. Architecture two is, communication-wise, a bit slower than Architecture three as architecture three features direct communication between the processor core and the reconfigurable fabric using a 'coprocessor' structure. The fourth architecture features a reconfigurable fabric which is present on the same chip as the processor, such an architecture does enable very high communication speed between the processor core and the reconfigurable fabric. Architecture number five resembles number four, but instead of adding 'a piece' of reconfigurable logic to a processor, a processor is added (implemented) on-to the reconfigurable fabric of an FPGA.

Using the last two architectures the processor can be either a 'hard core' meaning that a fixed part of the device contains a processor which is constructed on the same chip as the reconfigurable fabric, or a 'soft core'. Soft core processor meaning that the processor structure is made on the reconfigurable fabric, the complete chip hence consists of reconfigurable fabric, but on a piece of that reconfigurable fabric a processor is constructed using the reconfigurable fabric for its implementation. One of the benefits with the latest two design structures is that it is possible to customize the actual processor internals, it is possible to add custom instructions to the processor instruction set which is able to make custom calculations with only one call. This feature can in some applications give significant speedup as easily understood if the reader imagine a certain computational problem where a

number of arithmetic operations are required on the operands, and where the same calculation is carried out over and over again by the processor. If a normal processor is used the number of instructions needed is (in best case) equal to the number of arithmetic operations to be carried out, a customized processor on the other hand may be able to carry out all of the operations with a singe call and the speedup will hence be equal to the number of operations in this simplified example. This principle is called 'soft instruction processors' or 'flexible instruction processor'

The nature of the applications does of course decide which of the five different architectures above that is to prefer, Compton and Hauck provides a very good description of the benefits and drawbacks with the different structures. Using Architecture one for example the communication between the processor and the reconfigurable fabric is slow, hence this architecture is suitable for systems where large 'chunks' of work can be treated by the reconfigurable fabric independently. The reconfigurable unit of Architecture two has the same properties as a normal processor would have had in a multi processor system. Architecture three, the coprocessor architecture, is typically also capable of performing calculations independently from the processor core but it has access to the same memory and other facilities as the processor core has. Architectures four and five would be best suited when communication between the processor and the fabric needs to be vigorous, for example when the reconfigurable fabric is used to customize the processor in some way and communication hence needs to be very efficient. A drawback with the soft instruction processor approach is however that it is more difficult to utilize the possibility and parallelism with such a tight coupling to the processor. According to Todman systems according to Architecture one are the most common in commercial FPGA platforms.

It should also be noted that it is not every FPGA system which features a processor core even though it would be possible to include one. It is for example possible to design larger applications where the complete functionality is implemented entirely on the reconfigurable fabric. Such designs can be used to verify the functionality of actual Application-Specific Integrated Circuits (ASICs) or in cases when ASIC like performance is needed but it is too expensive to make a real ASIC.

#### 2.4 FPGA Design Tools and Methods

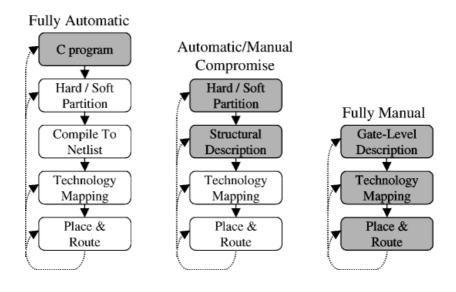

[Compton and Hauck, 2002] has written an excellent section about configuration of FPGA devices, Compton and Hauck explains the three design flows visible in Figure 2.6. Added to this [Todman *et al.*, 2005] covers more in detail a number of tools implementing the fully automated approach and describes some tools based on data flow graphs (e.g. Simulink). Selecting

**Figure 2.5** Five different architectures commonly used in mixed processor/hardware systems. The different architectures have different properties regarding for example communication-speed and flexibility and are hence suitable in different situations. Figure found in [Todman *et al.*, 2005].

a manageable and efficient FPGA design software is an important point which can ease the effort of implementation significantly. Which tool that is best suited depends largely on the type of implementation to be carried out, the skill of the hardware designer and the performance requirements of the final outcome. A fully manual approach (right in Figure 2.6) will, according to Compton and Hauck, give circuit-designs of very high quality, it however puts high demands on the developer regarding background knowledge about circuit design in general and also knowledge of the specific device in use. A fully automated approach on the other hand simplifies implementation greatly, the outcome however is often less efficient in terms of power consumption, speed and occupied chip area. It might however be worth its price to use a fully automated approach since it makes the FPGA technology available to a larger number of developers and since even a less optimal design still often has large gains compared to, for example a processor implementation. All these three design methods can be divided into separate steps as shown in Figure 2.6. These different steps will be described in the following sections. Before continuing it is crucial that the reader understands that even though traditional programming languages such as C, C++ or Java are used for high level hardware design, no program is run on the FPGA. Code written in these languages is synthesized into a connection scheme used for the reconfigurable fabric within for example an FPGA.

#### **Basic Implementation Steps**

Technology Mapping During technology mapping what basically is done is that the large design is broken down to small sub functions. Each sub function in turn is translated to actual logic on the FPGA device, meaning that each sub function is translated into the 'basic units' of the specific FPGA in use (e.g. look-up tables). The large design which is input for the technology mapping is described either at gate-level or at element-level, originating either directly from the designer if it is a fully manual design or from the design tool if it is some sort of automated design. This step is of course heavily device dependent since different devices contains different logic and are built according to different architectures.

Place & Route Subsequent to the technology mapping in the tool-chain is the place & route step. The place & route tool basically places the logic (assigns a location on the actual chip) corresponding to the different sub functions obtained from the technology mapping. A place & route tool needs to make difficult trade-offs carrying out the placement of the different sub functions, to do this successfully a technique called floor-planning is often applied before the actual detailed placement. The idea behind floor-planning is to analyse the sub functions and find which sub functions need

**Figure 2.6** Three different FPGA design-flows, implementing an algorithm using different levels of automation. Different tools and implementation approaches demand different amounts of manual intervention by the designer/user, grey denotes manual efforts of some sort in the corresponding step. Figure found in [Compton and Hauck, 2002].

to communicate frequently with each other. Such sub functions are grouped together in clusters enabling a higher intercommunication rate within these clusters. When floor-planning is finished (deciding the global placement) a more detailed placement is carried out by the placement tool. In the last step the different components positioned in different parts of the FPGA are interconnected by the routing tool. As is the case with placement and floor-planning, routing is a very difficult trade-off. Maximum FPGA clock-speed is decided by the longest signal path within the design (since all signals need to arrive within one clock cycle). It is not only important to the keep the longest route within the FPGA as short as possible. Routing resources (signal lines within the FPGA) are limited and care must be taken to optimize the usage of this resource. On top of it all, to be able to route a design in a good manner, it is essential that the placement tool has made a reasonably good placement.

#### **Low Level Design**

The 'lowest' level of circuit design would be the fully manual approach, meaning that the designer has to decide which of the FPGA internal components to use and how to connect them with each other, producing a design at element-level. Another option is that the designer makes a net-list containing components at gate-level which describes the circuit functionality. As earlier mentioned the fully manual method gives high performance designs, it should however only be used for smaller designs and only by designers with high skill and good knowledge about the actual FPGA device in use.

Next 'level' of low level design would be the usage of a structural design language such as VHSIC Hardware Design Language (VHDL), (VHSIC = Very-High-Speed Integrated Circuit) or the Verilog hardware descriptional language. VHDL is exhaustively described in [IEEE, VASG: VHDL Analysis and Standardization Group, 2007] and Verilog is described in the same manner in [IEEE, P1800, System Verilog Work Group, 2001]. These languages are used to describe a hardware design from building-blocks such as gates, flip-flops or other similar components. When the VHDL or Verilog code is compiled by e.g. an VHDL compiler the structural description in VHDL is translated to a gate or element-level design, technology mapping and placed & route is then carried out based on the compiled VHDL code. VHDL or Verilog can be programmed in a normal text editor much the same way as any other programming language. In most cases a more complete design tool would however probably be used. For most FPGA devices vendor specific design toolboxes exist, normally allowing the designer to design circuits either purely from VHDL (or Verilog) or using a 'mix' of VHDL code and some sort of graphical interface allowing the designer to draw the design using 'wires' and different building blocks, either defined by personal VHDL code or defined in advance by libraries, such blocks could be gates or flip-flops.

Both the fully manual design method and design using a structural design language puts demands of significant knowledge on the designer, regarding hardware design and regarding the actual FPGA device. A programming environment consisting of an editor and compiler for structural design languages in combination with some graphical interface, probably bundled into a large toolbox together with the technology mapping and place & route tools and normally supplied by the FPGA vendor, would as understood by the author by far be the most common FPGA design option.

#### **High Level Design Tools**

High level design tools are here used as a term for the two leftmost design flows in Figure 2.6, the fully automatic approach and the semi automatic approach. A fully automated approach is, compared to the fully manual design method, much more convenient to use and even not so experienced engineers can complete an FPGA design using one of the tools implementing a fully automatic approach. The drawback is as noted previously that the designs may be less efficient than a design which is made completely manually. Semi automated approaches are, simply put, any mix between fully automated and fully manual designs, an example could be where smaller interface or control parts are made manually while a larger or more complex algorithmic part is designed using an automated tool.

high level design tools typically generate an FPGA Hardware Compilers design based on a high level programming language. [Todman et al., 2005] shows examples using C, C++ or Java as 'host' languages. These tools work, as identified by Todman et al., according to three different principles. They are either annotation and constraint-driven, annotation-free or work according to the source directed compilation principle. The main idea with the annotation and constraint-driven approach is to use annotations and constrains in combination with the source code in the original language to generate the design. The annotation and constraint driven approach has the benefit that the source code originally intended for a normal microprocessor would only need minor modifications to be used as description code for hardware. Compilers which are annotation-free also exist. General C, C++ or Java code can be used, meaning that no code review is needed regardless of if the code is intended for the hardware or for a micro processor. Annotationfree compilers have the great benefit that code can be 'moved' from an processor core to a FPGA without modifying it at all, a property which is ideal when designing mixed processor hardware systems. The source directed approach on the other hand adapts the 'host' language to better suit the FPGA environment for example by extending the language with suitable operators and types.

Hardware/Software Partitioning systems where both reconfigurable hardware and a microprocessor are present and both components are to be used together the intended application must in some way be partitioned between hardware and software. For this purpose there are different possibilities, the system can either be manually partitioned. Each part is then developed using corresponding tools, if a hardware compiler is used for the hardware part either of the three types of hardware compilers could be used. Selecting an annotation and constraint driven or an annotation-free compiler would however give the largest flexibility to move code between the hardware and microprocessor. A manual approach will in any case not be very flexible regarding moving source code between the different parts. To solve this, compilers which co-target mixed micro processor/hardware systems have

been developed and examples are given both in Todman et al. and [Compton and Hauck, 2002]. These compilers often use the possibility of co-design and automatic partitioning, making partitioning and hardware design more 'transparent' for the developer (who probably is more familiar with the micro processor environment). Using for example annotation-free compilers the developer can either choose to let the compiler decide the partitioning, or the developer can decide how to partition the code between the micro-processor and the hardware.

It should also be said that hardware/software partitioning is tightly coupled both to parallelization and to the hardware compiler in use. Hardware compilers in some cases co-optimize or co-decide both the parallelization and the hardware software partitioning. Many parallelization tools by nature also implicitly decide the hardware/software partitioning during the process of deciding which parts of the code is suitable to pipeline and make parallel for putting in hardware, in order to off-load the microprocessor.

To fully utilize the potential performance gains from us-Parallelization ing reconfigurable hardware, parallel and pipelined structures should be used as much as possible in the design. It is important to note that parallelization in this context is an issue connected with hardware/software partitioning and hardware compilers, not a completely independent step. Parallelization of 'high-level' code is of course not an issue for the manual design method since it is included explicitly in the design since structure and timing of the circuit is totally up to the hardware designer (who of course should try to use parallel and pipelined structures as much as possible even in the manual design). Using some sort of hardware compiler it is however more difficult to extract parallel and pipelined parts from the (by nature) sequential source code in C, C++ or Java. And again there is basically the two possibilities of handling this manually or automatic. Several approaches exists for automatic extraction of parallel and pipelined structures and again Todman et al. and Compton and Hauck describes the most common ones. Automatic parallelization and pipelineing of inner loops, parallelization of common instruction paths (rarer paths are run on a processor) or parallelization of all loops through control flow diagrams of the complete source code are a few worth mentioning. As for fully manual parallelization the programmer typically would have to define parallel areas within some part of the source code, either by annotations or by using parallel threads similar to 'normal' parallel programming.

**Data Flow Graph Tools** Another type of high level design tools are those based on Data Flow Graphs. Data Flow Graphs (DFG) are typically used within the automatic control (technical computing) and DSP communities. There exist a number of DFG based FPGA tools which are specialized to

suit development of DSP like systems, they are of course suitable for other design purpose tools as well. One tool which has to be mentioned here is Simulink (Simulink is an extensive plug-in tool for Matlab), Simulink is based on the idea of DFGs and is hence very well suited for development of DSP and automatic control systems. Since Simulink is a tool which already is very well established within the technical computing and DSP community and extensively used for other purposes than FPGA development many of the large FPGA manufactures have made plug-in versions of their toolchain adapted for use in Simulink, enabling hardware design within the well known and easy to use Simulink environment. Besides Simulink there are other tools which are based on the DFG principle which are specialized in or adapted to DSP design for FPGAs.

Using FPGAs for DSPs or other similar technical computing applications has a lot of nice features regarding for example speed, jitter and accuracy. One distinct feature with DSP like implementations in FPGAs is the nonfixed word-length of the internal number representation, something that can be a strength if handled correctly and a barrier of implementation if not. A DSP is normally a processor based device and has hence fixed internal word-length as processors do. When implementing DSP-like applications in an FPGA however this limitation of the internal number representation no longer exist It is possible for the designer to decide how many bits to use for internal number representation in each step of the algorithm. There is an optimal internal number representation for each step of a given algorithm, this optimal representation will give the system best accuracy and noise reduction, even more accuracy than possible with a fixed word-length DSP. Those word-lengths can be found through-out the design, it is however difficult to find them, this is in fact an NP-hard optimisation problem. [Cantin et al., 2002] has written a survey of ways to automate the search for the optimal internal number representation and Todman et al. also discuss this subject, not all DFG based FPGA development tools support automated approaches on the word-length optimization problem. For example the Simulink based tool for Xilinx devices does not, as stated by Todman et al. and as experienced by the author and described in Chapter 4. Algorithmic settings must in the Xilinx case be selected by the designer in every calculation step, making work in this environment much more difficult for the designer. It is strongly recommended that a tool with automated word-length optimization is used since it makes implementation significantly easier and more efficient, especially if the designer is less experienced with working in the FPGA domain.

## 2.5 A Flavor of Application

Since FPGAs have been around for quite some time there exists a variety of scientific results on FPGA applications and design. This brief section is intended as a flavor (not a complete description) of applications and areas where reconfigurable computing technology has been applied successfully, in order to highlight the potential power of reconfigurable hardware. Enhancing feedback control system performance is, being the topic of this thesis, devoted a complete chapter (Chapter 3) and is hence not accounted for in this section.

A large application area for these systems is applications treating images or image streams (video). A good reason for using reconfigurable hardware in this kind of applications is that they are extremely computationally expensive. Heavy computations combined with the fact that many tasks have to be performed on-line puts very high demands on computational power of such systems. Examples of results in this area are [Djemal *et al.*, 2005], [Jörg *et al.*, 2004] and [Tao *et al.*, 2005] who all have implemented different FPGA or mixed FPGA processor systems in the domain.

Another very interesting application area is FPGA based super computers, meaning computers consisting of one or many FPGAs connected together in a matrix. The design within the FPGAs is totally customized to one specific calculation or simulation task and the FPGAs are able to, in a very rapid manner, solve the special problem which they are designed for. The 'secret' is of course heavy parallelization and pipelineing achieving outstanding performance and even price/performance. Very interesting results are published by among others [Jones *et al.*, 2006] and [Belletti *et al.*, 2006]. Such computers clusters are emerging as a serious competition to traditional processor based super computing clusters. The possibility also exists to make systems with one or more FPGAs to accelerate frequent or intensive tasks in a normal PC.

Different types of DSP applications are also common. Implementing DSPs and DSP-like systems in FPGAs are a very promising idea which is covered in an survey by [Tessier and W., 2000].

# 2.6 Chapter Summary

This chapter has covered the FPGA and reconfigurable hardware technology. Strengths, issues, design considerations and design tools have been discussed. The chapter started with a brief history about the FPGA which was invented by Ross Freeman in the mid 1980s and originating from similar devices such as the CPLD and PAL. An FPGA is a reconfigurable hardware device and works in the same manner as any digital/electric circuit. Com-

paring it to a processor it is found that a processor is a more general device since it can carry out a set of general instructions, an FPGA can only cope with the task it is specially designed for, it does on the other hand outperform the processor technology on that specific task.

There are two different 'levels' which are significant during FPGA design. One is the hardware-level meaning the architecture of the actual hardware of the device. Two significantly different architectures are distinguishable, a fine-grained architecture and a coarse-grained architecture. A finegrained architecture typically consist of a large number of look-up tables which can be configured to carry out an arbitrary task, the routing within a fine grained architecture can typically be controlled with a large precision. A coarse-grained architecture on the other hand typically consist of more high level blocks which are hence not as general as the fine-grained look-up tables, the control of the routing is also less precise. The benefit with a coarse grained architecture is that it will perform better in speed, power consumption and chip area when it fits the intended application. Architecture on the design level have been covered as well and systems consisting of both a processor core and reconfigurable fabric has been shown. It has been described in which situations different interconnections between the processor core and reconfigurable fabric are suitable.

FPGA design tools and methods have been thoroughly described. Low level design tool steps consisting of the technology mapping and the place & route step and low level design is carried out with the help of structural design languages. It was found that a design at this low level gave the fastest and most efficient circuits but is extremely demanding and only suitable for highly skilled designers and smaller designs with very high performance requirements. High level design tools were described as well, high level tools often consist of hardware compilers which generate FPGA designs from programs in the well known C, C++ or Java languages. These languages are suitable to use for normally skilled designers and in systems which are mixed FPGA/processor systems since code easily can be migrated between the different subsystems, or the different subsystems can be co-targeted. Hardware compilers should be used for larger designs when speed, area and power consumption requirements are less strict. Using hardware compilers and mixed systems, trade-offs regarding hardware software/partitioning and parallelization arises (parallelization is an important factor for low level designs as well). Systems can either be manually partitioned between the hardware and the software or partitioned by the hardware compiler, if the compiler is able to co target both the processor and the hardware. Parallelization can also be carried out either manually or automatically, different approaches exist for automatic partitioning, for example hardware acceleration (parallelization and pipelineing) of inner loops within the program. Data Flow Graph based tools (e.g. Simulink) and FPGA design using these

## Chapter 2. The Field Programmable Gate Array (FPGA)

tools were presented. The special issue of internal word-length optimization associated with algorithms within FPGAs was also mentioned, having the potential benefit of a solution with better performance than a fixed word-length algorithm. The optimal solution to the word-length problem can be found automatically but it is computationally intensive. The author strongly recommended an automatic approach since the word-length optimization problem is difficult to solve manually. Last but not least some success stories were presented.

# FPGAs in Feedback Control Applications

### 3.1 Introduction

Very promising results are shown applying FPGAs in the field of automatic control, as a platform for implementing automatic-control systems. Results are emerging dealing specifically with implementation of different controllers using FPGAs as well as general ideas regarding implementation of control systems using FPGAs, [Monmasson and Cirstea, 2007] deals with design of industrial control systems using FPGA techniques and also very briefly compares it with control implementation using micro-controllers. Furthermore extensive work has been carried out by many different authors addressing the task of implementing well-known control algorithms in the new FPGA environment, evaluating methods, gains and drawbacks in doing so. An FPGA has properties which in many ways makes it the ideal component for control system implementation, some of them are mentioned in Monmasson and Cirstea. Three main reasons can be identified as particular strengths of FPGAs for feedback-control implementation;

- Increased controller performance, speed and robustness

- Reduced controller price due to improved price-performance ratio

- Reduced system power consumption and space requirement (crucial in embedded system applications)

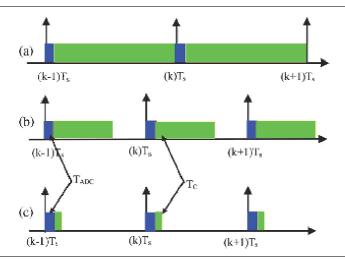

The main benefit using FPGAs is the enormous increase in speed compared to conventional techniques, Figure 3.1, from Monmasson and Cirstea, illustrates a typical situation using FPGA for control compared to either DSP

or normal micro-controllers. The figure illustrates a situation where a microcontroller is fully utilized, meaning that there is no 'spare' computation time available, with the periodic task of executing and updating a feedback control algorithm. The drawbacks with the 'full utilization' are reduced margins for instability caused either by insufficient controller bandwidth, influence of jitter or both. Added to this there is no possibility to increase the complexity of the control algorithm. Such a scenario is likely even using a stateof-the-art micro-controller due to the generic structure of micro-controllers (processors), performing good in average but bad on the specific problem. The case for a DSP performing the same task would be slightly better, of course, since the DSP architecture is better suited, adapted, to this kind of task. While using an FPGA the computation time of the feedback control algorithm typically would be less than or equal to the time needed to perform the actual sampling. The time 'margin' gained from using FPGA-technology could be used in different ways, increasing controller bandwidth, gaining stability margin could be one. It would be possible to 'over sample' the system, in some cases increasing controller performance. Many control problems suffer from lacking ability of the implementation platform. Controllers and control-oriented models have to be simplified, suffering in performance. FPGAs, to a large extent, increase the abilities of the implementation platform, at least from a calculation speed point of view. More complex and computationally intense control strategies can be used, with better accuracy. The spare time can also be utilized for other calculations, for example other control loops residing in the same system. FPGAs would, compared to micro-controllers and DSPs and depending on the properties of the algorithm to implement, offer performance only possible to match using fully analog control systems. At the same time the problems associated with analog control systems such as component ageing, related parameter drift and the subsequent risk of controller instability are avoided due to the digital nature of an FPGA. An interesting note to make is that, as an alternative to 'traditional' analog control systems, a control system could be implemented using a device called Field Programmable Analogue Array (FPAA). FPAAs are related to FPGAs and are best described as the analogue counterpart of FPGAs. These devices are not covered by this dissertation but for example [Hall et al., 2005] gives an insight in the world of FPAAs.

When it comes to system price there are a few sub-reasons which promotes an FPGA implemented approach over an micro-controller one. The price over performance ratio of an FPGA is superior to that of an micro-controller. This is easily understood from the fact that there, in a micro-controller, are a lot of 'go along' hardware not needed to solve the task but included in the device, thus increasing the price of it. Using an FPGA it is possible to only include the logic actually needed, hence a smaller device can be used. Adding to the price difference is the general and sequential

nature of a micro-controller which can not compete in performance compared to the parallel and customizable nature of an FPGA, drastically increasing performance as earlier thoroughly discussed. Hence a less powerful and cheaper device is needed. Related to the flexible internal nature of an FPGA it is, in larger systems, possible to include the exact mix of hardware needed on a single FPGA, even such components which typically would reside externally. Such an approach is called a System-on-a-Chip (SoC) solution and removes the need for much differing hardware greatly simplifying hardware-integration efforts, decreasing component cost and decreasing implementation time, 'time-to-market', all improving the economical performance. Monmasson and Cirstea also argues another reason giving shorter 'time-to-market' using FPGA devices compared to micro-controller and DSP devices; Significant effort is needed to hand-tune and optimize algorithms residing in DSPs in order to obtain the calculation speeds needed. Normal micro-controllers on the other hand need a lot of real-time considerations and probably a real-time operating system in order to implement feedback controllers. Although these remarks are true, they are weak as pro-FPGA arguments. Implementation, especially of control-algorithms, in an FPGA environment is far from straight-forward. Difficult considerations regarding, among other things, parallelization and number-format issues have to be made, probably increasing implementation effort to the same range as micro-controller implementations. Some of these considerations are noted previously and some are highlighted in this chapter. Concluding the discussion; economical performance of FPGAs exceed microcontrollers for matching performance, 'time-to-market' may gain somewhat from using FPGAs but is not the main strength of FPGAs.

Last but not least it should be said that FPGA technology potentially saves both space and power. The reduced power-consumption and space requirement are both in some sense related with the SoC approach, making it possible to include much of the external components on the FPGA. And again, the customized nature of the device, decreasing the device performance requirement adds to the benefit in power consumption.

## 3.2 Implementation of Digital Controllers

Implementing control and signal-processing algorithms either using micro-controllers or using FPGAs takes a lot of practical considerations, different considerations for different implementation platforms. In the well known micro-controller-case algorithmical considerations would for example have to be made depending on the performance of the device, depending on if the device holds floating-point support or if a real-time operating system is present on the device. The literature with in the topic of implementation

**Figure 3.1** Probable time consumption of a control algorithm running on a microcontroller, top, a DSP, middle, and an FPGA, bottom. Blue denotes time needed to perform one sample and green denotes time needed to perform computations. It is noticeable how the microcontroller typically needs all the time available between two samples to compute the controller (this would of course depend on design considerations). The DSP would probably use less time to compute the controller compared to the micro-controller, leaving more margin for stability. The FPGA on the other hand would in most cases not need more time to compute the controller than it takes to sample the system. Gained time can for example be used to increase system stability in some way. The figure was originally found in [Monmasson and Cirstea, 2007].

of control/feedback-control algorithms using conventional computers (e.g. micro-processors and DSPs) is quite extensive, [Åström and Wittenmark, 1997] is an excellent reference piece on the topic. Besides the task of performing the discretization of the controller algorithms in a manner which assures maintained properties of the algorithm many other implementation specific considerations has to be made. There are, in order to successfully implement a digital controller, essentially a union of four different parameters which needs to be balanced/full-filled.

- System frequency and controller frequency (bandwidth)

- Control-system sampling-speed

- Accuracy of controller parameters (word-length and number representation)

- Parameter conditioning

Starting from the top it is important that the bandwidth of the controller is high enough to guarantee stability in the closed-loop system. The sampling speed must be selected so that the desired controller bandwidth can be maintained (in the range of 10-30 times the bandwidth of the closed-loop system). The limit of controller sampling speed is in many cases the calculation capacity of the device used for implementation. If the samplingspeed is much higher than the bandwidth of the controller, special considerations have to be made to avoid for example noise issues. Maintaining controller stability when using limited-word-length arithmetics (which always is done in the real-world case) is another issue which needs to be handled to guarantee performance of the closed-loop system. Another thing to keep in mind implementing digital controllers is that it is important to use well-conditioned parameters, avoiding excessively large or small parameters especially in combination with 'normal' sized ones. There are mainly two reasons for avoiding ill-conditioned parameters, over/under-flow in the algorithms and noise sensitivity.

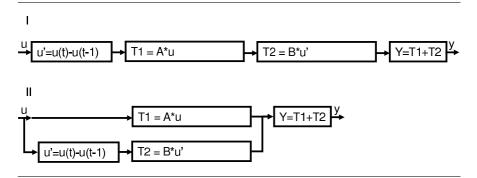

### Algorithmic Considerations for FPGA Implementation