## Microwave CMOS Beamforming Transmitters

Johan Wernehag

Lund 2008

LUND INSTITUTE OF TECHNOLOGY

Department of Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

No. 12 ISSN 1654-790X Series of licentiate and doctoral theses

© Johan Wernehag 2008. Produced using LATEX Documentation System. Printed in Sweden by *Tryckeriet i E-huset*, Lund. November 2008.

## Abstract

The increase of the consumer electronics market the last couple of decades has been one of the main drivers of IC process technology development. The majority of the ICs are used in digital applications, and for these CMOS is the choice of technology. The urge to squeeze more transistors on to a given area has led to shrinking feature sizes. It has resulted in higher transition frequencies and reduced supply voltage. During the last decade the increasing transition frequency has enabled CMOS to be used in RF applications, as well. Unfortunately, the decreasing supply voltage that, until recently, has accompanied the reduced feature sizes makes it more difficult to build power amplifiers that can deliver the amount of power needed to transmit the radio signal over the desired distance. In the receiver, the reduced supply voltage has resulted in reduced signal swing, which compromises linearity and dynamic range.

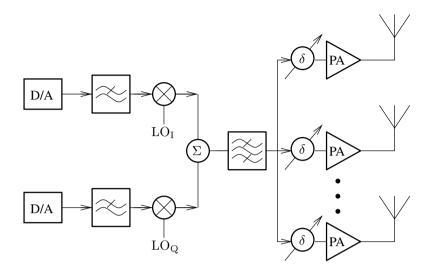

In this thesis new topologies for the power amplifier is investigated, and the approach to combine the power from multiple power amplifiers is taken. In this way, despite the low supply voltage, the transmitted power by the IC can still be high. The increased transition frequency of CMOS technology can be used to increase the operating frequency to tens of GHz. The possibility for small sized phased antenna arrays then reveals, giving high directivity of the antenna and the potential for electrical beam steering. This both reduces interference to nearby receivers through spatial selectivity, and increases the equivalent isotropic radiated power. Power amplifiers with digital 360° phase control and antenna arrays have been investigated.

In recent years applications at high operating frequencies have attained much focus from both academia and industry, such as automotive radar at 77 GHz and WLAN at 60 GHz. Even though the shrinking feature sizes of CMOS transistors have resulted in transit frequencies above 150 GHz, the high frequency required by many applications is still a great challenge for the CMOS designer. Therefore, in Paper IV and Paper VI different approaches to keep the on chip frequency lower than the RF carrier frequency as long as possible have been taken. In Paper IV two different frequency doubling 60 GHz power amplifier topologies are presented, and in Paper VI a subharmonic mixer with 30 GHz radio frequency and 15 GHz differential local oscillator is presented.

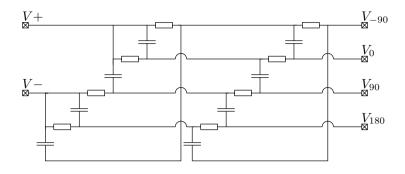

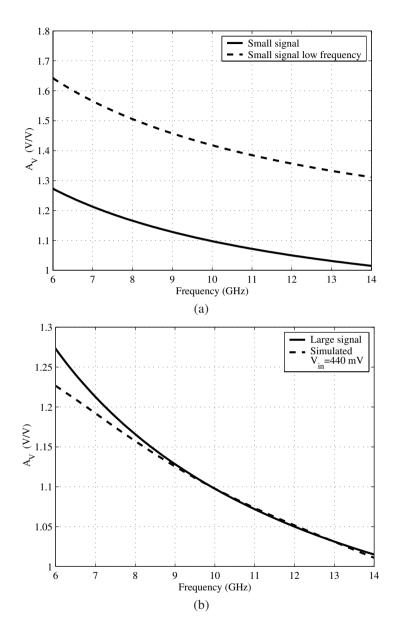

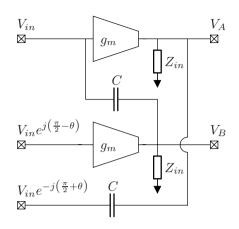

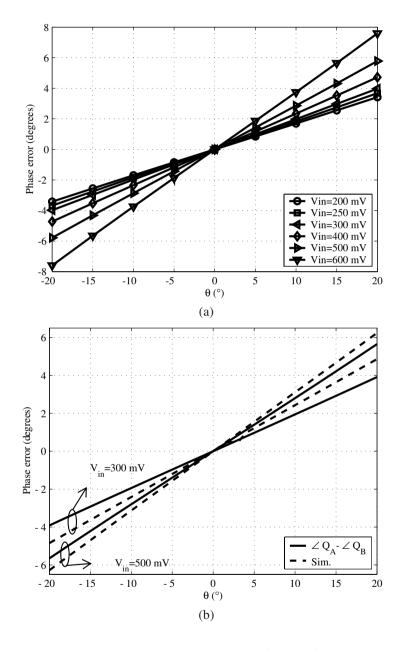

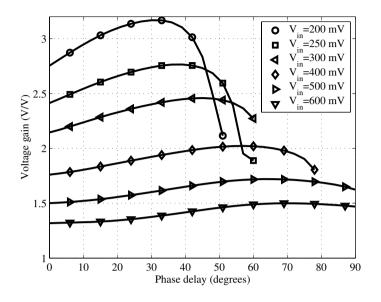

Many transceiver architectures rely on quadrature signals driving the down- or upconversion mixers. The power amplifiers in Paper I and II need quadrature signals to implement the digital phase control. Therefore, in Paper V a three-stage active polyphase filter with quadrature output signals, high operation frequency, and wide bandwidth is analyzed. Analytical equations for both voltage gain and phase transfer function of a loaded stage are derived. The filter shows robustness against process parameter spread and achieves high quadrature signal quality from 6 GHz to 14 GHz.

## Contents

| Abstract                                                                                                                   | iii             |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

| Contents                                                                                                                   | v               |  |  |  |  |  |  |  |  |

| Preface                                                                                                                    |                 |  |  |  |  |  |  |  |  |

| Acknowledgment                                                                                                             |                 |  |  |  |  |  |  |  |  |

| List of Acronyms                                                                                                           | xvii            |  |  |  |  |  |  |  |  |

| List of Symbols                                                                                                            | xxi             |  |  |  |  |  |  |  |  |

| Introduction                                                                                                               | 1               |  |  |  |  |  |  |  |  |

| 1 Motivation and Research Contributions                                                                                    | 1               |  |  |  |  |  |  |  |  |

| 1.1 Motivation                                                                                                             | 1               |  |  |  |  |  |  |  |  |

| 1.2 Research Contribution                                                                                                  | 2               |  |  |  |  |  |  |  |  |

| 2 Radio Transceiver Fundamentals                                                                                           | 5               |  |  |  |  |  |  |  |  |

| 2.1 What is a Radio Transceiver?                                                                                           | 5               |  |  |  |  |  |  |  |  |

| 2.2 Receiver                                                                                                               | 5               |  |  |  |  |  |  |  |  |

| 2.2.1 Receiver Architectures                                                                                               | 6               |  |  |  |  |  |  |  |  |

| Heterodyne Receiver                                                                                                        | 6               |  |  |  |  |  |  |  |  |

| Image Rejection Receiver                                                                                                   | 8               |  |  |  |  |  |  |  |  |

| Direct Conversion Receiver                                                                                                 | 10              |  |  |  |  |  |  |  |  |

| 2.2.2 Receiver Linearity and Noise                                                                                         | 12              |  |  |  |  |  |  |  |  |

| Noise                                                                                                                      | 13              |  |  |  |  |  |  |  |  |

| Linearity                                                                                                                  | 14              |  |  |  |  |  |  |  |  |

| 2.3 Transmitter                                                                                                            | 15              |  |  |  |  |  |  |  |  |

| 2.3.1 Transmitter Architectures                                                                                            | 16              |  |  |  |  |  |  |  |  |

| Direct Conversion Transmitter                                                                                              | 16              |  |  |  |  |  |  |  |  |

| Two-Step Transmitter                                                                                                       | 17              |  |  |  |  |  |  |  |  |

| Direct-Modulation Transmitter                                                                                              | 18              |  |  |  |  |  |  |  |  |

| 2.3.2 Transmitter Requirements                                                                                             | 18              |  |  |  |  |  |  |  |  |

|                                                                                                                            | 18              |  |  |  |  |  |  |  |  |

| Noise                                                                                                                      | 19              |  |  |  |  |  |  |  |  |

| 2.4 Power Amplifiers                                                                                                       | 19<br>20        |  |  |  |  |  |  |  |  |

| 2.4.1 Power Ampinier Classes                                                                                               | 20<br>24        |  |  |  |  |  |  |  |  |

| 2.4.2 PA Efficiency                                                                                                        | 24              |  |  |  |  |  |  |  |  |

| -                                                                                                                          |                 |  |  |  |  |  |  |  |  |

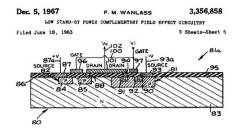

| <b>3 Some Aspects on CMOS Technology in High Frequency Design</b> .<br>3.1 The Birth of the Transistor and CMOS Technology | <b>29</b><br>29 |  |  |  |  |  |  |  |  |

| 3.1 The Birth of the Transistor and CMOS Technology                                                                        | 29              |  |  |  |  |  |  |  |  |

|   | 3.2  |                                                | 30 |

|---|------|------------------------------------------------|----|

|   |      | 1                                              | 32 |

|   |      |                                                | 34 |

|   | 3.3  |                                                | 36 |

|   |      | 3.3.1 Transconductances and Output Conductance | 37 |

|   |      | 1                                              | 38 |

|   |      |                                                | 39 |

|   |      | Gate Resistance                                | 39 |

|   |      |                                                | 40 |

|   | 3.4  |                                                | 41 |

|   |      | 0                                              | 41 |

|   |      | 6 6                                            | 42 |

|   |      |                                                | 43 |

|   |      | 5                                              | 43 |

|   |      |                                                | 44 |

|   |      |                                                | 45 |

|   |      |                                                | 45 |

|   |      | 1 5                                            | 46 |

|   |      |                                                | 47 |

|   | 3.5  |                                                | 48 |

|   |      |                                                | 49 |

|   |      |                                                | 50 |

|   |      | 3.5.3 Gate Induced Noise                       | 51 |

| 4 | Linl | k Budget                                       | 53 |

|   | 4.1  |                                                | 54 |

|   |      | 1                                              | 55 |

|   |      | 4.1.2 60 GHz WPAN Example                      | 56 |

| 5 | Pha  | sed Array Antenna                              | 59 |

|   | 5.1  |                                                | 59 |

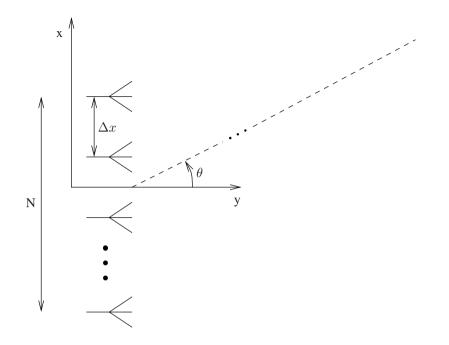

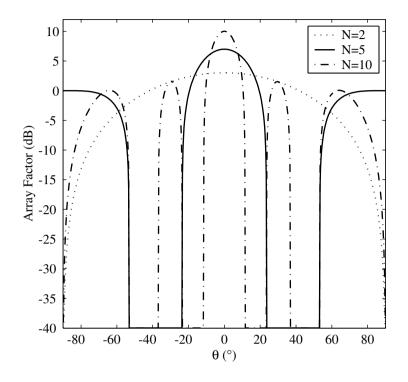

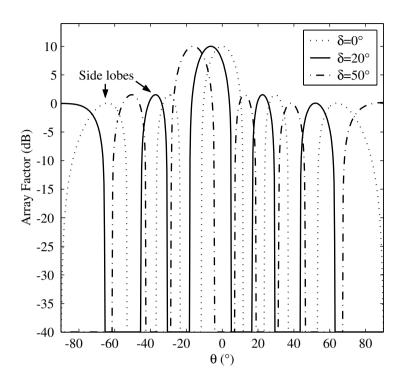

|   | 5.2  | Linear Phased Array Antenna                    | 60 |

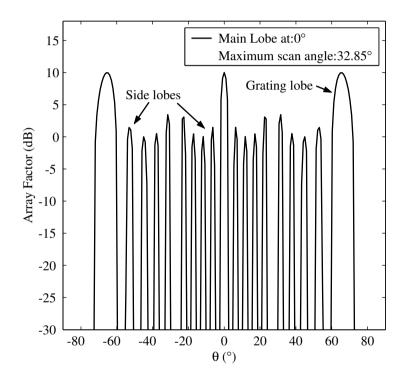

|   |      | 5.2.1 Grating Lobes                            | 63 |

| 6 | Bea  |                                                | 67 |

|   | 6.1  |                                                | 67 |

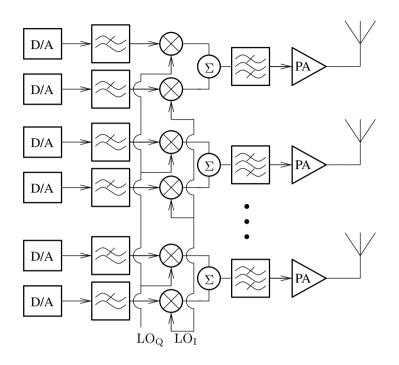

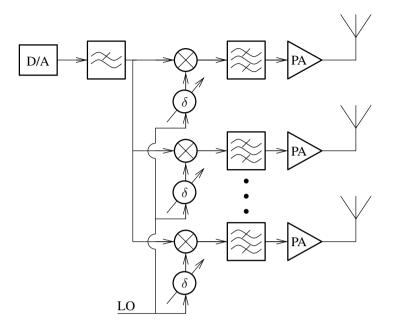

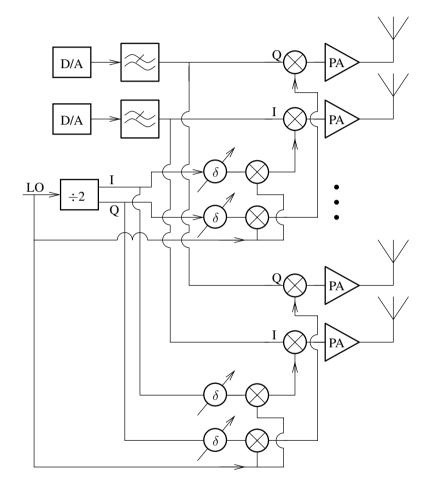

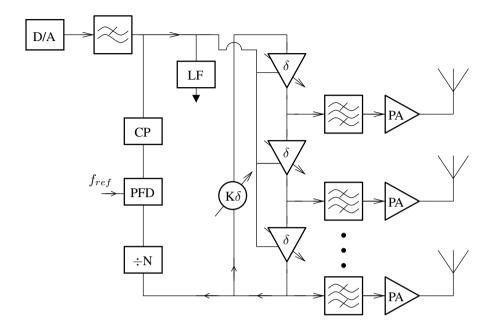

|   | 6.2  | 6                                              | 67 |

|   | 6.3  |                                                | 68 |

|   | 6.4  |                                                | 71 |

|   | 6.5  |                                                | 73 |

| 7 | Sun  |                                                | 75 |

|   |      |                                                | 79 |

|   |      |                                                |    |

| Α |      |                                                | 81 |

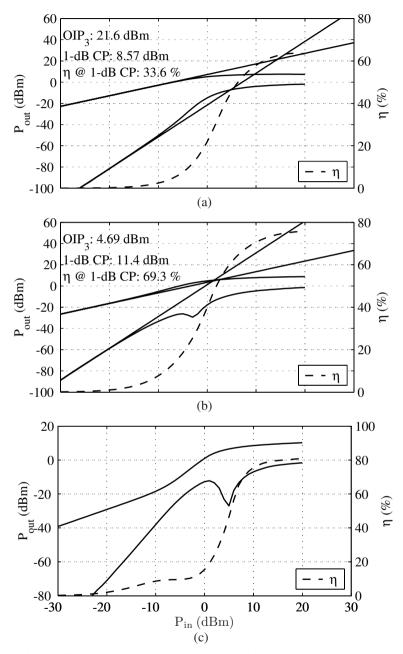

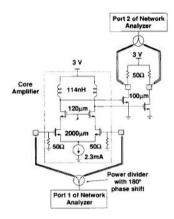

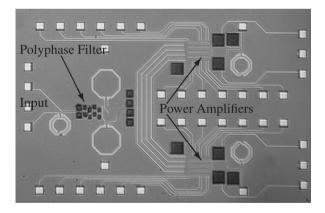

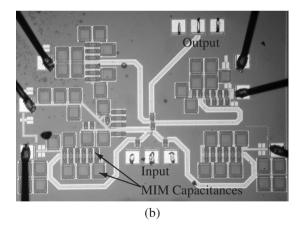

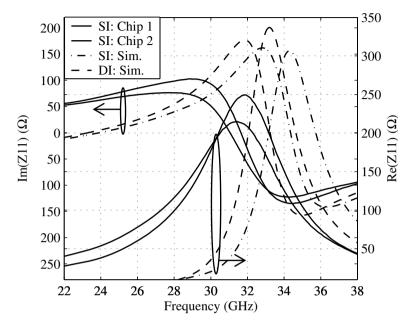

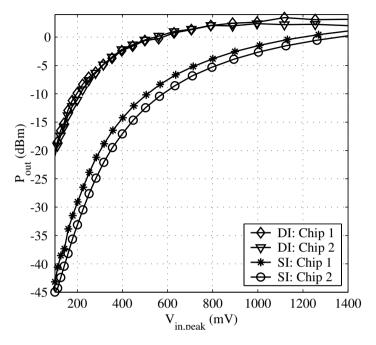

|   | A.1  | 10-GHz 130-nm CMOS Dual Power Amplifier        | 81 |

\_\_\_\_\_

|   | A.2 24-GHz 130-nm CMOS Power Amplifier                                       |

|---|------------------------------------------------------------------------------|

| R | eferences                                                                    |

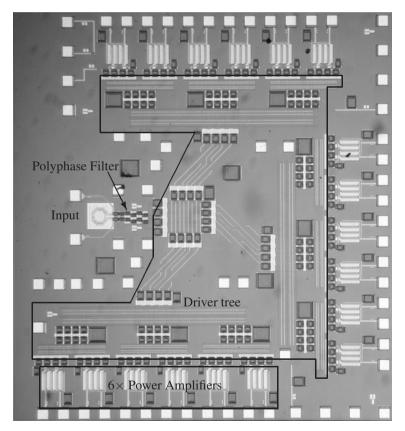

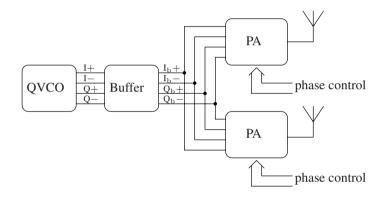

| A | n 8-GHz Beamforming Transmitter IC in 130-nm                                 |

|   | MOS                                                                          |

| 1 | Introduction                                                                 |

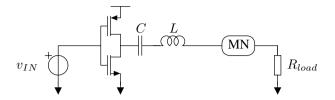

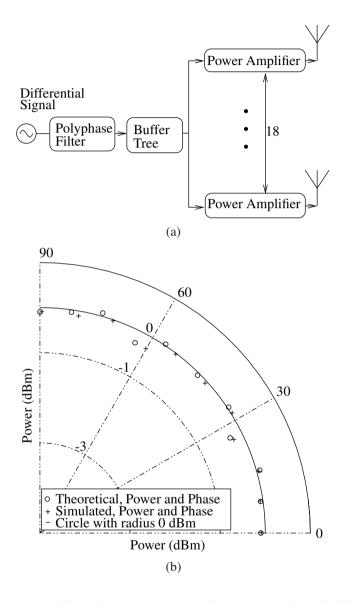

| 2 | Circuit Topology                                                             |

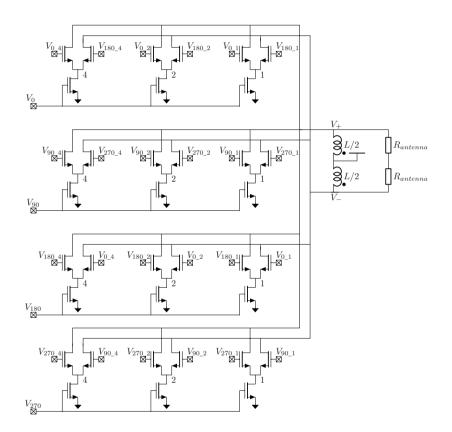

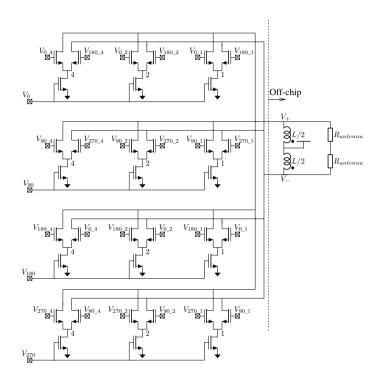

|   | 2.1 Power Amplifier                                                          |

|   | 2.2 Quadrature Voltage Controlled Oscillator and Buffer                      |

|   | 2.3 On-Chip Inductors                                                        |

| 3 | Results and Measurement                                                      |

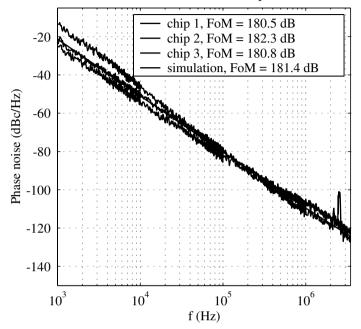

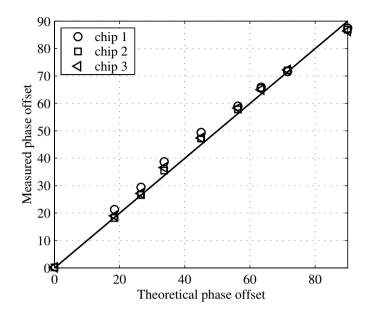

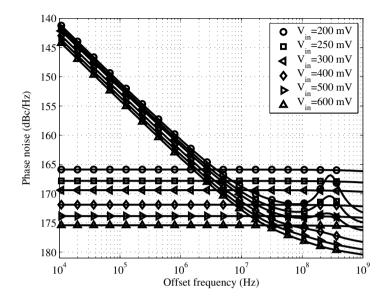

|   | 3.1 Quadrature Voltage Controlled Oscillator                                 |

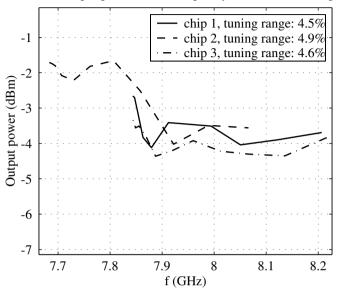

|   | 3.2 Power Amplifier                                                          |

|   | 3.3 Summary                                                                  |

| 4 | Conclusion                                                                   |

| R | eferences                                                                    |

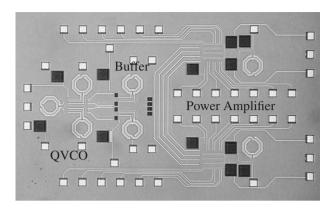

| B | 24-GHz Automotive Radar Transmitter with Digital eam Steering in 130-nm CMOS |

| 1 | Introduction                                                                 |

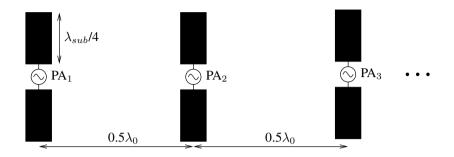

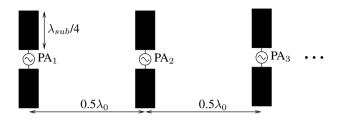

| 2 | Air Interface                                                                |

| 3 | Design and Simulation                                                        |

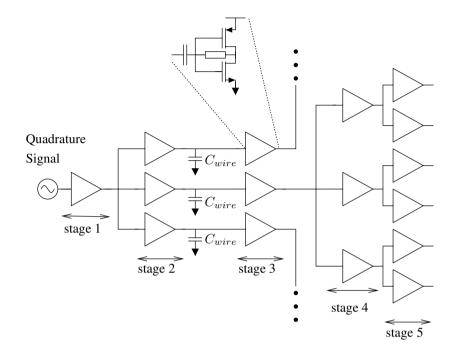

|   | 3.1 Polyphase Filter                                                         |

|   | 3.2 Inverter Tree Driver                                                     |

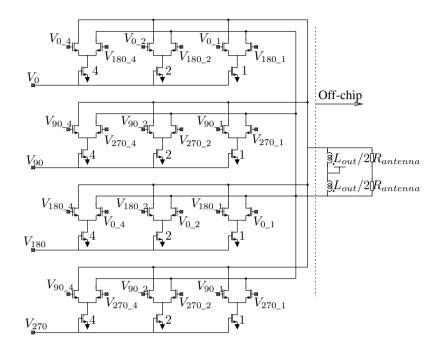

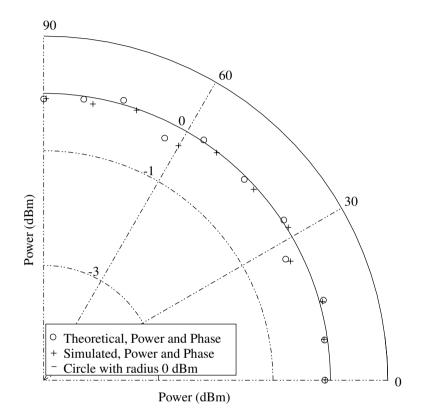

|   | 3.3 Power Amplifier                                                          |

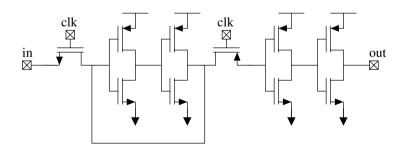

|   | 3.4 Shift Register                                                           |

|   | Conclusion                                                                   |

| R | eferences                                                                    |

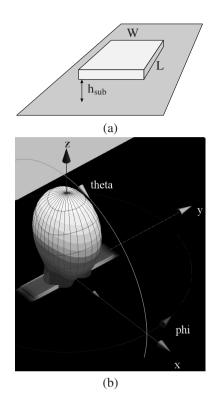

| A | ntenna Array for a 24-GHz Automotive Radar with                              |

|   | ipole Antenna Element Patches                                                |

| 1 | Introduction                                                                 |

| 2 | Radar Transmitter Circuit                                                    |

|   | Antenna Design                                                               |

| - | 3.1 Antenna Element                                                          |

|   | 3.2 Antenna Array                                                            |

|   |                                                                              |

| 4 | Conclusion                                                                   |

|   | AC<br>12<br>3<br>4 R<br>AB<br>12<br>3<br>4 R<br>AD<br>12                     |

| IV |                   | 0 GHz 130-nm CMOS Second Harmonic Power Ampli-<br>ers                                                                          |

|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------|

|    | 1                 | Introduction                                                                                                                   |

|    | 2                 | Circuit Topologies                                                                                                             |

|    | 3                 | Measurement Results                                                                                                            |

|    | 4                 | Conclusion                                                                                                                     |

|    | 5                 | Acknowledgment                                                                                                                 |

|    | R                 | eferences                                                                                                                      |

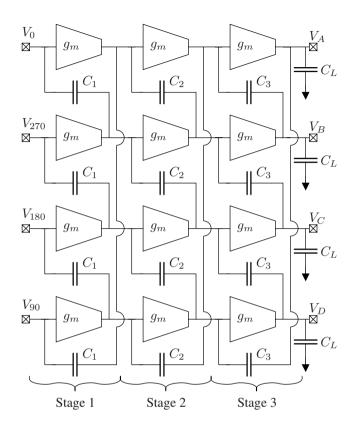

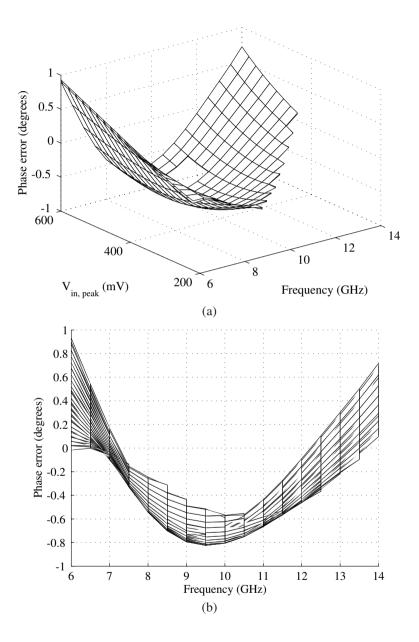

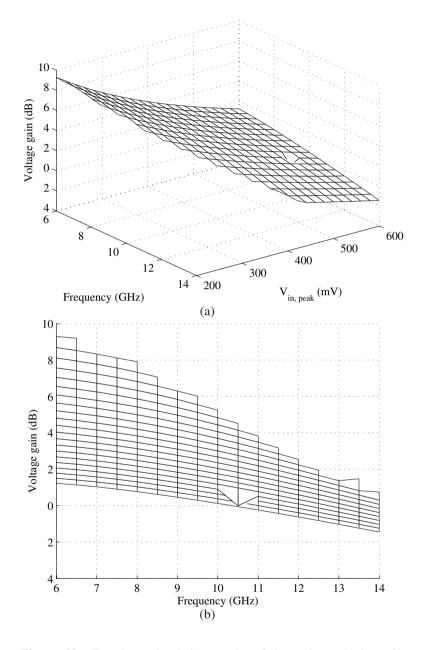

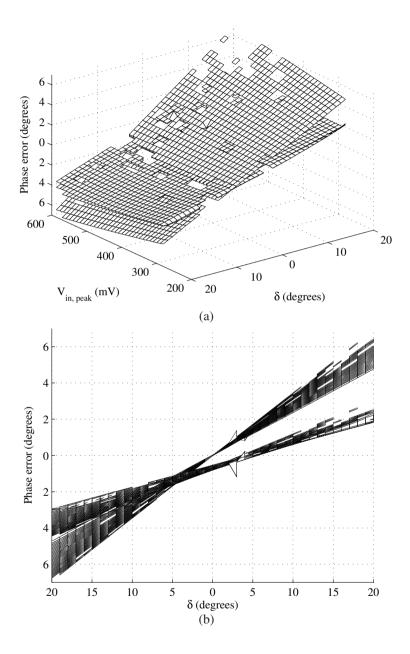

| 7  |                   | nalysis of a High Frequency and Wide Bandwidth Active<br>olyphase Filter Based on CMOS Inverters<br>Introduction               |

|    | 2                 | Passive Polyphase Filter                                                                                                       |

|    |                   | Active Polyphase Filter Analysis                                                                                               |

|    | -                 | 3.1 Stability of the Active Polyphase Filter                                                                                   |

|    | 4                 | Active Polyphase Filter Simulation                                                                                             |

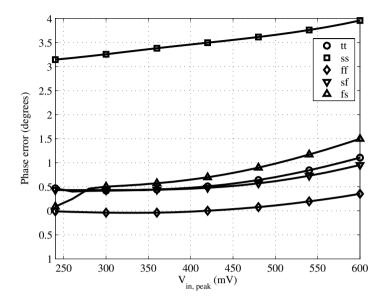

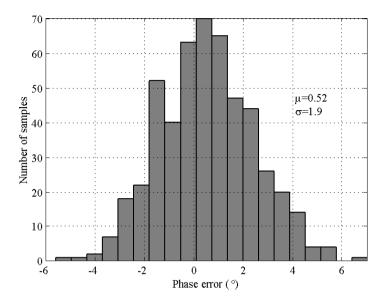

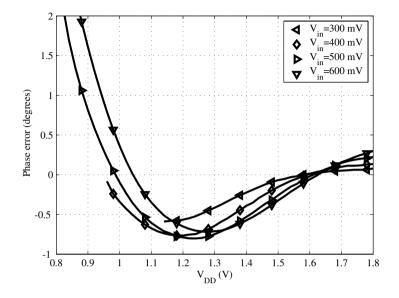

|    | <del>1</del><br>5 | Active Polyphase Filter Robustness Simulations                                                                                 |

|    | 5                 | 5.1 Process Variations       5.2 Supply Voltage Variation         5.3 Temperature Variation       5.2 Supply Voltage Variation |

|    | 6                 | Conclusion                                                                                                                     |

|    | R                 | eferences                                                                                                                      |

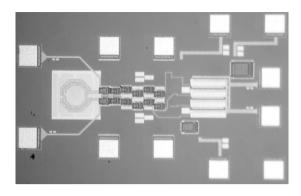

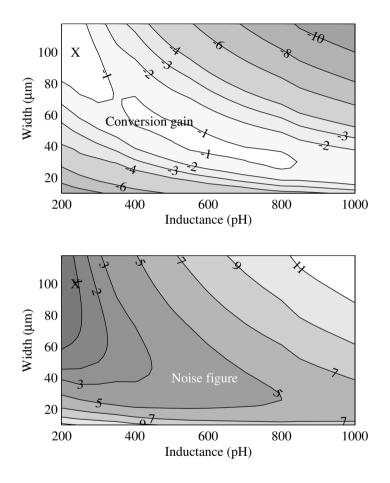

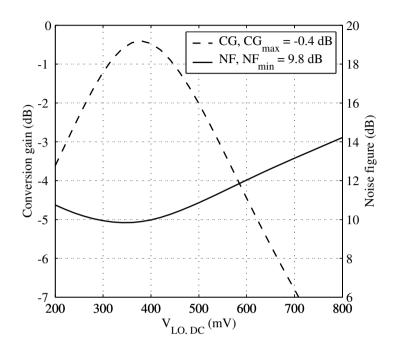

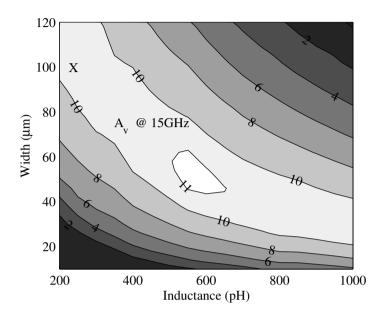

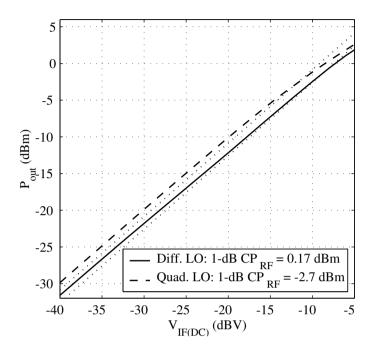

| VI | A<br>1            | . 30 GHz 90-nm CMOS Passive Subharmonic Mixer with<br>5 GHz Differential LO                                                    |

|    | 1                 | Introduction                                                                                                                   |

|    | 2                 | Subharmonic Mixer Topologies                                                                                                   |

|    |                   | 2.4 Summary                                                                                                                    |

|    | 3                 | Conclusion                                                                                                                     |

| 4 | Acknowledgment | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 205 |

|---|----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| R | eferences      | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 207 |

## Preface

This thesis summarizes my academic work in the Analog/RF Group at the Department of Electroscience and later the Department of Electrical and Information Technology, Faculty of Engineering, Lund University, for the Ph. D. degree in Circuit Design.

The content of the thesis is divided into two parts, where the first part is an introduction to the research area. General receiver and transmitter architectures are discussed, followed by different power amplifier topologies. CMOS transistor behavior and modeling is described in Chapter 3. In Chapter 4 link budget calculations are performed for two examples and in Chapter 5 the concept of phased array antennas for beam steering applications is illustrated. In Chapter 6 a few transmitter architectures suitable for integrated beamforming transmitters are discussed. The second part contains the included research papers.

#### **Part I: Introduction**

- **Chapter 1.** Starts with a short motivation to the research area and then lists the main research contributions of the thesis.

- **Chapter 2.** Begins with a short description of what a radio transceiver is. The most common transceiver architectures are then described. The heterodyne, the direct conversion, and the image rejection receivers are described as well as the direct conversion, the two-step, and the direct-modulation transmitters. The last section is dedicated to the power amplifier, which is, perhaps, the most critical and challenging block in the transmitter chain.

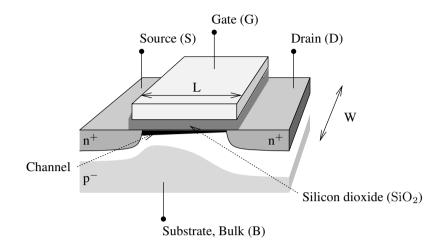

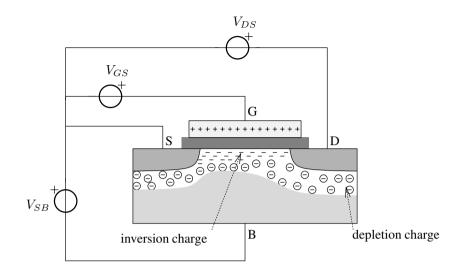

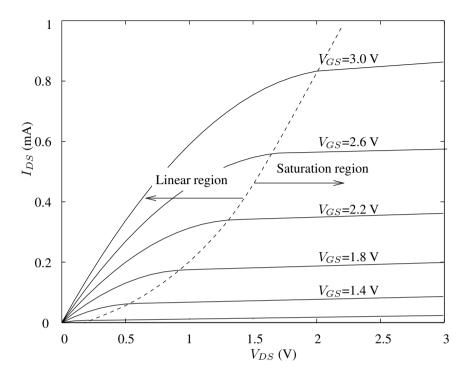

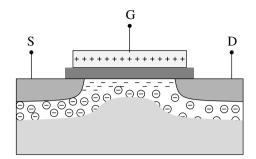

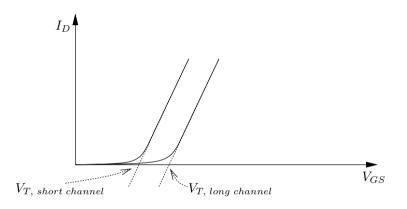

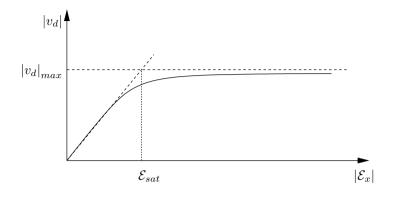

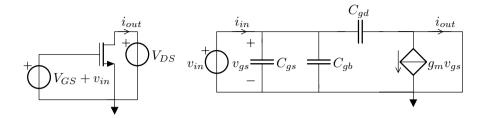

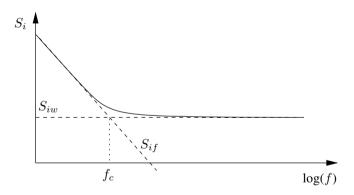

- **Chapter 3.** The operation of the n-channel MOS transistor is described. A low and medium frequency small signal model is described in strong inversion. Some small dimension effects are treated, e. g. channel length modulation, drain induced barrier lowering, and velocity saturation. The main noise sources in the MOS transistor are also discussed.

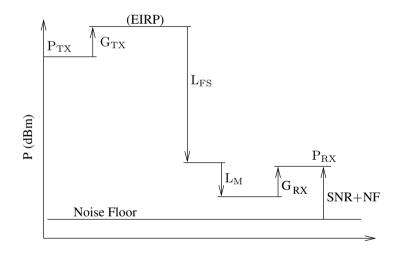

- **Chapter 4.** A short introduction to link budget calculations is presented and illustrated by two examples. The first example is a UMTS up-link budget calculation and the second example is a 60 GHz WPAN link budget calculation. In the second example, the use of an antenna array illustrates how to achieve high output power (EIRP) also in nanometer CMOS technologies.

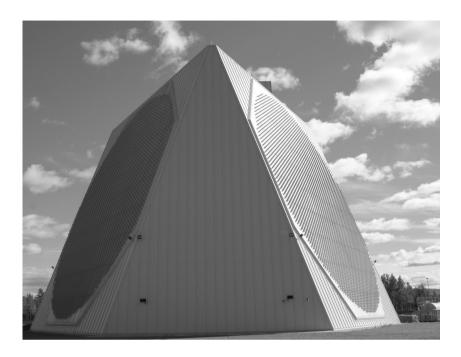

- **Chapter 5.** In this chapter the fundamentals of electrically scanned antennas are discussed. Topics such as directivity, array factor, and grating lobes are treated for phased array antennas. This chapter introduces the theory of how a beamforming transmitter should behave.

- **Chapter 6.** A few transmitter architectures suitable for integrated beamforming transmitters are discussed in this chapter. The following architectures are touched upon: baseband phase shifting, local oscillator phase shifting,

offset local oscillator phase shifting, variable ring oscillator phase shifting, and radio frequency phase shifting.

Chapter 7. A short summary of the included research papers.

**Chapter 8.** Different aspects of the research results of the thesis are discussed and future work based on these results are elaborated on.

#### Part II: Included Research Papers

The main contribution to the thesis is derived from the following publications.

- Johan Wernehag, Henrik Sjöland, "An 8-GHz Beamforming Transmitter IC in 130-nm CMOS", *IEEE Radio Frequency Integrated Circuits Symposium*, pp. 577–580, June 3–5, 2007, Honolulu, HI, USA.

- [2] Johan Wernehag, Henrik Sjöland, "A 24-GHz Automotive Radar Transmitter with Digital Beam Steering in 130-nm CMOS", *PhD Research in Microelectronics and Electronics*, pp. 481–484, June 11–16, 2006, Lecce Italy.

- [3] Johan Wernehag, Henrik Sjöland, "Antenna Array for a 24-GHz Automotive Radar with Dipole Antenna Element Patches", *International Symposium on Antennas and Propagation*, November 1–4, 2006, Singapore Singapore.

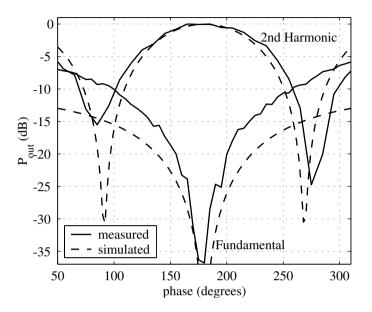

- [4] Johan Wernehag, Henrik Sjöland, "60 GHz 130-nm CMOS Second Harmonic Power Amplifiers", *IEEE Asia Pacific Conference on Circuits and Systems*, November 30–December 3, 2008, Macao China.

- [5] Johan Wernehag, Henrik Sjöland, "Analysis of a High Frequency and Wide Bandwidth Active Polyphase Filter Based on CMOS Inverters", *Analog Integrated Circuits and Signal Processing*, Springer Science, 2008, submitted.

- [6] Johan Wernehag, Henrik Sjöland, "A 30 GHz 90-nm CMOS Passive Subharmonic Mixer with 15 GHz Differential LO", *IEEE Proceedings of the 26th Norchip Conference*, November 17–18, 2008, Tallinn Estonia.

- **Related Publications:** The following publications are not included but contain overlapping, complementing and some additional material:

Johan Wernehag, Henrik Sjöland, "60 GHz Second Harmonic Power Amplifiers in 130-nm CMOS", *Proceedings of the 8th Swedish System-on-Chip Conference*, May 5–6, 2008, Södertuna slott Sweden.

Vara Prasad Goluguri, Johan Wernehag, Henrik Sjöland and Niklas Troedsson, "A Quad-Core 130-nm CMOS 57-64 GHz VCO", *Proceedings from the 9th GigaHertz Symposium*, March 5–6, 2008, Göteborg Sweden. Andreas Axholt, Filip Oredsson, Tony Petersson, Johan Wernehag and Henrik Sjöland, "A Low-Power Class-D Audio Amplifier in  $0.35 \mu m$  CMOS", *Proceedings of the 25th Norchip Conference*, pp. 1–4, November 19–20, 2007, Aalborg Denmark.

Johan Wernehag, Henrik Sjöland, "Measurement Considerations for a Phased Array Beamforming Transmitter", *RF Measurement Technology Conference*, September 11–12, 2007, Gävle Sweden.

Johan Wernehag, Henrik Sjöland, "Second Harmonic 60-GHz Power Amplifiers in 130-nm CMOS", *PhD Research in Microelectronics and Electronics*, pp. 149–152, July 2–5, 2007, Bordeaux France.

Johan Wernehag, Henrik Sjöland, "Beamforming Transmitter IC at 8-GHz in 130-nm CMOS", *Proceedings of the 7th Swedish System-on-Chip Conference*, May 14–15, 2007, Fiskebäckskil Sweden.

Johan Wernehag, Henrik Sjöland, "Automotive Radar Transmitter at 24-GHz with Digital Beam Steering in 130-nm CMOS", *Proceedings of the 6th Swedish System-on-Chip Conference*, May 4–5, 2006, Kolmården Sweden.

Niklas Troedsson, Johan Wernehag, Henrik Sjöland, "Differential Measurement and Parameter Extraction of Symmetrical Inductors", *Proceedings of the 23th Norchip Conference*, pp. 289–292, November 21–22, 2005, Oulu Finland.

Johan Wernehag, Henrik Sjöland, "A 90 nm CMOS 10 GHz Beam Forming Transmitter", *International Symposium on Signals, Circuits and System*, Volume I, pp. 375–378, July 14–15, 2005, Iasi Romania.

Johan Wernehag, Henrik Sjöland, "A Comparison of Two 10 GHz Beam Forming Transmitters, in 90 nm and 130 nm CMOS", *Proceedings of the 5th Swedish System-on-Chip Conference*, April 18–19, 2005, Tammsvik Sweden.

Johan Wernehag, Henrik Sjöland, "Low Power Radio Transmitter", *Proceedings from the Seventh GigaHertz Symposium*, November 4–5, 2003, Linköping Sweden.

**Published Pedagogical Papers and Teaching Material:** The author's interest in undergraduate teaching at the department has resulted in a new exercise material in the course *Analog Electronics*, mandatory for the junior Electrical Engineering classes and a couple of pedagogical publications presented at conferences.

Martin Anderson, Johan Wernehag, Henrik Sjöland, "Teaching Top Down Design of Analog/Mixed Signal ICs Through Design Projects", *Proceedings 37th Annual Conference Frontiers in Education*, pp. T1C-1–T1C-4, October 10–13, 2007, Milwaukee, WI, USA. Martin Anderson, Johan Wernehag and Henrik Sjöland, "IC-Project and Verification Course: Teaching Top Down Analog/Mixed Signal Design", *Proceedings of the 7th Swedish System-on-Chip Conference*, May 14–15, 2007, Fiskebäckskil Sweden.

Andreas Axholt, Tony Pettersson, Filip Oredsson, Johan Wernehag, and Henrik Sjöland, "IC-Project and Verification Course: An Integrated Class-D Audio Amplifier", *Proceedings of the 7th Swedish System-on-Chip Conference*, May 14–15, 2007, Fiskebäckskil Sweden.

Martin Anderson, Johan Wernehag, Roland Strandberg, *Analog Electronics, Exercises*, Department of Electroscience, Lund University, P.O. Box 118, SE-221 00 Lund, Sweden 2003.

## Acknowledgment

During my time as a postgraduate student I have met many people that have contributed in one way or another to this thesis, but to mention them all here is impractical and I restrict myself to those that have had substantial impact on this work.

I have been fortunate to have a very competent and enthusiastic supervisor, Professor Henrik Sjöland, who has inspired my work from master thesis to this doctoral thesis. His experience and knowledge in analog- and RF design cannot be overestimated.

I would like to thank all the colleagues at the department for a nice and relaxed atmosphere and some fruitful discussions in various fields, in particular the colleagues in the analog/RF group whom it have been nice to 'waist' time with, without mentioning names I want you all to feel included. The cooperation within the group has also, in a few cases, resulted in co-authored papers: Niklas Troedsson, Martin Anderson, and Andreas Axholt, thanks for bearing with me in the pursuit for perfection. A special thanks to Fredrik Tillman, for being there to discuss everything from process aspects to architectural considerations in the beginning of my PhD studies. I would also like to thank all the different people that I have been traveling with to different conferences, their companionship have made the trips more enjoyable: Peter Sjöblom, Henrik Sjöland, Markus Törmänen, and Andreas Axholt. I would also like to express my gratitude to all the anonymous conference organizers for choosing such nice locations.

I am very thankful for the help and support from the technical staff and administration at the department over the years. A special thanks to Erik Jonsson for quick computer support '24–7', Stefan Molund for Cadence support and making sure that the simulation tools were working, Lars Hedenstjerna for all kinds of mechanical assistance, such as bonding the chips, and last Pia Bruhn who has helped me with all different kinds of administration tasks and travel arrangements. A special thanks goes to Lars Olsson for proofreading this thesis.

Last but not least I would like to thank my fiancée, Christina Larsson, for her love and support, and excepting my sometimes distracted mind over the last years. Now I am back! To my parents, Rolf and Marianne Wernehag, thanks for believing in me throughout the years, always supporting me in the pursuit for higher education. My sisters, Camilla Wernehag, it was an inspiration and challenge trying to follow your results in school. In later days always good to talk to about everything, thanks for being there and listening.

I am grateful for the financial support from the Swedish Agency for Innovation Systems (Vinnova) and Competence Center for Circuit Design (CCCD).

John Mencheg

...*I knew you had to be tough or die...* "A Boy Named Sue" — Johnny Cash

# List of Acronyms

| AC   | Alternating Current                                        |

|------|------------------------------------------------------------|

| ACC  | Adaptive Cruise Control                                    |

| AICC | Adaptive Intelligent Cruise Control                        |

| AF   | Array Factor                                               |

| ADC  | Analog-to-Digital Converter                                |

| ADS  | Advanced Design System, a simulation software from Agilent |

| BB   | Baseband                                                   |

| BPF  | Band Pass Filter                                           |

| BSF  | Band Select Filter                                         |

| BSIM | Berkeley Short-channel IGFET Model                         |

| CG   | Conversion Gain                                            |

| CLM  | Channel Length Modulation                                  |

| CMOS | Complementary Metal Oxide Semiconductor                    |

| СР   | Compression Point                                          |

| CSF  | Channel Select Filter                                      |

| DC   | Direct Current                                             |

| DI   | Differential Input                                         |

| DIBL | Drain Induced Barrier Lowering                             |

| DUT  | Device Under Test                                          |

| EBT  | Ericsson Technology Licensing                              |

| EIRP | Equivalent Isotropic Radiated Power                        |

| EM   | Electro Magnetic                                           |

| ETSI | European Telecommunication Standards Insitute              |

| F    | Noise Factor                                               |

| FCC  | Federal Communication Commission                           |

| FDD  | Frequency Division Duplexing                               |

| FET  | Field Effect Transistor                                    |

| FoM  | Figure of Merit                                            |

| FoV     | Field of View                                       |

|---------|-----------------------------------------------------|

| FS      | Frequency Synthesizer                               |

| Gbps    | Giga bit per second                                 |

| GSG     | Ground Signal Ground                                |

| GSM     | Global System for Mobile Communications             |

| HPBW    | Half Power Beam Width                               |

| IBM     | International Business Machines                     |

| IC      | Integrated Circuit                                  |

| IEEE    | Institute of Electrical and Electronics Engineers   |

| IF      | Intermediate Frequency                              |

| IGFET   | Insulated Gate Field Effect Transistor              |

| $IIP_3$ | 3rd order Input referred Intercept Point            |

| IP      | Intercept Point                                     |

| IRF     | Image Reject Filter                                 |

| IRR     | Image Rejection Ratio                               |

| ISS     | Impedance Standard Substrate                        |

| ITRS    | International Technology Roadmap for Semiconductors |

| LNA     | Low Noise Amplifier                                 |

| LO      | Local Oscillator                                    |

| LPF     | Low Pass Filter                                     |

| MIM     | Metal-Insulator-Metal                               |

| MIMO    | Multiple Input Multiple Output                      |

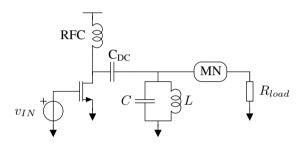

| MN      | Matching Network                                    |

| MOS     | Metal Oxide Semiconductor                           |

| NF      | Noise Figure                                        |

| nMOS    | N-channel MOS transistor                            |

| OFDM    | Orthogonal Frequency-Division Multiplexing          |

| $OIP_3$ | 3rd order Output referred Intercept Point           |

| PA      | Power Amplifier                                     |

| PAE     | Power-Added Efficiency                              |

| PCB                                                                             | Printed Circuit Board                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL                                                                             | Phase Locked Loop                                                                                                                                                                                                                                                                  |

| pMOS                                                                            | P-channel MOS transistor                                                                                                                                                                                                                                                           |

| QVCO                                                                            | Quadrature Voltage Controlled Oscillator                                                                                                                                                                                                                                           |

| RF                                                                              | Radio Frequency                                                                                                                                                                                                                                                                    |

| RFC                                                                             | Radio Frequency Choke                                                                                                                                                                                                                                                              |

| RFIC                                                                            | Radio Frequency Integrated Circuit                                                                                                                                                                                                                                                 |

| rms                                                                             | Root Mean Square                                                                                                                                                                                                                                                                   |

| SGS                                                                             | Signal Ground Signal                                                                                                                                                                                                                                                               |

| SHM                                                                             | Subharmonic Mixer                                                                                                                                                                                                                                                                  |

| SI                                                                              | Single-ended Input                                                                                                                                                                                                                                                                 |

| SiGe                                                                            | Silicon-Germanium                                                                                                                                                                                                                                                                  |

| $\mathrm{SiO}_2$                                                                | Silicon dioxide                                                                                                                                                                                                                                                                    |

| SNR                                                                             | Signal-to-Noise Ratio                                                                                                                                                                                                                                                              |

| SoC                                                                             | System-on-Chip                                                                                                                                                                                                                                                                     |

|                                                                                 |                                                                                                                                                                                                                                                                                    |

| SpectreRF                                                                       | Spectre Radio Frequency, a simulation software from Cadence                                                                                                                                                                                                                        |

| SpectreRF<br>SRR                                                                | Spectre Radio Frequency, a simulation software from Cadence<br>Short Range Radar                                                                                                                                                                                                   |

| -                                                                               |                                                                                                                                                                                                                                                                                    |

| SRR                                                                             | Short Range Radar                                                                                                                                                                                                                                                                  |

| SRR<br>SSB                                                                      | Short Range Radar<br>Single Sideband                                                                                                                                                                                                                                               |

| SRR<br>SSB<br>SWR                                                               | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio                                                                                                                                                                                                                        |

| SRR<br>SSB<br>SWR<br>TDD                                                        | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing                                                                                                                                                                                             |

| SRR<br>SSB<br>SWR<br>TDD<br>TL                                                  | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line                                                                                                                                                                        |

| SRR<br>SSB<br>SWR<br>TDD<br>TL<br>Tx                                            | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line<br>Transmitter                                                                                                                                                         |

| SRR<br>SSB<br>SWR<br>TDD<br>TL<br>Tx<br>UMC                                     | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line<br>Transmitter<br>United Microelectronics Corporation                                                                                                                  |

| SRR<br>SSB<br>SWR<br>TDD<br>TL<br>Tx<br>UMC<br>UMTS                             | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line<br>Transmitter<br>United Microelectronics Corporation<br>Universal Mobile Telecommunication System                                                                     |

| SRR<br>SSB<br>SWR<br>TDD<br>TL<br>Tx<br>UMC<br>UMTS<br>US                       | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line<br>Transmitter<br>United Microelectronics Corporation<br>Universal Mobile Telecommunication System<br>United States                                                    |

| SRR<br>SSB<br>SWR<br>TDD<br>TL<br>Tx<br>UMC<br>UMTS<br>US<br>US                 | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line<br>Transmitter<br>United Microelectronics Corporation<br>Universal Mobile Telecommunication System<br>United States<br>Ultra WideBand                                  |

| SRR<br>SSB<br>SWR<br>TDD<br>TL<br>TX<br>UMC<br>UMTS<br>UMTS<br>US<br>UWB<br>VCO | Short Range Radar<br>Single Sideband<br>Standing Wave Ratio<br>Time Division Duplexing<br>Transmission Line<br>Transmitter<br>United Microelectronics Corporation<br>Universal Mobile Telecommunication System<br>United States<br>Ultra WideBand<br>Voltage Controlled Oscillator |

# **List of Symbols**

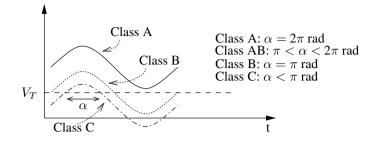

| $\alpha$                                            | (rad) Conduction angle of an amplifier or charge distribution profile                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $A_{em}$                                            | Maximum effective area of an antenna                                                                                                                                                                                                                                                                                                       |

| C <sub>DC</sub>                                     | (F) DC blocking capacitance                                                                                                                                                                                                                                                                                                                |

| $C_{ov}^{'}$                                        | (F/m) Capacitance per unit length from gate to source/drain                                                                                                                                                                                                                                                                                |

| $C_{ox}^{\prime}$                                   | (F/m <sup>2</sup> ) Capacitance per unit area                                                                                                                                                                                                                                                                                              |

| $C_{tg}$                                            | (F) Capacitance from trace-to-ground of an inductor                                                                                                                                                                                                                                                                                        |

| $C_{tt}$                                            | (F) Capacitance from trace-to-trace of an inductor                                                                                                                                                                                                                                                                                         |

| $\mathcal{E}_{sat}$                                 | (V/m) Critical field strength for velocity saturation                                                                                                                                                                                                                                                                                      |

| D                                                   | Duty cycle                                                                                                                                                                                                                                                                                                                                 |

| D                                                   | Directivity of an antenna                                                                                                                                                                                                                                                                                                                  |

| $\epsilon$                                          | Amplitude error in an image reject architecture                                                                                                                                                                                                                                                                                            |

| $\epsilon_x$                                        | (Vs/Am) Permittivity of material $x$                                                                                                                                                                                                                                                                                                       |

| η                                                   | (i) The ratio of $C_{max}$ to $C_{min}$ in a varactor or<br>(ii) Degree of non-saturation                                                                                                                                                                                                                                                  |

| $\eta_D$                                            | Drain efficiency                                                                                                                                                                                                                                                                                                                           |

|                                                     |                                                                                                                                                                                                                                                                                                                                            |

| $f_c$                                               | <ul><li>(Hz) Carrier frequency of a radio signal or</li><li>(Hz) Corner frequency between white and 1/<i>f</i>-noise</li></ul>                                                                                                                                                                                                             |

| $f_c$<br>$f_{sr}$                                   |                                                                                                                                                                                                                                                                                                                                            |

|                                                     | (Hz) Corner frequency between white and 1/f-noise                                                                                                                                                                                                                                                                                          |

| $f_{sr}$                                            | <ul><li>(Hz) Corner frequency between white and 1/<i>f</i>-noise</li><li>(Hz) Self-resonance frequency</li></ul>                                                                                                                                                                                                                           |

| $f_{sr}$<br>$f_T$                                   | <ul><li>(Hz) Corner frequency between white and 1/<i>f</i>-noise</li><li>(Hz) Self-resonance frequency</li><li>(Hz) Transition frequency of a transistor</li></ul>                                                                                                                                                                         |

| $f_{sr}$<br>$f_T$<br>$f_x$                          | <ul> <li>(Hz) Corner frequency between white and 1/f-noise</li> <li>(Hz) Self-resonance frequency</li> <li>(Hz) Transition frequency of a transistor</li> <li>(Hz) Frequency of the signal called x</li> </ul>                                                                                                                             |

| $f_{sr}$<br>$f_T$<br>$f_x$<br>$\gamma$              | (Hz) Corner frequency between white and 1/ <i>f</i> -noise<br>(Hz) Self-resonance frequency<br>(Hz) Transition frequency of a transistor<br>(Hz) Frequency of the signal called $x$<br>( $\sqrt{V}$ ) The body effect coefficient                                                                                                          |

| $f_{sr}$<br>$f_T$<br>$f_x$<br>$\gamma$<br>I+        | (Hz) Corner frequency between white and 1/f-noise<br>(Hz) Self-resonance frequency<br>(Hz) Transition frequency of a transistor<br>(Hz) Frequency of the signal called $x$<br>( $\sqrt{\nabla}$ ) The body effect coefficient<br>In phase positive signal                                                                                  |

| $f_{sr}$<br>$f_T$<br>$f_x$<br>$\gamma$<br>I+<br>I-  | <ul> <li>(Hz) Corner frequency between white and 1/<i>f</i>-noise</li> <li>(Hz) Self-resonance frequency</li> <li>(Hz) Transition frequency of a transistor</li> <li>(Hz) Frequency of the signal called <i>x</i></li> <li>(√∇) The body effect coefficient</li> <li>In phase positive signal</li> <li>In phase negative signal</li> </ul> |

| $f_{sr}$ $f_T$ $f_x$ $\gamma$ $I+$ $I-$ $\Im m$     | (Hz) Corner frequency between white and 1/ <i>f</i> -noise<br>(Hz) Self-resonance frequency<br>(Hz) Transition frequency of a transistor<br>(Hz) Frequency of the signal called $x$<br>( $\sqrt{V}$ ) The body effect coefficient<br>In phase positive signal<br>In phase negative signal<br>Imaginary part                                |

| $f_{sr}$ $f_T$ $f_x$ $\gamma$ $I+$ $I-$ $\Im m$ $k$ | (Hz) Corner frequency between white and $1/f$ -noise<br>(Hz) Self-resonance frequency<br>(Hz) Transition frequency of a transistor<br>(Hz) Frequency of the signal called $x$<br>( $\sqrt{V}$ ) The body effect coefficient<br>In phase positive signal<br>In phase negative signal<br>Imaginary part<br>(VC/K) Boltzmann's constant       |

| $L_s$        | (H) Series inductance                                                                                      |

|--------------|------------------------------------------------------------------------------------------------------------|

| $\mu$        | <ul> <li>(i) (m<sup>2</sup>/Vs) Mobility of electrons or</li> <li>(ii) Mean value of a data set</li> </ul> |

| n            | Number of turns of an inductor                                                                             |

| $N_A$        | (m <sup>-3</sup> ) Acceptor dopant concentration                                                           |

| $N_D$        | (m <sup>-3</sup> ) Donor dopant concentration                                                              |

| $\phi_0$     | (V) Surface potential of two-terminal MOS structure in strong inversion                                    |

| $\phi_F$     | (V) Fermi potential                                                                                        |

| $\phi_t$     | (V) Thermal voltage, equal to 26 mV in room temperature                                                    |

| $\psi_s$     | (V) Surface potential in the MOS channel                                                                   |

| $\Re e$      | Real part                                                                                                  |

| $R_s$        | $(\Omega)$ Series resistance                                                                               |

| $R_{sh}$     | $(\Omega)$ Effective resistance of an inductor shield                                                      |

| $R_{\Box}$   | $(\Omega)$ Resistance per square of a material                                                             |

| $\omega_0$   | (rad/s) Angular resonance frequency                                                                        |

| $\omega_x$   | (rad/s) Angular frequency of the signal called $x$                                                         |

| $\sigma$     | Standard deviation of a data set                                                                           |

| $\theta$     | (°) Phase error in an image reject architecture                                                            |

| $\theta_b$   | $(V^{-1})$ Mobility degradation parameter due to vertical field in a MOSFET                                |

| $P_x$        | (W) Power of signal $x$                                                                                    |

| Q            | Quality factor                                                                                             |

| Q+           | Quadrature phase positive signal                                                                           |

| Q-           | Quadrature phase negative signal                                                                           |

| $v_d$        | (m/s) Average velocity of charge carriers in the channel                                                   |

| $V_{DS}^{'}$ | (V) The value of $V_{DS}$ at onset of saturation                                                           |

| $V_{FB}$     | (V) The flat band potential                                                                                |

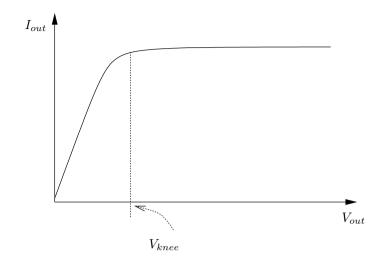

| $V_{knee}$   | (V) Voltage at the output of an amplifier in saturation                                                    |

| $V_T$        | (V) Threshold voltage of a transistor                                                                      |

| q            | (C) The negative charge of a single electron                                                               |

# Introduction

## Introduction

## **Chapter 1**

## **Motivation and Research Contributions**

#### 1.1 Motivation

There has always been a need for people to communicate and in many independent civilizations ways to communicate over long distances have evolved. The native Americans as well as Australian aboriginals communicated by smoke puffs. The aboriginals also communicated with different sounds, while people in woodland areas often used drums to communicate.

In China 500 BC a large canal construction started and along the canals watchtowers were built [7]. In these towers light sources was placed and by exposing and de-exposing the light in the direction of the next watchtower they were able to send messages down the canal in a 'Morse-like' fashion. This helped the emperor to communicate and control his large empire. This technique to communicate was still in use during the second world war on vessels at sea.

In the beginning of the 20th century wireless radio communication began with Guglielmo Marconi successful transmission of radio signals across the Atlantic Ocean [8, 9]. Since then radio communication development has been intense, and still is. The challenges today differ from the ones encountered by the pioneers, like Marconi and Popov, but still challenges remain and research in this area is therefore highly motivated. The existing public wireless communication standards like GSM, UMTS, Bluetooth etc. put high demands on the technology, especially at the time when they were introduced. The coming standards will also do this, as they too are trying to get the highest possible performance out of the system. But even though the performance requirements are tough, low cost is the main driving force.

Most of the building blocks in consumer electronics today work in the digital domain, and when treating digital signals the dominating integrated circuit (IC) technology is complementary metal oxide semiconductor (CMOS). A major part of the cost of consumer electronics is associated with assembling the different circuits. By implementing the analog and radio frequency parts in CMOS together with the digital circuits, the number of chips can be reduced. The ultimate reduction leads to a sin-

gle chip solution, usually called a system-on-chip (SoC). Another advantage of using the dominant technology is that the price per chip area is cheap in mass production leading to a more cost-efficient solution.

The possibility to integrate analog and digital circuits motivates a continued research of CMOS radio frequency circuits. Already today CMOS is successfully used in many systems, but demands on higher data rates will force some future systems to be more wideband. These larger bandwidths are available at high frequencies, e. g. at 60 GHz. The question is if CMOS will then still be a good choice of technology?

The decreasing supply voltage in sub-micrometer CMOS technology nodes makes the implementation of power amplifiers particularly difficult, therefore the focus in this thesis has been on power amplifiers. At high frequencies, a beamforming transmitter architecture is possible since the phased array antennas decrease in size. The demand on output power from the power amplifier decreases in a beamforming transmitter, thanks to increased antenna directivity and the possibility to use multiple power amplifiers in parallel.

#### **1.2 Research Contribution**

The main contributions are summarized in this section.

- ♦ A power amplifier with a full 360° range phase control has been designed and verified by measurements. The output phase control is achieved by summation of weighted quadrature signals. The weighting is performed by means of binary weighted transistor banks. An array of such power amplifiers can be put on a single chip, were the output phase of each of the power amplifiers is steerable individually. The different phases of the power amplifiers can be set by a digital control word, clocked in by a shift register.

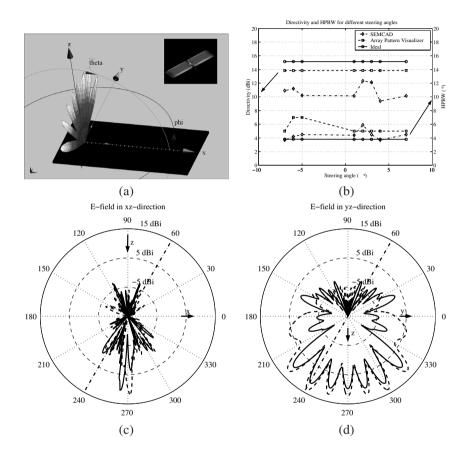

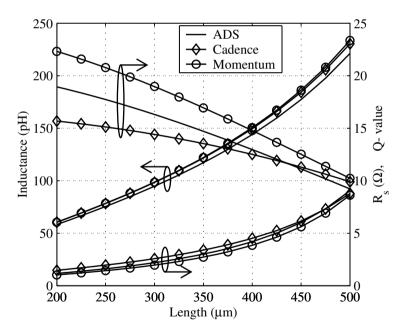

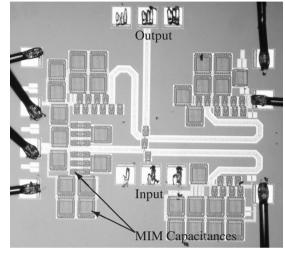

- An antenna array of dipole antenna element patches has been simulated to assess the suitability of such an antenna array in an integrated application, using power amplifiers with differential outputs.

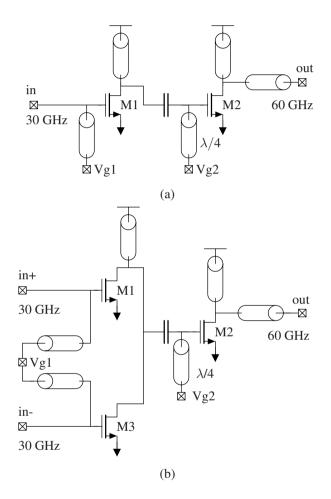

- Two different frequency doubling power amplifier architectures at 60 GHz have been implemented and measured, showing that the concept of frequency conversion at the antenna interface is possible. The benefits are larger tuning range for the on-chip voltage controlled oscillator, since it can operate at half the output frequency, and less losses thanks to smaller parasitics.

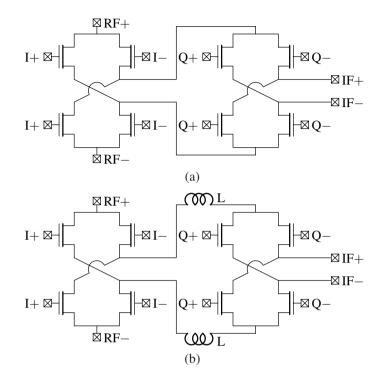

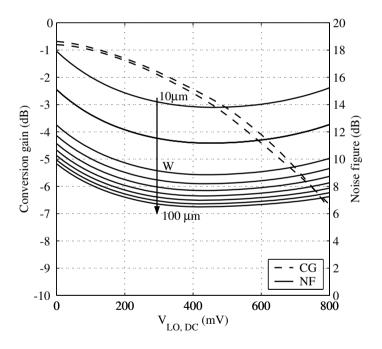

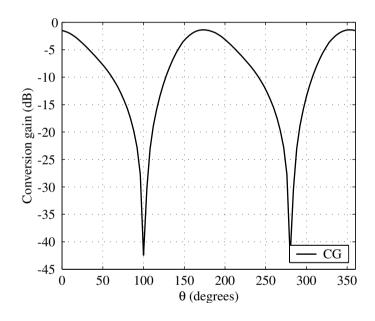

- ♦ A passive subharmonic mixer with differential local oscillator at 15 GHz and radio frequency at 30 GHz has been investigated and taped-out. The new topology uses a filter between the two mixer cores. As a result mixing is accomplish with a differential local oscillator instead of a quadrature one.

In a beamforming transmitter with multiple mixers it is beneficial to have a differential local oscillator, both regarding area and crosstalk. A combination of a frequency doubling power amplifier and a subharmonic mixer further increases the tuning range of the local oscillator and reduces the losses and sensitivity to parasitics.

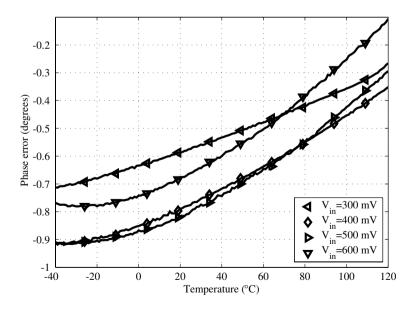

♦ An active polyphase filter was analyzed and analytic equations for the voltage gain and phase transfer function of a loaded stage have been derived. The quadrature phase error over wide bandwidth and for large input differential phase error has been examined, showing good performance. A thorough evaluation of robustness against process parameter spread, voltage variation, and temperature has been conducted.

## Chapter 2

## **Radio Transceiver Fundamentals**

#### 2.1 What is a Radio Transceiver?

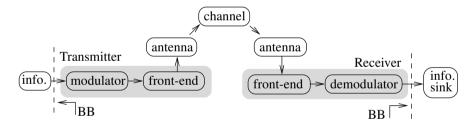

A transceiver consists of two parts; a transmitter and a receiver. The word transceiver is a fusion of these two words, *transmitter* and receiver. In the transmitter, the information to be transmitted is converted to a modulated radio frequency (RF) signal, which is amplified and fed to an antenna. The receiver does the opposite, it receives the RF signal through an antenna, amplifies, downconverts and demodulates it, and if everything is successful the original information is then retrieved. In Fig. 1 this is illustrated in a simple block diagram. The figure is meant as an illustration, and there are other ways this can be implemented, for instance the modulation and demodulation can also take place in the baseband (BB) regime.

Figure 1: A simple block diagram of a radio transmission

#### 2.2 Receiver

This section contains a brief discussion of receiver architectures. A more detailed description can be found in e. g. [10, 11].

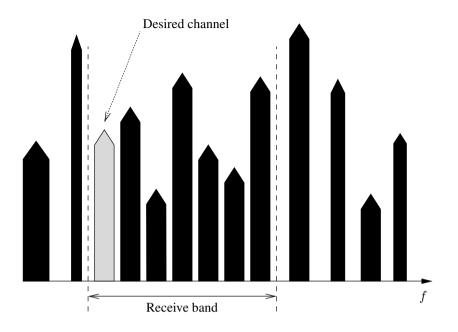

The main objective of the receiver is to filter out and amplify the channel containing the information, and also to downconvert it to lower frequencies. This is a challenging task, since the radio frequency spectrum is full of interfering signals, some of which are close in frequency (in-band) and others more distant (out-of-band). The

Figure 2: A typical radio spectrum that a receiver must be able to cope with

signal level of the different interferers can be much higher than that of the desired signal, see Fig. 2.

The most common architectures like the heterodyne receiver<sup>1</sup>, the image reject receiver, and the direct conversion receiver will be described in the following sections. Also a short section on how to calculate the overall receiver linearity and sensitivity is included.

#### 2.2.1 Receiver Architectures

#### **Heterodyne Receiver**

The heterodyne receiver is perhaps the most common architecture<sup>2</sup> [15, 16].

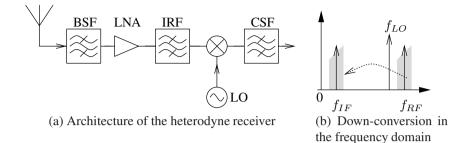

The heterodyne receiver architecture (Fig. 3) has a band select filter (BSF) close

<sup>&</sup>lt;sup>1</sup>The word heterodyne is derived from the Greek roots hetero-, 'different', and -dyne, 'power' [12].

<sup>&</sup>lt;sup>2</sup>Their are two types of of heterodyne receivers, firstly the heterodyne which historically had one downconversion to a rather low intermediate frequency (IF), in the audible frequency region. The heterodyne principle was invented by Reginald Aubrey Fessenden on Chrismas Eve 1906. He transmitted the first audio radio broadcast in history from Brant Rock, Massachusetts. The second type is the supersonic heterodyne receiver, or as it is more commonly called, the superheterodyne receiver. It also has a single down-conversion, but to a higher IF. It was patented by Edwin Howard Armstrong in 1918. Nowadays generally no distinction is made between the heterodyne and the superheterodyne, and that practice will be followed in this thesis as well [13, 14].

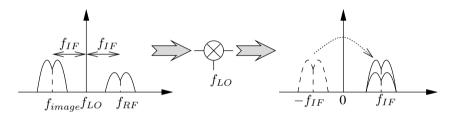

**Figure 3:** (a) The architecture of a heterodyne receiver. (b) Down-conversion in the frequency domain

to the antenna, which provides attenuation of out-of-band interferers. The radio frequency (RF) signal is then amplified by a low noise amplifier (LNA) followed by a second band pass filter (BPF). This filter is sometimes called image reject filter (IRF). These two filters can together provide an attenuation of 100 dB at frequencies far from the channel. The requirements on these filter are often tough and therefore they typically have to be implemented off-chip, which makes them bulky and expensive [9–11, 15, 17]. The second filter precedes the mixer, where the RF signal is downconverted to an intermediate frequency (IF) by mixing with a local oscillator (LO) signal. After the mixer, a channel select filter (CSF) filters out the channel to be demodulated. The selected frequency is at  $f_{IF} = |f_{RF} - f_{LO}|$  in Fig. 3(b).

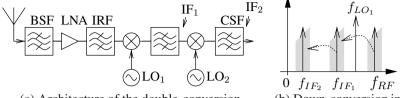

Sometimes the frequency down-conversion is performed in two steps i. e. with two separate mixer stages, resulting in the double-conversion heterodyne architecture, see Fig. 4. There are a few advantages with a double conversion, the gain and filtering can be distributed over more frequencies, which is beneficial when it comes to linearity, stability, and noise trade-offs, see Section 2.2.2. The gain being distributed over several frequencies reduces the risk for the receiver to self oscillate. The drawback is that the architecture is more complicated, e. g. it requires two different LOs.

The main problem of the heterodyne architecture is that the mixer is unable to separate the wanted channel from the image channel, as depicted in Fig. 5. The image is located on the opposite side of the  $f_{LO}$  compared to  $f_{RF}$ , and the distance between RF signal and image is  $2 \cdot f_{IF}$ . If the image is not rejected/suppressed before the mixer, it can not be distinguished from the wanted signal, since it will be downconverted to the same IF. The IRF is therefore placed before the mixer to take care of this issue.

The LNA has to be matched to the impedance of the off-chip filters, often 50  $\Omega$ , and the same goes for the input of the downconverter. The problem with the image leads to a trade-off in choosing  $f_{IF}$ . A high  $f_{IF}$  results in large spacing between the RF and the image, simplifying the image reject filter, but a high  $f_{IF}$  results in more difficulties with the CSF, and vice versa [9, 10, 17]. The double-conversion heterodyne receiver has an advantage here. The  $f_{IF_1}$  can be high leading to relaxed demands on

(a) Architecture of the double-conversion heterodyne receiver

(b) Down-conversion in the frequency domain

**Figure 4:** (a) The architecture of the double-conversion heterodyne receiver. (b) Down-conversion in the frequency domain

Figure 5: The image frequency problem

the IRF. At the same time the second IF can be low, and also the demands on CSF can be relaxed. It should also be noted, however, that one additional filter is needed in the double-conversion receiver.

#### **Image Rejection Receiver**

As described in the previous section, the image frequency is a problem in the heterodyne architectures. To deal with this issue, a frequency down-conversion mixer structure which suppresses the image signal can be used. There are two main image reject topologies, the Weaver<sup>3</sup> and the Hartley<sup>4</sup>, see Fig 6. Another possibility is to keep the I and Q paths separate in the analog part and perform the image rejection in the digital baseband, but this will not be further treated in this thesis. In the image rejection architectures it is very important that the phase and amplitude errors are minimized, since errors result in a reduced image rejection ratio (*IRR*) [20]. An equation (1) for *IRR* is derived in [10]:

<sup>&</sup>lt;sup>3</sup>The Weaver topology was first published in 1956 [18], the title of the paper were "A Third Method of Generation and Detection of Single-sideband Signals".

<sup>&</sup>lt;sup>4</sup>Ralph Hartley filed a patent for his idea in April 1928 [19], he then called it a "Single-sideband Modulator".

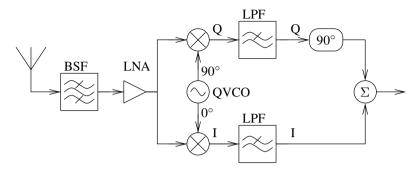

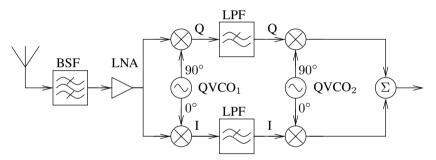

(a) The Hartley image reject architecture

(b) The Weaver image reject architecture

**Figure 6:** The two most common image reject receivers, (a) Hartley and (b) Weaver

$$IRR = \frac{P_{RF}}{P_{image}} = \frac{1 + 2(1+\epsilon)\cos\theta + (1+\epsilon)^2}{1 - 2(1+\epsilon)\cos\theta + (1+\epsilon)^2} \approx \left. \frac{4}{\epsilon^2 + \theta^2} \right|_{\epsilon \text{ and } \theta \text{ small}} \tag{1}$$

where  $\epsilon$  is the relative amplitude error and  $\theta$  is the phase error (in radians).

To get a 26 dB IRR, the structures require a maximum of 5% amplitude mismatch between the two branches and 5° phase error, and to get a more desirable IRR of, say 60 dB, 0.1% and 0.1° would be needed, requiring calibration circuitry. In the literature [21,22] two different CMOS circuits operating at 2.4 GHz are reported with an IRR of 45 dB and 30 dB, respectively. In [23, 24] calibration circuits are used in a Weaver architecture, and IRR of 57 and 59 dB are reported at 2 GHz and 1.8 GHz, respectively.

In the image reject architectures, the RF signal first passes a BSF and an LNA, as in a heterodyne architecture. The signal is then downconverted in two mixers with a quadrature LO signal, followed by a low pass filters (LPF). In the Hartley architecture a 90 degree phase shift is introduced in one of the signal paths, usually implemented as a +45 degrees in one path and a -45 degrees in the other. The two paths are then summed together and the downconverted image signals in the two branches ideally cancel each other, while the desired signals add in phase. In the Weaver architecture, the 90° phase shift is performed using a second set of mixers also fed with quadrature LO signals.

To examine how the image cancellation occurs, a brief walk-through in the Hartley case will follow. For a more detailed description see [10]. Assume that the RF and image signals are sinusoids and that  $f_{RF} > f_{LO}$ . In the upper path in Fig. 6(a), the RF and image signal are multiplied with another sinusoid. After the LPF, there are two cosines left with frequency  $f_{RF} - f_{LO} = f_{IF}^{RF}$  and  $f_{image} - f_{LO} = -f_{IF}^{image}$  since cosine is an even function, negative and positive arguments give equal results (2a). These cosine signals are phase shifted 90 degrees, which means that the cosine is replaced by a sine (2b),

$$\cos\left(f_{IF}^{RF}\right) + \cos\left(-f_{IF}^{image}\right) = \cos\left(f_{IF}^{RF}\right) + \cos\left(f_{IF}^{image}\right) \tag{2a}$$

(2a) + 90° phase shift

$$\longrightarrow \sin\left(f_{IF}^{RF}\right) + \sin\left(f_{IF}^{image}\right)$$

. (2b)

In the lower path, the input RF and image signals are multiplied by a cosine and after the LPF two sinusoids are left (3),

$$\sin\left(f_{IF}^{RF}\right) + \sin\left(-f_{IF}^{image}\right) = \sin\left(f_{IF}^{RF}\right) - \sin\left(f_{IF}^{image}\right).$$

(3)

After the summation of the right hand side of (2b) and (3) it is now clear that only the RF signal contributes to the output.

#### **Direct Conversion Receiver**

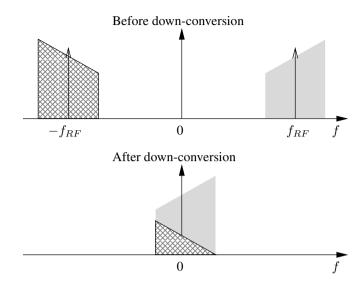

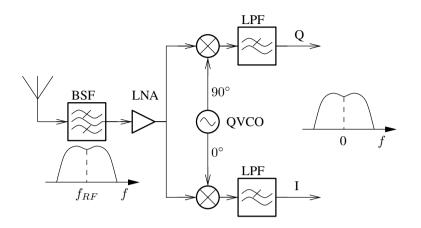

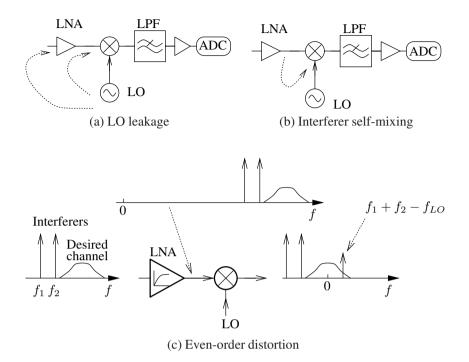

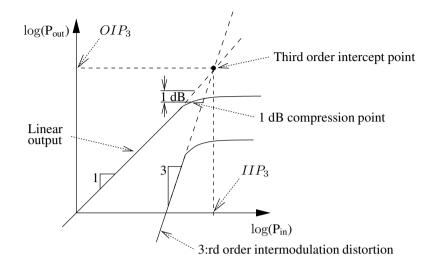

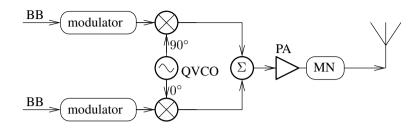

The direct conversion receiver is also called the homodyne<sup>5</sup> receiver or zero-IF receiver. The idea of the homodyne receiver is to downconvert the RF signal directly to baseband. This is accomplished by mixing the RF signal with an LO signal of the same frequency as the RF carrier,  $f_{RF}$ . The center of the band is then translated to a zero IF (4), see Fig. 7. The mixer is followed by a LPF that performs the channel select filtering.

$$\omega_{IF} = \omega_{LO} - \omega_{RF} = 0 \tag{4}$$

The requirements on the adjacent channel interference sets the minimum sharpness and thus the order of the low pass filter [10]. With the rather low corner frequency of the filter, it can typically be integrated as an active filter [27]. The main advantage of the direct conversion receiver is its simplicity, see Fig. 8, giving the architecture good ability for integration and a potentially low power consumption.

<sup>&</sup>lt;sup>5</sup>The homodyne receiver dates back to 1924 when it first was published by Colebrook [25, 26].

Figure 7: Spectrum before and after down-conversion with a direct conversion receiver

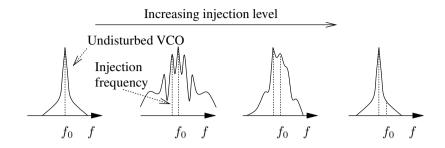

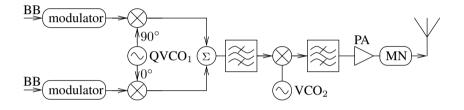

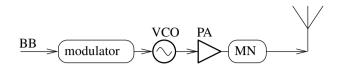

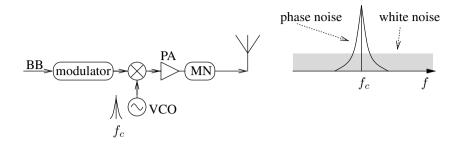

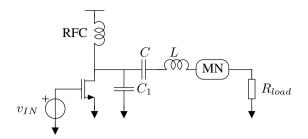

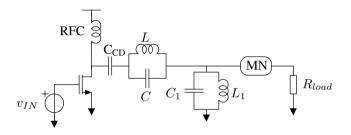

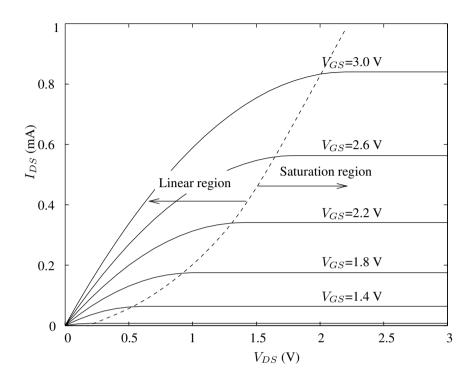

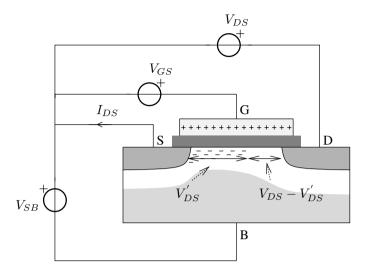

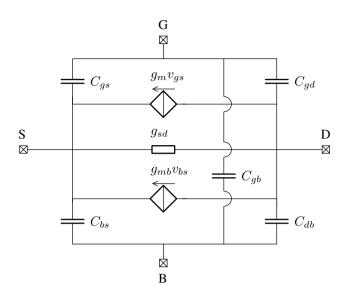

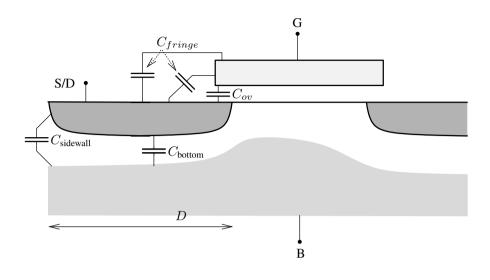

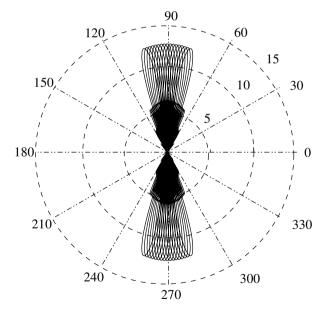

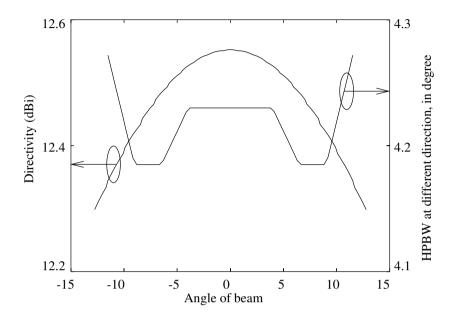

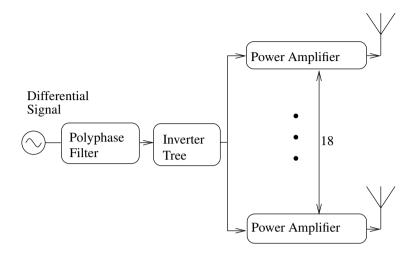

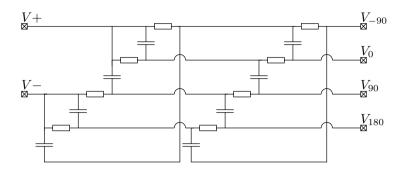

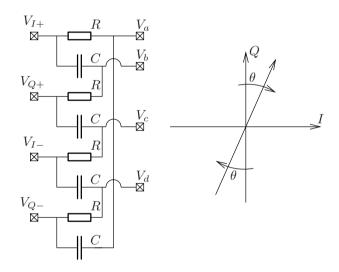

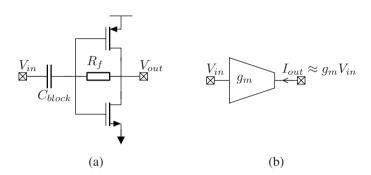

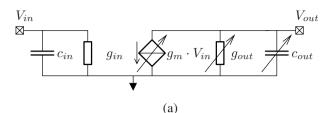

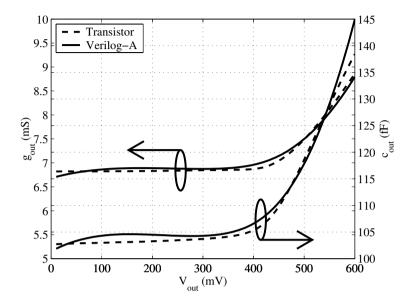

To be able to recover the phase information of the signal, complex mixing has to be applied, which makes it similar to the image reject architectures see Fig. 6 and 8. A difficulty with the heterodyne receiver and other architectures with a non zero-IF is the image frequency. With a zero-IF architecture the signal is its own image, thus avoiding the problem of image signals being stronger than the signal to receive, see Fig. 7.