## Al2O3/InAs metal-oxide-semiconductor capacitors on (100) and (111)B substrates

Wu, Jun; Lind, Erik; Timm, Rainer; Hjort, Martin; Mikkelsen, Anders; Wernersson, Lars-Erik

Published in: **Applied Physics Letters**

DOI:

10.1063/1.3698094

2012

#### Link to publication

Citation for published version (APA):

Wu, J., Lind, E., Timm, R., Hjort, M., Mikkelsen, A., & Wernersson, L.-E. (2012). Al2O3/InAs metal-oxidesemiconductor capacitors on (100) and (111)B substrates. Applied Physics Letters, 100(13), 132905-132905-3. https://doi.org/10.1063/1.3698094

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

PO Box 117 221 00 Lund +46 46-222 00 00

Download date: 18. May. 2025

# Al2O3/InAs metal-oxide-semiconductor capacitors on (100) and (111)B substrates

Jun Wu, E. Lind, R. Timm, Martin Hjort, A. Mikkelsen et al.

Citation: Appl. Phys. Lett. 100, 132905 (2012); doi: 10.1063/1.3698094

View online: http://dx.doi.org/10.1063/1.3698094

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v100/i13

Published by the American Institute of Physics.

#### **Related Articles**

Anomalous positive flatband voltage shifts in metal gate stacks containing rare-earth oxide capping layers Appl. Phys. Lett. 100, 102111 (2012)

Nanostructured all-solid-state supercapacitor based on Li2S-P2S5 glass-ceramic electrolyte Appl. Phys. Lett. 100, 103902 (2012)

Comparison of electrical and electro-optical characteristics of light-emitting capacitors based on silicon-rich Sioxide fabricated by plasma-enhanced chemical vapor deposition and ion implantation J. Appl. Phys. 111, 053109 (2012)

Improved AC conductance and Gray-Brown methods to characterize fast and slow traps in Ge metal—oxide—semiconductor capacitors

J. Appl. Phys. 111, 054102 (2012)

Effect of annealing ambient and temperature on the electrical characteristics of atomic layer deposition Al2O3/In0.53Ga0.47As metal-oxide-semiconductor capacitors and MOSFETs J. Appl. Phys. 111, 044105 (2012)

### Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

### **ADVERTISEMENT**

## Al<sub>2</sub>O<sub>3</sub>/InAs metal-oxide-semiconductor capacitors on (100) and (111)B substrates

Jun Wu, <sup>1,a)</sup> E. Lind, <sup>1,b)</sup> R. Timm, <sup>2,c)</sup> Martin Hjort, <sup>2</sup> A. Mikkelsen, <sup>2</sup> and L.-E. Wernersson <sup>1</sup> Electrical and Information Technology, Lund University, P.O. Box 118, 22 100 Lund, Sweden <sup>2</sup> Department of Physics, Lund University, P.O. Box 118, 22 100 Lund, Sweden

(Received 14 February 2012; accepted 3 March 2012; published online 28 March 2012)

The influence of InAs orientations and high-k oxide deposition conditions on the electrical and structural quality of Au/W/Al<sub>2</sub>O<sub>3</sub>/InAs metal-oxide-semiconductor capacitors was investigated using capacitance-voltage (C-V) and x-ray photoemission spectroscopy techniques. The results suggest that the interface traps around the conduction band edge are correlated to the As-oxide amount, while less to those of As-As bonds and In-oxides. The quality of the deposited Al oxide determines the border trap density, hence the capacitance frequency dispersion. The comparison of different processing conditions is discussed, favoring a 350 °C high-k oxide deposition on (111)B substrates followed by an annealing procedure at 400 °C. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.3698094]

III-V semiconductors with high-k dielectrics are attracting increasing interest for high-speed and low power electronics. Besides the well studied GaAs, a growing attention has in recent years been paid to the other materials of the III-V family such as the binary InAs which exhibits superior transport properties. The quality of the oxide layer and the semiconductor oxide interface is of crucial importance for the device performance<sup>2</sup> targeting good subthreshold characteristics, high transconductances, and the large drive-current. The presence of the native oxides is believed to generally degrade the electrical properties of the gate dielectrics.3-7 Although much effort in recent years has been made to study the electrical properties<sup>2,7</sup> and the amount of different native oxides<sup>8,9</sup> using C-V and x-ray photoemission spectroscopy (XPS) measurements, further studies related to the influence of the InAs orientation and high-k deposition conditions on the metal-oxide-semiconductor (MOS) performance are required. In particular, studies on (111)B-oriented substrates are important as it has been identified that the In-oxides are less effectively reduced, which makes As-terminated surfaces attractive. Furthermore, they serve as an important reference for zincblende InAs nanowires 10,11 grown by the vapor-liquid-solid (VLS) method, where (111) microfacets are found to dominate the surface.

In this work, we combine electrical measurements with XPS characterization to study metal/ $Al_2O_3$ /InAs MOS capacitors with different InAs orientations and oxide deposition temperatures. The results indicate that the interface traps around the conduction band edge are correlated to the amount of  $AsO_x$ , and generally a lower amount of interfacial oxides leads to a lower interface trap density  $D_{ii}$ . The effectiveness of the In-oxide reduction at various temperatures is also found to depend on the surface termination, but only very weakly on the deposition temperature. Meanwhile, an additional annealing at  $400\,^{\circ}\text{C}$  in the forming gas is found to

suppress the amount of interface traps. The results also show that the border traps <sup>12,13</sup> mainly reside inside the Al oxide and can be reduced by using lower deposition temperatures and higher annealing temperatures.

MOS capacitors were fabricated on InAs substrates with two different orientations (100) and (111)B with comparable n-type doping densities of  $3.5 \times 10^{16}$ /cm<sup>3</sup> and  $7.5 \times 10^{16}$ /cm<sup>3</sup>, respectively. The InAs substrates were pre-treated with HCl:H<sub>2</sub>O (1:1) for 60 s and rinsed in isopropanol for 15 s. 80 cycles of Al<sub>2</sub>O<sub>3</sub> (24 cycles for XPS measurements) were grown using trimethylaluminum and water as precursors at deposition temperatures of 200 °C, 250 °C, and 350 °C in a Cambridge Nanotech Savannah-100 ALD chamber starting with a Al-pulse. W/Au contacts were fabricated by sputtering combined with optical lithography and followed by dry/wet etching of the metals. The electrical properties were measured at room and liquid nitrogen temperatures using a Keithley 4200 parameter analyzer and a 4294 A impedance analyzer. The interface properties of reference samples with 24 cycles of Al<sub>2</sub>O<sub>3</sub> were measured using XPS at beam-line I311 of the MAX-II synchrotron.<sup>9</sup>

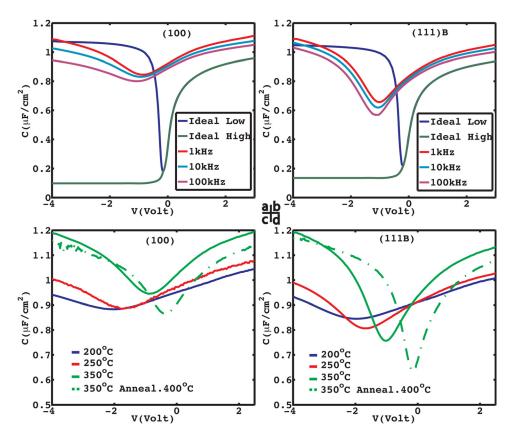

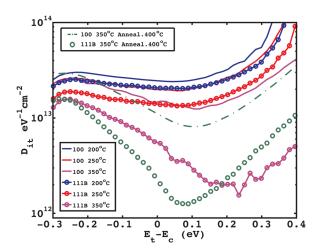

Figures 1(a) and 1(b) show the measured, room temperature, multi-frequency C-V curves of the (111)B and (100) deposited at T = 350 °C. A stronger C-V modulation for the (111)B sample is clearly visible, indicating a lower amount of interface traps. Figures 1(c) and 1(d) show the 1 kHz curves of the (100) and (111)B samples with different deposition conditions. For both cases, a stronger C-V modulation is observed for increasing the deposition temperature. To quantify these trends, the  $D_{it}$  levels were extracted using a low frequency fitting method<sup>14</sup> from the 1 kHz data at room temperature and conductance measurements at T = 77 K. The extracted values are shown in Figure 2. For trap levels around the conduction band edge, the Dit levels are seen to decrease with increasing the deposition temperature, with a stronger reduction for the (111)B sample, especially for the T = 350 °C sample. The lowest  $D_{it}$  value is around  $2 \times 10^{12}$ cm<sup>-2</sup>eV<sup>-1</sup> at E<sub>t</sub> - E<sub>c</sub> = 0.2 eV. Close to the valence band edge  $(-0.3 \,\mathrm{eV})$ , the  $D_{it}$  levels remain fairly high, around

a)Electronic mail: Jun.Wu@eit.lth.se.

b) Electronic mail: Erik.Lind@eit.lth.se.

c) Electronic mail: Rainer.timm@sljus.lu.se.

FIG. 1. Comparison of measured and simulated device C-V characteristics of (a) (100) and (b) (111)B samples with the deposition temperature being 350 °C. The effective oxide thickness used in the simulation is 6.45 nm for (100) and 6.62 nm for (111)B, respectively. [(c)–(d)] Comparison of the deposition temperature and annealing influence on the 1 kHz C-V characteristics of (100) and (111)B samples.

$2-3\times10^{13}$  independent of deposition temperatures.  $D_{it}$ -levels extracted by the Terman method 15 and conductance method 16 at  $T=77\,\mathrm{K}$  show similar results. The  $G_p/\omega$  measurement yields a magnitude lower  $D_{it}$  (at  $E_t$  -  $E_c=30\,\mathrm{meV}$ ), around  $1-1.5\times10^{12}~\mathrm{cm}^{-2}~\mathrm{eV}^{-1}$  for the (100) samples, and  $0.5-1\times10^{12}~\mathrm{cm}^{-2}~\mathrm{eV}^{-1}$  for the (111)B samples. This large discrepancy between the results obtained from two electrical methods can in part be explained by the omission of potential fluctuations 16 in the conductance method used, and that the defect densities extracted from the C-V curves are a mixture of interface and border traps.

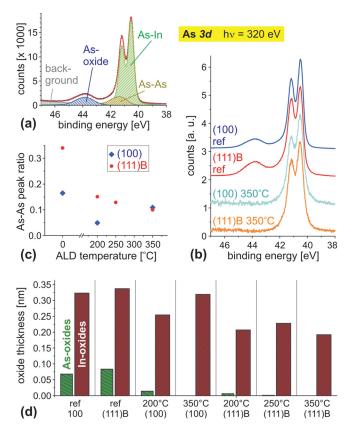

In order to reveal the cause for the different  $D_{it}$  values, we used XPS to characterize the interface. Figure 3(a) shows

FIG. 2.  $D_{it}$  vs.  $E_t$  -  $E_c$  extracted using the low frequency fitting method (see Ref. 14) as a function of InAs orientation and oxide deposition temperature. The x-axis denotes the position of the trap level  $E_t$  in the band gap with respected to the conduction band edge  $E_c$ .

different components of the fitted As 3d spectra (In 3d spectra not shown), from which the native oxide thickness is extracted (d). The In-oxide is found to dominate the native oxide layer in agreement with a previous study, which may explain the preference for the As-terminated (111)B-surface for the MOS capacitors. The amount of In-oxides after ALD deposition is essentially independent of the ALD temperature, but lower for the (111)B sample. The As-oxides decrease with increasing the temperature for both (100) and (111)B, to levels below the detection limit ( $\sim 2 \times 10^{13}$ cm<sup>-2</sup>) at T = 350 °C. Interestingly, the amount of As-oxides after ALD depositing is lower for the As-rich (111)B surface, as compared with (100) substrates. There are also substantial amount of As-As bonds (>10<sup>13</sup> cm<sup>-2</sup>), with a slightly lower level for (100) at T = 200 °C and with similar levels for both (100) and (111)B at T = 350 °C, a trend that is inconsistent with the C-V data. The high and constant  $D_{it}$  at the valence band edge could be related to In-oxides or to As-As bonds or As dangling bonds as suggested in Refs. 5 and 6, since the amount of As-As as well as InO<sub>x</sub> seems to be fairly independent of the temperature. Our data thus seem to indicate that the  $D_{it}$  around  $E_c$  is mainly correlated to the amount of  $AsO_x$  that is decreasing for both orientations and with lower values for (111)B. Unlike GaAs MOS systems<sup>3,4</sup> where Gadangling bond and As-As dimer induced states are generally present near the conduction band edge and the midgap, the narrower InAs band gap may move those states far into the conduction band. 5,6 The rise of  $D_{it}$  after 0.2 eV hence could be correlated with those defect amounts. Besides, Ga<sub>2</sub>O<sub>3</sub> induced states are also found near the valence band edge for GaAs, which is similar to the InAs case.

From the XPS data, we also looked for energy shifts between the (100) and (111)B samples to quantify the

FIG. 3. XPS results from (a-c) the As 3d core-level with a photon energy of 320 eV. (a) Fitted spectrum with different components as indicated. (b) Comparison of spectra from reference samples with a native oxide layer and samples with  $Al_2O_3$  deposited at 350 °C, for (100) and (111)B. The spectra are background-subtracted and normalized for the better clarity. (c) Relative intensity of the spectral component related to As-As bonds, as compared to the bulk InAs component, for different ALD temperatures. The value at 0 °C refers to the corresponding reference sample. From the measured XPS intensities of the oxide components in As 3 d and corresponding In 3 d spectra, the absolute thickness and the stoichiometry of the oxide film can be calculated (see Ref. 8). This is shown in (d) for the native surface oxide of reference samples and the interface oxide between InAs samples and  $Al_2O_3$  films with different ALD temperatures.

flat-band shift. For deposition at low temperatures, the shift is found to be negligible, but as the temperature increases, the magnitude of the shift increases and a value of 90 meV is measured for the 350 °C deposition. This compares well with the data obtained from the low-f  $D_{it}$  fitting, where the (111)B sample has a  $\sim$ 70 meV larger surface potential as compared with the (100), for the  $T=350\,^{\circ}\text{C}$  case.

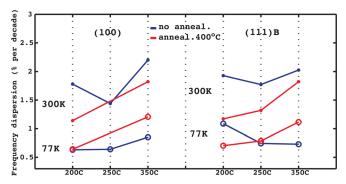

The amount of border traps is studied by measuring the frequency dispersion of the accumulation capacitance as shown in Figure 4. No clear orientation dependence is found, which is consistent with the expectation that the border traps are located mainly inside the Al<sub>2</sub>O<sub>3</sub> film. The measured dispersion for both orientations generally increases with the deposition temperature, differing from the trends of both the As- and In-oxides shown in Figure 3. This supports the assumption that the effect is caused by defects deeper in the oxide rather than at the interface. In addition, the frequency dispersion is found to be suppressed by decreasing the measurement temperature, <sup>13</sup> possibly due to a reduction in the thermally assisted tunneling to higher lying trap states. <sup>12</sup>

FIG. 4. Accumulation capacitance frequency dispersion at  $(V_{fb}+2.3)$  Volt as a function of different deposition conditions. The frequencies chosen range from 1 kHz to 100 kHz.

In conclusion, we have studied the influence of the InAs orientation and high-k oxide deposition conditions on the MOS electrical performance. We find that the (111)B samples generally show lower  $D_{it}$  than the (100) samples and that the interface defect properties are improved upon annealing at 400 °C. The XPS studies further indicate a reduction of  $AsO_x$  with increasing the ALD deposition temperature, whereas  $InO_x$  and As-As are relatively unaffected. In addition, the quality of the Al oxide layer dominates the border trap amount.

This work was supported by Swedish Research Council (VR), the Swedish Foundation for Strategic Research (SSF), the Crafoord Foundation, the Knut and Alice Wallenberg Foundation.

<sup>1</sup>Silicon (Si), Electro Mobility; Gallium Arsenide (GaAs), Electron Mobility; Indium Arsenide (InAs), Carrier Mobilities, Landolt-Brnstein, New Series, Group III, edited by O. Madelung, U. Rssler, and M. Schulz (Springer, New York, 2002).

<sup>2</sup>N. Li, Eric S. Harmon, J. Hyland, D. B. Salzman, T. P. Ma, Y. Xuan, and P. D. Ye, Appl. Phys. Lett. **92**, 143507 (2008).

<sup>3</sup>C. L. Hinkle, M. Milojevic, B. Brennan, A. M. Sonnet, F. S. Aguirre-Tostado, G. J. Hughes, E. M. Vogel, and R. M. Wallace, Appl. Phys. Lett. **94**, 162101 (2009).

<sup>4</sup>W. Wang, C. L. Hinkle, E. M. Vogel, K. Cho, and R. M. Wallace, Microelectron. Eng. 88, 1061 (2011).

<sup>5</sup>J. Robertson, Microelectron. Eng. **86**, 1558–1560 (2009).

<sup>6</sup>E. A. Chagarov, and A. C. Kummel, J. Chem. Phys. **135**, 244705 (2011).

<sup>7</sup>D. Wheeler, L.-E. Wernersson, L. Frberg, C. Thelander, A. Mikkelsen, K.-J. Weststrate, A. Sonnet, E. M. Vogel, and A. Seabaugh, Microelectron. Eng. 86, 1561 (2009).

<sup>8</sup>R. Timm, A. Fian, M. Hjort, C. Thelander, E. Lind, J. N. Andersen, L.-E. Wernersson, and A. Mikkelsen, Appl. Phys. Lett. **97**, 132904 (2010).

<sup>9</sup>R. Timm, M. Hjort, A. Fian, C. Thelander, E. Lind, J. N. Andersen, L.-E. Wernersson, and A. Mikkelsen, Microelectron. Eng. 88, 1091 (2011).

<sup>10</sup>P. Caroff, K. A. Dick, J. Johansson, M. E. Messing, K. Deppert, and L. Samuelson, Nature Nanotechnol. 4, 50 (2009).

<sup>11</sup>R. Timm, M. Hjort, A. Fian, B. M. Borg, C. Thelander, J. N. Andersen, L.-E. Wernersson, and A. Mikkelsen, Appl. Phys. Lett. 99, 222907 (2011).

<sup>12</sup>F. P. Heiman and G. Warfield, IEEE Trans. Electron Devices, 12(4), 167–178 (1965).

<sup>13</sup>E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, Appl. Phys. Lett. **96**, 012906 (2010).

<sup>14</sup>G. Brammertz, H.-C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, Appl. Phys. Lett. 95, 202109 (2009).

<sup>15</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, Appl. Phys. Lett. 97, 062905 (2010).

<sup>16</sup>E. H. Nicollian, A. Goetzberger, and A. D. Lopez, Microelectron. Eng. 88, 937 (1969)