#### **Energy-Centric Scheduling for Real-Time Systems**

Gruian, Flavius

#### Link to publication

2002

Citation for published version (APA): Gruian, F. (2002). Energy-Centric Scheduling for Real-Time Systems. [Doctoral Thesis (monograph), Department of Computer Science]. Department of Computer Science, Lund University.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 21. Dec. 2025

# Energy-Centric Scheduling for Real-Time Systems

Flavius Gruian

Doctoral dissertation, 2002

Department of Computer Science Lund Institute of Technology Lund University This thesis is submitted to the Board of Research: FIME — Physics, Informatics, Mathematics and Electrical Engineering — at Lund Institute of Technology (LTH), Lund University, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering.

Document built with: Large  $2\varepsilon$ , gnuplot 3.7.2, FreeHand 10, Xfig 3.2 patchlevel 2, and MS Excel.

Version: November 16, 2002

ISBN 91-628-5494-1 ISSN 1404-1219 Dissertation 15, 2002 LU-CS-DISS:2002-2

Department of Computer Science Lund Institute of Technology Lund University Box 118 SE-221 00 Lund Sweden

Email: Flavius.Gruian@cs.lth.se

WWW: http://www.cs.lth.se/home/Flavius\_Gruian

© 2002 Flavius Gruian

## ABSTRACT

ENERGY CONSUMPTION is today an important design issue for all kinds of digital systems, and essential for the battery operated ones. An important fraction of this energy is dissipated on the processors running the application software. To reduce this energy consumption, one may, for instance, lower the processor clock frequency and supply voltage. This, however, might lead to a performance degradation of the whole system. In real-time systems, the crucial issue is timing, which is directly dependent on the system speed. Real-time scheduling and energy efficiency are therefore tightly connected issues, being addressed together in this work.

Several scheduling approaches for low energy are described in the thesis, most targeting variable speed processor architectures. At task level, a novel speed scheduling algorithm for tasks with probabilistic execution pattern is introduced and compared to an already existing compile-time approach. For task graphs, a list-scheduling based algorithm with an energy-sensitive priority is proposed. For task sets, off-line methods for computing the task maximum required speeds are described, both for rate-monotonic and earliest deadline first scheduling. Also, a run-time speed optimization policy based on slack re-distribution is proposed for rate-monotonic scheduling. Next, an energy-efficient extension of the earliest deadline first priority assignment policy is proposed, aimed at tasks with probabilistic execution time. Finally, scheduling is examined in conjunction with assignment of tasks to processors, as parts of various low energy design flows. For some of the algorithms given in the thesis, energy measurements were carried out on a real hardware platform containing a variable speed processor. The results confirm the validity of the initial assumptions and models used throughout the thesis. These experiments also show the efficiency of the newly introduced scheduling methods.

# ACKNOWLEDGMENTS

Foremost, I would like to thank my supervisor, Krzysztof Kuchcinski, for his permanent support and guidance, and for his steady confidence in my work. Special thanks to my co-supervisor, Petru Eles, whose method and attitude towards research often served as a model for myself, ever since the time of my undergraduate studies. I am also very grateful to my other co-supervisor, Per Larsson-Edefors, for his invaluable help in the early stages of this thesis.

During my years as a PhD-student, I had the privilege of working in two successful departments, that both provided a pleasant and friendly environment. Many thanks to all the people in the Department of Computer and Information Science at Linköping University, where I started on the graduate studies path. My best regards also to the people in the Department of Computer Science at Lund University, where I finally completed this thesis. The present ESDLAB members and former CADLAB colleagues, and now friends, have played an important role throughout my studies.

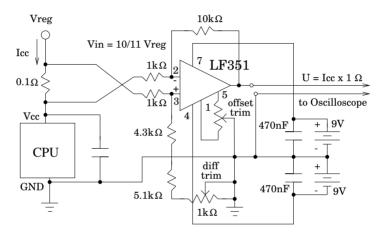

On the more practical side, many thanks to Intel, especially to Bill E. Brown and Atila Alvandpour, for providing not only the hardware platform for the experiments, but also prompt feedback and helpful suggestions. Also, I very much appreciate the help given by Martin Nilsson with the experimental setup and measurements. Many thanks to all the engineers in the technical group, for providing a trustworthy and efficiently working system. My appreciation to the administrative staff, for their excellent handling of all kinds of practical problems.

I would also like to mention that this work was supported initially by WITAS — The Wallenberg laboratory for research on Information Technology and Autonomous Systems — and subsequently by ARTES – A network for Real-Time research and graduate Education in Sweden.

I owe a lot to my friends from all over the world, who were of more help than they know it. My friends back home believed in me and supported me from the beginning; without them I would have never started this journey. The friends I made while in Linköping were of great help during my stay there, and continue to bring joy into my life. Special thanks to Paul, who took the time to read this thesis and to provide insightful feedback. My newest friends from Lund do a good job in reminding me that there are other things in life than writing theses. Thank you all. Finally, to someone very special: this might have nothing to do with the curtains, but thank you for every single moment we spent together...

None of this would have happened without the full support of my family. My deepest gratitude and love to my parents, Mili and Liviu, who always wanted the best for me.

Flavius Gruian Lund, November 16, 2002

# CONTENTS

| I | Intr | roduction                                   |

|---|------|---------------------------------------------|

|   | 1.1  | Motivation                                  |

|   | 1.2  | Thesis Objectives                           |

|   | 1.3  | Contributions                               |

|   | 1.4  | Thesis Layout                               |

| 2 | Bac  | kground 5                                   |

|   | 2.1  | Power, Energy, and Delay                    |

|   |      | 2.1.1 Power Consumption in CMOS Circuits    |

|   |      | 2.1.2 Energy Consumption in CMOS Circuits 9 |

|   | 2.2  | Real-Time Systems                           |

|   | 2.3  | System Synthesis                            |

|   | 2.4  | Related Research                            |

|   |      | 2.4.1 Task Level Scheduling                 |

|   |      | 2.4.2 Task Group Level Scheduling           |

|   |      | 2.4.3 System-Level Synthesis                |

| 3 | Mod  | lels 21                                     |

|   | 3.1  | Task Model                                  |

|   |      | 3.1.1 Task attributes                       |

|   | 3.2  |                                             |

|   |      | 3.2.1 Task Graphs                           |

|   |      | 3.2.2 Enhanced Task Graphs                  |

|   |      |                                             |

|   |     | 3.2.3  | Task Sets                                     | 26           |

|---|-----|--------|-----------------------------------------------|--------------|

|   | 3.3 | Proce  | ssor Models                                   | 27           |

|   |     | 3.3.1  | Fixed Speed Processors                        | 28           |

|   |     | 3.3.2  |                                               | 29           |

|   | 3.4 | Comn   |                                               | 37           |

| 4 | Tas | k Leve | el Scheduling 3                               | 9            |

|   | 4.1 | Slowe  | r Execution vs. Shutdown                      | 10           |

|   | 4.2 | Uniqu  | ue Execution Pattern                          | 2            |

|   | 4.3 | Proba  | bilistic Execution Pattern 4                  | 2            |

|   |     | 4.3.1  | Stochastic Scheduling                         | 4            |

|   |     | 4.3.2  | Compiler-Assisted Speed Scheduling 4          | 18           |

|   | 4.4 | Discu  |                                               | 60           |

|   |     | 4.4.1  |                                               | 60           |

|   |     | 4.4.2  | WCE Stretch vs. Stochastic 5                  | 1            |

|   |     | 4.4.3  | Stochastic vs. Compiler-Assisted Scheduling 5 | 64           |

| 5 | Tas | k Grou | up Scheduling 6                               | 1            |

|   | 5.1 |        |                                               | 32           |

|   | 5.2 |        |                                               | 64           |

|   | 5.3 | List-S | Scheduling with Proportional Stretch 6        | 37           |

|   | 5.4 | The L  | EneS Algorithm                                | 0            |

|   |     | 5.4.1  | Scheduling an Enhanced Task Graph             | 0            |

|   |     | 5.4.2  |                                               | 1            |

|   |     | 5.4.3  | The Priority Function                         | $^{\prime}2$ |

|   |     | 5.4.4  | LEneS Algorithm Pseudo-code                   | 4            |

|   |     | 5.4.5  | LEneS Evaluation                              | 7            |

|   |     | 5.4.6  | Conclusions                                   | 31           |

|   | 5.5 | Maxir  | num Required Speed Approach                   | 31           |

|   |     | 5.5.1  | 0                                             | 31           |

|   |     | 5.5.2  | MRS for RM scheduling                         | 86           |

|   | 5.6 | RM S   |                                               | 39           |

|   |     | 5.6.1  | 80                                            | 0            |

|   |     | 5.6.2  | 1                                             | 1            |

|   |     | 5.6.3  | 1                                             | 92           |

|   |     | 5.6.4  |                                               | 96           |

|   | 5.7 |        | · e                                           | 8            |

|   |     | 5.7.1  | 1                                             | 8            |

|   |     | 5.7.2  | Extending UBS for EDF                         | )7           |

|   |     | 5.7.3  | Conclusions                                   | 12           |

| 6  | Arc  | hitecture Selection and Scheduling             | 113 |

|----|------|------------------------------------------------|-----|

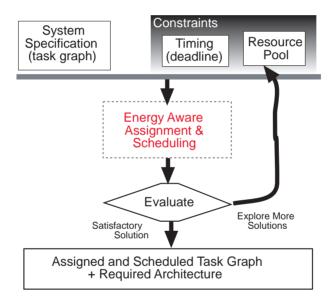

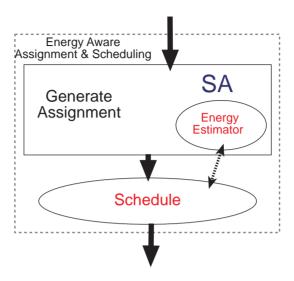

|    | 6.1  | An Overview of Our Design Flow                 | 113 |

|    | 6.2  | Fixed Speed Processor Architectures            | 115 |

|    |      | 6.2.1 Modeling the Problem with Constraints    | 115 |

|    |      | 6.2.2 Searching for Solutions                  | 119 |

|    |      | 6.2.3 Experiments                              | 121 |

|    | 6.3  | Variable Speed Processor Architectures         | 126 |

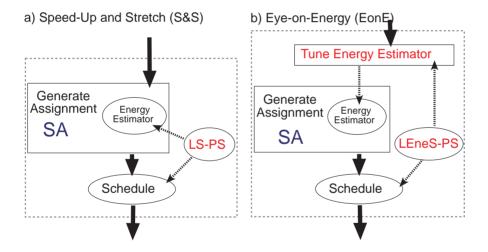

|    |      | 6.3.1 The "Speed-Up and Stretch" Approach      | 127 |

|    |      | 6.3.2 The "Eye-on-Energy" Approach             | 128 |

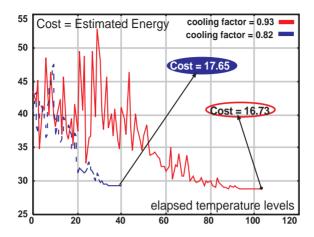

|    |      | 6.3.3 Simulated Annealing as Assignment Search | 130 |

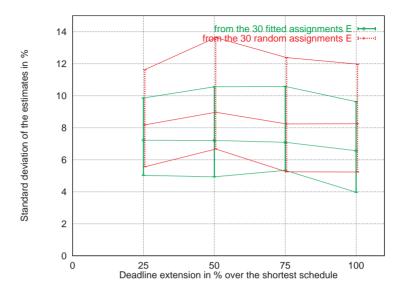

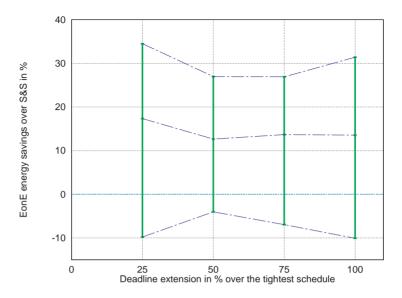

|    |      | 6.3.4 S&S vs. EonE Comparison                  | 131 |

|    | 6.4  |                                                |     |

| 7  | Fin  | al Remarks                                     | 135 |

|    | 7.1  | Summary and Conclusions                        | 135 |

|    | 7.2  | Future Trends                                  | 137 |

|    | 7.3  |                                                |     |

| Bi | blio | graphy                                         | 151 |

| A  | Pro  | ofs                                            | 153 |

|    | A.1  | Stochastic schedule energy lower bound         | 153 |

|    |      | Optimal order for UBS                          |     |

| В  | The  | e Test System                                  | 157 |

|    |      | ADI 80200EVB                                   | 157 |

|    |      | MAXIM MAX1855 EV kit                           |     |

|    |      | Measurements Setup                             |     |

| C  | Δ Т  | ask Laval Stochastic Schedula on 80200EVR      | 161 |

# Introduction

THIS FIRST CHAPTER starts by presenting the motivation behind the research work making the subject of this thesis, and continues with a succinct and general problem formulation. We then point out the contributions of the thesis to the real-time, design automation, and low power/energy areas. Finally, an overview of our work is given, briefly describing the structure of the thesis.

#### 1.1 Motivation

Energy consumption reduction is becoming nowadays an issue reflected in most aspects of our lives. For digital systems, energy efficiency is an acute problem appearing from the high computational demands in all sorts of applications. The obvious driving force behind addressing energy consumption in digital systems is, at the first glance, the development of portable communication and computation. The consumers demand better performance and more functionality from the hand-held devices, but this also means higher power and energy consumption. Battery life is one of the most important parameters for such devices, directly influencing the system size and weight. At the same time, although battery technology is also developing, its progress is rather slow and cannot keep up with the demands of the modern digital systems. At a deeper scrutiny, there are many areas that would benefit from design methods targeting energy efficiency:

Space applications is an area where weight has a great impact on cost, because of the limited load of the carrier rockets and shuttles. Energyefficient design methods yield smaller solar panels and batteries for all kinds of satellites and probes. For example, the electrical power system for the  $2001\,Mars\,Odyssey$  spacecraft accounts for 17% (65kg) of the total mass, planned to operate for 4.6 years. Reducing the energy demands through appropriate methods one could, for instance, add more data acquisition instruments on board. As another example, the energy available in a *Deep Space 2* probe would yield only about two hours talk time on an  $Ericsson\,628$  mobile phone.

- As mentioned before, portable devices, such as PDAs, mobile phones, laptops need to use the battery energy as efficiently as possible. The direct impact of energy-centric design techniques is on system size and/or cost. The indirect impact is the environmental effect of using less batteries (toxic waste) for the same functionality.

- Medical implants within the human body also require energy-efficient designs. Pacemakers and different kinds of regulators would ideally consume only the energy provided by the muscles. There exist already prototypes of simple artificial retinas functioning only based on the energy provided by the incident light.

- Lower energy consumption also means lower average power consumption. Consequently, lower power consumption means less dissipated heat. Finally, heat dissipation directly influences the packaging and cooling solutions for integrated circuits. Energy efficiency brings thus a bonus for all types of digital systems, in terms of lower cost packages and cooling.

With all these applications, there is little doubt that energy efficiency is an important optimization goal in digital system design. Furthermore, note that most of these are in fact time critical systems. This is why the current thesis addresses energy efficiency in the context of real-time systems.

## 1.2 Thesis Objectives

Timeliness and energy efficiency are often seen as conflicting goals. When designing a real-time system, the first concern is usually time, leaving energy efficiency as a hopeful consequence of empiric decisions. Yet, with the right methods both goals can be achieved. Energy-efficient architectures may be selected while still meeting the timing constraints. Furthermore, with the advent of variable speed processors, scheduling acquired the new dimension of processor speed. Classic real-time scheduling techniques can now be adapted to address both timing and energy through efficient selection of processing speed. The goal of the current thesis is to provide solutions to some of these problems. Briefly, the answer and the *leitmotif* of the thesis lies in trading off speed for energy, whenever timing requirements allow it.

#### 1.3 Contributions

This thesis bridges the gap between the design of real-time and energy-efficient systems by proposing several approaches that address timing and energy consumption in a unified manner. Their energy-efficient solutions, their successful use of stochastic information, and their use of the increasingly popular variable speed processors, makes the described methods unique, to our knowledge. Specifically, the thesis presents:

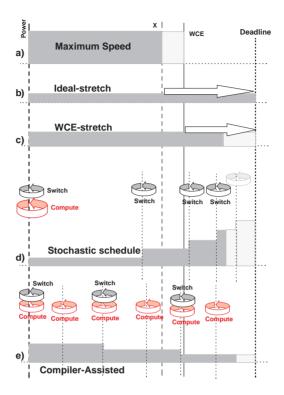

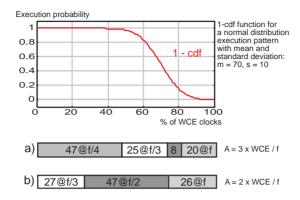

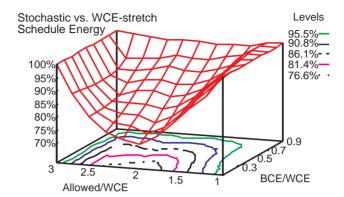

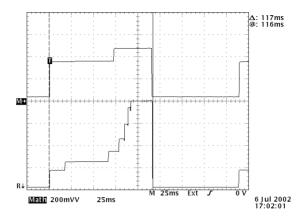

- A new task level scheduling strategy for tasks with probabilistic execution pattern entitled **Stochastic Scheduling**, first introduced in [Gru01a]. The technique is compared to several alternative approaches, including *compiler-assisted scheduling*. Some practical results on a real platform, showing the potential of our method, are also presented (Chapter 4).

- A new task graph static scheduling approach, based on list scheduling with an energy-centric priority function. The algorithm, entitled **LEneS**, was initially introduced in [GK01]. A less successful, but much simpler scheduling technique, **LS-PS**, is also described and compared to LEneS (Sections 5.4 and 5.3).

- Methods for computing **maximum required processing speeds** for task sets scheduled via the classic *Earliest Deadline First* and *Rate-Monotonic* approaches. The simplicity and efficiency of these methods, partially mentioned in [Gru01b, Gru01a], make them the basic real-time energy reduction methods on variable speed processors (Section 5.5).

- An extension of the classic *Rate-Monotonic Scheduling* (RMS) for including **run-time slack distribution**. This method, first introduced in [Gru01a], is proven to yield the same timing behavior as the classic RMS, but with significant reduction in energy consumption for sets of tasks with probabilistic execution pattern (Section 5.6).

- A new ordering method for sets of tasks with probabilistic execution times, named **Uncertainty-Based Scheduling**. Initially introduced in [Gru01b], this method uses stochastic information in an aggressive manner to lower the energy consumption without affecting the real-time behavior, as proven by practical results on a real platform (Section 5.7).

- Analysis of several system-level design flows for low energy, directed at task graphs, on both fixed and variable speed processor architectures.

For fixed speed processors we describe a novel approach for unified binding and scheduling, based on constraint programming, as introduced in

[GK99]. For variable speed processor architectures, we describe two approaches, initially introduced in [Gru00b], that are based on the Simulated Annealing heuristic and our own scheduling methods for low energy (Sections 6.2 and 6.3).

## 1.4 Thesis Layout

The thesis consists of four parts. The first, preliminary part, contains the theoretical background necessary for understanding our work (Chapter 2) and the models used throughout the thesis (Chapter 3). The subsequent parts focus on describing our own research.

The second part focuses on task level scheduling for variable speed processor architectures (Chapter 4).

The third part presents a large variety of task group level scheduling techniques (Chapter 5). These techniques address both task graphs and task sets. Both static and run-time methods are described for tasks with fixed or probabilistic execution pattern.

The fourth part addresses scheduling in the context of system-level design flow (Chapter 6). Several design flows for low energy are described, both for fixed and variable speed processor architectures.

Chapter 7 concludes the thesis, by presenting a summary and possible future trends in this research area.

# BACKGROUND

THIS CHAPTER SETS THE FRAME for our work by reviewing first some basic notions from micro-electronics, real-time systems, and design automation for system-level synthesis. In the second part, we present some of the relevant research related to our own, pointing out the significant differences.

## 2.1 Power, Energy, and Delay

In order to design power and energy-efficient systems, one has to understand first the physical phenomena that lead to power dissipation or energy consumption. Since today most digital circuits are implemented using CMOS¹ devices, it is important to examine the relations between power, energy, and signal delay in such devices. Although we focus here on CMOS circuits, the power-energy-delay dependencies could be generalized for any technology. Moreover, the methods and techniques we present in this thesis are at an abstraction level that is rather independent of technology. These conclusions are fundamental for our hardware models used in our work.

#### 2.1.1 Power Consumption in CMOS Circuits

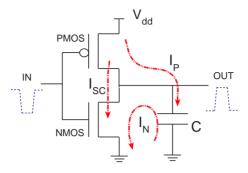

The issues discussed in the current section are valid for any CMOS circuit. For the sake of simplicity, consider the CMOS inverter of Figure 2.1. The power dissipated on this inverter can be decomposed into two basic types, static and dynamic [RP96]:

$$P_{CMOS} = P_{static} + P_{dynamic} (2.1)$$

<sup>&</sup>lt;sup>1</sup>CMOS: Complementary Metal Oxide Semiconductor

Figure 2.1: CMOS inverter

In the ideal case, CMOS circuits do not dissipate static power, since in steady state there is no open path from source to ground. In reality, there are always leakage currents through the MOS transistors, currents depending on the threshold voltage and on the technological process. These currents yield the static component of the CMOS power consumption. Although the static power is today about two orders of magnitude smaller than the total power, according to [Bor99] the typical chip's leakage power increases about 5 times each generation, and will soon become a significant portion of the total power. Fortunately, by reducing the die temperature one can substantially lower the leakage power. In other words, reducing the dynamic power component and employing better cooling techniques will be even more critical in advanced deep-sub-micron technologies.

The dynamic component of the CMOS power is dissipated during the transient behavior, i.e. during switching between logic levels. For the same CMOS inverter depicted above, if the input switches from one logic level to the opposite, at some moment both the NMOS and PMOS transistors will be open, thus allowing a short circuit current  $(I_{SC})$  to appear between source and ground. With a careful design of the transition edges, this dynamic subcomponent can be kept below 10-15% of the total power consumption.

Most of the power is, thus, consumed by charging and discharging the output capacitance. Consider, for the moment, that the input executes one full cycle from high logic-level to low logic-level and then back to high. During a high-to-low transition, an amount of energy equal to  $CV_{dd}^2$  is drained from  $V_{dd}$  through  $I_p$ , part of which is stored in the output capacitance while the rest is dissipated on the PMOS transistor. During the reverse, low-to-high transition, the output capacitance is discharged through  $I_N$ . Thus, during one cycle a total energy equal to  $CV_{dd}^2$  is consumed. Note that the power consumption

directly depends on the switching activity of the signals involved. In this context, let us define the switching activity,  $\alpha$ , as the number of high-to-low transitions during one predefined period. Since we are discussing synchronous circuits, involving a periodic signal (a clock) with frequency f, we can choose the predefined period mentioned earlier, as the clock period. The effective frequency of switches in this case is given by the product:  $\alpha f$ . In CMOS circuits, this component of power dissipation accounts for at least 85-90% of the total power consumption [RP96].

From all the considerations made above, we can approximate the power dissipated on a CMOS circuit node using the following formula:

$$P_{CMOS} \approx P_{dynamic} \sim \alpha f C V_{dd}^2$$

(2.2)

This means that the power consumption in a CMOS circuit is proportional to the switching activity, capacitive load, clock frequency, and the square of the supply voltage. All the power and energy reduction techniques try to minimize one or more of these factors. Unfortunately, they are all coupled in some manner. For example the circuit delay  $\Delta$ , which sets the clock frequency, depends on the supply voltage:

$$\frac{1}{f} \sim \Delta \sim \frac{V_{dd}}{(V_{dd} - V_t)^{\gamma}} \tag{2.3}$$

where  $V_t$  is the threshold voltage and  $\gamma$  is the saturation velocity index. For a sufficiently small  $V_t$  we can rewrite the relation between clock frequency and supply voltage as:

$$f \sim V_{dd}^{(\gamma - 1)} \tag{2.4}$$

Dependencies, although less obvious, exist between the other factors in the power formula. This means that power minimization is an issue that has to be treated carefully, as detailed below.

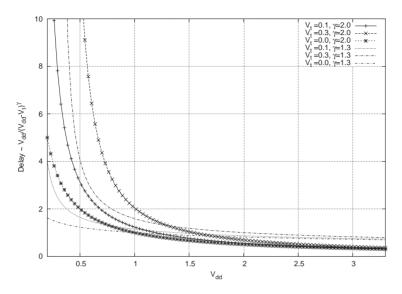

**Supply voltage**  $(V_{dd})$  reduction appears to be the most promising, because of its quadratic dependency to power. A decrease in voltage by a factor of two yields a decrease in power by a factor of four. Unfortunately, the possibility to reduce the supply voltage is limited by several factors, such as design performance and compatibility. When the supply voltage approaches the threshold voltage, the circuit delays become large (Figure 2.2), since the output capacitance is charged and discharged slowly. This sets the lower limit for the supply voltage around  $2 \times V_t$  [RP96]. The degradation in performance could be attenuated by working at lower threshold voltages, but this gives rise to other problems. When the threshold voltage becomes very small, the leakage currents through the MOS transistors increase, leading to an increase of static power consumption. Supply voltage reduction works best when combined with techniques which speed up the design, such as parallelization and

Figure 2.2: The dependency between circuit delay and supply voltage for different threshold voltages  $V_t$  and velocity saturation factors  $\gamma$ .

pipelining. The gain in speed can be converted into a decrease in power and energy, by reducing the supply voltage. Furthermore, reducing the supply voltage is a method that can be used for both dynamic and static CMOS circuits.

Lowering the **clock frequency** (f) has direct influence on the design performance, and it is usually combined with speed-up techniques and supply voltage manipulation. Stopping the clock for some circuit parts can be viewed as "component shut-down" at high levels of abstraction. This approach will only work for static CMOS components, since dynamic components loose information if the clock signal is turned off.

Decreasing the **capacitive load** (C) is yet another way to diminish the power consumption. The physical capacitance in a CMOS circuit consists in fact of two capacitances [RP96]: device and interconnect parasitic capacitance. In the past, the device capacitance has dominated over the interconnect parasitic capacitance but, with the process of technology down-scaling, the interconnect capacitance becomes more and more important, and has to be taken into consideration. Physical capacitance can be kept low by reducing the number of gates, using shorter wires and smaller devices. On the other hand, the reduction of device size reduces the current drive of the transistor, making the circuit to operate slower. This performance loss might prevent  $V_{dd}$  reduction, which is a more efficient technique for power minimization.

The **switching activity** ( $\alpha$ ) is much influenced by the data being processed (except for logic styles with pre-charged nodes [RP96]). From Equation 2.2, if a CMOS circuit does not change its state, it virtually does not consume any power. The signal with the highest activity in a circuit is, by far, the clock. Therefore, several power reduction methods focus on lowering the number of clocked nodes in a CMOS circuit. For certain logic styles, an important source of switching activity is glitching, or unwanted and spurious transitions that occur before a node settles down to its final steady-state value.

The switching activity is directly influenced by the choice of number representation in a design. For example, considering a signal oscillating around zero, using a 2's complement representation imposes the switching of most of the bits whenever passing through zero. In this case, a Sign-Magnitude representation could be more suitable. For counters and address buses, a Grey code representation is the best choice. Of course, one should consider also the implications in the functional units design and/or the conversion circuits, if needed, when choosing the number representation.

The work presented in this thesis is based mainly on supply voltage scaling coupled with clock frequency minimization. Switching activity or capacitive load reduction are only indirectly addressed, in the chapter dedicated to system-level synthesis. This comes from the fact that our scheduling problem assumes that the work performed by each task is already decided. More precisely the capacitive load and number of switches is fixed at the moment the tasks are scheduled. Furthermore, the low level aspects of power minimization are somewhat encapsulated in the power versus speed (clock frequency and supply voltage) dependency specific for each processor.

### 2.1.2 Energy Consumption in CMOS Circuits

As stated in the thesis title, we focus on energy rather than power consumption. Although low power and energy efficiency are often perceived as overlapping goals, there are certain differences when designing for one or the other. Formally, the energy consumed by a system is the amount of power used during a certain period of time:

$$E = \int_0^t P(t) dt \tag{2.5}$$

Every computation, simple or complex, requires a specific interval of time to be completed. The energy consumption decreases if the time required to perform the operation decreases and/or the power consumption decreases. Thus, compared to the pure power consumption minimization problem, energy reduction includes the time aspect. A technique that would lower the power, but at the same moment increase the computational time, might even lead to

an increase in energy consumption. For example, one could halve the power consumption by only halving the clock frequency in Equation 2.2. At the same time the overall computational time required to perform the same operation would double, leading to no effect on energy consumption. On the other hand, the supply voltage forces an upper limit on the clock frequency. For this reason supply voltage and clock frequency scaling are addressed in conjunction. Note that often lower energy consumption means slower systems. Real-time scheduling and energy minimization are therefore closely related problems, that should be tackled in conjunction for best results.

## 2.2 Real-Time Systems

Real-time systems are considered to be those types of systems which have to respond to certain stimuli within a finite and specified delay [BW01]. In other words, the correctness such systems depends not only on the logical result of the computations, but also on the time at which the results are produced [SSRB98]. For *hard* real-time systems, it is imperative that responses occur within the specified deadline, any exception leading to a total failure of the system. In *soft* real-time systems response times are important, but the system will still function correctly if some deadlines are occasionally missed.

Although the work presented in this thesis focuses on hard real-time systems, certain algorithms can be easily adapted for soft real-time systems, leading to even greater reductions in energy consumption while keeping a reasonable Quality of Service. Furthermore, we only consider the timing aspects characterizing real-time systems, without involving other specific features concerning, for instance, data sampling, computational accuracy, control efficiency, concurrency, reliability or safety. We also consider that, in principle, if basic real-time scheduling algorithms can be augmented with low energy techniques, then the extensions or enhancements of these algorithms for more complex real-time applications can employ the same low energy techniques. In fact, our energy-efficient methods can be applied once the real-time system timing behavior has been determined, without significantly affecting the design decisions beyond the choice of energy-aware components (such as variable speed processors).

Building upon the properties of the real-time applications, scheduling techniques exhibit several important characteristics [SSRB98, Axe97]:

- **Flexibility**, or the ability of the run-time scheduler to adapt to changes in the task set,

- **Predictability**, or the ability to analyze the run-time behavior by, for instance, estimating the task response time and verifying the timing constraints, and

• **Complexity**, or the volume of computation required to take scheduling decisions. One can distinguish between off-line complexity, when optimality is an issue, or at run-time complexity, when the scheduling overhead is important.

Following these properties, real-time scheduling algorithms can be distinguished into [Bur91, BW01]:

- Static or dynamic. A static approach takes all scheduling decisions in advance and requires prior knowledge about the properties of the system, but yields little run-time overhead. For instance, in the case of a fixed set of purely periodic, fixed execution time tasks, it is possible to lay out a complete schedule beforehand, using a cyclic executive approach. Yet, there are certain drawbacks with this method. For example, building the executive is NP-hard in the general case and sporadic tasks are difficult to handle [Loc92]. A dynamic scheduling method determines the schedules at run-time, being therefore more flexible. Fixed-priority scheduling (FPS) assigns static priorities to tasks, but schedules them at run-time. Rate-monotonic scheduling (RMS) is from the FPS class, since priorities are assigned according to task rates (fixed). By comparison, in earliest deadline first (EDF) scheduling even the priorities are computed at run-time, the highest priority tasks being those with the nearest deadline. Occasionally, in the real-time community, the scheduling approaches are referred to as static and dynamic depending on the decision regarding task priorities. In this sense FPS is called static and EDF, dynamic.

- **Preemptive or non-preemptive**. In a preemptive scheme certain low priority tasks may be suspended if higher priority tasks need to be executed. Alternatively, in non-preemptive approaches, once started each task finishes its execution without interruption from others. Clearly, preemptive schemes are more flexible, but they also introduce certain time overhead due to the context switches. Intermediate approaches also exist, such as *deferred preemption* schemes, where preemption cannot occur during certain critical time intervals.

- **Centralized or distributed**. A uni-processor system or a multi-processor system with shared memory, where the inter-processor communication time is negligible, are typical examples of centralized systems. In distributed systems, communications take considerable time that have to be accounted for, during feasibility analysis and scheduling.

The work presented in this thesis covers a wide range of scheduling techniques. For variable speed processors, the new dimension introduced by speed selection makes even the scheduling of individual tasks non-trivial, especially

for tasks with probabilistic execution time. At task group level, we look at both static and dynamic scheduling strategies for low energy. In particular, we address static cyclic scheduling for task graphs, FPS in the form of RMS or deadline-monotonic scheduling, and the EDF scheme. Preemption or non-preemption is assumed according the underlying real-time scheduling models. For instance, preemption is required in RMS, but not in some cases of EDF (single-rate, common arrival). In one case we advocate the use of preemption, just to lower the energy consumption when a non-preemptive strategy would also fulfill the real-time constraints (see Section 5.7). In all cases, preemption time overhead is considered to be negligible. We focus mainly on the uni-processor case, yet some of our scheduling methods are designed for heterogeneous architectures (see Sections 5.3, 5.4 and Chapter 6).

## 2.3 System Synthesis

For best results, the energy consumption issue should be addressed throughout the design cycle of a system. Therefore, it is important to stress the place of our methods in this whole design cycle. Although the thesis focuses mainly on task scheduling, in Chapter 6, we step back and look at how scheduling relates to the system architecture and task mapping. These are essential decisions that have to be taken during *system-level synthesis*, which is only a part of the typical design process, as detailed in the following.

Digital systems can be specified at different levels of abstraction. A traditional view of these levels and the relations between them is captured by the Y-chart, introduced in [GK83]. The most commonly used levels of abstraction are the physical, the logic, the register-transfer (RT), the behavioral, and the system level. At system level, the digital system is specified in terms of interacting, concurrent processes, which can be implemented either as hardware components, or in software. The support architecture is given in terms of boards, processors, memories, and buses. The hardware part of a system-level specification can be decomposed in several behavioral specifications, consisting of a sequential algorithm, or a single process. At RT level, the specification is further refined to a description in terms of operations between variables. At this point, the support architecture is composed of ALUs<sup>2</sup>, multiplexers, and registers. At logic level, digital hardware is represented in terms of boolean functions implementable by gates, latches, flip-flops, etc. Finally, at physical level, also referred to as circuit level, the hardware is described in terms of transistors, resistors or even silicon areas. Since there is no universally accepted description for these abstraction levels, different research and industry groups might have different views on this matter. It is also hard to

<sup>&</sup>lt;sup>2</sup>ALU: Arithmetic and Logic Unit

define clear cuts between any two adjacent levels. Very often, the digital system specification consists of several connected specifications, given at various levels of abstraction.

The complexity of certain systems can be dealt with by using high abstraction level descriptions. For a given specification, moving down from system to physical levels, more and more information is added. The specification becomes more detailed, larger and, therefore, harder to handle. We refer to this refinement process as synthesis [MLD92], although the term is often used to describe the translation from a behavioral representation of the design into a structural one [GDWL92, DeM94]. In particular, systemlevel synthesis deals with the formulation of the basic architecture of the implementation [EKP98a]. The most important decisions during the systemlevel synthesis step, are the allocation of the set of physical processors and the mapping of processes (or tasks) onto this processors while optimizing or fulfilling certain design parameters. For real-time applications, the timing constraints are an essential design parameter. Although, system partitioning, hardware/software co-design, and interconnect-structure design are a few fundamental issues related to system-level synthesis [EKP98a] that affect the energy consumption, we will not address them explicitly in this thesis. More precisely, assuming an already partitioned system, our architecture selection and task mapping approach choose specific task implementations, which might happen to be software or hardware solutions, and certain communication channels, based on the final effect on energy and timing, being oblivious to the lower level implementation choices. Furthermore, our scheduling methods only deal with ordering and speed selection (when necessary), without significantly altering the task implementations in order to affect the internal timing or energy consumption.

#### 2.4 Related Research

In the last few years, the research surrounding low power and low energy systems has become a flourishing area. Initially, most work focused on low power design at the lower abstraction levels. Gradually, as design automation started to be used at higher and higher abstraction levels, energy consumption became an important design metric, overshadowing power consumption at system-level. Finally, the already matured real-time area and low power and low energy design met first in the form of *dynamic power management* and then into *dynamic voltage scaling*, as variable voltage processors made their appearance. Relatively recent surveys of this area can be found in [Jha01, BD99, Ped01].

A large spectrum of compile-time techniques for low energy software also appeared. A few early reviews of such techniques can be found in [TMW94a,

TMW94b, MOI<sup>+</sup>97]. Some of these are memory energy reduction through efficient data access [PD99, DKV<sup>+</sup>02], switching reduction through register relabeling and instruction scheduling [Shi01, LLM<sup>+</sup>01, CC01, PKVI01], or various algorithmic transformations [CBD01, SBD01].

Note that all these techniques are orthogonal with speed scheduling algorithms. Once the tasks have been compiled to yield the lowest energy consumption with the compile-time techniques, task level and task group level speed scheduling techniques can be applied, in conjunction with power management, to additionally reduce the system energy consumption.

#### 2.4.1 Task Level Scheduling

At a first glance, deciding a task level speed distribution might appear as a trivial problem, implicitly solved at task group level. In fact, on fixed speed processors, it is not at all a problem. On the other hand, for variable speed processors, task level scheduling becomes an interesting issue because:

- real processors can only run at a limited, discrete range of speeds, most likely not including the ideal speed for the task in question, and

- an overwhelming majority of tasks exhibit variable (probabilistic) execution pattern, allowing for slowdown at run-time.

Thus, running the task always at only one speed, the one which guarantees meeting the deadline even for the worst case, is not the best solution from the energy consumption point of view. For this reason, several research groups have recognized and addressed the task level speed scheduling problem.

For applications involving variable processing rate, the available time for a given task may vary from instance to instance. Re-evaluating the speed for every instance can, thus, save energy. **Chandrakasan et al. (1996)** present in [CGX96] such an adaptive scheduling method, designed for digital signal processing (DSP) applications, such as MPEG. **Pering et al. (1998)** evaluate in [PBB98] several adaptive speed scheduling methods for DSP applications. The majority of these kind of methods are soft real-time, more concerned with the quality of service, than with meeting hard deadlines. The present thesis focuses on hard real-time systems.

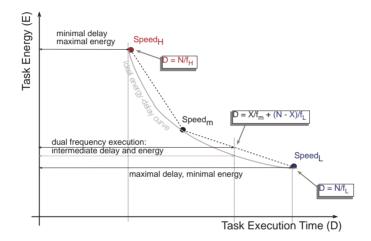

**Ishihara and Yasuura** (1998) have proven in [IY98] that a task can optimally run at any virtual speed, by running it in two phases at two different real speeds. These speeds are the ones bounding the virtual speed. The authors have also shown that the number and distribution of real available speeds has a direct impact on the energy efficiency of such a schedule. In fact, this dual-phase execution model seems to remain the standard for tasks with fixed execution pattern.

For tasks with variable execution pattern, the speed scheduling problem is even more interesting. Lee and Sakurai (2000) describe in [LS00b, LS00a] a method for run-time adjustment of processor speed. The task is divided in regions corresponding to time slots of equal length. At the end of each region's execution, a re-evaluation of the speed is performed in the following way. If the elapsed execution time after a certain number of regions is smaller than the alloted number of time slots, the execution speed can be lowered by an easily determined factor. A similar approach is presented by **Shin et al. (2001)** in [SKS01] as a part of a wider strategy, including task group level scheduling. Another task level scheduling method is described by **Mossé et al.** (2000) in [MACM00], where the regions and their corresponding time slots may have different sizes, while the slack (the difference between the elapsed and the worst case time at a certain moment) is distributed to regions according to various strategies. A more advanced approach, entitled intra-task scheduling, is described by Shin, Kim et al. (2001) in [SKL01]. In this method, speed re-calculation is performed after control decision affecting the execution path, at the beginning of representative basic blocks. A somewhat similar approach is taken by Hsu and Kremer (2001) in [HK01, HK02], where the task is profiled on basic-block level regions. In that work, a single or multiple regions are selected for speed scaling, based on their CPU and memory load. The method introduces a small performance degradation, acceptable only for soft real-time systems. The scheduling methods presented in this paragraph can all be classified as compiler-assisted approaches, since the task must be profiled and pre-processed off-line by, for instance, adding speed switching code snippets in essential points. Briefly, the algorithms must be aware of the internal structure of the task.

In parallel, a different class of scheduling method is emerging, which do not require knowledge about the internal structure of the task. These algorithms can be employed directly at run-time, without the need of a special pre-processing step. Besides our own *stochastic scheduling* method, the only other algorithm from the same class is *PACE* by **Lorch and Smith (2001)**. Presented in [LS01, Lor01], *PACE* was originally designed for soft real-time systems, but its pre-deadline part is based on the same idea as our own algorithm. Namely, it uses the probability distribution function of the task execution pattern to derive optimal schedules in the long run. The method of computing the distribution of the workload over the available processor speeds in *PACE* is slightly different from our own *stochastic scheduling*, but their results are also promising.

#### 2.4.2 Task Group Level Scheduling

One of the first attempts to an energy-sensitive scheduling strategy at task group level, appears to be the method of **Weiser et al.** (1994) presented in

[WWDS94]. Assuming a variable voltage processor, that work examines several speed scaling heuristics, all based on processor load. An extension of that work was presented by **Govil et al.** (1995) in [GCW95]. A more formal analysis of the minimum-energy scheduling problem, for periodic independent tasks on a variable speed processor, is presented by **Yao et al.** (1995) in [YDS95]. By examining the processor load on specific intervals, the authors describe an off-line optimal algorithm and two on-line heuristics for speed scheduling on top of the classical EDF. Furthermore, lower bounds for the on-line heuristics are determined in that work. Remaining one of the most important in the field, [YDS95] triggered the interest for a more formal approach to energy-efficient scheduling.

Hong et al. (1998) describe in [HPS98] a speed scheduling method for periodic and sporadic tasks, as an extension to EDF, also based on the processor load and worst case behavior. In [HKQ<sup>+</sup>98], the same authors present a non-preemptive speed scheduling strategy for sets of independent tasks with arbitrary arrivals and deadlines. The method is based on a heuristic task ordering step followed by a speed selection step. **Qu et al.** (1999) address in [QKPS99] energy reduction in pipelines, using variable speed stages selected depending on the latency constraints and data size.

Rate-monotonic scheduling (RMS) is first addressed in the context of energy-efficient scheduling by Lee and Krishna (1999) in [LK99]. Using a dual-speed processor model, the authors evaluate a speed scaling algorithm based on RMS, composed both of an off-line step and an on-line strategy. Furthermore, the authors investigate the energy efficiency of their method for tasks with probabilistic execution pattern. In [SC99], Shin et al. (1999) also present an extension of RMS, this time for multiple speeds processor. Based on tracking the next arrival times, their method adjusts the speeds for the running tasks, whenever there are no tasks waiting. The authors extend the method in [SKS01], to include task level speed scheduling based on compiletime application slicing. In another publication [SCS00], the same authors give an algorithm for computing a common maximal required speed for a task set, scheduled in with RMS. Our own RM-MRS method, presented in Section 5.5.2 improves this approach by identifying individual speeds for each task in the set. **Jejurikar and Gupta (2002)** further extend this method in [JG02], for handling task synchronization.

**Okuma et al.** (1999) introduce in [OIY98], and improve later in [OIY01], an EDF-based two phase scheduling algorithm that assigns speeds to tasks with different arrivals, deadlines, and capacitive load. In the off-line phase, each task is assigned a slot for execution and consequently a maximal speed, problem solved using ILP<sup>3</sup>. At run-time, if a task finishes early, the unused processor time is greedily assigned to the immediately next task instance,

<sup>&</sup>lt;sup>3</sup>ILP: Integer Linear Programming

lowering its off-line determined speed. On the same line, **Swaminathan** and **Chakrabarty** (2001) describe in [SC01b] both a MILP<sup>4</sup> approach and a heuristic for determining energy-efficient speed settings for EDF policy. Their approach assumes a dual-speed processor, but takes into account the speed switching latency and energy overhead.

Manzak and Chakrabarti (2000) present in [MC00] an off-line scheduling algorithm for tasks with arbitrary arrivals and deadlines, which again includes switching activity (or capacitive load as in [OIY01]). That approach is based on a heuristic that starts from a feasible schedule and gradually decreases the speed of certain tasks until no feasible schedule can be obtained. The same authors describe in [MC01] a speed selection algorithm based on a similar method, including periodic tasks this time. Their method tries to assign the same lowest possible speed for all tasks, but can still lead to unused processor times. Based on [MC00] and [YDS95], Pouwelse et al. (2001) describe in [PLS01] a low complexity sub-optimal scheduling method, implemented on a StrongARM with variable voltage platform. Their energy priority scheduler tries to level the speed schedule, by increasing the workload of low speed regions, through occasionally splitting tasks. Aydin et al. (2001) present in [AMMMA01] an off-line polynomial-time algorithm for determining the optimal speeds for tasks with fixed execution time, but with different power characteristics, scheduled using EDF.

**Quan and Hu** (2001) adapt in [QH01, QH02] the algorithm presented by Yao [YDS95] to tasks with fixed priorities. Their new approach still focuses on off-line scheduling for tasks with fixed execution pattern.

**Pillai and Shin (2001)** describe in [PS01] a few techniques for speed scheduling of periodic task sets, together with experimental results on an AMD K6-2+/ Linux platform. Their off-line method computes a single maximal required speed, based on utilization. Their cycle conserving on-line approach is similar to our slack distribution strategy presented in [Gru01a], to which the authors refer in their paper. Unlike in [Gru01a], no formal analysis of the feasibility of their method is presented. Another method they present, look-ahead DVS for EDF, tries to defer as much work as possible to as late as possible, while still keeping the deadline, in the hope that tasks will finish earlier than the worst case. Although it does not uses stochastic data for the tasks, their approach is based on a similar idea we base our task level stochastic scheduling method.

**Kim et al. (2002)** present in [KKM02] a run-time slack distribution strategy for EDF, based on an slack estimation heuristic that considers both accumulated and expected slack.

With the plethora of speed scheduling algorithms, a common evaluation platform becomes essential for the designer to detect the best method in a

<sup>&</sup>lt;sup>4</sup>MILP: Mixed Integer Linear Programming

specific case. **Shin et al.** (2002) present such an environment, SimDVS, in [SKJ $^+$ 02, KSY $^+$ 02], together with an performance evaluation of several dynamic voltage scaling algorithms, including some of our own.

Note that few of the approaches mentioned above take into account the run-time possibilities for speed scaling yield by the dynamic slack generated in the system [LK99, SC99, PS01, OIY01, KKM02]. This slack appears from tasks finishing execution early, from the variation of processor demand, etc. Even fewer techniques distribute this slack to the best advantage of the whole system [AMMMA01]. Most of these approaches were developed in fact in parallel with our own slack distribution strategy for RMS. Furthermore, none of these task group level techniques use the stochastic information related to task execution pattern to derive more efficient orders, as in our uncertainty based scheduling approach.

The work mentioned until now focuses on task sets of independent tasks. Scheduling task graphs for energy efficiency was also addressed in the context of distributed systems containing variable speed processors. **Luo and Jha (2000)** describe in [LJ00] a joint scheduling method for periodic task graphs and aperiodic tasks that allows for energy-efficient speed selection at run-time. The static phase dedicated to task graph scheduling, distributes the tasks loosely between arrival and deadline, such that the inter-task slack can accommodate aperiodic tasks or allow for speed reduction at run-time. The same authors improve their methods in [LJ02], with a critical-path analysis based static scheduling method, task execution order refinement, and a improved run-time speed recalculation algorithm. Since several researchers have addressed also architecture selection in conjunction with task graph scheduling, we cover these in the next section.

#### 2.4.3 System-Level Synthesis

For architectures with fixed speed processors, the problem of energy-efficient mapping and scheduling task graphs is somewhat similar to low power behavioral synthesis with multiple supply voltages, as addressed for example in ICP97, SR99, SC98, MC02, KB99, Mar001.

At system-level, the problem of energy consumption on processors with fixed speed was first addressed as a natural continuation of cost minimization or performance oriented co-synthesis. **Kirovski and Potkonjak** (1997) describe in [KP97] a system-level power minimization approach for hard real-time tasks, based on load balancing combined with supply voltage reduction. **Dave et al.** (1999) present in [DLJ99], an energy-aware co-synthesis system, COSYN-LP, based on an energy-conscious clustering technique for minimizing inter-processor communication. **Yang et al.** (2001) present in [YWM+01] a combined static-dynamic scheduling algorithm for task graphs on system containing a fixed speed processor system. The static phase finds a set of

schedules with different lengths and energy consumption, that may have different tasks allocated to processors with different speeds. The dynamic phase chooses the best schedule from the off-line set, based on the required processing rate. Thus, the allocation of tasks to processors and the schedule may change at run-time. **Dick (2002)** presents in [Dic02] several system-level synthesis algorithms targeting, among other objectives, low power consumption. The most representative in the context of our work are perhaps MOGAC [DJ97] and its enhancement, EMOGAC, for designing heterogeneous distributed systems based on a genetic algorithm (GA) for assignment and list-scheduling.

System-level synthesis using variable speed processors only recently made its way into the research community, our work from [Gru00b] being among the first addressing this subject. Schmitz and Al-Hashimi (2001) investigate the same problem in [SAH01, SAHE02], using GAs to optimize mapping and scheduling of task graphs. The GA optimizing the schedule it is nested in another GA, optimizing the mapping. In the scheduling GA heuristic, list-scheduling and voltage scheduling are performed consecutively, as two separate steps. In [SAHE02] the authors compare their scheduling strategy to our own LEneS method. Zhang et al. (2002) present in [ZHC02] an approach based on a two steps, the first being a combined assignment and ordering while the second being voltage selection for each task in the task graph. The first step is solved by a custom heuristics that balances the load on the processors. The voltage selection step is formulated and solved as an ILP problem.

There are many other approaches to reduce the energy consumption during system-level synthesis, that are based on memory size reduction, memory access minimization, algorithmic transformations, pipelining, etc. We only mentioned here the methods that are in the same class with the ones described in this thesis.

# Models

THROUGHOUT THE THESIS several different models are used for describing the system under design. The present chapter introduces these models. First we introduce the models used to describe the behavior of the system. Task and task group models are addressed at this point. Then we present the models describing the hardware resources available, such as processors and communication channels.

#### 3.1 Task Model

In the beginning of the system-level design and synthesis, before anything is decided about the implementation, a *task* models a certain part of the functionality of the system. Here we introduce a task as a computational process, yet this model is extensible to communications, as pointed out later.

**Definition 3.1.** A **task** is a sequential process, a single thread of execution, describing a part of the system behavior.

Furthermore, our task model has the following characteristics:

- 1. it may communicate with the outside world (other tasks) only before or after its execution, not during execution;

- it may be preempted at any point, unless the hardware resource imposes some restrictions in this sense.

Although the first point appears to be a restriction, it can be easily fulfilled, since any actual process that needs to exchange information during execution

can be decomposed into a sequence of processes interrupted by communications. When we are talking about a task assigned to a certain processor, *task* refers to an executable specially adapted (compiled, interpreted) to that processor. An *executable task* has additional characteristics:

- 3. it consists of atomic computational steps, namely clock cycles;

- 4. preemption can occur between any two consecutive clock cycles, but not during a clock cycle.

The number of clock cycles required by a task depends on the processor executing that task. Note also that point 4 is actually a refinement of the  $2^{nd}$  characteristic of a task.

Occasionally we use the term *task instance* (or *job*) to describe a process, running executable. For tasks with multiple possible execution paths this is an important distinction since two instances of the same task may exhibit different behavior. The interesting distinction for us is difference between the number of clock cycles required by the two instances. Later on we address both tasks using the same number of clock cycles for each instance and tasks with instances that use different number of clock cycles. The latter model is more realistic for tasks whose execution depends on the input data.

#### 3.1.1 Task attributes

Different scheduling methods describe tasks using abstract models of various complexity. A task is usually represented by a n-tuple of values (or attributes). Examining the attributes of a task, one can distinguish between requirements-related and implementation-related attributes.

The system specification usually contain requirements that refer to *deadlines*, task *period*, and maybe *dependencies* between tasks. All the scheduling methods described in this thesis were designed in principle to work for tasks with *hard deadlines* (see Section 2.2). Yet, most of the scheduling methods we present can be modified for *soft* or *firm deadlines*, as mentioned in specific sections. Since some of our methods were designed for *periodic* tasks, another task attribute used is the task period. Occasionally, deadlines or periods are specified for groups of (usually dependent) tasks instead of for each and every task separately. This is usually the case for systems described as task graphs (see Section 3.2.1).

Other task attributes, such as the computational demand, execution time or execution pattern, are strongly influenced by implementation. The processor type, its operating clock frequency, power consumption, the compiler, and the specific algorithms used are all implementation choices. Once the assignment of tasks to processors is decided, and the tasks brought to an executable format (i.e. compiled and linked) we can talk about the *execution pattern* of

that task. In its simplest form, the execution pattern can refer only to the number of clock cycles needed in the worst case (WCE). Most of the scheduling algorithms in the literature work only with timing information exhibited by the worst case execution. To achieve energy-efficient schedules, we actually make use of more extensive information about the task execution. In our case the proper definition for the execution pattern is the following.

**Definition 3.2.** The **execution pattern** of an executable task is a probability distribution function,  $\eta(x)$ , describing the probability that the task will execute for exactly x clock cycles.

Note that  $\eta(x)=0$  if  $x\notin[{\tt BCE},{\tt WCE}]$ , where BCE refers to clock cycles for the best case execution and WCE refers to the clock cycles for the worst case execution. Occasionally, even more information is required about the task. Some scheduling algorithms [SKL01] use a flow graph representation [ASU86] for the task. Such an algorithm will be briefly discussed in Section 4.3.2.

Although by *task* we usually refer to a computational process, communications can be modeled in a similar way. A reasonable assumption regarding communications is that tasks executed on the same processor can communicate instantly, in zero time, using for example shared memory. Inter-processor communication on the other hand takes time, resources (i.e. the bus), and consumes power. Moreover, we assume that communications do not take processor time (i.e. are handled by off-chip controllers and buffers). Our scheduling algorithms can thus treat computational tasks and communications in a similar manner, as long as the assignment step takes care of correctly binding tasks to processors and communications to channels (buses). The energy reduction techniques for communication channels are different than those for processors, but they turn up to be typical speed vs. energy trade-offs after all, as briefly described in Section 3.4.

Finally, in our algorithms a task  $\tau_i$  is represented by the following *n*-tuple:

$$\tau_i = \langle D_i, T_i, \eta_i(x) \rangle \tag{3.1}$$

where  $D_i$  is the deadline,  $T_i$  the period, and  $\eta_i(x)$  the execution pattern of task  $\tau_i$ . Some of the scheduling algorithms presented in this thesis use only specific characteristics of the execution pattern instead of the full function:

- $\bullet \,$  best case number of clock cycles,  $\mathtt{BCE}_i = \max\{x\}_{\eta_i(x)>0}$

- worst case number of clock cycles,  $WCE_i = min\{x\}_{n_i(x)>0}$

- mean number of clock cycles,  $\overline{X}_i = \sum_x \eta_i(x)x$

Note that for tasks with fixed execution pattern (single execution path)  $BCE_i = WCE_i = C_i$ , where  $C_i$  is the number of clock cycles required by the task.

# 3.2 Task Group Models

Usually the system under design is more complex than a single task, and needs to be represented by a group of tasks. The algorithms presented in this thesis, work either on task graphs or task sets, each representation exhibiting its own advantages and drawbacks, as described below.

## 3.2.1 Task Graphs

Task graphs are frequently used in hardware design automation, being similar to Data Flow Graphs (DFG) or Control Data Flow Graphs (CDFG) [DeM94]. Task graphs emphasize the dependencies between tasks and are suited for describing fairly static and possibly hierarchical structures.

**Definition 3.3.** A task graph is a directed a-cyclic graph  $\Gamma = (N, V)$  where each node is a task  $\tau_i \in N$  and each edge  $(\tau_i, \tau_j) \in V$  specifies that task  $\tau_i$  must finish its execution before  $\tau_j$  starts executing.

Conditional execution can be modeled in several ways. One may for example assign guards to some of the edges. Tasks which have guarded incident edges are executed not only when all its predecessors finished their execution but also only if the guard condition is true. In this case, each combination of conditions can be considered as representing a distinct non-conditional task graph. Scheduling a conditional task graph can be reduced then to scheduling several non-conditional task graphs and combining the results, as for example in [EKP<sup>+</sup>98b]. Alternatively, dealing with conditional paths in constraint programming based modeling is a straightforward extension of a non-conditional task graph scheduling, as shown in [Kuc99, SGK99, SGK00, KW01]. Another way to handle conditional execution is to move conditions inside tasks, obtaining tasks with variable execution time, depending on the conditions. The conditional task graph is then modeled as a non-conditional task graph made of tasks with variable execution time. Our static scheduling strategies can handle such task graphs, except the tasks will always be assumed to exhibit their worst case execution pattern. For the reasons described above we will not explicitly use the conditional task graph model in this thesis.

The nodes in the task graph described above can model both computations and communications. In general, the task graph can be viewed as a bipartite graph, where every edge connects a computational node with a communication node. Since we assume instantaneous communication for computational tasks assigned to the same processor, our task graphs can contain, after assignment, edges that connect two computations.

Since the task graph usually describes a repetitive process, an implicit loop is assumed over the whole graph. An iteration starts by executing first those tasks that do not depend on other tasks and proceeds executing the rest of the tasks once their predecessors finished. The iteration finishes as soon as all reachable tasks finish their execution. Timing constraints resulting from requirements at this level usually refer to the time required for executing one whole iteration. In our model, only when the current iteration finishes, a new task graph instance can begin executing. Correlating this with equation 3.1 containing the n-tuple describing a task, we can say that all tasks will have the same period and deadline,  $\forall i \in N, T_i = D_i = \text{GraphExecutionDelay}$ . By contrast, pipelining techniques use task graph execution models where iterations overlap [Kuc99, SGK00, KW01]. Although our techniques can be adapted to pipeline scheduling, this thesis does not explicitly address pipeline scheduling.

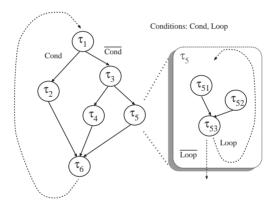

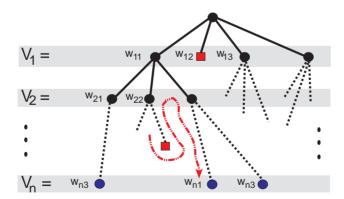

A-cyclic task graphs can also model internal loops, in a hierarchical manner. Each loop can be modeled by a node which is itself an a-cyclic sub-graph. Together with the implicit loop assumed for each a-cyclic graph, this hierarchical modeling can capture nested loops over sub-groups of tasks as in Figure 3.1.

Figure 3.1: A task graph with conditions and loops. The depicted graph is hierarchical, with  $\tau_5$  modeling a sub-graph forming a loop. *Cond* controls the execution to take either the  $\tau_2$  or  $\tau_3$  path. *Loop* controls the repetitive execution of the  $\tau_5$  sub-graph.

# 3.2.2 Enhanced Task Graphs

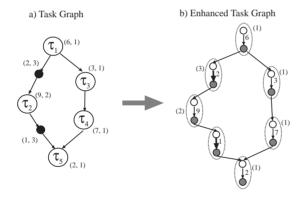

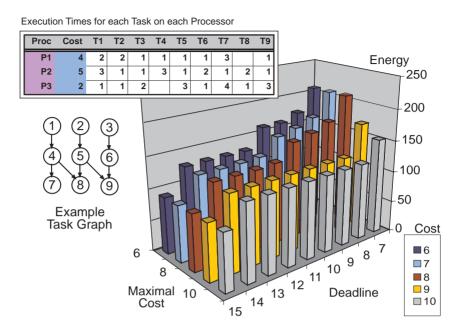

The scheduling algorithm presented in Section 5.4 uses an Enhanced Task Graph (ETG) model, derived from classic task graphs. Since the resources used are variable speed processors, the execution time of a task can vary depending on the processor clock frequency. Therefore, each task, is more accu-

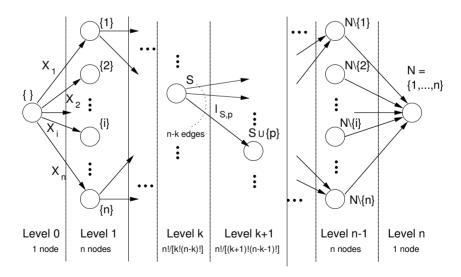

rately modeled by two important events: start of its execution and the end of its execution. Figure 3.2 details examples of a task graph and its corresponding ETG. In the task graph, depicted on the left, tasks are represented by the circles annotated by pairs of values. A pair consists of the execution time of the task and the identifier of the processor executing the task. The black disks represent communications annotated with the duration and the identifier of the bus/link used for that specific communication. The arcs define the partial order of task execution, which is imposed by the various data dependencies. The ETG is obtained from the initial task graph by substituting each node with a pair of nodes: a start node (the circles), marking the beginning of the execution of that node, and an end node (the grey disks), marking the completion of the task. The execution times of the tasks are now assigned to the internal edges. In our current model, only computational tasks are subject to change their execution delay, while the communication delays remain fixed. The thick edges in the ETG represent the fixed delays. The other edges depict modifiable delays, and the associated numbers define their minimal values. The information regarding the assignment of tasks to processors is also transferred to the ETG.

Figure 3.2: A Task Graph and its corresponding Enhanced Task Graph

## 3.2.3 Task Sets

The task set model emphasizes the timing requirements for each task. They are more suited for modeling dynamic systems employing priority based runtime scheduling. In our task set model, there is no data or control dependency between tasks, so there is no communication taking place between the tasks. Moreover, our scheduling algorithms focus on the case when the tasks run on

a single processor. Tasks are still represented using the triple from equation 3.1, with the mention that for any task the deadline is not larger than the period. Occasionally our algorithms use more restricted models (i.e. deadlines equal to periods), as explicitly stated in the corresponding sections.

An important characteristic of a task set is the processor *utilization* imposed by the task set. Since we are dealing with variable speed processors, the utilization is always defined for the reference speed, that is usually the maximum processor speed. Furthermore, since the tasks have variable execution pattern, we distinguish between *worst case utilization* and *actual utilization*. With the notations introduced in Section 3.1.1 we give the following definitions:

### **Definition 3.4.** Given a task set of N tasks

$\{\tau_i = (D_i, T_i, \eta_i(x))\}_{i=1...N}$  the **worst case utilization** is computed as:

$$U_{\text{WCE}} = \frac{1}{f_{ref}} \sum_{i=1}^{N} \frac{\text{WCE}_i}{T_i}$$

(3.2)

where  $f_{ref}$  is the reference clock frequency. The **actual utilization** over H hyper-periods is computed as:

$$U(H) = \frac{1}{f_{ref}} \frac{1}{H} \sum_{h=1}^{H} \sum_{i=1}^{N} \sum_{j=1}^{\lceil T_i/T_H \rceil} \frac{X_i^{hj}}{T_i}$$

(3.3)

where  $X_i^{hj}$  is the number of cycles executed by the  $j^{th}$  task instance of task  $\tau_i$  in hyper-period h.  $T_H$  is the duration of the hyper-period, computed as the least common multiple of all task periods,  $lcm\left(\{T_i\}_{i=1...N}\right)$ .

Note that the actual utilization can be accurately computed only after execution, when all the execution patterns for all task instances are known. For a sufficiently long interval of time, an estimate of the actual utilization is the expected value of utilization  $\overline{U}$ :

$$\overline{U} = U(t)|_{t \to \infty} \approx \frac{1}{f_{ref}} \sum_{i=1}^{N} \frac{\overline{X_i}}{T_i}$$

(3.4)

# 3.3 Processor Models

A basic assumption for modeling resources is that a task can exclusively use only one resource at a certain time. This can perfectly model for example tasks implemented as software running on a processor or ASICs implementing a

single task. Escaping our model are the cases where several tasks are implemented on a single ASIC, executing in parallel, sharing functional units. Yet, since our scheduling techniques focus mainly on architectures composed exclusively of processors running software tasks, the above mentioned assumption is reasonable enough.

Other assumptions are that the *processors are synchronous designs* (for which it makes sense to talk about clock frequency) and given a certain clock frequency, *all clock cycles require the same amount of energy*, irrespective of the computational requests. This means that the power consumption of a processor for a given clock speed remains almost constant and independent on the running task.

In practice the power difference between various instruction can vary considerably ([TMW94b]). Yet, complex tasks, as encountered in this design phase, consist of rather heterogeneous mixes of instructions, meaning that the variation in power consumption over a relatively small number of clock cycles is statistically insignificant [RJ98]. We make one exception from this rule for the NOP instruction, which is assumed to consume only around 20% of the normal (average) power [SC99]. A processor constantly executing NOPs will thus use only 20% of the energy it would use by doing some useful work.

The constant power per clock cycle assumption given above may also be inaccurate at task group level, if the tasks exhibit very different computational requirements. For example an intensive data processing tasks (such as shuffling data in memory) may consume more power than a control task. Although our algorithms do not explicitly distinguish between such tasks, they can be adjusted to accommodate these cases by assigning different weights to tasks accordingly.

# 3.3.1 Fixed Speed Processors

In the first part of Chapter 6 we address architecture selection for minimal energy, using fixed speed processors as resources. This type of resource models processors operating at constant clock frequency and voltage, thus dissipating a constant amount of power. They also have at least two power modes: ACTIVE, when they execute instructions, consequently consuming significant power, and SLEEP, when instruction processing is stopped and the power consumption is much lower. The processor can, thus, enter the SLEEP state whenever it is idle. Power modes are a common feature today for all types of processors, and especially embedded processors (see Example 3.1). Efficiently selecting power modes for resources, at run-time, is an area usually referred to as Dynamic Power Management (DPM). The Advanced Configuration and Power Interface (ACPI) specification is a joint effort by Compaq, Intel, Microsoft, Phoenix, and Toshiba towards a standard API supporting

DPM [Com02]. ACPI 2.0 is implemented in most Windows<sup>TM</sup> operating systems and in the Linux kernel version 2.4. However, DPM is not the focus of this thesis.

## Example 3.1 (Intel® 80200 Power Modes):