#### **Continuous-Time Delta-Sigma Modulators for Wireless Communication**

Andersson, Mattias

2014

#### Link to publication

Citation for published version (APA):

Andersson, M. (2014). Continuous-Time Delta-Sigma Modulators for Wireless Communication. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 19. Dec. 2025

## Continuous-Time Delta-Sigma Modulators for Wireless Communication

## **Mattias Andersson**

Doctoral Dissertation Lund, March 2014

Department for Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

ISSN 1654-790X, no.55 ISBN 978-91-7473-785-1 (print) ISBN 978-91-7473-786-8 (pdf) Series of licentiate and doctoral dissertations.

© Mattias Andersson 2014. Produced using IAT<sub>E</sub>X Documentation System. Printed in Sweden by *Tryckeriet i E-huset*, Lund. March 2014.

### Abstract

The ever increasing data rates in wireless communication require analog to digital converters (ADCs) with greater requirements on speed and accuracy, while being power efficient to prolong battery life. This dissertation contains an introduction to the field and five papers that focus on the continuous-time (CT)  $\Delta\Sigma$  modulator (DSM) as ADC.

Paper I analyses the performance degradation of dynamic nonlinearity in the feedback DAC of the DSM, caused by  $V_{th}$  mismatch in the current-switching (differential) pair of a current-steering DAC. A model is developed to study return-to-zero (RZ) and non-return-to-zero (NRZ) feedback DACs, with and without data-weighted averaging (DWA), where an RZ DAC with DWA recovers the performance.

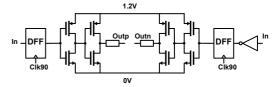

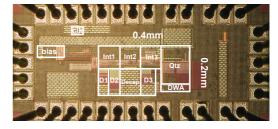

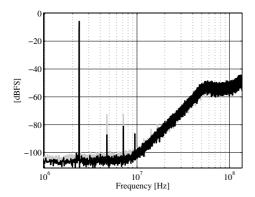

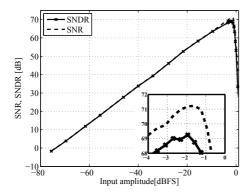

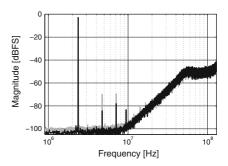

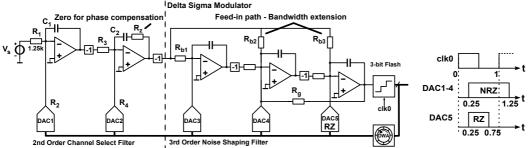

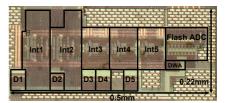

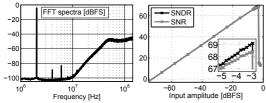

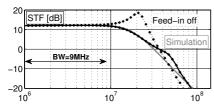

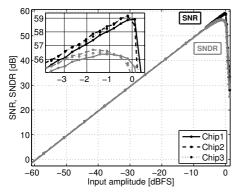

Paper II and III presents a feedback scheme for improved robustness against variations in loop delay. An RZ pulse, centered in the clock period, is used in the innermost feedback path which has the highest sensitivity to loop delay, while NRZ pulses are adopted in the outer feedback paths to reduce the sensitivity to clock jitter and lower the integrator slew rate requirements. Furthermore, the otherwise obligatory loop delay compensation path (e.g. an additional DAC and adder) could be omitted to reduce hardware complexity. A discrete-time model of the feedback scheme confirms a negligible loss in performance. The 3<sup>rd</sup>-order CT DSM in 65 nm CMOS with 9 MHz LTE bandwidth achieves 69/71 dB SNDR/SNR and consumes 7.5 mW from a 1.2 V supply. Measurements with OFDM signals verify an improved tolerance to blockers outside the signal band of the DSM.

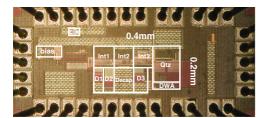

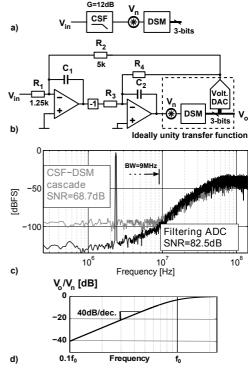

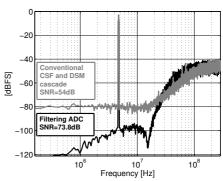

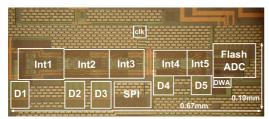

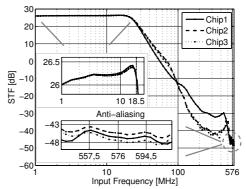

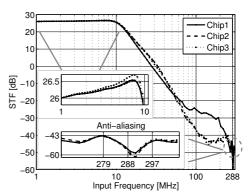

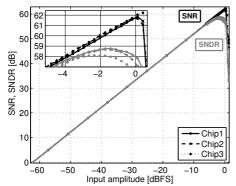

Paper IV and V present two filtering ADCs, where the DSM is merged into the channel select filter to suppress the noise from the DSM. The first and second prototypes provide a  $2^{\rm nd}$ - and  $3^{\rm rd}$ -order channel select filtering and improve the SNDR of the DSM by 14 dB and 20 dB, respectively, which in theory can be exploited to reduce the DSM power consumption by four to eight times.

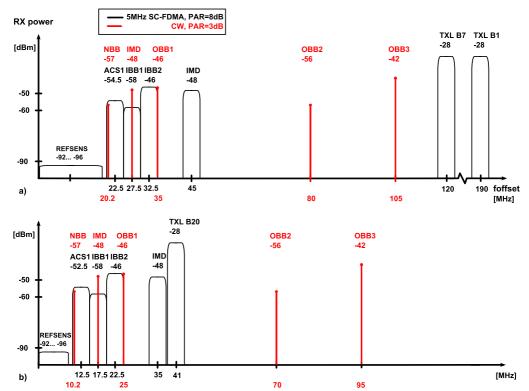

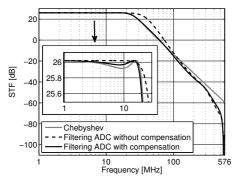

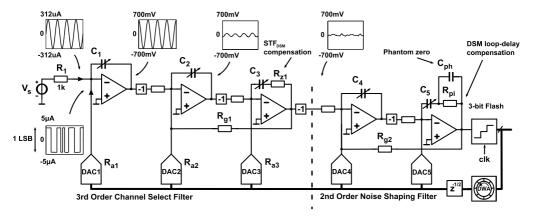

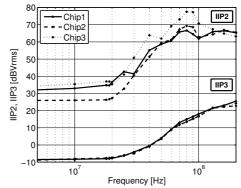

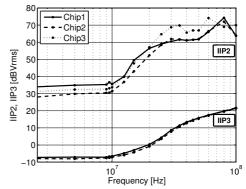

The first prototype has a 288 MHz clock frequency, a 9 MHz LTE bandwidth, a  $2^{\rm nd}$ -order Butterworth filter response with 12 dB gain, an inputreferred noise of  $8.1\,\rm nV/\sqrt{\rm Hz}$ , an in/out-of-band IIP3 of  $11.5/27\,\rm dBV_{\rm rms}$ , and a power consumption of  $11.3\,\rm mW$ . The second prototype is clocked at  $576/288\,\rm MHz$  with an  $18.5/9\,\rm MHz$  LTE bandwidth, a Chebyshev filter response with  $26\,\rm dB$  gain, a low input-referred noise of  $5\,\rm nV/\sqrt{\rm Hz}$ , and an in/out-of-band IIP3 of  $-8.5/20\,\rm dBV_{\rm rms}$ , with a power consumption of  $7.9/5.4\,\rm mW$  for  $2x\rm LTE20/LTE20$  mode. The prototype was characterized for OFDM modulated blockers and essentially meets the cellular standard LTE Rel. 11. A delay, introduced by the feedback DAC, is compensated by adjusting the filter coefficients to restore the original Chebyshev filter function.

vi

Both prototypes have state-of-the-art power efficiency compared to other filtering ADCs and are comparable or better than a stand-alone filter. Furthermore, the filtering ADC provides both filtering and A/D conversion, which suggests that the A/D conversion is included in a power efficient manner, broadly speaking "for free".

# Populärvetenskaplig sammanfattning

Trådlös kommunikation mellan olika batteridrivna enheter såsom smarta telefoner, används dagligen i våra liv. Kommunikationen sker ofta via internet med högkvalitativa bilder, filmer och ljud, vilket kräver högre datahastigheter i den trådlösa mottagaren (radiomottagaren). Den högre hastigheten ökar prestandakraven på komponenterna i mottagarkedjan, vilket generellt kräver en högre strömförbrukning. Således är det viktigt att förbättra både prestanda och energieffektivitet i komponenterna, så att de högre datahastigheterna kan nås för en rimlig strömförbrukning.

En begränsande komponent i mottagarkedjan är analog-till-digital omvandlaren (ADC:n), som tar emot den analoga radio signalen och omvandlar den till en digital representation (ettor och nollor) som sedan avkodas i efterföljande block. Den här avhandlingen innehåller fem vetenskapliga artiklar om tekniker som förbättrar en vanligt förekommande typ av ADC i radiomottagare, nämligen delta-sigma modulatorn (DSM). En DSM är ett återkopplat system som i sig internt innehåller både en ADC och flera DAC:ar (digital-till-analog omvandlare). Varje DSM använder i storleksordningen 0.1mm² kiselyta vid tillverkning i en så kallad 65 nm CMOS process och förbrukar i storleksordningen 5-10 mW i effekt. De två viktigaste lösningarna som presenteras i avhandlingen beskrivs nedan:

Den första tekniken sänker känsligheten mot fördröjningar internt i DSM, vilket gör den mer robust mot variationer i tillverkningsprocessen och förenklar utvecklingsarbetet. Dessutom är det möjligt att ta bort en av de interna DAC:arna och på så sätt spara ström och yta på chipet. Lösningen använder en annan slags puls i en av DAC:arna och är verifierad med mätningar av ett chip.

Den andra tekniken flyttar analog-till-digital omvandlaren in i ett filter för att skapa en filtrerande ADC. Ett filter används ofta före ADC:n för att sänka prestandakraven på ADC:n och totalt sett ge en lägre effektförbrukning. Fördelen med den filtrerande ADC:n är att kraven på ADC:n blir ännu lägre, vilket möjliggör en sänkning av effektförbrukningen i ADC:n med mer än fyra gånger. Konceptet är verifierat med två tillverkade chip, där det andra chipet stödjer en av de senaste standarderna för mobilkommunikation, "longterm evolution" (LTE) release 11. Den filtrerande ADC:n har lika bra eller bättre energieffektivitet jämfört med andra publicerade filter, vilket indikerar att själva analog-till-digital omvandligen sker effektivt.

Doktorandtjänsten och kiseltillverkningen har finansierats av projekten Design Methods for Radio Architectures GOing Nanoscale (DRAGON), Systemdesign-On-Silicon (SOS) och ST Microeletronics.

## Contents

| Abstrac   | t                                                | $\mathbf{V}$           |

|-----------|--------------------------------------------------|------------------------|

| Populär   | vetenskaplig sammanfattning                      | vii                    |

| Content   | s                                                | ix                     |

| Preface   |                                                  | xi                     |

| Acknow    | ledgments                                        | xiii                   |

| List of A | Acronyms                                         | $\mathbf{x}\mathbf{v}$ |

| List of S | Symbols                                          | xix                    |

| Introdu   | ction                                            | 1                      |

| 1 Int     | roduction                                        | 1                      |

| 1.1       | Motivation                                       | 1                      |

| 1.2       | Research contributions                           | 2                      |

| 1.3       | Outline                                          | 3                      |

| 2 Th      | e radio receiver                                 | 5                      |

| 2.1       | Introduction                                     | 5                      |

| 2.2       | Characterization of receiver blocks              | 7                      |

|           | 2.2.1 Input referred representation              | 7                      |

|           | 2.2.2 Noise                                      | 7                      |

|           | 2.2.3 Compression point, $P_{1dB}$ and $CP$      | 8                      |

|           | 2.2.4 Intermodulation intercept point            | 8                      |

| 3 Co      | ntinuous-time $\Delta\Sigma$ modulators          | 11                     |

| 3.1       | Introduction                                     | 11                     |

|           | Basics of filtering ADCs                         | 12                     |

|           | 3.2.1 The term filtering ADC                     | 14                     |

|           | 3.2.2 Previous work                              | 14                     |

|           | NTF and STF trade-offs                           | 15                     |

|           | Feed-forward modulators                          | 15                     |

|           | Improved selectivity and noise shaping           | 16                     |

| 3.3       | Performance comparison of filtering ADCs         | 16                     |

|           | 3.3.1 Comparison with filters                    | 17                     |

| 3.4       | Feedback DAC pulse                               | 19                     |

|           | 3.4.1 Fixed loop delay                           | 20                     |

|           | 3.4.2 Variations in loop delay                   | 21                     |

|           | 3.4.3 z-domain analysis of loop delay variations | 22                     |

x Contents

|              | DAC with highest sensitivity                                                                       | 23<br>23 |

|--------------|----------------------------------------------------------------------------------------------------|----------|

|              | Reduced sensitivity                                                                                | 23<br>24 |

|              | 4 Circuit level considerations                                                                     | 27       |

|              | 4.1 Feedback DAC                                                                                   | 27       |

|              | 4.1.1 Noise                                                                                        | 27       |

|              | 4.1.2 Output impedance                                                                             | 29       |

|              | 4.2 Flash ADC                                                                                      | 30       |

|              | 4.3 Active-RC Integrators                                                                          | 30       |

|              | 4.3.1 Superposition feedback model                                                                 | 32       |

|              | 4.3.2 Transfer function                                                                            | 33       |

|              | 4.3.3 Series resistor $R_z$ with integrator capacitor                                              | 34       |

|              | Impact on loop gain and phantom zero compensation                                                  | 35       |

|              |                                                                                                    |          |

|              | 5 Paper Summary and Conclusions                                                                    | 37       |

|              | 5.1 Summary                                                                                        | 37       |

|              | 6 Discussion and Future Work                                                                       | 41       |

|              | A Additional measurement results                                                                   | 43       |

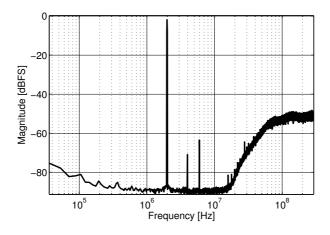

|              | A.1 FFT                                                                                            | 43       |

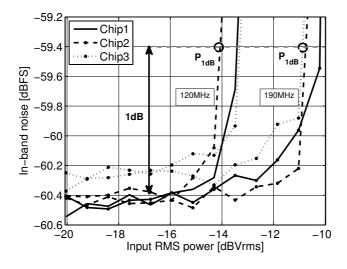

|              | A.2 Blocker tolerance                                                                              | 43       |

|              | A.3 Chip-to-chip variations                                                                        | 45       |

|              | B Positive feedforward/feedback compensation                                                       | 49       |

|              | B.1 Overview                                                                                       | 49       |

|              | B.2 Analysis                                                                                       | 50       |

|              | References                                                                                         | 53       |

| Ι            | Impact of MOS Threshold-Voltage Mismatch in Current-Steering DACs for CT $\Delta\Sigma$ Modulators | 63       |

| II           | A 7.5 mW 9 MHz CT $\Delta\Sigma$ Modulator in 65 nm                                                |          |

|              | CMOS With 69 dB SNDR and Reduced Sensitiv-                                                         |          |

|              | ity to Loop Delay Variations                                                                       | 71       |

| ттт          | Theory and Design of a CT $\Delta\Sigma$ Modulator with                                            |          |

| 111          | Low Sensitivity to Loop-Delay Variations                                                           | 79       |

| TT 7         |                                                                                                    |          |

| ΙV           | A 9MHz Filtering ADC with Additional 2nd-order $\Delta\Sigma$ Modulator Noise Suppression          | 97       |

|              | 22 Modulator Moise Suppression                                                                     | 91       |

| $\mathbf{V}$ | A Filtering $\Delta\Sigma$ ADC for LTE and Beyond                                                  | 105      |

## Preface

This dissertation summarizes my academic work for a Ph.D degree in Circuit Design in the Mixed Signal Design group, at the Department of Electrical and Information Technology, Lund University, Sweden. The Ph.D studies took place from February 2009 until March 2014. The dissertation is divided into two parts, where the first part has six chapters that contains an introduction to the research field, followed by an appendix with supplementary results. The second part contains the included research papers, which are listed below.

#### **Included Research Papers**

The main contribution is derived from the following publications:

- [1] M. Andersson, M. Anderson, P. Andreani, and L. Sundström, "Impact of MOS threshold-voltage mismatch in current-steering DACs for CT ΔΣ modulators," in *Proc. of IEEE International Symposium on Circuits and Systems, ISCAS'10*, Paris, France, May 30–Jun. 2 2010, pp. 4021–4024.

- [2] M. Andersson, M. Anderson, L. Sundström, and P. Andreani, "A 7.5 mW 9 MHz CT ΔΣ Modulator in 65 nm CMOS With 69 dB SNDR and Reduced Sensitivity to Loop Delay Variations," in *Proc. of IEEE A-SSCC*, Kobe, Japan, Nov. 12–14 2012, pp. 245–248.

- [3] M. Andersson, L. Sundström, M. Anderson, and P. Andreani, "Theory and design of a CT  $\Delta\Sigma$  modulator with low sensitivity to loop-delay variations," *Analog Integrated Circuits and Signal Processing*, vol. 76, no. 3, pp. 353–366, Sep. 2013.

- [4] M. Andersson, M. Anderson, L. Sundström, S. Mattisson, and P. Andreani, "A 9MHz Filtering ADC with Additional 2nd-order  $\Delta\Sigma$  Modulator Noise Suppression," in *Proc. of 39th IEEE ESSCIRC 2013*, Bucharest, Romania, Sep. 16–20 2013, pp. 323–326.

- [5] M. Andersson, M. Anderson, L. Sundström, S. Mattisson, and P. Andreani, "A Filtering ΔΣ ADC for LTE and Beyond," *IEEE Journal of Solid-State Circuits, submitted (invited)*, July 2014.

#### Related publications

I have also co-authored the following papers, which are not considered as a part of this dissertation.

M. Anderson, R. Strandberg, S. Ek, L. Wilhelmsson, L. Sundström, M. Andersson, I. ud Din, J. Svensson, T. Olsson, and D. Eckerbert, "A

xii Preface

4.75 - 34.75 MHz Digitally Tunable Active-RC LPF for >60 dB Mean RX IRR in 65 nm CMOS," in *Proc. of 38th IEEE ESSCIRC 2012*, Bordeaux, France, Nov. 17–21 2012, pp. 470–473.

L. Sundström, M. Anderson, M. Anderson, and P. Andreani, "Harmonic Rejection Mixer at ADC Input for Complex IF Dual Carrier Receiver Architecture," in *RFIC*, Montreal, Canada, Jun. 17–19 2012, pp. 265–268.

#### Patent applications

M. Anderson, M. Andersson, S. Mattisson, and P. Andreani, "A frequency selective circuit configured to convert an analog input signal to a digital output signal," *International application*, No. PCT/EP2013/053424, 2013.

## Acknowledgments

First, I would like to express my sincere gratitude to my supervisor, Associate Professor Pietro Andreani, for giving me the opportunity to pursue Ph.D studies at Lund University. Prof. Andreani's passion for integrated circuits has encouraged me during the five years of hard study. It has been an honor to collaborate with such a competent supervisor that has outstanding theoretical and communication skills. His genuine interest and large patience has numerous times been exploited through long friendly discussions and reviews of the manuscripts and presentations in detail - Thank you for your support!

I have been fortunate to have Dr. Martin Anderson as a co-supervisor from the academia and later from the industry. Thank you for introducing me to Ph. D studies and guiding me in the right direction when I was lost. You have always taken your time to generously share your knowledge and ideas for me. I appreciate your friendship, and the countless inspiring discussions on technical (and non-technical) matters during my studies.

I would also like to thank Dr. Lars Sundström, senior specialist at Ericsson, for your guidance. His expertise span over a wide area, ranging from circuit level design to radio system specifications, and he is an invaluable source of knowledge to harvest from. Lars sound ideas, correctness and structured approach has truly been helpful to bring my work forward.

My strong interest in integrated circuits and analog circuit design is largely thanks to the inspiring undergraduate courses I took from Henrik Sjöland, Viktor Öwall and Bertil Larsson. In particular, I would like to thank Bertil for allowing me to teach in his courses and for the things you have taught me.

At Ericsson, several people have assisted me during different periods of my career. Thank you Sven Mattisson for being active in the project at the time when I needed it the most. I am also very thankful to Roland Strandberg and Jim Svensson for many reasons.

To all my former colleagues at Cambridge Silicon Radio (CSR), I am grateful for the three years we spent together and the knowledge you shared with me. In particular, thank you Martin Lantz, Per-Olof Brandt, Henrik Geis, Hashem Zare-Hoseini, and Henrik Johansson.

At the university, I give a big thank you to Andreas Axholt and Anders Nejdel for being my lunch mates and for the fun and comprehensive conversations we have had. Thank you Carl Bryant for your help and for sharing my interest in brass music; Markus Törmänen, Peter Sjöblom, and Johan Wernehag for your friendship; Dejan Radjen and Xiaodong Liu for being excellent room mates and tolerating my whining during hard times. I will never forget the exiting road trip with Dejan to San Francisco in 2011. Thank you Ping Lu, Tobias Tired, Waqas Ahmad, Mohammed Abdulaziz, Therese Forsberg, Jonas Lindstrand, Rohit Chandra, Nafiseh Seyed Mazloum, Linnea Larsson,

Oskar Andersson, Isael Diaz, Yasser Sherazi, Reza Meraji, Chenxin Zhang, Michal Stala, Babak Mohammadi, Rakesh Gangarajaiah, Hemanth Prabhu, Steffen Malkowsky, Christoph Müller, Liang Liu, Johan Löfgren, Mats Ärlelid, Joachim Rodrigues, Peter Nilsson, Clas Agnvall, and Lars Olsson for your support, and the friendly and positive atmosphere that you bring. Thank you Erik Jonsson, Stefan Molund, Lars Hedenstjerna, and Pia Bruhn for making sure that technical and administrative tasks run smoothly.

Last but not least, I am very thankful to my friends and my family: Evald, Birgitta, Rickard, and Cecilia for always being there. Thank you Lisa for making the few hours outside the office so delightful with your love.

Mattias Andersson

Design is a funny word. Some people think design means how it looks. But of course, if you dig deeper, it's really how it works.

– Steve Jobs –

## List of Acronyms

A/D Analog-to-digital

ADC Analog-to-digital converter

BW Bandwidth of desired A/D converted channel

${\it CIFB} \qquad {\it Cascaded integrators with feedback compensated loop filter}$

CIFF Cascaded integrators with feedforward compensated loop filter

CMFB Common-mode feedback

CMOS Complementary metal oxide semiconductor

CP Compression point

CSF Channel-select filter

CT Continuous time D/A Digital-to-analog

DAC Digital-to-analog converter

DC Direct current

DR Dynamic range

DSM Delta-sigma modulator

DT Discrete time

DWA Data-weighted averaging

${\rm FOM} \qquad {\rm Figure \ of \ merit}$

FFT Fast fourier transform

${\rm GBW} \hspace{0.5cm} {\rm Gain \ band-width}$

GE Gain error

HF High-frequency

HP High-pass

$\label{eq:inside} \text{IB} \qquad \quad \text{In-band (inside the desired bandwidth)}$

IBN Noise within the desired bandwidth

ICP Input-referred compression point

$IIPn \qquad \text{ n-th order input-referred intercept point} \\$

IMn n-th order intermodulation distortion

IPn n-th order intercept point

IRN Input-referred noise

ISI Inter symbol interference

IF Intermediate frequency

LF Low-frequency

LHP Left half plane

LNA Low-noise amplifier

LP Low-pass

LSB Least significant bit

LTE 3GPP long-term evolution

LTE20 LTE with 20 MHz channel bandwidth at RF

NF Noise figure

NRZ Non-return-to-zero

NTF Noise transfer function

OCP Output-referred compression point

OFDM Orthogonal frequency division multiplexing

OOB Out-of-band

OSR Oversampling ratio

PAR Peak-to-average ratio

PCB Printed circuit board

PI Proportional integrating

PM Phase margin

PSD Power spectral density

RF Radio frequency

RFFE RF front-end

RHP Right half plane

List of Acronyms xvii

RX Receiver

RZ Return-to-zero

SDR Software defined radio

SFDR Spurious-free dynamic range

S/H Sample-and-hold

SNDR Signal-to-noise-and-distortion ratio

SNR Signal-to-noise ratio

SQNR Signal-to-quantization-noise ratio

STF Signal transfer function

TF Transfer function

TX Transmitter

## List of Symbols

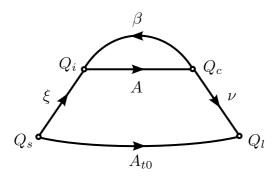

$A\beta$ Loop gain Transfer function from source to load  $A_t$  $A_{t\infty}$ Ideal transfer function from source to load  $\alpha$ Time instant where feedback DAC pulse starts β Time instant where feedback DAC pulse ends Δ Quantization step n<sup>th</sup> order harmonic distortion  $HD_n$  $f_s$ Clock/sampling frequency [Hz] n<sup>th</sup> order intermodulation distortion  $IM_n$ n<sup>th</sup> order (intermodulation) intercept point  $IP_n$ Input-referred n<sup>th</sup> order intercept point  $IIP_n$ Boltzmann's constant,  $\approx 1.381 \times 10^{-23} \text{ [J/K]}$ kNFNoise figure Input power where the IBN increases by 1 dB  $P_{1dB}$  $T_s$ Sampling period [s] TTemperature [k]  $V_{\rm th}$ MOS transistor threshold voltage

## Introduction

## Chapter 1

#### Introduction

#### 1.1 Motivation

Today, the major innovations in consumer electronics are demonstrated in portable, battery powered devices such as smartphones and tablets. These devices use a large data rate via a wireless communication link, and therefore require high performance radio receivers with wider bandwidths and/or higher signal-to-noise ratios. Moreover, a receiver with higher performance in general consumes more power, which shortens the battery life of the device. Thus, research is needed to improve the power efficiency and performance of the receiver, to be able to deliver a high data rate with reasonable power consumption. Furthermore, analysis of the circuits enables the designer to understand the performance limiting factors and invent better integrated circuits (chips). These chips are mass-produced and require robust solutions that have low sensitivity to process-variations from manufacture.

A key component in the radio receiver is the analog-to-digital converter (ADC), which provides an interface between analog (the world) and digital (the ones and zeroes). A popular type of ADC is the  $\Delta\Sigma$  modulator (DSM), which was first invented in the early 1960s and commercially used for audio conversion in the late 80s. These high performance, low-speed data converters (often operating in discrete time) rely on oversampling and feedback to push the quantization noise out of the wanted band, a technique called noise shaping. The DSM contains analog integrators, an internal ADC with one or a few bits in the forward path, and internal DACs in the feedback paths. Although only a few bits are used in the ADC and DAC, the noise shaping enables the DSM to achieve a very high resolution (beyond 12 effective bits) with moderate requirements in component matching. During the last decade, the continuous-time (CT) DSM has been extensively used in high-speed wireless receivers due to speed/power advantages over its discrete-time counterpart and an anti-alias filtering that is included.

On the other hand, the CT DSM is sensitive to delays in the loop. These

delays are to some extent unknown due to process-variations during manufacturing. A loop delay that differs from the nominal case must be taken care of to ensure a robust operating condition and avoid a performance degradation, or even instability of the modulator.

Furthermore, the DSM is sensitive to noise and distortion generated by the first DAC and integrator. These components are therefore highly interesting to analyze and improve, as they limit the performance of the DSM.

This dissertation addresses the above mentioned challenges to implement high performance continuous-time  $\Delta\Sigma$  modulators that convert an analog input into a digital output, for the wireless cellular standard LTE. Moreover, the dissertation studies the concept of *filtering ADCs*, where a channel select filter and ADC are combined into a unit that offers significantly lower requirements on the ADC itself and enables an improved power/performance tradeoff in the radio receiver.

#### 1.2 Research contributions

This section provides a list of the most important research contributions from this doctoral dissertation with the corresponding paper cited.

- Development of the filtering ADC concept, where the channel-select filter and A/D converter (DSM) are merged to provide additional shaping of noise and distortion coming from the DSM. The key benefit of the concept is significantly lower requirements on the DSM, which enables power savings [4,5].

- A model and analysis of the filtering ADC to provide new coefficients that preserve the filter transfer function in presence of the feedback DAC [5].

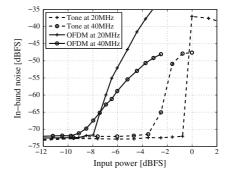

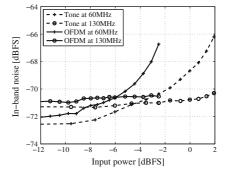

- Two implementations of filtering ADCs (576/288 MHz clock frequency with 18.5/9 MHz bandwidth) for verification of the concept. The measurements include unconventional ADC parameters such as compression point and intermodulation distortion intercept point vs frequency [4, 5]. The second filtering ADC is verified against a blocker specification for LTE Rel. 11 using OFDM modulated blockers [5].

- An analysis of performance degradation due to  $V_{\rm th}$  mismatch in the current-switching pair of the first current-steering DAC in the DSM. The results provide insight of how to improve the linearity of the DAC [1].

- A feedback scheme to: (i) Make the DSM more robust against variations in loop delay. (ii) To omit implementing the otherwise obligatory loop delay compensation path (e.g. an additional DAC and adder) to reduce hardware complexity [2].

1.3 Outline 3

• Model and analysis of the new feedback scheme. The results provide a tool for the designer to evaluate and predict the impact on stability and performance of a modulator that implements the technique [3].

- Implementation and measurement verification of the new feedback scheme in a 7.5 mW, 288 MHz CT DSM with 69 dB SNDR for 9 MHz bandwidth [2]. The overload behavior of the DSM to out-of-band blockers was studied by measurements with OFDM modulated signals [3].

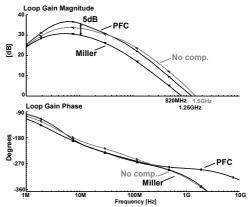

- A frequency compensation technique that boosts the loop gain of the integrator in-band [4].

- Use of a phantom-zero frequency compensation of the last integrator in the loop filter to improve the phase margin without loss in bandwidth, or increase in power consumption [5].

- An AC-coupled push-pull output stage to improve the linearity of the amplifier and deliver a large dynamic current needed to sink high frequency blockers, to improve the power efficiency of the amplifier [4,5].

#### 1.3 Outline

The dissertation provides an introduction to the field, as a base for appreciating the main contributions of the included papers. For more in-depth understanding, the author recommends reading the excellent books of [6–8]. The chapters and papers included in this dissertation are listed below, together with a brief explanation of their contents.

- **Chapter 1** presents a motivation for the dissertation, followed by a list of the research contributions and finally the organization.

- Chapter 2 introduces a radio receiver system and commonly used performance metrics.

- **Chapter 3** describes the architecture level aspects of CT DSMs. Here, the concept of filtering ADCs is introduced, along with a performance comparison to previous work.

- Chapter 4 presents the circuit-level implementation aspects.

- **Chapter 5** gives summaries and conclusions of the included papers along with the author's contribution.

- **Chapter 6** provides a discussion with suggestions for future work.

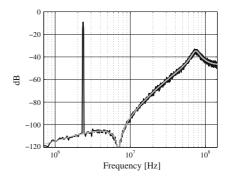

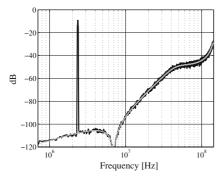

- **Appendix A** contains additional measurement results that were not included in paper V.

- **Appendix B** extends the analysis of the positive feedforward/feedback frequency compensation in paper IV.

- **Paper I** analyses the impact of mismatch in the switching transistors, that are part of a unit-current cell, used in a current-steering feedback DAC.

- **Paper II** presents the implementation and measurements of a DSM that is more robust against variations in loop delay.

- **Paper III** extends paper II with theory of the proposed approach and additional measurements with OFDM signals.

- **Paper IV** presents the implementation and measurements of the first of two filtering ADCs, where a  $2^{\text{nd}}$ -order filter is merged with a  $3^{\text{rd}}$ -order DSM.

- **Paper V** presents the theory, implementation and measurements of the second filtering ADC, that has an improved selectivity and better performance, targeting LTE Rel. 11 [9], 3GPP compliance with support for two contiguous channels (2xLTE20).

## Chapter 2

#### The radio receiver

This chapter describes the radio receiver system and introduces common performance metrics.

#### 2.1 Introduction

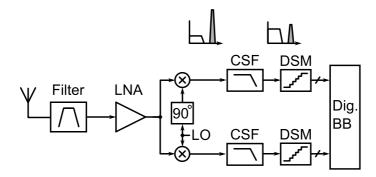

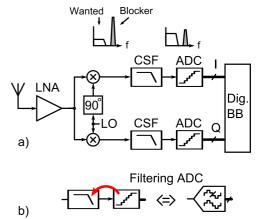

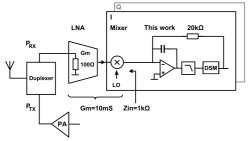

A commonly used radio receiver in wireless communication is the homodyne receiver, also known as zero-IF or direct converting receiver, Fig. 1. The receiver contains an antenna filter, low-noise amplifier (LNA) for amplification, mixers to down-convert the signal from RF frequencies to baseband, channel-select filters (CSFs) and A/D converters (ADCs), the latter shown as  $\Delta\Sigma$  modulators (DSMs). It is also possible to directly feed the RF signal into a bandpass DSM [10] or a DSM with mixers in the feedback loop [11]. The digital baseband after the ADC performs demodulation of the received signal.

The worst sensitivity scenario is when the receiver is far away from the basestation, where the received wanted signal is very weak and a strong interfering signal called a blocker is present, situated outside the channel bandwidth, out-of-band (OOB)<sup>1</sup>. These signals appear at the input of the CSF, after amplification by the LNA and down-conversion to zero-IF by the mixers, as indicated in Fig. 1. The CSF attenuates the strong blocker by its low-pass characteristic, to relax the dynamic range (DR) requirements on the ADC (i.e. the difference between the strongest and weakest signal), which allows fewer bits to be used in the ADC to decrease the power consumption. The attenuation of the blocker allows the filter to amplify the weak wanted signal, without causing clipping at the output of the filter, to relax the noise requirements of the ADC as the input referred ADC noise is reduced by the gain of the filter.

The chosen filter characteristic is a trade off between CSF and ADC complexity, where a higher order CSF leads to a lower power consumption in the ADC, but more power in the CSF. To summarize, there is in principle no re-

<sup>&</sup>lt;sup>1</sup>Since this dissertation concerns ADC design, the term band refers to the desired channel, e.g. in-band noise (IBN) is used instead of in-channel noise (ICN). The term band has a different definition in radio receivers, where a band typically contains several channels.

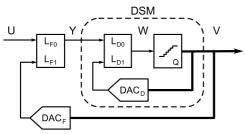

**Figure 1:** The homodyne receiver architecture with cascade of CSF and DSM.

Figure 2: The homodyne receiver architecture with filtering ADC.

quirement to have a filter prior to the ADC, other than to improve the overall power efficiency, or to make the ADC design easier<sup>2</sup>.

The ADC can be merged into the CSF to create a filtering ADC as illustrated in Fig. 2. Since the input signals to the filtering ADC and CSF in Fig. 1 are identical, the requirements in dynamic range for the filtering ADC are similar to those of the CSF. The filtering ADC is briefly described in chapter 3 and more thoroughly in [4,5], with complementary measurement results in Appendix A.

<sup>&</sup>lt;sup>2</sup>In general, an anti-alias filter is needed to avoid folding of high-frequency interferers on top of the wanted signal. However, the CT DSM has implicit anti-alias filtering that may be sufficient to eliminate the filter.

#### 2.2 Characterization of receiver blocks

This section describes the main parameters that are used to characterize the behavior of circuit blocks in receivers. The main parameters are input referred

- Noise

- Compression point (clipping)

- Intermodulation intercept point (linearity)

In essence, the minimum input signal the receiver can detect is determined by the noise of the circuit, while the maximum allowed signal is limited by the ADC clipping level, often set near the supply voltage. In addition, due to limits imposed by receiver linearity, large OOB blockers may degrade the performance by generating intermodulation products that mask the wanted signal.

#### 2.2.1 Input referred representation

In this dissertation, the input referred metrics are used, e.g. input referred 3<sup>rd</sup>-order intercept point (IIP3). The input referred quantity is as usual found by moving a source at the output back to the input by division of the transfer function. Depending on the transfer function, the input referred quantity can be represented as a voltage, current or power. The performance parameters of the filtering ADCs are represented with a voltage quantity due to its voltage-mode interface.

For example, the input referred intermodulation distortion (IM) product or intercept point (IP) is found by referring the IM at the output back to the input via division by the in-band gain (IBG, typically equal to the DC gain) of the filter,

$$IIMn = OIMn - IBG, (1)$$

where all quantities are in dB units.

#### 2.2.2 Noise

The input referred noise sets a lower bound on the required input signal level for the receiver to successfully demodulate the data. The input referred noise is often given in [dBV<sub>rms</sub>] or as a voltage spectral density in [nV/ $\sqrt{\rm Hz}$ ] in baseband circuits with a voltage interface [12, 13].

In the radio receiver, the input referred noise is represented by the noise figure (NF), which is a measure of how much noise the circuit adds to the receiver. The highest noise requirement is at the first stage of the receiver (the LNA), as the input referred noise contribution from the following circuits is diminished by the gain of the preceding blocks. The relationship between noise

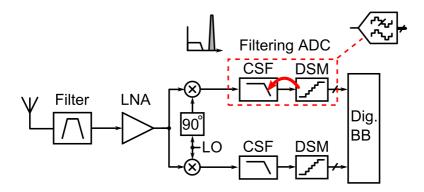

Figure 3: a) Input referred compression point. b)  $3^{rd}$ -order intercept point.

figure and noise factor (F) is NF= $10\log(F)$ , where the noise factor is given by [14,15]

$$F = \frac{N_{tot}}{N_s}. (2)$$

$N_{tot}$  is the total noise power of the receiver including that of the source (e.g.  $N_{tot} = N_{rx} + N_s$ ) and  $N_s$  is the noise solely from the source. In all practical cases, the circuit adds noise, resulting in a NF larger than 0 dB.

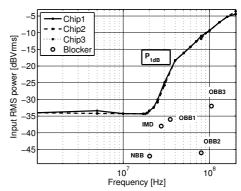

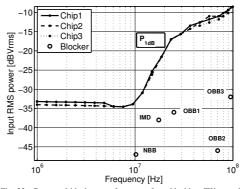

#### 2.2.3 Compression point, $P_{1dB}$ and CP

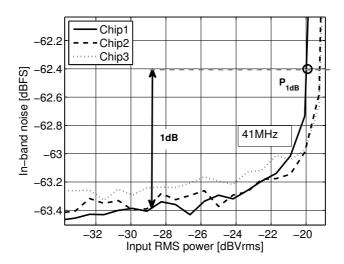

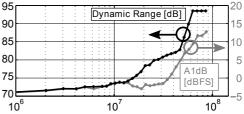

In the filtering ADC, the maximum allowed input signal is characterized by a metric called  $P_{1dB}$ . We have defined  $P_{1dB}$  as the input signal level that yields a 1 dB increase in in-band noise (IBN). The filtering ADC has a  $P_{1dB}$  and dynamic range that improve with increasing frequency, due to the lowpass attenuation of high frequency signals.

In radio front-ends, the compression point (CP) specifies the maximum linear input signal. For small input tones, the input-output characteristic is linear and the amplitude of the fundamental output tone increases linearly with  $1\,\mathrm{dB/dB}$  increase of the input signal, as illustrated in Fig. 3a. The compression point is found where the gain of the fundamental output tone drops by  $1\,\mathrm{dB}$  compared with the extrapolated linear dashed line, and it can be either input referred (ICP) or output referred (OCP).

#### 2.2.4 Intermodulation intercept point

The  $2^{nd}$ - and  $3^{rd}$ -order intercept point, IP2 and IP3 respectively, are commonly used to characterize the linearity of a circuit. When two tones are present at the input with frequencies  $f_1$  and  $f_2$ , a nonlinear circuit exhibits harmonic distortion at integer multiples of  $f_1$  and  $f_2$ , and intermodulation distortion

(IM) at linear combinations for integer multiples of  $f_1$  and  $f_2$  at the output. The second order IM (IM2) is found at  $f_1 - f_2$  and  $f_1 + f_2$ , while IM3 is found at  $2f_1 - f_2$  and  $2f_2 - f_1$ . The IM caused by strong OOB blockers may appear in-band, on top of the wanted signal for certain frequencies of  $f_1$  and  $f_2$ . For example, the IM2 measurements in this dissertation were carried out at various offset frequencies  $f_o$ , with the two tones placed at  $f_1 = f_o + f_{im}/2$  and  $f_2 = f_o - f_{im}/2$ , such that the IM always appears in-band with  $f_{im}=1$  MHz. In general, an OOB blocker with wide bandwidth will due to IM2 generate components in-band that potentially masks the wanted signal.

The amplitude of an IM3 product versus one of the two, equal in power, input tones is sketched in Fig. 3b. The dashed lines show the linearly extrapolated curves of the fundamental tone (1 dB/dB) and the IM3 product (3 dB/dB). The input referred IP3 (IIP3) is the input amplitude where the two extrapolated curves intersect with each other, as indicated by the graph. The benefit of characterizing linearity for a circuit with IP is that the IP is independent of amplitude, while an IM product should be specified together with the corresponding amplitude.

The IP can be extrapolated from a single point instead of using several data points with [12,14]

$$IIP2 = 2P_{in} - IIM2, (3)$$

and

$$IIP3 = \frac{3P_{in} - IIM3}{2} \tag{4}$$

where IIMn is the input referred n-th order IM product and all variables are in dB units (e.g. dBm or dBV<sub>rms</sub>). The equations should be applied in the region where the IM product varies by ndB/dB when calculating IPn.

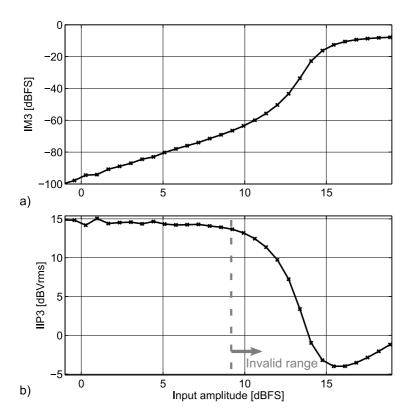

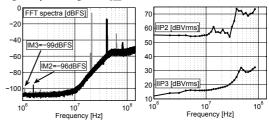

As an example, a two-tone measurement of the circuit in [5] is shown in Fig. 4. For low input amplitudes, the IM3 product follows the expected 3 dB/dB increase, resulting in an extrapolated IIP3 that is essentially constant with amplitude, while the IM3 product rises quickly at large input amplitudes due to higher-order nonlinearities becoming significant as the circuit approaches compression.

**Figure 4:** Measured IIM3 and IIP3 vs input amplitude of [5] for two tones with equal power at 86 and  $43.5\,\mathrm{MHz}$ .  $2\times\mathrm{LTE20}$  mode.

## Chapter 3

## Continuous-time $\Delta\Sigma$ modulators

This chapter starts by defining common terminology used in the context of CT DSMs and then continues with a brief introduction to filtering ADCs including an overview of previous work and performance comparisons. The remaining part of this section describes non-idealities in the feedback DACs of the CT DSM.

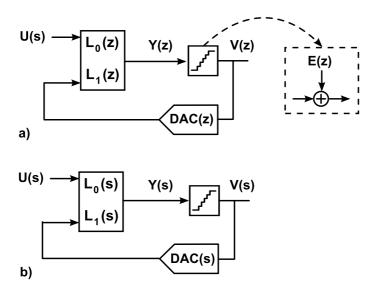

#### 3.1 Introduction

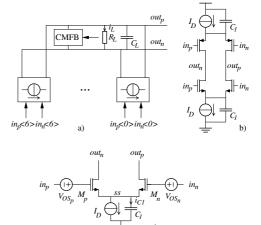

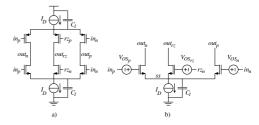

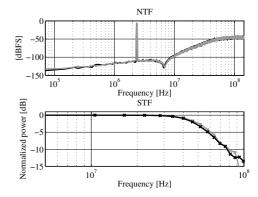

The DSM is a feedback system with a quantizer that operates in discrete-time (DT) on samples. A general DT DSM can be represented with the schematic in Fig. 5a that contains a linear DT loop filter L, an n-bit ADC, and an n-bit feedback DAC. During the last decade, the attention has increased towards DSMs with CT loop filters (Fig. 5b), due to an inherent anti-aliasing, absence of kT/C noise and benefits in speed compared with its DT counterpart [7]. The design of the CT modulator is often based on a DT reference modulator, that for example can be synthesized using Schreiers toolbox in Matlab [16].

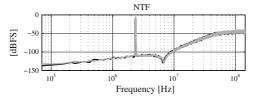

The noise transfer function (NTF) contains the closed loop poles of the DSM, which determines the maximum signal-to-quantization noise ratio (SQNR) and the stability of the DSM. The NTF from quantization noise injected at node Y to the output V of the DSM, assuming a unity quantizer gain, is from linear analysis,

$$NTF(z) = \frac{V(z)}{E(z)} = \frac{1}{1 - L_1(z)}.$$

(5)

The NTF of the DT and CT DSM (Fig. 5a and b, respectively) can be made identical with the impulse invariant transform, to present the same impulse response at the input of the quantizer at the sampling instants. The (time domain) impulse response is the inverse Laplace or Z-domain of the transfer function from the output of the quantizer V back to the input Y. Equivalence between the two systems yields [3,6,17–19],

$$\mathcal{L}^{-1} \{ DAC(s)L1(s) \} |_{t=nT_s} = \mathcal{Z}^{-1} \{ L1(z) \}, \tag{6}$$

**Figure 5:** General representation of a) DT modulator as reference. b) CT modulator.

that enables to find the CT loop filter coefficients in  $L_1(s)$  analytically. Alternatively, the coefficients can be found with numerical impulse response matching [20] for arbitrary DAC waveforms.

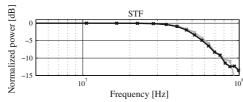

The signal transfer function (STF) from the input signal X to the output V of the DT DSM is

$$STF(z) = \frac{U(z)}{Y(z)} = \frac{L_0(z)}{1 - L_1(z)} = L_0(z)NTF(z).$$

(7)

The STF for the CT DSM is a mixture between CT and DT operation [6,7,21],

$$STF(s) = \frac{L_0(s)}{1 - L_1(z)} = L_0(s)NTF(z)$$

(8)

where  $z = e^{sT_s}$ , with a sampling period  $T_s$ . From this it is clear that even if a direct path exists from U to Y ( $L_0(s) = 1$ ), STF(s) has anti-alias filtering thanks attenuation by NTF(z).

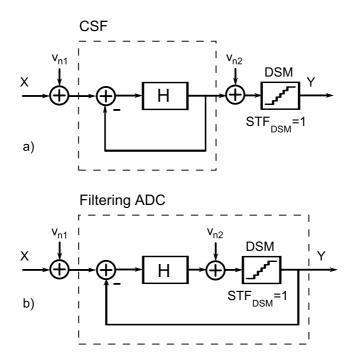

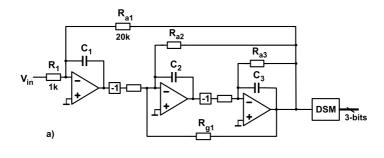

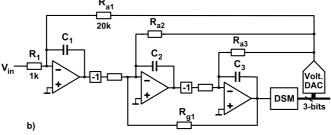

#### 3.2 Basics of filtering ADCs

In this section, the concept of filtering ADCs is very briefly explained, as more details are given in the included papers in this dissertation.

**Figure 6:** Simplified architecture of a) CSF and DSM in cascade. b) Filtering ADC.

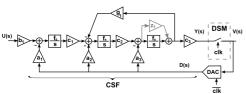

In the filtering ADC, the DSM is incorporated inside the global feedback loop of the CSF, resulting in a suppression of flicker and thermal noise, distortion and quantization noise from the DSM. This is the key benefit compared with having the CSF and DSM in a cascade. The resulting filtering ADCs in this dissertation are equivalent to high-order DSMs [4,5].

This additional noise suppression principally enables three design choices: if both CSF and DSM are kept unchanged, the overall noise and linearity of the analog baseband is improved by the noise suppression. Alternatively, the overall performance can be kept constant and the DSM redesigned with a suitably lower performance to save power. Finally, if the DSM is kept unchanged, the CSF can be redesigned with a higher noise contribution and a lower power consumption. In any case, the filtering ADC provides an improved trade-off between noise and power consumption.

To demonstrate the noise suppression, the CSF-DSM cascade and the filtering ADC are modeled as shown in Fig. 6a and b, respectively. The input referred noise of the CSF and the DSM, are represented with  $V_{n1}$  and  $V_{n2}$ , respectively. The transfer functions from the input X and the noise sources  $V_{n1}, V_{n2}$  to the output Y for the two systems in Fig. 6 are easily found as,

$$Y = \frac{H}{H+1}X + \frac{H}{H+1}V_{n1} + V_{n2} \tag{9}$$

for the CSF-DSM cascade and

$$Y = \frac{H}{H+1}X + \frac{H}{H+1}V_{n1} + \frac{V_{n2}}{H+1}$$

(10)

for the filtering ADC. First note that the filter transfer function from X to Y is the same in both systems as a first order approximation, with  $STF_{DSM}=1$ . More importantly, (10) shows the advantage of the filtering ADC, as the noise source  $V_{n2}$  is suppressed by a factor (H+1) with  $H\gg 1$  in the filtering ADC, while  $V_{n2}$  is directly seen at the output for the CSF-DSM cascade. The noise suppression improves the SNDR of the DSM by 14 dB and 20 dB, respectively, in the included papers [4, 5]. This leads to very relaxed requirements on the DSM and allows for power savings or improved performance in the analog baseband, as previously mentioned.

The ADC is here shown as a DSM, but can in principle be anything from a simple flash ADC to an  $n^{th}$ -order DSM. The main limitation is that an  $STF_{DSM}$  of unity is desired (no attenuation and zero phase shift) in order to preserve the filter transfer function. More details about methods for mitigating deviations from the ideal  $STF_{DSM}$  and design of filtering ADCs is described in [4,5].

### 3.2.1 The term filtering ADC

The term filtering ADC is ill defined, since all lowpass DSMs (both discrete-time and continuous-time) have a loop filter (H) which in general provides some filtering at high frequencies. Traditionally, the DSM is designed with high-frequency poles for the NTF to maximize SQNR, at the expense of reduced filtering for the adjacent channels. While these ADCs present some high-frequency filtering, they do not qualify as filtering ADCs, as they implement no filtering of adjacent channels (sometimes these channels are even amplified). In this dissertation, we define a filtering ADC as a DSM where the positions of some poles have been compromised to yield a specific transfer function, different from the transfer function obtained for a purely SQNR optimized DSM<sup>3</sup>.

#### 3.2.2 Previous work

This section contains an overview of previous work that acknowledge the importance of the OOB STF for low-pass DSMs. In many applications, the OOB

<sup>&</sup>lt;sup>3</sup>The filtering ADCs in this thesis have both the conventional high-frequency poles to provide a sufficiently high SQNR and a few low-frequency poles for channel-select filtering (that provides the additional noise suppression mentioned previously).

STF may not matter, while in wireless communication systems it is of utmost importance due to the typically rather hostile radio environment with strong blockers.

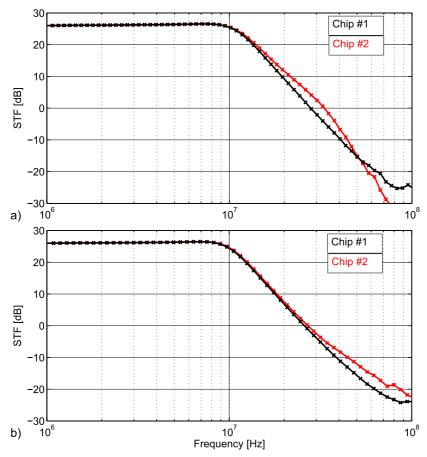

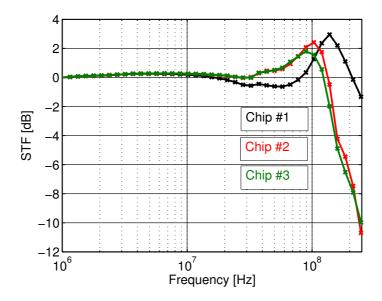

#### NTF and STF trade-offs

It is well-known that CT DSMs with feedback-compensated loop filters (CIFB) can provide a sharp filtering of high-frequency blockers by the proper design of their STF [22, 23]. However, a fundamental issue in a filtering DSM is that its STF and its noise transfer function (NTF) share the same poles [23, 24]; therefore, the more aggressive the filtering, the poorer the NTF in-band quantization-noise shaping. In the filtering ADC of [23,25], this is circumvented by inserting a 1<sup>st</sup>-order low-pass filter in the forward path, while stability is preserved by a corresponding high-pass filter in the feedback path. While this approach provides the necessary filtering, the presence of both a high-pass and a low-pass filter results in an NTF with no net improvement in terms of noise shaping. Furthermore, the complexity of the high-pass filter increases when a higher-order transfer function (TF) is desired.

#### Feed-forward modulators

A vast amount of research has also been devoted to improve control of the STF in feedforward compensated modulators [26–31], which have a favorable power consumption but tend to display a pronounced high-frequency STF overshoot (STF peaking), which is undesirable in applications where large OOB blockers are expected. Starting with [26], a mix between feedback and feedforward modulator is used to achieve lower STF peaking than a feedforward modulator. This structure is used by [24] when blocker levels are low; however, when blockers are present, the DSM adaptively reconfigures the loop-filter based on a blocker detector, to operate as a conventional feedback modulator for improved selectivity.

In [28, 29, 31], a filtering STF is achieved for the feedforward modulator by using negative feed-in paths. These feed-in paths implement signal cancellation, which is sensitive to process variations [28,31]. For improved robustness, [28,30] suggests to omit the feed-in paths, add a second DAC and add a path from the output of the first integrator to the input of the other integrators. With this structure, the lowpass STF of a conventional feedback modulator is achieved, with fewer DACs. Although the design has a peaking free STF with good anti-alias filtering, there is no filtering of adjacent channels next to the wanted band.

The selectivity can be improved with a complex impedance in parallel with the output of the first integrator in the loop filter, to shunt the signal to ground at a specific frequency [32]. This technique is however limited to notching out

| Parameter                    | [5]  | [4]   | [23] | [33]    |

|------------------------------|------|-------|------|---------|

| BW (MHz)                     | 18.5 | 9     | 1    | 6       |

| fs (MHz)                     | 576  | 288   | 64   | 405     |

| SNDR (dB)                    | 56.4 | 68.4  | 59   | 74.6    |

| $f_{-3dB}$ (MHz)             | 25.0 | 16.9  | 3    |         |

| $IRN (nV/\sqrt{Hz})$         | 5.1  | 8.1   | 280* | _       |

| In-band IIP3 $(dBV_{rms})$   | -8.5 | 11.5  | 19*  | _       |

| Tech. (nm)                   | 65   | 65    | 180  | 90      |

| Vdd(V)                       | 1.2  | 1.2   | 1.8  | 1.2-1.8 |

| Power (mW)                   | 7.9  | 11.3  | 2    | 54      |

| DR at BW×4 (dB)              | 82   | 80    | 65   | 90      |

| FOM1 at BW×4 (fJ/conv. step) | 21   | 77    | 700  | 180     |

| FOM2 (fJ)                    | 0.32 | 0.075 | 1.98 | -       |

**Table 1:** Comparison of low-pass filtering ADCs. \*Calculated from data in [25].

certain blockers local in frequency and is not a general remedy for improved selectivity.

#### Improved selectivity and noise shaping

As a further step toward improved selectivity with higher-order noise shaping, the DSM can instead be incorporated into a Rauch filter to create a filtering ADC [33, 34]. The key benefit is that the global feedback loop of the CSF provides a first order noise shaping of the noise from the DSM, to improve the performance and relax the requirements on the DSM itself, compared with a conventional CSF-DSM cascade. The designs presented in this dissertation were obtained in a similar manner; more details are found in [4,5].

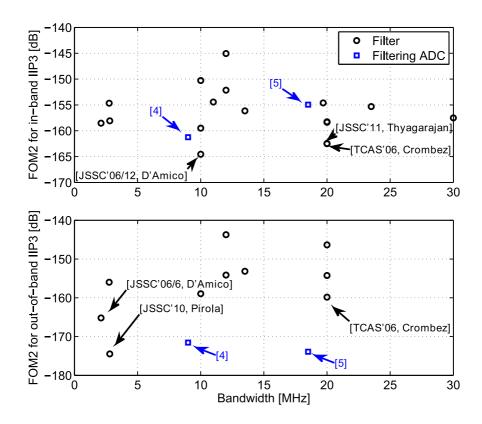

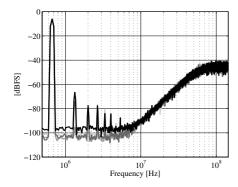

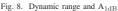

# 3.3 Performance comparison of filtering ADCs

This section presents an overview and performance comparison of filtering ADCs. While a survey of state-of-the-art ADCs can be found in [35], the concept of filtering ADCs is a quite new approach with only a few implementations reported in the literature. These implementations are compared in Table 1 for power efficiency figure-of-merits (FOMs) FOM1 and FOM2, defined in [5]. It is seen that [4,5] achieve state-of-the-art FOMs, where a lower FOM is better.

The FOM1 is calculated based on the OOB performance of the filtering ADC, since it is not fair to base a comparison on the in-band performance, for the following reason. Consider a lowpass filter that is placed in front of an ADC: the filter adds noise, non-linearity and consumes power, which worsens the in-band performance of the overall chain. On the other hand, the filter

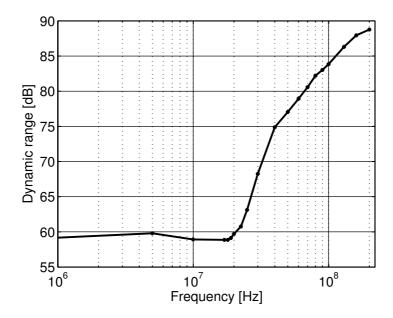

Figure 7: Measured dynamic range (P<sub>1dB</sub>-IBN) for filtering ADC [5].

improves the OOB dynamic range, which is not captured using conventional ADC FOMs that are based on the in-band performance.

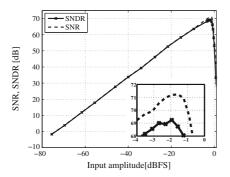

For comparison with Table 1, consider also the example of using a standalone ADC that targets 2xLTE20<sup>4</sup>, connected directly after the RX mixers, with the assumptions on the RF front-end in [5]. The ADC needs a baseband bandwidth of 18.5 MHz and a DR in excess of 85 dB, which is very challenging to implement. Furthermore, these requirements translate into a power consumption beyond 25 mW, assuming the DSM can be implemented with a state-of-the-art FOM of 50 fJ/conv.step and has a frequency independent DR. On the other hand, the frequency dependent DR of the filtering ADC in [5], shown in Fig. 7, is tailored for 2xLTE20 support and exploits the low IB and high OOB DR requirements in the LTE receiver.

### 3.3.1 Comparison with filters

This section compares a stand-alone filter (without ADC) against the filtering ADC, which behaves like a filter with a digital output.

$<sup>^42\</sup>mathrm{xLTE}20$  means that the receiver supports two contiguous LTE channels with  $20\,\mathrm{MHz}$  bandwidth each at RF.

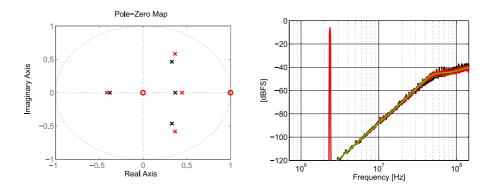

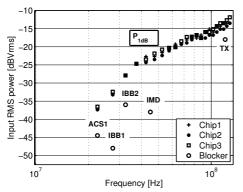

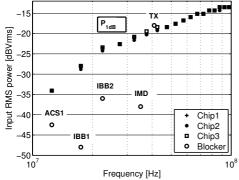

**Figure 8:** State-of-the-art CMOS active filters and the filtering ADCs in [4,5] evaluated for in-band IIP3 (top) and out-of-band IIP3 (bottom).

A performance comparison for state-of-the-art CMOS active filters is shown in Fig. 8, based on a survey by Saari [12] with the recently published filters added. The comparison uses the well-known filter FOM [36] (denoted FOM2 in [4,5]), evaluated for both in-band IIP3 and the maximum OOB IIP3<sup>5</sup>, with the top three filters in both cases highlighted  $[37-41]^6$

It is interesting to note that the power efficiency of the filtering ADC compares well against the filters in in-band performance and exceeds several in

<sup>&</sup>lt;sup>5</sup>The filtering ADCs uses the OOB IIP3 at TX duplex distance, which is the relevant IIP3 test case for FDD systems, although a higher IIP3 was recorded at higher offset frequencies. Furthermore, the offset frequency is not standardized and not reported for all filters. Also note that fewer filters report the OOB IIP3.

<sup>&</sup>lt;sup>6</sup>FOM2 is calculated for the channel BW (band edge), as the 3dB BW contains noise that is removed by the following digital decimation filters.

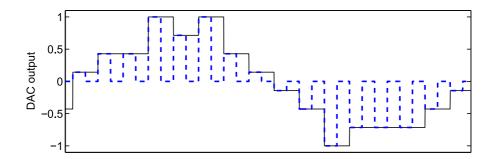

**Figure 9:** Time domain DSM output of an 8-level feedback DAC, normalized to  $V_{\text{ref}}$ , for a sine wave input. Solid black: NRZ DAC. Dashed blue: RZ DAC.

**Figure 10:** Rectangular feedback DAC pulse from  $\alpha$  to  $\beta$ .

OOB performance. Furthermore, the filtering ADC provides both filtering and A/D conversion, which indicates that the A/D conversion is included in a power efficient manner, loosely speaking "for free".

As already mentioned, the filtering ADCs in this dissertation are equivalent to high-order CT DSMs. The following sections describes non-idealities of the feedback DACs in the DSM.

# 3.4 Feedback DAC pulse

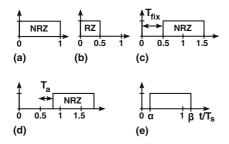

The CT DSM (previously shown in Fig. 5b) is sensitive to the accuracy of the feedback DAC pulse in both time and magnitude. The feedback DACs often use a rectangular non return-to-zero (NRZ) and/or return-to-zero (RZ) pulse, which are illustrated in Fig. 9. There exist also various alternative pulse shapes that reduce the sensitivity to clock jitter, such as the switched capacitor with resistor DAC [20, 42].

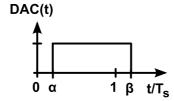

The rectangular DAC pulse is specified with the parameters  $\alpha$  and  $\beta$  as a fraction of the clock period (Fig. 10), where the NRZ pulse has a pulse width

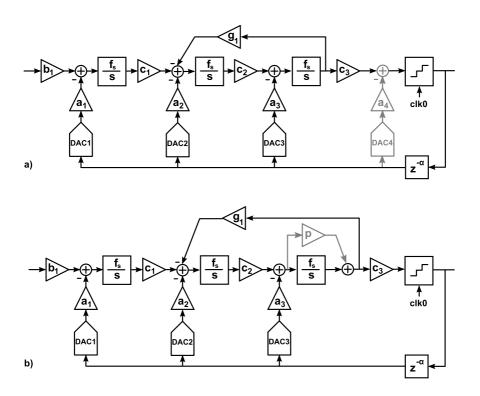

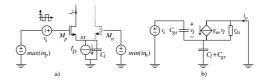

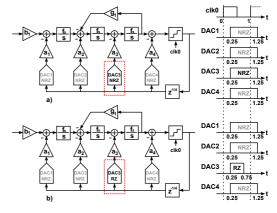

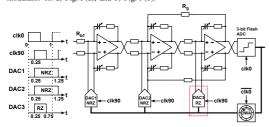

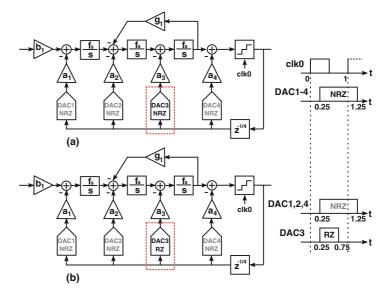

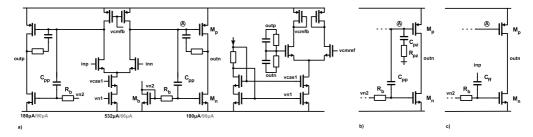

**Figure 11:** Third order CT DSM with CIFB loop filter.  $g_1$  shifts the NTF zeros from DC to in-band with a resonator path. a) DAC4 and  $a_4$  compensate for loop delay. b) p compensates for loop delay.

of  $\beta - \alpha = 1$  and the RZ pulse has  $\beta - \alpha < 1$ , with a transfer function of

$$DAC(s) = \frac{1}{s} \left( e^{-s\alpha T_s} - e^{-s\beta T_s} \right). \tag{11}$$

From this, it is clear that if  $\alpha$  and  $\beta$  vary (the DAC pulse width and position), the NTF of the DSM is affected via the CT impulse response, given by (6). The following sections describe why an intentional delay of  $\alpha$  is commonly used and how the DSM can be made more robust against variations in  $\alpha$ .

## 3.4.1 Fixed loop delay

A conventional third order CT DSM with cascade of integrators feedback (CIFB) [7] loop filter is shown in Fig. 11. A delay of the DAC pulse is known as loop delay and may come from the regeneration time in the flash ADC, delay in the feedback network of for example dynamic element matching circuits [2–5],

internal delays in the DACs, delay in the loop filter due to integrators with finite GBW, and delay in the preamplifiers in the flash ADC. The exact value of these delays are to some extent unknown and affect the impulse response, which can lead to a performance degradation or even instability if not accounted for in the design [18, 43–48].

The uncertainty of the delay from the flash ADC output to the DAC input is often removed by intentionally clocking the DACs with a delayed clock that is a fixed amount of the clock period, to allow the digital signal to settle before rising edge of the DAC clock. The delay  $\alpha$  is modeled by the  $z^{-\alpha}$  element shown in Fig. 11. For the commonly used NRZ pulse, a delay causes the pulse to extend into the next clock period ( $\beta > 1$ ), which in general requires an additional path directly from the output to the input of the flash ADC, to nominally compensate for loop delay. The components for loop delay compensation are  $a_4$ , DAC4, and the adder illustrated in grey in Fig. 11a.

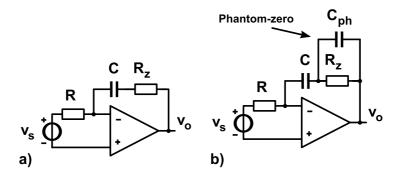

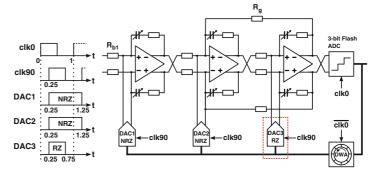

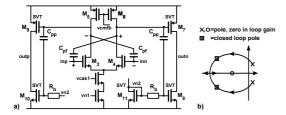

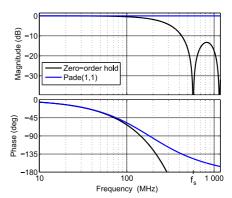

An alternative compensation technique is a PI loop delay compensation [5, 45, 48, 49] shown in Fig. 11b. A proportional path is added to bypass (feed-forward) an integrator in the signal-flow graph to create an LHP zero in the integrator transfer function. The zero is implemented by adding a series resistor with the integrator capacitor, as shown in Section 4.3.3. This technique avoids the additional DAC and adder, and preserves the NTF of the DSM, while the STF is affected by the feedforward path, i.e. a zero appears in  $L_0$  of (8). A summary of the most popular loop delay compensation techniques is presented in [45].

The above methods nominally compensate for the fixed delay caused by intentionally clocking the DACs with a delayed clock. The following section shows how the sensitivity to delay from the DAC, finite integrator GBW, and preamplifier can be reduced.

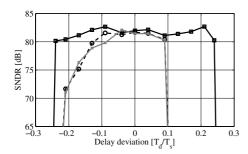

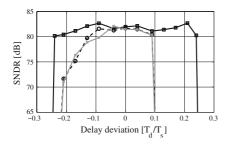

### 3.4.2 Variations in loop delay

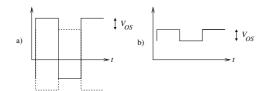

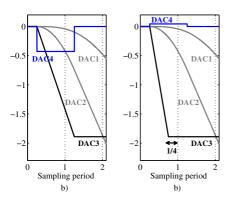

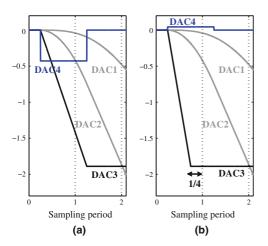

This section graphically illustrates how an RZ pulse that is centered in the clock period can reduce the sensitivity to variations in loop delay.

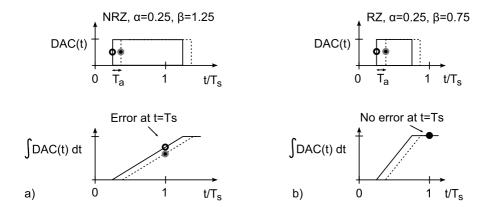

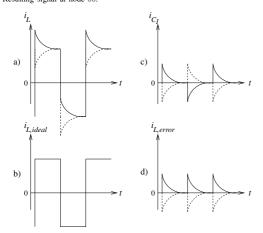

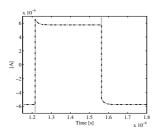

Consider first Fig. 12a where an NRZ pulse with a quarter clock period fixed loop delay,  $\alpha=0.25$ ,  $\beta=1.25$ . The solid line shows the initial position of the NRZ pulse in the time domain and the first order integration of the pulse, i.e. the impulse response of the DAC3 path in Fig. 11. If the pulse is delayed by  $T_a$  as shown by the dashed line, the first sample of the impulse response sees an error, as indicated by the two circles. The error occurs due to the incomplete integration of the pulse, as it extends beyond the first sample into the next clock period.

The same procedure is illustrated with an RZ pulse centered in the clock period ( $\alpha = 0.25$ ,  $\beta = 0.75$ ) in Fig. 12b. In this case, the integration finishes within the sampling period and the two integrals coincide prior to the first

**Figure 12:** Impulse response of path with first order integration, with the DAC pulse in nominal position and delayed by  $T_a$  for a) NRZ pulse. b) RZ pulse.

sample with no error. Consequently, the DSM becomes more robust against variations in loop delay by using an RZ pulse in particular for the inner most loop [2,3]. Another benefit is that the loop delay coefficient  $(a_4$  in Fig. 11) reduces significantly and may even be omitted in the implementation to reduce hardware complexity.

The following section analytically confirms the above mentioned benefits.

#### 3.4.3 z-domain analysis of loop delay variations

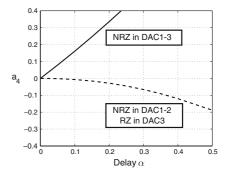

This section provides an extended analysis of the results in [2,3]. It applies the method in [18] to study how the z-domain NTF poles vary with loop delay for the third order DSM in Fig. 11 for three cases: First, the quarter clock period delayed NRZ pulse is used in all DACs, to illustrate that DAC3 has the highest sensitivity to loop delay. Secondly, the sensitivity is reduced with an RZ pulse that is centered in the clock period in DAC3. Thirdly, the NRZ/NRZ/RZ feedback scheme in [2–4], where DAC4 is omitted, is studied.

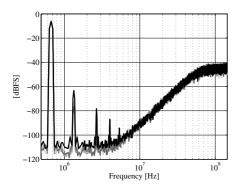

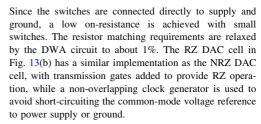

A DT model of the CT DSM is developed to show the pole-zero locations of the NTF and perform fast Matlab simulations with Schreiers toolbox [16]. The DT model was found by transforming the CT loop filter in Fig. 11 into a DT representation with the impulse invariant transform [6, 18, 19, 50], repeated in Table 2 for convenience. The output spectrum (8192-point FFT) for a -6dBFS input tone with 32 times averaging is recorded, together with the pole-zero locations in the NTF.

| _ | pass from a to p. |                                                                                                                                                 |  |  |  |  |  |

|---|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

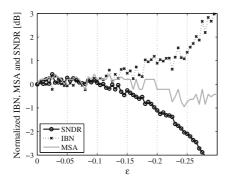

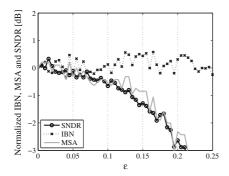

|   | s-domain          | z-domain                                                                                                                                        |  |  |  |  |  |

|   | 1/s               | $\frac{y_0}{z-1}, y_0 = \beta - \alpha$                                                                                                         |  |  |  |  |  |

|   | $1/s^{2}$         | $\frac{y_1z+y_0}{(z-1)^2}$                                                                                                                      |  |  |  |  |  |

|   |                   | $y_1 = \frac{1}{2} (\beta(2-\beta) - \alpha(2-\alpha)), y_0 = \frac{1}{2} (\beta^2 - \alpha^2)$                                                 |  |  |  |  |  |

|   | $1/s^{3}$         | $\frac{y_2 z^2 + y_1 z + y_0}{(z-1)^3}$                                                                                                         |  |  |  |  |  |

|   |                   | $y_2 = \frac{1}{6}(\beta^3 - \alpha^3) - \frac{1}{2}(\beta^2 - \alpha^2) + \frac{1}{2}(\beta - \alpha)$                                         |  |  |  |  |  |

|   |                   | $y_1 = -\frac{1}{3}(\beta^3 - \alpha^3) + \frac{1}{2}(\beta^2 - \alpha^2) + \frac{1}{2}(\beta - \alpha), y_0 = \frac{1}{6}(\beta^3 - \alpha^3)$ |  |  |  |  |  |

**Table 2:** z-domain representation of s-domain integration [50]. Rectangular DAC pulse from  $\alpha$  to  $\beta$ .

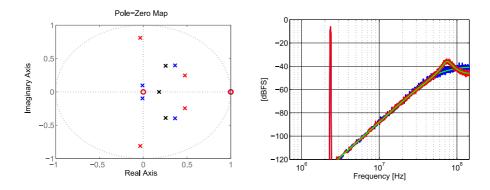

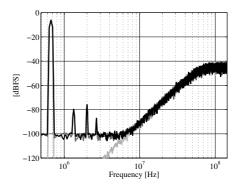

#### DAC with highest sensitivity

For the nominal pulse position in Fig. 13 ( $\alpha = 0.25$ ,  $\beta = 1.25$ ), the three zeroes are located at z = 1 and the three poles are scattered around the origin, as expected. The figure also shows two additional simulations when DAC1 or DAC3 is delayed by  $T_a = 0.1T_s$  from the nominal pulse positions, resulting in an additional pole and zero that increases the order of the DSM. It is clear that DAC3 is much more sensitive to the delay than DAC1, as the poles have shifted by a larger amount and peaking is seen in the output spectrum. It is also seen that the z-domain linear model (in green) shows excellent agreement with the FFT.

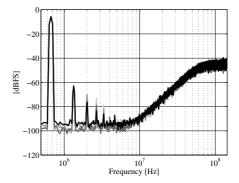

#### Reduced sensitivity

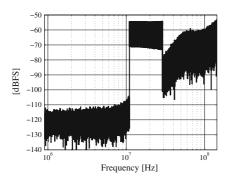

The above analysis was repeated for a CT DSM with an RZ pulse in DAC3, for a nominal case ( $\alpha = 0.25$ ,  $\beta = 0.75$ ) and with all DACs delayed by  $T_a = 0.1T_s$  in Fig. 14. The nominal result is as expected identical to the previous result in Fig. 13, while the poles are much less affected by the additional delay in this case. This illustrates the benefit of using an RZ pulse that is centered in the clock period, in the innermost DAC (DAC3) [2,3].

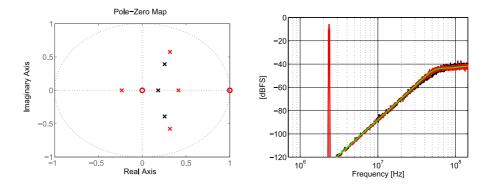

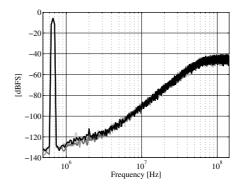

For completeness, the NRZ/NRZ/RZ feedback scheme in [2–4] where DAC4 is omitted, is presented in Fig. 15. Already in the nominal case, the absence of DAC4 increases the order of the DSM, as seen by the left half plane pole and the zero in origin [2,3]. More importantly, also this DSM shows a reduced sensitivity to loop delay variations, as is clear from the pole zero plot and the output spectrum. As a final remark, the poles remain inside the unit circle for  $T_a = \pm 0.25 T_s$ , as expected from the simulations in [2,3].

**Figure 13:** Pole-Zero plot and FFT. NRZ DAC1-4. Black: Nominal case. Blue: DAC1 delayed by  $0.1T_s$ . Red: DAC3 delayed by  $0.1T_s$ .

**Figure 14:** Pole-Zero plot and FFT. NRZ DAC1,2,4; RZ DAC3. Black: Nominal case. Red: All DACs delayed by  $0.1T_s$ .

## 3.4.4 Feedback DAC non-linearity

A critical component in the DSM is the feedback DAC, since its errors are not shaped (contrary to the ADC). The non-linearity of a feedback DAC can be divided into a static and a dynamic non-linearity. The static non-linearity is caused by mismatch in the DAC output levels, often represented by integral non-linearity (INL) and differential non-linearity (DNL) in Nyquist converters [51]. The variability of the output levels comes from mismatch in the unit elements comprising the DAC, e.g. the current sources in a current-mode DAC. The linearity is often improved with a dynamic-element matching (DEM) method, such as data-weighted averaging (DWA) [52].

The dynamic non-linearity occurs at the switching event of the DAC and

**Figure 15:** Pole-Zero plot and FFT. NRZ DAC1,2; RZ DAC3; DAC4 omitted. Black: Nominal case. Red: All DACs delayed by  $0.1T_s$ .

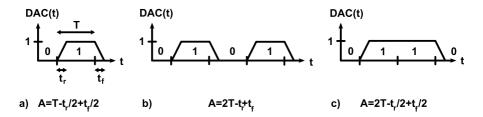

Figure 16: DAC output for code: a) '01'. b) '0101'. c) '0110'.

is therefore problematic for high sampling speeds, or for extreme linearity requirements [53]. To illustrate dynamic non-linearity, a DAC output with the corresponding area (charge) for digital codes '01', '0101' and '0110' is illustrated in Fig. 16a, b and c respectively. In case the rise and fall times differ, the DAC output in Fig. 16b and c are not identical, i.e. the output depends on the previous code. This is known as inter-symbol-interference (ISI), which is a well-known challenge with NRZ feedback DACs. It is clear from the figure that the rise and fall time should be identical to preserve linearity in the DAC [54].

In a differential implementation of the DAC, the output has inherently a symmetric rise and fall time (as a first order approximation), even if the output is constructed by two asymmetric signals [55, 56]. However, it has later been shown that the output of a differential current-steering DAC may be asymmetric, due to second-order effects. For example, the two transistors in the differential switch pair may inject a different amount of charge, or have a  $V_{\rm th}$  mismatch that in combination with a tail capacitor results in an asymmetric pulse [1,57]. This ISI effect, in combination with DWA, results in even order distortion [1,53,57–61].

A common solution to avoid ISI is to use an RZ DAC, at the expense of increased clock jitter sensitivity [6]. The jitter sensitivity can be reduced by implementing an effective NRZ pulse with two RZ pulses within the clock period [62], assuming that the fall time of the first and rise time of the second RZ pulse are derived from the same clock edge. While this approach require twice the clock frequency to generate the RZ pulses, [63] use two parallel signal paths with DWA and a full clock period RZ pulse in an interleaved fashion to implement the effective NRZ pulse.

Recently, a more elegant approach has been presented which mitigate the ISI with an ISI shaping dynamic-element matching [53]. The algorithm turns the static and dynamic non-linearity of the DAC into noise with a mismatch shaping loop and an ISI shaping loop, respectively.

# Chapter 4

# Circuit level considerations

This chapter describes some of the design considerations at circuit level for CT DSMs. The section compares the resistive feedback DAC with the current-steering DAC with respect to output impedance and noise. It also contains an analysis of the active-RC integrator.

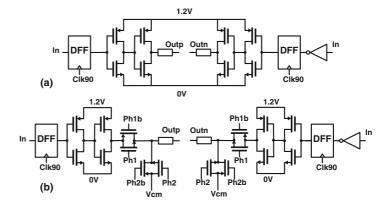

### 4.1 Feedback DAC

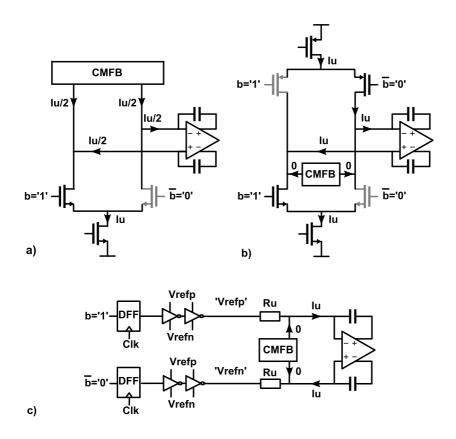

The unit cells of three common NRZ current-mode DACs are shown in Fig. 17. The DACs in Fig. 17a and b are current-steering and contain a constant current source together with switches to direct the unit current  $I_u$  to the branches, depending on the digital code. The complementary resistive DAC in Fig. 17c switches the two resistors to  $V_{refp}/V_{refn}$  and  $V_{refn}/V_{refp}$  for a digital code of '1' and '0', respectively. The DAC has a differential unit current of

$$I_u = \frac{V_{refp} - V_{refn}}{2R_u},\tag{12}$$

where  $R_u$  is the unit resistor value. Assuming that  $V_{refp}$  and  $V_{refn}$  are centered around the common-mode voltage, the current into the CMFB is zero.

The unit current flows according to the figure for a digital input of b='1'. In the two complementary DACs, the complete signal current flows through the integrator, while in the differential DAC, half of the signal current is lost in the CMFB network. Thus, the differential DAC requires twice the unit current to provide the same load current, thereby implementing the same coefficient in the DSM.

#### 4.1.1 Noise

As shown above, the differential DAC in Fig. 17a should have twice the unit current to provide the same current into the load and implement the same feedback coefficient as the complementary DAC in 17b. The noise current at the output of the differential and complementary DAC is the same for the following reason: the PMOS and NMOS current source of the complementary

**Figure 17:** DAC architectures: a) Differential current-steering. b) Complementary current-steering. c) Complementary resistive.

DAC produce a total noise of  $2S_{ID}^{7}$ , while the differential DAC has a single NMOS current source with the same noise,  $2S_{ID}$ , since the unit current is doubled.

The main reason for using a resistive DAC is the lower thermal noise of the DAC itself, compared to a current-steering DAC [2, 3, 64]. This is clearly seen by inspecting the thermal current noise of a resistor and of a MOS current source, which are given by

$$S_{IR} = \frac{4kT}{R_u} = \frac{4kTI_u}{V_u},\tag{13}$$

<sup>&</sup>lt;sup>7</sup>The PMOS and NMOS current source typically produce similar thermal noise, assuming the transconductances are matched to achieve comparable overdrive voltages.

4.1 Feedback DAC 29

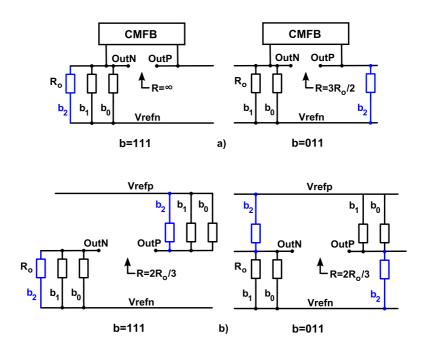

**Figure 18:** Differential output resistance for 2-bit a) differential DAC. b) Complementary DAC.

$$S_{ID} = 4kT\gamma g_m \tag{14}$$

respectively [15].  $I_u$  is the unit current,  $V_u$  the voltage across the unit transistor or resistor,  $g_m$  the transconductance, k is Boltzmann constant, T the absolute temperature, and  $\gamma$  the channel noise factor. The noise is minimized with a small transconductance; however, the smallest transconductance for MOS current source is obtained at the boundary between the triode and active region with  $V_{od} = V_{ds} = V_u$ , resulting in  $g_m = 2I_u/V_u$ , assuming the long-channel equations are valid. The noise of the MOS current source is at least twice that of the resistor for a  $\gamma$  of unity in (14). Typically, the transconductance and noise power becomes 2-4 times larger for the MOS current source than for the resistor, as e.g. a cascode current source further reduces the voltage headroom for the transistor.

## 4.1.2 Output impedance

It is well-known that a signal dependent output impedance of a DAC, together with a non-zero load impedance, results in distortion of the signal [51,65]. For

that reason, the output impedance of the DAC is often boosted with cascode transistors. As an example of signal dependent impedance, the differential output impedance of a 2-bit differential DAC is depicted for the codes b='111' and b='011' in Fig. 18a. As the varying impedance may degrade the performance due to distortion, it is not advisable to use this architecture in a low-impedance resistive DAC.

On the other hand, the complementary DAC in Fig. 18b is more suited for resistive DACs, as it has a constant output impedance with control word, which preserves the linearity although the impedance is low.

Also note that the complementary resistive DAC in Fig. 17c does not require a CMFB circuit. This is easily realized by observing that the DSM provides a short between  $Out_P$  and  $Out_N$  in Fig. 18b (the virtual ground of the integrator), that causes the common-mode to be centered between  $V_{refp}$  and  $V_{refn}$  if the unit resistors are identical.

### 4.2 Flash ADC

The requirements on the flash ADC are low since any errors injected in the ADC such as clock jitter, DC offset, thermal noise, and distortion are shaped by the loop. However, the flash ADC should have a low input capacitance to minimize the capacitive loading and loss in GBW of the last integrator.

Furthermore, the delay from the ADC input to the actual sampling event of the signal introduces a loop delay. This delay should be taken into account to preserve the loop dynamics (position of poles and zeroes in the NTF), by e.g. delaying the ADC clock with the same amount as the delay [30]. In case preamplifiers are used in the comparators, the delay can be reduced with a higher bandwidth in the input stage of the preamplifier.

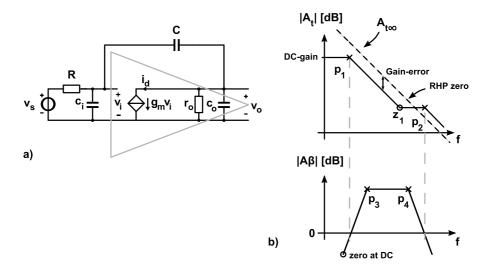

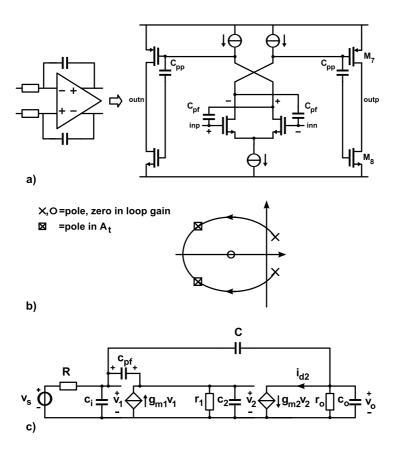

# 4.3 Active-RC Integrators

DSMs often use active-RC integrators with an ideal, closed-loop integrator transfer-function of  $A_{t\infty} = -1/sRC$ , and an actual, non-ideal transfer-function of  $A_t$  which deviates from  $A_{t\infty}$ . This section examines these deviations in  $A_t$  based on a model of the integrator.

The active-RC integrator has an active part and two passives R, C that performs the voltage-to-current conversion and integration, respectively, shown in Fig. 19a. The active part is modelled by a single transconductance  $g_m$ , but may contain multiple, frequency dependent amplifier stages that will add additional poles to the circuit (e.g.  $g_m$  is frequency dependent). The input and output capacitance  $c_i$  and  $c_o$ , and the output resistance  $r_o$ , model the impedances seen at those nodes<sup>8</sup>.

<sup>&</sup>lt;sup>8</sup>For example,  $r_o$  models both the output conductance of the amplifier and the load resistance from the input resistors of the following integrator;  $c_i$  includes the capacitance

Figure 19: a) Active-RC integrator modelled with  $g_m$  and  $r_o$ . b) Sketch of integrator transfer function  $A_t$ , compared against  $A_{t\infty}$  and the loop gain  $A\beta$ .

For a qualitative understanding, the integrator transfer function  $A_t$  is sketched together with the loop gain (described in section 4.3.1) in Fig. 19b. The following unwanted deviations from  $A_{t\infty}$  can be identified due to the finite transconductance:

- Finite DC gain  $(p_1)$

- Gain error at intermediate frequencies

- RHP zero  $(z_1)$

- High-frequency pole  $(p_2)$