### Nanowire Transistors and RF Circuits for Low-Power Applications

Persson, Karl-Magnus

2014

### Link to publication

Citation for published version (APA):

Persson, K.-M. (2014). Nanowire Transistors and RF Circuits for Low-Power Applications. [Doctoral Thesis (compilation), Faculty of Engineering, LTH]. Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## Nanowire Transistors and RF Circuits for Low-Power Applications

Doctoral Thesis Karl-Magnus Z. Persson

Thesis Supervisor:

Professor Lars-Erik Wernersson

Faculty Opponent: Professor Sylvain Bollaert

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden

Academic thesis for the degree of Doctor of Technology at the Faculty of Engineering, Lund University, to be defended on Friday the 14<sup>th</sup> of March, 2014. The defense will take place at 10:00 in room E:1406, found in the E-building, LTH, at Ole Römersväg 3, Lund, Sweden.

# Nanowire Transistors and RF Circuits for Low-Power Applications

Doctoral Thesis Karl-Magnus Z. Persson

Thesis Supervisor:

Professor Lars-Erik Wernersson

Faculty Opponent: Professor Sylvain Bollaert

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden

Lund, Sweden, 2014

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University P. O. Box 118 SE-221 00 Lund Sweden

© Karl-Magnus Persson ISSN 1654-790X ISBN 978-91-7473-809-4 (printed version) ISBN 978-91-7473-810-0 (pdf verison) Printed in Lund, Sweden, by *Tryckeriet i E-huset* February 2014

### Populärvetenskaplig sammanfattning

Surfplattor och mobiltelefoner med prestanda i klass med den hos stationära datorer för bara några år sedan är resultatet av den kontinuerliga hårdsatsning som i över 50 års tid stadigt lyckats göra den minsta elektronikkomponenten, transistorn, mindre, snabbare och mer strömsnål. Under senare år har det dock blivit svårare att förbättra prestandan enbart genom att minska transistorns storlek. För att längre framöver kunna få fortsatta prestandaökningar, som i sin tur kan generera nya och spännande sätt att interagera med elektronik, kan det behövas helt nya tillverkningsmetoder. Framtida transistorer konstruerade med nanotrådar är ett alternativ som kan ge möjlighet att fortsätta öka prestandan samtidigt som energiförbrukningen kraftigt kan minskas. Vi har demonstrerat nanotrådskretsar som opererar vid gigahertz-frekvenser, vilket är unikt då det visar på en högre nivå av funktion än vad som tidigare har publicerats kring nanotrådar. För att förstå hur nanotrådsteknik kan ge framtida fördelar är det nödvändigt att ge en övergripande bakgrund.

En transistor är en elektronisk ledare där flödet mellan två kontakter kan styras av och på från en tredje kontakt kallad styret. Transistorer används till att förstärka t.ex. radiosignaler, som är en analog applikation, alternativt utföra logiska beräkningar med 1:or och 0:or, som är en digital applikation. Mobiltelefonen är ett exempel på en elektronisk apparat som behöver transistorer i kretsar för både analoga och digitala applikationer.

Tidigt i utvecklingen av transistorn kom kisel att vara det halvledarmaterial som framstod som bäst lämpat. Kisel finns i överflöd, vanligen i form av sand, och det har varit relativt enkelt att omvandla denna halvledare till bra elektronledare. Det finns dock andra material som har egenskaper som i vissa avseenden är mer åtråvärda när det kommer till att bygga bra transistorer. Indium Arsenid (InAs), som är en förening av två grundämnen från grupp 3 och 5 i periodiska systemet, har förmågan att kunna transportera elektroner betydligt snabbare än vad som är möjligt i kisel. Detta ger fördelar både när det gäller hur snabbt en transistor kan slå av och på, samt hur mycket energi som förbrukas vid transporten av elektroner. Forskning tyder på att energiförbrukningen hos en transistor skulle kunna minskas med en faktor 10 i jämförelse med kiselteknik, samtidigt som arbetsfrekvensen kan ökas.

Arkitekturen hos en transistor har även den varit relativt konstant sedan den första integrerade kretsen utvecklades. Två kontakter har förbundits med en tvådimensionell (2D) yta, kanalen, som kan ändra motstånd genom att reglera en pålagd spänning på styret. En transistor med en 2D-kanal kallas för planar. Den aggressiva skalningen, för att öka prestandan, har dock lett till att kanalen har blivit väldigt kort i riktningen mellan de strömledande kontakterna, vilket i sin tur gör att fältverkan, inducerad av spänningen på styret, börjar bli otillräcklig. En lösning för att öka kontrollförmågan via styret är att ändra form på kanalen, och att istället för

en planar design konstruera den som en pinne. Styret kan då läggas runtom pinnen och påverka från alla riktningar samtidigt. Detta är idén med en nanotrådstransistor. För att förstå hur strömmen styrs av och på i en nanotrådstransistor kan det var illustrativt att göra en liknelse med ett vattenflöde i en vattenslang. Styret fungerar då som en hand som kan greppa vattenslangen och krama åt alternativt släppa upp. Vid små dimensioner har ett omslutande styre visat sig vara långt mer effektivt än ett styre som endast inducerar ett elektriskt fält från en riktning.

Vi har tillverkat nanotrådstransistorer i InAs som uppvisat mycket bra prestanda. Genom att förfina tillförlitligheten i vår process har vi även kunnat tillverka kretsar bestående av tre stycken sammankopplade nanotrådstransistorer i en mixer design. En mixer används för att konvertera en signal till en högre eller en lägre frekvens och används t.ex. i mobiltelefoner för att skicka och ta emot data. Resultatet tillhör ett av de första rapporterade för nanotrådar med en kretsprestanda som ligger i närheten av gigahertz-området och som därmed närmar sig de frekvenser som är intressanta för att skicka data.

Planära kiseltransistorer kommer troligtvis att finnas kvar en lång tid framöver på grund av den låga tillverkningskostnaden. Med framtida krav på högre dataöverföring kan det dock finnas utrymme för specialiserade utökningar. Intresset från industrin inom området för alternativa tekniker är stort och många av de betydande företagen håller på med utveckling av transistorer som nyttjar nya kanaltyper och andra material än kisel.

### Abstract

The background of this thesis is related to the steadily increasing demand of higher bandwidth and lower power consumption for transmitting data. The work aims at demonstrating how new types of structures, at the nanoscale, combined with what is referred to as exotic materials, can help benefit in electronics by lowering the consumed power, possibly by an order of magnitude, compared to the industry standard, silicon (Si), used today.

Nanowires are semiconductor rods, with two dimensions at the nanoscale, which can be either grown with a bottom-up technique, or etched out with a top-down approach. The research interest concerning nanowires has gradually increasing for over two decades. Today, few have doubts that nanowires represent an attractive alternative, as scaling of planar structures has reached fundamental limits. With the enhanced electrostatics of a surrounding gate, nanowires offer the possibility of continued miniaturization, giving semiconductors a prolonged window of performance improvements.

As a material choice, compound semiconductors with elements from group III and V (III-Vs), such as indium arsenide (InAs), have the possibility to dramatically decrease power consumption. The reason is the inherent electron transport properties of III-Vs, where an electron can travel, in the order of, 10 times faster than in Si. In the projected future, inclusion of III-Vs, as an extension to the Si-CMOS platform, seems almost inevitable, with many of the largest electronics manufacturing companies showing great interest.

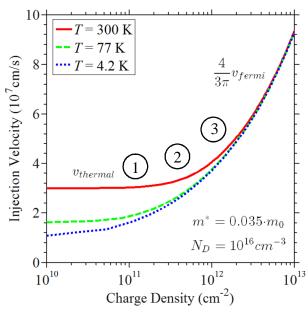

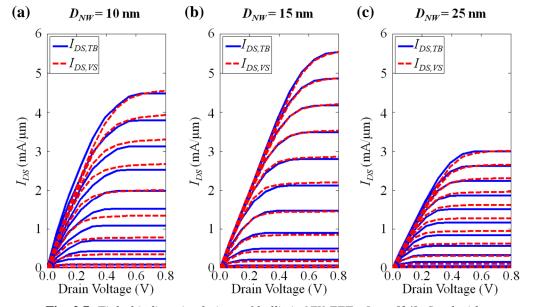

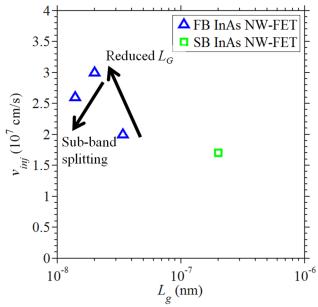

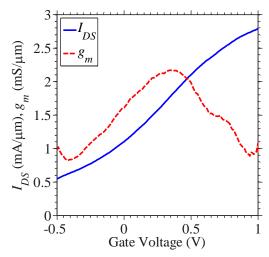

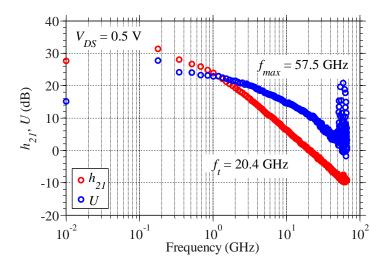

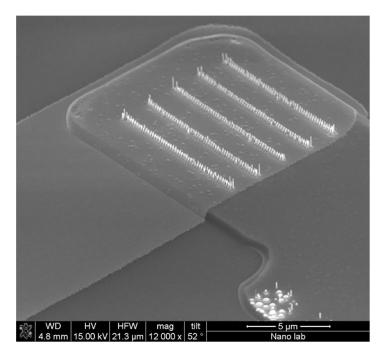

To investigate the technology potential, we have fabricated InAs nanowire metal-oxide-semiconductor field effect transistors (NW-FETs). The performance has been evaluated measuring both RF and DC characteristics. The best devices show a transconductance of 1.36 mS/µm (a device with a single nanowire, normalized to the nanowire circumference) and a maximum unilateral power gain at 57 GHz (for a device with several parallel nanowires), both values at a drive voltage of 0.5 V. The performance metrics are found to be limited by the capacitive load of the contact pads as well as the resistance in the non-gated segments of the nanowires. Using computer models, we have also been able to extract intrinsic transport properties, quantifying the velocity of charge carrier injection, which is the limiting property of semi-ballistic and ballistic devices. The value for our 45-nm-in-diameter nanowires, with 200 nm channel length, is determined to  $1.7 \cdot 10^7$  cm/s, comparable to other state-of-the-art devices at the same channel length.

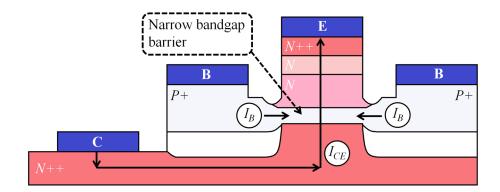

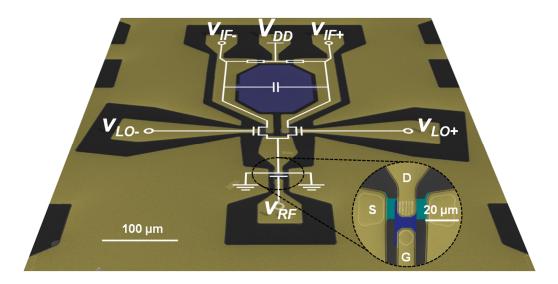

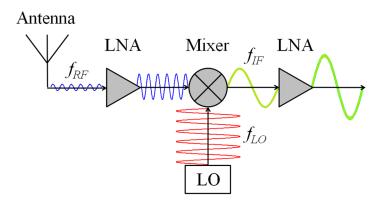

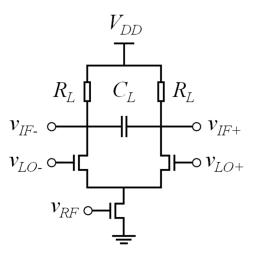

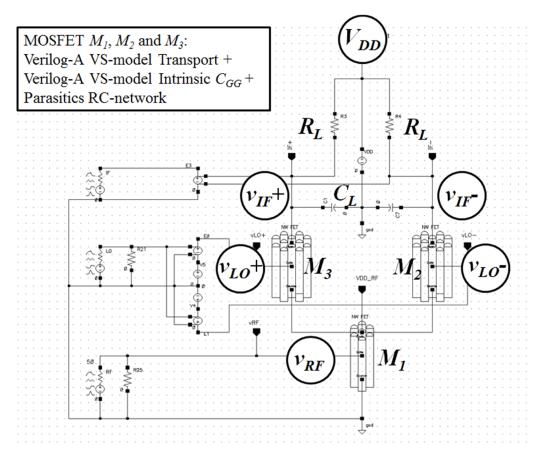

To demonstrate a higher level of functionality, we have connected several NW-FETs in a circuit. The fabricated circuit is a single balanced differential direct conversion mixer and is composed of three stages; transconductance, mixing, and transimpedance. The basic idea of the mixer circuit is that an information signal can either be extracted from or inserted into a carrier wave at a higher frequency than the information wave itself. It is the relative size of the first and the third stage that accounts for the circuit conversion gain. Measured circuits show a voltage

conversion gain of 6 dB and a 3-dB bandwidth of 2 GHz. A conversion mixer is a vital component when building a transceiver, like those found in a cellphone and any other type of radio signal transmitting device.

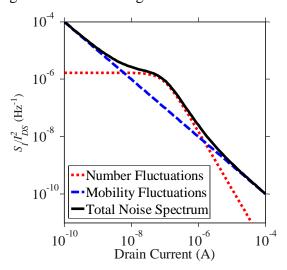

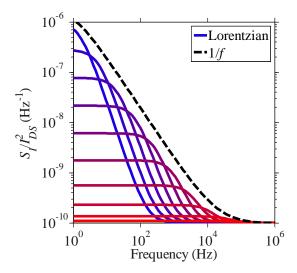

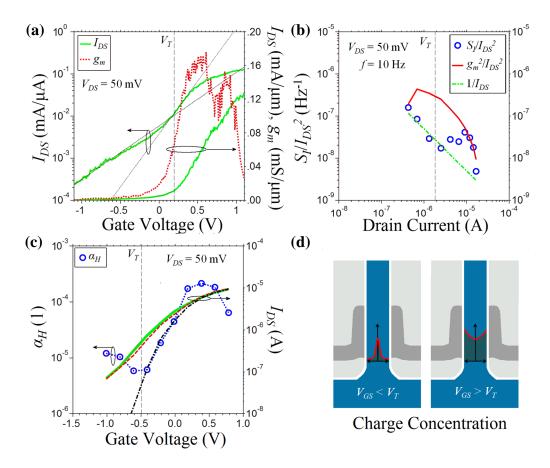

For all types of signals, noise imposes a fundamental limitation on the minimal, distinguishable amplitude. As transistors are scaled down, fewer carriers are involved in charge transport, and the impact of frequency dependent low-frequency noise gets relatively larger. Aiming towards low power applications, it is thus of importance to minimize the amount of transistor generated noise. Included in the thesis are studies of the level and origin of low-frequency 1/f-noise generated in NW-FETs. The measured noise spectral density is comparable to other non-planar devices, including those fabricated in Si. The data suggest that the level of generated noise can be substantially lowered by improving the high-k dielectric film quality and the channel interface. One significant discovery is that the part of the noise originating from the bulk nanowire, identified as mobility fluctuations, is comparably much lower than the measured noise level related to the nanowire surface. This result is promising as mobility fluctuations set the lower limit of what is achievable within a material system.

### **Acknowledgments**

"There are three methods to gaining wisdom. The first is reflection, which is the highest. The second is limitation, which is the easiest. The third is experience, which is the bitterest."

#### - Confucius

I would like to take this opportunity to give a big thanks to all my collaborators for their time invested in me. My first directed appreciation goes to you Lars-Erik for initially believing in me. Lars-Erik has, beyond wide-ranging knowledge of the scientific field, a deep understanding of the world at large. Besides the transferred knowledge, I am grateful for having a source of inspiration. In your role as a leader, you manage to keep the group motivated by being the infectively enthusiastic, and you always seem to have a way to address seemingly harsh problems from a different angle of vision, turning weaknesses into strengths.

Moving on I would like to acknowledge my appreciation of my two assistantsupervisors. When visiting a conference together with Erik Lind, it is made clear that he has made quite an impression in the field, with people sometimes lining up for discussions. Few would question Erik's technical authority as he has developed a sort of unique, intuitive understanding for the non-intuitive. I am grateful for all your teachings.

My other assistant-supervisor is the talented Henrik Sjöland who is not only an authority in his field but also has an astonishing ability to pick up detailed information in other scientific branches and have sense on how it would impact the performance of a circuit. I am grateful for all your input and happy knowing that the nanowire technology has now reached a higher level of maturity where your deep knowledge of circuit-design will become an even greater resource.

Continuing, I would particularly like to thank my PhD-student colleague Martin Berg for all of our collaborations. Together we have fought many battles and although we didn't win all of them, in my book, which this is, we stood triumphant at last. Martin, you are a perfectionist by nature and with a rock-solid patience; your set of skills and ways of approaching problems have been an appreciated complement to mine.

Further, I would like to express my gratitude towards the rest of the group for all the exchange we have had and all the fun moments we have shared. Now, instead of writing short texts on each one of you describing your many talents and skills I will leave it at thanking you for our professional interactions. First I would like to acknowledge Sofia, Anil, Mattias, Jun, Claes, Kristofer, Micke, and Johannes for our collaborations concerning the nanowires. Johannes should also be acknowledged for his kindness of giving extensive feedback on this thesis (together with my supervisors and Sofia); Johannes exceptional eye for detail has significantly improved this thesis. Secondly, I would like to thank Lars, Carl, Anders, Marcus, and Mats, for all the inputs on measurements. Thirdly I would like

to thank Cezar, Elvedin, Jiongjiong, Aein, and Guntrade for knowledge exchange in all the meetings.

I would also like to thank Gunnar Malm at KTH for our collaboration concerning low-frequency noise measurements; I am appreciative of you Gunnar, not only for sharing your recognized expertise, but also for the warm welcome I received in Kista.

Continuing I would like to thank all the people involved in making my thesis work not only possible but in most cases effortless outside the actual scope, and the list is long. From the physics department my special thanks goes to those doing the good job at keeping the Lund Nanolab up and running: Ivan, Mariusz, Anders, Peter, George and Håkan. At Chalmers I would like to thank Vladimir for the help with all the depositions. From the electronics department I would like to thank those who have aided me administratively or with knowhow: Victor, Göran, Peter, Martin, Vince, Molund, Pia, Erik, Bertil, and Josef.

To all the people involved in the study council and the PhD board I would like to give my appreciation for all the important dedicated work, improving the situation for all the peers. During the time I was involved, I enjoyed interesting discussions and learned a great deal.

At last there are many more people, friends and family, of which I am of course especially grateful towards; thank you for being part of my life.

### **Table of Contents**

| Pop  | ulärvet | enskaplig sammanfattning                                       | 1    |

|------|---------|----------------------------------------------------------------|------|

| Abs  | tract   |                                                                | 3    |

| Ack  | nowled  | gments                                                         | 5    |

| Tab  | le of C | ontents                                                        | 7    |

|      |         |                                                                |      |

| List | of Pap  | ers                                                            | 9    |

| 1    | Introd  | uction                                                         | .13  |

| 1.1  |         | tivation –A Diverse Future                                     |      |

| 1.2  |         | Transistor – An Overview                                       |      |

|      |         | Evolvement                                                     |      |

|      | 1.2.2   | The Present and the Near Future.                               |      |

| 1.3  | Fun     | damental Electron Device Transport Mechanics                   |      |

|      | 1.3.1   | Electronic Materials                                           |      |

|      | 1.3.2   | Electronic Transport                                           | . 20 |

|      | 1.3.3   | Charge Control                                                 | . 21 |

|      | 1.3.4   | Scattering.                                                    | . 22 |

| 1.4  | The     | Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) .   |      |

|      | 1.4.1   | The Planar MOSFET                                              |      |

|      | 1.4.2   | A Classical MOSFET Model                                       |      |

|      | 1.4.3   | Velocity Saturation                                            |      |

|      | 1.4.4   | Short-Channel Effects                                          |      |

| 1.5  | CM      | OS                                                             | .33  |

| 2    | Mode    | rn MOSFET Modeling                                             | .35  |

| 2.1  |         | Virtual Source Model                                           |      |

|      | 2.1.1   | A Compact Virtual Source Model                                 | . 39 |

|      | 2.1.2   | Material and Structural Considerations                         | . 40 |

| 2.2  | Stu     | dies of VS Model Application                                   | .45  |

|      | 2.2.1   | Fabricated InAs NW FETs                                        |      |

|      | 2.2.2   | Atomistic Modeled Ballistic InAs NW FET                        | .46  |

|      | 2.2.3   | Data Fitting Evaluation                                        |      |

| 2.3  | Ben     | chmarking                                                      | .48  |

| 3    | High-   | speed Technologies                                             | 49   |

| 3.1  | Tra     | nsistor Metrics                                                | 49   |

| 3.2  | Tecl    | nnology Overview                                               | .52  |

|      | 3.2.1   | The Heterojunction Bipolar Transistor (HBT)                    |      |

|      | 3.2.2   | The High-Electron Mobility Transistor (HEMT)                   | . 54 |

|      | 3.2.3   | The Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) |      |

|      | 3.2.4   | The InAs Nanowire MOSFET (NW-FET)                              | . 56 |

| 3.3        | Benchmarking                                                 | 58        |

|------------|--------------------------------------------------------------|-----------|

| 4          | Noise                                                        | 61        |

| 4.1        | Low-Frequency Noise                                          |           |

|            | 4.1.1 Number Fluctuations                                    |           |

|            | 4.1.2 Mobility Fluctuations                                  |           |

|            | 4.1.3 Measurement of 1/f-noise in InAs nanowire MOSFETs      |           |

|            | 4.1.4 Technology Comparison                                  |           |

| 4.2        | High-Frequency Noise                                         | 67        |

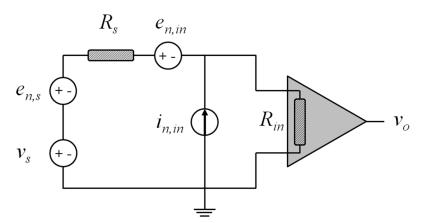

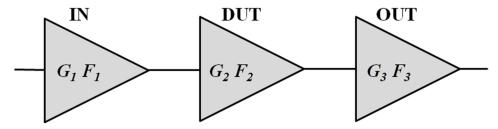

|            | 4.2.1 Noise Figure for an Amplifier Stage                    | 68        |

|            | 4.2.2 Friis Formula                                          | 69        |

| 5          | RF Circuits                                                  | 71        |

| 5.1        | The Mixer Circuit                                            |           |

| 0.1        | 5.1.1 Mixer Noise Figure                                     |           |

|            | 5.1.2 Mixer Simulations                                      |           |

| 5.2        | Benchmark                                                    | 79        |

| 6          | Nanofabrication                                              | <b>Q1</b> |

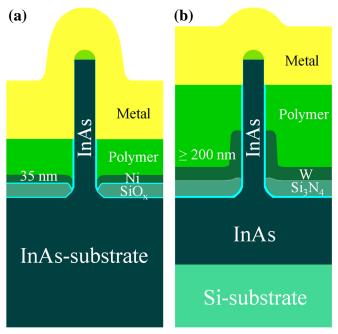

| 6.1        | The Vertical Challenge                                       |           |

| 6.2        | Contact Spacer Formation                                     |           |

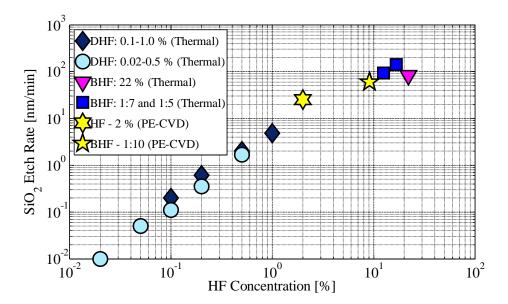

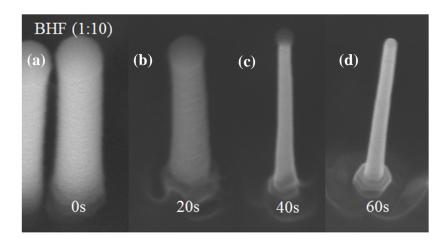

| 0.2        | 6.2.1 Formation of the SiO <sub>2</sub> spacer               |           |

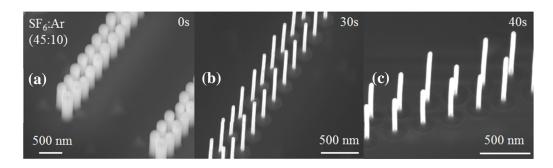

|            | 6.2.2 Formation of the Si <sub>3</sub> N <sub>4</sub> spacer |           |

| 7          | Perspectives                                                 | 89        |

| 7.1        | Technology and Evolution                                     |           |

| 7.2        | Future Possibilities                                         |           |

| 7.3        | At the end of the Road                                       |           |

|            |                                                              |           |

| Ret        | erences                                                      | 93        |

| List       | t of Acronyms                                                | 98        |

| <b>A.1</b> | Electron Transport                                           | 99        |

|            | Mixer Simulations                                            |           |

|            | liography                                                    |           |

|            |                                                              |           |

### **Preface**

I have devoted my last 5 years to investigating the future potential of InAs nanowire field-effect transistor technology as a mean to dramatically decrease power consumption while allowing operation at higher frequencies. As a technology demonstration, we have been able to fabricate a III-V nanowire RF circuit with GHz operation. Other investigations include intrinsic transistor transport metrics extraction and low-frequency noise characterization.

The thesis is built up around two parts where the first is an introduction and overview with seven chapters. Chosen topics from the research are explained in greater detail, and minor unpublished studies related to the thesis are discussed. The second part is the reprinting of published work.

### **List of Papers**

#### **Circuit Performance**

#### I. In As Nanowire MOSFET Differential Active Mixer on Si-substrate

<u>Karl-Magnus Persson</u>, Martin Berg, Henrik Sjöland, Erik Lind, and Lars-Erik Wernersson.

Electronic Letters (submitted)

I co-fabricated the devices, made the DC and RF characterization in collaboration, analyzed the data, and wrote the paper.

### **II. InAs Nanowire MOSFETs Implemented in Active Mixers**

Martin Berg, <u>Karl-Magnus Persson</u>, Erik Lind, Henrik Sjöland, and Lars-Erik Wernersson.

Nano Letters (manuscript)

I co-fabricated the devices, made the DC and RF characterization in collaboration, took part in discussions, and co-edited the paper.

#### **Transistor Metrics**

# III. InAs Nanowire Wrap Gate Transistors With $f_t > 7$ GHz and $f_{max} > 20$ GHz Mikael Egard, Sofia Johansson, Anne-Charlotte Johansson, Karl-Magnus Persson, Anil Dey, Mattias Borg, Claes Thelander, Lars-Erik Wernersson, and Erik Lind *Nano Letters*, **10**, 809-812 (2010)

I co-fabricated the devices and co-edited the paper.

### IV. Extrinsic and Intrinsic Performance of Vertical InAs Nanowire MOSFETs on Si Substrates

<u>Karl-Magnus Persson</u>, Martin Berg, B. Mattias Borg, Jun Wu, Sofia Johansson, Johannes Svensson, Kristofer Jansson, Erik Lind, and Lars-Erik Wernersson *Transcripts on Electron Devices*, IEEE, **60**, 2761-2767 (2013)

I co-fabricated the devices and developed new fabrication procedures, did the DC and RF characterization in collaboration, made the data-analysis, and wrote the paper.

### **Energy Traps and Low Frequency Noise**

### V. Low-Frequency Noise in Vertical InAs Nanowire FETs

<u>Karl-Magnus Persson</u>, Erik Lind, Anil Dey, Claes Thelander, Henrik Sjöland, and Lars-Erik Wernersson

*Electron Device Letters*, IEEE, **31**, 428-430 (2010)

I did the measurements and data-analysis, and wrote the paper.

### VI. A High-Frequency Transconductance Method for Characterization of High-κ Border Traps in III-V MOSFETs

Sofia Johansson, Martin Berg, <u>Karl-Magnus Persson</u> and Erik Lind *Transcripts on Electron Devices*, IEEE, **60**, 776-781 (2012). I co-fabricated the devices and co-edited the paper.

### VII. Surface and core contribution to 1/f-noise in InAs nanowire metal-oxide-semiconductor field-effect transistors

<u>Karl-Magnus Persson</u>, Gunnar B. Malm, and Lars-Erik Wernersson *Applied Physics Letters*, **103**, 033508 (2013)

I co-fabricated the devices, did the measurements in collaboration, made the dataanalysis, and wrote the paper.

### **Additional Papers**

The contest of these papers are either considered to overlap the included papers, or to be peripheral regarding the main topic of this thesis.

### VIII. Fabrication Technology for RF Circuit Implementation of Vertical III-V MOSFETs (oral presentation)

<u>Karl-Magnus Persson</u>, Anil Dey, Erik Lind, Claes Thelander, Henrik Sjöland, and Lars-Erik Wernersson

Swedish System-on-Chip Conference (SSoCC), IEEE, May 4-5 (2009)

### IX. Low-Frequency Noise in Vertical InAs Nanowire FETs with $L_{\rm g}$ =35nm (oral presentation)

<u>Karl-Magnus Persson</u>, Erik Lind, Anil W. Dey, Claes Thelander, Henrik Sjöland, and Lars-Erik Wernersson

*GigaHertz 2010*, Lund, Sweden, March 9-10 (2010)

### X. 35 nm Lg Vertical InAs Nanowire FETs: DC and Noise Performance (oral presentation)

<u>Karl-Magnus Persson</u>, Erik Lind, and Lars-Erik Wernersson *Materials Research Society Conference (MRS)*, San Francisco, CA, USA, April 26-29 (2011)

#### XI. Vad är en bra lärare?

Joakim Bood, Patrik Nyman, <u>Karl-Magnus Persson</u>, Moa Sporre, and Can Xu *Lärande i LTH*, **13**, 3 (2011)

### XII. High-Frequency Performance of Self-Aligned Gate-Last Surface Channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET

Mikael Egard, Lars Ohlsson, Mats Ärlelid, <u>Karl-Magnus Persson</u>, Mattias B. Borg, Fredrik Lenrick, Reine Wallenberg, Erik Lind, and Lars-Erik Wernersson *Electron Device Letters*, IEEE, **33**, 369-371 (2012)

#### XIII. InAs Nanowires for High Frequency Electronics (oral presentation)

<u>Karl-Magnus Persson</u>, Sofia Johansson, Martin Berg, Anil Dey, Kristofer Jansson, Mattias Borg, Johannes Svensson, Claes Thelander, Henrik Sjöland, Lars-Erik Wernersson, and Erik Lind

GigaHertz 2012, Stockholm, Sweden, March 6-7 (2012)

### XIV. Vertical InAs Nanowire MOSFETs with $I_{DS} = 1.34$ mA/ $\mu$ m and $g_m = 1.19$ mS/ $\mu$ m at $V_{DS} = 0.5$ V (oral presentation)

<u>Karl-Magnus Persson</u>, Martin Berg, Mattias Borg, Jun Wu, Henrik Sjöland, Erik Lind and Lars-Erik Wernersson

Device Research Conference (DRC), IEEE, 195-196, University Park, PA, USA, June 18-20 (2012)

### XV. Performance Advantages of III-V on Si Technology for 60 GHz RF Circuits (oral presentation)

<u>Karl-Magnus Persson</u>, Erik Lind, Henrik Sjöland, and Lars-Erik Wernersson Swedish System-on-Chip Conference (SSoCC), IEEE, Ystad, Sweden, March 18 (2013)

### XVI. 1/f-noise in Vertical InAs Nanowire Transistors (oral presentation)

<u>Karl-Magnus Persson</u>, Martin Berg, Erik Lind, Lars-Erik Wernersson *International Conference on Indium Phosphide and Related Materials* (IPRM), IEEE, 1-2, Kobe, Japan, May 19-23 (2013)

### CHAPTER 1

### 1 Introduction

*In all things of nature there is something of the marvelous.*-Aristotle

### 1.1 Motivation –A Diverse Future

The internet is arguably one of the most important inventions of all time. From the coinciding development of the internet and that of digital processors and cellular communication has sprung the continuously growing market for connected mobile computers known as smartphones. A modern smartphone incorporates hundreds of millions of transistors and is as powerful as a desktop computer from the mid-2000s, yet, at much lower power dissipation. Today, a considerable part of the semiconductor industry is driven by the low power mobile sector and yesterday's stationary computer market giants are eager to take part. To lower cost and reduce power consumption, the development has gone from smartphone solutions of many dedicated chips towards few multipurpose chips with different types of electronics made with the same fabrication technology. There is circuitry for digital processing, analog radio signal amplification, transmitting, and receiving, as well as circuitry to convert between analog and digital signals. The semiconductor industry for digital applications has been so successful in cost-effective miniaturization of its Si fabrication technology that it has become the universal fabrication technology for all electronics. In the recent years, however, the Si industry has, from one generation to the next, strayed away from its former rigid path of merely decreasing structure dimensions. The introduction of enhancement boosters, coping with dimensions reaching fundamental limitations, inherently differentiates the industry. Future market demands are in one direction pursuing ultra-low-power circuits with high cost efficiency, and in another, ever increasing operation frequencies within acceptable power restraints. With requirements becoming more diversified, more extensive technology branching is perhaps the unavoidable future where different technologies will target different purposes.

Looking ahead in the market segment for ultra-low power consumption, when fabrication cost and the consumed power of radio circuits can be sufficiently reduced, among other exciting possibilities is the Internet of Things [1]. The Internet of Things aims to connect everything in our lives from the walls of our

house to the milk carton in the supermarket by putting sensors with radio circuits on them. A fully connected world with billions of sensors can for starters give collaborative minimization of waste of resources by reducing energy consumption and food chain spillage.

Non-Si technologies are often referred to as exotic. Commercially available transistors made with compound materials from elements of group III and V (III-Vs), such as those implementing InAs technology, are expensive and exclusively found in applications with extreme requirements of speed. Present technologies for tremendously high-frequency circuits (defined as 300 GHz and above) is based on fast electron transport at the lack of an isolating barrier between the electron channel and the controlling gate, resulting in electrostatics not suitable for further channel reduction below 30 nm. Another aspect is that the integration area is tightly coupled with fabrication cost, and the area size difference between a contemporary tremendously high-frequency technology device and a contemporary digital Si technology device, can be up to a factor of a thousand.

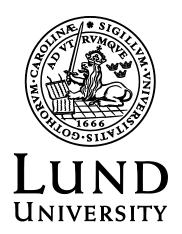

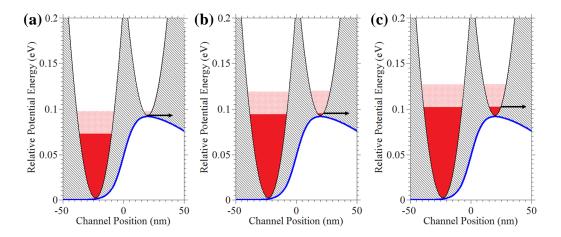

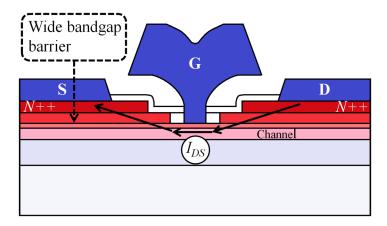

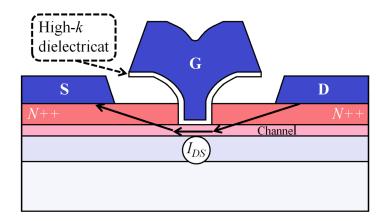

**Fig 1.1.** Schematic comparison of three different MOSFET electrostatic architectures, where the arrows indicate the directions of field control. The blue material is a gate metal, the white material is an isolating dielectric, and the light red material is a semiconductor. The direction of the channel current flow is inwards into the figure. For the three structures, the electrostatic efficiency is increasing going from left to right [2].

Nanowire metal-oxide-semiconductor field-effect transistors (MOSFETs) enable advantageous electrostatic control by asserting a potential on all sides of the channel [2], as shown in Fig. 1.1. With the incorporation of a gate-insulator, effectively functioning as a tall separating energy barrier, the technology offers possibility for high scalability along with low power applications. Vertical integration also decouples area-foot print and channel length thus possibly increasing integration density. Further, bottom-up nanowires, with its large surface to volume ratio, have several possibilities for crystal relaxation, making it viable for integration directly on a substrate with different atom spacing [3], or with the use a thin planar buffer [4]. If InAs nanowire MOSFET (NW-FET) technology could be fabricated on Si wafers alongside its Si counterpart, as a platform extension, it could become attractive not only for ultra-high frequencies, but also for certain low power applications. A first point of large scale application

convergence of different technologies is the broad future market of radio circuits in mobile devices in the non-licensed frequency band at around 60 GHz, a worldwide standard for high bitrate and short distance communication.

### 1.2 The Transistor – An Overview

The transistor is the fundamental building-block in electronic circuits that offer the possibility of logic computations and radio communication. The transistor is a device with three essential terminals where one is used to switch the conduction between the other two, on and off. For a computational circuit, the ability to have distinct conduction levels, enabling the digital representation of 1 and 0, is fundamental. For an analog radio circuit, the ability to selectively amplify a specific input signal is a key ability. A circuit can be assembled with discrete components, where transistors and passive elements (resistors, capacitors, and inductors) are linked together by metal stripes. For circuits with physically large components, such as protective power relay capacitors, this is common. However, when it comes to logic or radio circuits or more than a handful of not necessarily large components, integrated circuits are the preferred choice for reasons of practicality and cost. The fabrication of integrated circuit chips is very complicated with processing steps up to thousands and with fabrication facilities, by any measure, very expensive to setup. The main reasons integrated chips can still be bought at a relatively low cost are high integration density and mass production.

#### 1.2.1 Evolvement

Although there are transistors incorporating mechanical switching, most transistors rely on switching merely with the movement of charge. In fact, any material that can be made to have semiconductor-like behavior can in principal be made into a transistor; for example, organic transistors are a growing research field [5]. The vast majority of transistors found in computers and cellphones, however, are based on just one element; Si. The fabrication of integrated Si transistors has been refined since its introduction under the workings of a process called scaling. Scaling is where the dimensions of a structure are miniaturized while keeping function intact. For transistors this means that the electrical field strength should be kept constant when shrinking the thickness of a constituent slab. The implication is that the applied voltage across the slab can be decreased proportionally. The gains of scaling include increased number of transistors in the same area, lowering of power consumption, and faster switching speed. In a paper from 1965, written by Gordon Moore [6], co-founder of Intel Corporation, it was stated that from an observation of the 7 years since the invention of the integrated circuit, it seemed as if the number of transistors per unit area doubled every two years. This statement is referred to as Moore's law and became a self-fulfilling prophecy for the industry. Moore's law has now been valid for over 50 years and as a result, device

dimensions of modern transistors can be measured in sub-hundred atoms across, with some layer thicknesses down to just a few monolayers. In fact, if scaling could continue, without the laws of physics setting a limit, the entire transistor would be made up of just a single Si atom in the year 2033. Understandably, other approaches than scaling have to be applied to continue enhancing performance; the trick is that whatever technology the future holds, it can only reach market appeal if it is cost effective in its niche of possible applications.

#### 1.2.2 The Present and the Near Future

The latest transistor node is currently down to 22 nm meaning that within 100 mm<sup>2</sup> of chip area, it would be possible to fit up to 200 billion transistors. The actual transistor density on a chip is, however, nowhere near as dense as the theoretical maximum and is instead closer to 1% or less, mostly due to all sorts of interconnects. The largest commercial chips to date, measured in transistor count, have roughly 7 billion transistors at an area of around 500 mm<sup>2</sup> [7]. That number can be compared to the number of neurons in the human brain, around 100 billion [8]. Transistor density is also limited by the generated heat; there is an upper limit to how much heat that can be dissipated per unit area. The result of hitting the roof of heat dissipation about a decade ago is that instead of going for faster switching speeds for each generation, the gain of scaling has been taken out in pure power efficiency. Consumers might have noticed that computer processors have been operating at about the same frequency for several years and instead, increased performance comes from an increased number of computational units, often referred to as cores. Depending on the level of parallelization of a computer task, more or less cores are simultaneously active. With steadily increasing number of transistors and with many computer tasks needing only one or a few cores under a limited period of time, each transistor is spending more time in the off-state. A turned-off transistor is, however, not fully off due to thermally assisted conduction and thus it has a constant leakage. The leakage in the off-state causes sub-threshold power dissipation, which is increasing in proportion to the active power dissipation, and could eventually surpass the average energy consumed in the active mode. Concern over off-currents has fueled the research of so called steep slope devices, aiming to reduce the current in the off-state. Since about 7 years back, the industry has not only officially welcomed incorporation of structural and material novelties, but it has been required to make the transition from one generation to the next. Some enhancements, such as future steep slope devices may, however, not be desirable for high-end RF circuits if the on-performance cannot be substantially improved [9], and could eventually lead to platform extensions of specialized RF fabrication technologies.

## 1.3 Fundamental Electron Device Transport Mechanics

In electronic devices, electrons and holes are responsible for carrying a flow of charge, a current, and they are called carriers. Holes are in reality the absence of electrons but can still be treated as particles very similar to electrons, although with opposite charge. One profound scientific discovery was that all particles are dualistic in nature; their behavior shows characteristics of both a classical Newtonian object and a wave. For particles of matter, the relation derived by de Broglie links together particle momentum and corresponding wave length,

$$\bar{\lambda} = \frac{h}{p},\tag{1.1}$$

where  $\bar{\lambda}$  is the de Broglie wavelength, h is the Planck's constant, and p is the particle momentum [10]. Besides being one of the foundations of quantum mechanics,  $\bar{\lambda}$  indicates the distance at which wave properties have a significant influence on the particle behavior. For a traveling electron or hole in a condensed matter, atomic distances are within the electron's de Broglie wavelength and hence, wave properties will determine how a carrier "perceives" its surroundings. The wavenumber, k, reciprocal to  $\bar{\lambda}$ , determines the direction of the spatial sinusoidal wave of an electron,  $\Psi$ . In one dimension,  $\Psi$  can be written as  $\exp(ikx)$ . Using Bloch's theorem, the solution of the Schrödinger's equation (see Eq. A1) in a lattice of atoms can be written as a periodic function U:

$$\Psi(x) = \exp(ikx)U(k,x). \tag{1.2}$$

In solid state physics, Eq. 1.2 is essential for energy band theory and constitutes the basics for electronic transport in semiconductors. The following sections will describe the movement of electrons in a more qualitative fashion.

#### 1.3.1 Electronic Materials

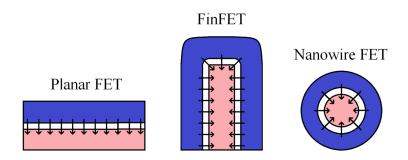

Quantum mechanics can describe electron transitions between different atomic orbitals. One significant property is that allowed orbitals are found at certain electron-nucleus binding energies, specific for each chemical element. If a material is structured in periodic lattices, in crystalline form, the description of the possible energy states of an electron can be expanded to the form of bands, stretching through-out the crystal. Knowing the energy of the electron, it is thus possible to calculate inter atom displacement. An atomic unit cell, with which the periodical structure of a crystal can be described, is illustrated in Fig. 1.2a. It is the interactions of the atomic orbitals that generate continuous bands of energy states, distributed at different energy depths. Between bands of allowed energy states there

are gaps of non-allowed energy states. For a crystal lattice with 2 or 3 dimensions being significantly larger than  $\bar{\lambda}$ , the bands of allowed states typically overlap and all energies, except a single material specific gap between the bound and the free states, are accessible.

**Fig 1.2.** (a) Atoms placed in a periodic lattice. The movement of electrons can be modelled using bands of accessible states, originating from periodic atomic orbitals. (b) Semiconductor band energy diagram displaying the valance band edge,  $E_V$ , and the conduction band edge,  $E_C$ , separated by the energy gap,  $E_G$ . The Fermi level of the material,  $E_F$ , is here situated in the middle of the gap.

Atoms in covalent crystals, in contrast to ionic crystals known as salts, are held together by sharing the outer electrons, where neighboring atoms have shared orbitals. Any atom with an excess outer electron not used for binding with a nearby atom, contributes with a free electron, instead bound to the entire crystal. The opposite is likewise true for an atom lacking an outer electron to share, where this atom instead binds a borrowed electron and thereby contributes with a free hole carrier. In metals, all atoms have loosely bound valence electrons, one or two, and these gather in a shared mobile cloud, hence the concentration of free carriers is in the same order as the concentration of atoms. In isolators, on the other hand, valence electrons are so tightly bound to the atoms that the work needed to free an electron corresponds to several volts, and practically no atoms contribute towards a common carrier population. In between metals and isolators, there are the semiconductors. Semiconductors are characterized by that they can be manipulated to be either conductive or isolating; when looking at the band diagram of a semiconductor, there are bands of allowed energy states divided by a gap of nonallowed energy states. The two sides of the gap correspond to the valance band and the conduction band, respectively. A carrier can either occupy an energy state where it is bound to an atom, in the valance band, or it can be in a conducting energy state where it can travel freely, in the conduction band. When referring to the associated energy state of a carrier, it is in terms of probability as exact energy

and position cannot be simultaneously determined (due to Heisenberg's uncertainty principle). It is, in fact, desirable to leave out the particles altogether and focus on the probabilities of the possible energy states, whether or not they are occupied. To do this, statistical mechanics with a concept of a chemical potential referred to as the Fermi level is introduced. The Fermi level is the corresponding energy depth where there is an equal probability to find an energy state to be occupied and nonoccupied, respectively. In a pure semiconductor crystal, called an intrinsic material, the Fermi level is situated roughly in the middle of the energy band gap,  $E_G$ , and this is illustrated in Fig. 1.2b. There are no energy states in the energy gap but the likelihood of finding a state to be occupied above the Fermi level is decreasing exponentially with increasing energy and if the distance between the Fermi level and the conduction band edge is large, there are hardly any free carriers. Similarly, at a decreasing energy depth, the probability of finding a state to be occupied goes exponentially towards one at the valance band edge. The likelihood n(E) of finding an occupied state at the energy level of E is described by the Fermi-Dirac distribution:

$$n(E) = \frac{1}{1 + \exp(\frac{E - E_F}{q \varphi_T})}.$$

(1.3)

In Eq. 1.3,  $E_F$  is the Fermi level energy, q is the fundamental charge corresponding to that held by one single electron, and  $\varphi_T$  is the thermal voltage,  $\varphi_T = k_B T/q$ . T is the temperature and  $k_B$  is the Boltzmann's constant. One important aspect of semiconductors is that position of the Fermi level is not fixed but can be moved up or down with the introduction of doping. Doping is the insertion of atoms with more or fewer outer electrons than the inherent crystal atoms. An increase in doping concentration raises the Fermi energy and will move the Fermi level closer to either the conduction band edge, or the valance band edge, depending on doping type. When the Fermi level crosses either of the two band edges, the conductivity becomes linear in respect to the applied acceleration voltage, similar to the conduction in a metal. It is often desirable to have highly doped semiconductor regions when forming a contact to a metal, not to create a barrier in between. A semiconductor-metal junction without a barrier is referred to as an Ohmic contact while a junction with a barrier is called a Schottky contact.

If the dopant atoms contribute with electrons, the material is referred to as n-doped. For contribution of holes, the material is instead called p-doped. The doping level can be written as N, N-, N+, N++, etc., where the + and – signs indicate a two decade range, orders of magnitude higher or lower than N, which ranges between  $10^{14}$ - $10^{15}$  cm<sup>-3</sup>. Modern electronics fabrication implements high precision doping control able to make not only sharp and distinct regions of high carrier concentrations but also graded doping profiles where the doping concentration is gradually increased along a certain axis.

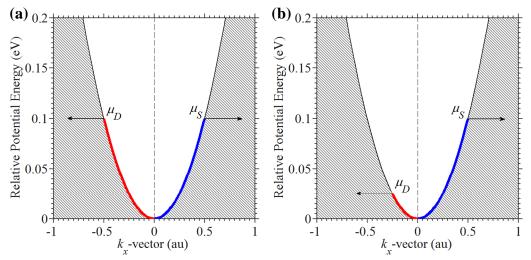

**Fig 1.3.** The energy-distribution of electrons as function of  $k_x$ -vector in an arbitrary point along the x-direction in a crystal lattice. The available states are occupied up to the corresponding level of the potentials  $\mu_S$  (blue) and  $\mu_D$  (red) found at left and right of the spatial point, respectively. (a)  $\mu_S$  and  $\mu_D$  are equal and the average directional transport along the x-direction is zero. This would correspond to a flat conduction band as shown in Fig. 1.2b. (b)  $\mu_S$  is larger than  $\mu_D$  and the average directional transport is larger than zero in the positive x-direction. This would correspond to a tilted conduction band.

### 1.3.2 Electronic Transport

Going back to the electron wave behavior, carriers do not only interact with surrounding atoms but may also interact with each other. For non-metals, however, the concentration of carriers being at least several magnitudes lower than the atomic concentration, it is low enough that the average distance between carriers is much longer than the de Broglie wavelength, and wave interactions can thus be disregarded. The entirety of carriers in a semiconductor is often referred to as a classical gas, as it can be treated with the same classical physics as a gas found elsewhere, such as in in the atmosphere, although with the difference that the gas of carriers is "trapped" in a crystal with allowed and non-allowed energies. A gas is called degenerate if the accessible energy states are filled according to the lowest energy configuration, where the possibility of spin up and down allows for two electrons at each energy state. A gas is fully degenerate at zero temperature, where all accessible states up to the Fermi level are occupied and none above. At a higher temperature, as described by Eq. 1.3, some states above the Fermi level are going to be filled as well, relative to the temperature. Carriers found in a state above the Fermi level are called non-degenerate. Non-degenerate carriers have an energy corresponding to the available thermal energy, while carriers at or below the Fermi level have an associated maximum energy corresponding to the Fermi energy (more on one of the implications in section 2.1).

Modern electronic devices are transitioning to confinements in two dimensions, meaning that the possibility for a carrier to move freely is only available one direction. Confinements affect the bending of the energy bands and will impact carrier transport. A nanowire, if thin enough, can be seen as a 1dimensional (1-D) object and this will have substantial effects on its conductivity. Taking into consideration the effects of structural confinements, such as nonoverlapping energy sub-bands, the transport in an approximately non-confined direction can still be calculated with the use of classical physics. Under the assumption of a travel direction greatly exceeding  $\bar{\lambda}$ , the movement of electrons and holes is attributed to processes called drift and diffusion. Surrounding thermal energy constantly provide carriers with a finite energy, elevating their associated energy state. Diffusion is a process where a carrier is relocating at random, which at a many-particle scale effectively counteracts any carrier concentration gradients. Drift on the other hand, is a transport process where a carrier is accelerated by a potential gradient, seen as a tilt in the energy band structure. The tilt can be induced by a difference in doping, or a heterojunction, where materials with different bandstructure are combined. A tilt can also be achieved by an externally applied field. The energy distribution of states as function of k-vector is shown in Fig. 1.3a and Fig. 1.3b for a crystal with and without an applied external field, respectively. In the case of an isolated semiconductor slab with a flat band structure, the net flow of current, measured over long enough time, will be zero as there will be equal amount of carriers traveling in both directions, and is referred to as equilibrium state. If, however, there is an applied potential difference, the band structure is going to be tilted and carriers will be less likely to diffuse in the direction of higher potential as it requires a larger thermal elevation. Unsurprisingly, it turns out that the requirement for a steady-state current flow is an external injection of carriers.

### 1.3.3 Charge Control

For semiconductor electrical devices, current control is achieved by direct or indirect applied voltages. In a charge based transistor, a controllable potential barrier is used to turn current flow on and off. Diffusive conduction (thermally fueled) will limit the steepness in turning a device off with an exponential dependence to the barrier height. The bipolar transistor, a device that is similar to two merged diodes, is constructed in a way that the diffusion process is the governing mechanism in all of its operation modes. The other, more common type of transistor device, the field effect transistor (FET), instead relies on drift conduction and carrier acceleration with the use of an applied field. The band diagrams of a FET for two different biases are shown in Fig. 1.4a and Fig. 1.4b. For the description of drift conduction, a parameter named mobility is introduced. Mobility relates to the average velocity of a carrier in relation the electric field strength and is dependent on the effective carrier mass. The effective mass is a complex theoretical construction related to the material energy band structure. To make a simplified explanation, the effective mass is an equivalent mass of the

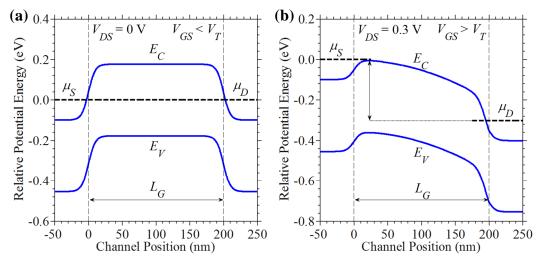

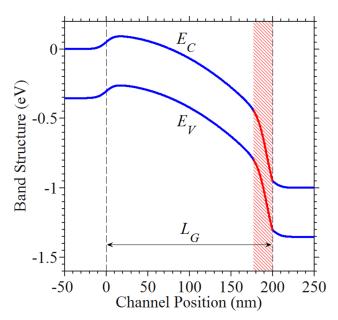

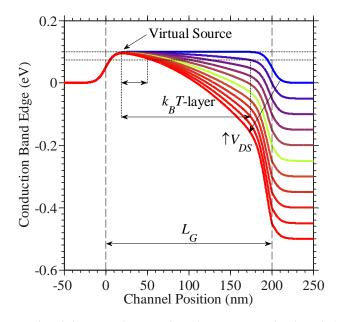

**Fig 1.4.** (a) Band energy diagram of a FET with the channel contact potentials,  $\mu_S$  and  $\mu_D$ , levelled, and with a barrier in between with a height above the contact potentials.  $L_G$  is the channel length, here corresponding to 200 nm. (b) Band energy diagram of a FET with the contact potentials shifted by an applied drain-source voltage,  $V_{DS}$ .

spread-out of a wave of a carrier, making it possible to calculate the transport of a wave as if it was a particle. The lower the effective mass, the less acceleration field strength is needed to reach a certain average velocity and the higher the mobility. Different semiconductors have different associated mobilities; bulk InAs has an electron mobility above  $20,000 \text{ cm}^2/\text{Vs}$  while, in contrast, the value for bulk Si is around  $1,400 \text{ cm}^2/\text{Vs}$ , meaning that it is, in theory, possible to transport an electron in a slab of InAs, at the same velocity, with less than 1/10 of the field-strength and 1/100 of the power ( $P \sim V^2$ ) used for an electron in a slab of Si. This has long been the underlying motivation for low effective mass III-V transistors.

### 1.3.4 **Scattering**

For modern transistors, drift and diffusion is no longer sufficient to describe the transport characteristics since the channel is so short that the approximation of an infinitely long channel is no longer accurate. In a deeper analysis of drift conduction, transport consists of a series of accelerations and collisions, as shown in Fig. 1.5. The average distance between collisions is called mean free path,  $\lambda_{mp}$ . In the acceleration phase of the transport, the carrier undergoes a ballistic trajectile. Ballistic carrier transport well below a relativistic speed (the case in an electronic device) will follow the same principles as a much larger Newtonian projectile, like a cannon ball. One difference is that while a cannonball, after being shot out of the cannon, faces deceleration due to drag resistance, a carrier may instead be accelerated if it is traveling in an electrical field. Secondly, at the atomic scale, gravity is relatively a very weak force and so it is disregarded. Thirdly, a carrier

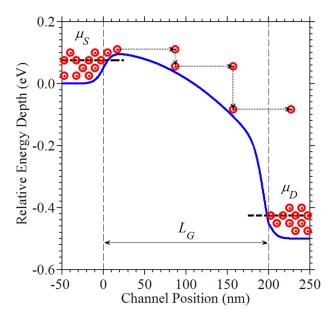

Fig 1.5. The diagram shows the relative energy depth of the conduction band of a FET. The different contact potentials,  $\mu_S$  and  $\mu_D$ , are biased at different levels and separated by a barrier that constitutes the lower doped channel in between the contacts. Electrons, represented by red circles, are injected at  $\mu_S$  and then drift towards  $\mu_D$ . During the transport, the carriers endure sets of collisions in relation to the material mobility. As the channel is tilted proportionally to  $\mu_S$ - $\mu_D$ , carriers are continuously and directionally accelerated towards the low potential.

traveling ballistically in a crystal is better likened with a cannon ball being shot into a forest; sooner or later, the carrier encounters a collision. A carrier collision is referred to as a scattering event and there are multiple mechanisms in which a carrier can scatter. When scattered inelastically, the carrier may lose momentum and subsequently lower its energy state. If the carrier is instead scattered elastically, the carrier will only change its direction, where the direction of travel can be described with the wavenumbers  $k_x$ ,  $k_y$  and  $k_z$ . If a carrier encounters an inelastic scattering event, it will subsequently lower its energy state. At the new energy state, if the carrier is in an electrical field, it will accelerate and start another trajectile.

A transistor channel length within a few  $\lambda_{mp}$  is called semi-ballistic as the entire travel distance is covered by a few ballistic transport events. If the travel distance is equal or less than the  $\lambda_{mp}$ , the transport is called fully ballistic. For a ballistic transistor, the mobility becomes somewhat peripheral as the time for traversing the channel is small compared to the mean time between scattering events. Instead, velocity at which the carrier is injected becomes dominating. Injection velocity is, however, like mobility also related to the effective mass and materials with high mobility typically also have high injection velocities. For a semi-ballistic device, both mobility and injection velocity are important.

## 1.4 The Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET)

The commercial market workhorse with its favorable digital device performance is the metal-oxide-semiconductor field-effect transistor (MOSFET). By its broad application range and wide market adoption, the MOSFET effectively marginalizes all other technologies today. MOSFETs are fabricated with various architectures for various purposes and are often specialized for either low-power or high performance. Another classification is the type of carriers they conduct; a MOSFET with electron carriers is called an n-type while a MOSFET with hole carriers is called a p-type. Having both an n-type and a p-type MOSFET is vital for logic circuits, as explained in section 1.5.

### 1.4.1 The Planar MOSFET

Large-scale commercial integrated circuits are commonly fabricated on Si substrates due to its high cost efficiency. Wafers that measure up to 300 mm in diameter go through up to thousands of different processing steps, before being sliced into chips that are mounted on circuit boards. One of the initial steps in fabricating planar MOSFETs is to define the regions for each device by implanting low concentrations of dopant atoms, contributing with either free electrons or free holes, by bombarding the substrate with ions. To create the two basic contacts between which there will be a flow of current, namely the source and the drain contacts, ions are implanted once again, locally forming regions with a much higher carrier concentration. The contacts are doped with opposite charge compared to those from the ions previously implanted in the substrate. The reason for having the substrate contain carriers of opposite charge is that, for an n-type device, it effectively raises the conduction band around the source and drain regions, making the contact carriers face an uphill potential on all sides. At this stage, the source and the drain have no conduction path between them.

To keep the substrate at a fixed potential during operation, a body contact may also be introduced. The body contact is non-essential and it is not present in all types of FETs; to make a FET, a source-, a drain- and a gate electrode is needed. By applying a potential,  $V_G$ , on the gate electrode, a temporary path may be formed, a channel, between the source and drain. When conduction is switched on,  $V_G$  will be of the same sign as the charge of the substrate carriers, thus opposite sign to the charge in the contact regions. For an n-type device, a positive  $V_G$  will repel positive charges and eventually attract negative charges, something called inversion, as the charge sign of the carriers under the gate is inverted.

To avoid a current flow in and out of the gate, an energy barrier is introduced between the gate contact and the substrate. If the barrier consists of an insulator and the gate is of metal, the material stack under the gate is referred to as metal-oxide-semiconductor, MOS. The low leakage properties of the MOSFET makes it the

preferred choice for digital applications, enabling very-large-scale-integration (VLSI). For an n-type MOSFET, a strong enough positive voltage on the gate will at a critical level attract a sheet of negative charges, an inversion layer, in the channel close to the oxide surface. The critical field occurs at the threshold voltage,  $V_T$ . An applied gate voltage,  $V_G$ , above  $V_T$  will increase the depth of the channel and thus lower the resistance between source and drain. To get a current flow between source and drain,  $I_{DS}$ , there must be a difference between the source potential,  $V_S$ , and the drain potential,  $V_D$ , providing an accelerating voltage,  $V_{DS} = V_D - V_S$ . For an n-type MOSFET, if  $V_{DS}$  is larger than the net voltage above threshold at the gate,  $V_G - V_T$ , the excessive voltage,  $V_{DS} - V_G - V_T$ , will instead drop in the end of the channel region, at the drain side, and thereby not contribute to further carrier acceleration. This is referred to as pinch-off and one outcome is that the drain contact region will start expanding in proportion to  $V_{DS}$  and thus shorten the effective channel length, something that can be problematic for short channel devices.

A device biased above pinch-off is said to be in saturation, in active mode, as an increase of the  $V_{DS}$  will, ideally, not increase the  $I_{DS}$ . With few important exceptions (digital logic), a device should always be in saturation so that current is only controlled by  $V_G$ . If a FET is biased below saturation but above threshold, it is said to be in the triode region. In the triode region, the FET acts as a gated resistor

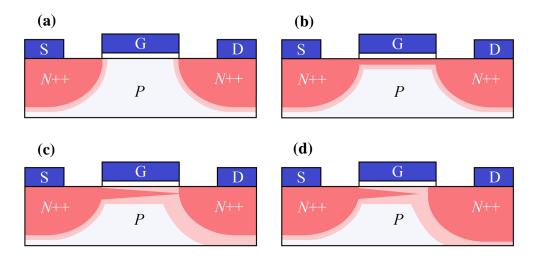

**Fig 1.6.** Schematic illustrations of different biasing conditions of a planar MOSFET. The device has metal deposited in direct contact with highly doped (N++) regions at the source, S, and the drain, D. The lower doped channel (P) is controlled by the potential in gate, G, where the metal contact is separated by a dielectric film. Between the positive and negative charges there is a depletion layer. (a) No gate bias is applied and there is no conducting path between S and D. (b) A gate bias beyond threshold is applied, meaning that an inversion layer is formed at the channel surface. (c) The gate is biased at a higher potential than in S (b) and the potentials of S and S differ to an extent corresponding to channel pinch-off. (d) The potential difference between S and S is increased beyond pinch-off and thus the effective channel length is reduced.

where current control is achieved with all potentials. In Fig. 1.6, a MOSFET under 4 different bias conditions (a, b, c, and d) is shown, illustrating the spatial charge concentration.

#### 1.4.2 A Classical MOSFET Model

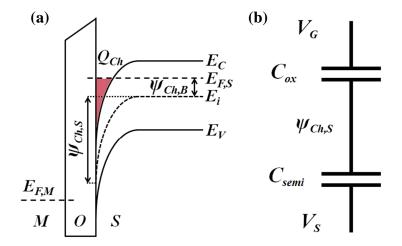

The description of the behavior of a FET can be accomplished with different types of models, depending on the purpose. To develop a model, a first step is to identify the nodes and potentials of importance. In Fig. 1.7a, a model of the MOS interface is shown, indicating the different potentials of the band structure; if the portrayed spatial axis is in the transverse direction, then  $I_{DS}$  flows in the perpendicular, longitudinal direction, or the x-direction. For simplicity, x = 0 is the channel at the source contact and  $x = L_G$  is the channel at the drain contact. Assuming that the transverse field is much stronger than longitudinal field in every point along the channel, the channel in the longitudinal direction can be seen as a series connection of infinitely small resistive elements, where the bulk Fermi potential,  $E_{F,S}(x)$ , at each node is set by the superposition of  $V_S$  and  $V_D$  [10]. The total channel charge area density,  $Q_{Ch}(x)$ , can be thus described as the superposition of the charge area density attributed to the gate-source voltage,  $V_{GS}$  and the gate-drain voltage,  $V_{GD}$ ,  $Q_S(x)$  and  $Q_D(x)$ , respectively:

**Fig 1.7.** (a) A schematic illustration of the MOS interface for an n-doped MOSFET channel, biased at a positive gate-metal potential,  $E_{F,M}$ . The channel charge,  $Q_{Clb}$  has accumulated at the semiconductor surface. The surface potential,  $\psi_{Ch,S}$ , is the difference between the intrinsic potential,  $E_i$ , in the bulk semiconductor and at the channel surface. The bulk potential,  $\psi_{Ch,B}$ , is the difference between the intrinsic level and the semiconductor Fermi level,  $E_{F,S}$ . (b) A schematic illustration of the most important nodes and the different capacitors between gate and source. By replacing  $V_S$  with  $V_D$ , the illustration would instead show the most important potentials and series capacitances between gate and

$$Q_S(x) = C_G(V_{GS} - \psi_{Ch,S}(x)), \tag{1.5}$$

$$Q_D(x) = C_G(V_{GD} - \psi_{ChS}(x)). \tag{1.6}$$

In Eq. 1.5 and 1.6,  $\psi_{Ch,S}(x)$  is the semiconductor surface potential and  $C_G$  is the total gate capacitance. Fig. 1.7b shows a simplified model of the most important potentials and capacitances between gate and source. The semiconductor capacitance,  $C_{semi}$ , corresponds to the derivative of the channel charge in respect to  $\psi_{Ch,S}$ .  $C_G$  is the series connection of the geometrical oxide capacitance density,  $C_{ox}$ , and  $C_{semi}$ .

The current flow in a MOSFET can be modeled with two most significant parameters; the average channel charge area density,  $Q_{Ch}$ , and the average carrier velocity,  $v_{Avg}$ . For a long-channel FET, the current can be described by:

$$\frac{I_{DS}}{W} = Q_{Ch} v_{Avg}. (1.7)$$

In Eq. 1.7, the device current  $I_{DS}$  is normalized with the width of the channel, W.  $Q_{Ch}$  can be calculated by integrating  $Q_{Ch}(x)$  over the channel. If  $Q_{S,i} = Q_S(0)$  and  $Q_{D,i} = Q_D(L_G)$ , then:

$$Q_{Ch} = \frac{1}{L_G} \int_0^{L_G} \left[ Q_{S,i} \left( 1 - \frac{x}{L_G} \right) + Q_{D,i} \left( \frac{x}{L_G} \right) \right] dx = \frac{Q_{S,i} + Q_{D,i}}{2}.$$

(1.8)

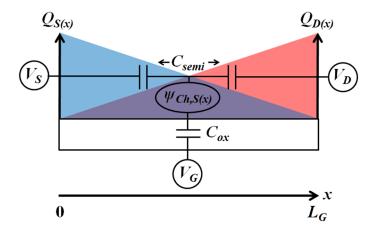

**Fig 1.8.** A schematic illustration of a MOSFET channel with indicated voltage terminals,  $V_G$ ,  $V_S$ , and  $V_D$ , channel surface potential,  $\psi_{S,Ch}$ , oxide capacitance,  $C_{ox}$  the semiconductor capacitance,  $C_{semi}$ , and the channel charge density associated with the source,  $Q_S$ , and drain,  $Q_D$ . The illustrated device is in equilibrium ( $V_S = V_D$ ), where the charge is conformally distributed along the channel.

In equilibrium  $(V_S = V_D)$ , the charge area density equals the average in every point along the channel and thus,  $Q_{Ch} = Q_{S,i} = Q_{D,i}$ . It is the difference in charge area density between  $Q_S$  and  $Q_D$  in combination with injection of carriers that give rise to a steady state drift current, as explained in section 1.3. Fig. 1.8 shows  $Q_S(x)$  and  $Q_D(x)$  from x = 0 to  $x = L_G$  for a channel in equilibrium.

The second factor of the right-hand-side of Eq 1.7,  $v_{Avg}$ , can be expressed as:

$$v_{Avg} = \mu_{eff} \frac{v_{Acc}}{L_G}. \tag{1.9}$$

In Eq. 1.9,  $\mu_{eff}$  is the effective mobility and  $V_{Acc}$  is the carrier acceleration voltage corresponding to potential difference between the drain and source contact. Using Eq. 1.5 and 1.6,  $V_{Acc}$  can be translated into an equivalent charge difference between x = 0 and  $x = L_G$ :

$$V_{Acc} = \frac{Q_{S,i} - Q_{D,i}}{C_G}. (1.10)$$

Inserting Eq. 1.10 in Eq. 1.9 gives:

$$v_{Avg} = \mu_{eff} \frac{Q_{S,i} - Q_{D,i}}{C_G L_G}.$$

(1.11)

By inserting Eq. 1.8 and 1.11 into 1.7, the device current can be expressed as:

$$\frac{I_{DS}}{W} = \mu_{eff} \frac{Q_{S,i} + Q_{D,i}}{2} \frac{Q_{S,i} - Q_{D,i}}{C_G L_G}.$$

(1.12)

With a simple rearrangement, Eq. 1.12 can be altered into:

$$\frac{I_{DS}}{W} = \mu_{eff} \frac{1}{2C_G L_G} (Q_{S,i}^2 - Q_{D,i}^2). \tag{1.13}$$

As described in section 1.4.1,  $V_T$  corresponds to the gate potential at which a first layer of carriers are accumulated (or inverted) at the channel surface.  $V_T$  can be calculated using the potentials shown in Fig. 1.7, or it can be estimated from a measurement. To simplify the modelling and avoid band structure calculations,  $Q_{S,i}$  can be described with an approximate MOS-function expression [11], using an estimated  $V_T$  instead of  $\psi_{Ch,S}$ :

$$Q_{S,i} = C_G \varphi_T \left( \ln(1 + \exp\left(\frac{(V_G - V_T)/\gamma - V_S}{\varphi_T}\right) \right). \tag{1.14}$$

The right-hand-side of Eq. 1.14 describes the potential difference both in sub- $V_T$  and above- $V_T$  operation, where the term  $Q_{S,i}$  converges to  $C_G(V_G-V_T-V_S)$  high above

threshold and to  $C_G(\varphi_T)$  for well below, where the thermal voltage,  $\varphi_T = k_B T/q$ . The  $\gamma$ -parameter is a combination of a Fermi function,  $F_f$ , and the inverse sub-threshold slope (SS) factor, n;

$$n = 1 + C_D/C_i, \tag{1.15}$$

where  $C_D$  is  $C_{semi}$  in depletion and  $C_i$  is the parallel parasitic capacitance induced by interface energy traps (more about energy traps in chapter 4). The  $\gamma$ -parameter and  $F_f$  are given by:

$$\gamma = nF_f + (1 - F_f), \tag{1.16}$$

$$F_f = \frac{1}{1 + \exp((V_G - V_T)/\varphi_T))}. (1.17)$$

$F_f$  mitigates a transition between sub- $V_T$  and above- $V_T$  operation as  $\gamma$  takes the value of n at sub- $V_T$  and unity at above- $V_T$ . Regarding the depletion capacitance, in in an ideal transistor there is a sharp transition of  $C_{semi}$  towards zero when decreasing the gate potential below  $V_T$ . This is the case for a small  $C_D/C_i$  ratio, where n thus is close to unity. However, if there is a large trap density around the conductance band edge, n will be considerably large than 1 and it will thus require a large negative voltage, relative to  $V_T$ , to deplete the channel such that it is considered off. This would then compromise the constraints of the voltage envelope, leakage and possibly the switching time constant.

The description of  $Q_{D,i}$  can done in the same manner as for  $Q_{S,i}$ . Using Eq.

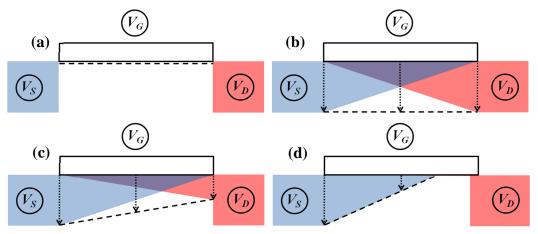

**Fig 1.9.** Schematic illustrations of different biasing conditions of a planar MOSFET. The positive channel area charge density axis points downwards in the figures and the charge density at x = 0,  $x = L_G/2$ , and  $x = L_G$  are indicated. The blue area corresponds to  $Q_S$ , while the red area corresponds to  $Q_D$ ; the striped line is the superposition of the two. (a)  $V_G$  is below  $V_T$ . (b)  $V_G$  is above  $V_T$  and  $V_D > V_S$ . (c)  $V_G$  is above  $V_T$  and  $V_D > V_S$ . (d)  $V_G$  is above  $V_T$  and  $V_D$  is beyond pinch-off.

1.14 and an equivalent expression for  $Q_{D,i}$ , for operation above  $V_T$ , Eq. 1.13 can be rewritten as:

$$\frac{I_{DS}}{W} = \mu_{eff} \frac{c_G}{2L} ((V_{GS} - V_T)^2 - (V_{GD} - V_T)^2). \tag{1.18}$$

For a FET in saturation,  $Q_{D,i}$  goes towards zero (pinch-off) and thus the current is effectively controlled by  $V_{GS}^2$ , and this is true for devices with a low  $V_{DS}/L_G$  ratio. The pinch-off behavior can also be described by introducing a saturation voltage,  $V_{sat}$ , where  $V_{DS} = V_{sat} = V_{GS}-V_T$  for  $V_{DS} > V_{GS}-V_T$ . The superposition of  $Q_S(x)$  and  $Q_D(x)$  for 4 different biases, including pinch-off, is shown in Fig 1.9a, b, c, and d, respectively.

#### 1.4.3 Velocity Saturation

For a FET with  $L_G >> \lambda_{mp}$ , where the current is reduced by scattering along the channel, there are other effects than pinch-off that causes saturation. When the acceleration field reaches a critical level, the carrier velocity will saturate due to carrier-lattice interactions. To account for velocity saturation in the classical model, Eq. 1.13 must first be split into the individual contributions, the carrier density and the carrier velocity, respectively, as in Eq. 1.12. For above- $V_T$  operation, the normalized drain current is given by:

$$\frac{I_{DS}}{W} = \mu_{eff} \frac{C_G}{2L} ((V_{GS} - V_T) + (V_{GD} - V_T)) \cdot ((V_{GS} - V_T) - (V_{GD} - V_T)).$$

(1.19)

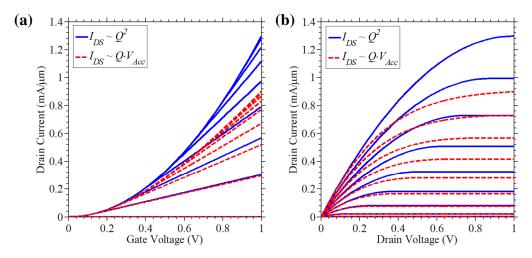

**Fig. 1.10** Simulated data of an InAs NW MOSFET with 600 nm channel length, illustrating the impact of velocity saturation (the red striped curves compared to the blue solid curves). The data is normalized to the nanowire circumference. It should be noted that the graphs show intrinsic performance without any added series resistance. (a) Transfer characteristics. (b) Output characteristics.

Using Eq. 1.7 and 1.9, Eq. 1.19 can be rewritten as:

$$\frac{I_{DS}}{W} = \frac{C_G}{2} \left( \left( \mathsf{V}_{GS} - V_T \right) + \left( \mathsf{V}_{GD} - V_T \right) \right) \left( \mu_{eff} \frac{V_{Acc}}{L_G} \right). \tag{1.20}$$

The current saturation in Eq. 1.20 can now be modeled by introducing a saturation function of  $V_{Acc}$ :

$$V_{Acc} = \frac{V_{DS}}{1 + V_{DS}/V_{Sat}}. (1.21)$$

In Eq. 1.21,  $V_{Sat}$  is the corresponding voltage that when multiplied with  $\mu_{eff}$  gives the saturation velocity. A device that is biased in velocity saturation will have a linear current dependence,  $I_{DS} \sim V_{GS}$ , differing from what was shown for the square dependence,  $I_{DS} \sim V_{GS}^2$ , for a device that is saturated solely by pinch-off. The transfer characteristics,  $I_{DS}$  as a function of  $V_{GS}$ , and the output characteristics,  $I_{DS}$  as a function of  $V_{DS}$ , are plotted in Fig. 10a and b, respectively, for the described MOSFET model, with and without velocity saturation.

The concept of saturation velocity is applicable for intermediately long channel devices, however, for semi-ballistic devices, if the transition time between the point of injection and point of unlikely return (explained in chapter 2) is short enough compared to the time scale for carrier-lattice interactions, velocity can overshoot (not restricted by saturation), and thus velocity saturation can be disregarded. A consequence of this is that in semi-ballistic transport, the current is primarily affected by scattering in the beginning of the channel. For such a device, the velocity of interest is instead at the point of injection.

#### 1.4.4 Short-Channel Effects

For a more complete FET description, the effects of drain-induced barrier lowering (DIBL) and channel-length modulation can also be introduced. DIBL is where the drain potential impacts the curvature of the conduction band structure and thereby change the gate-barrier height, effectively lowering the threshold value proportionally to  $V_{DS}$  and a  $\delta$ -parameter:

$$V_T = V_{T0} + \delta V_{DS}. \tag{1.22}$$

Another effect with similar impact on the transistor characteristics is the channel length modulation, where the channel is shortened due to expansion of the drain region beyond pinch-off. This is modeled with a  $\lambda$ -parameter that is zero below pinch-off and some measured or estimated value above:

$$I_{DS} = I_{DS}(1 + \lambda(V_{DS} - V_{Sat})). \tag{1.23}$$

**Fig 1.11.** Band energy diagram indicating in red the high-field region. The effects of impact ionization, where free electrons can knock out bound electrons, in turn creating a carrier avalanche, occur if the channel is biased steep enough.

A MOSFET in pinch-off is shown in Fig. 1.6d and 1.9d. The two effects described in Eq. 1.22 and 1.23 are referred to as short-channel-effects (SCE). The later of the two will, however, have a minor impact in semi-ballistic devices as the channel resistance is only vaguely dependent on the channel length (explained in chapter 2). Another SCE present in narrow bandgap devices is impact ionization (IMIO), a phenomenon where high momentum carriers may knock out bound valance electrons and thus create a hole-electron pair. If the high field region is of considerable length, both the original and the knocked-out carrier may in turn knock out another pair and this process may go on, creating an avalanche effect with an exponentially increasing current, possibly physically damaging the device. The region of IMIO is indicated in Fig. 1.11. Modeling of IMIO can be accomplished by introducing a critical field,  $F_C$ , above which impact ionization occurs.  $F_C$  is directly related to the semiconductor bandgap energy,  $E_G$ , as  $F_C$  =  $E_G/(qL_{ii})$ , where  $L_{ii}$  is the length of high-field region where the IMIO occurs. As a rough estimate, it is possible calculate the field strength by simply using the potential difference between the drain and gate potential,  $V_{DG}$ , times a fitting parameter  $\alpha$  [12]. The description of the total device current, including the contribution of the IMIO, can thus be expressed as;

$$I_{DS} = I_{DS} (1 + \beta e^{(\alpha V_{DG})/(F_C L_{ii})}),$$

(1.24)

where  $\beta$  is another fitting parameter. By exchanging  $F_C$  with  $E_G/(qL_{ii})$ , 1.24 can be rewritten as:

$$I_{DS} = I_{DS} (1 + \beta e^{q(\alpha V_{DG})/E_G}). \tag{1.25}$$

As with other tunneling dependent processes, due to the finite response time in band-to-band tunneling (BTB) of carriers, IMIO will not affect high frequency gate potential switching, but can still have a detrimental effect in RF applications as it may increase circuit DC power consumption.

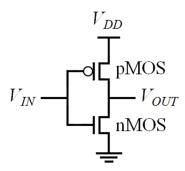

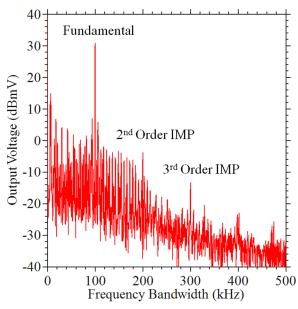

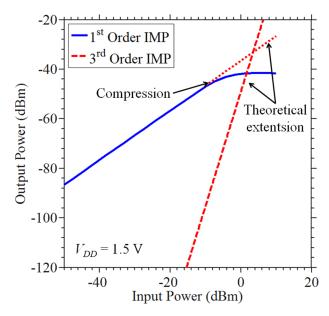

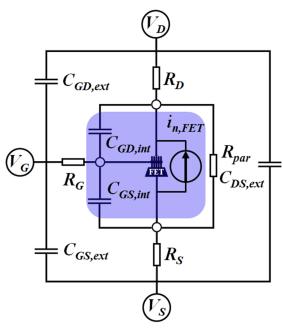

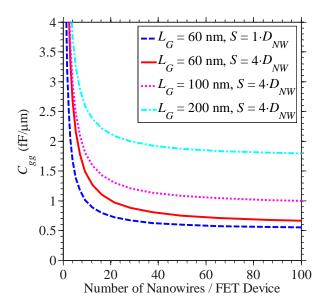

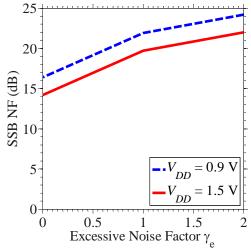

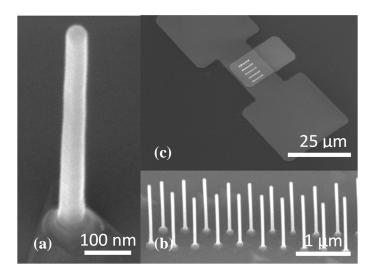

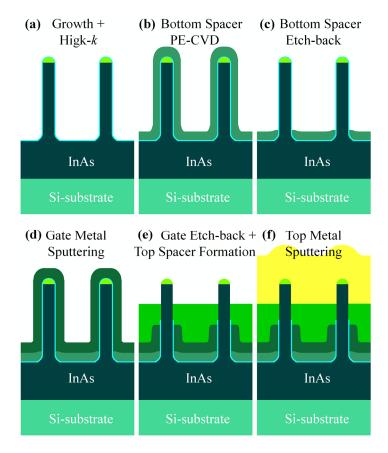

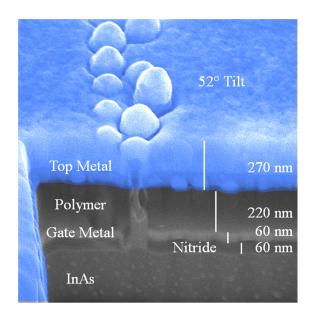

#### 1.5 **CMOS**