Wu, Jun

#### Link to publication

2016

Citation for published version (APA):

Wu, J. (2016). *Vertical III-V/High-k Nanowire MOS Capacitors and Transistors*. [Doctoral Thesis (monograph), Department of Electrical and Information Technology]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 19. Dec. 2025

Jun Wu

Doctoral Thesis Electrical Engineering Lund, April 2016

"template" — 2016/3/21 — 15:04 — page ii — #2

Jun Wu Department of Electrical and Information Technology Lund University Ole Römers väg 3, 223 63 Lund, Sweden

Series of licentiate and doctoral theses ISSN 1654-790X; No. 81 ISBN 978-91-7623-680-2 (printed) ISBN 978-91-7623-681-9 (digital)

#### © 2016 Jun Wu

Typeset in Palatino and Helvetica using  $\LaTeX 2_{\epsilon}$ . Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

## **Abstract**

The emerging nanowire technology in recent years has attracted an increasing interest for high-speed, low-power electronics due to the possibility of a gate-all-around (GAA) geometry enabling aggressive gate length scaling, together with the ease in incorporating high-mobility narrow band gap III-V semiconductors such as InAs on Si substrates. These benefits make vertical nanowire transistors an attractive alternative to the planar devices. However, huge challenges are also encountered. Apart from the large parasitics associated with the device layout, vertical III-V/high- $\kappa$  nanowire MOSFETs so far are also suffering from a less efficient gate control partially due to the defect states existing in the MOS gate stack. Besides the narrow band gap InAs may result in impact-ionization and band-to-band tunneling at high drain voltages, influencing both the power efficiency and speed of modern integrated circuits (ICs).

In this thesis, results on planar InAs/high- $\kappa$  MOS gate stacks investigated in detail using both the capacitance-voltage (C-V) and the x-ray photoelectron spectroscopy (XPS) techniques are first presented (Paper I and II). The origin of the specific trap state energy distribution is clarified and compared to the well studied InGaAs and GaAs materials. The results highlight the benefit of using InAs, with optimized high- $\kappa$  deposition strategies, as the n-MOSFET channel.

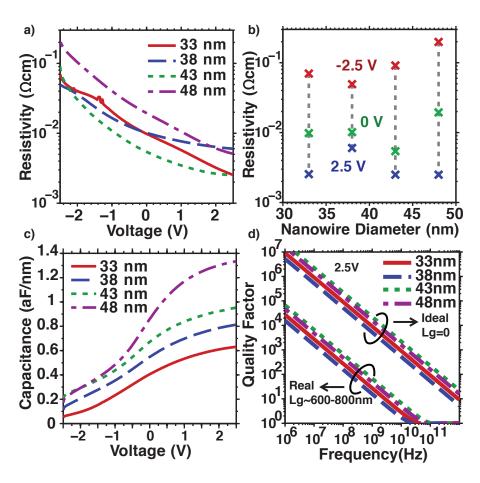

The second focus of the thesis is the improvement of vertical GAA nanowire MOS gate stacks (Paper III and IV). By developing the fabrication scheme and design, conventional C-V technique is successfully applied to extract detailed trap state distributions. A low interface trap state density ( $D_{it}$ ) below  $10^{12}$  eV<sup>-1</sup>cm<sup>-2</sup> near the MOS semiconductor conduction band edge is achieved. Furthermore, RF C-V measurements, together with the development of a com-

plete small signal equivalent circuit model, for vertical GAA nanowire MOS systems are also presented for the first time, which enables characterizations of border trap density, interface trap density, channel resistivity and quality factor of the nanowire MOSFETs simultaneously.

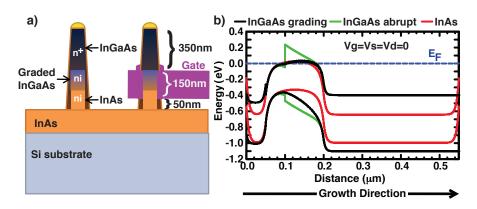

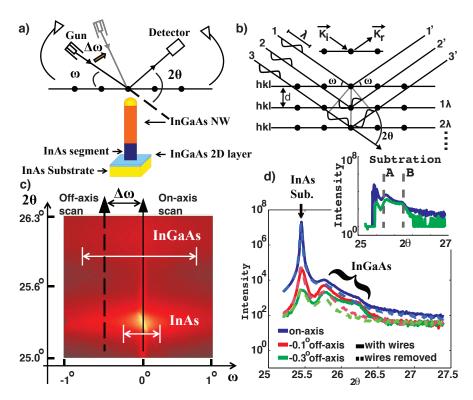

The third focus is the development of a device structure to reduce detrimental impact-ionization and band-to-band tunneling due to the narrow band gap of InAs (Paper V and VI). An asymmetric InAs/InGaAs vertical nanowire MOSFET with a large band gap drain region is proposed, taking advantage of the efficient strain relaxation of nanowire epitaxial growth. Control of the InGaAs nanowire composition has been successfully demonstrated.

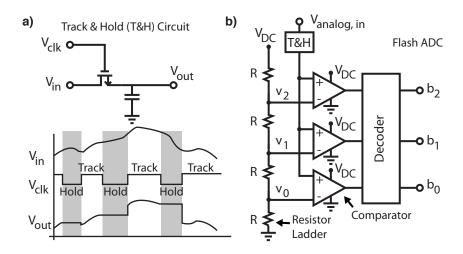

Finally, a vertical integration scheme was developed in the thesis, where track-and-hold circuits, consisting of a MOSFET in series with a metal-insulator-metal capacitor, were successfully fabricated along vertical InAs nanowires (Paper VII).

"template" — 2016/3/21 — 15:04 — page v — #5

## Populärvetenskaplig Sammanfattning

INCE 1947 when the first transistor was invented, electronics was transited into an unprecedented era. Different from a resistor that only has two terminals with the applied voltage and flowing current always obeying Ohm's law, a transistor has the third terminal in between, called "gate", which is made by, for metal-oxide-semiconductor field effect transistors (MOSFETs), an oxide layer sandwiched between the metal electrode and the semiconductor channel. This terminal can control the current flowing through the semiconductor by creating an electrical field in the channel when a voltage is applied, hence realizing the switching function between digital 1 (switching on with current flowing) and digital 0 (switching off with current blocked). This is the basis of all digital calculations, and, hence, all modern computers. Besides, a small voltage variation (input signal) sent to the gate node can create a large variation in current in the channel (output signal) under some conditions, which realizes, on the other hand, the signal amplification function. This is the basis of all analogue applications, and, hence, all modern mobile phones.

Based on the transistor technology, the first integrated circuit (IC) was invented in 1960s, which was another revolutionary creation of that century. In an IC, many transistors are integrated in the semiconductor material of silicon to realize different digital and analog functions. The co-founder of Intel, Gordon Moore, predicted in 1965 that the number of transistors per chip would double every 24 months. This prediction later was called Moore's law, and it was accurately followed during the last 50 years via the continuous transistor size downscaling. It also became one of the main goals of the semiconductor industry, since reducing the transistor size not only resulted in an increased packing density of modern ICs and a reduced fabrication cost per transistor, but also an increased circuit speed and a reduced power

consumption as the transistor gate length was reduced continuously.

The transistor size downscaling, however, is not a permanent strategy unfortunately, since as the transistor gate length is reduced below several tens nanometers. The gate will lose control of the channel charges, which is usually termed "short channel effects". After 2002, people began to seek alternative solutions to continuously increase the IC performance. One of the most promising solutions, which is also the main topic of the thesis, was the vertical warp-gated indium arsenide (InAs)/high-k oxide nanowire MOS-FETs. The vertical nanowire geometry enables gate electrode surrounding the nanowire, i.e. warp-gated, as compared with the conventional planar MOSFET technique. Thus electric field can be applied from all directions, leading to more efficient gate control. Besides the use of InAs provides high mobility charge carriers, which means that the charges can transport faster than those in Si under the same voltage bias. In addition, the use of high-k oxide in the gate leads to larger gate capacitance, which also increases the gate efficiency.

Challenges also exist, however, for the new candidate. From the material's point of view, the interface between the high-k oxide and the semiconductor turns out to be a key to success, since defects at this interface will influence the charge control inside the semiconductor significantly, which is also one of the most severe hindrances of the technology so far.

This work presents the development of a reliable technique to study the vertical wrap-gated nanowire gate stack, understanding and improvement of the gate performance of this type of MOSFETs. Besides, the thesis also presents a new vertical nanowire transistor design with further improved performance. In addition, a vertical integration scheme was developed, where track-and-hold circuits, consisting of a MOSFET in series with a metal-insulator-metal capacitor, were successfully fabricated along vertical InAs nanowires.

## Acknowledgments

"Do not go gentle into that good night."

- Dylan Thomas

It this end of my expedition to "Dr. Jun Wu", I would like to express my great gratitude to quite a lot of people who helped and accompanied me during these years.

First and foremost, I really appreciate my main supervisor, Lars-Erik, for your continuous inspiration, guidance, encouragement, and numerous fruitful discussions in my researches. I would also like to thank my supervisor, Erik, for sharing your gigantic knowledge about semiconductor physics and devices. Your two's wide-ranging knowledge and deep understanding of the entire field impress me unforgettably. It is really my great honor to have you as my ph.D. supervisors. Besides, I would like to acknowledge all my fantastic colleagues. Especially, I want to thank Johannes who contributed a lot of valuable suggestions in my researches and checked my thesis patiently and carefully. I would also like to thank Elvedin, Olli-Pekka, Kristofer, Aein, Martin, Sofia, Mattias, Anil, Markus for all our enjoyable collaborations. It was great for me also to have Sebastian, Lars, Cezar, Fredrik, Guntrade, Jiongjiong during these years. Sebastian, your comment on my personality means a lot to me, and I promise I will keep being a lovely person in the future.

Finally, I would also like to acknowledge Rainer, Martin H., Anders, Jovana, Sofie in synchrotron radiation group; Daniel, Kimberly in FTF for your expertise and contributions in my work. Also thank those engineers who maintaines the labs in Lund.

"template" — 2016/3/21 — 15:04 — page viii — #8

*Jun Wu* Lund, April 2016

viii

## Contents

| Abstract                                                               | iii  |

|------------------------------------------------------------------------|------|

| Populärvetenskaplig Sammanfattning                                     | v    |

| Acknowledgments                                                        | vii  |

| Contents                                                               | ix   |

| Preface                                                                | xiii |

| Structure of the Thesis                                                | xiii |

| Included Papers                                                        | xiv  |

| Extraneous Papers                                                      | xv   |

| Funding Organisations                                                  | xvi  |

| INTRODUCTION                                                           | 1    |

| 1: Background                                                          | 3    |

| 1.1: Evolution of transistor architecture                              | 4    |

| 1.2: III-V semiconductors and high- $\kappa$ dielectrics               | 5    |

| 1.3: Enhancement-mode InAs/high- $\kappa$ vertical GAA nanowire MOSFET | 7    |

| 1.4: Challenges                                                        | 8    |

| 2: Planar InAs/High-κ MOS Gate Control                                 | 11   |

| 2.1: Substrate surface                                                 | 12   |

| 2.2: Native oxides and atomic layer deposition                         | 13   |

|                                 | 2.5. WOS capacitor fabrication and measurements                             | 10         |

|---------------------------------|-----------------------------------------------------------------------------|------------|

|                                 | 2.4: Device characterization                                                | 16         |

|                                 | 2.4.1: MOS capacitor C-V characteristics                                    | 16         |

|                                 | 2.4.2: Trap characterization by low frequency C-V fitting                   | 18         |

|                                 | 2.4.3: Aluminum oxide                                                       | 21         |

|                                 | 2.4.4: Hafnium oxide                                                        | 24         |

| 3:                              | In As/High- $\kappa$ Verical Wrap-Gated Nanowire MOS Gate Control           | <b>2</b> 5 |

|                                 | 3.1: Nanowires used for MOSFETs                                             | 26         |

|                                 | 3.1.1: Nanowire growth                                                      | 26         |

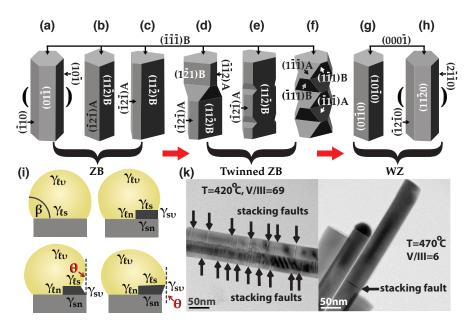

|                                 | 3.1.2: Crystalline phase control                                            | 29         |

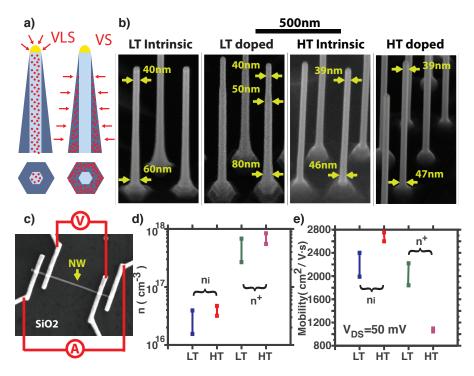

|                                 | 3.1.3: In-situ doping                                                       | 32         |

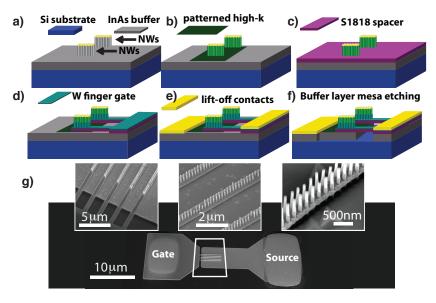

|                                 | 3.2: Nanowire MOS capacitor fabrication                                     | 33         |

|                                 | 3.2.1: Parasite capacitance v.s. gate capacitance                           | 33         |

|                                 | 3.2.2: Finger gate nanowire MOS capacitor                                   | 35         |

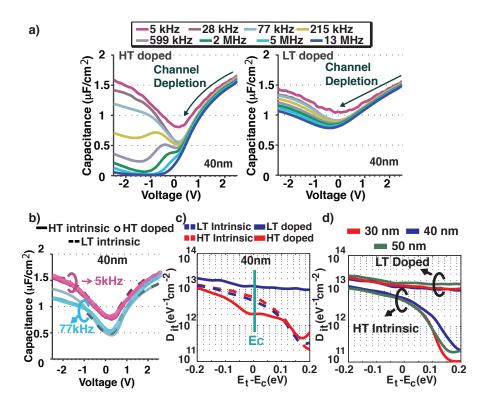

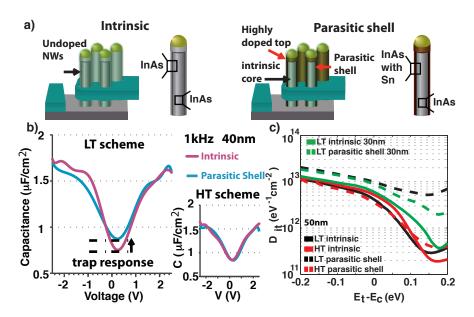

|                                 | 3.3: Trap density profiling                                                 | 38         |

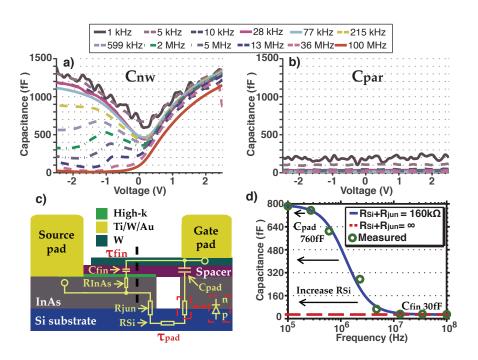

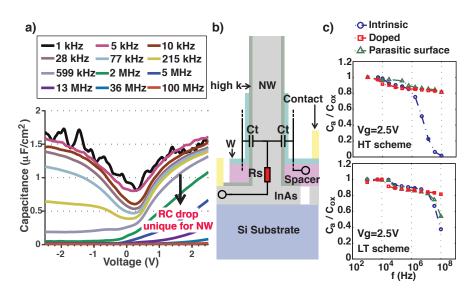

|                                 | 3.4: Complete equivalent circuit model and RF C-V characteristics .         | 41         |

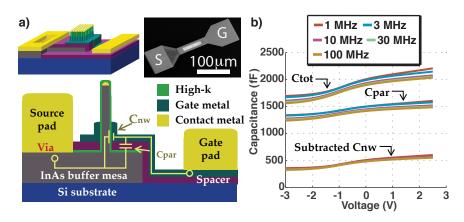

|                                 | 3.4.1: RF-compatible nanowire MOS capacitor design                          | 42         |

|                                 | 3.4.2: Low frequency full trap model                                        | 43         |

|                                 | 3.4.3: RF C-V small signal model                                            | 46         |

| 4:                              | Asymmetric InAs/InGaAs Vertical Nanowire MOSFETs                            | 53         |

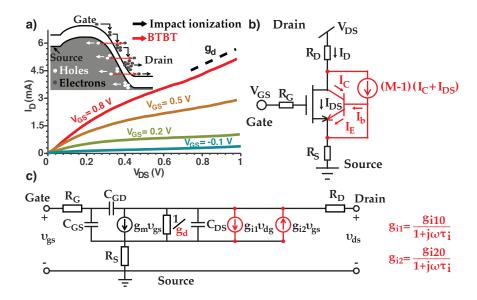

|                                 | 4.1: Impact-ionization and band-to-band tunneling for InAs nanowire MOSFETs | 53         |

|                                 | 4.2: Asymmetric InAs/InGaAs verical nanowire MOSFET design                  | 56         |

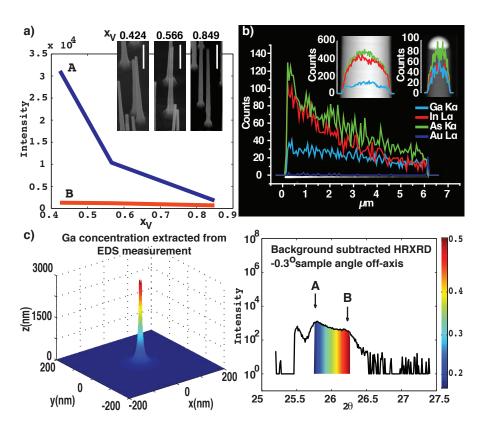

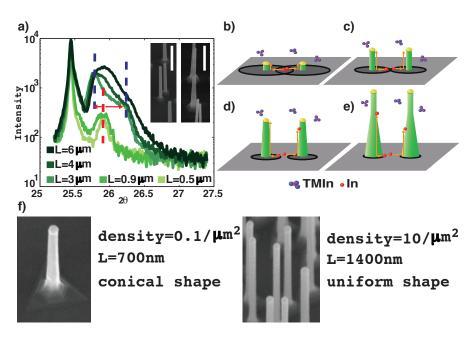

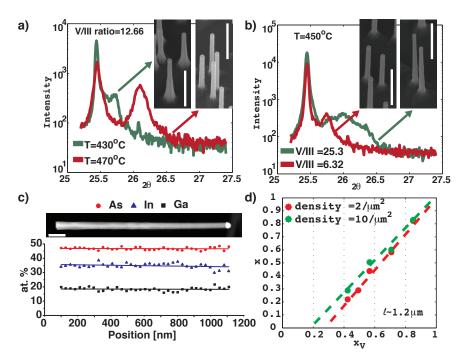

|                                 | 4.3: Ga incorporation control in InGaAs nanowires                           | 57         |

|                                 | 4.3.1: High resolution X-ray diffraction off nanowires                      | 57         |

|                                 | 4.3.2: InGaAs nanowire growth model                                         | 59         |

|                                 | 4.3.3: Nanowire morphology and Ga concentration control                     | 62         |

| 5:                              | Track-and-Hold Circuit Integrated along Vertical InAs Nanowires             | 65         |

| 6:                              | Conclusion and Outlook                                                      | 67         |

|                                 | bliography                                                                  | 69         |

| $\boldsymbol{\nu}_{\mathbf{I}}$ | DIIOGIUPIIY                                                                 | 07         |

"template" — 2016/3/21 — 15:04 — page xi — #11

PAPERS 81

"template" — 2016/3/21 — 15:04 — page xii — #12

## **Preface**

THIS thesis summarizes my academic works of the last four and a half years within the Nanoelectronics group, Lund University, under the supervision of Professor Lars-Erik Wernersson. The thesis focuses on understanding and improving the vertical III-V nanowire based devices and circuits.

#### STRUCTURE OF THE THESIS

This thesis is divided into two parts: introduction and included papers

#### INTRODUCTION

The research field is reviewed and summarized, with emphasis on the papers that are included in the thesis.

#### 1: Chapter 1

This chapter provides a historical review of the field, which leads to the motivation of the researches performed in the thesis.

#### 2: Chapter 2

This chapter discusses the optimization of the InAs/high-κ metal-oxide-semiconductor (MOS) gate performance. Planar MOS capacitance-voltage (C-V) technique (including the development of a fitting method) and x-ray photoelectron spectroscopy technique are introduced. By combining the electrical and chemical characterizations, the correlation between the trap states across the InAs band gap and different interface chemical species is presented, together with the optimized MOS gate stack fabrication recipes. This chapter is related to Paper I and Paper II.

#### 3: Chapter 3

In this chapter, the C-V technique to characterize the vertical wrapgated InAs/high- $\kappa$  nanowire MOS gate stacks is introduced. The influence of nanowire growth conditions and doping on the MOS gate stack quality is discussed. At the end, RF C-V technique and a complete small signal equivalent circuit model are presented. This chapter is related to Paper III and Paper IV.

#### 4: Chapter 4

This chapter presents the development of an asymmetric InAs/InGaAs vertical nanowire MOS field effect transistor (MOS-FET) in order to suppress the impact ionization and band-to-band tunneling effects commonly observed in InAs MOSFETs. Band engineering of the new design is presented. Besides, understanding of the ternary InGaAs nanowire growth and control of the Ga incorporation are discussed. This chapter is related to Paper V, Paper VI.

#### 5: Chapter 5

This chapter presents an integration scheme to realize track-and-hold circuits along vertical InAs nanowires. This chapter is related to Paper VII

#### 6: Chapter 6

This chapter summarizes the conclusions from the thesis and discusses the future of the research field.

#### PAPERS

The included papers are reproduced in the last part of the thesis. Observe that the copyrights of the papers are owned by the respective publishers.

#### **INCLUDED PAPERS**

The following papers are included in this thesis and the respective published or draft versions are appended at the back of this thesis.

- Paper I: J. Wu, E. Lind, R. Timm, M. Hjort, A. Mikkelsen, and L.-E. Wernersson, "Al2O3/InAs metal-oxide-seminonductor capacitors on (100) and (111)B substrates" *Applied Physics Letters*, vol. 100, pp. 132905, Mar. 2012.

- ▶ I performed almost all the works on this paper except for the XPS measurements.

- **Paper II:** E. Lind, J. Wu, and L.-E. Wernersson, "High-κ oxides on InAs 100 and 111B surfaces" *ECS Transactions*, vol. 45, no. 3, pp. 61–67, Apr. 2012.

- ▶ In this work, I fabricated the devices, performed the electrical characterization, and participated in the data analysis as well as the result discussions.

- Paper III: J. Wu, A. S. Babadi, D. Jacobsson, J. Colvin, S. Yngman, R. Timm, E. Lind, and L.-E. Wernersson, "Low trap density in InAs/high-κ nanowire gate stacks with optimized growth and doping conditions" *Nano Letters*, Manuscript accepted, DOI: 10.1021/acs.nanolett.5b05253.

- ▶ I performed almost all the works on this paper except for the AFM, TEM and transport measurements.

- **Paper IV:** J. Wu, K. Jansson, A. S. Babadi, M. Berg, E. Lind, and L.-E. Wernersson, "RF characterization of vertical wrap-gated InAs/high-κ nanowire capacitors" *IEEE Transactions on Electron Devices*, vol. 63, no. 2, pp. 584–589, Feb. 2016.

- ▶ *In this work, I developed the techniques of device fabrication and electrical characterization, participated in the data analysis, and wrote the manuscript.*

- **Paper V:** K.-M. Persson, M. Berg, M. B. Borg, <u>J. Wu</u>, S. Johansson, J. Svensson, K. Jansson, E. Lind, and L.-E. Wernersson, "Extrinsic and intrinsic performance of vertical InAs nanowire MOSFETs on Si substrates" *IEEE Transactions on Electron Devices*, vol. 60, no. 9, pp. 2761–2767, Sep 2013.

- ▶ *In this work, I grew the nanowires and participated in the result discussions.*

- **Paper VI:** J. Wu, B. M. Borg, D. Jacobsson, K. A. Dick, and L.-E. Wernersson, "Control of composition and morphology in InGaAs nanowires grown by metalorganic vapor phase epitaxy" *Journal of Crystal Growth*, vol. 383, pp. 158–165, Aug 2013.

- ▶ I performed almost all the works on this paper except for the TEM and XEDS measurements.

- **Paper VII:** J. Wu, AND L.-E. WERNERSSON, "3D integrated track-and-hold circuit using InAs nanowire MOSFETs and capacitors" *IEEE Electron Device Letters*, Manuscript (to be submitted soon)

- ▶ *I performed all the works on this paper.*

#### **EXTRANEOUS PAPERS**

The following papers are not included in the thesis, but summarize related work which I have contributed to.

- Paper viii: M. Berg, K.-M. Persson, J. Wu, E. Lind, H. Sjöland, and L.-E. Wernersson, "InAs nanowire MOSFETs in three-transistor configurations: single balanced RF down-conversion mixers" *Nanotechnology*, vol. 25, pp. 485203, Nov. 2014.

- **Paper ix:** K. M. Persson, M. Berg, M. Borg, <u>J. Wu</u>, H. Sjöland, E. Lind, and L.-E. Wernersson, "Vertical InAs nanowire MOSFETs with  $I_{DS}$ =1.34 mA/ $\mu$ m and  $g_m$ =1.19 mS/ $\mu$ m at  $V_{DS}$ =0.5  $I_{DS}$ =1.34" in 70th Annual Device Research Conf. (DRC), pp. 195–196, Jun. 2012.

- **Paper x:** S. Johansson, K.-M. Persson, M. Berg, J. Wu, J. Svensson, L.-E. Wernersson, and E. Lind, "RF characterization of vertical InAs nanowire MOSFETs" in 12nd Swedish System-on-Chip Conf. (SSoCC), May. 2013.

- Paper xi: J. Wu, D. Jacobsson, B. M. Borg, K. A. Dick, and L.-E. Wernersson, "InGaAs nanowires grown by metalorganic vapor phase epitaxy for future device application" in 41st International Symposium on Compound Semiconductor (ISCS), May. 2014.

#### **FUNDING ORGANISATIONS**

This work was supported in part by the Swedish Foundation for Strategic Research, in part by the Knut and Alice Wallenberg Foundation, in part by the Crafoord Foundation and in part by the Swedish Research Council.

## INTRODUCTION

"template" — 2016/3/21 — 15:04 — page 2 — #18

## Background

SINCE 1947 when the first transistor was invented by John Bardeen, Walter Brattain and William Shockley [1, 2], electronics was transited into an unprecedented era. The revolution was further boosted later in 1960s with the advent of the first integrated circuits (ICs). During the last several decades, the number of transistors per chip roughly doubled every 24 months via the continuous downscaling of the transistor size, following Gordon E. Moore's prediction in 1965 [3,4]. Since the increased packing density of modern ICs went hand in hand with an exponentially increased performance in both speed and power efficiency, fulfilling Moore's law became a major goal of the entire electronics semiconductor industry.

However, geometrical downscaling became less attractive after 2002, since Si complementary metal-oxide-semiconductor (CMOS) technology entered into the so-called power-constrained scaling era after the power dissipation on chip reached  $100~\rm W/cm^2$  [5]. Sacrificing speed seemed inevitable to avoid overheating if a further increase in transistor density was pursued. This limitation became the driving force to exploit the multi-core system after 2004 where the computer tasks were separated into parallel problems and designated to separate cores to ensure the highest efficiency in power usage. The effective performance of multi-core CPUs, however, relied strongly on the parallelization degree of the computer tasks instead of the addition of more cores, as demonstrated by Gene Amdahl in 1967 [6], which finally limited the gain of this technology.

In the future, a revolution of the basis, i.e. the transistors, is highly expected since it means not only a breakthrough of these current limitations in pursuing Moore's law, but also more flexibility in fulfilling the diversified needs as the era of Internet of Thing [7] is coming. These stimulate today's

industry and academy to rethink the way we realize the most fundamental building-block of electronics, the metal-oxide-semiconductor field-effect transistor (MOSFET). One promising candidate for the future is the gate-all-around (GAA) nanowire-based devices, in combination with the advanced high-speed material, which is the subject of this thesis.

In this chapter, we lay the background of the thesis, including both the benefits and challenges in realizing vertical standing GAA III-V/high- $\kappa$  nanowire MOSFETs.

#### 1.1 EVOLUTION OF TRANSISTOR ARCHITECTURE

One key problem associated with downscaling MOSFETs is the short channel effects (SCEs), such as the drain induced barrier lowering, the sub-threshold slope degradation, the threshold voltage roll-off etc. These undesirable effects all result from the reduced efficiency of gate electrostatic control as the gate length is aggressively reduced and SCEs lead to increased dynamic and static power dissipations in modern ICs.

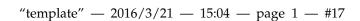

One solution is to redesign the transistor architecture so that the electrical field from the gate affects the channel simultaneous from multiple directions. This allows further scaling of the gate length without losing gate control. Figure 1.1 shows the evolution of the transistor architecture from the conventional planar, to multiple-gate, and finally to GAA MOSFETs. The tri-gate MOSFET in (c) has been commercially realized by Intel in 2012 for the 22 nm node [8], and as reported, this technology increases the performance by 37 %, and meanwhile reduces the power dissipation by 50 %, as compared to the planar MOSFET technology [9] in figure 1.1(a).

The GAA geometry, (d), is expected to provide the ultimate electrostatic control, and in recent years, it has begun to attract increasing interest. Auth. et al. showed that compared to the double-gate geometry, (b), the cylindrical GAA geometry enables the minimum effective gate length to be reduced by 40 % [10]. Lateral GAA MOSFETs formed by removing the substrate under the tri-gate transistors have been recently reported with very promising performance [11]. Meanwhile the introduction of the vertical nanowire formation, either through top-down [12] or bottom-up [13] approaches, provides an another platform to realize the vertical standing GAA geometry. This gives additional benefits. First of all, the vertical nanowire geometry enables the possibility to integrate the circuit components in the vertical dimension with small footprints. This can further increase the circuit density with the same chip size. Besides, the nanowire formation methodologies usually can relax strains caused by lattice mismatch between different materials. This enables the possibility to realize more complicated heterogeneous junctions both

1: Background

**Figure 1.1:** Evolution of the transistor gate geometry: (a) planar; (b) doublegate; (c) try-gate; (d) gate-all-around (both lateral and vertical). The black arrows illustrate the direction of the electric field at different surfaces

axial [14] and radial [15], as well as the possiblity to incorporate advanced materials onto the cost-effective Si platform [16, 17]. Promising results of MOSFETs based on the technology have been published in recent years [18].

#### 1.2 III-V SEMICONDUCTORS AND HIGH- $\kappa$ DIELECTRICS

Except for power dissipation, another concern for electronics is the speed. High speed ICs, independent on application areas, in general rely on a large on-state drain-source current of the MOSFETs,  $I_{ds,on}$ , in order for a fast charging and discharging of gate and load capacitors at each IC stage. However, as scaling down the supply voltage became a trend for modern ICs in order to reduce the power dissipation, retaining the diminished onperformance of Si MOSFETs (a high  $I_{ds,on}$ ) is challenging [19]. Thus low-power, high-speed electronics attracted increasing interest and for modern ICs, the on/off-current ratio,  $I_{on}/I_{off}$ , and the quality value,  $Q=g_{m,max}/SS_{min}$  (maximum transconductance/minimum sub threshold slope), become very important figures of merit to evaluate the transistor performance.

$I_{ds,on}$  is proportional to the total amount of charges available in the channel,  $Q_{ch}$ , and the velocity that these charges travel due to the electrical field induced by the source-drain bias,  $v_d$ .  $Q_{ch}$  is directly related to the gate capacitance density,  $C_g$  (in  $F/m^2$ ), through  $Q_{ch}=A\cdot C_g\cdot (V_{gs}-\psi_s)$ , where A is the gate area and  $(V_{gs}-\psi_s)$  is the voltage drop over the gate dielectric.  $v_d$  is directly related to the charge mobility,  $\mu$ , by  $v_d=\mu\cdot \xi_{ds}$ , in which  $\xi_{ds}$  is the drain-source electrical field. Before around 2005,  $C_g$  was increased by scaling the oxide thickness,  $t_{ox}$ . However, as  $t_{ox}$  was reduced down to a few nanometers,

**Table 1.1:** Relative dielectric constant, band gap and conduction band offset with respect to InAs for high- $\kappa$  dielectrics and SiO<sub>2</sub>

|                  | κ   | $E_g$ (eV) | $\Delta E_{c,InAs}(eV)$ |

|------------------|-----|------------|-------------------------|

| SiO <sub>2</sub> | 3.9 | 9          | 4.1                     |

| $Al_2O_3$        | 9   | 8.8        | 3.6                     |

| HfO <sub>2</sub> | 25  | 5.8        | 2.5                     |

**Table 1.2:** Electron and hole mobilities ( $\mu_e$  and  $\mu_h$ ) of some selected semicondutors [20]

| (cm <sup>2</sup> /Vs) | Si   | Ge   | GaSb | GaAs | $In_{0.53}Ga_{0.47}As$ | InAs  | InSb  |

|-----------------------|------|------|------|------|------------------------|-------|-------|

| $\mu_e$               | 1400 | 3900 | 3000 | 8500 | 12000                  | 40000 | 77000 |

| $\mu_h$               | 450  | 1900 | 1000 | 400  | 300                    | 500   | 850   |

the gate leakage due to quantum mechanical tunneling became significant and the static power dissipation of ICs increased. To solve the problem, an alternative approach by increasing the effective dielectric constant,  $\kappa$  was proposed. High-κ material, such as Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, was then introduced into the transistor fabrication, which solved the leakage issue by enabling thicker oxides [21]. A comparison of electrical properties between high- $\kappa$ material and  $SiO_2$  is shown in table 1.1. The commercial usage of high- $\kappa$ has been realized by Intel for the 45 nm node in 2007. To boost  $\mu$ , on the other hand, high-speed semiconductor materials beyond the conventional Si have to be considered. III-V compound semiconductor hence attracted great interest in recent years. Table 1.2 presents electron and hole mobilities ( $\mu_n$ and  $\mu_{\nu}$ ) of a few selected semiconductors. As can be seen, Si is inferior to III-V semiconductors in general within which InAs and In<sub>0.53</sub>Ga<sub>0.47</sub>As show fairly high  $\mu_n$ , making them promising for future n-MOSFETs. Although InSb shows the highest  $\mu_n$ , its narrow band gap is making it hard to avoid bandto-band tunneling in an InSb based MOSFET. In this thesis, the InAs MOSFET is chosen as the subject due to several reasons. Except for high  $\mu_n$ , InAs can also form ohmic contacts due to the Fermi level pinning at the metalsemiconductor junction [22, 23]. Moreover, promising performance of InAs nanowire MOSFETs, both DC and RF, has been reported recently based on the technique of an InAs buffer layer grown on low-cost Si substrate [24]. All of those make InAs highly attractive. In term of hole mobility, Ge and GaSb are very good candidates for future p-type MOSFETs [25,26]. The ITRS roadmap

1: Background

has speculated that the replacement of Si by III-V in CMOS technology will take place in around 2018-2026 with an about 50 % increase in switching speed and 40 % in power efficiency for the 10 nm node technology [27]. For analog applications, such as amplifiers, III-V semiconductors are already used due to the higher speed requirements at the lower cost sensitivity. High electron mobility transistors (HEMTs), metal-semiconductor field-effect transistors (MESFETs) and heterojunction bipolar transistors (HBTs) based on III-V materials are quite important nowadays due to the excellent high frequency performance the material provides as compared to Si [28,29].

## 1.3 ENHANCEMENT-MODE InAs/HIGH- $\kappa$ VERTICAL GAA NANOWIRE MOSFET

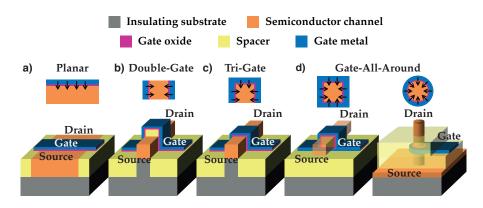

InAs/high- $\kappa$  vertical GAA nanowire MOSFETs are thus a promising candidate for future electronics. Figure 1.2(a) presents a vertical GAA nanowire MOSFET in common source configuration. The source contact in this work is realized by a highly n-doped InAs buffer layer on a the highly-resistive p-type Si substrate. On the buffer layer nanowires are grown by epitaxy, followed by high- $\kappa$  dielectric deposition. The gate/drain contacts are realized using metal sputtering. Between them are low- $\kappa$  dielectric spacers. The band diagrams in (b)-(c) illustrate how a n-type enhancement mode MOSFET works. As a positive gate bias,  $V_{gs}$  is applied to the gate node, electrons in semiconductor are attracted towards the surface by the electrical field. The charge accumulation provides a current channel as long as a drain-source bias,  $V_{ds}$ , is applied. As a negative  $V_{gs}$  is applied to the gate, the electrical field created beneath the gate will repel electrons, hence depleting the channel. The transistor is thus switched off.

MOSFETs provide two basic functions for modern ICs: 1) the logic-switch function for digital applications, i.e. using high and low input/output voltages to represent the logic 1 and 0 [26]; 2) the signal-amplifier function for analog and RF applications, i.e. using a small input signal variation,  $\delta v_{gs}$ , to generate a large output signal change,  $\delta i_{ds}$  [30]. MOSFETs are inherently very suitable for digital application since the use of voltage to control the channel leads to a reduced power dissipation as compared to HBTs. However, the analog performance of MOSEFTs is inferior than e.g. HBTs due to the smaller transconductance. Nowadays, since more and more stringent requirements are put on the power dissipation for modern ICs [5], there is a trend to develop MOSFET-based analogue and RF ICs.

**Figure 1.2:** Schematics of (a) an enhancement-mode vertical GAA InAs/high- $\kappa$  nanowire MOSFET, (b) the band diagram of the transistor on-state, and (c) the band diagram of the transistor off-state.

#### 1.4 CHALLENGES

To realize the new type of MOSFETs with the anticipated performance is challenging, and the challenges can be divided into two categories. One is from the MOSFET itself. The other is from the parasitic components arising when connecting the MOSFET with the external world. In fact, the active region serving as a functioning MOSFET is only the gated segment, as shown in figure 1.2(a), whereas the other parts of the nanowire, as well as the contacts, work purely as leads connecting the MOSFET with other circuit components or measurement probes. In this section, both the intrinsic and the extrinsic parts will be discussed.

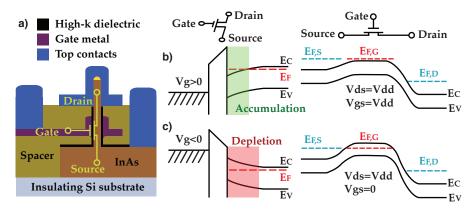

The key functions of a MOSFET rely on the performance of the MOS gate stack, and since it is made by combining the crystalline semiconductor and the amorphous dielectric, defects at the semiconductor/dielectric interface and inside the dielectric, characterized by the interface trap density,  $D_{it}$ , and the border trap density,  $N_{bt}$ , respectively, are unavoidable and usually large [31,32]. This significantly constrains the MOSFET performance since the charging or discharging of the defect-induced trap states across the band gap greatly reduces the movement of the Fermi Level with gate voltage, figure 1.3(a), finally resulting in increased SS [33] and reduced  $I_{on}$  and extrinsic  $g_m$  [34]. The InAs/high- $\kappa$  system usually results in  $D_{it}$  and  $N_{bt}$  in the order of  $10^{13}$  eV<sup>-1</sup>cm<sup>-2</sup> and  $10^{19}$  eV<sup>-1</sup>cm<sup>-3</sup>, respectively [35–38], which is far higher than in the Si/SiO<sub>2</sub> system [39,40]. Another challenge is the narrow band gap of InAs, 0.35 eV [20]. The first trouble of using a narrow band gap channel is the impact-ionization and band-to-band tunneling (BTBT) at the gate-drain

1: Background

**Figure 1.3:** (a) Band diagrams of the MOS gate stack with and without trap states. (b) Band diagram of the gate-drain junction, showing the impactionization and band-to-band tunneling. (c) Band diagram of the MOS gate stack, showing the problem due to the small density of state (DOS) of InAs. (d)-(e) Parasitic resistances and capacitances. In the subscripts, s, m, b, w, and o denote contact, metal, bottom, wire, and overlap, respectively, and S, D, and G denote source, drain and gate.

junction, figure 1.3(b). This increases the MOSFET output conductance,  $g_d$ , hence reducing the device self-gain  $g_m/g_d$  and cutoff frequency  $f_t$  [41, 42], and reduces the breakdown voltage, hence restricting the transistor power applications [43,44]. Besides, the narrow band gap is always associated with a small density of state (DOS) [20], and thus another problem arises due to the quantum capacitance limit (QCL), figure 1.3 (c). In brief, scaling the dielectric thickness cannot give a continuous increase in gate capacitance density since  $C_g$  is finally dominated by quantum capacitance (or semiconductor capacitance),  $C_q$ , which is proportional to semiconductor's DOS.

Parasitics outside the MOSFETs pose another type of challenge, figure 1.3(c). The existence of these components dramatically hinders the extrinsic performance of the MOSFETs, which to some extent is more crucial than the intrinsic. As shown in the figure, the parasitic capacitances can severely slow down the ICs since charging/de-charging these capacitors takes time [18], whereas the parasitic resistances limits the effective voltage drops between electrodes, hence degrading  $I_{on}$  and  $g_m$  significantly. Besides, the existence of these components makes the characterization of the intrinsic performance

"template" — 2016/3/21 - 15:04 — page 10 - #26

Vertical III-V/High- $\kappa$  Nanowire MOS Capacitors and Transistors

#### difficult.

The thesis aims at solving the problems related to the challenges from the nanowire MOSFET itself. But before that, methods to reduce the parasitics are developed, since they can conceal the intrinsic performance significantly, as discussed in later chapters.

## 2

## Planar InAs/High-κ MOS Gate Control

FIGH-efficiency InAs/high- $\kappa$  metal-oxide-semiconductor (MOS) gate control is a key to realize a high-performance MOSFET. However, the gate performance is hampered in reality by defects resident both inside the high- $\kappa$  layer and at the high- $\kappa$ /InAs interface. These defects contribute a significant amount of trap states across the band gap, which restricts the control of Fermi-level movement [45], therefore increasing the sub-threshold slope, and reducing the extrinsic transconductance as well as the charge mobility and the on-state current. Indeed, the large defect density is one of the most important challenges for III-V material to replace Si in the existing technology nodes [40]. Thus, a major task in the development of next-generation high-speed, low-power electronics is to reduce these trap states down to tolerable levels.

To manage the task, reliable characterization techniques both to profile the trap density across the band gap and to determine the chemical species across the interface are necessary. Planar MOS capacitance-voltage (C-V) measurements in combination with X-ray photoelectron spectroscopy (XPS) measurements have become a staple in studying MOS gate stacks. For over 70 years, there have been great achievements, based on these techniques [46–49], which enables understanding and further improvements of the III-V MOS performance. The results have revealed that high performance MOSFETs rely intimately on the detailed processing conditions including substrate surface preparation, dielectric deposition, and post-annealing etc. The planar MOS study thus is the starting point of the thesis to understand the InAs/high- $\kappa$  system. The knowledge gained from the study can either be used to improve the planar InAs/high- $\kappa$  MOSFET performance or be transferred directly to the nanowire MOSFET technology.

#### 2.1 SUBSTRATE SURFACE

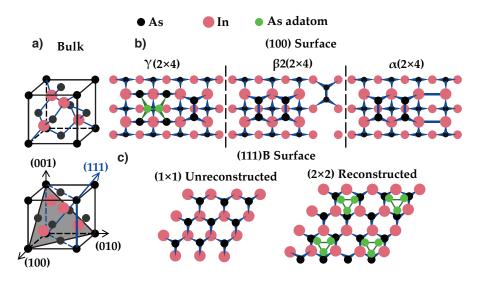

The control of the high density of structural defects at the InAs surface is the most task crucial for the InAs/high-κ MOS gate stack. Naturally, the surface structure is determined by the bulk crystal, and for the case of bulk InAs, it crystalizes into the so-called zinc-blend (ZB) structure, figure 2.1(a). The structure consists of two interlocking face-centered-cubic (FCC) lattices, one of each constituted by In and As, respectively, with the basis at (0,0,0) and (1/4,1/4,1/4). Each In atom (or As atom) is bonded with four As atoms (or In atoms) at four neighboring tetragonal sites. InAs has partially ionic and partially covalent bonds with a lattice constant of 6.0584 Å, and the covalent radiuses of 1.44 Å and 1.2 Å for In and As atoms, respectively. In general, the surface structure cannot repeat exactly its bulk structure due to the bond scission at the terminating plane. The resulting surface after bond scission is full of "dangling" bonds and is energetically unstable. To reduce the free energy of the system, adjacent surface atoms tend to bond together forming dimers, accompanied by a re-arrangement of the atoms on the entire surface, and the resulting surface usually has a highly ordered structure but significantly different from the bulk crystal. This process is termed surface reconstruction.

The InAs semiconductor can be terminated in various planes, as depicted in figure 2.1(a). The most widely studied is the (100) plane. The InAs(100) surface is a polar unstable surface, which can end up with either the In or the As monolayer. The As terminated surface could be beneficial since it provide an As cap, which may prevents the formation of the highly stable In oxide that is detrimental for the device performance, as discussed in later sections. In addition, bonds on the (100) surface exhibit a more covalent nature. The resulting possible reconstructions are very complicated [50–52], ranging from the In-rich  $(4\times2)$  In-dimer surface to the As-rich  $(4\times4)$  As-trimer surface, depending on the specific growth conditions. Figure 2.1(b) illustrates the most common III-V (100) surface reconstructions within the transition region of  $(2\times4)$  between the two extremes. As can be seen, an InAs(100) surface could consist of a large amount of In or As dimers, vacancies as well as dangling bonds and anti-sites (not shown). Besides, the surface In proportion steadily increases from the As-rich  $\gamma(2\times4)$  towards the In-rich  $\alpha(2\times4)$ . These surface species will influence the final MOS performance significantly [53]. Compared to the (100) surface, the (111)B surface shows more promising character but MOSFETs based on the surface have not been well studied yet. The InAs (111)B surface is As-terminated but with a larger surface atom density than (100). However, the surface bonds exhibit more ionic nature. Astonishingly, stable unreconstructed (111)B surfaces are prevalently found [54], although some researchers also found a (2×2) As trimer reconstruction on the As-

2: Planar InAs/High-κ MOS Gate Control

**Figure 2.1:** (a) Zinc-blende crystal structure of bulk InAs. (b)-(c) Possible surface reconstructions of InAs (b) (100) surface and (c) (111)B surface. The As adatoms are usually found on As-rich surfaces obtained by growing the crystal with high As pressure and low temperature [58], and can be thought of as the opposite to the As surface vacancies.

rich surface [55], figure 2.1(c). In the unreconstructed condition, As dangling bonds are occupied. Mankefors et al. demonstrated that the the stability of the surface results from the charge redistribution over several atomic layers so that the charges are transferred from the surface to the bulk [54]. In later sections, MOS C-V characteristics using both surfaces are studied in detail. The (111)A surface is also studied in the thesis, which is an In-terminated surface with  $(2\times2)$  In vacancies in general [56], however, all devices made on this surface show huge leakage currents, and thus no electrical measurements were performed. This could be attributed to the fact that there is a 2D electron gas layer (2DEG) commonly observed across the clean InAs (111)A surface, opposite to the unreconstructed (111)B surface that cannot host a 2DEG [57].

#### 2.2 NATIVE OXIDES AND ATOMIC LAYER DEPOSITION

Compared to defects introduced by the surface reconstruction, it is found in Paper I that the quality of the InAs/high- $\kappa$  interface is influenced more by the presence of various native oxides due to the narrow band gap of InAs (as shown later in the following sections). InAs surfaces exposed to air usually consist of As 5+, As 3+ and In 3+ oxides [59], resulting in In-O or As-O

**Table 2.1:** List of stable InAs oxides and their bulk oxide Gibbs free energies  $\Delta G$  (kcal/mol) [60]

|       |                                | U         | •         |           |

|-------|--------------------------------|-----------|-----------|-----------|

| Oxide | As <sub>2</sub> O <sub>3</sub> | $As_2O_5$ | $In_2O_3$ | $InAsO_4$ |

| ΔG    | -137.7                         | -187      | -198.6    | -209.4    |

bonding configurations across the surface that provide trap states. In table 2.1, stable InAs oxides and their bulk oxide Gibbs free energies are listed. It can be seen that, in general, As native oxides are less stable than In oxides and are readily removed.

It has been found that at elevated temperatures, the unstable As oxides in InAs will convert to more stable ones through the reaction [60]

$$As_2O_3 + 2InAs \rightarrow In_2O_3 + 4As, \ As_2O_5 + In_2O_3 \rightarrow 2InAsO_4$$

(2.1)

A surface pre-cleaning procedure before the high- $\kappa$  deposition, usually termed as "passivation" in device technologies, is found to reduce the amount of the native oxides by either reacting with the As-O and In-O bonds or by forming e.g. In-Si bonds in advance, hence preventing the As-O and In-O bond formation. Commonly used cleaning chemicals include chalcogenides (e.g.  $(NH_4)_2S_x$  solutions [61]), or etchants (e.g. HCl solution [62]). Alternatively, other surface treatments such as As-flux capping [63], hydrogen plasmas [62], Si over-layer growth on III-V [64] etc. are also used. These approaches are again more efficient in reducing the amount of unstable As oxides than In oxides. In fact, the most efficient approach in removing the native oxides is through the "self-cleaning" during the high- $\kappa$  dielectric atomic layer deposition (ALD) [61], as explained below.

ALD is based on the hydrolysis reaction between water and alkyls such as trimethyl-aluminum (TMAl) and Tetrakis(dimethylamino)hafnium (TDMA-Hf). To deposit e.g. Al<sub>2</sub>O<sub>3</sub> on InAs, short pulses of TMA are introduced into the ALD reactor chamber. Each TMA pulse is followed by a short water pulse. The hydrogen bonds in water will break the methyl bonds in TMA, forming gaseous CH<sub>4</sub> and leaving a Al-O layer on the substrate surface. One such a cycle of pulses usually gives 1 Å Al<sub>2</sub>O<sub>3</sub>. In-situ XPS measurements [47,61,65] have revealed that the ligand exchange reaction also occurs between metal precursors and surface native oxides, and several cycles of TMAl pulses are found to greatly reduce the As native oxides by converting As-O bonds to As-Al or As-Hf bonds. However, ALD is less efficient in removing In<sub>2</sub>O<sub>3</sub> since In-O-Al or In-O-Hf bonds usually results from the ligand exchange reaction. Besides, the ALD process, or any oxidation process, creates other types of defects such as dangling bonds and dimers etc. at the III-V/high-κ

2: Planar InAs/High-κ MOS Gate Control

interface [32]. In addition, the ALD deposited high- $\kappa$  material is usually not purely amorphous but polycrystalline.

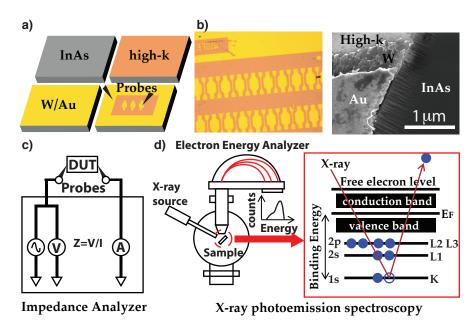

#### 2.3 MOS CAPACITOR FABRICATION AND MEASUREMENTS

Planar MOS capacitors were fabricated on n-type InAs substrates with (100) and (111)B orientations. The doping density for the two cases were comparable,  $3.5\times10^{16}~\rm /cm^3$  and  $7.5\times10^{16}~\rm /cm^3$  for (100) and (111)B surfaces, respectively. The samples were pre-treated in HCl solution (HCl:H<sub>2</sub>O 1:1) for 1 min and then rinsed in 2-isopropanole (IPA) for 15 s. 80 cycles of high- $\kappa$  oxide (24 cycles for XPS measurements) were deposited on the sample under various deposition temperatures in a Cambridge Nanotech Savannah-100 ALD chamber, using either TMAl or TDMA-Hf and water as precursors. The deposition always started by one alkyl pulse for self-cleaning. W/Au contacts were then sputtered, followed by patterning using UV lithography and dry/wet etching of the metals. After that, some samples were annealed in hydrogen forming gas at 400  $^{o}$ C for 5 min. Figure 2.2 (a) shows the schematic of the processing as well as the optical microscope image of the final devices plus a SEM image of the capacitor cross-section.

The C-V characteristics of the MOS capacitors were measured by a 4294A impedance analyzer. A simplified schematic of the measurement setup is shown in figure 2.2(b), which includes a signal source, a voltmeter and an ammeter. The input signal to the device under test (DUT) consists of a small AC signal superimposed on a DC bias sweep. In reality AC and DC voltages are supplied separately. The vectors (both magnitudes and phase angles) of the small signal current and voltage are measured by the voltmeter and ammeter, from which the complex impedances of the DUT can be obtain. In reality, the ammeter is replaced by an I-V converter consisting of an operational amplifier with a negative feed-back to increase the accuracy and robustness of the measurements, and, besides, an open-short-load calibration before the measurements is necessary in order to completely remove the parasitic components inside the measurement setup. The frequency bandwidth of the small signal is from 40 Hz to 110 MHz. To characterize the interfacial chemistry, samples with 24 cycles of high- $\kappa$  oxide and of uncoated references were measured by XPS at beam-line I311 of the MAX-II synchrotron, as illustrated in figure 2.2(c). An X-ray with energy  $E_{photon}$  was incident onto the sample, which ejected core electrons of different surface species. The energy difference between the Fermi level and the core level where the excited electron previously resided is called binding energy, E<sub>binding</sub>, and for different species, E<sub>binding</sub> of the same core level is different. Hence the energy can be used as a finger print to identify the existence and amount of different

**Figure 2.2:** (a) Schematic of the planar MOS capacitor fabrication. (b) Optical microscope image of the MOS capacitors and SEM image of the capacitor cross-section. (c) Schematic of the Impedance analyzer setup. (d) XPS measurements.

species. The generated electrons were collected through an energy analyzer where a magnetic field was applied. Under the Lorentz force, the trajectories of electrons with different ejection kinetic energies,  $E_k$ , bended with different radius, which enabled the energy selective election counting and thereby the chemical species quantification. The measured  $E_k$  is converted to  $E_{binding}$  by  $E_{binding} = E_{photon} - (E_k + \Phi)$ , in which  $\Phi$  is the work function that is the energy difference between the Fermi level and the free electron level.

#### 2.4 DEVICE CHARACTERIZATION

#### 2.4.1 MOS CAPACITOR C-V CHARACTERISTICS

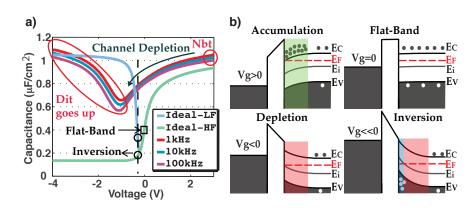

In this subsection, the measured C-V degradation due to trap states will be discussed. Figure 2.3 shows the comparison of measured and simulated C-V curves as well as the band diagrams of different bias regimes. The measured capacitances are determined from the measured impedances by first subtracting the series resistance in the probes and contacts and then adopting a model with a capacitor in parallel with a conductor. The simulated C-V

2: Planar InAs/High-κ MOS Gate Control

**Figure 2.3:** (a) Comparison between the measured and ideal InAs/high- $\kappa$  C-V characteristics. (b) Band diagrams of different bias regions.

curves are obtained by solving Poisson's equation using Fermi-Dirac statistics [49,66] with the non-parabolic band effect considered [48], but contains no trap states, hence reflecting the ideal C-V characteristics. For the ideal cases, accumulation, depletion and inversion can be readily reached since the Fermi level can be easily tuned across the band gap without hinderance. A steep slope of the capacitance decrease between 1 V and 0 V reflects a quick depletion of the channel. The capacitance finally reaches a minimum of 0.2  $\mu$ F/cm<sup>2</sup>, corresponding to the maximum depletion width. In addition, the frequency modulation in the inversion region (negative biases) should be strong due to the larger time constant of the minority carriers. In contrast, the measured C-V curves of InAs/high-κ MOS capacitors are far from ideal. In the case, the Fermi level can only be tuned between accumulation and depletion, and larger voltage span is needed to charge and de-charge the trap states inside the band gap. The C-V curves, thus, show a significant stretching. Besides, an additional trap capacitance  $C_{it}$ , originating from the interface trap response to the input ac signal, is added to the intrinsic semiconductor capacitance C<sub>s</sub> at each bias, which increases the total measured capacitance. This effect can most clearly be seen from the increased minima of the measured C-V curves. Finally the  $C_{it}$  is also frequency dependent through a trap time constant,  $\tau$ . The characteristic frequency of  $C_{it}$  can be written as [67]

$$f_c = \frac{1}{\tau} = \frac{\sigma v_t N_C}{exp(\Delta E/kT)},\tag{2.2}$$

where  $\Delta E$  is the energy difference between the Fermi level and the conduction band edge (CBE); k, T,  $\sigma$ ,  $v_t$ , N<sub>C</sub> are the Boltzmann constant, temperature, trap cross-section, electron thermal velocity and effective electron density of

state in the conduction band, respectively. This means that the frequency modulation of  $C_{it}$  becomes strong as the Fermi level can be moved further away from the CBE (larger  $\Delta E$ ). In the figure, however, the C-V curves show a fairly small frequency dependance at negative biases, indicating that the Fermi level movement is restricted nearby the CBE. It is thus believed that the rise in capacitance below -1.5 V does not result from the minority carrier response, but from an increased interface trap density (hence increased  $C_{it}$ ) towards mid-gap. Finally, a frequency dispersion in the strong accumulation region is common observed, which originates from the response of trap states inside the oxide (border traps) [68]. The non-ideality of the measured C-V curves, in fact, contains all the information of traps in the system.

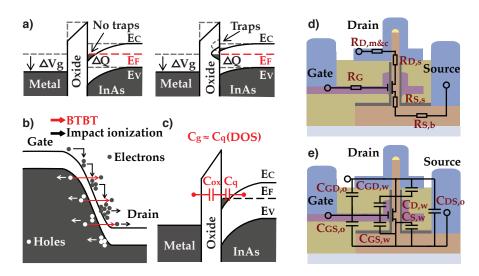

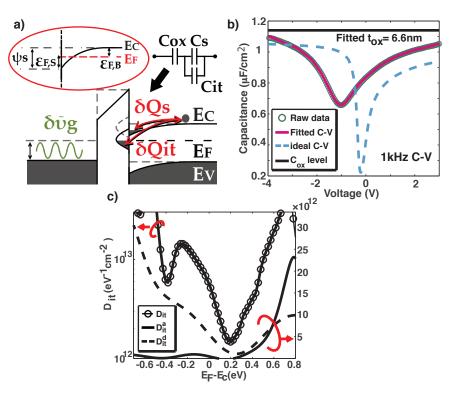

#### 2.4.2 TRAP CHARACTERIZATION BY LOW FREQUENCY C-V FITTING

To characterize the interfacial trap density across the energy gap, a low frequency C-V fitting method has been developed. At low frequencies, the charge response of interfacial defect states can follow the input small signal variation, as illustrated in figure 2.4(a). Under such circumstances, these states act as a capacitor,  $C_{it}$ , parallel to the intrinsic semiconductor capacitor,  $C_s$ . The total capacitance measured can thus be modeled as

$$\frac{1}{C_{tot}(V_g)} = \frac{1}{C_{ox}(V_g)} + \frac{1}{C_s(V_g) + C_{it}(V_g)},$$

(2.3)

where  $C_{ox}$  is the oxide capacitance. The next task is thus to evaluate  $C_{tot}$  and  $V_g$  at each relative Fermi level location ( $E_F$ - $E_c$ ) with the interface trap density profile, i.e.  $D_{it}(E_F$ - $E_c)$ , and  $C_{ox}$  as the fitting parameters until the measured and evaluated C-V curves fit each other.

$C_s$  can be evaluated by solving Poisson's equation, which, by applying Gauss theorem, can be expressed as

$$Q_{s} = sign(\varepsilon_{F,S} - \varepsilon_{F,B}) \sqrt{-2\epsilon_{s}kT \int_{\varepsilon_{F,B}}^{\varepsilon_{F,S}} [N_{d}^{+} + p(\varepsilon_{F,S}) - n(\varepsilon_{F,S})] d\varepsilon_{F,S}}, \quad (2.4)$$

where  $Q_s$  is the semiconductor surface net charge, p and n are the hole and electron densities, respectively,  $N_d^+$  is the ionized dopant concentration,  $\varepsilon_s$  is the InAs dielectric constant, and  $\varepsilon_{F,S}$  and  $\varepsilon_{F,B}$  are relative Fermi level location at the interface and inside the bulk normalized to the thermal energy, kT, as illustrated by the inset in figure 2.4(a). n, p and  $N_d^+$  can be evaluated from the Fermi-Dirac statistics, which gives

$$n = \frac{2N_C}{\sqrt{\pi}} \int_0^\infty \frac{\sqrt{x(1+\alpha x)}(1+2\alpha x)}{1+exp(x-\varepsilon_{F,S})} dx \ (\alpha = kT(1-m_e^*)^2/E_g),$$

(2.5)

2: Planar InAs/High- $\kappa$  MOS Gate Control

Figure 2.4: (a) Band diagram and low frequency MOS capacitor charge response to the small input signal.  $E_C$ ,  $E_V$  and  $E_F$  represent the semiconductor conduction band edge, valence band edge and Fermi level, respectively.  $\delta Q_s$  and  $\delta Q_{it}$  are small variations of charge density in the semiconductor surface energy levels and the trap states, in response to the low frequency small input signal  $\delta_V$ . The inset shows how the surface band bending  $\psi_s$ , relative Fermi level location at the interface  $\varepsilon_{F,S}$  and in the bulk  $\varepsilon_{F,B}$  are related. (b) Lowfrequency C-V fitting. (c) Trap densities used in achieving good fit in (b).

$$p = \frac{2N_V}{\sqrt{\pi}} \int_{0}^{\infty} \frac{x}{1 + exp(x - (\varepsilon_{F,S} + \varepsilon_g))} dx,$$

(2.6)

and

$$N_d^+ = \frac{N_d}{1 + 2exp(\varepsilon_{F,S})},\tag{2.7}$$

where  $N_C$  and  $N_V$  denote the effective density of states (DOS) in the conduction and valence bands. The  $\alpha$  in equation 2.5 is the nonparabolicity factor, in which  $m^*$  and  $E_g$  are the electron effective mass and band gap of InAs.

Since for InAs, the DOS in the conduction band is small, the Fermi level can easily move quite far into the conduction band. The non-parabolic band effect thus become significant [48]. For p, one can simply assume a Fermi-Dirac distribution of holes. In addition, the ionization effect of dopants is considered by assuming that the dopant level overlaps the CBE.  $C_s$  then can be evaluated by

$$C_s(\varepsilon_{F,S}) = dQ_s(\varepsilon_{F,S})/d\varepsilon_{F,S}$$

(2.8)

The  $C_{it}$  can be obtained the same way, i.e.

$$Q_{it}(\varepsilon_{F,S}) = \int_{-\infty}^{\varepsilon_{F,S}} D_{it}^{a}(x) dx - \int_{\varepsilon_{F,S}}^{\infty} D_{it}^{d}(x) dx, \quad C_{it}(\varepsilon_{F,S}) = \frac{dQ_{it}(\varepsilon_{F,S})}{d\varepsilon_{F,S}}, \quad (2.9)$$

where the  $Q_{it}$  is the net electron density in interface states, similar to  $Q_s$  in equation 2.8. The interface trap states are classified into donor type and accepter type. The trap density of the donor type,  $D_{it}^d$ , peaks below midgap, whereas the trap density of the acceptor type,  $D_{it}^a$ , peaks above mid gap. In the fitting, both  $D_{it}^d$  and  $D_{it}^a$  are simulated by a Gaussian function with coefficients as the fitting parameters. The donor type trap is positive when empty and neutral when charged. The acceptor type trap, on the contrary, is neutral when empty and negative when charged, as shown in equation 2.9.

Finally  $\varepsilon_{F,S}$  can be related to  $V_g$  by

$$V_g(\varepsilon_{F,S}) = \psi_s + \frac{Q_s(\varepsilon_{F,S})}{Cox} + \frac{Q_{it}\varepsilon_{F,S}}{Cox}, \text{ where } \psi_s = \frac{kT(\varepsilon_{F,S} - \varepsilon_{F,B})}{q}.$$

(2.10)

$\psi_s$  and q are the surface band bending, figure 2.4(a), and the elementary charge, respectively.

The measured C-V curve can be perfectly fitted by the approach, as shown in figure 2.4(b), using the trap density profiles in figure 2.4(c). As can be seen, due to the low DOS of InAs, the ideal C-V curve cannot reach  $C_{ox}$  level under strong accumulation because of the smaller  $C_s$  in series with  $C_{ox}$ . Smaller  $C_s$  reduces the gain in  $t_{ox}$  scaling for enhancement-mode MOSFETs, making it readily reach the quantum capacitance limit. However, the low frequency C-V fitting method have a few shortcomings. Firstly, it cannot discriminate the densities of surface border traps from the interface traps, so the evaluated  $D_{it}$  represents the upper limit of interfacial defects. Secondly, for  $D_{it}$  below  $10^{12}$  eV $^{-1}$ cm $^{-2}$ , the method will introduce errors since the difference between the real and ideal C-V curves will be too small to resolve. Thirdly the accuracy will gradually decrease towards the valence band edge and further into the conduction band since the values evaluated there are based on interpolation rather than on real measurements. However, the approach is still far better, to some extent, than the commonly used conductance method or Terman

2: Planar InAs/High-κ MOS Gate Control

method [66] since the widest energy range of  $D_{it}$  profiling is obtained, and no true high frequency C-V curves or conductance peaks are needed, which are usually not observed for room temperature C-V measurements of InAs MOS capacitors.

#### 2.4.3 ALUMINUM OXIDE

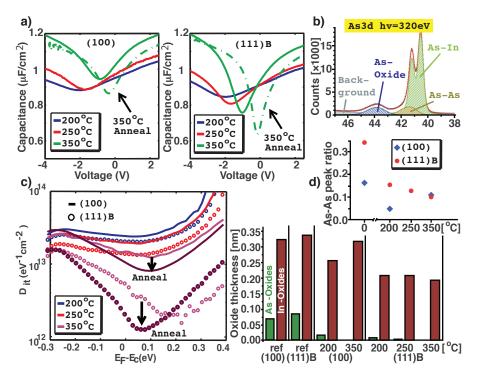

The InAs/Al<sub>2</sub>O<sub>3</sub> gate stack is studied in detail. Figure 2.5(a) shows the measured C-V characteristics of InAs/Al<sub>2</sub>O<sub>3</sub> capacitors with different InAs orientations and Al<sub>2</sub>O<sub>3</sub> deposition temperatures. In general, the (111)B surfaces show better C-V modulation than (100) surfaces, e.g. less C-V stretch-out, lower capacitance minimum etc., which indicates better interface quality. Besides, a higher Al<sub>2</sub>O<sub>3</sub> deposition temperature and the use of a post-annealing step are found to improve the interface for both surfaces. Figure 2.5(c) shows the corresponding  $D_{it}$  profiles extracted using the low frequency fitting method. As can be seen, the (111)B surfaces have smaller D<sub>it</sub> values in general. Besides, when increasing the thermal budget, through the use of either a high Al<sub>2</sub>O<sub>3</sub> deposition temperature or a post annealing step, a significant drop of  $D_{it}$  near the CBE is observed for both surfaces. For trap states near the mid gap (about -0.15 eV), however, a strong reduction of  $D_{it}$  is only observed for the (111)B surface. Figure 2.5(b) shows different components of the fitted As 3d spectra measured by XPS, from which the amounts of different surface species can be extracted, figure 2.5(d). As can be seen, the (111)B surfaces, after ALD deposition, have smaller amounts of native oxides (but larger amounts of As-As bonds) than (100) surfaces in general, indicating a more efficient self-clean during ALD for the (111)B surface. Besides, by increasing the thermal budget, the amount of the As native oxides keeps decreasing for both surface orientations, whereas that of the In-oxides slightly decrease for (111)B surfaces, but increase for (100) surfaces. A similar trend to In-oxides is found for As-As bonds, as shown in the inset. The As-As bonds can come from either dimers or anti-sites, and it is difficult to distinguish their origin.

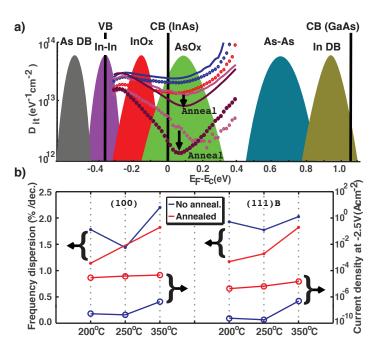

The comparison between C-V and XPS results indicates a correlation between As-oxides and  $D_{it}$  near the CBE, and a correlation between In-oxides and  $D_{it}$  towards the mid-gap. By combining the conclusion of this work with the current understanding on GaAs [32,53], the possible origins of trap states across the band gap for both InAs and GaAs are qualitatively illustrated and compared in figure 2.6(a). As can be seen, due to the narrow band gap of InAs, the dominant trap origins near the CBE and midgap, which are critical for n-MOSFET applications, are changed, as compared to GaAs. For the latter, the trap origins near the CBE and midgap are Ga-dangling bonds and As-As dimers, respectively [32]. The strategies to reduce the gap states for small

**Figure 2.5:** (a) Comparison of the deposition temperature and annealing influence on the 1 kHz C-V characteristics of (100) and (111)B samples. (b) XPS spectrum with fits for various species of the As 3d core-level obtained with a photon energy of 320 eV. (c)  $D_{it}$  v.s.  $E_t$ - $E_c$  extracted using the low frequency fitting method as a function of InAs orientation, oxide deposition temperature and annealing. The x-axis denotes the position of the trap level  $E_t$  with respect to the conduction band edge  $E_c$ . (d) Absolute thicknesses of Asoxide and In-oxide, extracted from the measured As 3d and In 3d spectra, as a function of the high- $\kappa$  deposition temperature. The inset shows the relative intensity of the spectral component of As-As bonds, as compared to the bulk In-As bonds, for different high- $\kappa$  deposition temperatures.  $0^o$ C refers to the corresponding reference samples without high- $\kappa$  ALD.

band gap InAs is hence far different than that for the larger band gap GaAs, and since it is easier to decomposed the As-oxides than to remove the Gadangling bonds and dimers, it could be beneficial to use InAs as the channel material also in terms of the gate electrostatic control. Although the removal of In oxides is difficult, it could be managed by fine control of the surface termination or facets as for the case of nanowires.

The border traps inside the high- $\kappa$  layer can be qualitatively studied by eval-

**Figure 2.6:** (a) Comparison of the possible trap state origins across the band gap between InAs and GaAs, adapted after the works by Wang et al. [32] and Robertson [53]. (b) Accumulation capacitance frequency dispersion and gate leakage current density at  $V_g$  of -2.5 V as a function of the processing condition.

uating the frequency dispersion of the accumulation capacitance  $C_a$  [68,69], as shown in figure 2.3(a). The slope of  $C_a$  v.s.  $\log(f)$ , in the unit of percentage per decade, is proportional to the border trap density,  $N_{bt}$ , according to Heiman and Warfield's charge tunneling model [68]. Figure 2.3(b) shows the comparison of frequency dispersion and gate leakage current density for different samples. It can be seen that the high deposition temperature in general results in worse high- $\kappa$  layer and increased leakage. This could be due to the high- $\kappa$  layer crystallization, which increases the amount of traps and tunneling leakage. Annealing in forming gas can passivate the defects since hydrogen atoms can penetrate into the layer, however it usually results in an elevated gate leakage since the external atom penetration introduces additional current paths. This also significantly limits the use of post-annealing in the MOSFET fabrication. Thus to obtain both a better interface and a better high- $\kappa$  layer, a two-temperature deposition scheme can be a good solution.

**Figure 2.7:** (a) Comparison of (a)  $D_{it}$ , (b) frequency dispersion and gate leakage current density for MOS capacitors with  $Al_2O_3$  and  $HfO_2$  using both a single-temperature and a 2-temperature deposition schemes. The inset in (b) shows the schematic of the proposed optimal gate stack for InAs/high-κ MOSFETs.

#### 2.4.4 HAFNIUM OXIDE

The InAs/HfO<sub>2</sub> gate stack is also studied, and since the HfO<sub>2</sub> has far higher  $\kappa$  (table 1.1), it is more promising than Al<sub>2</sub>O<sub>3</sub>. However, HfO<sub>2</sub> in general is far inferior in terms of quality. Figure 2.7 shows the comparison of  $D_{it}$ , frequency dispersion and gate leakage of HfO2 (blue, solid) and Al2O3 (red, solid) deposited under the same temperature, 250 °C, and on the same InAs surface, (111)B. The poorer D<sub>it</sub> profile reflects a less efficient self-cleaning of native oxides for HfO<sub>2</sub>. The larger frequency dispersion and leakage, on the other hand, are due to the fact that HfO2 can crystalize at lower temperature than Al<sub>2</sub>O<sub>3</sub>, and hence it is a less amorphous dielectric. Results of using a 2-temperature HfO<sub>2</sub> deposition scheme (2T) is also shown (dashed), in which the first 10 cycles of HfO<sub>2</sub> are deposited at 250 °C and the remaining 70 cycles are deposited at 150 °C. By comparing the 2T HfO<sub>2</sub> and single-temperature HfO<sub>2</sub> results, it can be seen that the interface quality is preserved for the 2T scheme due to the high temperature deposition of the first 10 cycles, whereas a significant improvement of the high- $\kappa$  layer quality is gained. In the future, since the  $HfO_2$  has higher  $\kappa$  but poorer quality on InAs, a sandwiched interfacial Al<sub>2</sub>O<sub>3</sub> deposited at high temperature between the substrate semiconductor and the low-temperature deposited HfO2 could be a solution, as shown by the inset in figure 2.7(b), to preserve the benefits of both high- $\kappa$  materials as much as possible.

## 3

## InAs/High-κ Verical Wrap-Gated Nanowire MOS Gate Control

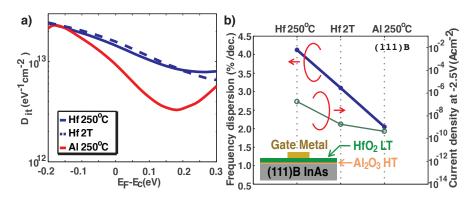

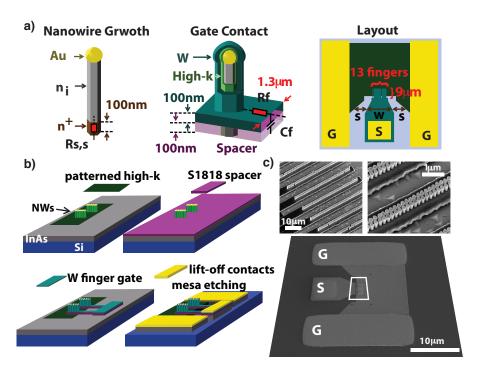

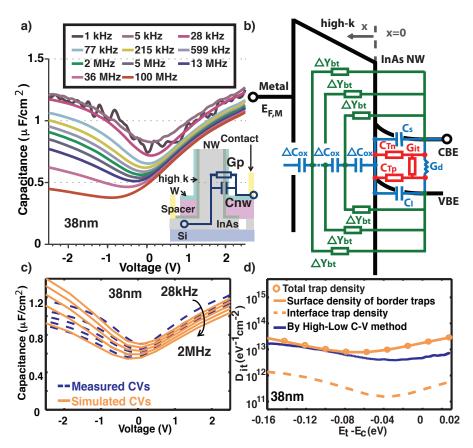

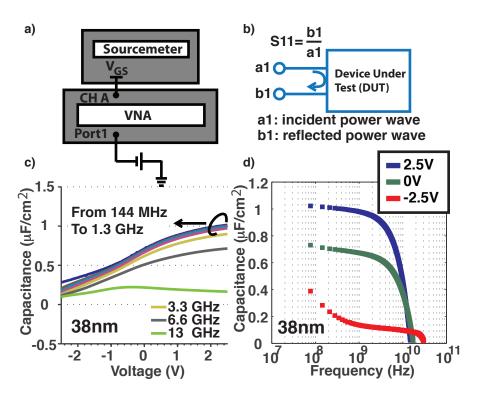

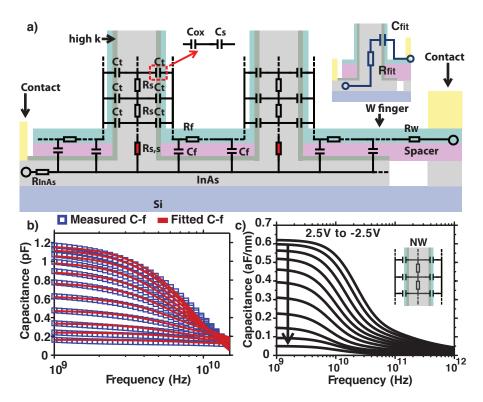

EVELOPING the C-V technique to investigate the vertical GAA nanowire MOS gate control is challenging, especially when the conventional geometry of vertical nanowire MOSFETs needs to be conserved so that the knowledge gained is applicable to these devices. As shown in figure 1.3, in order to approach the intrinsic performance of a nanowire MOSFET, the spacer layers between electrodes needs to be thin enough [70] so that the associated series resistances are minimal. This, however, results in large parasitic overlapping capacitances between contacts, which can readily conceal the measured intrinsic MOS C-V characteristics that are usually small. This is also a reason why detailed C-V studies on vertical nanowire MOS capacitors are seldom found in literature [71,72]. In the thesis, the problem is solved by using a finger gate contact approach [18], which, hence, enables detailed D<sub>it</sub> profiling and gate control optimization for vertical nanowire MOSFETs. In addition, radio-frequency (RF) C-V characterization of vertical GAA nanowire MOS capacitors is realized for the first time. Combined with a complete small-signal equivalent circuit model ranging over the entire measurement frequencies, this technique allows us to evaluate both interface and border traps, channel resistivity, and quality factor of the vertical GAA nanowire MOSFETs. In this chapter, the nanowire growth will be discussed first, since, as demonstrated in chapter 2, the gate stack performance relies intimately on the semiconductor surface condition and nanowires usually exhibit large differences in terms of surface condition, as compared to their planar counterparts. After that, detailed D<sub>it</sub> profiling for nanowire MOS gate stacks is presented. Finally, The RF C-V technique is introduced.

#### 3.1 NANOWIRES USED FOR MOSFETS

#### 3.1.1 NANOWIRE GROWTH

Nanowires can be formed in various ways, either top-down or bottom-up. In the thesis, nanowires are grown by low pressure (100 mbar) metalorganic vapor phase epitaxy (MOVPE) using Au as seed particles [13]. Figure 3.1(a) illustrate how a horizontal-reactor cold-wall MOVPE system works, in which hydrogen is used to carry the metalorganics (mainly group III and dopant precursors) stored in the bubblers into the reaction chamber. Meanwhile, the group V gas is also supplied and except for trimethylantimony (TMSb), most of the group V precursors are gaseous hydrides. The gas flow rates are controlled by mass flow controllers (MFCs). In the reaction chamber, the sample is placed onto a graphite susceptor heated by infrared lamps. Excess gases will be exhausted and burned safely. The chemical reactions during the epitaxial growth are in fact very complicated, including a stepwise release of methyl and hydrogen in precursor gas molecules via either homogeneous or heterogeneous reactions or both. The net reaction for growing InAs can be expressed as

$$In(CH)_3 + AsH_3 \rightarrow InAs + 3CH_4. \tag{3.1}$$

One drawback of MOVPE is that the -CH<sub>3</sub> in metalorganics usually cannot be removed completely due to the incomplete decomposition, leaving some carbon incorporated into the grown material, which contributes to a background doping level for the final devices. [73,74].

In the reaction chamber, figure 3.1(b), the molecules of different gaseous precursors often behave differently during the growth. According to fluid dynamics, the velocity of the flowing gas drops close to the hot susceptor surface, forming a viscous layer. The layer boundary is defined by the velocity drop by 1 %. If the rate-limiting process is the transport of growth species through the layer (left arrow), the growth is termed mass-transport limited growth. On the contrary, if the rate-limiting process occurs on the substrate surface (right arrow), it is called kinetic-limited growth, which gives a temperature dependent growth rate. Trimethylindium (TMIn) can decompose homogeneously in H<sub>2</sub> and completely above 350 °C [75]. This temperature is far lower than the normal growth temperature. Trimethylgallium (TMGa) for example, however, can only decompose completely above 550 °C [76] that is higher than the temperature used for most nanowire growth. Joyce et al. examined the nanowire radial growth rates as a function of the growth temperature for both InAs and GaAs nanowires and found that a masstransport limited growth behavior has already occurred above 420 °C for InAs, but for GaAs, the growth remains kinetic-limited at least above 500 <sup>o</sup>C [77]. This fundamental difference is a main challenge when growing

**Figure 3.1:** (a) Schematic illustration of the MOVPE reactor for crystal growth. (b) Gas velocity profile inside the reaction chamber, as well as two ratelimiting mechanisms for crystal growth. (c) Schematic illustration demonstrating the nanowire growth mechanism. (d) Schematics of ZB and WZ crystal structures, as well as two main types of defects, i.e. twin plane and stacking fault, commonly observed during nanowire growth.

ternary InGaAs nanowires, as discussed in detail in chapter 4.

The reason why nanowires grow cannot be explained merely by thermodynamics. Nanowire growth, to some extent, is a result of the kinetic benefit of nucleation at the vapor-solid-liquid (VLS) triple phase boundary (TPB) [78]. As shown in figure 1.3(c), for growth to proceed, a supersaturation between the supply phase (vapor) and the grown phase (solid) of the growth species, with the chemical potential of  $\mu_v$  and  $\mu_s$ , is first necessary. In the presence of liquid Au seed particles, it requires that  $(\mu_v - \mu_l) > 0$  and  $(\mu_l - \mu_s) > 0$  for nanowires to grow, where  $\mu_l$  denotes the chemical potential of the growth species in the liquid droplets. This thermodynamic requirement seems to say the bulk growth is always more favorable than the nanowire growth since  $(\mu_v - \mu_s)$  is larger both than  $(\mu_v - \mu_l)$  and  $(\mu_l - \mu_s)$ . Taken into account kinetics now, the nucleation rate  $\kappa_{nuc}$  is given by

$$\kappa_{nuc} = v_0 e^{-\Delta G/kT} \left( \Delta G = -V_n \Delta \mu + \gamma_n A_n \right)$$

(3.2)

where k, T and  $v_0$  are the Boltzmann constant, growth temperature and a pre-factor. The change in Gibbs free energy by nucleation,  $\Delta G$ , is given in the bracket, in which the first term describes the energy reduction when a nucleus forms where  $V_n$  and  $\Delta \mu$  represent the nucleus volume and the chemical

potential difference per III-V pair per unit volume between the supply phase and the solid phase; the second term describes the additional energy due to the formation of new interfaces of the nucleus where  $A_n$  and  $\gamma_n$  are the nucleus area and interface energy per unit area. The equation indicates a critical nucleus size where  $\Delta G$  reaches its maximum. Nuclei beyond the size will expand, whereas those below the size will shrink, both of which cause reduction in  $\Delta G$ . This maximum  $\Delta G$  can be thought of as the energy barrier for growth to occur. Comparing same nuclei at the TPB and the substrate, the changes in Gibbs free energies are

$$\Delta G_{TPB} = -V_n \Delta \mu + [Ph\gamma_{vs}x + Ph\gamma_{ls}(1-x)] - Ph\gamma_{lv}xsin\beta + A\gamma_{sn}$$

(3.3)

and

$$\Delta G_{substrate} = -V_n \Delta \mu + Ph \gamma_{vs} + A \gamma_{sn}$$

(3.4)