#### **Code Generation for Custom Architectures using Constraint Programming**

Arslan, Mehmet Ali

2016

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Arslan, M. A. (2016). Code Generation for Custom Architectures using Constraint Programming. [Doctoral Thesis (compilation), Faculty of Science]. Department of Computer Science, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 17. Dec. 2025

# Code Generation for Custom Architectures using Constraint Programming

## **Mehmet Ali Arslan**

Doctoral Dissertation, 2016

Department of Computer Science Lund University

978-91-7753-024-4 (Press) 978-91-7753-025-1 (PDF)

ISSN: 1404-1219 Dissertation 54, 2016 LU-CS-DISS: 2016-06

Department of Computer Science Lund University Box 118 SE-221 00 Lund Sweden

$Email: \verb|mehmet_ali.arslan@| cs.lth.se|$

Typeset using LATEX Printed in Sweden by Tryckeriet i E-huset, Lund, 2016

© 2016 Mehmet Ali Arslan

In loving memory of Mehmet Hadi Arslan (1982 - 2013), and for Yusuf to outmatch...

# **C**ONTENTS

| Po | pulai | Science  | e Summary                                 | 1  |

|----|-------|----------|-------------------------------------------|----|

| A  | knov  | vledgme  | ents                                      | 3  |

| 1  | Intr  | oductio  | on.                                       | 5  |

| 2  | Bac   | kgroun   | d                                         | 9  |

|    | 2.1   | Custor   | m architectures                           | 9  |

|    |       | 2.1.1    | Pipelined execution                       | 9  |

|    |       | 2.1.2    | Single Instruction Multiple Data          | 10 |

|    |       | 2.1.3    | Multi-bank memory and access restrictions | 11 |

|    |       | 2.1.4    | ePUMA architecture                        |    |

|    | 2.2   | Code g   | generation                                | 14 |

|    |       | 2.2.1    | Overview                                  | 14 |

|    |       | 2.2.2    | Instruction selection                     | 14 |

|    |       | 2.2.3    | Instruction scheduling                    | 15 |

|    |       | 2.2.4    | Data assignment                           |    |

|    | 2.3   | Constr   | raint programming                         |    |

| 3  | Rela  | ited Wo  | ork                                       | 21 |

|    | 3.1   | Instruc  | ction scheduling                          | 21 |

|    | 3.2   |          | er Allocation                             |    |

|    | 3.3   | Unifie   | d approaches                              | 23 |

|    | 3.4   | SIMD     | specific approaches                       | 24 |

| 4  | Prol  | blem sta | atement                                   | 27 |

| 5  | Ove   | rview o  | f contributions                           | 29 |

vi CONTENTS

| 6  | Con  | clusions                                                    | 31        |

|----|------|-------------------------------------------------------------|-----------|

|    | 6.1  | Summary                                                     | 31        |

|    | 6.2  | Future work                                                 | 32        |

|    |      |                                                             |           |

| 7  | List | of papers                                                   | 35        |

|    | 7.1  | Papers included in the thesis                               | 35        |

|    | 7.2  | Papers not included in the thesis                           | 36        |

|    |      |                                                             |           |

|    |      | I.D.                                                        | 41        |

| In | clud | ed Papers                                                   | 41        |

| I  | Inst | ruction Selection and Scheduling for                        |           |

|    | DSP  | Kernels                                                     | 43        |

|    | 1    | Introduction                                                | 43        |

|    | 2    |                                                             | 45        |

|    | 3    |                                                             | 46        |

|    | 4    |                                                             | 48        |

|    |      |                                                             | 48        |

|    |      | 1                                                           | 49        |

|    |      | $\varepsilon$                                               | 50        |

|    |      | · · · · · · · · · · · · · · · · · · ·                       | 59        |

|    |      | $\epsilon$                                                  | 61        |

|    | 5    |                                                             | 63        |

|    | 6    | 1                                                           | 66        |

|    | 7    |                                                             | 67        |

|    | /    | Conclusions                                                 | 07        |

| II | Pros | gramming Support for Reconfigurable Custom Vector Architec- |           |

|    | ture |                                                             | 71        |

|    | 1    | Introduction                                                | 71        |

|    | •    |                                                             | 73        |

|    |      |                                                             | 74        |

|    | 2    | $\varepsilon$ $\varepsilon$                                 | 7.<br>75  |

|    | 3    |                                                             | 77        |

|    | 3    | 11                                                          | , ,<br>77 |

|    |      |                                                             | 77<br>78  |

|    |      | 1                                                           | 70<br>83  |

|    |      | 8                                                           |           |

|    |      | •                                                           | 85<br>80  |

|    | 4    | <u> </u>                                                    | 89<br>80  |

|    | 4    | 1                                                           | 89        |

|    |      | 6 11                                                        | 90        |

|    |      |                                                             | 90        |

|    | _    | ·                                                           | 91        |

|    | 5    | Conclusions and future work                                 | 93        |

CONTENTS vii

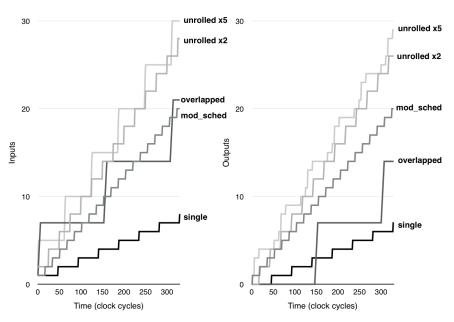

|     | Comparative Study of Scheduling Techniques for Multimedia Ap- |     |

|-----|---------------------------------------------------------------|-----|

| _   |                                                               | )7  |

| 1   |                                                               | 8   |

| 2   |                                                               | 9   |

| 3   | Context                                                       |     |

| 4   | Approach                                                      |     |

|     | 4.1 Scheduling one iteration                                  |     |

|     | 4.2 Overlapping execution                                     |     |

|     | 4.3 Modulo scheduling                                         |     |

| _   | 4.4 Unrolling and modulo scheduling                           |     |

| 5   | Experiments                                                   |     |

| 6   | Discussion                                                    |     |

|     | 6.1 Average throughput                                        |     |

|     | 6.2 Code size                                                 |     |

| 7   | 6.3 Storage requirements and data rates                       |     |

| 7   | Conclusions                                                   | . 3 |

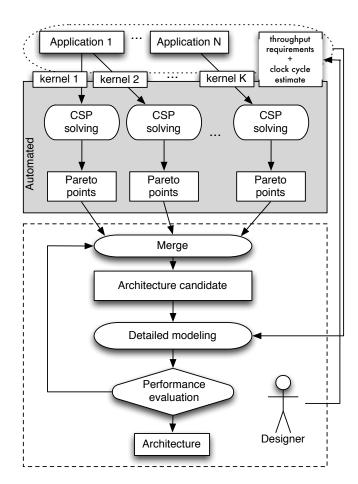

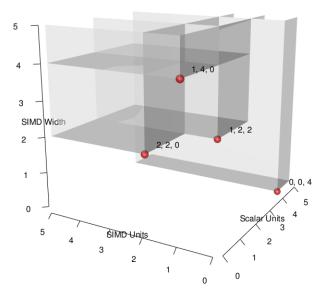

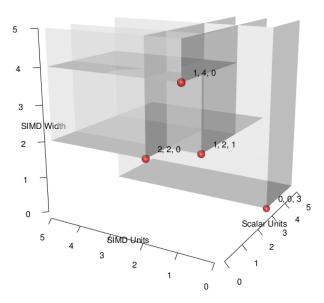

|     | plication-Set Driven Exploration                              |     |

|     | Custom Processor Architectures 11                             |     |

| 1   | Introduction                                                  |     |

| 2   | Related Work                                                  |     |

| 3   | Background                                                    |     |

|     | 3.1 Constraint programming                                    | 0.  |

|     | 3.2 Pareto points                                             |     |

|     | 3.3 Modulo scheduling                                         | 12  |

| 4   | Problem definition                                            | 22  |

| 5   | Approach                                                      | !3  |

|     | 5.1 Pareto points generation                                  | 25  |

|     | 5.2 Modeling details                                          | 26  |

| 6   | Case study                                                    | 27  |

|     | 6.1 Automated Pareto points generation                        | 27  |

|     | 6.2 Candidate selection and evaluation                        | 31  |

| 7   | Conclusions                                                   | 31  |

| Co  | de Generation for a SIMD Architecture                         |     |

| wit | th Custom Memory Organisation 13                              | 57  |

| 1   | Introduction                                                  | 8   |

| 2   | Related Work                                                  | 39  |

| 3   | Background                                                    |     |

|     | 3.1 Constraint programming                                    | 1   |

|     | 3.2 Target architecture: ePUMA                                |     |

| 4   | Problem definition                                            |     |

| -   | 4.1 Architectural assumptions                                 |     |

| •••          | CONTENTS |

|--------------|----------|

| V <b>111</b> |          |

|              |          |

|              |          |

|   | 4.2 Application assumptions |

|---|-----------------------------|

| 5 | Approach                    |

|   | 5.1 Modeling details        |

| 6 | Experiments                 |

|   | 6.1 Assumptions             |

|   | 6.2 Applications            |

|   | 6.3 Results                 |

| 7 | Conclusions and Future work |

# POPULAR SCIENCE SUMMARY

The computation power we expect from the various smart devices we use keeps increasing. Not only do we want faster devices but also less power hungry and energy efficient devices, both for the environment and our personal convenience (remember that "mobile phone" attached to a power plug at all times?).

One way of addressing this demand is to build custom processor architectures that focus on a specific application domain and meet specific demands such as limited power budget, bandwidth requirements, and chip area. As a wise woman once said, "there is no such thing as a free lunch" and in contrast to general purpose processor architectures, these architectures tend to end up notoriously hard to program. This is because of the customization of the hardware to a level that it becomes hard and inefficient to use tools and languages available for general purpose processors. So much so, that they quite often become solely programmable in the machine language specific to the architecture. This means many expert-hours spent in manual translation of relatively simple programs into machine code, rendering the architecture hardly usable by anyone else than the architect.

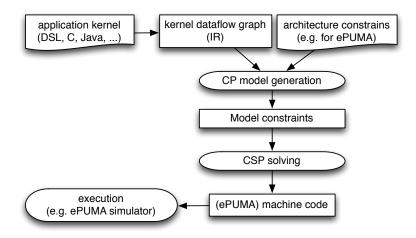

This thesis is the result of our effort to increase the programmability of such custom architectures through automatic code generation, without losing performance compared to code written manually by the architect. Automatic code generation for general purpose architectures is a well studied research area and there exist many straightforward techniques. However, modeling code generation for custom architectures is complicated by the restrictions and constraints of the architectures, and performance requirements that need to be met for the targeted applications.

Constraint programming is a programming paradigm that fits problems defined naturally by constraints and relations between entities. Here, a problem is formulated as a series of constraints over placeholder variables (much like the empty

2 CONTENTS

squares in sudoku) and solved by a constraint solving engine. The solving engine eliminates the infeasible values for each placeholder variable step-by-step, until a solution with each variable assigned to a value is found. As the capabilities and restrictions on the architectures, and the requirements on the applications we target can easily be translated into constraints, we choose constraint programming as our tool for modeling code generation for custom architectures.

Throughout the thesis we demonstrate the effectiveness of our method by comparing to theoretical or practical bounds and code written manually by the architect. The frameworks we present make the architectures easier to program by letting the programmer write in a higher level language than the specific architecture's machine language. Our experiments show that the machine code generated by our frameworks are competitive with the state of the art.

### **ACKNOWLEDGMENTS**

Have We not opened up thy heart,

and lifted from thee the burden

that had weighed so heavily on thy back?

And [have We not] raised thee high in dignity?

And, behold, with every hardship comes ease:

verily, with every hardship comes ease!

Hence, when thou art freed [from distress], remain steadfast,

and unto thy Sustainer turn with love.

**Al-Inshirah, Qur'an** (As rendered by Muhammad Asad)

Five years is a long time. Several times I doubted I would make it to the "Acknowledgments". But here we are. This would not be possible without the help I got from quite many people.

I am forever grateful to Prof. Krzysztof Kuchcinski for his utmost patience and almost fatherly support during these years, besides the excellent supervision he provided me. I was very lucky to have Dr. Flavius Gruian as a friend and supervisor, with his extreme-precision-feedback and bulletproof tolerance to all the "things" I came up with during these five years. Also, between you and me, he is funny.

A special thanks to Dr. Jörn W. Janneck for his supervision and timely brutal honesty, which helped me get back on track when I felt lost the most. Thanks to Prof. Pierre Flener for his contagious enthusiasm about constraint programming. Without his introduction, I would not find my favorite topic in computer science.

Collaboration in writing a paper can be very tricky. Big thanks to Andréas Karlsson, Chenxin Zhang, Yangxurui Liu and Essayas Gebrewahid for making it so easy.

CONTENTS

Another big thanks to the administrative staff in the department, who put up with my silly questions, annoying issues about my visa, and many other things... Thanks to all Pakistani and non-Pakistani colleagues in the department for creating the inclusive and welcoming atmosphere.

Thanks to Çağdaş Aydın for introducing me to computer science, and saving me from choosing economy or something as boring. Thanks to Prof. Muhammet Toprak and his wonderful family for helping me in my first contact with Sweden, cushioning the culture shock. Thanks to Esat Arslan for being my mentor in life. Eternal thanks to my brother Ihsan Arslan and his family for being there whenever I needed them. And to Mehdi, for his love, wisdom and care.

My friends educated me throughout my life, I would not be this self without them. The list is long, but they know who they are, so thank you.

I have a really huge family back home in Turkey, and I know all of them have been rooting and praying for me since I decided to move to Sweden for studying. In contrast, I have a relatively short space here, so while I am grateful to all of them, I will single out my singular mother here, who raised me alone, with lots and lots of unconditional love. I owe her everything and if this thesis makes her proud, then I am proud of myself.

My last year in PhD was by far the best one, as this is the one I met my love and best friend, Lina Dahlman. I am so very lucky to have you. On that note, thank you Han Solo; yes you died, but it was definitely worth it.

As I hinted with the quote above, all this gratitude originates from and returns to The Most Gracious, The Dispencer of Grace - Allah. I am humbled by the countless blessings poured over me...

# 1 Introduction

Embedded systems are a special class of computing systems with very specific requirements on performance, cost and power/energy consumption. Applications that are targeted by embedded systems are getting more and more computation hungry. Many of these applications, especially those in telecom and signal processing, require high throughput (processed data per time unit) preferably with low latency, so that when the result of a requested computation is produced, it is still relevant to the user. On the other hand, the power and area budget is limited, for reasons varying from battery lifetime and pocket space to environmental concerns. These requirements are often addressed via special design and architectural choices. In particular, custom processor architectures (a.k.a. customizable processors) are often employed. To meet the requirements, custom architectures are tailored to fit the target application domain. This includes providing the amount of instruction level parallelism (the number of instructions the processor can run simultaneously) that is sufficient for the applications, implementing certain critical operations in hardware, moving non-critical functionality from hardware to software (e.g. by emulation) to increase clock speed and customizing the memory structure to fit the common data access patterns [1, 2, 3].

Many applications that are designed for embedded systems (e.g. image processing, telecom, surveillance) are inherently *parallel*. This means that, even though they are defined as a series of sequential instructions, a significant amount of those instructions are independent of each other and thus can be run simultaneously. A specific type of parallelism that commonly occurs in digital signal processing (DSP) and multimedia applications is *data parallelism*, where the same operation is executed on many data. This type of parallelism is usually supported by Single Instruction Multiple Data (SIMD) instructions, which enable processing vectors of data instead of single elements. However, having a vector processor without the data management that enables vector access would only make the processor wait for the data. Therefore SIMD instructions require high-bandwidth memory architectures to feed the processor with enough data.

Introduction

From an embedded system architect's point of view, architectural customization may be the only step necessary to meet the specific requirements from the application and user domain. However, the target application has to be programmed in a custom manner as well, to reap the benefits of having special hardware. Each programmable processor architecture has its own machine language for program development, but for an application developer, programming in it is most of the time overly tedious and error prone. In such a language, the programmer needs to specify almost everything explicitly. This would include deciding which instruction to execute and when (instruction selection and scheduling), also which memory or register address to store each data (data assignment). For custom architectures with SIMD instructions, the programmer would also be tasked with grouping operations on scalars into vector operations. This entails handling the data assignment and access for the vector inputs and outputs of these operations.

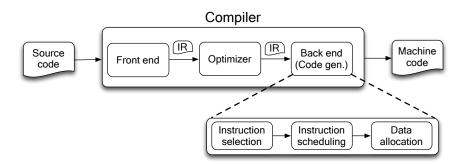

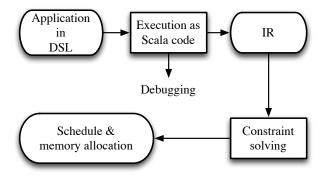

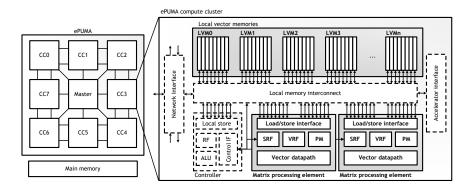

Traditionally, instead of the machine language, the programmer uses a higher level language (such as the C programming language) that lets her/him focus on how things are to be done, rather than the details of the architecture. The mediator here is the compiler. As depicted in Figure 1, the compiler takes the code written by the programmer in the high-level language (i.e. the source code) as input and outputs a translation to the target architecture's machine language (i.e. the machine code). The resulting machine code has all the details necessary to make it executable on the target architecture, as mentioned earlier. This process can be divided into three major parts: front end, optimizer and back end (also referred to as code generation) [4]. The front end of a compiler textually analyzes the source code to check its validity, both syntactic and semantic, and translates it into an intermediate representation (IR). The resulting IR is a data structure, generally some type of graph, that represents the source code in a way that enables further processing by the optimizer and the back end. The optimizer is responsible for platform independent optimizations over the IR, such as removing unreachable code (dead-code elimination) and avoid recomputation of expressions(common subexpression elimination). Finally, the back end is responsible for machine code generation from the IR the optimizer outputs, together with architecture specific optimizations [4, 5].

Code generation itself can be divided into three steps (subproblems), namely: instruction selection, instruction scheduling and register/data allocation. Traditionally, these steps are executed sequentially and in isolation [4]: instructions to implement the application are selected, selected instructions are scheduled, and finally, data assignment for the inputs and outputs of the scheduled instructions is decided. While it is possible and sometimes beneficial to change the order of these steps (e.g. just in time compilation of media processing applications for very large instruction word processors [6]), traditional compiler technique uses the given order of execution. Each step is hard (NP-complete) to solve optimally [4, 7]. To reach solutions in a reasonable amount of time, each step is commonly solved seperately using heuristic or approximate algorithms that generate suboptimal so-

Figure 1: Structure and context of a traditional compiler [7]

lutions. For custom architectures, this is further complicated by the irregularities in the architecture [1]. Traditional techniques for each subproblem becomes harder to apply to custom architectures as these techniques are not designed to exploit the special hardware design. Moreover, the interdependence between subproblems becomes more significant for the overall result. For example, a specific vectorization of operations in scheduling may cause latency penalties because of irregular data access, depending on data allocation. In some scenarios this may offset the speedup from vectorization altogether. We experienced such a scenario in our initial experiments, where we separated the subproblems as traditional compilers do. The code generated this way had three times lower throughput than machine code written by the architect. Because of the custom nature of the architectures and the separation of subproblems, using standard techniques and tools to compile from a high level language comes at the price of very low quality of the generated machine code.

The preferred alternative for custom architectures is to write machine code by hand. But as mentioned earlier, this is a very time consuming, tedious and error prone process, as the programmer has to do the compiler's job. Furthermore, the programmer has to write machine code that uses the capabilities provided by the custom architecture, otherwise the architecture is utilized poorly, which beats the purpose of having a custom architecture. As there is no assistance from a compiler, the programmer needs to know the intricate details and complexities of architecture, including, but not limited to, processor structure, memory layout, machine instructions. Most of the time this information is available only to the architect of the processor, leaving programming solely to the architect.

In short, custom architectures are a good solution for the high-performance, low power budget demands in embedded systems, but their custom nature introduces a new challenge, which we call the *programmability bottleneck*: Traditional code generation techniques generate poor-performance code for custom architectures; therefore obtaining high-performance code is limited to programming in the machine language and requires in-depth knowledge of the architecture. In this

8 Introduction

thesis we address the problem of programmability for custom architectures from different perspectives. The rest of the thesis is organized as follows: Chapter 2 provides a background to the papers included in the thesis, to acquaint the reader to the essential topics and concepts. Chapter 3 gives an overview of the field and related publications. Chapter 4 presents our problem formulation and Chapter 5 gives an overview of our contributions. In Chapter 6, we present our conclusions and a give glimpse into possible future work. Finally, a list of papers together with author contributions precedes the included papers themselves, in Chapter 7.

# 2 BACKGROUND

In this part, we briefly introduce custom architectures, code generation and constraint programming to provide a background for our work.

#### 2.1 Custom architectures

Throughout this thesis, we targeted two custom architectures: the EIT architecture [2] and ePUMA [3]. Both of these architectures are endowed with a Single Instruction Multiple Data (SIMD) pipeline and a high-bandwidth banked memory. To familiarize the reader with these concepts, in this section we introduce pipelined execution, Single Instruction Multiple Data processing, banked memory organization and access restrictions that come with it. We conclude the section with an overview of the ePUMA architecture as an example. More details on the architectures can be found in papers II and V.

#### 2.1.1 Pipelined execution

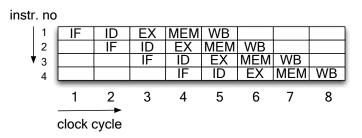

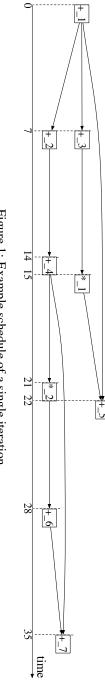

Exploiting the parallelism inherent to target applications is crucial to increase the throughput of an architecture. One common technique, which is also used by the architectures we target, is *pipelined execution*. Pipelined execution divides instructions into stages to run them as in an assembly line, overlapping different stages of multiple instructions. When there are enough independent instructions to run, this technique improves the utilization of the resources and increases the throughput, without changing the issue-width [4]. An example is depicted in Figure 2, where each instruction is executed in five sequential stages, each taking one clock cycle to complete. This makes the execution time of an instruction, i.e. the *latency*, 5 clock cycles. If four instructions are executed sequentially, the total execution time would be 20 clock cycles. With pipelining this number is reduced to 8 clock cycles. Moreover, after filling the pipeline in the 5th clock cycle, we get one result per cycle. This makes the *throughput* 1 instruction per cycle (IPC). Without

10 Background

Figure 2: Pipelined execution example. Each instruction comprises five sequential parts: IF (instruction fetch), ID (instruction decode), EX (instruction execution), MEM (memory access), WB (write back).

pipelining, the throughput would be 1/5 = 0.2 IPCs. The benefit comes from improved utilization of the hardware dedicated to each pipeline stage, by overlapping different stages from several instructions.

Instructions that are data dependent on each other may cause stalls in the pipeline, as an output in a previous instruction may be input to the following instruction. Some architectures employ techniques like *forwarding* to potentially eliminate stalls. This is done by additional hardware that can feed the result back from a pipeline stage to a previous stage for a later instruction. For the architectures we target, there is no forwarding, which means simpler hardware and simpler dependency analysis in code generation.

For architectures targeting application domains that incorporate many conflicting standards (e.g. a 4g mobile terminal complies to more than 10 different radio standards [8]), achieving flexibility together with the high-performance and low energy consumption requirements is a significant challenge. Architectures like EIT overcome this by designing dynamically reconfigurable hardware for each pipeline stage, providing a cheaper alternative to developing specific hardware for each standard, with regards to area consumption and development time [2]. In such an architecture the standards share resources and dynamically reconfigure them when necessary.

#### 2.1.2 Single Instruction Multiple Data

As mentioned earlier, data parallelism commonly occurs in digital signal processing (DSP) and multimedia applications, where the same operation (e.g. filtering, conversion) is applied on many data points. *Single Instruction Multiple Data* (*SIMD*) processing units are developed to exploit this kind of special parallelism. Instead of single elements, a SIMD processor's input and output is a vector of data.

While the idea is straightforward, SIMD processors present challenges in programming and data alignment. As a general rule in parallel execution, the opera-

tions that are to be run in parallel have to be independent of each other. The SIMD paradigm adds the single instruction restriction on top of this, which makes a hard problem (identification/exposing parallelism) even harder. Organization of input and output of the SIMD unit as vectors is another challenge connected to the register and memory structure provided by the architecture. As the SIMD processor accesses vectors of data, vector accesses may be challenging as well, depending on the underlying register and memory structure,

#### 2.1.3 Multi-bank memory and access restrictions

A vector processing unit without a memory that provides enough bandwidth to read and write vectors is useless, as the computation bottleneck will be replaced by a data/memory access bottleneck. Therefore, the memory organization of the architectures we target is an essential part of their custom nature.

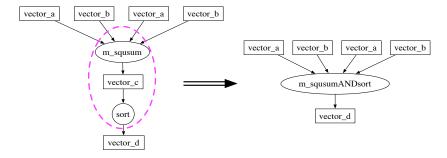

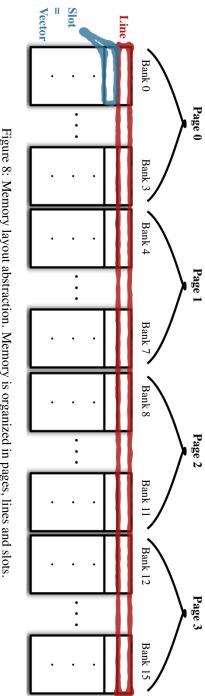

The common technique to achieve high-bandwidth access for the architectures we target is to have a multi-bank memory structure. A memory is divided into banks with independent access ports. Each address in a bank contains data that can be part of a vector. Access to several banks simultaneously enables reading/writing an entire vector. This structure enables accessing each bank independently (i.e. different address for each bank) and flexibly assembling a vector from these accesses.

Both EIT and ePUMA incorporate a multi-bank memory structure. However, there are some differences. EIT takes the abstraction from scalars to vectors one step higher and works with matrices as vectors of vectors. To support this they provide a multi-bank matrix memory, where each address in a bank contains a vector. In ePUMA, each bank address contains a scalar instead. We simplify this in modeling by treating vectors as scalars and matrices as vectors for EIT. Another difference is in the number of access ports per bank. While EIT banks are dual-ported i.e. one read and one write per clock cycle is possible, ePUMA banks are single-ported i.e. one read or write per cycle is possible.

Both architectures allow some flexibility in assembling a vector from scalars, but differ in how they do it. To simplify memory access configuration, EIT divides the memory further into lines and groups banks into pages. The allowed access patterns are stored in access descriptor registers. ePUMA on the other hand allows different types of regular access without any penalty, and irregular access with possible latency penalty, depending on the other accesses happening in the pipeline at the same time. Further details on these restrictions and how we model them are presented in each paper targeting these architectures.

#### 2.1.4 ePUMA architecture

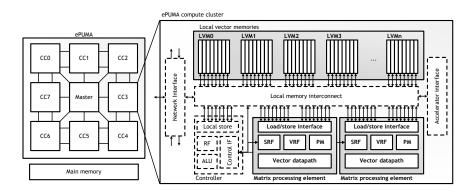

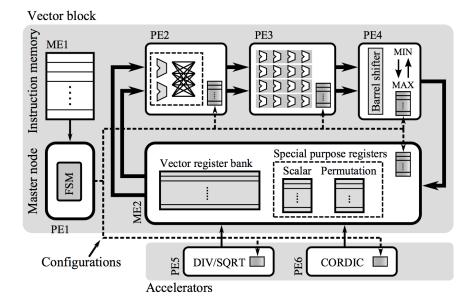

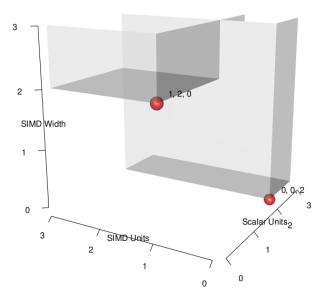

To illustrate how these concepts fit in a custom architecture, we give an overview of the ePUMA architecture, as depicted in Figure 3. To the left, the entire system,

12 Background

Figure 3: Overview of an example custom architecture - the ePUMA architecture.

with eight computing clusters and a master processor to control them is shown. A computing cluster contains a local controller, multiple vector DSP compute processors called Matrix Processing Elements (MPEs) and a set of local vector memories (LVMs), as shown in the right side of the figure. Each MPE can be assigned two of the local memories at a time for processing. The memories may be reassigned to exchange data between cores. When the target architecture is ePUMA, the focus of this work is limited to code generation for a single MPE, as each MPE is a complete custom architecture. The interconnection of several MPEs is the subject of another study that I contributed to [9].

A MPE has a complex pipeline structure (vector datapath), with 16 multipliers and three levels of arithmetic units, to accelerate general and application-specific computing patterns. With SIMD instructions, the processor can operate on vectors of arbitrary length directly in the local memories, processing chunks of size up to 128-bits, per clock cycle. Figure 3 also depicts the scalar register file (SRF), vector register file (VRF) and the program memory (PM) for each MPE.

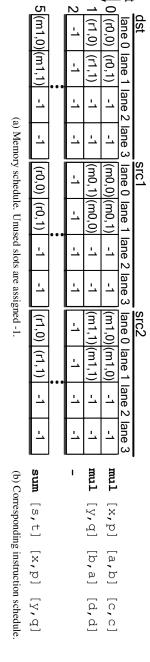

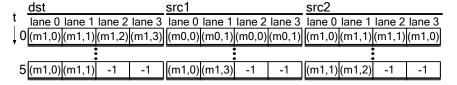

The targeted version of the architecture implements instructions that have the following format:

#### op dst src1 src2

where op is the instruction code and dst represents the destination of the output, while src1 and src2 represent the first and second operands of the instruction respectively. Commonly in signal processing, each scalar is a complex number represented by a 32-bit word. As the maximum size of a vector is 128, each vector can have 4 complex numbers. The SIMD width (SW) is configured accordingly to operate on up to 4 complex numbers at the same time. Figure 4 depicts an example instruction for the targeted version of the architecture, where SW = 4. The SIMD logic works point-wise over the operands and aligns operations to *lanes* 0 to SW - 1 of the SIMD processor.

```

\begin{array}{l} p=a+e \\ q=b+f \\ r=c+g \end{array} \Rightarrow \quad \mathbf{sum} \, [\mathrm{p,q,r,s}] \, [\mathrm{a,b,c,d}] \, [\mathrm{e,f,g,h}] \\ s=d+h \end{array}

```

Figure 4: SIMD logic

The operands in dst, src1 and src2 can reside either in the memory or a register, but each vector operand has to come from the same memory/register. Registers provide faster access while memory provides more space and flexibility. There are two 4-bank memories and 8 vector registers available. Each multi-bank memory allows reading a full vector in one clock cycle, provided that the access does not involve reading multiple elements from the same bank which constitutes a *bank conflict*. Some access patterns (henceforth called *regular access*) are supported implicitly through the hardware implementation while other patterns can be used through the help of a *permutation vector* stored in the program memory as long as it does not entail any bank conflicts.

The architecture can issue an instruction each clock cycle but instruction latency depends on several factors. Different operation types can have different latencies. We assume that the default latency for a multiplication is 4 clock cycles, i.e. the output of a multiplication is ready to use 4 cycles after its issue. The same figure for an addition is 1 clock cycle. This default latency is extended when one of the following occurs:

- Writing back to memory: Results in one clock cycle additional latency.

- Bank conflict: Results in one clock cycle additional latency per conflict, per bank.

- *Memory conflict:* Both *src*1 and *src*2 are read from the same memory. As the memory is single-ported, this adds one clock cycle latency.

- *Too many permutations:* Each irregular access needs a permutation vector to be defined and kept in the program memory. The architecture provides a way to avoid the permutation penalty if there is only one read permutation in the pipeline. But when there is more, this adds to the latency.

Registers, on the other hand, cause no such additional latency or delay penalties. However, they only allow regular access.

14 Background

#### 2.2 Code generation

Here we give an overview of code generation and briefly introduce its subproblems, as each of them is a research topic in and of itself. For more details and advanced topics that are beyond this thesis, we refer the reader to [5, 4, 6].

#### 2.2.1 Overview

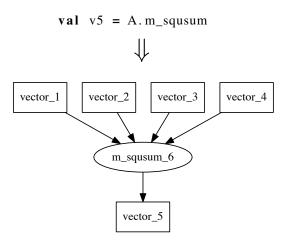

As described earlier and depicted in Figure 1, the front end of a compiler takes the source code and translates it into an intermediate representation (IR). This IR is then fed into the optimizer phase of the compiler which does code optimizations prior to code generation by the back end. In paper II we introduce a domain specific language targeting the EIT architecture, that generates an IR as the input for the code generation. Further details on IR can be found in that paper. In this section, we focus instead on code generation as it is more central to this thesis.

Code generation is the process of translating an intermediate representation of an application into machine code that can be run directly on the targeted architecture. Traditionally, code generation is divided into several subproblems in order to keep it manageable, as each subproblem in itself is very hard to solve optimally [4].

#### 2.2.2 Instruction selection

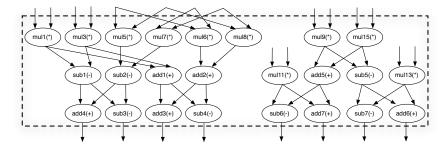

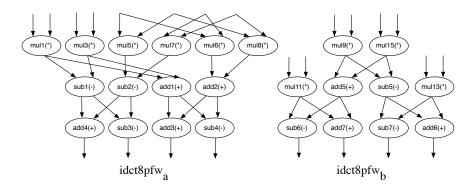

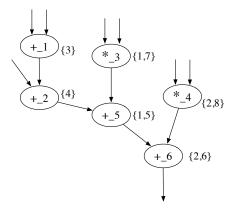

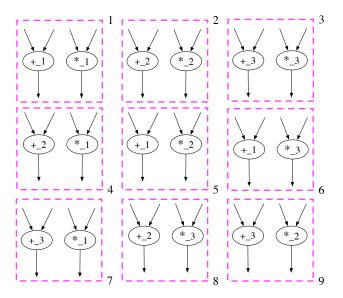

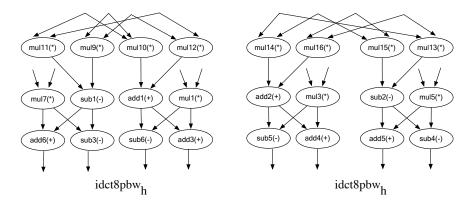

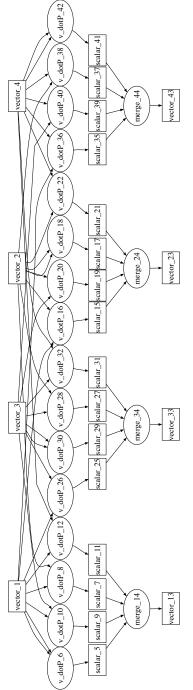

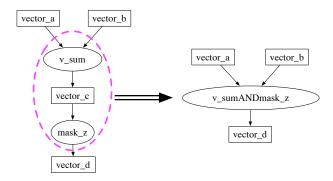

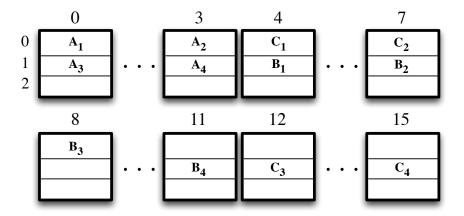

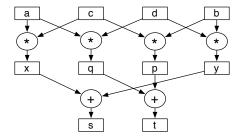

The operations in the IR are abstract operations. They do not necessarily correspond to one instruction in the machine language. Instruction selection is the phase where the abstract operations in the IR are mapped to machine instructions. Custom architectures tend to provide complex instructions for groups of operations that are common in the target application domain. For example the ePUMA architecture provides two instructions that together implement inverse discrete cosine transformation (IDCT), a very common operation in multimedia applications. Figure 5 shows one of those instructions in a simplified IR form, where nodes represent operations and edges represent dependencies between them. Note that the instruction takes two vectors with eight scalars as input and generates one vector with eight scalars as output.

Generally the architecture enables several different implementations of the application, therefore, to select the one that performs the best becomes another objective for instruction selection. The performance metric depends on the objectives of the programmer and the application domain, but most of the time is one of minimal execution time, code size or power/energy consumption. Even though the eventual performance of the generated code is also highly dependent on the other code generation steps (i.e. instruction scheduling and data assignment), methods such as profiling are used to estimate the cost of selecting an instruction [7].

Figure 5: First half of IDCT in ePUMA, implemented by the instruction named *idct8pfw*

#### 2.2.3 Instruction scheduling

After instruction selection, the order of execution (i.e. the schedule) for the selected instructions needs to be specified. If there are several functional units capable of executing the instructions, a schedule additionally entails the assignment of instructions to particular units. A valid schedule needs to respect the constraints of the architecture and the application. Architectural constraints include available functional units, issue width (number of instructions that can be issued simultaneously), types of operations that can be bundled together (for a SIMD unit, this is equal to one), etc. On the other hand, application constraints consist of control and data dependencies between operations.

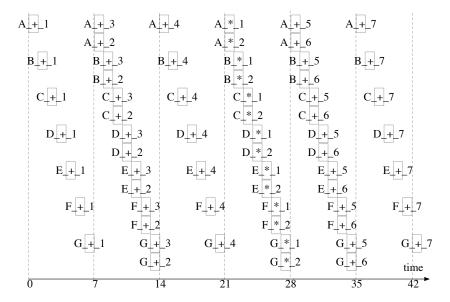

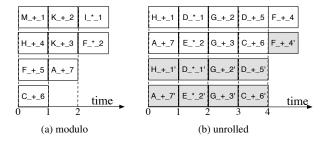

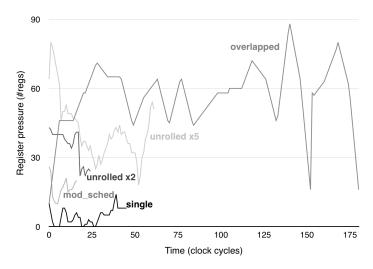

When optimizing for high-performance i.e. high throughput, as is the case for us, the objective is to come up with a schedule that performs the best i.e. the optimal schedule, or satisfy some performance thresholds such as minimum throughput and maximum latency. To achieve this goal, it is important to exploit the parallelism inherent to the application and the instruction-level parallelism (the capability to run several instructions simultaneously) the architecture provides. Loops constitute a special source for parallelism. as independent operations from different iterations can be run in parallel. For this reason, several techniques target loops for scheduling with improved parallelism. One such technique is called modulo scheduling [10]. It involves finding a schedule that initiates iterations as soon as possible, taking into account dependencies and resource constraints, while also repeating regularly with a given interval (initiation interval II). Loop unrolling is originally a compiler optimization technique that unrolls several consecutive iterations of the loop together to decrease the loop overhead [5]. With reordering of operations, it can help eliminate stalls because of data dependences, by executing operations from a following iteration. As it possibly increases the number of independent operations, it can also be used to expose more parallelism [11]. The main downside in this case is the increase in the code size. Modulo scheduling and loop unrolling can also be combined. For further details, see paper III.

16 Background

#### 2.2.4 Data assignment

Together with the inputs and outputs of the application, the intermediate data i.e. the data produced and consumed within the application, have to reside somewhere during the interval between the define and last use time for each data (i.e. *lifetime*). Data assignment is the phase that decides on where each live data is kept.

Commonly, registers are situated closer to the processing elements and provide faster access compared to other memory units. Higher access speed comes with higher price, and therefore architectures tend to have only a limited number of registers available [12]. This entails that only a limited amount of live data can reside in registers, while the rest has to be stored in slower memory units (i.e. spilling to memory). Therefore, traditionally, data assignment is focused on finding a register allocation with minimal amount of spills, to minimize additional memory access latency caused by the spills. Most of the state of the art is based on a graph coloring method by Chaitin [13]. The graph coloring problem is to minimize or limit the number of colors necessary to color each node in a graph, where adjacent nodes have to be colored differently. This is a problem that predates computers, and therefore has many existing solution techniques. In order to benefit from these techniques, Chaitin uses an interference graph to represent the competition among data to be placed in a register. In this undirected graph, each node represents a data (i.e. a temporary) and two nodes are connected if their lifetimes overlap. With this graph, the register allocation problem is turned into a graph coloring problem.

The architectures we target are built to run data intensive applications. Therefore, they are highly dependent on memory-bandwidth, in order to achieve the required throughput. As mentioned earlier, this is addressed by customized memory structures. However, in order to achieve high bandwidth, data should be assigned and accessed in specific ways, defined by the memory structure. Otherwise, either the instruction schedule becomes invalid as some of the inputs or outputs can not be accessed, or significant latency penalties occur for conflicting accesses. As a result of the complexity in the memory structure, memory access and allocation becomes the focus of data assignment, instead of register allocation.

### 2.3 Constraint programming

In all the included papers we use constraint programming (CP) to model our problems. Therefore, each paper has an introduction to CP, highlighting the aspects relevant to that paper. Here, we give a more general introduction. A thorough description can be found in the Handbook of Constraint Programming [14].

The models in the CP paradigm are defined as constraint satisfaction problems over a series of variables. The variables represent the decisions that constitute a solution, such as start times of operations, memory locations and lifetimes of data. Variables are defined by the values they can take, namely their domains. A solution is an assignment of a singular value to each variable. Constraints cap-

ture the relation between variables, such as precedence between two operations, non-overlapping lifetimes for data on same location. These relations restrict the combinations of values the variables can simultaneously take.

Each constraint is paired with a consistency method (a propagator) to eliminate the infeasible values (a.k.a. *pruning*). These methods can be complete (pruning all infeasible values at once) or incomplete (pruning a subset of infeasible values), depending on the choice of algorithms implementing them. Incomplete methods are preferred when complete methods have too high algorithmic complexity. A constraint and its consistency method are often used interchangeably, i.e. "constraint" referring to the method that prunes infeasible values. Constraints are independent of each other but affect each other through the domains of the variables. This independence provides a significant amount of flexibility as constraints can be plugged in and out easily, simplifying the update and maintenance of models.

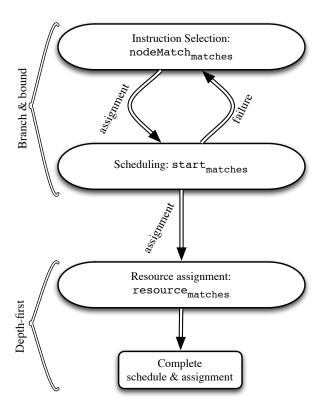

A constraint solver is a framework that provides the programmer with a library of built-in constraints, together with a constraint solving engine. This engine is responsible for coordination of the propagators and the guessing method e.g. search with backtracking. In a simplified view, the engine runs each propagator until a fixed-point (where no more pruning is possible via propagators) is reached (i.e. a round of propagation). If the reached fixed-point is not a solution, the solver needs to resort to guessing. A guess involves picking a variable and constraining its domain e.g. assigning it to a single value. This new domain can make some of the constraints invalid for some values, triggering new propagations. As a guess may be wrong, a way to backtrack from it is necessary. This is achieved by keeping track of the guesses as a tree (i.e. the search tree). The strategy for picking which variable to guess on (i.e the variable selection heuristic) and the strategy for constraining the selected variable's domain (i.e. value selection heuristic) decides the shape of the search tree. The search tree can be used to turn a satisfaction problem into an optimization problem. An efficient technique to search for optimality using the search tree is branch-and-bound technique [15].

A distinct feature and strength of CP is the concept of *global constraints*. A global constraint logically combines several simpler constraints and handles them together. While semantically equivalent to the conjunction of these simpler constraints, a global constraint lets the solver exploit the structure of a problem by providing a broader view to it [16]. Propagators to these constraints are commonly implemented by existing algorithms from well-studied fields such as graph theory and operations research.

Throughout this thesis, we used the JaCoP framework as our constraint solver [17]. JaCoP provides a wide selection of built-in global constraints, some of which are specially designed for scheduling (cumulative), and others that can be used to formulate data assignment diff2 and access constraints regular.

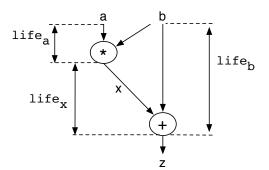

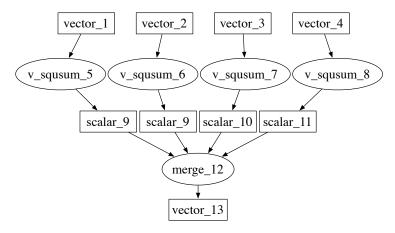

To make things more concrete, consider the example IR in Figure 6. The graph consists of two operations and four data. There are two inputs (a and b), one output (z) and one intermediate data (x). Data b is input to both the multiplication and the

18 Background

addition. The other input of the addition is the result of the multiplication, i.e. x. Therefore there is a data dependency between the operations, which is translated into a precedence constraint in the model as follows:

$$t_* + l_* \le t_+$$

Here, t denotes the start time of the operation and l denotes its latency. For an operation, latency corresponds to the time that needs to elapse after the start of execution, for its result to be ready.

The dashed lines in the figure denote the definition point and last use of each data. If the inputs (a and b) are assumed to reside in registers or memories before the execution starts, their definition time can be assumed to be zero. However, the definition time of x depends on the multiplication, more specifically it is  $t_* + l_*$ , as it is defined when the result of the multiplication is ready. The last use time on the other hand, depends on the operation that finishes using the data. We assume that an operation uses an input data during its execution time, which we denote with d. Therefore, the last use time for a is  $t_* + d_*$ ; for b and x this is  $t_+ + d_+$ . Note that the start times of operations (t) are variables, and will be set by scheduling decisions made by the solver. Another detail to note is that the latency (l) and the execution time (d) of an operation can be different.

Figure 6: A simple IR. Dashed lines denote the definition point and the last use point for each data.

The time between the definition and last use identifies the *lifetime* of a data. Lifetime analysis is important in order to reuse registers and memory addresses without assigning two or more live data to the same address. In the example above, lifetimes of a and x are not overlapping, therefore they can reside in the same location. However, the lifetime of b overlaps both with a and x, therefore it can not share address with them. An overlap, therefore, happens in a two-dimensional space, the dimensions being the address of a data and its lifetime. Assuming that the size of a data does not change depending on where it is located, the assignment for each data i can be represented in this two dimensional space, as a rectangle

originating from  $(address_i, def_i)$  with width  $life_i$  and unit height. In this case,  $def_i$  denotes the definition time of data i. With this reasoning, data assignment can be modeled as non-overlapping rectangles, using the diff2 global constraint. As the lifetime of a data is dependent on the start times of the operations that use or define it, the diff2 constraint will interact with the scheduling constraints such as precedence constraints and cumulative.

### 3 RELATED WORK

Each paper included in this thesis has a separate section on related work specific to that paper. Here, we present the related work more general to the field. Note that some newer papers are also included here, that are published after the publication of our papers. We contrast subproblem-specific works (i.e. instruction scheduling and register allocation) to more unified/integrated approaches and situate our work in the latter. Note that we do not allocate a separate section for instruction selection as we mention the most related work under unified approaches. For further reading we refer to the extensive survey on instruction selection by Blindell [7].

### 3.1 Instruction scheduling

Optimal instruction scheduling is a very hard problem, for a single-issue processor it is NP-complete if there is no fixed bound on the maximum latency [18]. For this reason, it is common practice to use list scheduling with a priority heuristic, instead of an exact method aiming for an optimal schedule. A compelling case for using exact techniques such as constraint programming for instruction scheduling is made in [19]. The authors performed an extensive computational study of heuristic and exact techniques for superblock instruction scheduling using realistic architectural models of processors that were commonly used in telecommunications and DSP, at the time of the study. One important conclusion of this study is that the exact scheduler (which internally uses constraint programming) always results in better code however with the downside of longer scheduling time compared to heuristic schedulers. Hence the exact methods are suitable for aggressive optimization but maybe not for general purpose compilation.

Malik et al. [20] present a superblock instruction scheduler based on CP, targeting multiple issue pipeline processors with several functional units for instructions such as load/store, integer, floating point and branch instructions. Isolating the instruction scheduling problem, they focus on the DAG representation of the superblock and make use of graph transformations presented in [21] to im-

22 Related Work

plement implied dominance constraints. These help reduce the search space for solutions, therefore decrease optimization time. Our experiments showed that this propagation is already done when we use the cumulative global constraint. This makes us believe that the implementation of cumulative in JaCoP already covers the implied dominance constraints. The study reports optimal solutions to superblocks containing up to 2600 instructions from SPEC2000 integer and floating point benchmarks. As mentioned, the study solves instruction scheduling in isolation, while we combine it with other subproblems of code generation, i.e. instruction selection and register/memory allocation.

Modulo scheduling is a recurring method in embedded systems for loops/kernel scheduling. Many studies are reported during recent years. Kudlur and Mahlke present modulo scheduling for stream graphs in [22]. They integrate actor fission and processor assignment as an ILP as a first phase, followed by a phase that assigns actors to pipeline stages, overlapping communication and computation, to increase overall utilization. Mei et al. introduce modulo scheduling to Coarse-grained reconfigurable architectures (CGRAs) to exploit loop-level parallelism [23], while Kim et al. [24] tackle the problem of long compile times for modulo scheduling for CGRAs, caused by the difficulty of finding a good routing of operands through the processors. They propose patternized routes in order to simplify the problem, and this trade-off results in 6000 times faster compilation while preserving 70% throughput on average compared to the state-of-the-art. We on the other hand use modulo scheduling as a set of additional constraints rather than the core method for scheduling.

### 3.2 Register Allocation

Register allocation is a research area in and of itself. This subproblem is studied in depth for compilers targeting traditional processor architectures and most works base themselves on the seminal graph coloring method by Chaitin [13]. This method is briefly explained in Section 2.2.4. There are many combinatorial methods targeting register allocation as well, a detailed overview for these methods can be found in [25]. Here we focus instead on the studies closely related to ours, that target register allocation in isolation. Methods similar to ours that target register allocation as part of a unified approach is covered in the following section.

The work by Domagała et al. [26] uses a two-dimensional instruction tiling approach (one dimension for intra-iteration, another for inter-iteration) to expose register reuse among several unrolled loop iterations. The focus here is to minimize register pressure and spill code to avoid the high memory latency. The optimization is modeled as a constraint satisfaction problem and solved using constraint programming. Once the tiling is decided a trivial scheduling is employed. Therefore we classify this as an isolated solution for register allocation. In contrast, at

each of our studies where we target data assignment including register allocation, we combined it with other subproblems of code generation.

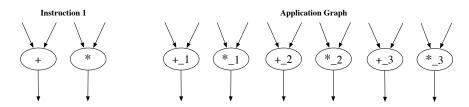

In [27], You and Chen present a vector-aware register allocator, targeting GPU shader processors. The target architecture provides a combination of scalar and vector operations. They observe that in the shader programs, there are many variables that are either scalar, or comprise *N* scalars where *N* is less than the size of a vector register. Therefore, they present a framework that divides vector registers into scalar parts, and allocate each variable to these slots (i.e. *element-based register allocation*). They also incorporate register packing to avoid wasting contiguous register space. The register allocation is implemented in an in-house just-in-time compiler, therefore register allocation is done before scheduling. The experiments show improvements in register utilization and decrease in spills to the memory. As ePUMA allows scalar access and groupings that are smaller than the vector register size, we also implement element-based register allocation. We do not explicitly pack registers, but this is done implicitly through scheduling of vector operations, as we integrate register and memory allocation with instruction scheduling.

### 3.3 Unified approaches

One of the first studies aiming at a unified approach is by Kessler and Bednarski [28]. They solve the combined instruction selection and scheduling problem with a limited number of registers, optimally, using dynamic programming. Similar to our approach, they target basic blocks that are represented as directed acyclic grpahs. However, their approach is practically limited to small graphs (< 50 nodes) for finding a solution in a reasonable amount of time. They expand this approach to cover code generation for very large instruction word (VLIW) architectures [29], but the approach is still applicable only to small graphs. In contrast, our approach can solve 4-5 times larger graphs optimally or almost optimally for combined instruction selection and scheduling.

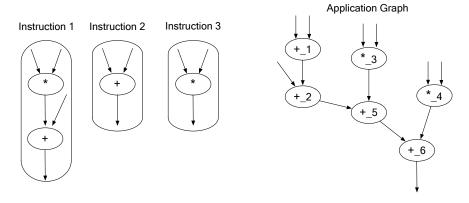

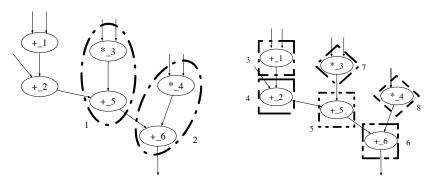

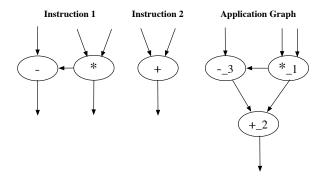

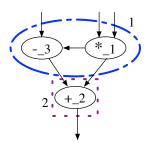

Unison is a project aimed to combine the traditionally separated instruction selection, register/memory allocation and instruction scheduling problems into one problem to use the inter-dependency between these subproblems to achieve improved code generation [30]. For instruction selection, Blindell et al. propose a universal scheme using constraint programming in [31]. They combine control-flow with program-/data-flow to select instructions for kernels that span over several basic blocks. They incorporate a subgraph isomorphism algorithm (which is also used to implement the subgraph isomorphism propagator in JaCoP) to match instructions that are represented as pattern graphs with parts of the combined application graph. This pattern matching is similar to our approach in [32] for identifying possible instructions. It is possible to use the same idea to identify and select processor extensions as part of application compilation for reconfigurable processors as done in [33].

24 Related Work

In [34, 35], Casteñada et al. detail the integrated register allocation and instruction scheduling for code generation, as part of Unison. Target architectures for experimental evaluation are MIPS32 and Hexagon V4, a VLIW processor included in Qualcomm's Snapdragon [36]. As we do throughout the papers that include register and memory allocation, they formulate register allocation as the non-overlapping rectangles problem. This allows them to use global constraints that capture specifically this. For bundling operations as VLIW instructions they make use of the cumulative global constraint as we do for both VLIW and SIMD groupings in scheduling. They also solve many subproblems of register allocation such as coalescing and register packing that we do not consider. In contrast to this focus on register allocation, we focus on the subproblems of data assignment such as permutation vector optimization and simultaneous multi-bank access problems caused by custom memories that are designed to feed the SIMD processors we have targeted. These subproblems are directly influenced by the instruction scheduling, therefore our models have full integration of memory allocation and instruction scheduling through data access constraints, while their approach integrates them only through live ranges of program variables.

Another integrated method is by Eriksson and Kessler [37], where the authors present an integer linear programming model for optimal modulo scheduling, that solves instruction selection, register allocation, instruction scheduling and instruction allocation together. Instruction selection uses a pattern matching scheme similar to our approach. They compare this integrated model to modulo scheduling with separated stages. Target architecture is a clustered VLIW, with access to a limited number of registers. They report optimal solutions for graphs with size up to 142 nodes with a time-out of 15 minutes. The differences to note compared to our work are on the target architecture and the method used. While we modeled VLIW architectures as well, our main focus was on SIMD processors and their custom memory/register structures. This entails that our work is not limited to register allocation but also allocates memory as well. While our approaches are similar, we use the constraint programming paradigm versus integer-linear programming. This gives us ease and flexibility in modeling. Comparing target applications and results, we target application graphs with size up to 250 nodes, and solve them with a time-out of 10 minutes.

### 3.4 SIMD specific approaches

An integrated approach that targets SIMD processors is presented in [38]. The authors extract *vectorizable codelets* from loops that enable polyhedral transformations. They model the scheduling problem as an integer linear program and incorporate polyhedral compilation framework to extract scheduling constraints. Our work could also be extended to include constraints derived from polyhedral transformations. On the other hand, as mentioned earlier, the architectures we tar-

get come with custom memory and register organizations that need to be taken into consideration during scheduling. This complicates the vectorization significantly as each vector access to the memory is subject to restrictions which may result in delay penalties, which is addressed in our work.

Kim and Han [39] focus on SIMD code generation for irregular kernels with array indirection, which makes auto-vectorization a difficult task. Working on data-flow graphs, they exploit both intra- and inter-iteration parallelism for loops. Inter-iteration parallelism is covered by superword level parallelism, in which the source and result operands of a SIMD operation are packed in a storage location [40]. For intra-iteration parallelism, they identify the vectorizable operations within the loop. They account for the overhead in data reorganization operations such as load, store and shifting, and optimize placement of necessary data reorganization code. Our approach works as well for irregular loops, making it possible to generate efficient code regardless if the original code has regular or irregular references. We make use of the custom nature of the architecture and try to minimize data permutations without employing data reorganization code.

Another approach by Hormati et al. [41] takes the SIMD code generation for streaming applications to a higher level and focuses on *SIMDization* of actors in a streaming program. They call this macro-SIMDization. This perspective provides high-level information such as execution rates of actors and communication patterns among them, valuable for vectorization. Using their terminology, we focus in micro-SIMDization, targeting kernels that are run many times within an application. If these kernels are implemented as actors in a streaming application, macro-SIMDization could be used to vectorize the operations that can not be vectorized with our methods because of data dependences.

#### **4 PROBLEM STATEMENT**

As introduced earlier, custom architectures come hand in hand with a programma-bility bottleneck. One way to overcome the programmability bottleneck is through an automatic code generator that provides high quality machine code, that is competitive with machine code written by the architect. On the other hand, custom architectures are becoming more and more common, and each architecture has its own custom capabilities and restrictions. Even these capabilities and restrictions are open to change as the these architectures tend to version frequently. Therefore it is important to devise a strategy that enables building a code generator that can be changed, customized and maintained easily. Otherwise, for each version or new architecture, a new code generator needs to be built from scratch, wasting many man-hours.

This thesis is the result of our effort to overcome the programmability bottleneck of custom architectures by automating the code generation process. Two major goals for a code generation framework targeting custom architectures are:

- The machine code it generates performs at least as well as machine code written by the architect.

- It is easy to adapt it to different architectures or versions, without requiring the development of specific solutions from scratch for each new target.

Such a code generator should also avoid the shortcomings of code generation in traditional compilers for custom architectures. These include:

- Poor utilization of the special hardware.

- Neglecting the interdependence of subproblems by staging them.

- Difficult to adapt to architectural change.

To avoid these shortcomings, we propose code generation frameworks modeled using the *constraint programming* (CP) paradigm. CP fits the irregular nature

28 Problem statement

of custom architectures, as constraints are designed to be defined and to work independently. Once a skeleton model is built to capture essential parts of code generation, special hardware capabilities and requirements, or switching the target architecture can be reflected by plugging constraints in or out. This way, using CP can address the poor utilization of special hardware and achieve the goal of easy adaptation to architectural change. To reflect the interdependence of the subproblems of code generation, we aim for unified models that combine the targeted subproblems.

As our main focus is on code generation, three out of the five included papers directly target its subproblems. Paper I presents a combination of instruction selection and scheduling of complex instructions for DSP kernels. Paper II combines instruction scheduling and memory allocation for a dynamically reconfigurable custom vector architecture (EIT). Finally, paper V combines instruction scheduling, data allocation (both memory and register) and data access patterns in a single model, targeting another SIMD architecture (ePUMA). The remaining two papers deal with topics relatively peripheral to code generation. Paper III is a comparative study on scheduling techniques for kernels running on architectures with SIMD pipelines. Paper IV presents a design space exploration framework for assisting architectural decisions on custom vector architectures.

## 5 OVERVIEW OF CONTRIBUTIONS

• A high-level programming framework for custom architectures with SIMD capabilities and complex memory organization.

We propose a framework that can take a dependency graph as intermediate representation, that is generated from code written in a high-level language, and generate high quality machine code for the target architecture automatically. As the high-level language for our purpose, we developed an in-house domain specific language, while a dependency graph generated from another high-level language would work as well. The framework enables instruction scheduling with SIMD groupings and data allocation with optimized data access patterns. For further details, see paper V.

• Formulation of modulo scheduling as part of a constraint programming model for both code generation and design space exploration.

While it is commonly used separately, we integrated modulo scheduling into a code generation framework and design space exploration. The integration uses a novel constraint-based formulation of the problem and does not require major changes in the rest of the constraint model. This integration is part of papers II, III and IV.

An automata based formalization of the restrictions on data access patterns for a custom memory.

The custom, multi-bank memory that comes with the SIMD processing unit for one of the architectures we target, enables vector access with or without additional latency, depending on the access pattern. For our constraint model, we formalized this as an automaton, using the regular global constraint. The only similar attempt we found in the existing literature [42], focuses on minimizing cache misses in program-level, and targets scalar

processing. Our contribution is on minimizing the latency caused by irregular vector accesses, happens at the instruction-level, and targets vector processing. Details can be found in paper V.

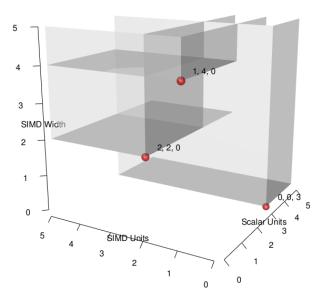

• A method for fast exploration of application specific architectures.

The architectures we targeted are constantly under improvement and change, based on the application requirements. Keeping this in mind, we developed a method for exploring potential architectural configurations for application set specific SIMD processor architectures. We employed constraint programming, and formulated the problem as Pareto optimization in a three dimensional space (number and width of SIMD units, number of scalar units), using modulo scheduling to ensure throughput requirements are met. This contribution is the main focus of paper IV.

• Formalization and integration of subproblems of code generation as a constraint satisfaction problem.

To reflect the fact that the subproblems of code generation are intertwined, we merged the subproblems we targeted, and formalized them as a unified constraint satisfaction problem. This is in contrast to the traditional compiler technique of solving each step separately and merging the solutions.

In paper I, we integrate instruction selection and scheduling. Paper II combines instruction scheduling with memory allocation. Finally, paper V integrates instruction scheduling and data assignment (both register allocation and memory allocation) with optimized data access patterns. Note that the idea of a unified model is not novel in itself, while the integration of data access constraints into a unified model is, to the best of my knowledge.

#### **6 CONCLUSIONS**

#### 6.1 Summary

Custom architectures are powerful tools for achieving high performance with low cost. However, the fact that they are extremely hard to program limits their use to a handful of programmers and therefore limits their benefits. Our work is a step towards alleviating this problem by making these architectures easier to program. Papers I, II and V demonstrate how we successfully address subproblems of code generation for custom architectures in a more unified manner compared to traditional compilers. In our experiments we compare the schedules and machine code we generated to theoretical lower bounds and manual code written by experts in the field and of the target architecture. We targeted kernels from real-life applications that are common for the target architecture, with varying IR sizes and shapes. For these applications, we either matched or got close enough to either the theoretical bound or the manual code, targeting two different custom architectures. Therefore, we deem that our automatic code generation scheme achieves the goals we laid out in the problem statement.

Using constraint programming, we built flexible yet highly detailed models of the target architectures and applications. All the models in this thesis share the same skeleton for the overlapping problems, such as instruction scheduling. The rest of the model is extended from this skeleton by plugging in new variables and constraints. This flexibility of modeling in constraint programming allows one to experiment with the level of abstraction when modeling architectures. Adding or removing a detail in the architecture corresponds to adding or removing a group of variables and constraints. A good example of this flexibility is the models for different scheduling techniques in paper III, where the shared "skeleton" corresponds to 70%-80% of the models.

During our discussions with the architects of the systems we targeted, we realized that these architectures are under constant development and update, based on the application requirements. Therefore, additionally to code generation, we 32 Conclusions

proposed a preliminary framework for design space exploration of custom architectures, with focus on meeting the requirements of the target application domain. Here, the exploration parameters are limited to the properties of the SIMD processing unit and the number of scalar units. For a more comprehensive design space exploration, more parameters should be taken into account, such as the number of registers and properties of the memory.

#### 6.2 Future work

The problems we target are inherently hard. Both instruction selection and instruction scheduling are proven to be NP complete. Even though constraint programming provides flexibility in modeling, this algorithmic complexity forced our models to be very complex in turn, with many different types of variables and complicated constraints and complex search heuristics. The combination of a hard problem and a complex model can turn a constraint solver into a black box. Problems with reasonable sizes get quickly untraceable. In a future work, a mathematical analysis of what kinds of graphs we can solve in a reasonable amount of time should be provided for sound reasoning, instead of relying only on experiments.

For the entirety of the thesis we limited ourselves to the EIT and ePUMA architectures, together with some theoretical architecture models (such as a generic very large instruction word processor). However, it is important to target other custom architectures in order to ensure the robustness of our technique. It would be interesting to target custom architectures that provide some sort of programming support (other than assembly) such as [43], and compare the code our tools generate with the code generated by the existing tools.

Our experiments showed that for applications larger than a certain size (corresponding to 256 nodes in the IR) our techniques do not terminate with a solution in a reasonable amount of time. In order to address this, we would like to investigate graph partitioning methods similar to the ones presented in [33]. There are many aspects to this problem, as a graph could be partitioned "vertically" or "horizontally", in an overlapping or independent fashion, with different partition sizes, and with different order of partitions to solve. The problem gets further complicated with constraints on data allocation and access, as a decision in one partition may render another partition infeasible.

From a constraint programming perspective, we quite often ended up with constraints that worked orthogonally to each other, but were actually interdependent in the bigger picture. An example is the interdependency of data access constraints and scheduling constraints in paper V. It would be interesting to see if it is beneficial to develop a set of global constraints that act as a combination of these orthogonal constraints. Later on, these constraints could be generalized for other purposes.

6.2 Future work 33

We suspect that symmetrical solutions comprise a big part of the search space in our problems. Eliminating these symmetries would result in a smaller and hopefully more manageable search space. Another way to shrink the search space is to decide whether or not the reached state in a search node (with all the variable domains and the constraints) is subsumed by another node. This is referred to as dominance and can limit the number of search nodes to visit significantly [44].

As mentioned earlier, we used the JaCoP framework as our constraint solver, as it provides a rich set of built-in constraints. It is also built as an open source library in Java, which makes it easier to program with and merge with additional code such as pre- and post-processing and supporting data structures, if necessary. However, there are many other constraint programming frameworks available. Some of these are particularly interesting as they focus on advanced search techniques such as lazy-clause generation [45], which is shown to be particularly useful in solving resource-constrained scheduling problems [46]. In future work, we would like to investigate whether or not another solver suits our problem better.

#### 7 LIST OF PAPERS

#### 7.1 Papers included in the thesis