#### High Performance LNAs and Mixers for Direct Conversion Receivers in BiCMOS and **CMOS Technologies**

TIRED, TOBIAS

2012

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

TIRED, TOBIAS. (2012). High Performance LNAs and Mixers for Direct Conversion Receivers in BiCMOS and CMOS Technologies (First ed.). [Licentiate Thesis, Department of Electrical and Information Technology].

Total number of authors:

Creative Commons License: Unspecified

Unless other specific re-use rights are stated the following general rights apply: Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### Licentiate Thesis

# High Performance LNAs and Mixers for Direct Conversion Receivers in BiCMOS and CMOS Technologies

By

# **Tobias Tired**

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden

#### **Abstract**

The trend in cellular chipset design today is to incorporate support for a larger number of frequency bands for each new chipset generation. If the chipset also supports receiver diversity two low noise amplifiers (LNAs) are required for each frequency band. This is however associated with an increase of off-chip components, i.e. matching components for the LNA inputs, as well as complex routing of the RF input signals. If balanced LNAs are implemented the routing complexity is further increased. The first presented work in this thesis is a novel multiband low noise single ended LNA and mixer architecture. The mixer has a novel feedback loop suppressing both second order distortion as well as DC-offset. The performance, verified by Monte Carlo simulations, is sufficient for a WCDMA application. The second presented work is a single ended multiband LNA with programmable integrated matching. The LNA is connected to an onchip tunable balun generating differential RF signals for a differential mixer. The combination of the narrow band input matching and narrow band balun of the presented LNA is beneficial for suppressing third harmonic downconversion of a WLAN interferer. The single ended architecture has great advantages regarding PCB routing of the RF input signals but is on the other hand more sensitive to common mode interferers, e.g. ground, supply and substrate noise. An analysis of direct conversion receiver requirements is presented together with an overview of different LNA and mixer architectures in both BiCMOS and CMOS technology.

# Acknowledgements

I would like to thank my supervisor Pietro Andreani at EIT for first of all arranging the position as industry PhD student for me. Secondly I am also grateful for the time he spent reviewing the two papers presented in this Licentiate Thesis. Furthermore I would also like to thank my assisting supervisor Markus Törmänen for reviewing the thesis.

I am also extremely grateful to my wife, Maria and my three children Axel, Nils and Signe for allowing me to spend time writing the two included papers and the thesis during vacations and evenings.

**Tobias Tired**

Lund, 2012-02-10

# **Table of Contents**

| Abstract2                     |                   |                                                   |    |  |  |  |  |

|-------------------------------|-------------------|---------------------------------------------------|----|--|--|--|--|

| A                             | Acknowledgements3 |                                                   |    |  |  |  |  |

| Table of Contents             |                   |                                                   |    |  |  |  |  |

| Preface                       |                   |                                                   |    |  |  |  |  |

|                               |                   |                                                   |    |  |  |  |  |

| Abbreviations9                |                   |                                                   |    |  |  |  |  |

| Part I General Introduction11 |                   |                                                   |    |  |  |  |  |

| 1                             | Intr              | oduction                                          | 12 |  |  |  |  |

|                               | 1.1               | Background                                        |    |  |  |  |  |

|                               | 1.2               | Cellular radio systems duplexing architectures    |    |  |  |  |  |

|                               | 1.3               | Silicon process technology choices                |    |  |  |  |  |

|                               | 1.4               | Thesis structure                                  | 16 |  |  |  |  |

| 2                             | Rec               | eiver requirements                                | 17 |  |  |  |  |

| _                             | 2.1               | Introduction                                      |    |  |  |  |  |

|                               | 2.2               | Sensitivity                                       |    |  |  |  |  |

|                               | 2.3               | Single sideband and double sideband noise figure  |    |  |  |  |  |

|                               | 2.4               | Noise folding                                     |    |  |  |  |  |

|                               | 2.5               | Intermodulation                                   | 20 |  |  |  |  |

|                               | 2.5.1             | Introduction                                      | 20 |  |  |  |  |

|                               | 2.5.2             |                                                   |    |  |  |  |  |

|                               | 2.5.3             |                                                   |    |  |  |  |  |

|                               | 2.6               | Compression                                       |    |  |  |  |  |

|                               | 2.7               | Desensitization                                   |    |  |  |  |  |

|                               | 2.8               | Harmonic mixing                                   |    |  |  |  |  |

|                               | 2.9               | Reciprocal mixing                                 |    |  |  |  |  |

|                               | 2.10              | Second order distortion in FDD systems            |    |  |  |  |  |

|                               | 2.11              | Third order distortion in FDD systems             |    |  |  |  |  |

|                               | 2.12              | Cross modulation in FDD systems                   |    |  |  |  |  |

|                               | 2.12.             |                                                   |    |  |  |  |  |

|                               | 2.12.             |                                                   |    |  |  |  |  |

|                               | 2.13              | Linearity requirements in E-GSM/GPRS/EDGE systems | 29 |  |  |  |  |

| 3                             | Rec               | eiver architectures                               | 30 |  |  |  |  |

|                               | 3.1               | Introduction                                      | 30 |  |  |  |  |

|                               | 3.2               | Image rejection                                   | 30 |  |  |  |  |

|                               | 3.3               | The direct conversion receiver                    | 31 |  |  |  |  |

|   | 3.3.1      | Direct conversion receiver architecture                | 31 |

|---|------------|--------------------------------------------------------|----|

|   | 3.3.2      | Direct conversion receiver drawbacks                   | 31 |

|   | 3.4        | The low-IF receiver                                    | 33 |

|   | 3.5        | Receiver architecture summary                          | 34 |

| 4 | Pro        | cess technology and device performance                 | 35 |

| _ | 4.1        | Introduction                                           | 35 |

|   | 4.2        | Process technology                                     |    |

|   | 4.3        | Package technology                                     |    |

|   | 4.4        | Substrate coupling                                     |    |

|   | 4.5        | Basic equations for the MOS and bipolar transistors    | 38 |

|   | 4.5.1      | Introduction                                           | 38 |

|   | 4.5.2      | MOS transistor equations                               | 38 |

|   | 4.5.3      | Bipolar transistor equations                           | 39 |

| 5 | LNA        | A architectures                                        | 41 |

|   | 5.1        | Introduction                                           |    |

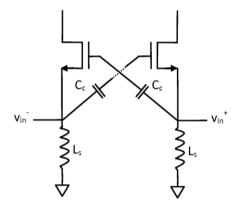

|   | 5.2        | Single ended versus differential LNA architectures     |    |

|   | 5.3        | LNA architectures in CMOS technology                   | 42 |

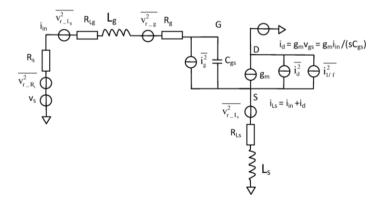

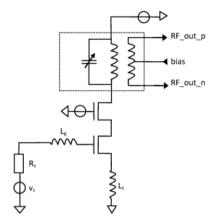

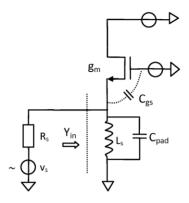

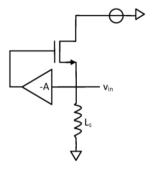

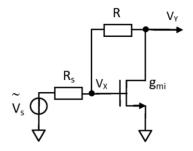

|   | 5.3.1      | Common-source LNA with inductive degeneration          | 42 |

|   | 5.3.2      | $\mathcal{C}$                                          |    |

|   | 5.3.3      | $\mathcal{E}$                                          |    |

|   | 5.3.4      |                                                        |    |

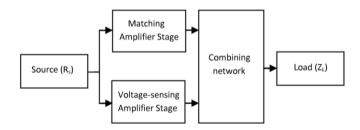

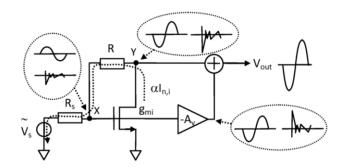

|   | <b>5.4</b> | Noise cancelation                                      |    |

|   | 5.4.1      |                                                        |    |

|   | 5.4.2      |                                                        |    |

|   | 5.4.1      | Noise cancelation with combination of CG- and CS stage | 58 |

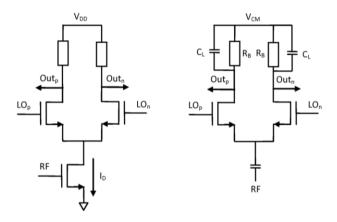

| 6 | Mix        | er architectures                                       | 62 |

|   | 6.1        | Introduction                                           | 62 |

|   | 6.2        | Active mixers                                          |    |

|   | 6.2.1      |                                                        |    |

|   | 6.2.2      | ~6                                                     |    |

|   | 6.2.3      |                                                        |    |

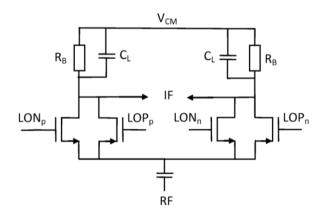

|   | 6.3        | Passive mixer                                          |    |

|   |            | Introduction                                           |    |

|   | 6.3.2      |                                                        |    |

|   | 6.3.3      | 1                                                      |    |

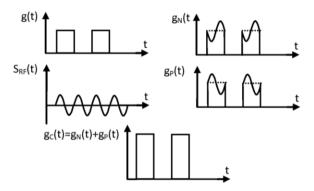

|   | 6.3.4      | Passive mixer frequency translation                    | 74 |

| 7 | Futi       | ıre radio architectures                                | 76 |

|   | <b>7.1</b> | Introduction                                           |    |

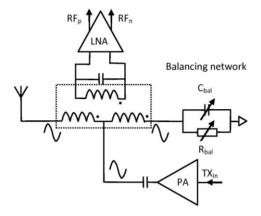

|   | 7.2        | Duplexer elimination                                   | 76 |

|   | 7.3        | E-GSM SAW-filter elimination                           | 77 |

| 8 Conclusions              | 79  |

|----------------------------|-----|

| References                 | 80  |

| Part II Included papers    | 89  |

| Summary of included papers | 90  |

| Paper I                    | 91  |

| Paper II                   | 120 |

#### **Preface**

This licentiate thesis is about some of the work made by me on the topic of linear LNAs and mixers for direct conversion receivers. The publications have been made in parallel with my work at the RF technology department at ST-Ericsson. Having a background in the wireless industry has given me valuable experience for writing this thesis. To be commercially viable new radio front end architectures must fulfill hard requirements determined by the 3GPP organization as well as chip set customers. The front-end requirements are analyzed in the first part of this work. Several alternative LNA and mixer architectures are also provided. In the second part, two of my publications regarding linear LNAs and mixers are included. The first paper describes the design and simulations of a single ended LNA and single ended mixer implemented in BiCMOS technology. The second paper regards a low noise single ended multiband amplifier with tunable on-chip matching implemented in CMOS technology. The performance of the published architectures are well in-line with the front-end requirements that are discussed in the first part of the thesis.

#### **Included publications**

- I. T. Tired, "A BiCMOS single ended multiband RF-amplifier and mixer with DC-offset and second order distortion suppression", *Springer Analog integrated circuits and signal processing*, vol. 68, no. 3, pp. 269-283, 2011.

- II. T. Tired, "Single Ended Low Noise Multiband LNA with programmable integrated matching and high isolation switches", in the proceedings of *NORCHIP 2011*, ISBN 978-1-4577-0514-4, pp 1-4, Nov. 2011

#### Other publications

I. Y. Le Guillou, O. Gaborieau, P. Gamand, M. Isberg, P. Jakobsson, L. Jonsson, D. Le Deaut, H. Marie, S. Mattisson, S, L. Monge, T. Olsson, S. Prouet, T. Tired, Philips Semiconductors., Caen, France, "Highly integrated direct conversion receiver for GSM/GPRS/EDGE with onchip 84-dB dynamic range continuous-time ΣΔ ADC",

- *IEEE Journal of Solid State Circuits*, vol. 40, no. 2, pp. 403-411, Feb. 2005

- II. Luca Vandi, Pietro Andreani, Tobias Tired, Sven Mattisson, "A novel approach to negative feedback in RX front-ends", in the proceedings of *NORCHIP* 2006, ISBN 1-4244-0772-9, pp. 231-234, Nov. 2006

- III. M. Nilsson, S. Mattisson, N. Klemmer, P. Andreani, T. Tired et al, "A 9 band WCDMA/EDGE transceiver supporting HSPA evolution", in the proceedings of 2011 International Solid State Circuits Conference (ISSCC), ISBN 978-1-61284-303-2, pp. 366-368, Feb, 2011

# **Abbreviations**

LNA Low Noise Amplifier

E-GSM Extended Global System for Mobile communication

LTE FDD Long Term Evolution Frequency Domain Duplex

LTE TDD Long Term Evolution Time Domain Duplex

WCDMA Wideband Code-Division Multiple Access

PCB Printed Circuit Board

SAW Surface Acoustic Wave

RFIC Radio Frequency Integrated Circuit

WLAN Wireless Local Area Network

GPS Global Positioning System

WiMAX Worldwide Interoperability for Microwave Access

TD-SCDMA Time Division Synchronous Code Division Multiple Access

TD-CDMA Time Division Code-Division Multiple Access

CMOS Complementary Metal Oxide Silicon

BiCMOS Bipolar Complementary Metal Oxide Semiconductor

SNR Signal-to-noise ratio

BER Bit-error-rate

QAM Quadrature Amplitude Modulation

GPRS General Packet Radio Service

EDGE Enhanced Data Rates for GSM Evolution

LO Local Oscillator

CW Continuous Wave

AM Amplitude modulation

VCO Voltage Controlled Oscillator

PCB Printed Circuit Board

Wi-Fi Wireless Fidelity

# Part I General Introduction

# CHAPTER 1

# 1 Introduction

# 1.1 Background

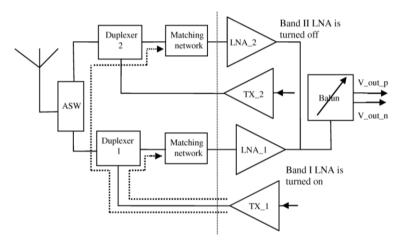

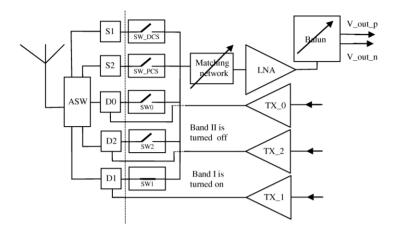

The first chipsets targeted for E-GSM [1] in the 1990s only supported one single frequency band. Since then there has been a tremendous growth in the number of subscribers of different cellular radio systems. This development has also resulted in an increase in the number of frequency bands a cell phone must support since different operators over the word have licenses for different parts of the frequency spectrum. For LTE FDD [2], [3] receive frequency bands between 700MHz and 2700MHz are defined while LTE TDD [2], [3] operates in bands between 1800MHz and 3800MHz. For the cell phone user multiband operation offers great advantages while moving across operator regions but for the chipset manufacturer multiband support also results in increased complexity of the RF front end, both on-chip and on the PCB. The increased complexity also increases the importance of designing new front end solutions to keep the cost low for the complete radio transceiver. However, new innovative solutions are always benchmarked against old architectures in terms of current consumption, performance and die area thereby making the implementation of new ideas a very challenging task. Both paper I and II in this thesis concerns single ended LNA and mixer architectures. The single ended topology is used to reduce the complexity of the multiband front end

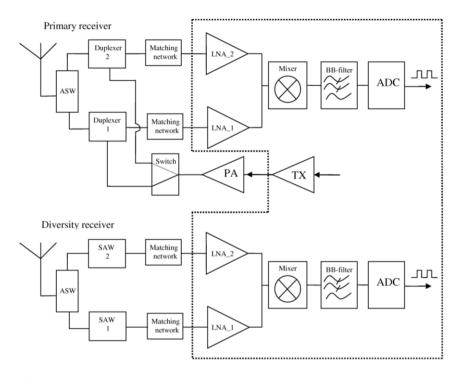

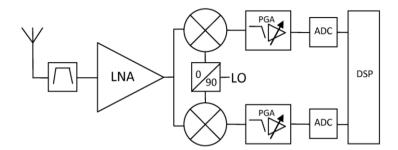

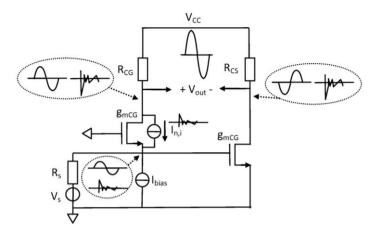

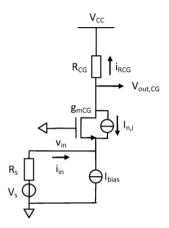

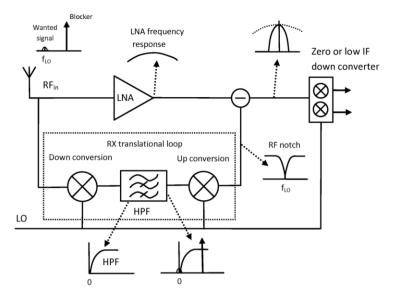

The illustration of the multiband direct conversion receiver [4], [5] in Fig.1 is simplified and only shows two LNAs in the primary and diversity receiver chains. In reality an implementation that covers the majority of the WCDMA or LTE frequency bands plus the E-GSM bands contains a larger number of LNAs. The mixer is however as illustrated shared between the LNAs. The received RF signal is downconverted in the mixer and low-pass filtered in the baseband filter. An analog to digital converter, ADC, converts the analog signal into a bit stream for subsequent processing. The introduction of antenna diversity [6] doubled the number of required LNAs. When support for antenna diversity is implemented the receiver contains two independent receiver chains connected to separate antennas as depicted in Fig.1. In e.g. urban environments the radio signal is reflected against buildings and destructive interference can occur due to multipath propagation. Having two receivers connected to different antennas separated by a small distance reduces the impact of deep fading dips significantly.

Fig.1. Multiband direct conversion receiver with primary and diversity receiver chains

Each RF input, except the diversity inputs, needs a dedicated duplexer for the supported frequency band if the radio system is operating in full duplex e.g. WCDMA [3] and LTE [3]. The purpose of the duplexer is to attenuate the transmitted signal from the power amplifier, denoted PA in Fig. 1, in order for this signal not to compress the receiver. If the RF input is used for a TDD [3] system like E-GSM a SAW filter is required in order to attenuate the out of band interferers [7]. Typically the duplexer or SAW-filter is required to be matched to 50  $\Omega$  impedance in a single ended architecture. If a differential LNA is used the RX impedance is higher, e.g.  $100~\Omega$  or  $200~\Omega$ . Each LNA normally needs off-chip matching components to fulfill the matching requirement. This adds both cost and PCB area. A solution with programmable on-chip matching is presented in paper II. The PCB routing of the RF input signals from the antenna switch, through the duplexers, to the RFIC becomes increasingly more complex as more frequency bands are added.

The direct conversion receiver radio architecture has been the dominating architecture in cellular RF chipsets for more than 10 years. It has a lot of advantages but also some drawbacks, especially in a FDD radio system. The main advantage is that the IF-filter present in the superheterodyne receiver [4] is

eliminated. The drawback is the receiver sensitivity to second order distortion. In radio systems like WCDMA and LTE the transmitter and receiver are on simultaneously. The transmit signal is a digitally modulated signal that contains both amplitude and phase modulation. A small part of the transmit signal leaks into the receiver where the amplitude part of the modulation together with second order distortion in the LNA and mixer will cause an in-band interferer that cannot be removed and therefore causes the bit-error-rate (BER) of the receiver to increase for high transmit powers. This is troublesome since the typical scenario when transmitting with full power coincides with the fact that high sensitivity is also required, i.e. the terminal is very far from the base station. In Paper II a single ended mixer is presented with a feedback loop that suppresses second order distortion. A second drawback associated with the direct conversion receiver is that this architecture is sensitive to low frequency flicker noise. A third drawback of this architecture is the impact of DC-offsets in the receiver chain on the receiver performance [5].

The low noise amplifier (LNA) and mixer are the key building blocks when designing a receiver. By designing these two blocks with high performance regarding e.g. noise figure, gain and linearity, the specifications of the succeeding blocks, i.e. baseband filter and the analog to digital converter (ADC), can be relaxed. Designing high performance LNA and mixers are therefore of highest importance since these building blocks determine many of the overall system parameters of the radio receiver, e.g. sensitivity and blocking.

Lately coexistence issues [8] between cellular systems and other radio technologies like WLAN [8], Bluetooth [1] and Global Positioning System (GPS) have been getting higher attention since support for these radio standards are now more frequently integrated in the cell phone. In a handheld device there are typically one antenna for the cellular transceiver and another antenna for e.g. WLAN in close proximity. The isolation between these antennas is rather low, in the range of 10-15dB, resulting in that a large interferer will leak into the cellular receiver. This can result in receiver performance degradation, especially if a broadband LNA without selectivity is used. There are however several ways to reduce this interferer by novel LNA and mixer design.

## 1.2 Cellular radio systems duplexing architectures

All standards for cellular communications systems specify a way to send and receive data simultaneously. This is denoted as duplexing. There are two basic concepts to achieve this, FDD, frequency division duplex and TDD, time division duplex. In TDD systems the same frequency is used both to receive and transmit but transmission and reception occurs at different time slots. In FDD systems the receiver and transmitter are using different frequencies separated by the duplex distance. Some cellular standards have both a TDD and a FDD mode, i.e. WiMAX

[10] and LTE [3]. Typical TDD systems are E-GSM [1], Time Division Code-Division Multiple Access (TD-CDMA) [2], Time Division Synchronous Code Division Multiple Access (TD-SCDMA) [2], and LTE TDD [3]. WCDMA [3] and LTE FDD [3] are well known FDD systems.

There are advantages and drawbacks related to both TDD and FDD systems. The fact that the transmitter and receiver are simultaneously turned on in a FDD system increases the requirements on the receiver since it must be designed in such a way that it can withstand any performance degradation caused by transmit signal. In order to relax the requirements on the receiver a duplexer is connected after the antenna to separate the transmit and receive frequencies. FDD systems must have a frequency distance between the transmit and receive frequencies that is large enough to achieve enough filtering in the duplexer. On the other hand a TDD system needs a distance in time to separate the transmit and receive signal [11]. One drawback associated with TDD systems is that the time distance must increase if the distance between the base station and the mobile is large, i.e. in large cells [12]. This thesis only considers radio architecture issues related to FDD systems.

#### 1.3 Silicon process technology choices

Today the RF CMOS technology is the dominating process choice for the wireless industry. For ASICs that are to be implemented in high volume consumer products cost is the main driver for choosing process technology. Some years ago when RF CMOS devices were not performing as well as their bipolar counterparts the BiCMOS technology was the technology of choice offering both high performance devices for RF design as well as CMOS devices for the digital part. Advances in RF CMOS process technology has resulted in devices with a transit frequency (f<sub>T</sub>) exceeding 300GHz in the 28nm process node [13]. Devices with low F<sub>min</sub> are available that enables the design of low noise amplifiers. The main difference compared to digital CMOS is that the RF CMOS process has a process option with low resistance metal layers in order to implement on chip inductors with high Qvalues. RFICs developed today include an increasingly large digital part for each generation making future process scaling important for cost effectiveness. The BiCMOS technology has evolved into the silicon germanium (SiGe) BiCMOS process [14]. With this technology high performance heterojunction [14] devices are available with high f<sub>T</sub>. SiGe BiCMOS is popular for designing e.g. power amplifiers due to its higher breakdown voltages compared to RF CMOS as well as lower power consumption [14]. The LNA and mixer described in Paper I of this thesis is implemented in BiCMOS technology while the LNA presented in paper II is designed in a 90nm CMOS process.

#### 1.4 Thesis structure

The first part of the thesis provides the theoretical background that constitutes the base for the two included publications. The radio requirements, e.g. sensitivity, intermodulation and compression are described in chapter 2. An overview of receiver architectures besides the direct conversion receiver is provided in chapter 3. In chapter 4 key device parameters are compared for bipolar and CMOS technology. In chapter 5 the package technology evolution from wire-bonded to wafer-level packaging is described. Different LNA architectures, i.e. single-ended, balanced, narrow-band, broadband architectures, are described in chapter 5 together with the key LNA performance parameters. In chapter 6 the mixer non-idealities are described together with a comparison between different mixer architectures, i.e. active mixers and passive mixers in their single ended and double balanced versions. Future radio architectures targeted towards SAW-less E-GSM receivers and FDD systems without duplexers are described in chapter 7. The conclusions are given in chapter 8.

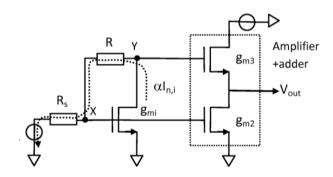

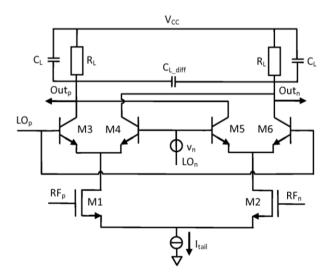

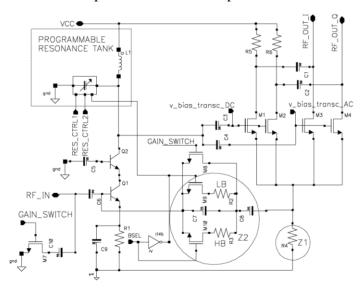

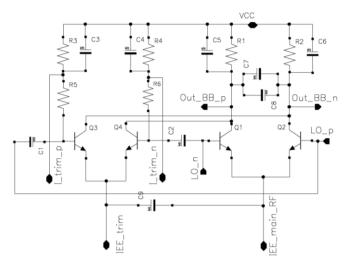

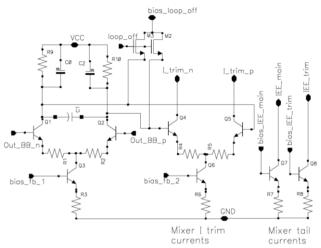

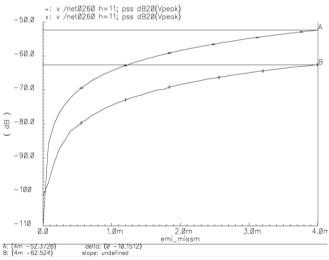

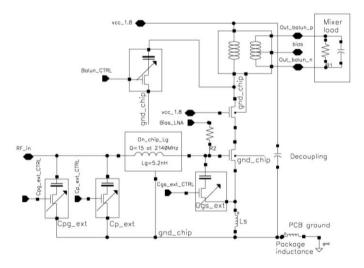

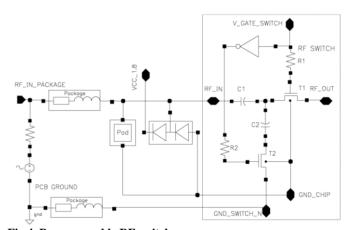

In the second part the two included publications are discussed. Paper I describes the design and simulation of a novel single ended LNA and mixer designed in BiCMOS targeted for direct conversion architectures. The single ended mixer has a feedback loop around the mixer switching core to reduce the second order distortion. The third order distortion is minimized through a feedback loop in the mixer transconductance stage. Paper II is a conference paper that describes the design of a single ended multiband CMOS LNA with integrated matching inductor. The matching can be programmed for different frequency bands using switched capacitors. The different band inputs are connected to the multiband LNA through programmable switches that provide both high isolation and low on-resistance depending on which mode they are in.

# 2 Receiver requirements

#### 2.1 Introduction

Radio communication standards, such as GSM/EDGE [15], WCDMA, LTE and WiMAX use a variety of modulation schemes for transmitting and receiving data. The requirements on the signal-to-noise ratio, SNR, at the detector to achieve a certain bit-error-rate (BER) [16] are therefore different. High data rates in the downlink using modulation schemes as e.g. 64-QAM [16] are actually only possible to achieve when the signal strength is high. The receiver requirements on the individual blocks will also depend on which architecture is used. The zero-IF architecture is the most commonly used but the linearity requirements on the LNA and mixer are harder compared to a super heterodyne topology. In this chapter a zero-IF architecture is assumed when the requirements are analyzed.

#### 2.2 Sensitivity

One of the most important metrics of the receiver is its sensitivity [17]. The receiver sensitivity if defined as the minimum input radio signal that results in a certain bit-error-rate. Typically a receiver of today has a sensitivity that is better than -110dBm. Even though such high sensitivity is not required by standardization organs, e.g. 3GPP [3], the metric is used to compare radio architectures between competitors. A high sensitivity is beneficial when designing a cellular radio network since high sensitivity means that the radio base stations do not have to be that densely located that would have been the situation if the terminals within the network would have had lower sensitivity.

The sensitivity of the receiver is affected by several parameters:

- the noise figure, NF, of the integrated receiver

- the insertion loss in the antenna switch receive path

- the insertion loss in the external filters, i.e. the E-GSM SAW filters and the duplexers for FDD systems

the required minimum carrier to noise and interference ratio, C/(N+I) for the detector

The stringent requirements on sensitivity strongly limit the radio architectures that are possible to implement in order to achieve a sensitivity that is as high as -110dBm. Regarding e.g. LNA architectures, topologies that have advantages such as broadband input matching and high linearity as the common-gate architecture are not often implemented in a cellular terminal. This is due to that the noise figure of the common-source LNA is slightly lower than for a common-gate LNA under certain bias conditions and operating frequencies [18]. In the link budget the receiver noise figure is balanced against the requirements for linearity. Too high gain in the first stages of the receiver, i.e. the LNA and mixer is advantageous for the total noise figure but the linearity is usually compromised resulting in an overall reduction of the carrier to noise and interference ratio. Typically the integrated receivers of today have a noise figure of 2.5-3dB including the noise from the external matching components for the LNA.

Thermal noise in the resistance of the signal source puts a fundamental limit on the minimum input signal that can be detected by the receiver [17]. When the power of the signal is reduced below the noise level of the source resistance the signal can no longer be distinguished from the noise. The available noise power  $P_{NA}$  [17] is defined by (1) where k equals Boltzmann's constant (1.38e-23J/K), T is the absolute temperature in Kelvin and  $\Delta f$  equals the noise bandwidth in Hz.

$$P_{NA} = kT\Delta f \tag{1}$$

At  $T=T_0=290K$  the available noise power  $P_{NA}$  with  $\Delta f=1$ Hz equals 4.00e-21W or -174dBm. The noise figure (2) of the receiver is defined by the SNR at the receiver input and output [4].

$$NF = SNR_{in} / SNR_{out} = P_{sig} / P_{R\_source} / SNR_{out}$$

(2)

$P_{sig}$  is defined as the power of received signal per unit bandwidth and  $P_{R\_source}$  is the noise power of the source resistance per unit bandwidth. Solving for  $P_{sig}$  and integrating over a certain bandwidth  $\Delta f = B$  gives the signal power  $P_{sig}$  BW.

$$P_{sig-BW} = P_{R-source} \cdot NF \cdot SNR_{out} \cdot B \tag{3}$$

The receiver sensitivity can be calculated using equation (3) and the minimum required SNR value for the detector [4]. The noise power of the source resistance  $P_{R\_source}$  is then equal to -174dBm/Hz.

$$P_{sensitivity} = P_{R\_source\_dBm/Hz} + NF_{dB} + SNR_{\min\_dB} + 10\log B$$

(4)

Inserting typical values for E-GSM, i.e. NF=3.5dB including SAW filter and antenna switch,  $SNR_{min\_dB} = 10$ dB and B=135 kHz then gives a sensitivity of -109dBm which is approximately the performance of a receiver today.

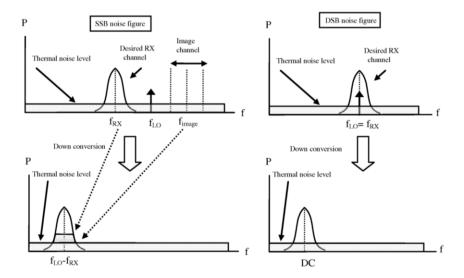

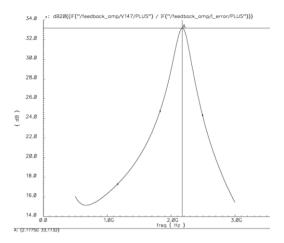

# 2.3 Single sideband and double sideband noise figure

The measured noise figure of the direct conversion receiver is given by the double sideband noise figure,  $NF_{DSB}$ . With this definition of noise figure the image and the wanted RF signal are down converted to the same baseband frequency. With the single sideband noise figure definition,  $NF_{SSB}$ , noise at the image frequency is downconverted to the same baseband frequency as the wanted signal. However, since there is no signal at the image frequency for the single sideband noise figure definition, the SNR of the baseband signal decreases. The noise figure definitions [4] are outlined in Fig. 2. Compared to the single sideband noise figure,  $NF_{SSB}$ ,  $NF_{DSB}$  is 3dB less than  $NF_{DSB}$  if the noise level at the wanted and image frequency are the same.

Fig. 2. Single and double sideband noise figure definitions

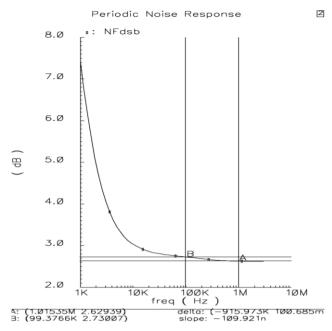

# 2.4 Noise folding

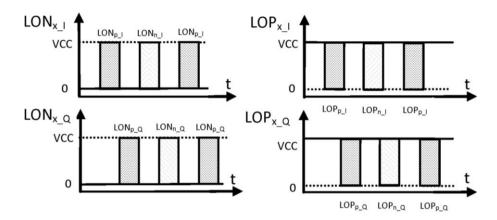

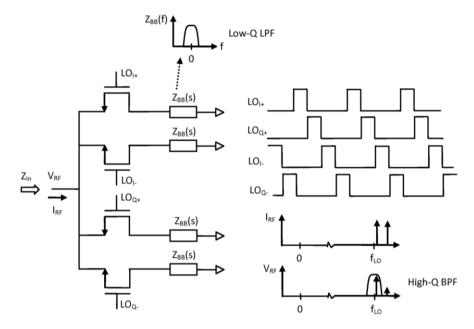

The mixer LO signal is a square wave, i.e. ideally its Fourier transform only contains odd harmonics of  $f_{LO}$ . In a mixer noise at odd harmonics of  $f_{LO}$  is down converted to baseband frequencies as well [17]. The degradation of the noise figure due to noise folding can be significant, especially if a broadband LNA is used. The programmable active mixer in paper I uses a tunable low-pass filter in the transconductance amplifier to attenuate the noise at  $3f_{LO}$ .

#### 2.5 Intermodulation

#### 2.5.1 Introduction

Intermodulation is a key parameter when defining the receiver requirements. The nonlinearities of the receiver can generate in-band intermodulation distortion from two interfering signals that are located outside the channel bandwidth. The interfering signals can originate from the transmitted signals from the base station to neighboring cellular terminals, from the transmitter of the own terminal or from the transmitter of other terminals. Different radio communications systems deployed in the same area might cause undesired interaction.

#### 2.5.2 Second and third order nonlinearities

#### 2.5.2.1 Second order nonlinearities

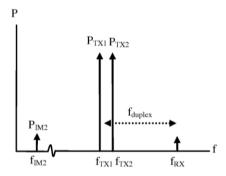

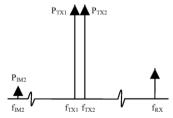

The interferer is in certain cases a modulated signal that contains both AM and FM modulation. The AM modulation of the signal can be represented by a two-tone interferer with two close frequencies,  $f_{TXI}$  and  $f_{TX2}$ , separated by the modulation frequency. For WCDMA or LTE the largest modulated signal is the TX leakage signal into the LNA through the finite isolation of the duplexer. The maximum receiver IM<sub>2</sub> level due to TX-leakage is specified in a 3GPP test case defining the minimum receiver sensitivity while transmitting at full power, i.e. 24dBm. This is depicted in Fig. 3 with second order distortion generated at the interferer difference frequency  $f_{IM2} = f_{TX1} - f_{TX2}$  [19].

Fig. 3. Second order distortion with AM modulated TX-leakage

The nonlinear system consisting of the LNA and mixer can be represented with a mixer output signal y(t) and an input signal x(t). If only second and third order nonlinearities are accounted for the output signal is given by (5).

$$y(t) = a_1 x(t) + a_2 x^2(t) + a_3 x^3(t)$$

(5)

If the input signal is the two-tone interferer at  $\omega_1$  and  $\omega_2$ , x(t) is given by (6) where A is the signal amplitude of the interferers.]

$$x(t) = A\cos(\omega_1 t) + A\cos(\omega_2 t) \tag{6}$$

The second order nonlinearity will create second order distortion products,  $y_2(t)$  defined by (7) [20]

$$y_2(t) = a_2 A^2 (1 + \frac{1}{2} \cos(2\omega_1 t) + \frac{1}{2} \cos(2\omega_2 t) + \cos((\omega_1 + \omega_2)t) + \cos((\omega_1 + \omega_2)t))$$

(7)

The second order intermodulation products are created at frequencies  $\omega_I + \omega_2$ ,  $\omega_I - \omega_2$  and DC [19], [20]. The power of the intermodulation products is calculated by squaring and integrating the contributions in (7). In power the  $IM_2$  products are then distributed as 50% (-3dB) at DC, 25% (-6dB) at  $\omega_I + \omega_2$  and 25% (-6dB) at  $\omega_I - \omega_2$ . With the second order intercept point referred to the input denoted as  $IIP_2$  and if each of the two input tones has the power P, the following applies in log-scale for the second order intermodulation product  $P_{i\_IM2\_(f_1-f_2)}$  calculated back to the LNA input [19]

$$P_{i-IM2-(f_1-f_2)} = 2P - IIP_2 \tag{8}$$

#### 2.5.3 Third order nonlinearities

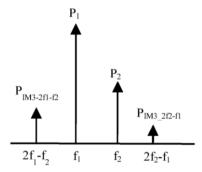

If the two-tone input signal is given by (9) with different amplitudes  $A_I$  and  $A_2$  the third order nonlinearity of (5) will create low frequency third order intermodulation products given by (10) [20]. The interferer scenario is depicted in Fig. 4.with two interferers at  $f_I$  and  $f_2$ .

Fig. 4. Third order distortion with interferers of different powers

$$x(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t) \tag{9}$$

Third order intermodulation products will be generated at  $2f_1$ - $f_2$ ,  $2f_2$ - $f_1$ ,  $2f_1$ + $f_2$  and  $2f_2$ + $f_1$ . Only the two first products as defined by (10) are of interest in a receiver.

$$y_3(t) = \frac{3}{4}a_3A_1^2A_2\cos(2\omega_1 - \omega_2)t) + \frac{3}{4}a_3A_2^2A_1\cos(2\omega_2 - \omega_1)t) + \dots$$

(10)

With the input third order intercept point defined as  $IIP_3$ , the  $IM_3$ -product at  $2\omega_2$ - $\omega_l$  in log-scale is given by (11) [20].

$$P_{IM_{3}-2\omega_{2}-\omega_{1}} = 2P_{2} + P_{1} - 2IIP_{3}$$

(11)

For the  $IM_3$ -product at  $2\omega_1$ - $\omega_2$  (12) applies [20].

$$P_{IM_2-2\omega_1-\omega_2} = 2P_1 + P_2 - 2IIP_3 \tag{12}$$

Setting  $P_1 = P_2 = P$  gives the intermodulation product defined by (13).

$$P_{IM_2} = 3P - 2IIP_3 \tag{13}$$

#### 2.6 Compression

Compression of a receiver occurs when the input signal level is high enough that the receiver is close to clipping. The nonlinearities of the receiver are then increasing rapidly with input power and the gain is reduced. The compression point, CP<sub>1dB</sub>, is defined as the input power where the gain has dropped by 1dB. Typically there are requirements on two different compression cases. In the first case the wanted signal is compressing the receiver. This can occur if the cellular terminal is close to the base station. The maximum power of the WCDMA wanted signal is -25dBm [3] With a strong wanted signal the gain of the receiver chain can be reduced while still maintaining a SNR that is high enough that the bit-error rate, BER, is not affected. Typically the gain in both the LNA and the baseband filter is programmable. In paper I the gain switch is implemented in the transconductance amplifier. In paper II the gain of the LNA is altered by reducing the bias current of the LNA. The 50  $\Omega$  input matching is maintained by tuning the on-chip matching. In the second case an out of band signal or a signal close to the received channel is the interferer that compresses the receiver. The receiver must be able to handle this signal level otherwise desensitization [4] will occur. For interferers that are outside the channel bandwidth compression typically occurs before the low pass baseband filter, i.e.in the LNA and mixer. To avoid cross compression of the small wanted signal by the interferer the biasing current must be increased.

The external filters preceding the LNA, i.e. the SAW filter in GSM and the duplexer in WCDMA and LTE FDD attenuate out of band interferers. In GSM the largest interferer is at 0dBm [3]. In WCDMA and LTE it is reduced to -15dBm [3], [20]. Without the GSM SAW filter the current consumption of the LNA would become unreasonably high. The requirement that is defining the GSM cross compression point is instead the blocking signal at  $\Delta f$ =3MHz from the carrier. For

this interferer CP<sub>1dB</sub> should be at least -23dBm [3]. For FDD systems, e.g. WCDMA and LTE FDD the required compression point is defined by the transmitter signal that leaks through the duplexer. A duplexer typically has a TX to RX attenuation of 50-55dB. The maximum output power at the antenna is +24dBm [3]. If the combined insertion loss in the TX path of the duplexer plus the antenna switch is 2dB the required output power from the power amplifier is +26dBm. If a duplexer isolation of 52dB is assumed the TX power is -26dBm in RX. This is the largest interferer that the WCMDA/LTE receiver must handle. The -15dBm out-of-band interferer is attenuated by the duplexer to -around 45dBm [20] The instantaneous power is higher though due to that certain modulation schemes, have a crest factor [21] that increases the peak power.

Recently there have been a lot of research activities in receiver architectures that can handle large interferers without depending on external SAW filters in GSM/GPRS/EDGE [22], [23], [24] or duplexers in WCDMA/LTE [25], [26]. As the cellular terminal supports an increasing number of frequency bands, the cost of the external filters is in the same range as the RF ASIC itself.

#### 2.7 Desensitization

Receiver desensitization [4] is a reduction of the receiver sensitivity when a large interferer is present simultaneously as the desired signal. The desensitization is a combination of several effects. When the amplitude of the interferer is increased above a certain level the gain of the wanted signal starts to decrease. This is denoted as cross compression of the receiver. If the gain of the LNA and mixer is reduced the noise of the baseband filter and ADC will be more visible, i.e. the receiver noise figure is increased. In a FDD system like WCDMA or LTE FDD the worst interferer is the own modulated transmitter signal. Second order nonlinearities in the receiver will generate an in-band interferer that will cause desensitization. The active mixer presented in paper I is programmable in two modes depending on the TX power. For low TX power the transconductance stage is DC coupled to the mixer switching core. For high TX power the low frequency IM<sub>2</sub> products are heavily attenuated using AC coupling. The current consumption of the mixer is significantly reduced in the DC coupled mode. Another effect causing receiver desensitization is the down conversion of the TX phase noise at the receiver LO frequency. The TX noise leaks into the receiver through the finite isolation of the duplexer. This puts requirements on the VCO, the LO path and the IQ modulator [25]. At present a typical receiver has an overall noise figure of 2.5-3dB and is specified with 0.5-1dB noise figure degradation due to the TX-leakage at full output power. [25]. The duplexer with its high TX to RX isolation reduces the desensitization but also adds insertion loss [26].

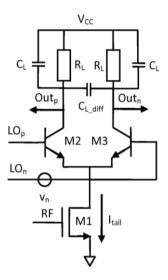

# 2.8 Harmonic mixing

The mixer LO signal is a square wave, i.e. ideally its Fourier transform only contains odd harmonics of  $f_{LO}$ . The wanted RF signal is down converted with the fundamental tone of the LO signal to a baseband signal. However, the harmonics down convert RF signals to exactly the same baseband signal. This will deteriorate the receiver performance especially when large interferers are present at  $n*f_{IO}$ . The square wave shape of the LO signal is necessary in order to achieve a low noise figure and high linearity of the mixer [4]. The interferer that is down converted by harmonic mixing could be generated within the cellular terminal itself. Radio communication systems like e.g. WLAN [27] will in the nearby future more often be integrated in the terminal together with the cellular radio. These coexistence issues [28] become increasingly complex as the cellular terminal supports more communication standards. At present a lot of research is being done on SAW-less receivers [22], [23], [24] with no filtering before the LNA. In these novel architectures harmonic mixing is one of the main obstacles. There are several ways to address the issue with harmonic down conversion. One way is not to use broadband LNAs without selectivity. The LNA in paper II uses programmable narrow band matching in combination with a tunable narrow band balun to reduce the harmonic mixing at  $3f_{LO}$ . Another way is to use an eight phase mixer [29] that mimics the sinusoidal LO signal using a sequence of eight square-wave shaped LO signals. With this solution the noise figure and linearity is not compromised.

# 2.9 Reciprocal mixing

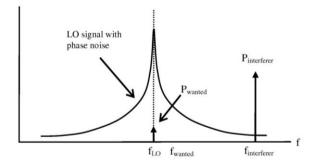

Reciprocal mixing [4] is an undesired effect that result in downconversion of an interferer by the phase noise of the LO signal. This is depicted in Fig. 8 outlining the interferer scenario with a small wanted signal and a large interferer.

Fig. 5. Reciprocal mixing

The interferer will be downconverted to DC by the phase noise. With a high power interferer the noise in the downconverted desired channel will be significant. The reciprocal mixing effect sets a limit on the maximum phase noise at the interferer frequency.

# 2.10 Second order distortion in FDD systems

For WCDMA there are both in-band and out-of-band requirements that are defined by the receiver second order linearity. The in-band requirements are defined by the in-band blocking test with a modulated blocking signal at either 10MHz or 15MHz offset from the wanted signal. Second order distortion generates intermodulation products inside the bandwidth of the wanted signal. It is however not the in-band requirement that defines the minimum  $IIP_2$  of receiver, this is determined by the out-of-band requirement, i.e. the own TX-leakage. The receiver  $IM_2$  level due to TX-leakage is tested in a 3GPP standard test case [3] that specifies the minimum required sensitivity while the TX signal is at maximum power level, i.e.+24dBm, at the antenna. Sensitivity to second order distortion is one of the most important drawbacks with the zero-IF receiver [5]. As depicted in Fig. 3 second order intermodulation products are created by the AM-modulated TX-leakage. There are four mechanisms that generate second order distortion from AM-modulated TX-leakage in a zero-IF receiver [5], [20], [32]-[37].

#### 1. RF self-mixing

The RF signal can leak to the LO signal in the mixer through parasitic coupling in the mixer switching core devices [5]. If the LO-amplitude is not high enough the mixer behaves like a linear multiplier [30] and the mixer output will contain a signal that is proportional to the square of the input signal i.e. an  $IM_2$  product.

- 2. Second order nonlinearity in the mixer transconductance stage The transconductance transistors in the active mixer have a second order nonlinearity generating a low frequency  $IM_2$  product that leaks to the mixer output. If the mixer switching core, LO driver and mixer load is perfectly balanced, i.e. without mismatch the second order intermodulation will cancel at the differential mixer output [31]. Mismatch is however always present resulting in second order distortion at the mixer output.

- 3. Second order nonlinearity of the switching mixer core devices

The switching mixer core devices have a second order nonlinearity. The IM<sub>2</sub> product generated from the core devices is common-mode, i.e. without simultaneous mismatch in the switching core devices, the LO driver or the mixer load, the second order intermodulation will cancel at the differential mixer output.

# 4. Cross modulation of the LO-leakage

The AM-modulation of the TX-leakage at the mixer core RF input will transfer to the LO-leakage at the mixer RF input through the cross modulation mechanism [20], [32]-[37]. Downconversion of the AM-modulated LO-leakage with the LO-signal itself will generate a differential mixer output signal at the  $IM_2$ -frequency.

### 2.11 Third order distortion in FDD systems

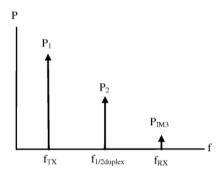

The worst third order intermodulation case is when an interferer is present at half the duplex distance between the RX and TX frequency [20] as depicted in Fig. 6. The third order nonlinearity of the LNA and mixer will then create an intermodulation product at the RX frequency.

Fig. 6. Third order intermodulation from TX-leakage and half duplex interferer

With a TX-leakage into the LNA of power  $P_1$ , a half duplex interferer of power  $P_2$  and a third order input intercept point  $IIP_3$ , the third order intermodulation product at the LNA input,  $P_{i-IM3}$ , is given by (20)

$$P_{i-1M3}(dBm) = 2P_2(dBm) + P_1(dBm) - 2IIP_3(dBm)$$

(14)

The in-band  $IIP_3$  requirement is determined by the adjacent channel selectivity (ACS) test case [3] with two blocking signal signals at 3.5 MHz and 5.9 MHz from  $f_{LO}$ . The out-of band  $IIP_3$  requirement depicted in Fig. 8 however still determines the linearity.

#### 2.12 Cross modulation in FDD systems

# 2.12.1 Cross modulation from TX-leakage

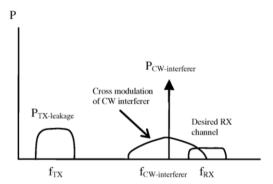

Cross modulation [20], [30]-[35] is defined as the transfer of the AM-modulation of an interferer on to a simultaneously present not modulated signal. The modulation transfer is governed by the third order nonlinearity of the system. However, in relation to the power of the modulated interferer the cross modulation power is seen as a second order effect. If the input signal to the receiver, x(t), is the sum of an un-modulated interferer,  $x_1(t)$ , and the AM-modulated TX-leakage,  $x_2(t)$ , the summed input signal leakage,  $x_3(t)$ , is given by (14).

$$x(t) = A_1 \cos(\omega_1 t) + A_2 [1 + m(t)] \cos(\omega_{TX} t)$$

(15)

In (14) m(t) is the amplitude modulation of the TX-leakage. Inserting (15) into (5) and expanding the third order nonlinearity will give an output intermodulation product [20] defined by (16).

$$y_{crossmod}(t) = \frac{3}{2} a_3 A_1 A_2^2 (1 + m(t))^2 \cos(\omega_1 t)$$

(16)

The interferer at frequency  $\omega_1$  is now amplitude modulated by the square of the amplitude of the TX-leakage as depicted in Fig. 7.

Fig. 7. Cross modulation of a CW interferer by AM-modulated TX leakage

As depicted in Fig. 6 each sideband of the cross modulated signal is at a distance from the carrier equal to the bandwidth of the AM modulated interferer [31], [35]. If a continuous wave (CW) blocker is close to the desired channel cross modulation from an AM-modulated interferer will create interference inside the bandwidth of the desired channel. In FDD systems, e.g. WCDMA and LTE FDD the strongest AM-modulated interferer is the own TX-signal.

The output cross modulation product (15) is referred to the input by dividing with the gain  $a_1$  of (1). Given the gain  $a_1$  and the third order nonlinearity coefficient  $a_3$ , the third order intercept point,  $IP_3$ , is defined as (17).

$$IP_3 = \sqrt{\frac{4a_1}{3a_3}} \tag{17}$$

The input cross modulation product,  $x_{crossmod}(t)$ , is defined in (18).

$$x_{crossmod}(t) = \frac{y_{crossmod}(t)}{a_1} = \frac{A_1 2A_2^2 ((1 + m(t)))^2}{IP_3^2} \cos(\omega_1 t)$$

(18)

Converting (17) to log-scale defines  $P_{i\_crossmod}$  in power units at the input [31] in (19). The cross modulation product is linear proportional to the interferer power and to the square of the TX-leakage.

$$P_{i \text{ crossmod}} = 6 + P_1(dBm) + 2(P_2(dBm) - IP_3(dBm))$$

(19)

Cross modulation is a second order effect that is inversely proportional to the square of the third order intercept point. As depicted in Fig. 6 the amount of interference that overlaps the desired channel will depend upon the distance between the non-modulated interferer as well of the modulation bandwidth of the TX-signal. The interferer power that overlaps the desired channel will be downconverted together with the desired channel. As with second order distortion the cross modulation is proportional to the square of the interferer power. There is however an important difference. Distortion generated by second order nonlinearities is common-mode, i.e. device mismatch is required to generate a differential intermodulation product. Distortion created by cross modulation is added to the desired RF channel before down conversion. It will therefore appear as a differential signal at the mixer output, in the same way as the desired channel. With digital modulation of the TX signal the expression (18) is modified to include a correction factor [20], [35]. The expression is therefore re-written as (120) with a correction factor including the 6dB in (19).

$$P_{i \text{ crossmod}} = C_{factor} + P_1(dBm) + 2(P_2(dBm) - IP_3(dBm))$$

(20)

The correction factor depends on the distance between the cross modulated interferer and the desired channel as well as the modulation of the TX-signal.

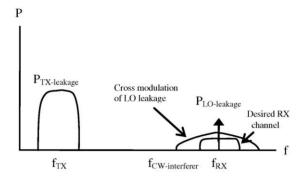

### 2.12.2 Cross modulation in FDD systems with zero-IF receivers

In a zero-IF receiver the local oscillator is set to the same frequency as the centre of the received RF channel. There is always a certain level of LO-leakage present at the LNA input acting as an interferer. The cross modulation effect will transfer the AM-modulation of the TX-leakage to the LO-leakage. The interferer scenario is now different compared the case with the external CW interferer depicted in Fig. 7 since a larger fraction of the cross modulation power will coincide with the desired RF channel. The cross modulation effect with the LO-leakage as the interferer is depicted in Fig. 8. Given that the bandwidths of the TX and RX signal are equal, a part of the cross modulated LO-leakage will be outside the RX channel since the bandwidth of the cross modulated signal is two times the TX signal. Second order distortion is created by the down conversion of the AM-modulated LO-leakage. In paper II a feedback loop around the mixer is described

Fig. 8. Cross modulation of the LO leakage in a zero-IF receiver by AM-modulated TX-leakage

The mixer is driven by a square wave signal, i.e. the LO signal as well as the leakage at the LNA input contains odd harmonics of  $f_{LO}$ . The LO leakage at the harmonics of  $f_{LO}$  will also be cross modulated. In the mixer the cross modulated harmonics will be down converted to baseband by the harmonics of the mixer clock. This effect increases the distortion generated by cross modulation. To reduce cross modulation either the duplexer isolation should be increased or the LO leakage should be decreased. Alternatively the  $IP_3$  of the system should be increased.

# 2.13 Linearity requirements in E-GSM/GPRS/EDGE systems

In the GSM system the  $IIP_2$  requirement is defined by an AM-modulated interferer 6MHz from the wanted carrier with a power of -31dBm [3]. The power of the wanted signal equals -99dBm in this test. The test sets a limit on the BER degradation with the interferer present. In a multimode receiver supporting both GSM and WCDMA this is however not the requirement that defines the minimum required  $IIP_2$ . This is instead defined by the second order distortion from the TX-leakage. The  $IIP_3$  requirement is defined in a test case with one CW interferer at 800 kHz offset from the wanted signal together with a modulated interferer at 1600 kHz from the wanted signal [3]. In a multimode terminal for both GSM and WCDMA the hardest requirement defining for third order linearity is defined by the half duplex interferer [20] in WCDMA.

# CHAPTER 3

# 3 Receiver architectures

#### 3.1 Introduction

In the early days of cellular radio communication the super heterodyne receiver [4] was the dominating receiver architectures. Once the cellular terminal started to become a high volume product a lot of research efforts both in academia as well as in the telecommunications industry were targeted towards investigating other architectures that could have equal performance but with a lower current consumption and lower cost. As the size of terminals decreased the PCB area occupied by the radio also became an important parameter. The super heterodyne architecture requires an external image reject filter [4] plus a second down conversion mixer and is therefore not a cost effective solution. Nowadays the zero-IF receiver architecture [5] is found in almost every cellular terminal. Receiver architectures are typically compared with parameters as current consumption, sensitivity, image rejection [4], blocker tolerance [3] and the required number of external components.

# 3.2 Image rejection

Image rejection [4] is a key parameter when evaluating receiver architectures. If the local oscillator frequency,  $f_{LO}$  is located at a distance  $f_{IF}$  lower than the RF carrier,  $f_{RF}$  an interferer at  $f_{IMAGE} = f_{LO}$ -  $f_{IF}$  will be down converted to the same frequency as the wanted signal. In a cellular network this interferer scenario can be troublesome especially since the wanted signal can be much smaller than the interferer at the image frequency. The receiver sensitivity will then be strongly degraded. Image rejection is an issue in all receivers that utilize an IF frequency, e.g. super heterodyne and low-IF receivers [4].

#### 3.3 The direct conversion receiver

#### 3.3.1 Direct conversion receiver architecture

Compared to a super heterodyne receiver the direct conversion receiver architecture [5] depicted in Fig 9 only has a single down converting mixer. If the local oscillator frequency is equal to the received frequency the architecture is a homodyne or zero-IF receiver.

Fig. 9. Architecture of the zero-IF receiver

The direct conversion receiver completely dominates the receiver architectures of cellular chipsets today. The shift towards this architecture started in the late 1990s when the first homodyne receivers where commercialized. If the local oscillator frequency,  $f_{LO}$ , is shifted to the centre frequency of the carrier frequency,  $f_{RF}$ , the IF frequency,  $f_{IF}$ , will be zero. The centre of the carrier frequency is down converted to DC. The issue with an image frequency that can interfere with the wanted signal is eliminated [5]. This is one of the two great advantages with this receiver architecture. The second advantage is the simplicity of the baseband filter in a zero-IF receiver. It is realized with only a low-pass filter [5].

#### 3.3.2 Direct conversion receiver drawbacks

#### 3.3.2.1 LO-leakage at the LNA input

The LO-leakage at the LNA input is associated with three receiver performance issues that must be addressed: LO radiation at the antenna [5], DC offset at the mixer output [5] and cross modulation of the LO-leakage with the TX-leakage [20], [32]-[37]. Since the mixer clock frequency  $f_{LO}$  is at the same frequency as the received channel the LO-leakage at the LNA input will mix with itself in the receiver mixer [5]. There are requirements [3] restricting the power of the mixer clock frequency and its harmonics at the antenna since this leakage will be radiated out of the cellular terminal and becomes an interferer for other terminals [5]. The LO-leakage at the antenna will be down converted to DC at the mixer output that can compress the performance of the baseband filter and ADC.

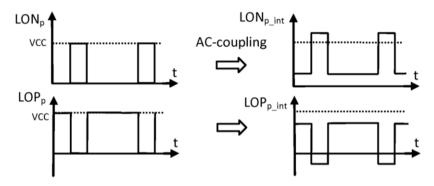

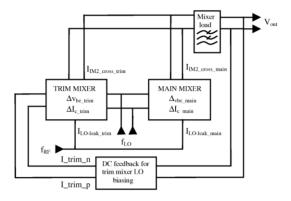

In zero-IF receivers the DC offset at the mixer output has been reduced by running the receiver voltage controlled oscillator (VCO) at a frequency  $f_{VCO}$  that is an even multiple of the mixer clock frequency  $f_{LO}$ . If the clock signal to the mixer is a square wave the Fourier transform of this signal only contains odd harmonics of  $f_{LO}$ . Leakage at  $f_{VCO}$  or at harmonics of  $f_{VCO}$  at the LNA input does not result in any DC offset since the mixer clock signal does not contain any harmonics of  $f_{VCO}$ . In paper I the LO-leakage due to mismatch in the switching stage of the active mixer is attenuated with a feedback loop around the mixer core.

#### 3.3.2.2 DC-offset at the mixer output

One easy way to eliminate the problem with DC-offset would be to AC-couple the output signal from the mixer [2]. However this is not a feasible architecture since modulation schemes used for high speed communication, e.g. 64QAM [16] contain information at low frequencies close to DC. Considering the impedance in the interface between the mixer and the baseband filter the size of the AC-coupling capacitor, required not to cause increased BER, is not feasible to integrate on-chip. The preferred way to reduce the DC-offset is instead to use offset cancellation techniques [5]. With these techniques the DC-offset is measured and averaged over time and then subtracted from the output signal. DC-offsets as well as cut-off frequencies in the baseband filter are reduced by using calibration techniques. In paper I the mixer DC-offset is attenuated using a feedback loop around the mixer core.

#### 3.3.2.1 Sensitivity to second order distortion

Second order nonlinearities in the zero-IF receiver cause performance degradation in TDD as well as in FDD systems. In E-GSM the receiver must handle an AM-modulated interferer at 6MHz offset from  $f_{LO}$ . In FDD systems the AM-modulation of the TX-leakage generates second order distortion from self mixing [5], second order nonlinearities in the transconductance stage [31], second order nonlinearity in the switching core devices and cross modulation of the LO-leakage [20], [32]-[37].

#### 3.3.2.2 Sensitivity to mixer 1/f noise

Since the RF signal is down converted to DC the zero-IF receiver is sensitive to 1/f noise [5]. The 1/f noise in active mixers with a bipolar switching core is much lower compared to the 1/f noise in active mixers in CMOS technology. In CMOS technology the passive mixer architecture is therefore dominating. The mixer in paper I is designed with a bipolar switching core.

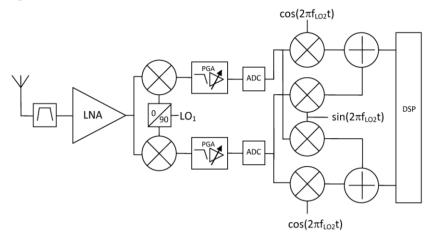

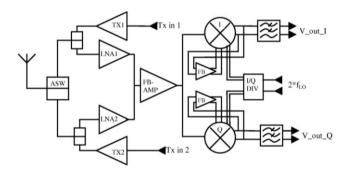

#### 3.4 The low-IF receiver

In the low-IF architecture [38], [39] the LO frequency is offset from the RF carrier frequency in the range of the channel bandwidth [38]. The down conversion to baseband frequencies can take place in a complex mixer in the digital domain [38] providing image rejection. A typical low IF receiver architecture is depicted in Fig. 10.

Fig. 10. Architecture of the low-IF receiver

Since both the wanted signal and the image frequency are present in the input signal to the ADC the requirements for the ADC in a low-IF receiver are higher compared to a homodyne receiver. This increases the power consumption of the ADC. The image power could be significantly higher compared to the wanted signal. One advantage with this architecture is that the ADC is AC coupled to the preceding analog part of the receiver. This eliminates the need of DC-offset compensation. The low-IF receiver is less sensitive to 1/f noise originating from the mixer since the carrier frequency is not down converted to DC as in the zero-IF receiver. Especially in active CMOS mixers noise figure degradation due to 1/f noise is troublesome. Passive CMOS mixers ideally do not suffer from excess 1/f noise since there is no DC biasing current [40]. Compared with the zero-IF receiver, the signal processing of the IF-signal that is required after the mixer is more demanding in a low-IF receiver. In the low-IF receiver image rejection [38], [39] must be implemented either in the analog or the digital domain. In either way the image rejection is highly sensitive to mismatch. [38], [39].

Instead of implementing a complex mixer for image suppression in the digital domain a complex band pass filter could be designed in the analog domain [38].

# 3.5 Receiver architecture summary

The zero-IF receiver architecture is the preferred choice for cellular terminal receivers even if there are drawbacks with this solution. However, compared to the calibration required to achieve sufficient image rejection in a low-IF receiver these drawbacks are easier to circumvent by high performance design of e. g. LNAs and mixers.

# CHAPTER 4

# 4 Process technology and device performance

#### 4.1 Introduction

The digital part of the integrated transceivers is increased for each new circuit generation. It is common today even to include a microprocessor used in automatic calibration of the circuit. In these system on chip architectures digital signals, e.g. harmonics of the digital clock frequency can leak to the LNA input through the supply lines, electromagnetic coupling or through the substrate [41]-[49]. On-chip isolation governed by package and process technology is therefore becoming increasingly important. An increased digital part also means that more digital devices are switching simultaneously thereby creating more interference [44], [49]. Digital and analog functions that used to be on different dies are now merged together. The effectiveness of e.g. triple-well devices [49] is reduced for higher RF frequencies in new operating bands. For high frequency bands the package impedance is also higher.

# 4.2 Process technology

CMOS is the silicon mass production technology of today [14]. This applies to both cellular transceiver circuits as well as digital circuits. As a result of the high CMOS volumes the production cost is reduced. For cellular RF circuits in the mid 2000s BiCMOS technology was still competitive. The last technology step in BiCMOS was the performance enhancement by introduction of the SiGe bipolar devices [50]. There are several differences between bipolar and CMOS devices that affect the architecture and design tradeoffs for a transceiver circuit [50]. One difference is that the bipolar devices have a higher transconductance-to-current ratio compared to the MOS device. The  $g_m/I_C$  ratio for a bipolar device equals  $I/V_T$ . For a MOS device the  $g_m/I_D$  ratio for a long channel device equals  $2/(V_{GS}-V_T)$  and  $I/(V_{GS}-V_T)$  for a short channel device [50]. Compared to a bipolar device the  $g_m/I_D$  of the MOS device decreases when the device bias current increases. Despite this drawback the  $f_T$  of CMOS processes is today very high due to device scaling. The supply voltage is reduced as the gate oxide thickness reduces. This is a difference compared to bipolar devices that offer high  $f_T$  with high supply

voltage [14]. High voltage devices are an advantage in e.g. power amplifier design [14]. A second difference comparing bipolar and CMOS technology is the much higher level of 1/f noise in CMOS. The 1/f noise originates from traps in the interface between the gate oxide and the silicon that randomly release charges [52]. The passive mixer [52] is the preferred architecture in CMOS technology compared to BiCMOS technology where an active mixer with bipolar switching commonly used. This architecture is used in the mixer presented in paper I. Using CMOS devices in the switching core increases the 1/f noise.

When the device size is reduced the matching properties is deteriorated. This is an issue for e.g. differential architectures making it difficult to use the minimum size devices. For low frequency design device up-scaling is an effective way to counteract mismatch. This technique is used in the mixer DC feedback loop in paper I.

The performance of the analog RF part is strongly dependent on the passive components, i.e. the inductors and capacitors. The Q-value of an on-chip inductor [41], [48], [51] is one of the key metrics for comparing semiconductor processes. The noise figure of the LNA with integrated matching presented in paper II is strongly dependent on the Q-value of the integrated matching inductor.

# 4.3 Package technology

The package technology evolution has resulted in that the wire-bonded package type is no longer used for integrated transceivers for cellular terminals. The inductance of the bond wires was in the range of a few nanohenries. Coupling between nearby wires as well as supply line noise coupling was an issue in RF design. The state-of-the art packages today instead use flipped dies mounted on ball-grid arrays (BGAs) [53]. The total inductance of a connection pin is then about 200pH, including routing inductance in the flip-chip redistribution layer. The redistribution layer is the routing interface between the BGA and the pads of the die. Compared to the coupling between bond wires the coupling between the balls of the BGA package is negligible since the ball inductance is less than 50pH. There is however still a significant coupling between wires in the chip redistribution layer. For a ground connection a low inductance is obtained using parallel connection of multiple grounds. Passive components as decoupling capacitors and matching components for LNAs can be placed inside the package reducing the number of components on the PCB. This is used in the design presented in paper I requiring two off-chip capacitors. A low package inductance is desirable since the supply and ground will become more ideal, thereby relaxing the requirement on power supply rejection ratio (PSRR). Low impedance paths to ground are important for isolation, e.g. for the effectiveness of shunting an undesired signal to ground. This is used in the multiband LNA in paper II for increasing the isolation between different RF inputs. To reduce the coupling careful planning and routing is required regarding placement of signals in the die pad ring and BGA package. Supply connections with low package impedances

make it possible to use architectures that would otherwise have been hard to implement, e.g. the multiband single ended LNA presented in paper II.

# 4.4 Substrate coupling

Compared to differential architectures single ended architectures are more sensitive to substrate noise and interference and require more careful substrate interference robust [45] design. Substrate noise is caused by different sources [41] - [43]. These sources can be divided into internal sources and external sources referring to how the noise couples to the substrate [42]. The internal noise is generated when e.g. digital gates are switched [44] and the noise is coupled through the parasitic capacitances of the active devices, wells and interconnects. The external noise is created when the noise path from the digital to analog part of the die goes through the power domain network. The switching gates introduce noise on the supply lines. This noise is then coupled back to the sensitive analog part through substrate contacts in the analog domain connected to supply and ground [41], [42]. Depending on the package inductances and decoupling capacitors of the power distribution network the external noise can be dominating. Low package inductance is therefore important to reduce the external coupling. [41]. The internal noise becomes more important when the packages inductances are very small. Three mechanisms govern substrate interference: injection, propagation and reception [42]. Noise can be injected into the substrate in three ways [42]

## 1. Substrate coupling through capacitances [41], [42], [47]

The source and drain of each MOS devices is coupled to the substrate through a depletion capacitance. Depletion capacitance coupling is also an issue in bipolar process technology [46]. Interconnect lines also have a capacitance to the substrate [48]. If the interconnect carries a rail to rail digital signal and the length of the wire is long the injected substrate noise can be substantial. Bond pads have a significant capacitance to ground as well. If e.g. a digital I/O signal is connected to the pad noise can be injected into the substrate.

## 2. Injection through substrate contacts [41], [42]

NMOS and PMOS devices have either p+ or n+ diffusions close to the devices to set the potential of the bulk to either *VCC* or *GND*. The source and bulk terminal are usually connected together. The supply and ground on the die are connected to ideal ground through the series inductance and resistance of the package resulting in supply and ground bounce when e.g. a digital transition occurs in the circuit. Noise is thereby injected into the substrate through the substrate contacts connected to the noisy supply and ground.

## 3. Impact ionization currents [41], [42]

Electron-hole pairs are generated by high electric filed in the drain. The holes will diffuse down to the substrate.

Noise propagation in the substrate depends on the substrate type. Three types of substrates are used in CMOS processes [43]

## 1. Epitaxial substrates

The wafer consists of a high-resistivity thin layer on top of a low resistivity bulk. The majority of the substrate noise propagates in the highly doped bulk. Due to the low resistivity the bulk can be regarded as one node. The purpose of this type of substrate is to prevent latch-up.

## 2. Non-epitaxial substrates

The wafer consists of only high resistivity bulk. The substrate current is more uniformly distributed. Increasing the distance between an interfering block and a noise sensitive block helps to improve the isolation with this type of substrate.

## 3. Silicon-on-insulator (SOI) substrates

The devices are fabricated in silicon islands isolated from the substrate by a buried oxide layer. These processes have a much higher isolation compared to the two other types.

The same effects that cause noise injection also govern noise reception. Substrate injection and reception can be reduced using triple-well devices. The benefit is however strongly dependent on the operating frequency as well as the package impedance of the well connection [49]. Substrate propagation can be reduced using guard rings. Guard rings are more efficient in a lightly doped process [42]. The substrate noise is attenuated by sinking the noise current to a low impedance ground. The effect of the ring is dependent on the inductance of the supply connection [49]. Other substrate propagation reduction techniques are trenches, N-wells to break the channel stop and deep N-wells below the interfering block [42]. Reduction of noise reception can be achieved by using differential structures [42] since substrate noise can be regarded as common mode noise. On-chip decoupling is efficient to prevent noise from reaching the supply lines [41].

## 4.5 Basic equations for the MOS and bipolar transistors

#### 4.5.1 Introduction

The design presented in paper I is single ended LNA and active mixer in BiCMOS technology. The LNA presented in paper II is designed in CMOS technology. The fundamental transistor equations for both CMOS and bipolar devices are provided in section 4.5.2 and 4.5.3 respectively.

## 4.5.2 MOS transistor equations

In the saturation region (21) applies for the relation between the drain current  $I_D$ , the threshold voltage  $V_t$ , the gate-source voltage  $V_{GS}$  and the drain-source voltage  $V_{DS}[54]$ , [55].

$$I_D = \frac{k'W}{2L}(V_{GS} - V_t)^2 (1 + \lambda V_{DS})$$

(21)

The parameter k' defined in (22) is the product of the electron mobility  $\mu_n$  and the gate oxide capacitance per unit area  $C_{ox}$ .

$$k' = \mu_n C_{ox} = \frac{\mu_n \mathcal{E}_{ox}}{t_{ox}} \tag{22}$$

The parameters  $\varepsilon_{ox}$  and  $t_{ox}$  are the permittivity and thickness of the gate oxide respectively [54], [55]. The parameter  $\lambda$  in (23) is defined by the output resistance and drain current of the NMOS [54], [55]. With shrinking device dimensions the output resistance is decreased which is not beneficial for analog design.

$$\lambda = \frac{1}{r_{out}I_D} \tag{23}$$

The small signal transconductance [54], [55] is defined in (24).

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = k \frac{W}{L} (V_{GS} - V_t) (1 + \lambda V_{DS})$$

(24)

If  $\lambda V_{DS} << 1$  the transconductance is approximated by (25).

$$g_{m} = k \frac{W}{L} (V_{GS} - V_{t}) = \sqrt{2k \frac{W}{L} I_{D}}$$

(25)

The transconductance  $g_m$  is proportional to W/L times the overdrive voltage,  $V_{ov}$  [54], [55] defined in (26).

$$V_{ov} = V_{GS} - V_t \tag{26}$$

Decreasing the channel length and the thickness of the gate oxide increases the transconductance  $g_m$ . The MOS transistor cut-off frequency  $\omega_T$  [54], [55] given by (27) can be used to calculate the expected transconductance of e.g. an LNA.

$$\omega_T = \frac{g_m}{C_{gs}} \tag{27}$$

A thorough description of MOS device parameters is provided in [54], [55].

# 4.5.3 Bipolar transistor equations

For the bipolar transistor in the forward-active region (28) applies for the relation between the collector current  $I_C$ , the base-emitter voltage,  $V_{BE}$ , the saturation current,  $I_S$  and the collector-emitter voltage,  $V_{CE}$  [55].

$$I_C = I_S (1 + \frac{V_{CE}}{V_A}) \exp \frac{V_{BE}}{V_T}$$

(28)

The parameter  $V_A$  is the early voltage [55] defining the variation of  $I_C$  with  $V_{CE}$ . The threshold voltage is denoted  $V_T$ . The small signal transconductance,  $g_m$ , is given by (29).

$$g_m = \frac{\partial I_C}{\partial V_{RF}} = \frac{qI_C}{kT} \tag{29}$$

The output resistance [55],  $r_o$ , is defined in (30).

$$r_o = \frac{\partial V_{CE}}{\partial I_C} = \frac{V_A}{I_C} \tag{30}$$

The bipolar transistor cut-off frequency [55],  $\omega_T$ , is given by (31)

$$\omega_T = \frac{g_m}{C_\pi + C_u} \tag{31}$$

The emitter-base junction depletion capacitance is denoted  $C_{\pi}$  and  $C_{\mu}$  is the collector-base junction capacitance. A detailed description of bipolar device parameters is provided in [55].

# CHAPTER 5

# 5 LNA architectures

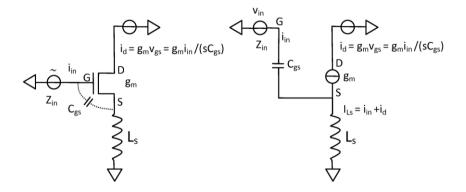

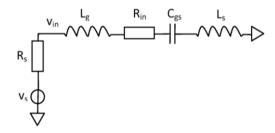

## 5.1 Introduction