# LUND UNIVERSITY

#### Adaptive Baseband Pro cessing and Configurable Hardware for Wireless Communication

Gangarajaiah, Rakesh

2017

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Gangarajaiah, R. (2017). Adaptive Baseband Pro cessing and Configurable Hardware for Wireless Communication. [Doctoral Thesis (compilation), Lund University]. Department of Electrical and Information Technology, Lund University.

Total number of authors: 1

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

# Adaptive Baseband Processing and Configurable Hardware for Wireless Communication

Rakesh Gangarajaiah

# LUND UNIVERSITY

Doctoral Dissertation Electrical Engineering Lund, March 2017

Department for Electrical and Information Technology Lund University P.O. Box 118 SE-22100 LUND SWEDEN

No. 99 ISSN 1654-790X ISBN 978-91-7753-180-7 (print) ISBN 978-91-7753-181-4 (pdf) Series of licentiate and doctoral dissertations.

CRakesh Gangarajaiah 2017. Produced using IATEX Documentation System. Printed in Sweden by Tryckeriet i E-huset, Lund. March 2017. To my Family

# Abstract

The world of information is literally at one's fingertips, allowing access to previously unimaginable amounts of data, thanks to advances in wireless communication. The growing demand for high speed data has necessitated the use of wider bandwidths, and wireless technologies such as Multiple-Input Multiple-Output (MIMO) have been adopted to increase spectral efficiency. These advanced communication technologies require sophisticated signal processing, often leading to higher power consumption and reduced battery life. Therefore, increasing energy efficiency of baseband hardware for MIMO signal processing has become extremely vital. High Quality of Service (QoS) requirements invariably lead to a larger number of computations and a higher power dissipation. However, recognizing the dynamic nature of the wireless communication medium in which only some channel scenarios require complex signal processing, and that not all situations call for high data rates, allows the use of an adaptive channel aware signal processing strategy to provide a desired QoS. Information such as interference conditions, coherence bandwidth and Signal to Noise Ratio (SNR) can be used to reduce algorithmic computations in favorable channels. Hardware circuits which run these algorithms need flexibility and easy reconfigurability to switch between multiple designs for different parameters. These parameters can be used to tune the operations of different components in a receiver based on feedback from the digital baseband. This dissertation focuses on the optimization of digital baseband circuitry of receivers which use feedback to trade power and performance. A co-optimization approach, where designs are optimized starting from the algorithmic stage through the hardware architectural stage to the final circuit implementation is adopted to realize energy efficient digital baseband hardware for mobile 4G devices. These concepts are also extended to the next generation 5G systems where the energy efficiency of the base station is improved.

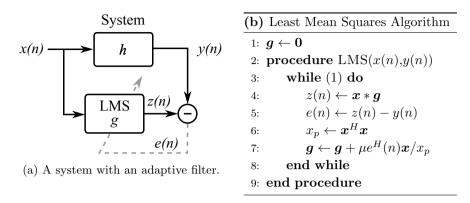

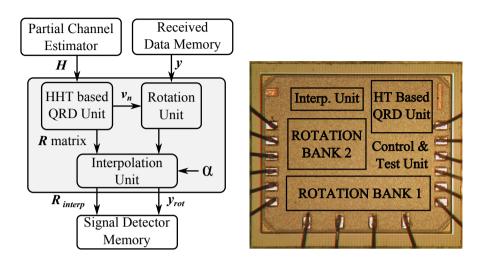

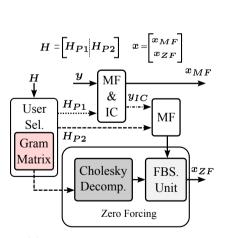

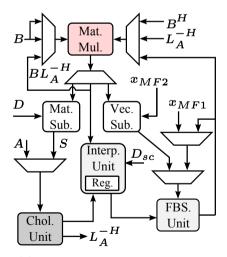

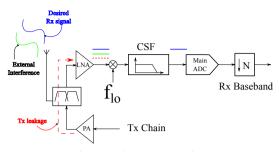

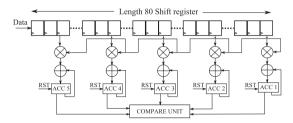

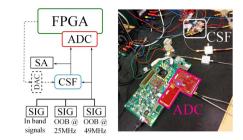

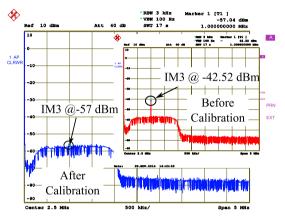

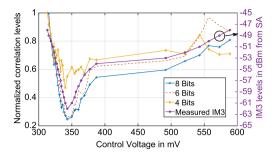

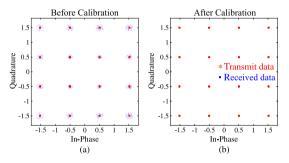

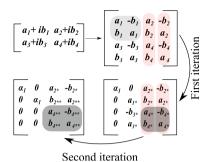

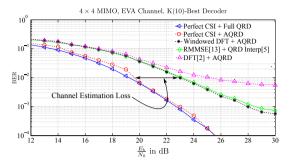

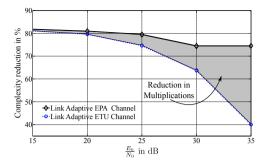

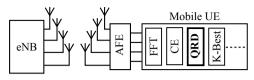

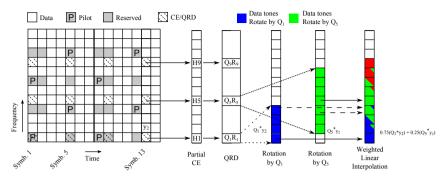

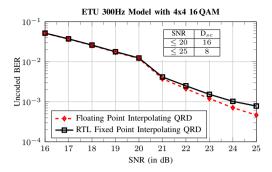

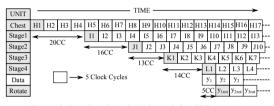

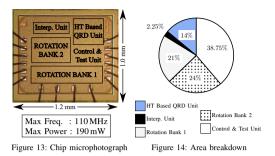

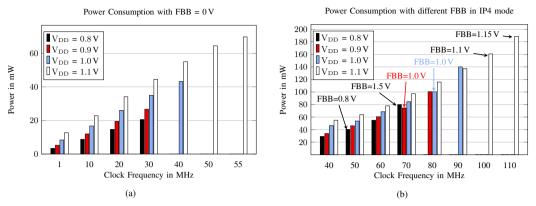

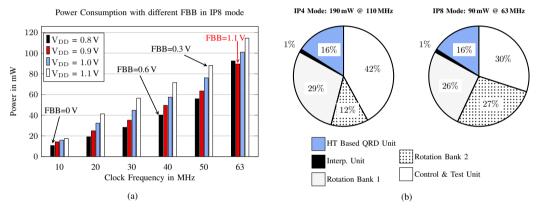

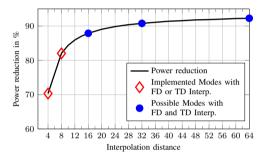

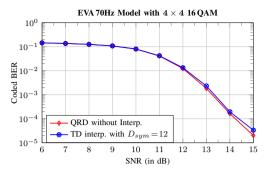

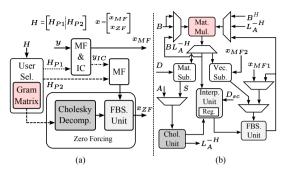

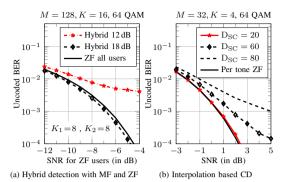

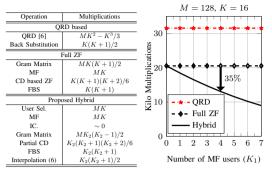

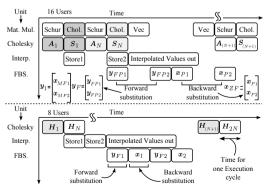

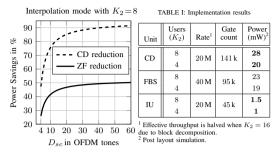

This work includes six papers that examine digital circuits in MIMO wireless receivers. Several key blocks in these receiver include analog circuits that have residual non-linearities, leading to signal intermodulation and distortion. Paper-I introduces a digital technique to detect such non-linearities and calibrate analog circuits to improve signal quality. The concept of a digital nonlinearity tuning system developed in Paper-I is implemented and demonstrated in hardware. The performance of this implementation is tested with an analog channel select filter, and results are presented in Paper-II. MIMO systems such as the ones used in 4G, may employ QR Decomposition (QRD) processors to simplify the implementation of tree search based signal detectors. However, the small form factor of the mobile device increases spatial correlation, which is detrimental to signal multiplexing. Consequently, a QRD processor capable of handling high spatial correlation is presented in Paper-III. The algorithm and hardware implementation are optimized for carrier aggregation, which increases requirements on signal processing throughput, leading to higher power dissipation. Paper-IV presents a method to perform channel-aware processing with a simple interpolation strategy to adaptively reduce QRD computation count. Channel properties such as coherence bandwidth and SNR are used to reduce multiplications by 40% to 80%. These concepts are extended to use time domain correlation properties, and a full QRD processor for 4G systems fabricated in 28 nm FD-SOI technology is presented in Paper-V. The design is implemented with a configurable architecture and measurements show that circuit tuning results in a highly energy efficient processor, requiring 0.2 nJ to 1.3 nJ for each QRD. Finally, these adaptive channel-aware signal processing concepts are examined in the scope of the next generation of communication systems. Massive MIMO systems increase spectral efficiency by using a large number of antennas at the base station. Consequently, the signal processing at the base station has a high computational count. Paper-VI presents a configurable detection scheme which reduces this complexity by using techniques such as selective user detection and interpolation based signal processing. Hardware is optimized for resource sharing, resulting in a highly reconfigurable and energy efficient uplink signal detector.

# **Popular Science**

It was not so long ago that the internet was accessible only through computers hooked up to a fixed telephone line. Data connections were expensive and slow, often requiring minutes to download a picture or a video. Thanks to the advances in wireless communication and semiconductor technology, cheap smart telephones that can perform multiple functions ranging from simple text messaging to live video streaming are now commonly used. Multiple users can seamlessly communicate with one another using different technologies such as Wi-Fi, Bluetooth, 3G, and 4G. The demand for high speed mobile data connections is growing, and 4G networks are being deployed all over the world. Several proposals have already been made for the next generation or 5G communication systems that promise download speeds of several gigabits/s even in crowded places such as stadiums or city centers. It is estimated that more than seven billion mobile subscriptions are now in use and almost half of them have internet connectivity. Although data download speeds have increased over generations, satisfying the needs of online gaming and social media, one aspect of the smartphone has left users dissatisfied. The battery life is woefully short, requiring a recharge almost every day. Modern semiconductor chips consume much less power compared to chips ten years ago, but it appears that battery life has actually reduced over time. One of the important reason for this is the processing algorithms that remove noise and interference from the extremely low power signals that are received by the mobile device. Imagine sunbathing on a good sunny day and compare it to sitting in front of a candle. The power of the signal transmitted from the base station is similar to what you would experience from the sun whereas what a mobile phone receives is comparable to the power from a candle placed several kilometers away! Furthermore, other sources of interference are continually present due to the wireless nature of the communication medium, increasing the complexity of algorithms needed for signal detection, and thus power consumption.

Despite these challenging conditions, 4G provides higher data rates than previous generations. One of the techniques that has enabled these high speeds is multi-antenna communication. Several parallel streams of data are transmitted by the base station to a user. However, even more complex signal processing is needed to recover those parallel streams compared to single antenna communication. One way of reducing this complexity is to adaptively change the processing based on environmental conditions and user requirements. For example, streaming data for a high-definition video when sitting at home is relatively easy when compared to streaming data on a high speed train. Additionally, channel conditions are highly variable in mobile communication environments, and user requirements also have a wide range. For instance, dropping a few frames when streaming a live sporting event is acceptable, whereas downloading a file has to be done with almost no errors. Adaptively detecting these requirements enables the phone to become smarter, allowing performance adjustments to be made to conserve battery power. Hardware has to be designed to support this adaptability, and a certain degree of reconfigurability is therefore required in chip implementations.

This dissertation explores such adaptive processing techniques and reconfigurable hardware for wireless receivers that use feedback to trade performance and power. Different methods of using awareness about operating conditions to improve energy efficiency are presented. The focus is on algorithms and digital implementations for wide-band multi-antenna receivers. Applications, where the analog part of the radio receiver is optimized for performance with the support of digital algorithms are also considered. Additionally, some of these concepts are applied to receivers designed for 5G systems to dynamically optimize their operation. The dissertation includes a brief introduction to the research field and six papers that present details on the experiments. The results show that using feedback with channel-aware adaptive techniques not only improves energy efficiency but is often necessary to produce cost effective mobile devices for high speed data communication.

This work was performed as part of the "Digitally Assisted Radio Evolution (DARE)" project, funded by Swedish Foundation for Strategic Research and chip fabrication was supported by STMicroelectronics.

# Contents

| Abst            | rac   | t                                                                                                                   | v                      |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------|------------------------|

| Ρορι            | ılar  | Science                                                                                                             | vii                    |

| Cont            | ent   | s                                                                                                                   | ix                     |

| Prefa           | ace   |                                                                                                                     | xi                     |

|                 |       |                                                                                                                     | •••                    |

| АСКІ            | 10W   | ledgments                                                                                                           | xiii                   |

| $\mathbf{List}$ | of A  | Abbreviations                                                                                                       | $\mathbf{x}\mathbf{v}$ |

| Intro           | odu   | ction                                                                                                               | 1                      |

| 1               | Mo    | $tivation \ldots \ldots$ | 1                      |

|                 | 1.1   | Scope of this Dissertation                                                                                          | 3                      |

|                 |       | Contributions and Outline                                                                                           | 4                      |

| <b>2</b>        | Dig   | gital Baseband Processing                                                                                           | 7                      |

|                 | 2.1   | Introduction                                                                                                        | 7                      |

|                 | 2.2   | The Digital Baseband                                                                                                | 13                     |

|                 | 2.3   | Channel Properties and Adaptive Processing                                                                          | 27                     |

| 3               | Co    | mplexity and Power Reduction                                                                                        | 35                     |

|                 | 3.1   | Introduction                                                                                                        | 35                     |

|                 | 3.2   | Algorithmic Techniques for Adaptive Processing                                                                      | 37                     |

|                 | 3.3   | Architectural Techniques for Configurability                                                                        | 45                     |

|                 | 3.4   | Circuit Techniques for Power Reduction                                                                              | 49                     |

| 4               | Ap    | plications in Digitally Assisted Radio Receivers                                                                    | 53                     |

|                 | 4.1   | Non-linearity Mitigation for Analog Circuits                                                                        | 53                     |

|                 | 4.2   | Channel Preprocessor for Small Scale MIMO Systems                                                                   | 57                     |

|                 | 4.3   | Detectors for Massive MIMO Systems                                                                                  | 62                     |

| 5               | Paj   | per Summary and Discussion                                                                                          | 69                     |

|                 | 5.1   | Research Contributions                                                                                              | 69                     |

|                 | 5.2   | Discussion and Future Work                                                                                          | 73                     |

| R               | lefer | ences                                                                                                               | <b>81</b>              |

| Inc | luded Papers                                                                               | 83  |

|-----|--------------------------------------------------------------------------------------------|-----|

| Ι   | A Digitally Assisted Non-Linearity Suppression Scheme<br>for RF front ends                 | 87  |

| Π   | A Digitally Assisted Non-Linearity Mitigation System<br>for Tunable Channel Select Filters | 97  |

| III | A High Speed QR Decomposition Processor for Carrier-<br>Aggregated LTE-A Downlink Systems  | 107 |

| IV  | Low Complexity Adaptive Channel Estimation and QR<br>Decomposition for an LTE-A Downlink   | 115 |

| V   | An Adaptive QR Decomposition Processor for Carrier-<br>Aggregated LTE-A in 28 nm FD-SOI    | 125 |

| VI  | A Cholesky Decomposition based Massive MIMO Uplink<br>Detector with Adaptive Interpolation | 141 |

\_\_\_\_\_

# Preface

This dissertation summarizes my work from October 2011 to February 2017 as a PhD student in the Digital ASIC group, at the Department of Electrical and Information Technology, Lund University, Sweden. The dissertation is divided into two parts, and the first part has five chapters that provide a general introduction to the research field. The second part includes papers written during the past four years which are also listed below.

#### Included Research Papers

The main contribution is derived from the following publications:

- I R. Gangarajaiah, M. Abdulaziz, L. Liu, and H. Sjöland, "A Digitally Assisted Non-Linearity Suppression Scheme for RF front ends", reprinted from the *Proceedings of IEEE 25th Annual International Symposium on Personal, Indoor and Mobile Radio Communications*, Washington DC, USA, September 2014, pp. 623–627.

- II R. Gangarajaiah, M. Abdulaziz, H. Sjöland, P. Nilsson, and L. Liu, "A Digitally Assisted Non-Linearity Mitigation System for Tunable Channel Select Filters", reprinted from the *IEEE Transactions on Circuits and* Systems-II: Express Briefs, vol. 63, no. 1, pp. 69–73, January 2016.

- III R. Gangarajaiah, P. Nilsson, L. Liu and O. Edfors, "A High Speed QR Decomposition Processor for Carrier-Aggregated LTE-A Downlink Systems", reprinted from the *Proceedings of IEEE European Conference on Circuit Theory and Design*, Dresden, Germany, September 2013, pp. 1–4.

- IV R. Gangarajaiah, P. Nilsson, O. Edfors and L. Liu, "Low Complexity Adaptive Channel Estimation and QR Decomposition for an LTE-A Downlink", reprinted from the *Proceedings of IEEE 25th Annual International Symposium on Personal, Indoor and Mobile Radio Communications*, Washington DC, USA, September 2014, pp. 459–463.

- V R. Gangarajaiah, O. Edfors and L. Liu, "An Adaptive QR Decomposition Processor for Carrier Aggregated LTE-A in 28 nm FD-SOI", accepted for publication in the *IEEE Transactions on Circuits and Systems-I: Regular Papers*, 2017.

- VI R. Gangarajaiah, O. Edfors, and L. Liu, "A Cholesky Decomposition based Massive MIMO Uplink Detector with Adaptive Interpolation," accepted for publication in the *IEEE International Symposium on Circuits* and Systems, 2017.

#### Other Publications

I have also contributed to other publications during my research studies that are listed below. They are however, not considered to be a part of this dissertation.

- P. Nilsson, Y. Sun, **R. Gangarajaiah**, and E. Hertz, "Low Power Unrolled CORDIC Architectures", *IEEE Nordic Circuits and Systems Conference*, Oslo, Norway, October 2015, pp. 1–4.

- P. Nilsson, A.U.R. Shaik, **R. Gangarajaiah**, and E. Hertz, "Hardware Implementation of the Exponential Function using Taylor Series, *IEEE NORCHIP*, Tampere, Finland, October 2014, pp. 1–4.

- M. Stala, **R. Gangarajaiah**, O. Edfors and V. Öwall, "Area and Power Reduction in DFT Based Channel Estimators for OFDM systems, *IEEE NORCHIP*, Vilnius, Lithuania, November 2013, pp. 1–4.

# Acknowledgments

First and foremost, I would like to express my sincere and deepest gratitude to Professor Peter Nilsson, Associate Professor Liang Liu, and Professor Ove Edfors for their continuous support and guidance. They accepted me as a student and I am forever thankful for their belief that I could reach this stage.

I have known Professor Peter Nilsson from my time as a master student. I will forever be indebted to him for his guidance, encouragement and invaluable feedback. It will be hard to find a better teacher and a more humble person. I feel fortunate to have had the opportunity to work with him. The way Peter interacted with students will always inspire me. His approach that no idea is unwise, and no question is foolish, has made me comprehend what it takes to be a good teacher. I will forever cherish fond memories of Peter.

Associate Professor Liang Liu has mentored me with clear direction and vision through difficult times when I felt lost. He has been instrumental in helping me understand many technical concepts, especially writing research articles. I cannot thank him enough for not getting bored of pointing out the same mistakes, and for having been so patient in helping me improve skills on all fronts. I also thank him for finding time to discuss different projects, for spending many weekends reading over reports, papers, this dissertation and providing feedback on innumerable occasions.

I started out as a student in chip design and Professor Ove Edfors introduced me to wireless communication, a fascinating field which I still find hard to understand well enough. He is always full of dazzling ideas and suggestions. I thank him for his feedback, inspiration and motivation.

I would also like to thank the seniors at the department of EIT. Associate Professor Joachim Rodrigues recommended me for the position of a PhD student, without whom I would probably not be here today. Professor Viktor Öwall, Professor Henrik Sjöland, Associate Professor Pietro Andreani and Associate Professor Erik Larsson have provided insightful comments on multiple occasions. I also thank them for giving me the opportunity to work with many talented researchers.

The past few years with the Digital ASIC group has been immensely enjoyable. Ahmed, Yang, Mojtaba, Dimitar, Farrokh, Breeta, Babak, Oskar, Xiaodong, Siyu, Hemanth, Steffen, Muris, Mohammed, Anders, Waqas, Johan, Isael, Deepak, Chenxin, Yasser, Reza and others I may have not mentioned here have helped me on numerous occasions. I would also like to thank Michal and Magnus at Mistbase for a very fruitful internship.

Many others at EIT have made life easier. Pia has helped on multiple occasions with administrative issues. Stefan, Martin, Andreas, Eric J., Joseph and Robert have assisted with lab equipment and computer issues. I would not have been in Sweden today, if not for the sacrifices made by my family. I am forever grateful to my parents and sister for supporting my choices. I will never be able to repay this debt, but I will strive to make them proud every day. Megi has been the pillar of support over the past four years. It would have been impossible to reach this stage without her unconditional love and affection. She has encouraged me at every step. I thank her for her understanding about the late hours and several work related weekends.

Many friends from India supported me during undergraduate studies and encouraged me to come to Sweden. I would like to thank them all, especially the ashrama boys and friends from Tumkur.

Sweden has welcomed me with open arms and has provided many opportunities. I would like to thank everyone who has directly and indirectly made it possible for students like me to study here. I would like to acknowledge the Swedish Foundation for Strategic Research for funding this work and Ericsson for supporting conference visits. I would also like to thank others who I may not have named here for all their help and support over the past many years.

falesh MG.

Rakesh Gangarajaiah

# List of Abbreviations

| 3GPP          | 3rd Generation Partnership Project      |

|---------------|-----------------------------------------|

| ADC           | Analog to Digital Converter             |

| ASIC          | Application Specific Integrated Circuit |

| BER           | Bit Error Rate                          |

| BS            | Base Station                            |

| BW            | Bandwidth                               |

| CA            | Carrier Aggregation                     |

| CD            | Cholesky Decomposition                  |

| CE            | Channel Estimation                      |

| CFO           | Carrier Frequency Offset                |

| CMOS          | Complementary Metal Oxide Semiconductor |

| CP            | Cyclic Prefix                           |

| CSF           | Channel Select Filter                   |

| DVFS          | Dynamic Voltage and Frequency Scaling   |

| EPA           | Extended Pedestrian A                   |

| ETU           | Extended Typical Urban                  |

| EVA           | Extended Vehicular A                    |

| EVM           | Error Vector Magnitude                  |

| FD-SOI        | Fully Depleted Silicon on Insulator     |

| FDD           | Frequency Division Duplex               |

| FFT           | Fast Fourier Transform                  |

| FIR           | Finite Impulse Response                 |

| FPGA          | Field Programmable Gate Array           |

| $\mathbf{GS}$ | Gram-Schmidt                            |

| HB            | Half Band                               |

| HHT           | Householder Transform                   |

| HLS           | High Level Synthesis                    |

| IM3           | $3^{rd}$ Order Intermodulation          |

| IQ            | In-phase and Quadrature                 |

| ISI           | Inter Symbol Interference               |

| LMS           | Least Mean Squares                         |

|---------------|--------------------------------------------|

| LNA           | Low Noise Amplifier                        |

| LS            | Least Squares                              |

| LTE           | Long Term Evolution                        |

| LTE-A         | Long Term Evolution-Advanced               |

| MF            | Matched Filtering                          |

| MGS           | Modified Gram-Schmidt                      |

| MIMO          | Multiple-Input Multiple-Output             |

| ML            | Maximum Likelihood                         |

| MMSE          | Minimum Mean Square Error                  |

| OFDM          | Orthogonal Frequency Division Multiplexing |

| PDP           | Power Delay Profile                        |

| PVT           | Process, Voltage and Temperature           |

| QAM           | Quadrature Amplitude Modulation            |

| QoS           | Quality of Service                         |

| QRD           | QR Decomposition                           |

| $\mathbf{RF}$ | Radio Frequency                            |

| SNR           | Signal to Noise Ratio                      |

| SVD           | Singular Value Decomposition               |

| TDD           | Time Division Duplex                       |

| UE            | User Equipment                             |

| $\mathbf{ZF}$ | Zero-Forcing                               |

# Introduction

### Chapter 1

### Motivation

Wireless communication systems have undergone a revolutionary change over the past few decades, transforming society and heralding an era of information exchange. New standards have emerged, and the frequency spectrum has become crowded to cater to the increasing demand for high speed data connections. The progress in Complementary Metal Oxide Semiconductor (CMOS) technology has been one of the key contributors to the growth of the wireless industry and the evolution of the smartphone. The transistor, which is the building block of semiconductor designs has shrunk in size and the number of transistors on a chip has roughly doubled every two years, following Moore's predictions closely [1]. These denser integrated circuits have facilitated the implementation of complex digital algorithms for a multitude of functions found in a modern day smartphone. This increased functionality, however, comes with the drawback of higher power consumption [2]. While this may not be an issue in devices operated with a direct power source, it is a major concern in battery operated devices. Furthermore, the wireless communication channel is highly variable due to fading effects, interference and noise sources. Regardless of the channel conditions, users desire a high Quality of Service (QoS). Traditional design methodologies with optimization of individual blocks can provide the required QoS. But, this strategy with just in-block optimizations is not efficient in terms of both silicon area and power dissipation. Therefore, a more global approach which involves cross optimization of several blocks together with local optimizations is needed to achieve energy efficiency.

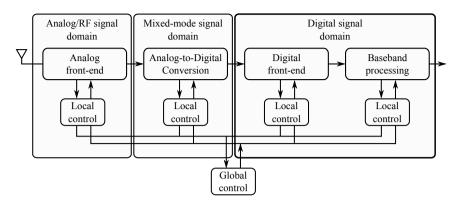

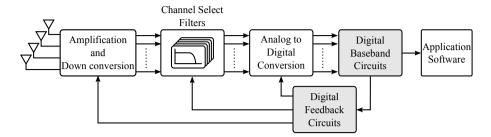

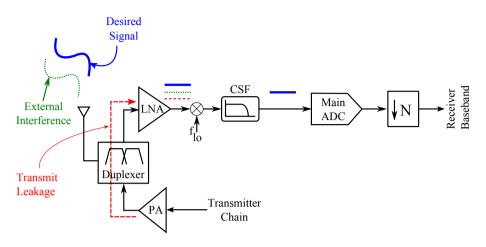

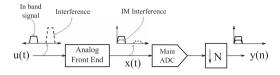

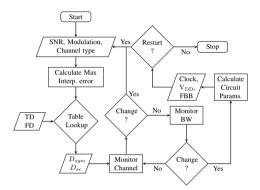

To address this, chip designers and researchers have looked at different methods of optimizing the performance of receivers with low power consumption. Figure 1.1 shows a high level block diagram of a wireless receiver. The analog front end is used to receive, amplify and filter signals transmitted from another device. Analog to digital converters transform the output of the analog front end into the digital domain where most of the processing is performed. Local feedback within the signal domains with local controllers shown in Figure 1.1 is used to optimize the performance of individual blocks. Nonetheless, to achieve the goal of high performance at low power, a more global feedback

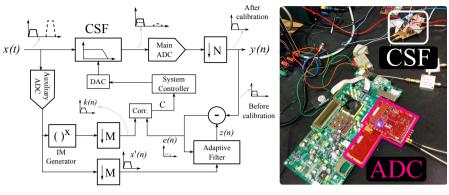

Figure 1.1: Digitally assisted radio receiver.

strategy is needed, where different blocks interact across these domains. This feedback is essential for receivers implemented with the latest CMOS technologies where the design of analog blocks has become more challenging due to increased process, voltage, temperature variations and low supply voltage headroom. On the other hand, newer CMOS technologies have immensely benefited digital circuits. The computational capability has increased tremendously, allowing complex algorithms to run on these circuits and the supply voltage reduction has lowered power dissipation. Though several design techniques are used to improve the performance of analog blocks [3-5], it has become essential to harness the digital computation power to compensate for some of the losses in the analog front end. Purely analog compensation techniques have been proposed for intermodulation mitigation [6] and fully digital compensation methods have been employed to efficiently compensate for errors such as Carrier Frequency Offset (CFO). A third method, which combines analog and digital domain solutions to tune the analog component towards optimal operation may also be used. This can be performed by monitoring the performance in the digital baseband and using a control structure similar to the one shown in Figure 1.1. The same tuning concept can also be applied to circuits in the digital baseband.

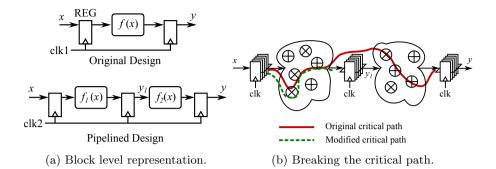

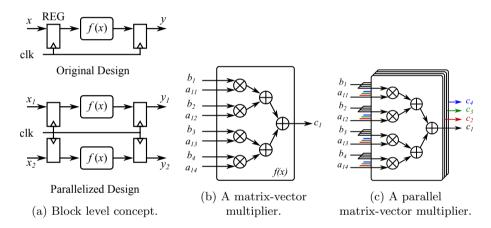

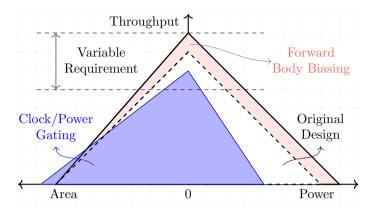

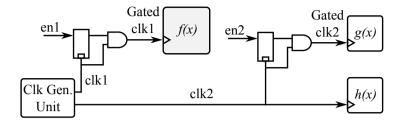

A mobile receiver operates in different channel scenarios with varying levels of interference and noise. Algorithms used to decode signals in such conditions have a significant impact on both performance and power dissipation, with higher complexity algorithms providing better performance. The inherent variability in the channel indicates that different levels of effort are required to achieve a particular QoS. Thus, local feedback of channel conditions and user requirements can be used to optimize performance of algorithms and corresponding circuits towards lower power dissipation. This can be achieved with flexible hardware architectures that allow on-the-fly switching between different algorithms at the cost of increased silicon area. Careful architectural level choices are thus required to minimize the area overhead while keeping flexibility for the adaptive tradeoff between power and performance. Together with algorithmic and architectural design choices, several circuit level modifications can be used to reduce power dissipation. Dynamic voltage and frequency scaling is a commonly used method in processors to tune performance based on run-time requirements. Multiple power domains are used in designs to drastically reduce power consumption in unused blocks. Features such as the back gate in Fully Depleted Silicon on Insulator (FD-SOI) technology, provide another degree of control to reduce static power or to dynamically increase operational frequency. An efficient implementation of a wireless receiver requires a right balance of local and global feedback together with algorithmic, architectural and circuit level optimizations. A design approach with co-optimization across these different levels is required to achieve energy efficiency and cost effectiveness.

#### 1.1 Scope of this Dissertation

The goal of this research is to improve the energy efficiency of high data rate receivers by adaptively tuning performance based on operating conditions. Cooptimization techniques are employed to achieve this goal. Namely, the exploration of strategies to combine feedback, algorithms, reconfigurable hardware architectures and corresponding circuit implementations to realize power efficient receivers for current and next generation wireless devices. Multiple-Input Multiple-Output (MIMO) communication has become the norm in high performance receivers. The driving force behind this performance is digital baseband processing which is the main topic of research.

MIMO technology enhances data rates and spectral efficiency but at the cost of higher complexity and power consumption at the receiver. Although most tasks related to MIMO are digital in nature, the interface to the outside world is still analog. High linearity is required in these analog blocks to fully extract MIMO gains in the digital baseband. Performance and power reduction are on different ends of a see-saw, where reducing one may allow higher gains in the other. This dissertation addresses the design of adaptive receivers and aims to answer the following questions:

- How can a low complexity feedback mechanism be designed to improve the performance of analog circuits?

- How can the complexity of digital baseband circuits be reduced by using information about operating conditions and QoS requirements?

- How can co-optimization be leveraged to design efficient hardware with sufficient configurability and low overhead?

- How can these concepts be applied to improve the energy efficiency of circuits in the current and next generation wireless receivers?

#### 1.2 Contributions and Outline

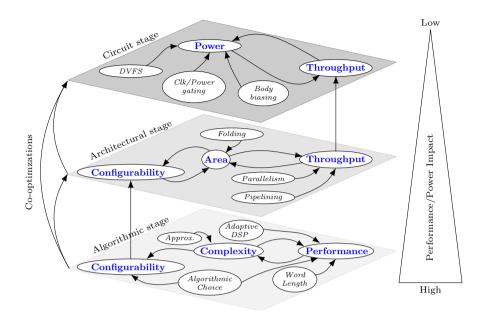

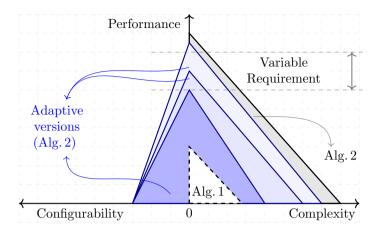

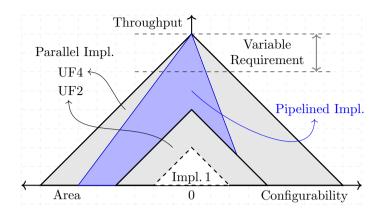

Figure 1.2 shows a design space with multiple levels of optimizations for different wireless systems (standards) and two feedback strategies. The work performed in this dissertation is mapped into this design space as highlighted. The optimization process is divided into algorithmic, architectural and circuit levels. The algorithmic design stage generally provides the highest flexibility to improve performance. The architectural level exploration is used to find efficient hardware implementations while the circuit optimizations are aimed at reducing power dissipation and improving throughput. Although energy efficiency can be enhanced by optimizing the design at each level, higher gains are obtained by combining all three levels. Two feedback strategies, digital to analog (Dig. $\rightarrow$ Ana.) and digital to digital (Dig. $\rightarrow$ Dig.) are considered.

The dissertation is divided into two sections. The first section is organized into five chapters and provides an introduction to the research field.

Chapter 1 presents the motivation and the outline of this work.

- **Chapter 2** provides an overview of baseband processing. A few methods to enhance spectrum efficiency are introduced and challenges in wireless receiver design are discussed. Properties of the channel are also examined.

- **Chapter 3** introduces techniques for reducing complexity and power consumption in different stages of a circuit design cycle.

- **Chapter 4** presents the techniques in Chapter 3 in light of three example applications. These applications are also presented in more detail in the included papers.

- **Chapter 5** summarizes the research contributions and includes a brief discussion on possible improvements and future research topics.

The second part of this dissertation includes six papers that target different standards by combining optimizations and feedback as depicted in Figure 1.2. The analog front end blocks in a radio usually have some level of reconfigurability, used to change parameters such as gains, oscillator frequencies and resolution of Analog to Digital Converters (ADCs). Some implementations also include controls to reduce distortion and improve linearity. A system which detects non-linearities of analog circuits in the digital domain and provides Digital $\rightarrow$ Analog feedback is presented in **Paper I**. The non-linearity

Figure 1.2: Dissertation contribution mapping.

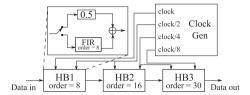

tuning system proposed in Paper I is optimized, implemented in a Field Programmable Gate Array (FPGA) and tested by interfacing a tunable analog filter. These results are presented in **Paper II**.

In the entirely digital feedback domain, baseband circuits used in MIMO systems are optimized for energy efficiency. Small scale MIMO systems such as the ones in the Long Term Evolution-Advanced standard [7,8] rely on non-linear signal detectors to fully realize spatial multiplexing gains. The QR Decomposition (QRD) channel preprocessor is often used to ease the implementation of these detectors. A high speed QRD processor capable of decoding wideband signals is presented in **Paper III**. To reduce the computation count of QRD in Carrier Aggregation (CA) scenarios, an adaptive strategy which exploits channel conditions is proposed in **Paper IV**. A design which incorporates this adaptive approach with Digital→Digital feedback is optimized on the architectural and circuit level. The design is fabricated in 28 nm CMOS and measurement results are presented to highlight the advantages of co-optimization in **Paper** V. These concepts are extended to the next generation of communication systems based on massive MIMO [9]. An adaptive uplink detector with hybrid detection that combines two algorithms to reduce complexity is presented in **Paper VI**. Several architecture level techniques are combined with algorithmic optimizations to result in an energy efficient, high throughput signal detector for massive MIMO base stations.

#### Notation

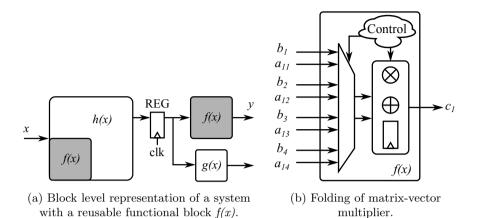

The following notations will be used throughout this dissertation. Non-bold letters, e.g. a, or  $\alpha$ , will be used for scalars. Bold-upper case letters, e.g.  $\boldsymbol{A}$  will be used for matrices and bold lower case letters, e.g.  $\boldsymbol{a}$  will be used for column vectors. The Hermitian conjugate is  $(\cdot)^H$ . The transpose of a matrix or a vector is denoted by the  $(\cdot)^T$  operator, and the complex conjugate is denoted by  $(\cdot)^*$ . Numbered subscripts are used for column vectors in a matrix, e.g.  $\boldsymbol{a}_1$  refers to the first column of a matrix  $\boldsymbol{A}$ . Two subscripts are used when referring to a single element of a matrix, e.g.  $\boldsymbol{a}_{14}$  is the element on the first row of the fourth column of a matrix  $\boldsymbol{A}$ .

### Chapter 2

### **Digital Baseband Processing**

This chapter begins by presenting methods to achieve high data rates with good reliability in communication links between a Base Station (BS) and a mobile User Equipment (UE). The effects of the wireless channel on data reception are examined, and methods for increasing the resilience of communication links to channel fading while improving spectral efficiency are presented. Later, the building blocks of a typical wireless receiver are introduced with a focus on the tasks performed in the digital baseband. A brief introduction to properties of wireless channels and challenges in system design for cellular standards are presented. Finally, the need for adaptive processing and techniques exploiting channel properties in order to achieve energy efficiency are discussed. The following chapter will present optimizations of algorithms and hardware implementation details for a few key blocks presented in this chapter.

#### 2.1 Introduction

The demand for cellular data has increased exponentially in the past few years and is expected to reach around 50 Exabytes/month by the end of this decade [10]. Increasing communication bandwidth is one of the ways to increase capacity, but the price/Hz for sub-6 GHz frequencies have reached exorbitant numbers, a recent auction fetching \$45 billion for 65 MHz of spectrum [11]. Thus, spectral efficiency has become critical, which has spurred researchers into finding methods to maximize the data rate while serving an increasing number of users in a cellular network. Time and frequency multiplexing allows the BS to share a limited spectrum with multiple users, and spatial multiplexing with multiple antennas is used to increase communication link capacity. However, advanced signal processing algorithms are required at the receiver to decode data and to obtain the high data rates promised by these methods. The additional performance gains from these algorithms come at the cost of increased power dissipation, which is a major concern in mobile devices operating on limited battery energy. Thus, the design of wireless receivers optimized for energy efficiency has been at the forefront of research for several years.

Today's smartphones can communicate using different wireless standards, for example, Bluetooth, Wi-Fi, 3G, more recently 4G or Long Term Evolution-Advanced (LTE-A), and the next generation of 5G devices are just around the corner. These mobile devices operate in cellular systems, where a BS transmits and receives data from multiple devices simultaneously. The signals transmitted from the BS are scattered by objects in the environment such as trees and buildings before reaching the UEs. Thus, the signals arrive at the UE through multiple paths, each with a different delay and attenuation. These multi-path components vary over time, resulting in a time varying frequency selective channel, causing small scale fading at the UE. Additionally, the movement of the UEs and scatterers in the environment results in shadow fading. The received signal also experiences a path loss in proportion to the distance between the BS and UEs [12]. Furthermore, many network operators and mobile devices may communicate with different standards in nearby frequencies, causing interference. Nonetheless, mobile receivers are expected to operate even with very low received signal power, in the range of  $-95 \,\mathrm{dBm}$  for LTE-A compliant devices [13]. Techniques such as increasing transmit power, data pre-coding, choosing between modulation alphabets, spread spectrum signaling [12], channel coding with interleaving [14] and diversity schemes [15] have been introduced to increase the reliability and capacity of communication links between the BS and UEs.

#### 2.1.1 Wireless Access Technologies

The received signal power and the communication Bandwidth (BW) govern the capacity of the communication link, or the data rate at which information can be reliably exchanged. The Shannon-Hartley theorem defines an upper limit on this data rate in an additive white-noise Gaussian channel. This rate C, can be computed by

$$C = BW \times \log_2\left(1 + \frac{S}{N}\right),\tag{2.1}$$

where BW is the bandwidth measured in Hz, S is the signal power and N is the noise power. Thus, capacity can be increased by either using more bandwidth or increasing the signal power. The latter provides limited gains due to its logarithmic dependency. Furthermore, the power transmitted from the BS has to satisfy regulatory limits and also has practical limitations. Hence, increasing BW has been the preferred choice in the cellular standardization process. A BW of 200 kHz was used in earlier 2G systems, which has now increased to 100 MHz in 4G systems. Though a theoretically linear increase in channel capacity can be obtained by increasing BW, the Bit Error Rate (BER) performance, which determines the reliability of the link, is dependent on channel properties such as fading and interference from external sources. Strong interference cause problems in the Radio Frequency (RF) front end circuits in the receiver, and

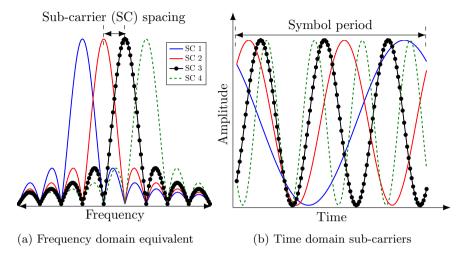

Figure 2.1: OFDM signaling.

thus require careful design for linearity. Fading can be effectively handled in the digital baseband and some methods of reducing fading effects are presented below.

#### **Orthogonal Frequency Division Multiplexing**

Multi-path propagation of signals with different delays causes frequency selective fading. Additionally, the mobility of the UEs results in a time varying frequency selectivity. The Orthogonal Frequency Division Multiplexing (OFDM) technique makes it easier to equalize these fading effects and has been adopted in many wireless standards. It operates by dividing the communication BW into multiple bands called sub-carriers, each with a much smaller BW. The division is performed by examining channels properties and the sub-carriers BWs are chosen so that the channel's frequency selectivity is invisible over any given sub-carrier. More importantly, the sub-carriers are tightly spaced as shown in Figure 2.1(a) and are orthogonal in both time and frequency. Figure 2.1(b) depicts the time domain equivalent of the four sub-carriers, each with an increasing frequency. The OFDM symbol period is chosen to include an integer number of component sub-carriers cycles. However, a Cyclic Prefix (CP) is often necessary when operating in multi-path wireless channels, which increases the length of the symbol.

UEs in a cell experience different levels of selectivity and fading due to their distributed nature and dissimilar mobility. This may result in situations where some UEs have a good channel at a frequency where other UEs do not. The BS may exploit this phenomenon when using OFDM to distribute the

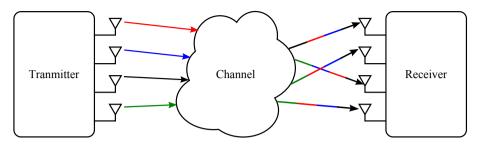

Figure 2.2: Multiple antenna communication.

full communication BW among multiple UEs with a goal of maximizing the Signal to Noise Ratio (SNR) at each receiver [12]. Each sub-carrier can also be individually modulated with a different alphabet, allowing the transmitter to increase spectral efficiency with higher order modulation alphabets such as 64-Quadrature Amplitude Modulation (QAM) or 256-QAM [16]. From a hardware perspective, OFDM can be implemented efficiently with the Fast Fourier Transform (FFT) algorithm, and its corresponding butterfly structures provide a simple way to divide the communication BW among several users.

Notwithstanding these advantages, practical utilization of OFDM modulation has an overhead in the form of a CP which is needed to avoid inter symbol interference in multi-path channels. Accurate timing and carrier synchronization are also needed, requiring analog calibration and digital compensation to maintain orthogonality between the digitized sub-carriers. Furthermore, the peak to average ratio of OFDM signaling is high, requiring more than a few dBs of back-off in power amplifiers during transmission [14]. Though tight spacing of the sub-carriers increases spectral efficiency, 10% - 40% of the BW is not used for data transmission to minimize adjacent channel leakage. Nevertheless, OFDM has been widely adopted in several standards such as 802.11 ac high speed Wi-Fi, LTE-A and is also considered for the next generation cellular communication.

#### Multiple Antenna Communication

Although the amount of BW allocated for cellular communication has increased, the number of subscribers for mobile connectivity has grown at an even faster rate. Resource scheduling with frequency and time multiplexing are two techniques used by network operators to share a limited BW among multiple users. The BS can use feedback on channel conditions to schedule downlink data transmissions, with the goal of maximizing the data rates and QoS offered to users. The spatial domain offers a third alternative to increase data rates and link reliability, and is exploited by using multiple antennas at the BS and the UE [17]. These antennas can be used to either increase the SNR with diversity techniques or to create multiple communication streams. Figure 2.2 depicts such a spatial multiplexing system which has four antennas at both transmitter and receiver. A MIMO system with N transmitter and Mreceiver antennas may be represented in the baseband by

$$\boldsymbol{y} = \boldsymbol{H}\boldsymbol{x} + \boldsymbol{n}, \tag{2.2}$$

where  $\mathbf{y} = [y_1, y_2, ..., y_M]^T$  is the received data vector,  $\mathbf{H} \in \mathbb{C}^{M \times N}$  is the complex numbered channel gain matrix and  $\mathbf{x} = [x_1, x_2, ..., x_N]^T$  is the baseband equivalent of the transmitted signal. All other sources of interference and noise are modeled by the vector  $\mathbf{n}$ . The receiver estimates the effects of the channel by the use of predefined reference signals sent from the transmitter at regular intervals and informs the BS on the channel conditions during uplink data transfer. Based on this feedback, the BS adapts the communication link by methods such as pre-coding to cancel some of the channel effects, changing modulation format or switching between diversity schemes to improve SNR. In good channel conditions such as when  $\mathbf{H}$  in (2.2) is full rank with a low condition number and SNR at the receiver is high, parallel data communication with multiple streams can take place between BS and UE. On the other hand, diversity schemes may be employed in scenarios when the UE experiences low SNR due to deep fading [15].

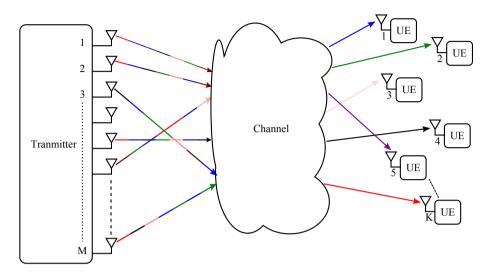

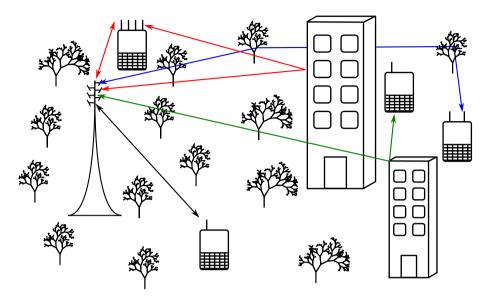

#### Massive MIMO

The communication link quality can be improved by increasing the number of antennas at either the transmitter, the receiver or at both ends. However, increasing the number of antennas at the BS is easier due to factors such as the availability of a direct source of power and physical space. Furthermore, FPGAs and digital signal processors can be used to implement baseband algorithms instead of Application Specific Integrated Circuits (ASICs) as hardware efficiency and power consumption are not as great a concern as in a UE. Massive MIMO systems are based on this concept and typically employ around 100 or more BS antennas to serve 10 to 20 active users [18, 19]. Such a system is shown in Figure 2.3 where M antennas at the BS communicate with K single antenna UEs. A large number of antennas at the BS provide high spatial resolution which may be used to accurately precode transmit signals. This precoding may be chosen to equalize channel effects and minimize interference, thus simplifying baseband processing on the battery operated UEs. The high spatial resolution also enables the full BW to be simultaneously assigned to multiple users, increasing system capacity. Small scale fading, which degrades the performance in small scale MIMO systems such as the ones in Figure 2.2, can be reduced significantly with simple signal processing. The transmit power from each of the antennas at the BS can also be reduced to the order of milli-

Figure 2.3: A massive MIMO system with M antennas at the BS and K single antenna UEs.

Watts [18], compared to the power in the range of tens of Watts in currently deployed BSs [20]. Moreover, the robustness of the BS is increased as the impact of failure from a few transceivers is limited. The massive MIMO system can also be represented by (2.2), with  $\mathbf{H} \in \mathbb{C}^{M \times K}$  and an additional constraint of M >> K, where M is the number of antennas at the BS and K is the single antenna UE count. Furthermore, linear pre-coding and detection schemes can be used in massive MIMO systems as the number of BS antennas are typically much larger than the number of users.

Although massive MIMO brings several advantages; it comes with its fair share of challenges. The data processing required at the BS increases due to a large number of radios. A central processing unit is needed to combine this data and process it in a timely fashion. Even though linear detection algorithms provide good performance, the dimension of the channel matrix  $\boldsymbol{H}$  presents implementation challenges concerning processing latency and silicon area. Accurate channel estimation is another problem. Time Division Duplex (TDD) mode is often employed in massive MIMO systems and pilot symbols from the UEs may be used to simplify channel estimation. However, this may limit the number of users that can be simultaneously served and lead to interference and pilot contamination between nearby cells [9]. The quality of downlink pre-coding is directly dependent on the estimation accuracy, and reciprocity calibration is needed in TDD systems [21]. Notwithstanding these challenges, massive MIMO has shown promising results and is thus one of the leading candidates for the 5G communication era [22].

Figure 2.4: Structure of a multi-antenna wireless receiver.

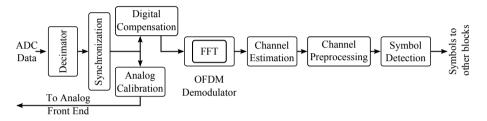

Figure 2.5: Digital baseband blocks in a MIMO-OFDM receiver.

#### 2.2 The Digital Baseband

MIMO and OFDM presented in the previous subsection are two methods to improve communication capacity and reliability. A practical implementation of these techniques in low power mobile radios needs efficient hardware architectures to maximize energy efficiency. A simplified block diagram of a wireless receiver capable of using MIMO and OFDM is shown in Figure 2.4. The RF signals transmitted from a BS are collected by multiple antennas at the receiver, which are amplified and down converted to baseband frequencies with Low Noise Amplifiers (LNAs) and mixers. Analog Channel Select Filters (CSFs) remove interference close to the baseband and the ADCs digitize the filtered signal. These samples are processed by the digital baseband circuits where further filtering, equalization and signal detection are performed before the data is used by the application software. The digital baseband also detects, calibrates and compensates for imperfections in the analog front end. Figure 2.5 shows a more detailed view of the digital blocks. The ADCs often oversample the signals which are further filtered and converted to the baseband rate with decimators. Synchronization is used to lock the UE to the BS followed by detection of residual timing and frequency offsets. The analog calibration block provides feedback to the components such as mixers to adjust carrier frequencies if needed, or tunes the performance of blocks such as LNAs, CSFs and ADCs. The digital compensation block improves the signal quality by performing tasks such as CFO and In-phase and Quadrature (IQ) imbalance removal. The OFDM demodulator implemented with FFTs, converts the signal into its frequency domain equivalent. The Channel Estimation (CE) unit detects the effects of the multi-path channel and feeds data to the channel preprocessor. The received signals and the data from the preprocessor are used for symbol detection followed by decoding. The combined goal of the digital baseband blocks is to use information such as the estimates of channel gains, modulation format and SNR to decode signals from the analog front end into a stream of bits (symbols). The performance of the receiver while achieving this goal may be measured by using metrics such as the Bit Error Rate (BER), which indicates the average number of bits incorrectly detected in a long stream of data bits. This dissertation adopts BER as one of the metrics to evaluate the performance of baseband algorithms and corresponding hardware solutions in different operating conditions. The next few subsections describe the functionality of the blocks in the MIMO-OFDM receiver in Figure 2.5 in more detail. Some common problems in these receivers and corresponding algorithmic implementations to mitigate their effects to reduce BER are also discussed.

#### 2.2.1 Digital Front End

The digital front end performs tasks such as compensation and calibration of analog blocks, sample rate conversion and synchronization on each stream of data from the multiple receiver chains in a MIMO system.

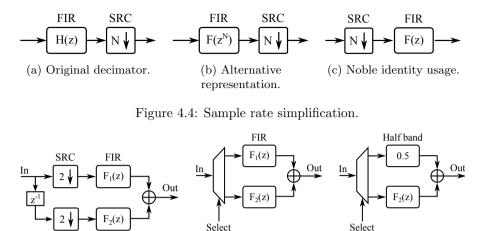

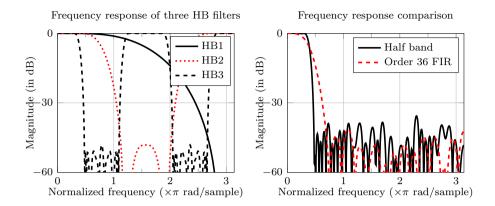

#### Decimation

The ADC is the interface between the analog signals and the digital baseband circuits. Different implementations of ADCs are available, and oversampling is often employed to reduce inband noise and enhance resolution.  $\Delta\Sigma$  ADCs are one such implementation that provide high resolution with low power consumption [23]. These ADCs require filters to remove out-of-band noise and sample rate converters to match the output rate to the baseband rate. Oversampling may also be used to relax decimation filter requirements and to improve timing synchronization in the baseband [24]. Furthermore, multi-mode cellular devices capable of decoding signals from different wireless standards also require sample rate converters. The filtering process and the sample rate conversion is usually combined into the decimation process [25]. Finite Impulse Response (FIR) configurations are popular due to their simple architecture and half band FIR filter implementations are used to reduce cost [26]. These filters are implemented to provide configurable output rates, to match different BWs and sample rates of corresponding standards depending on the receiver settings [27]. The decimated data is used by the synchronization block to find the reference carrier frequency and OFDM symbol timing.

Figure 2.6: Effects of timing errors.

#### Synchronization

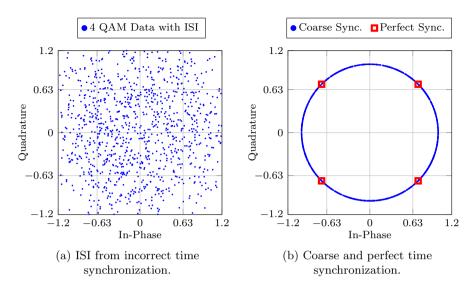

Wireless receivers do not share a common reference with the BS and hence require both timing and frequency synchronization (Sync.). Additionally, OFDM systems rely on maintaining the orthogonality of sub-carriers. To ease the synchronization process, OFDM systems organize data transmission into structures called frames or packets by combining several data symbols and insert special reference or training symbols at regular intervals [28]. The UE may perform timing synchronization using these reference signals in two steps. First, coarse frame synchronization is done to get a rough estimate of the starting sample of a frame [29, 30]. Next, accurate symbol start may be obtained to find the first sample in the OFDM symbol with the cyclic prefix [24]. However, fine synchronization may be hard to accomplish in the presence of noise and interference. Methods such as scheduling the inputs to the FFT unit in the right order can be used to improve the result after coarse synchronization is achieved.

The effects of incorrect timing synchronization are shown in Figure 2.6(a), where Inter Symbol Interference (ISI) causes a complete breakdown of communication. Figure 2.6(b) shows the constellation diagram with coarse synchronization, where the ISI is completely removed and also fine synchronization which results in an ideal 4-QAM constellation.

The second type of synchronization required is between the carrier frequencies of the BS and the UE. The local oscillator at the UE needs to feed the mixers with the same carrier frequency as used by the BS to upconvert the baseband transmit signals. Good carrier synchronization is required to avoid inter-carrier interference, and the next subsection presents the effects of Carrier Frequency Offset (CFO) and a method to mitigate its effect.

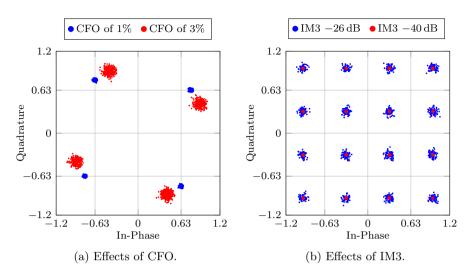

#### **Digital Compensation and Analog Calibration**

Designers have invented many techniques to improve the performance of components in the analog front end. But Process, Voltage and Temperature (PVT) variations, which cannot be completely controlled at design time, affect linearity and precision. Thus, these variations must be compensated for, either with analog techniques [4, 31, 32] or in the digital domain [33, 34]. Digital implementations are more robust to PVT variations due to the on-off nature of digital circuits. As an example of digital compensation, consider the problem of inter-carrier interference due to CFO. Coherent detection, used in a majority of modern wireless communication systems relies on the capability of the receiver's oscillators to lock to the transmitter's carrier frequency. However, a perfect lock is not always achieved and CFO values of around 0.1 ppm are accepted in communication standards such as LTE-A [13]. CFO causes intercarrier interference in OFDM systems and Figure 2.7(a) shows the effect of 150 Hz and 500 Hz offsets, corresponding to 1% and 3% of the sub-carrier spacing in LTE-A, respectively [13]. There are mainly two methods of compensating for such problems due to analog imperfections in the digital domain.

The **first** method uses the computation power of digital circuits to cancel the non-linearities in the baseband and algorithms with their corresponding hardware implementations have been proposed in literature to detect and mitigate the effects [35,36]. One of the choices is the use of a digital compensation block, such as the one in Figure 2.5. For example, fractional CFO value of  $+\Delta f$ , which is less than half the sub-carrier spacing in an OFDM system may be canceled by multiplying the time domain samples by a complex sinusoid as

$$y(n)_{\text{cfo_fixed}} = y(n) \times e^{\frac{-j2\pi\Delta fn}{F_s}}, \forall n \in \{0, 1, 2\cdots\} \mod BL,$$

$$BL = \frac{F_s}{\Delta f},$$

(2.3)

where  $F_s$  is the baseband sample rate and BL is the block repetition length. Similarly IQ imbalance from mixers may be canceled in the digital domain by estimating the amplitude and phase imbalance [36].

The simplified baseband model of a MIMO system in (2.2) assumes linearity of the wireless channel which is valid for all practical cellular communication systems. Additionally, the model also relies on the linearity of the analog front end which is difficult to achieve in all conditions, especially under PVT variations. Non-linearities create intermodulation, increasing interference in

Figure 2.7: Effects of analog imperfections.

the baseband, and can be modeled by

$$\boldsymbol{y}_{ant} = \boldsymbol{H}\boldsymbol{x} + \boldsymbol{n},$$

$$\boldsymbol{y} = \begin{bmatrix} Gy_{ant1} + \alpha y_{ant1}^2 + \beta y_{ant1}^3 + \cdots \\ \cdots \\ Gy_{antM} + \alpha y_{antM}^2 + \beta y_{antM}^3 + \cdots \end{bmatrix} + \boldsymbol{n},$$

(2.4)

where  $\boldsymbol{y}$  is the baseband signal similar to (2.2),  $y_{ant1}$  is the baseband equivalent of the signal at the receiver antenna 1,  $y_{antM}$  is the baseband equivalent of the signal at the receiver antenna M. The combined linear gain of the analog front end is denoted by G. The scaling factors for the second and third order non-linearity components  $y_{ant}^2$  and  $y_{ant}^3$  are  $\alpha$  and  $\beta$  respectively. In practical receivers, the values of  $\alpha$  and  $\beta$  are much lower than G. Nonetheless, if the signal  $y_{ant}$  contains frequency components  $f_1$  and  $f_2$ , intermodulation between these frequencies results in components at

$$(f_1 - f_2), (f_1 + f_2), (2f_1 - f_2), (2f_1 - f_2), (2f_2 - f_1), (2f_2 + f_1), \cdots$$

(2.5)

The second order intermodulation terms  $(f_1 - f_2), (f_1 + f_2)$  are reduced to the level of device mismatch by using differential signaling in the analog front end. In the presence of strong interference, the third order intermodulation may affect receiver sensitivity and corrupt the signals of interest. Figure 2.7(b) shows the effects of  $3^{rd}$  Order Intermodulation (IM3) distortion on the baseband signal. Another important metric for receiver performance in addition to BER is the Error Vector Magnitude (EVM). IM3 distortion with a power 26 dB lower than the baseband signal results in an EVM of around 5%. The maximum allowed EVM is dependent on the signaling constellation and 4G systems require the combined EVM of the analog front end to be lower than 8% for 64-QAM modulation [37]. Additional phase noise from the oscillators [38], IQ imbalance in the mixers, sample clock offsets in the ADCs will further increase EVM. The variable nature of these non-linearities and dependence on external factors such as interference signals, requires frequent monitoring and calibration to ensure signal fidelity.

The **second** approach of mitigating these non-linearites, in contrast to the first completely digital compensation technique, relies on detection and tuning the RF components towards higher linearity. This approach may be more power efficient as the digital circuits associated with tuning can be switched off once the desired level of performance is achieved.

#### **OFDM** Demodulator

The data from the digital compensation block in Figure 2.5 is processed by the OFDM demodulator. One of the key benefits of using OFDM is its low complexity FFT based implementation. Several efficient algorithms with different radices have been proposed with the radix-2 and radix-4 adopted in many hardware implementations [39]. Mixed radices may also be beneficial in some scenarios [40, 41]. The OFDM demodulator block converts the time domain signals into their frequency domain equivalents to be used by the following channel estimators and symbol detectors. For MIMO systems, one FFT unit is used for each antenna port of the receiver.

#### 2.2.2 Channel Estimation

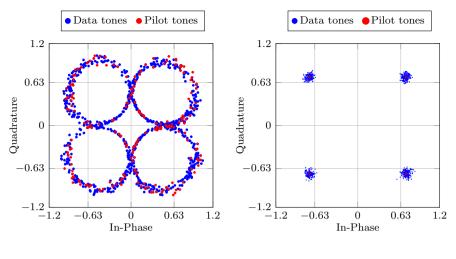

The signal at receiver antennas is a modified and combined version of the transmitted signals as depicted in Figure 2.2. The effects of the wireless channel on the transmitted data have to be estimated before they can be equalized. The CE block in the baseband performs this task with the help of reference symbols and tones transmitted by the BS at different frequencies and time instants. Though the addition of reference signals reduces resources available to transmit data, a certain minimum number of pilots are essential to detect frequency selectivity and time variations in the channel. Figure 2.8(a) shows 4-QAM data received through such a frequency selective channel. The pilot tones interspersed with data tones, are compared against a set of reference values to estimate the effects of the channel. These estimates are then used for equalization resulting in the constellation shown in Figure 2.8(b). It is evident from Figure 2.8 that accurate CE is necessary to recover data. Several implementations with varying complexity based on the Singular Value Decomposition (SVD) [42], the Minimum Mean Square Error (MMSE), the Least

(a) Received data @ SNR = 25 dB.

(b) Data equalized with Least Squares (LS) estimates.

Figure 2.8: Effects of frequency selective channel.

Squares (LS) criterion [12, 43], and matching pursuit algorithms [41, 44] have been proposed. The UE may use the CE data to provide feedback to the BS for changing parameters such as BW, modulation and spatial multiplexing order.

#### 2.2.3 Channel Matrix Preprocessing

The data from the CE unit is used by the symbol detector to equalize channel effects and to decouple the spatial streams in MIMO systems. A channel preprocessing unit is employed to re-format the data from the CE unit to ease the implementation of these symbol detectors. This preprocessing usually involves matrix decompositions, the results of which may also be used in the precoding process for downlink transmission in massive MIMO systems. One of the methods proposed in [45] uses an SVD preprocessor to convert the channel matrix into a product of two unitary and a diagonal matrix. Another preprocessor based on QRD converts the input matrix into a product of a unitary and an upper triangular matrix. LU decomposition may be used to solve equations of linear systems similar to Gaussian elimination [46]. Massive MIMO systems may use approximate matrix inversions instead of direct matrix inversions [47] to reduce hardware cost and speed up the detection process. Cholesky Decomposition (CD), LDL decomposition [48] and Eigenvalue decomposition are other methods which can also be used in massive MIMO systems. In this dissertation, two of these preprocessing operations, namely the QRD and the CD are considered.

#### **QR** Decomposition

A matrix may be decomposed into a unique product of an orthonormal matrix Q and an upper triangular matrix R (upto their signs). The channel estimates H in (2.2) is in most cases non-singular and hence, the QRD process may be used. Consider an estimate H in a 4 × 4 MIMO system

$$\boldsymbol{H} = \begin{bmatrix} h_{11} & h_{12} & h_{13} & h_{14} \\ h_{21} & h_{22} & h_{23} & h_{24} \\ h_{31} & h_{32} & h_{33} & h_{34} \\ h_{41} & h_{42} & h_{43} & h_{44} \end{bmatrix}.$$

(2.6)

The QRD of this matrix yields

$$\boldsymbol{H} = \boldsymbol{Q}\boldsymbol{R},$$

$$\boldsymbol{H} = \begin{bmatrix} q_{11} & q_{12} & q_{13} & q_{14} \\ q_{21} & q_{22} & q_{23} & q_{24} \\ q_{31} & q_{32} & q_{33} & q_{34} \\ q_{41} & q_{42} & q_{43} & q_{44} \end{bmatrix} \begin{bmatrix} r_{11} & r_{12} & r_{13} & r_{14} \\ 0 & r_{22} & r_{23} & r_{24} \\ 0 & 0 & r_{33} & r_{34} \\ 0 & 0 & 0 & r_{44} \end{bmatrix}.$$

$$(2.7)$$

The matrix  $\boldsymbol{Q}$  is unitary, i.e.,  $\boldsymbol{Q}^{H}\boldsymbol{Q} = \boldsymbol{I}$ , where  $\boldsymbol{I}$  is the identity matrix and  $\boldsymbol{R}$  is upper triangular with real entries on the diagonal. Algorithms used for QRD can be classified into two broad categories. The first category orthonormalizes the  $\boldsymbol{H}$  matrix by a series of right multiplications with upper triangular matrices. An example of this triangular orthogonalization category is the Gram-Schmidt (GS) process. The second category, classified under orthogonal triangularization, convert  $\boldsymbol{H}$  into an upper triangular matrix by a series of left multiplications with orthonormal matrices [46]. The Householder Transform (HHT) and Given's rotations fall into this category. These two sets of algorithms can be mathematically described as

Triangular Orthogonalization  $\rightarrow Q = HR_1R_2\cdots R_N$ , and  $Q_M\cdots Q_2Q_1H = R \rightarrow \text{Orthogonal triangularization},$

where  $\mathbf{R}_1, \mathbf{R}_2, \cdots, \mathbf{R}_N$ , are upper triangular matrices and  $\mathbf{Q}_1, \mathbf{Q}_2, \cdots, \mathbf{Q}_M$  are unitary matrices.

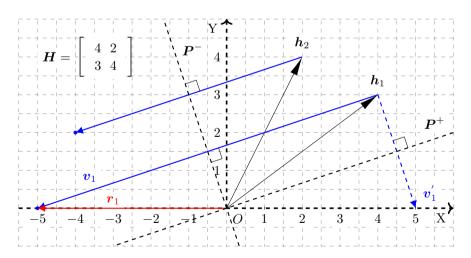

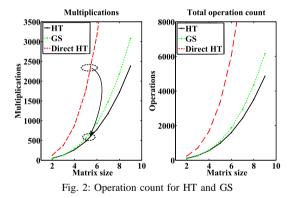

Algorithm 1 lists the GS process, and a pictorial representation of the GS algorithm on a  $2 \times 2$  matrix is presented in Figure 2.9. The process starts by using the first column vector  $\boldsymbol{h}_1$ , of the input  $\boldsymbol{H}$  matrix as the starting reference, and  $\boldsymbol{q}_1$  is obtained by normalizing the length of  $\boldsymbol{h}_1$ . The projection of  $\boldsymbol{h}_2$  in the direction of  $\boldsymbol{q}_1$ ,  $(\boldsymbol{h}_2^H \boldsymbol{q}_1) \boldsymbol{q}_1$  is then subtracted from  $\boldsymbol{h}_2$ , resulting in a vector orthogonal to  $\boldsymbol{q}_1$ . The second orthonormal vector  $\boldsymbol{q}_2$  is obtained by normalizing this result. The full  $\boldsymbol{Q}$  matrix is constructed by using the individual vectors  $\boldsymbol{q}_1, \boldsymbol{q}_2, \dots \boldsymbol{q}_N$ . Although the algorithm is straightforward to

Figure 2.9: Gram-Schmidt orthogonalization process.

implement in hardware, the GS process suffers from instabilities in fixed point implementations and an alternative version of the algorithm called the Modified Gram-Schmidt (MGS) is used to improve stability [46]. The complexity of algorithms are often measured by the number of multiplication operations and total multiplication count for the GS algorithms for an  $M \times N$  matrix is obtained by

$$\sum_{j=1}^{N} \left( \sum_{i=1}^{j-1} 2M \right) + 2M = MN^2 + MN.$$

(2.8)

The complexity is in the order of  $\mathcal{O}(M^3)$  for full rank square matrices of size  $M \times M$ .

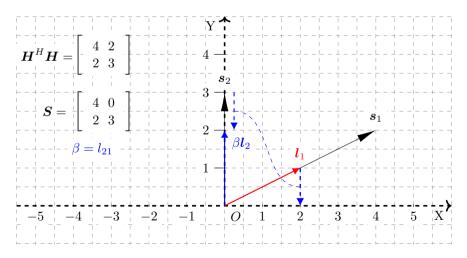

On the other hand, the HHT operates by using reflections, and an implementation of the HHT is shown in Algorithm 2. The pictorial representation of the HHT for the same example matrix as used for the GS process is shown in Figure 2.10. The transform starts by operating on the first column  $h_1$ , similar to the GS process. However, instead of normalizing this vector to produce  $q_1$ , the HHT reflects the vector  $h_1$  onto the X-axis to produce  $r_1$ . This is achieved by left multiplying  $h_1$  with the reflection matrix of the form

$$\boldsymbol{Q} = \left( \boldsymbol{I} - 2\frac{\boldsymbol{v}\boldsymbol{v}^{\boldsymbol{H}}}{\boldsymbol{v}^{\boldsymbol{H}}\boldsymbol{v}} \right), \qquad (2.9)$$

where v is a vector orthogonal to the reflection plane. There are two such possible reflection planes, the edges of which are marked by  $P^+$  and  $P^-$ . These planes can be visualized as being perpendicular to the page on which Figure 2.10 is printed, but placed along the dashed lines marked by  $P^+$  and  $P^-$ . The HHT picks the plane which is farthest from the vector being reflected, resulting in improved resilience to rounding errors in fixed point hardware. The reflection matrix is applied on all subsequent columns of the input matrix, resulting in reflected vectors as shown in Figure 2.10. For the next iteration, the matrix is deflated by removing the first column and row of the modified H matrix and the reflection procedure is repeated. It can be noticed from Algorithm 2 that the HHT operates on vectors with decreasing size as j increases from 1 to Nand the computational complexity is obtained by

$$\sum_{j=1}^{N} \left( \sum_{k=j}^{N} 2c + 2c \right) \approx MN^2 - \frac{N^3}{3},$$

(2.10)

where c is defined as (M + 1 - j). The complexity of the HHT algorithm is also in the order of  $\mathcal{O}(M^3)$  for full rank square matrices. Although the complexity is lower than the GS process, it has to be noted that the Q matrix is not explicitly computed in the HHT algorithm.

**Algorithm 2** Householder Transform based QRD for  $M \times N$  matrix.

| 1: procedure HOUSEHOLDER( $H$ ) $\triangleright$ Mult                                                                                                               | tiplications |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| 2: $\triangleright$ Intialize $V$ to identity matrix                                                                                                                |              |  |  |  |  |

| 3: $V \leftarrow I$                                                                                                                                                 |              |  |  |  |  |

| 4: $\triangleright$ Start decomposition                                                                                                                             |              |  |  |  |  |

| 5: for $j = 1$ to $N$ do                                                                                                                                            |              |  |  |  |  |

| $6: \qquad c \leftarrow M + 1 - j$                                                                                                                                  |              |  |  |  |  |

| 7: $oldsymbol{x} \leftarrow oldsymbol{H}_{j:M,j}$                                                                                                                   |              |  |  |  |  |

| 8: $oldsymbol{e} \leftarrow oldsymbol{I}_{j:M,j}$                                                                                                                   |              |  |  |  |  |

| 9: $\boldsymbol{v} \leftarrow sign(x_1) \  \boldsymbol{x} \ _2 \boldsymbol{e} + \boldsymbol{x} \qquad \triangleright c$                                             |              |  |  |  |  |

| 10: $r \leftarrow 2/(\boldsymbol{v}^H \boldsymbol{v})$ $\triangleright c$                                                                                           |              |  |  |  |  |

| 11: <b>for</b> $k = j$ <b>to</b> $N$ <b>do</b>                                                                                                                      |              |  |  |  |  |

| 12: $\boldsymbol{H}_{j:M,k} \leftarrow \boldsymbol{H}_{j:M,k} - r\boldsymbol{v}\left(\boldsymbol{v}^{H}\boldsymbol{H}_{j:M,k}\right) \qquad \triangleright \ c + c$ | ?            |  |  |  |  |

| 13: end for                                                                                                                                                         |              |  |  |  |  |

| 14: $oldsymbol{V}_j \leftarrow oldsymbol{v}$                                                                                                                        |              |  |  |  |  |

| 15: <b>end for</b>                                                                                                                                                  |              |  |  |  |  |

| 16: return $\boldsymbol{V}, \boldsymbol{H}$                                                                                                                         |              |  |  |  |  |

| 17: end procedure                                                                                                                                                   |              |  |  |  |  |

Figure 2.10: The first Householder reflection.

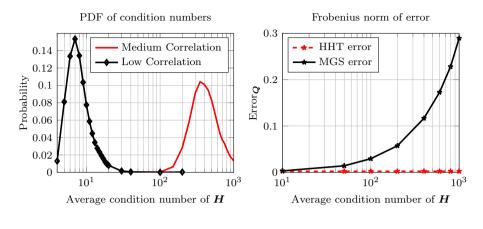

#### **Cholesky Decomposition**

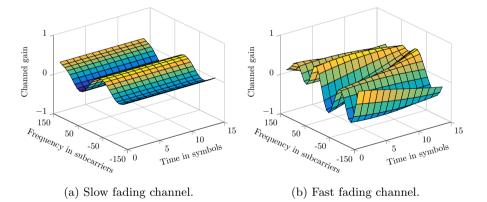

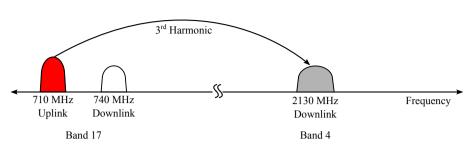

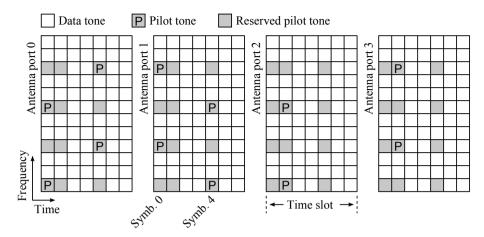

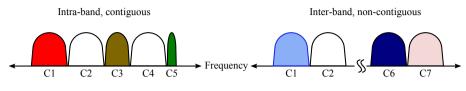

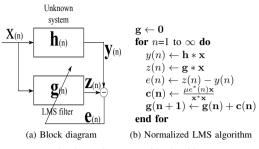

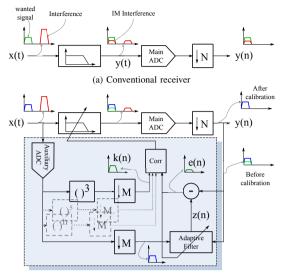

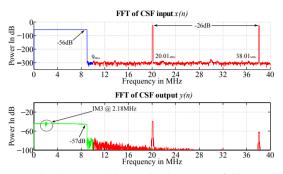

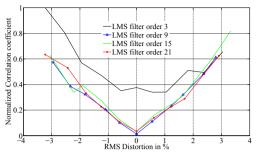

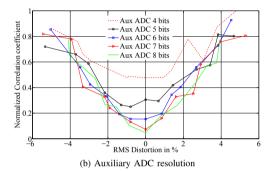

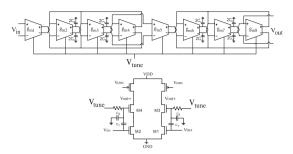

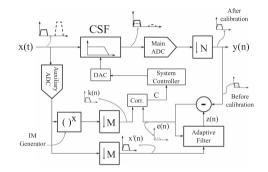

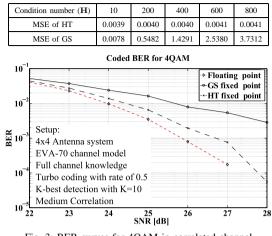

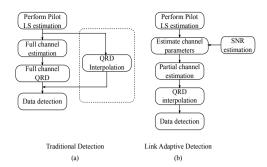

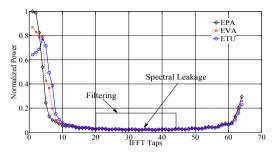

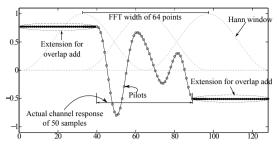

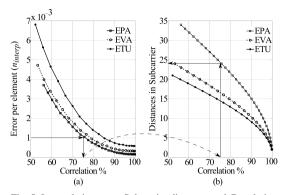

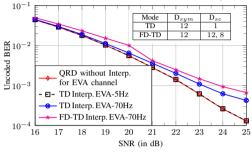

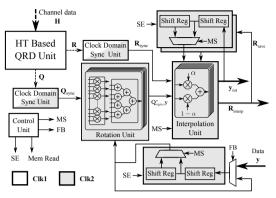

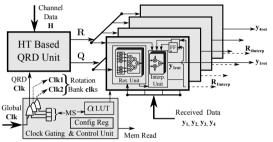

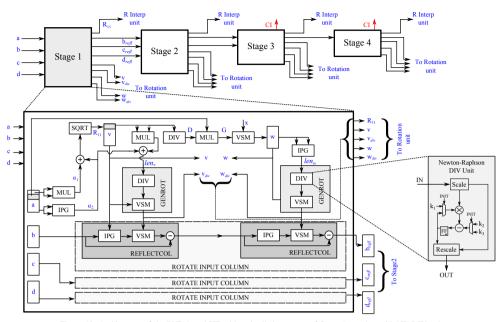

Cholesky decomposition (CD) may be used for decomposing Hermitian positive definite matrices. Such matrices are used in Zero-Forcing (ZF) and MMSE based symbol detectors. In massive MIMO systems with K single antenna users, the linear system represented by (2.2) has a large dimension due to the value of M (the number of antennas at the BS). This dimension may be reduced by multiplying (2.2) from the left by the Hermitian  $H^H$ , resulting in the Gram matrix  $H^H H$  of dimension  $K \times K$ . Such Hermitian matrices can be decomposed with either LDL decomposition or when they are positive definite, by the Cholesky decomposition. Consider a Gram matrix defined as