### Continuous-Time Delta-Sigma Modulators for Ultra-Low-Power Radios

Radjen, Dejan

2014

### Link to publication

Citation for published version (APA):

Radjen, D. (2014). Continuous-Time Delta-Sigma Modulators for Ultra-Low-Power Radios. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 19. Dec. 2025

# Continuous-Time ∆∑ Modulators for Ultra-Low-Power Radios

Dejan Radjen

Doctoral Dissertation Mixed Signal Circuit Design Lund, August 2014

Dejan Radjen

Department of Electrical and Information Technology

Mixed Signal Circuit Design

Lund University

P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral dissertations ISSN 1654-790X; No. 62 ISBN 978-91-7623-039-8

© 2014 Dejan Radjen Typeset in Palatino and Helvetica using LATEX  $2_{\mathcal{E}}$ . Printed in Sweden by Tryckeriet i E-huset, Lund University, Lund.

No part of this dissertation may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

# **Abstract**

The modern small devices of today require cheap low power radio frequency (RF) transceivers that can provide reliable connectivity at all times. In an RF transceiver, the analog-to-digital converter (ADC) is one of the most important parts and it is also one of the main power consumers. There are several architectures for implementing an ADC, but in the last decade, continuous-time  $\Delta\Sigma$  modulators (CT DSMs) have become popular due to their potential of achieving low power consumption and the inherent anti-alias filtering.

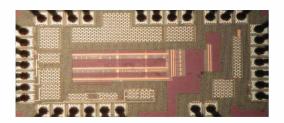

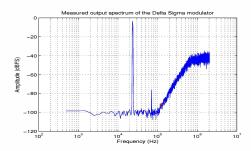

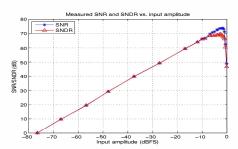

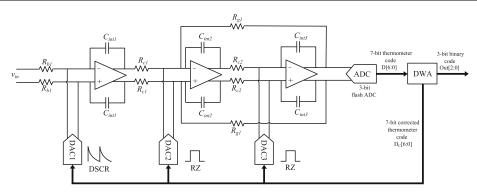

This thesis investigates different implementations of CT DSMs intended for an ultra-low-power (ULP) receiver operating in the 2.45 GHz ISM band. The main focus is on power saving techniques and jitter insensitive solutions. Papers I and II present a CT DSM with dual switched-capacitor-resistor (DSCR) feedback used in the first DAC. This technique has been developed for the purpose of reducing the jitter sensitivity of the CT DSM while keeping the DAC peak current lower than for conventional SCR feedback. A lower peak current translates into more relaxed slew-rate requirements on the first operational amplifier and thereby less power consumption. Papers III and IV present a low power 2nd-order CT DSM with one operational amplifier. The main objective was to reduce the power consumption of the usually more critical analog part while still achieving a 2nd-order noise shaping. The thesis also examines the possibility of using a successive approximation register (SAR) quantizer instead of the commonly used flash quantizer to reduce the power consumption of the digital part as well.

|   | _011, 0, 10 | <br>Page 11 |  |

|---|-------------|-------------|--|

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

|   |             |             |  |

| İ |             |             |  |

# Populärvetenskaplig sammanfattning

Små, trådlösa och portabla apparater utgör idag en stor del av vår uppkopplade värld. Under det senaste decenniet har dock flera teknologiska framsteg lett mot en utveckling där allt från maskiner till kläder kommunicerar med varandra. Detta brukar kallas för "sakernas internet" och uppskattas involvera 50 miljarder enheter år 2020. Genom att förse dessa enheter med små och smarta sensorer är det möjligt att känna av omgivningen och samla in olika former av data. Det finns många potentiella applikationer där detta är av intresse t.ex. medicinska implantat, spelkontroller, smarta hus och industriell övervakning. Inom medicinska tillämpningar har sensornätverk redan använts för att hålla reda på patientens tillstånd och olika kroppsvärden.

En av de största utmaningarna med sensornätverk är effektförbrukningen som bestämmer hur länge batteriet för en sensor kommer att räcka. Det är viktigt att batteritiden är så lång som möjligt eftersom sensorerna kan vara placerade på ställen som är svåra och farliga att komma åt. Energin från batteriet som sensorn har är det enda energin som den kommer få under dess livslängd. Eftersom batteritekniken går sakta framåt, är det viktigt att utveckla effektiva elektroniska kretsar och algoritmer som minimerar effekten som dras från batteriet.

En sensor kräver i slutändan digitala signaler för att uppnå den funktionalitet som anses viktig idag. Eftersom alla signaler i naturen är analoga, måste de omvandlas till digitala signaler. Detta är en uppgift för Analog-till-digital (A/D) omvandlaren som är en viktig del i det radiochip som sänder och tar emot signalerna i sensornätverket. Det kostar energi att omvandla analoga till digitala signaler vilket innebär att A/D omvandlaren är en kritisk komponent och ansvarar för en stor del av energiförbrukningen i ett radiochip. Det finns många typer av A/D omvandlare men under senare tid har  $\Delta\Sigma$  modulatorn blivit populär inom många applikationer.

Den här avhandlingen undersöker flera kretslösningar med syftet att minska känsligheten för tidsfel, så kallad klockjitter, och sänka effektförbrukningen i  $\Delta\Sigma$  modulatorn för en lågeffektsradio. Den första  $\Delta\Sigma$  modulatorn som konstruerades använde en speciell lösning med dubbla exponentiella pulser för att minska känsligheten för klockjitter. Dessa pulser håller den maximala återkopplingsströmmen på en rimlig nivå och sänker därför strömkravet för den första förstärkaren. Den här tekniken har verifierats med simuleringar och mätningar på ett tillverkat chip. I den andra  $\Delta\Sigma$  modulatorn undersöktes ett andra ordningens filter med bara en förstärkare för att minska effektförbrukningen i den analoga delen. Detta resulterade i en låg effektförbrukning medan den övriga prestandan uppfyllde kraven för lågeffektsradion. Den här tekniken har verifierats med simuleringar och mätningar på ett tillverkat chip. Slutligen användes en annan typ av A/D omvandlare s.k. successiv approximation A/D omvandlare som en del i den sistnämnda  $\Delta\Sigma$  modulatorn för att ytterligare sänka effekten i den digitala delen. Konceptet har hittills verifierats med simuleringar.

Det här arbetet har varit en del av ett större projekt som går ut på att konstruera en mottagarkedja för en lågeffektsradio. Kravet för den totala chipstorleken är 1 mm<sup>2</sup> och den maximala effektförbrukningen ska vara 1 mW. Projektet sponsrades av Swedish Foundation for Strategic Research (SSF).

# Contents

| C  | onter          | nts                                             | vii  |

|----|----------------|-------------------------------------------------|------|

| Pı | eface          | 2                                               | xi   |

| A  | ckno           | wledgments                                      | xiii |

| Li | st of          | acronyms                                        | xv   |

| Li | st of          | symbols                                         | xix  |

| 1  | Intr           | roduction                                       | 1    |

|    | 1.1            | Motivation                                      | 1    |

|    | 1.2            | The UPD project                                 | 2    |

|    | 1.3            | Research contributions                          | 3    |

|    | 1.4            | Outline                                         | 3    |

| 2  | $\Delta\Sigma$ | modulators                                      | 5    |

|    | 2.1            | Principles of $\Delta\Sigma$ modulation         | 5    |

|    |                | 2.1.1 Oversampling                              | 5    |

|    |                | 2.1.2 Noise shaping                             | 6    |

|    | 2.2            | $\Delta\Sigma$ modulator topologies             | 6    |

|    |                | 2.2.1 Discrete-time $\Delta\Sigma$ modulators   | 7    |

|    |                | 2.2.2 Continuous-time $\Delta\Sigma$ modulators | 9    |

|    | 2.3            | DAC feedback pulses                             | 12   |

|    |                | 2.3.1 Rectangular pulses                        | 13   |

|   | 5.4 | Results                                                    |  |

|---|-----|------------------------------------------------------------|--|

|   |     |                                                            |  |

|   |     | 5.3.3 SAR                                                  |  |

|   |     | 5.3.2 Comparator and ready generation                      |  |

|   | 3.3 | 5.3.1 SAR quantizer                                        |  |

|   | 5.3 | 5.2.2 Controlling the STF                                  |  |

|   |     | 5.2.1 Loop delay compensation                              |  |

|   | 5.2 | Implemented $\Delta\Sigma$ modulator                       |  |

|   | 5.1 | CT $\Delta\Sigma$ modulators with SAR quantizers           |  |

| 5 |     | Now power CT $\Delta\Sigma$ modulator with a SAR quantizer |  |

|   |     | 4.1.5 Amplifier non-idealities                             |  |

|   |     | 4.1.4 Anti-aliasing                                        |  |

|   |     | 4.1.3 Single opamp loop filters                            |  |

|   |     | 4.1.2 Active-passive loopfilters                           |  |

|   |     | 4.1.1 Passive loop filters                                 |  |

|   | 4.1 | Reducing the number of opamps                              |  |

| 4 | Pov | ver saving techniques                                      |  |

|   | 3.3 | Mismatch errors                                            |  |

|   | 22  | 3.2.4 Reducing the effect of clock Jitter                  |  |

|   |     | 3.2.3 Effect on the performance                            |  |

|   |     | 3.2.2 Jitter sensitivity of rectangular pulses             |  |

|   |     | 3.2.1 Jitter error sources in $\Delta\Sigma$ modulators    |  |

|   | 3.2 | Clock jitter                                               |  |

|   |     | 3.1.2 Loop delay and RZ feedback                           |  |

|   |     | 3.1.1 Loop delay compensation                              |  |

|   | 3.1 | Excess loop delay                                          |  |

| 3 | DA  | C non-idealities in CT $\Delta\Sigma$ modulators           |  |

|   |     | 2.3.3 Amplitude efficiency                                 |  |

|   |     | 2.3.2 Exponential pulses                                   |  |

| 17  | A Continuous Time $\Delta\Sigma$ Modulator with Reduced Clock Jitter Sensitivity through DSCR Feedback | 65 |

|-----|--------------------------------------------------------------------------------------------------------|----|

| II  | A Continuous Time Delta-Sigma Modulator with Reduced Clock Jitter Sensitivity through DSCR Feedback    | 73 |

| III | A Low-Power 2nd-order CT $\Delta\Sigma$ Modulator with a Single Operational Amplifier                  | 89 |

| IV  | A Low-Power 2nd-order CT Delta-Sigma Modulator with a Single Operational Amplifier                     | 97 |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

|     |                                                                                                        |    |

## **Preface**

This dissertation summarizes my research performed at the Department of Electrical and Information Technology at the Lund University for a Ph.D degree in circuit design. The following papers are considered to be a part of this thesis [1–4]:

- D. Radjen, P. Andreani, M. Anderson, and L. Sundström, "A Continuous Time ΔΣ Modulator with Reduced Clock Jitter Sensitivity through DSCR Feedback", in *Proc. of 29th NORCHIP Conference*, Lund, Sweden, Nov. 14-15 2011, pp. 1-4.

- D. Radjen, P. Andreani, M. Anderson, and L. Sundström, "A Continuous Time ΔΣ Modulator with Reduced Clock Jitter Sensitivity through DSCR Feedback", *Analog Integrated Circuits and Signal Processing*, vol. 74, pp. 21-31, Jan. 2013.

- D. Radjen, P. Andreani, M. Anderson, and L. Sundström, "A Low-Power 2nd-order CT  $\Delta\Sigma$  Modulator with a Single Operational Amplifier", in *Proc. of 31th NORCHIP Conference*, Vilnius, Lithuania, Nov. 11-12 2013, pp. 1-4.

- D. Radjen, M. Anderson, L. Sundström and P. Andreani, "A Low-Power 2nd-order CT ΔΣ Modulator with a Single Operational Amplifier", Analog Integrated Circuits and Signal Processing, Accepted for publication.

I have also co-authored the following papers which are not considered as a part of this dissertation:

• H. SJÖLAND, J. B. ANDERSON, C. BRYANT, R. CHANDRA, O. EDFORS, A. J. JOHANSSON, N. S. MAZLOUM, R. MERAJI, P. NILSSON, D. RADJEN, J. N. RODRIGUES, S. M. Y. SHERAZI AND V. ÖWALL, "A Receiver Architecture for Devices in Wireless Body Area Networks", *IEEE J. Emerging and Selected Topics in Circuits and Systems*, vol. 2, no. 1, pp. 82-95, Mar 2012.

- Y. Wu, X. Liu, D. Ye, V. Viswam, L. Zhu, P. Lu, D. Radjen and H. Sjöland, "A 0.13 $\mu$ m CMOS  $\Delta\Sigma$  PLL FM transmitter", in *Proc. of 29th NORCHIP Conference*, Lund, Sweden, Nov. 14-15 2011, pp. 1-4.

- J. Lindstrand, D. Radjen, R. Fitzgerald, A. Axholt and H. Sjöland, "An Integrated 3-Level Fully Adjustable PWM Class-D Audio Amplifier in 0.35μm CMOS", in *Proc. of 26th NORCHIP Conference*, Tallinn, Estonia, Nov. 16-17 2008, pp. 168-171.

# Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor, Associate Professor Pietro Andreani, for his great support, encouragement and important feedback throughout all these years. His guidance and advice have been truly helpful in bringing this work forward when I was stuck. It has been an honour working with you.

I extend my sincere gratitude to my co-supervisor, Dr. Martin Anderson, who initially got me interested in Ph.D studies. His guidance, especially during the first years, has been of great importance for me. I appreciate all the long discussions that we have had and all the ideas and knowledge that you have shared with me

I am also thankful to Dr. Lars Sundström who has always shown great interest and enthusiasm for my and other projects in the mixed signal group. His broad knowledge and expertise have been invaluable, especially during regular meetings. Thank you for your advice and feedback on my manuscripts.

Thanks to Professor Henrik Sjöland for supervising the UPD project which I was a part of. I am also thankful to Carl Bryant, Nafiseh Seyed Mazloum, Reza Meraji, Rohit Chandra and Yasser Sherazi for being great project members and friends.

Already during my master studies, I was fortunate to get to know Carl and Jonas Lindstrand with whom I have discussed many topics and learned much about circuit design from. Thank you both for being great friends and for all the lunches and dinners that we had.

A big thanks to Mattias Andersson and Xiaodong Liu for being great roommates. We have been working in the same field and had interesting discussions over both technical and non-technical matters. It sure has been a pleasure working with you all these years.

I'm grateful to all other colleagues including Anders Nejdel, Babak Mohammadi, Chenxin Zhang, Dimitar Nikolov, Henmanth Prabhu, Isael Diaz, Joachim

Rodriguez, Liang Liu, Markus Törmänen, Mohammed Abdulaziz, Oskar Andersson, Ping Lu, Rakesh Gangarajaiah and Tobias Tired for the great atmosphere at the department.

Thanks goes to Erik Jonsson, Lars Hedenstjerna, Pia Bruhn and Stefan Molund for managing all technical and administrative issues.

Lastly, I would like to thank my family and my friends for constant support and great times outside the office.

Dejan Radjen Lund, August 2014

# List of acronyms

AA Anti-alias

ADC Analog-to-digital converter

CIFB Cascaded integrator feedback

CIFF Cascaded integrator feedforward

CT Continuous-time

DAC Digital-to-analog converter

DEM Dynamic-element matching

DLL Delay-locked loop

DSCR Dual switched-capacitor-resistor

DSM  $\Delta\Sigma$  modulator

DT Discrete-time

DWA Data weighted averaging

FSCR Full clock period switched-capacitor-resistor

WFSK Wide-band frequency shift keying

GBW Gain bandwidth

IBN In-band noise

IID Independent and identically distributed

LSB Least significant bit

NRZ Nonreturn-to-zero

NTF Noise transfer function

OBG Out-of-band gain

OSR Oversampling ratio

PLL Phase-locked loop

PP Pulse-position

PW Pulse-width

RF Radio frequency

RZ Return-to-zero

SAR Successive approximation register

SC Switched-capacitor

SCR Switched-capacitor-resistor

SCSR Switched-capacitor switched-resistor

SCVR Switched-capacitor variable-resistor

SNR Signal-to-noise ratio

SNDR Signal-to-noise-and-distortion ratio

SOA Single operational amplifier

SQNR Signal-to-quantization noise ratio

SSF Swedish Foundation for Strategic Research Signal transfer function STF Ultra-low-power ULP UPD Ultra-portable devices xvii

# List of symbols

$A_f$  Activity factor

α Starting time instant of a DAC pulse

$\beta$  Ending time instant of a DAC pulse

dQ Charge error

Δ Quantization step

$e_a$  amplitude error sequence

$e_q$  Jitter charge error sequence

$f_{bw}$  Signal bandwidth

$f_s$  Sampling frequency

$H_{CT}$  Continuous-time feedback transfer function

$H_{DT}$  Discrete-time feedback transfer function

*G<sub>CT</sub>* Continuous-time forward transfer function

*G*<sub>DT</sub> Discrete-time forward transfer function

$IBN_{j,exp}$  In-band noise due to jittered exponential pulses

$IBN_{j,rec}$  In-band noise due to jittered rectangular pulses

L Loop filter order

N Number of bits in the quantizer

$N_q$  Quantization noise

NTF Noise transfer function

$\eta_a$  Amplitude efficiency

$\eta_j$  Jitter suppression efficiency

OSR Oversampling ratio

Q Charge

STF Signal transfer function

$\sigma_i$  Standard deviation of the jitter timing error

$t_d$  Loop delay

$t_d$  Jitter timing error

$T_s$  Sampling period

au Time constant

$\tau_d$  Normalized loop delay

$\tau_n$  Normalized time constant

1

# Introduction

### 1.1 MOTIVATION

In today's modern world, the use of wireless communication has expanded into many areas of our life. This development stimulates the innovation of new technologies to meet the ever increasing demands on the communication systems. As the wireless revolution now takes its first steps into a future scenario where all things communicate with everything and everywhere, also referred to as Internet of Things, new challenges arise and the old ones are getting more prominent. One of the most critical of these challenges is the power consumption. Especially in ultra-low-power (ULP) wireless applications such as smart sensors and medical implants, it is important to minimize the power consumption and achieve battery lifetimes of several years. The next step is the use of scavenged energy from the surroundings which would eventually eliminate the need for batteries. This level of portability can only be realised by addressing the design issues of the radio frequency (RF) transceiver which is the most critical component in ULP wireless applications. To achieve a truly low power operation, the transceiver should only be activated when sending/receiving data. Furthermore, it should consume minimum amount of power when active and provide sufficiently reliable connectivity at all times.

The analog-to-digital converter (ADC) is a mandatory component in an RF transceiver and cannot be avoided due to the required interface between analog and digital domains. Conversion of analog to digital signals is a power hungry operation which makes the ADC one of the highest power consumers in an ULP RF transceiver. The  $\Delta\Sigma$  modulator (DSM) is a type of ADC that has increased in popularity and also found its way in ULP applications. Its operation is based on a negative feedback system which combines two important concepts: oversampling and noise shaping. This enables the use of quantizers with only a few bits while still achieving a high resolution. Due to negative feedback and a low number of

2 Introduction

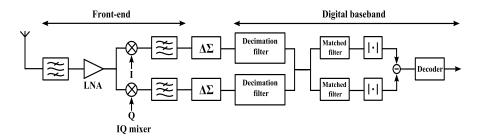

Fig. 1.1: UPD project, receiver chain.

bits, the matching requirements in the quantizer are relaxed.

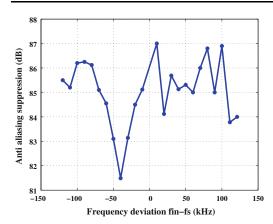

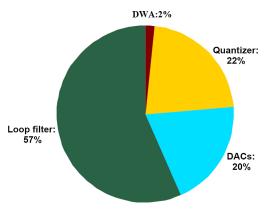

Traditionally DSMs have been implemented with discrete-time (DT) circuits. These types of modulators are referred to as DT DSMs. In recent years, DSMs using continuous-time (CT) circuits i.e. CT DSMs have received increasing attention due to the following reasons: 1) Relaxed amplifier requirements compared to DT DSMs resulting in lower power consumption. 2) Implicit anti-alias (AA) filtering which is especially beneficial in radio applications. The loop filter is usually the largest power consumer in a CT DSM due to the use of operational amplifiers. This dissertation addresses the issue with power consumption by using alternative loop filter implementations with fewer operational amplifiers while still maintaining the desired resolution. An attempt has also been made to decrease the power consumption in the quantizer. Furthermore, the high clock jitter sensitivity usually associated with CT DSMs has also been considered.

### 1.2 THE UPD PROJECT

This work has been a part of the ultra-portable devices (UPD) project which was sponsored by Swedish Foundation for Strategic Research (SSF). The objective was to design a receiver chain intended for ULP short range wireless applications. Some of the specifications are as follows:

• Power consumption (active mode): 1 mW.

• Data rate: 250 kb/s.

• Frequency band: 2.45 GHz.

• Chip area: 1 mm<sup>2</sup>.

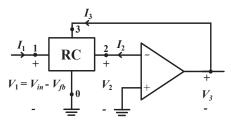

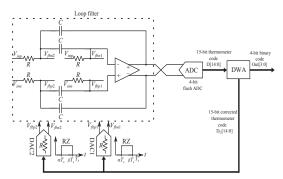

The architecture of the receiver chain is shown in Fig. 1.1. It consist of a direct conversion front-end followed by the  $\Delta\Sigma$  ADCs and the digital baseband. The chosen modulation was wideband frequency shift keying (WFSK). This is a constant envelope modulation that is easy to demodulate and it supports the use of

1.4. Outline 3

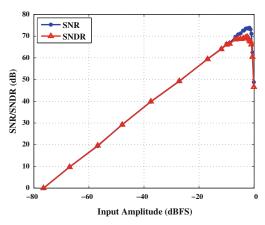

non-linear but efficient power amplifiers. The power budget for one ADC was allocated to  $100~\mu W$  and the minimum required signal-to-noise-and-distortion ratio (SNDR) found from simulations was 50 dB. More details about the receiver can be found in [5].

### 1.3 RESEARCH CONTRIBUTIONS

The following are the research contributions from the dissertation:

- A new technique termed dual switched-capacitor-resistor (DSCR) feedback which reduces the peak current of the feedback digital-to-analog converter (DAC) while still maintaining a low sensitivity to clock jitter. Reduced peak current relaxes the slew-rate requirements on the operational amplifiers.

- Analysis and calculation of thermal noise contribution from the DSCR DAC and design procedure for DSCR feedback in CT DSMs.

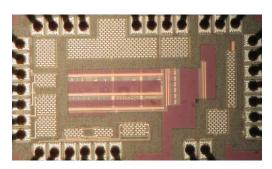

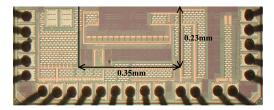

- A fabricated and measured chip which implements a CT DSM with DSCR feedback.

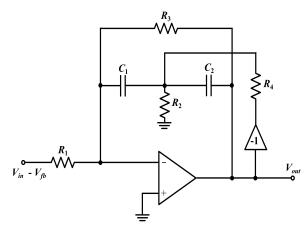

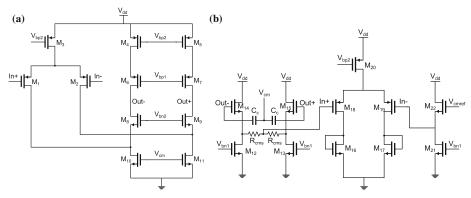

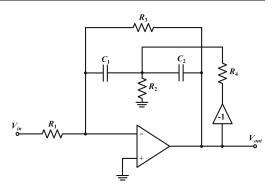

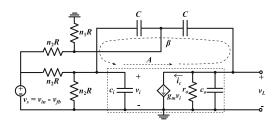

- Reduction of power consumption in CT DSMs using a 2nd-order single operational amplifier (SOA) loop filter.

- A method for extending the range of realizable feedback coefficients in the chosen 2nd-order SOA loop filter compared to prior work.

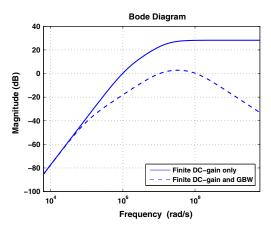

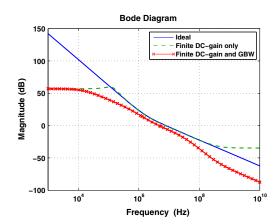

- Simulation results including amplifier non-idealities which can be used to assist the design of CT DSMs with the chosen SOA loop filter.

- A fabricated and measured chip which implements a CT DSM with the SOA loop filter. This circuit meets the required specifications of the receiver chain used in the UPD project.

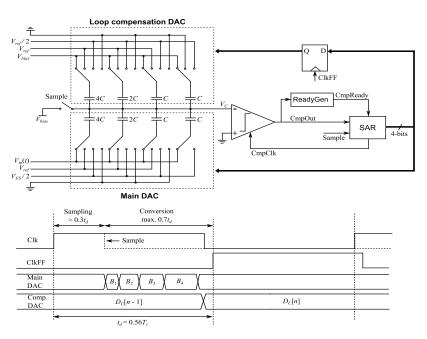

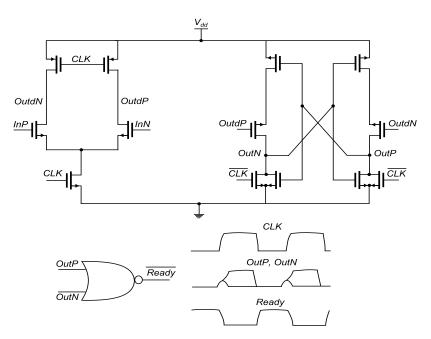

- Reduction of power consumption in CT DSMs by replacing the commonly used flash quantizer with an asynchronous successive approximation (SAR) quantizer.

### 1.4 OUTLINE

The outline of the dissertation is as follows:

**Chapter 1** presents the motivation behind the research topic and gives a short introduction to the UPD-project which this work was a part of. The main research contributions of this dissertation are also outlined.

4 Introduction

**Chapter 2** gives a basic introduction to DSMs. The concepts that are relevant for the following content are covered.

**Chapter 3** discusses the non-idealities typically present in CT DSMs such as excess loop delay, clock jitter and mismatch errors. Different techniques to handle the non-idealities are also covered.

**Chapter 4** introduces passive, active-passive and SOA loop filters and how they can be used to reduce the power consumption of CT DSMs. Different circuit implementations are analysed and compared.

**Chapter 5** introduces asynchronous SAR quantizers and how they can be used to reduce the power consumption of CT DSMs.

Chapter 6 gives conclusions and future work.

Papers I - IV

# 2

# $\Delta\Sigma$ modulators

This chapter gives a brief introduction to the basic principles of  $\Delta\Sigma$  modulators (DSMs) and then focuses on CT DSMs. Important design aspects of CT DSMs such as discrete to continuous-time conversion, selection of the feedback pulses and anti-alias (AA) filtering are covered as well.

### 2.1 PRINCIPLES OF $\Delta\Sigma$ MODULATION

DSMs employ a combination two important concepts: oversampling and noise shaping. Both of these are discussed in this section.

### 2.1.1 OVERSAMPLING

Analog-to-digital converters (ADCs) can be divided into two types: Nyquist-rate ADCs and oversampling ADCs. The type of ADC is determined by the oversampling ratio (OSR) which is the ratio between the Nyquist frequency and the signal bandwidth i.e.

$$OSR = \frac{f_s}{2f_{bw}} \tag{2.1}$$

where  $f_s$  is the sampling frequency and  $f_{bw}$  is the signal bandwidth. A strict definition of a Nyquist ADC would be OSR = 1 as the sampling frequency is twice the signal bandwidth, just enough to fulfil the Nyquist sampling criterion. However, in practice, Nyquist ADCs use slightly higher OSR, typically less than 8, to relax the AA filtering [6]. The OSR for oversampling ADCs is usually significantly larger than for Nyquist ADCs and could be several hundreds for certain cases.

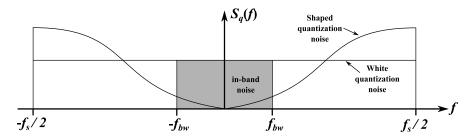

Assuming that the quantization noise from an N-bit ADC can be approximated as white noise [7] [8], the power spectral density is spread uniformly in the Nyquist interval as shown in Fig. 2.1. It is obvious that an increased OSR will reduce the IBN since the signal band occupies a smaller portion of the Nyquist in-

$\Delta\Sigma$  modulators

**Fig. 2.1:** Quantization noise spectra with oversampling and noise shaping.

terval. Every doubling of the OSR improves the signal-to-quantization-noise ratio (SQNR) by 3 dB [9]. However, this improvement is not always sufficient and very high OSRs are often required to significantly increase the SQNR.

### 2.1.2 NOISE SHAPING

Oversampling can become more effective if the IBN is further reduced by noise shaping. The noise shaped spectrum is also shown in Fig. 2.1 where the quantization noise is shaped by an appropriate high-pass filter function. If a 1st-order high-pass filter is used, every doubling of the OSR results in an SQNR improvement of 9 dB [9]. Consequently, the combination of oversampling and noise shaping is more effective compared to oversampling alone. The performance can be further improved by using a higher order filter. It should be noted that noise shaping does not reduce the total noise power in the Nyquist interval. Integrating the noise from 0 to  $f_s/2$  would still yield the same power as for oversampling alone. However, the IBN is reduced and more noise is pushed towards higher frequencies. To fully exploit the benefit provided by oversampling and noise shaping, a sharp low-pass digital filter is required after the ADC to filter out the noise outside the band of interest. Furthermore, the sampling rate at the output of the ADC must be reduced to the Nyquist rate by discarding (i.e. decimating) the unnecessary samples. Usually, filtering and decimation are combined into one filter called decimation filter [10].

### 2.2 $\Delta\Sigma$ MODULATOR TOPOLOGIES

The simplest approach to achieve noise shaping is by placing a high-pass filter after the quantizer. The problem with this approach is that the signal will be filtered as well. This is undesirable since ideally the input signal should remain unaffected. To avoid filtering of the input signal, while still achieving high-pass filtering of the quantization noise, a loop filter can be placed in a feedback loop together with the quantizer. This is the basic architecture of a DSM. The loop filter

can be implemented either in the DT or CT domain and the resulting modulators are referred to as DT respectively CT DSMs. Both types of DSMs are covered in this section.

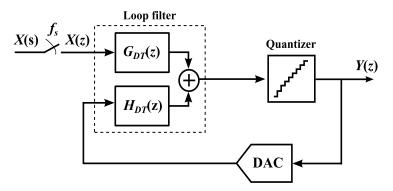

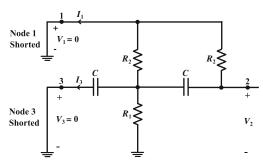

### 2.2.1 DISCRETE-TIME $\Delta\Sigma$ MODULATORS

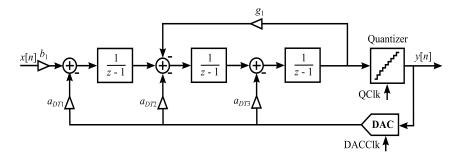

The block diagram of a general DT DSM is shown in Fig. 2.2. It is a feedback configuration consisting of a DT loop filter, a quantizer with arbitrary number of bits and a feedback digital-to-analog converter (DAC). The DAC is required to convert the digital signal after the quantizer to a DT signal that is fed back to the loop filter. The CT signal at the input is sampled, i.e. converted to a DT signal, before entering the loop filter. The forward transfer function  $G_{DT}(z)$  and the feedback transfer function  $H_{DT}(z)$  are usually realized as a two-input loop filter.

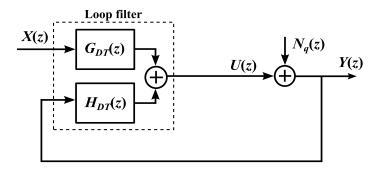

### DT LINEAR MODEL

The system in Fig. 2.2 is difficult to analyze mathematically due to the non-linear transfer characteristics of the quantizer. However, an intuitive understanding of its operation can be obtained by replacing the quantizer with its linear model consisting of additive quantization noise  $N_q$  and a unity gain block. Furthermore, if the feedback DAC is ideal, it can be omitted since only operation at sampling instants is of interest. The resulting linearised model is shown in Fig. 2.3. By performing linear analysis, it can be shown that the output Y can be written as a linear combination of the input signal X and the quantization noise  $N_q$ :

$$Y(z) = STF(z)X(z) + NTF(z)N_q(z)$$

(2.2)

where

$$NTF(z) = \frac{1}{1 + H_{DT}(z)}$$

(2.3)

is the noise transfer function (NTF), and

$$STF(z) = \frac{G_{DT}(z)}{1 + H_{DT}(z)} = G_{DT}(z)NTF(z)$$

(2.4)

is the signal transfer function (STF). From (2.3) it can be concluded that the feedback transfer function  $H_{DT}(z)$  must be large in the band of interest to reduce the NTF there and implement high-pass filtering of the quantization noise. According to (2.4), the forward transfer function  $G_{DT}(z)$  must also be large in the same range to force the STF to equal unity. Consequently, both  $G_{DT}(z)$  and  $H_{DT}(z)$  must be low-pass transfer functions.

$\Delta\Sigma$  modulators

Fig. 2.2: General DT DSM.

Fig. 2.3: DT linear model.

### **STABILITY**

The DSM in Fig. 2.2 is a non-linear feedback system and hence stability is of great importance. Although the linear model is simple and intuitive, it fails to predict the stability behaviour of DSMs in many cases. This is due to the fact that the gain of the quantizer is signal dependent, an effect that is not captured by the linear model. More sophisticated models that change the quantizer gain in accordance with the input signal do exist [11] [12]. However, to predict stability without any doubt, extensive simulations should always be performed.

The stability requirement also restricts the possible choices of the NTF [13]. This becomes more important for higher order loop filters as less aggressive NTFs are required to guarantee stability. Assuming a loop filter with order *L*, the simplest NTFs are Lth order differentiators:

$$NTF(z) = (1 - z^{-1})^{L} (2.5)$$

A high order differentiator yields a more effective noise shaping but it also results in a large out-of-band gain (OBG). For L > 2, the large OBGs can lead to

Fig. 2.4: A 3rd-order DT CIFB DSM.

instability, especially if single-bit quantizers are used [13]. To ensure stable operation, the NTFs in (2.5) can be modified by shifting the poles from the origin. The pole locations can then be controlled to reduce the OBG and thereby enable the implementation of high order NTFs. This procedure is implemented in the commonly used Schreier's toolbox in Matlab [14]. The toolbox takes into account the trade-off between OBG and maximal achievable SQNR and optimizes the NTF accordingly. The resulting NTF yields a realistic SQNR that differs significantly from the one predicted by the linear model.

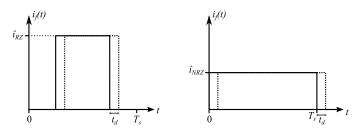

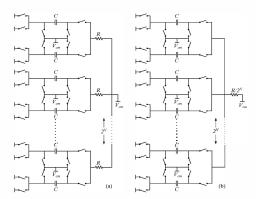

### IMPLEMENTATION OF DT LOOP FILTERS

There are many different ways of implementing loop filters for DSMs. The two most common architectures for low pass DSMs are: cascaded integrator feedback (CIFB) and feedforward (CIFF) [15]. The former has been used in [1–4]. As an example, a DSM employing a CIFB loop filter of order 3, which achieves a unity STF in-band, is shown in Fig. 2.4. The feedback coefficients  $a_{DT1} - a_{DT3}$  can be obtained from [14] when a suitable NTF has been determined. By introducing the coefficient  $g_1$ , zero-optimized NTFs can be achieved which further increases the SQNR.

The DT integrators I(z)=1/(z-1) are implemented using switched-capacitor (SC) circuits. The summing operations can be realized with summing SC integrators while the coefficients are given by capacitance ratios. The latter is beneficial regarding process variations as capacitor ratios can be implemented accurately in CMOS processes [16].

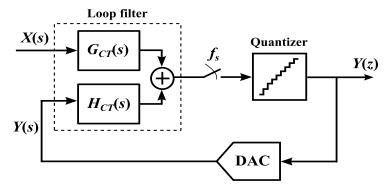

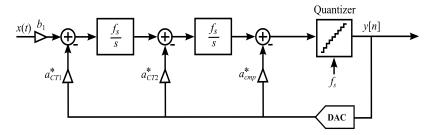

### 2.2.2 CONTINUOUS-TIME $\Delta\Sigma$ MODULATORS

The first DSM modulator was actually implemented with a CT loop filter [17]. When SC circuits were introduced, DT DSMs became popular due to their low sensitivity to process variations. However, recently CT DSMs have received increasing attention due to lower power consumption and AA filtering. Furthermore, for low-voltage applications, the resistance of the switches in DT DSMs is

$\Delta\Sigma$  modulators

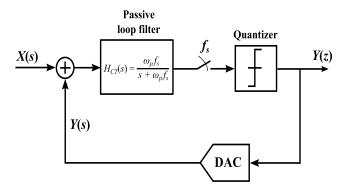

Fig. 2.5: General CT DSM.

Fig. 2.6: CT linear model.

increased due to the lower overdrive voltage [18]. This issue is avoided in CT DSMs since the loop filter does not require any switches. Several low-voltage (below 1V) CT DSMs have been demonstrated in [19–21].

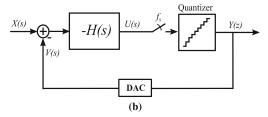

The block diagram of a general CT DSM is shown in Fig. 2.5. Compared to the DT DSM in Fig. 2.2, the loop filter is CT and the sampling operation is moved inside the loop. In practical implementations, sampling is performed by the quantizer.

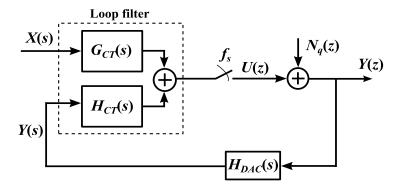

### **CT LINEAR MODEL**

If the quantizer is replaced by additive noise and a unity gain block as in 2.2.1, a linear model of the CT DSM in Fig. 2.5 is obtained and shown in Fig. 2.6. An important distinction to the DT linear model is that the the transfer function of the feedback DAC,  $H_{DAC}(s)$ , needs to be taken into account. This is since the loop filter processes CT signals and the behaviour between sampling instants cannot be ignored. However, the transfer function from output Y to the input of the

quantizer *U* is still DT, due to the sampling operation inside the loop.

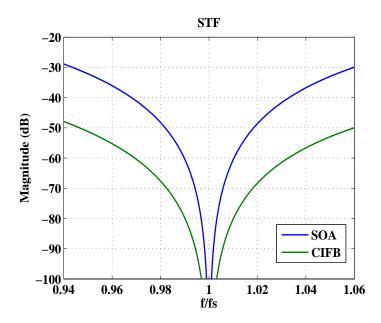

The processing of the input signal also requires special attention since the definition of the STF for a CT DSM is not as straight forward as for the DT DSM. From Fig. 2.6 it is obvious that the CT input signal is pre-filtered by the forward transfer function  $G_{CT}(s)$  before it is sampled. This action improves the AA filtering present in CT DSMs. The shorthand expression for the signal after filtering and sampling is  $[G_{CT}(s)X(s)]^*$  where \* is the star operator [22] and refers to the periodic spectrum repetition after sampling. Since the input signal is in the CT domain and the output signal is in the DT-domain, it is not possible to define a DT STF [23]. However, it is possible to define a CT STF. After direct analysis of the block diagram in Fig. 2.6, it can be shown that the output signal can be written as

$$Y(z) = NTF(z)[G_{CT}(s)X(s)]^{*} + NTF(z)N_{q}(z)$$

=  $[G_{CT}(s)NTF(e^{sT_{s}})X(s)]^{*} + NTF(z)N_{q}(z)$  (2.6)

where NTF(z) is the same as for the DT DSM and is given by (2.3) and  $z = e^{sT_s}$  with a sampling period of  $T_s$ . The input signal is multiplied by  $G_{CT}(s)NTF(e^{sT_s})$  before the star operator is applied and therefore the CT STF is defined as

$$STF(s) = G_{CT}(s)NTF(e^{sT_s}). (2.7)$$

Just as for DT DSMs, the STF depends on the NTF. This effect further improves the AA filtering in CT DSMs.

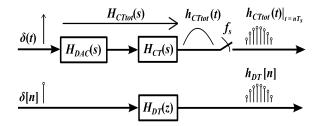

### **DISCRETE TO CONTINUOUS TIME CONVERSION**

The design of CT DSMs usually starts by transforming a DT system to its CT equivalent. This approach is preferred since the theory of optimizing a desired DT loop filter to meet certain specifications is well established. Furthermore, there is software available for efficient design and fast simulation of DT systems [14].

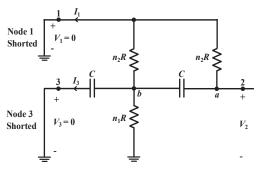

The equivalence between CT and DT DSMs is achieved by using the impulse invariant transformation [9] [23]. This method is based on the observation that the transfer function from the output to the input of the quantizer in both DT and CT DSMs is in the DT domain, compare Fig. 2.3 and Fig. 2.6. Then by simply equating the impulse responses from the output to the input of the quantizer, as shown in Fig. 2.7, the equivalence is achieved. In other words, the following equation is solved:

$$\mathcal{Z}^{-1}\{H_{DT}(z)\} = \mathcal{L}^{-1}\{H_{CT}(s)H_{DAC}(s)\}|_{t=nT_s}.$$

(2.8)

For simple DAC feedback pulses,  $H_{DAC}(s)$ , (2.8) can be solved analytically [23–25]. More complicated pulses can be handled by using numerical methods [26] [27].

12  $\Delta\Sigma$  modulators

Fig. 2.7: Impulse invariant transformation.

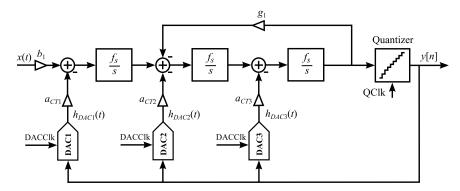

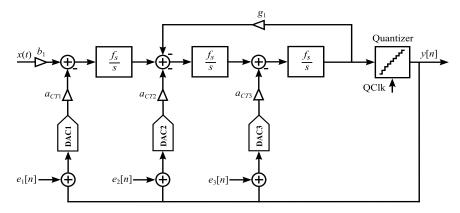

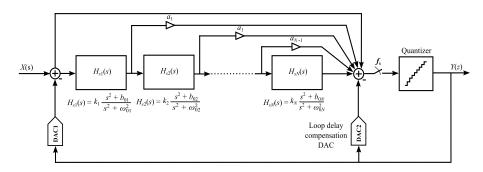

Fig. 2.8: A 3rd-order CT CIFB DSM.

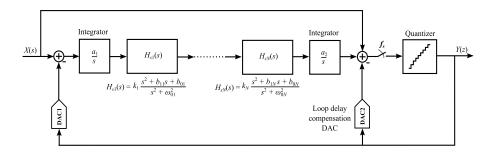

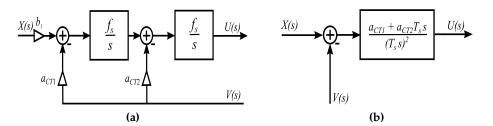

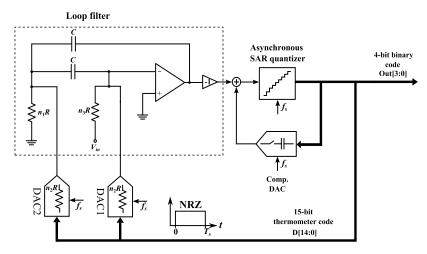

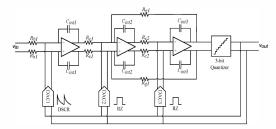

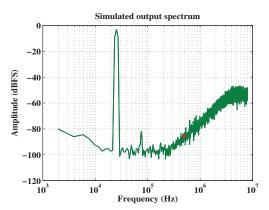

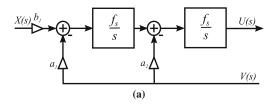

### IMPLEMENTATION OF CT LOOP FILTERS

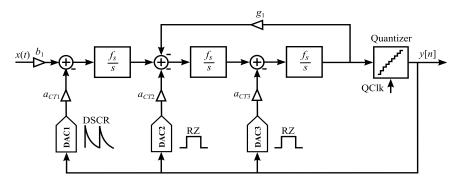

Fig. 2.8 shows a DSM employing a CT version of the CIFB loop filter in Fig. 2.4. The basic architecture is the same as for the DT loop filter. However, the integrators are of CT type with the transfer function  $I(s) = f_s/s$ . In practice, active-RC and/or gmC-integrators can be used to realize I(s) and the loop filter coefficients. Starting with a DT loop filter with DT feedback coefficients  $a_{DT1} - a_{DT3}$ , the CT feedback coefficients  $a_{CT1} - a_{CT3}$  can be obtained by solving (2.8) for DAC pulses  $h_{DAC1}(t) - h_{DAC3}(t)$ .

### 2.3 DAC FEEDBACK PULSES

Theoretically, there is an endless number of possible DAC pulses that can be used in CT DSMs. The choice is usually restricted by practical considerations such as ease of implementation and timing errors which include clock jitter and loop delay. The effect of timing errors in CT DSMs will be discussed in the chapter 3.

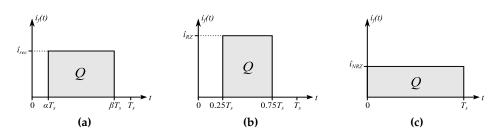

### 2.3. DAC feedback pulses

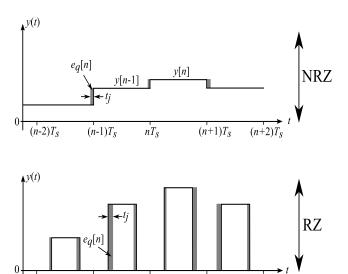

**Figure 2.9:** Rectangular DAC pulses. (a) General rectangular pulse, (b) RZ-pulse with duty cycle of 0.5, (c) NRZ-pulse.

### 2.3.1 RECTANGULAR PULSES

The most commonly used feedback pulses are rectangular pulses [24] [28]. These pulses are simple to generate by switching either current or voltage sources with control signals derived from the main clock. A general rectangular pulse of the DAC at the input of the corresponding integrator is shown in Fig. 2.9a where  $\hat{i}_{rec}$  is the DAC peak current and Q is the amount of charge transferred during one sampling period. The pulse is contained within one sampling period  $T_s$ . The transfer function of a DAC generating rectangular pulses is found by taking the Laplace transform of the pulse in Fig. 2.9a

$$H_{rec}(s) = \hat{i}_{rec} \frac{e^{-\alpha T_s s} - e^{-\beta T_s s}}{s}.$$

(2.9)

This transfer function can be used in (2.8) to analytically obtain the feedback coefficients for general rectangular feedback pulses.

### **RETURN-TO-ZERO FEEDBACK**

If  $\beta - \alpha < 1$  for the pulse in Fig. 2.9a, the feedback is referred to as return-to-zero (RZ) as the DAC current returns to zero at  $\beta T_s$ . It is common to use RZ pulses with  $\beta - \alpha = 0.5$ , as shown in Fig. 2.9b, since this results in a duty cycle of 0.5 which is easy to implement. In chapter 3, it will become clear that RZ feedback is most sensitive to clock jitter and can be critical if used in the outermost DAC in a DSM. However, it can be used in the subsequent DACs with benefit to avoid additional circuit complexity due to loop delay compensation.

### NONRETURN-TO-ZERO FEEDBACK

Another special case of the rectangular pulses, shown in Fig. 2.9c, is obtained if  $\alpha=0$  and  $\beta=1$ . The DAC current is high during the entire sampling period and therefore the feedback is referred to as nonreturn-to-zero (NRZ). For two equivalent DSMs employing NRZ and RZ feedback, respectively in the first feedback

13

$\Delta\Sigma$  modulators

branch, the peak current for the NRZ modulator is reduced by half compared to the RZ modulator. The reason is that the transferred charge Q for two equivalent modulators is the same and the current must be doubled for RZ feedback to transfer the same charge during  $T_s/2$ . This translates into a larger CT feedback coefficient for the RZ modulator i.e.  $a_{CT1,RZ} = 2a_{CT1,NRZ}$ .

The reduced peak current of the NRZ pulses is beneficial since it relaxes the integrator amplifier slew-rate requirements. As will become clear in chapter 3, NRZ feedback is less sensitive to clock jitter than RZ feedback. However, excess loop delay prevents the use of NRZ feedback in all DACs as the delay can easily shift the NRZ pulses into the next sampling period which in turn can lead to an unstable DSM.

### 2.3.2 EXPONENTIAL PULSES

In the recent decade, there have been several works that have used shaped feedback pulses to further reduce the jitter sensitivity of CT DSMs. The most widely used shaped feedback pulses are exponentially decaying pulses [2] [25] [26] [29] [30] since they are fairly easy to generate. In its most simplest form, exponential decay can be achieved by letting a capacitor discharge through a resistor.

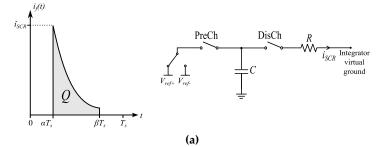

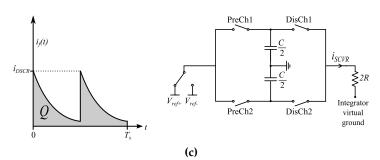

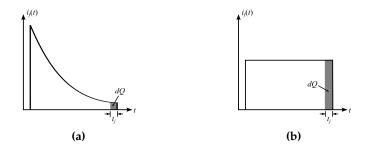

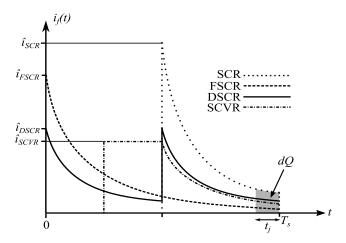

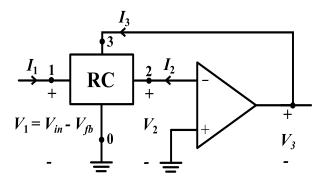

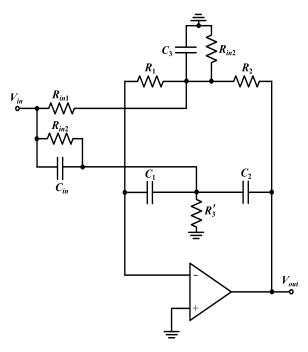

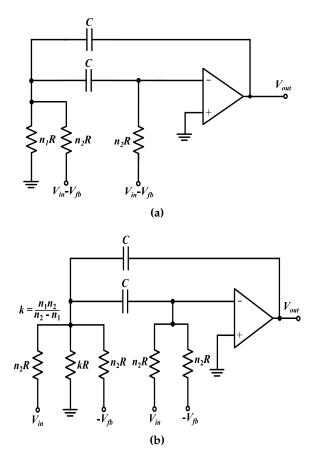

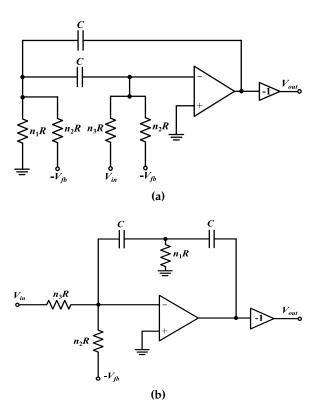

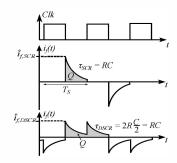

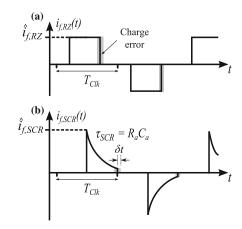

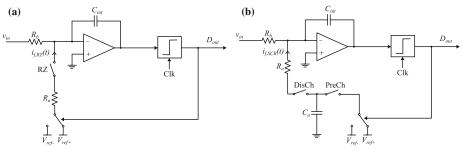

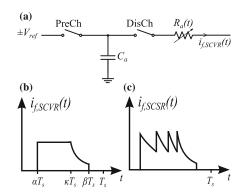

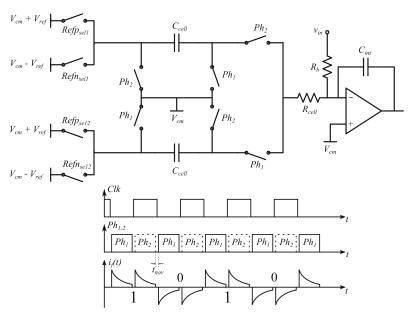

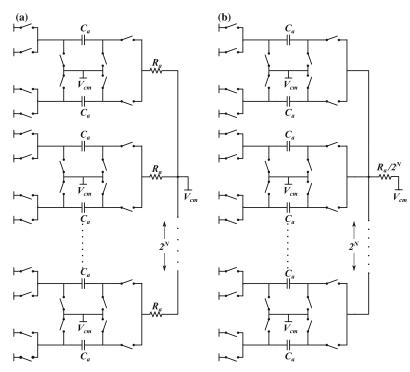

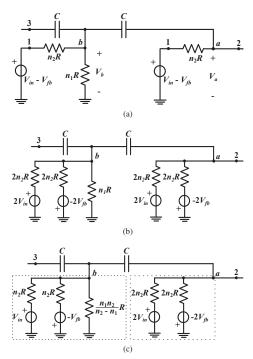

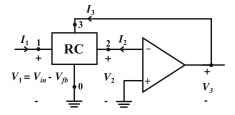

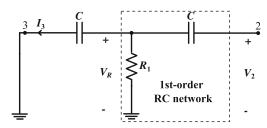

### SWITCHED-CAPACITOR-RESISTOR FEEDBACK

Switched-capacitor-resistor (SCR) feedback, shown in Fig. 2.10a together with the circuit implementation, was first introduced in [29]. The basic idea is to charge a capacitor C during the first half of the sampling period and discharge it through a resistor R during the second half of the sampling period. The jitter sensitivity is determined by the time constant  $\tau = RC$ . Compared to rectangular pulses for the same charge transferred during one sampling period, the peak current of exponential pulses is larger since more charge is transferred in the beginning. This requires again a larger feedback coefficient than for an equivalent NRZ or RZ feedback path. The peak current required to transfer a charge Q using SCR feedback is also dependent on  $\tau$ .

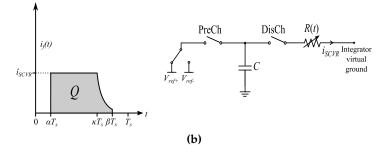

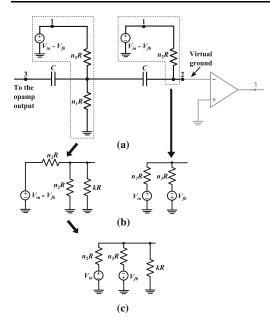

### SWITCHED-CAPACITOR VARIABLE-RESISTOR FEEDBACK

One method of reducing the peak current while still maintaining a low jitter sensitivity was presented in [26]. The feedback pulse and the circuit implementation are shown in Fig. 2.10b. Since the capacitor is discharged through a variable resistor, the technique is called switched-capacitor variable-resistor (SCVR) feedback. The capacitor is first charged for  $0 < t < \alpha T_s$  and then discharged through the variable resistor for  $\alpha T_s < t < \kappa T_s$ . The resistance must vary in a linear fashion to keep the current constant during discharge. Finally, for  $\kappa T_s < t < \beta T_s$ , the resistance is held constant and the current decreases exponentially. In this way a

#### 2.3. DAC feedback pulses

**Figure 2.10:** Exponential pulses and circuit implementations. (a) SCR pulse, (b) SCVR pulse, (c) DSCR pulse, (d) FSCR pulse.

$\Delta\Sigma$  modulators

combination of an RZ and SCR pulses is created with a reduced peak current and low jitter sensitivity.

Implementation of a continuously varying resistance is not trivial and can only be approximated by switching in several resistors in discrete steps. The feedback is then called switched-capacitor switched-resistor (SCSR) feedback. Although SCSR feedback manages to lower the peak current, the circuit complexity increases significantly compared to SCR feedback.

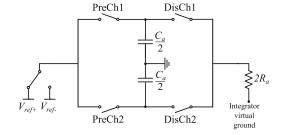

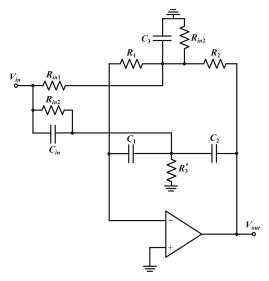

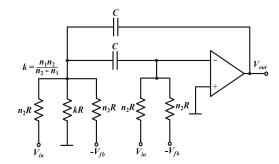

#### **DUAL SWITCHED-CAPACITOR-RESISTOR FEEDBACK**

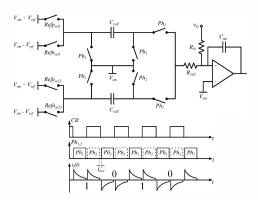

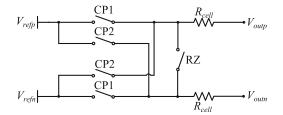

Another technique with intention of reducing the peak current of exponential feedback pulses was presented in [1][2]. The main idea is to divide the exponential pulse into two identical units. This is shown in Fig. 2.10c together with the circuit implementation. The feedback is referred to as dual switched-capacitor-resistor (DSCR) feedback. The operation is based on two capacitors that are alternately charged and discharged through a common resistor. Each discharge process lasts for  $T_s/2$ . Compared to SCR feedback, for the same time constant  $\tau = RC$  and charge Q, each capacitor must be C/2 as it stores a charge of Q/2. In order to keep the same time constant, the resistor of the DSCR implementation must be doubled which reduces the peak current by half. Furthermore, compared to SCSR feedback, the circuit implementation is simple as there is no need to implement a varying resistance.

#### FULL CLOCK PERIOD SWITCHED-CAPACITOR-RESISTOR FEEDBACK

During the course of this work, another SCR-technique has been presented in [30]. The feedback pulses together with the corresponding circuit implementation are shown in Fig. 2.10d. The technique is called full clock period switched-capacitor-resistor (FSCR) feedback because the charge is transferred during the entire clock period. This leads to both reduced peak current and improved immunity to clock jitter compared to SCR feedback. Similar to DSCR feedback, the operation is based on two capacitors that are alternately charged and discharged through a common resistor. The difference is that each of these processes lasts during the entire clock period.

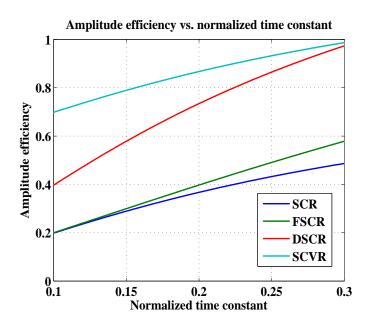

#### 2.3.3 AMPLITUDE EFFICIENCY

In 2.3.2, it became clear that exponential feedback pulses require larger peak currents than their rectangular counterparts. This also results in larger feedback coefficients compared to rectangular feedback. To more easily compare the different feedback pulses in terms of peak current, the amplitude efficiency  $\eta_a$  was defined in [26]. It is given as  $\eta_a = a_{CT1,RZ}/a_{CT1,exp}$  where  $a_{CT1,RZ}$  is the CT feedback coefficient of an RZ DAC in the first feedback branch with  $\alpha=0.5$  and  $\beta=1$

and  $a_{CT1,exp}$  is the CT feedback coefficient of an exponential DAC in the first feedback branch. Thus, a high peak current translates into a low amplitude efficiency. For NRZ feedback, which has the lowest peak current and feedback coefficient,  $\eta_a = 2$  and it is the highest amplitude efficiency that can be achieved. For all the exponential pulses covered in 2.3.2, the expression for  $\eta_a$  can be generalized as

$$\eta_a = 2R \left( \gamma + \tau_n \left( 1 - e^{-\frac{\beta - \kappa}{\tau_n}} \right) \right) \tag{2.10}$$

where R is the repetition factor (R=2 for DSCR feedback and R=1 for the other feedbacks),  $\gamma$  is the normalized length of the constant current phase for SCVR feedback,  $\tau_n=\tau/T_s$  is the normalized time constant,  $\kappa$  is the normalized time instant which indicates when exponential decay begins and  $\beta$  is the normalized time instant which indicates when exponential decay ends. This expression is used later in chapter 3 for comparison of different pulses.

| 0110501001011 | <b>-</b> 011/ 0/ 10 | <br>P. 80 10 |  |

|---------------|---------------------|--------------|--|

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

|               |                     |              |  |

### 3

### DAC non-idealities in CT $\Delta\Sigma$ modulators

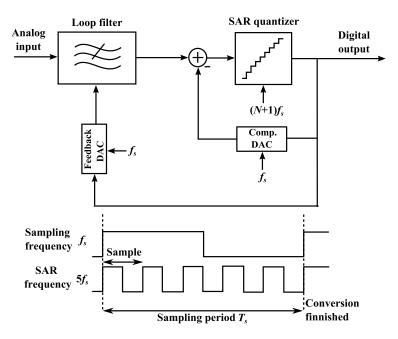

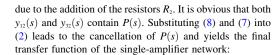

This chapter discusses the impact of feedback DAC non-idealities on the performance of CT DSMs. Since the DAC waveforms in a CT DSM are integrated over time, any errors perturbing these waveforms will affect the integrated output. There are mainly two types of DAC errors: timing errors, which include loop delay and clock jitter, and mismatch errors which affect the DAC levels and are critical when multi-bit DACs are used.

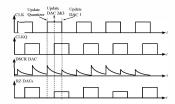

#### 3.1 EXCESS LOOP DELAY

Considering again the CT DSM in Fig. 2.8. Ideally the DACs should react immediately after the quantizer clock edge. However, in practical implementations, the finite transistor switching times causes a delay between the quantizer clock and the DAC waveforms. This delay is called excess loop delay or just loop delay. The effect of loop delay on DAC pulses is shown in Fig. 3.1 for RZ and NRZ feedback. Both pulses are shifted by  $t_d < T_s$  compared to the ideal pulse positions. The RZ pulse stays inside the sampling period and is integrated between 0 and  $T_s$  without any error. The NRZ pulse, on the other hand, is shifted into the next sampling period and the part after  $T_s$  is missed by the integrator resulting in an error. Obviously, a large loop delay is required to push the RZ pulses into the next sampling period which makes the RZ feedback less sensitive to loop delay compared to NRZ feedback.

The detrimental effect of loop delay on the performance of CT DSMs has been studied in [24] [28] [31]. It can be shown that loop delay results in coefficient mismatch which affects the NTF and increases the quantization noise. Furthermore, if the pulse is pushed into the next sampling period, the order of the modulator increases eventually leading to instability. It is also of importance to understand which of the feedback paths in a CT DSM is most sensitive to loop delay. In [32], it was shown that the first feedback path is the least sensitive to loop delay while

Fig. 3.1: RZ and NRZ pulses affected by loop delay.

**Fig. 3.2:** Addition of an extra feedback path for loop delay compensation.

the following feedback paths are successively more sensitive. The last feedback path is, however, most critical which must be considered during design.

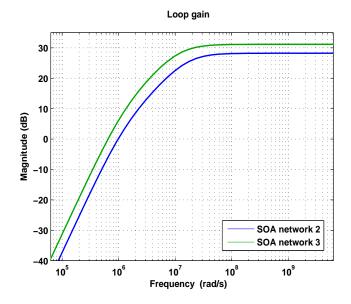

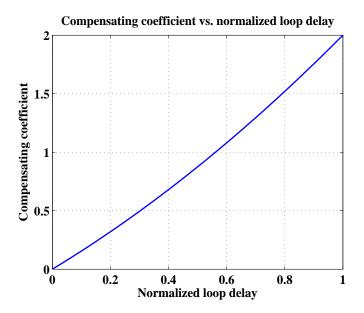

#### 3.1.1 LOOP DELAY COMPENSATION

In practical implementations, a certain amount of loop delay is required to ensure proper operation. There are two main reasons for this: First the DACs should be updated only after the quantizer has finished the conversion of the current sample, hence, there must be a delay between the quantizer and the DACs. Second, loop delay is not well controlled as it is both dependent on signal and process variations. By introducing a deliberate loop delay, which is significantly larger than the worst case delay, all the variations can be incorporated. Unfortunately, the introduced loop delay can shift the DAC pulses into the next sampling period, especially if NRZ feedback is used, increasing the order of the modulator from L to L+1. Since there are still only L feedback coefficients, it is intuitive to add an additional coefficient to restore full controllability of the system [31] [33] [34]. This method is shown in Fig. 3.2 where a fourth feedback path has been added around the quantizer. By readjusting the rest of the coefficients, loop delays up to one sampling period can be compensated by this method and full performance

#### 3.1. Excess loop delay

Fig. 3.3: Loop delay insensitive DSM architecture.

Fig. 3.4: Timing diagram of the loop delay insensitive DSM.

restored. The disadvantage is that an additional DAC and a summing operation is required where the latter is more critical as it is usually implemented using a summing amplifier. In [35], two other promising compensation techniques that address the above issues have been reviewed with some disadvantages regarding the integrator gain bandwidth (GBW) requirements and STF peaking.

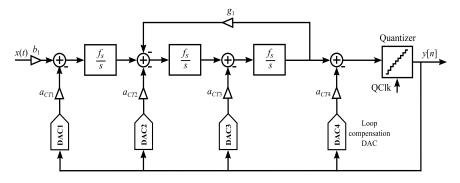

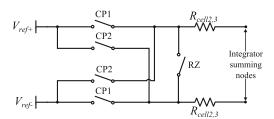

#### 3.1.2 LOOP DELAY AND RZ FEEDBACK

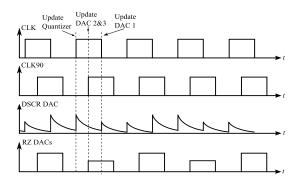

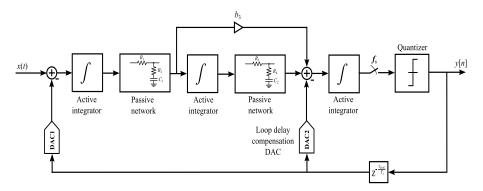

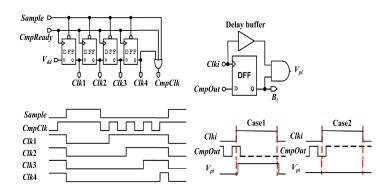

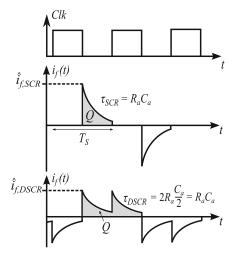

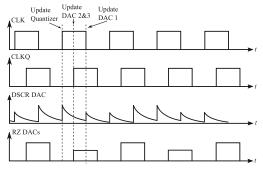

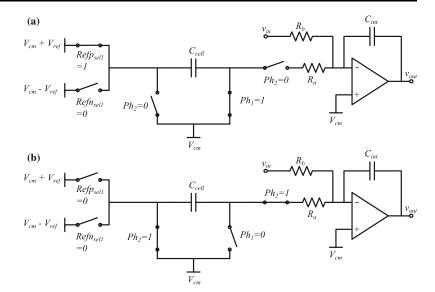

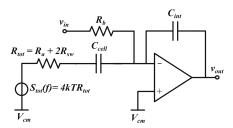

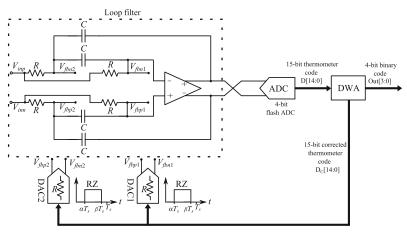

In Fig. 3.1, it was shown that RZ feedback is less sensitive to loop delay than NRZ feedback. The RZ pulse was centred in the middle of the sampling period which has two advantages: There is a  $T_s/4$  delay between the quantizer and the DAC which ensures proper operation; There is a  $T_s/4$  delay margin until the next sampling period. The above advantages suggest the use of RZ pulses in later feedback paths which are most sensitive to loop delay [32]. This has been adopted in [1][2], as shown in Fig. 3.3, where RZ pulses are used in the two last feedback paths while the first feedback path employs DSCR pulses to reduce the sensitivity to clock jitter. The overall timing diagram of the DSM is shown in Fig. 3.4. All

DACs are updated well after the beginning of the clock period which ensures that the quantizer has processed the samples before they are converted to analog form. The extension of the DSCR pulses into the next clock period is not an issue since the first feedback path is highly insensitive to loop delay.

The advantage of RZ feedback is that no additional circuit complexity is required to reduce the sensitivity to loop delay. However, the loop delays in high frequency applications can occupy significant portions of the sampling period and shift even RZ pulses into the next sampling period. In this case, the compensation techniques in 3.1.1 cannot be avoided.

#### 3.2 CLOCK JITTER

Clock jitter is caused by statistical variations of the clock edges and depends on the purity of the clock source. There are mainly two types of jitter: Independent (white) jitter and the more realistic accumulated jitter [36] [37]. If a clock waveform is affected by independent jitter, the sampling instants are given as

$$t_n = nT_s + t_{in}, \quad n = 0, 1, 2, ..., N - 1$$

(3.1)

where  $t_{jn}$  are independent and identically distributed variables (IID) which represent the random variations from the ideal sampling instants, and N is the length of the sequence  $t_n$ . In practical implementations, the clock reference is generated in a phase-locked loop (PLL) and the jittered sampling instants due to phase noise can be approximated by

$$t_n = nT_s + \sum_{i=0}^{n} t_{ji}, \quad n = 0, 1, 2, ..., N - 1.$$

(3.2)

Although  $t_{ji}$  are still IID, the actual timing deviations from ideal sampling instant are accumulated due to the summation and depend on previous values.

#### 3.2.1 JITTER ERROR SOURCES IN $\Delta\Sigma$ MODULATORS

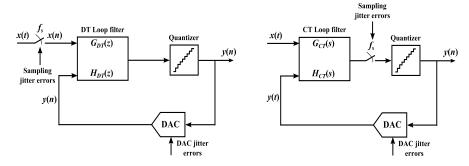

Fig 3.5 shows block diagrams of general DT and CT DSMs. The most critical errors resulting from clock jitter are generated either at the input or in the feedback DAC. These errors are as follows:

- 1. Sampling jitter errors: A jittered clock will cause the CT signal at the input of the DT DSM to be sampled at wrong time instants. This results in amplitude errors that are injected directly at the input. Sampling jitter errors also affect the CT DSM before the quantizer. However, all errors at this point are suppressed by the NTF and can usually be neglected.

- DAC jitter errors: Any timing variations affecting the clock that controls the DAC will modify the starting and ending points of the feedback pulses.

3.2. Clock jitter 23

Fig. 3.5: Jitter error sources in DT and CT DSMs.

**Figure 3.6:** DAC pulses under jitter influence. (a) Jittered DT DAC pulse, (b) Jittered CT DAC pulse.

A typical feedback pulse in a DT DSM affected by clock jitter is shown in Fig. 3.6a. The shape is exponential since the capacitors in SC circuits are discharged through switches with finite on-resistances. Most of the charge is transferred during the beginning of the sampling period and therefore the charge lost due to an error is small. This is not the case for CT DSMs as shown in Fig.3.6b for the commonly used rectangular pulses. More charge is lost due to the rectangular shape which results in high sensitivity to clock jitter.

The sampling jitter errors at the input only affect the signal while the DAC jitter errors affect the sum of the signal and the quantization noise. Since the latter contains a significantly larger power, CT DSMs are more sensitive to clock jitter than DT DSMs.

#### PROPAGATION OF DAC JITTER ERRORS

To understand the effect of DAC jitter errors in more detail, the 3rd order CT DSM in Fig. 3.7 is considered. It has been shown in several publications that jitter

Fig. 3.7: Modeling clock jitter as additive amplitude errors.

in the feedback DAC can be modelled as an additive amplitude error sequence that produces the same charge error as the timing variations due to clock jitter [38–40]. This is the purpose of the error sequences  $e_1[n] - e_3[n]$  in Fig. 3.7. The effect of these errors can be studied by referring them back to the input and then multiplying by the STF which is ideally unity in band. The following conclusions can be reached from this approach:

- 1. The DAC errors  $e_2[n]$  and  $e_3[n]$  are at least 1st-order noise shaped when referred back to the input since they are preceded by at least one integrator.

- 2. The error  $e_1[n]$ , on the other hand, is unaffected and directly injected at the input. Due to this reason, the first DAC is most critical and measures have to be taken to keep its errors from significantly affecting the performance.

These conclusions can be generalized for a loop filter of order *L*.

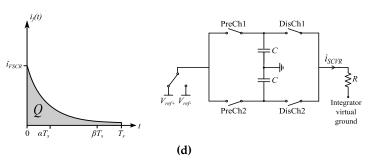

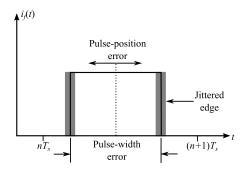

#### **PULSE-WIDTH AND PULSE-POSITION ERRORS**

There are two possible pulse errors that result from DAC jitter errors: pulse-width (PW) and pulse-position (PP) errors. These are shown in Fig. 3.8 for an arbitrary rectangular pulse. The timing error due to clock jitter  $t_j$  affects the pulse edges but it also changes the pulse-width and shifts the center of the pulse. The effect of PW and PP errors on the performance of CT DSMs has been modelled in [41][42] and can be explained with the help of the conclusions above and Fig. 3.7. PW errors from the first DAC are most critical as they are directly injected at the output without any suppression. PW errors from the rest of the DACs are not as problematic since they are at least first order noise shaped. The performance is not affected by PP errors in the first DAC since only the position of the pulse is changed and not the pulse-width. Since the integral of the pulse is not dependent

3.2. Clock jitter 25

Fig. 3.8: Pulse-width and pulse-position errors.

on the position, the impulse response remains the same. However, it can be shown that PP errors from the rest of the DACs affect both the impulse response and the remaining feedback coefficients [24] [42]. Fortunately these errors are at least first order noise shaped.

In conclusion, PW errors from the first DAC are most dominant but the errors from the other DACs should be included when modelling clock jitter since they cannot always be neglected [26].

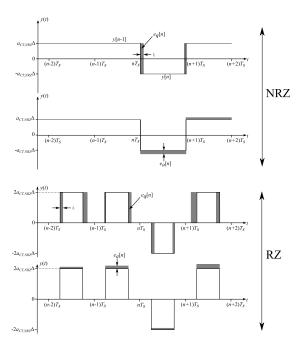

#### 3.2.2 JITTER SENSITIVITY OF RECTANGULAR PULSES

The charge errors  $e_q[n]$  due to clock jitter affecting the RZ and NRZ pulses are shown in Fig. 3.9 for single-bit feedback. The peak values of the DAC outputs are determined by the feedback coefficient  $a_{CT,RZ}$  or  $a_{CT,NRZ}$  and the quantization step  $\Delta$  which equals the DAC reference voltage in this case. It is obvious that the charge errors due to clock jitter are generated only during the transitions of the DAC output signal. The NRZ DAC output always transitions between  $a_{CT,NRZ}\Delta$  and  $-a_{CT,NRZ}\Delta$  while the RZ DAC output only transitions between  $\pm a_{CT,RZ}\Delta$  and 0. However, as discussed in 2.3.1,  $a_{CT,RZ}=2a_{CT,NRZ}$ , assuming a duty cycle of 0.5, and therefore the height of the transitions is the same in both cases. Consequently, the charge error affecting one edge of both the RZ and NRZ pulses is also the same and is given by:

$$dQ = 2a_{CT,NRZ}\Delta t_i. (3.3)$$

The difference between NRZ and RZ is the number of transitions. The RZ DAC is forced to always transition two times during every clock period even when the input data does not change. Obviously, this increases the power of the charge error compared to the NRZ DAC which transitions only when the input data changes. Due to this reason, RZ feedback is more sensitive to clock jitter than NRZ feedback.

Fig. 3.9: NRZ and RZ pulses affected by clock jitter.

#### 3.2.3 EFFECT ON THE PERFORMANCE

The equivalent additive amplitude errors  $e_a[n]$  of the charge errors  $e_q[n]$  are also shown in Fig. 3.9. These are obtained by normalizing  $e_q[n]$  with the sampling time  $T_s$  which yields for NRZ [36] [39] [43]

$$e_a[n] = (y[n] - y[n-1])\frac{t_j}{T_s}.$$

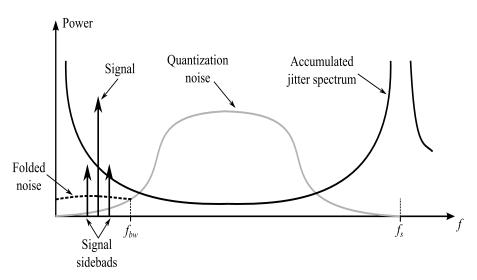

(3.4)

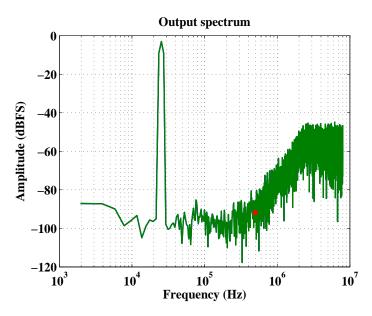

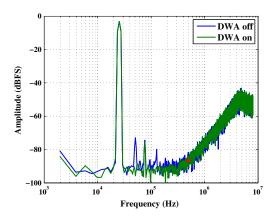

It is obvious from (3.4) that the jitter timing error  $t_j$  interacts with the output y[n] which contains both the signal and the quantization noise. The multiplication between  $t_j$  and the signal transition dy[n] = y[n] - y[n-1] translates into convolution in the frequency domain. This implies that clock jitter modulates with both the signal and the quantization noise [40] [44]. Assuming that the clock is affected by accumulated jitter given by (3.2), the impact on the spectrum of a CT DSM is shown in Fig. 3.10. The error  $e_a[n]$  consists of two main components:

1. The side-bands around the signal which are caused by modulation between jitter close to the sampling frequency and the signal. A similar effect can be observed in DT DSMs if the sampler at the input is affected by accumulated clock jitter [37] [44].

3.2. Clock jitter 27

Fig. 3.10: Effect of clock jitter in the frequency domain.

2. White noise which is a result of the modulation between wideband jitter and the quantization noise. Since the noise at high frequencies is folded down, it fills the signal band and degrades the SNR.

It has been shown in [41] that the sidebands are caused by PP errors while the white noise is caused by PW errors.

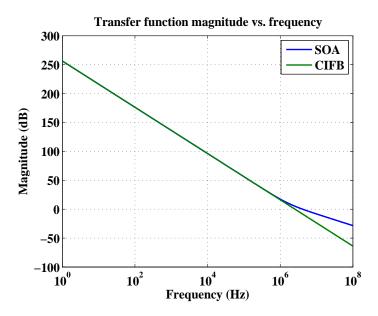

In many publications, the independent or white jitter modelled by (3.1) is also used to study the impact on the performance. The reason is that the white noise component resulting from the modulation between wideband jitter and quantization noise accounts for the increased sensitivity to clock jitter in CT DSMs. Therefore the white jitter model can be used to obtain a measure of jitter sensitivity and also results in simple expressions. It can be shown that the IBN resulting from the white jitter affecting the first DAC in a CT DSM employing single-bit rectangular pulses is given by [24]

$$IBN_{j,rec} = \frac{A_f}{OSR} \left( \frac{a_{CT1,NRZ}}{b_1} \frac{\Delta \sigma_j}{T_s} \right)^2$$

(3.5)

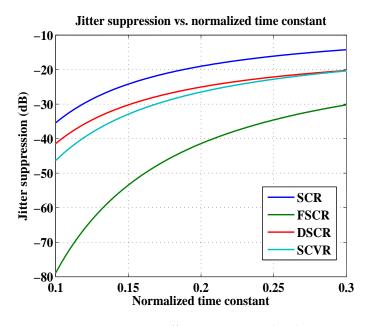

where  $a_{CT1,NRZ}$  and  $b_1$  are the first NRZ-feedback coefficient and forward coefficient (see Fig. 3.7),  $\sigma_j$  is the standard deviation of the white jitter and  $A_f$  is the activity factor which models the number of transitions for every clock cycle. It is obvious that for RZ pulses,  $A_{f,RZ}=2$  since there are always two transitions every clock cycle. For NRZ pulses,  $A_{f,NRZ}<1$  since a transition does not necessarily occur every clock cycle. In [28] it was found that  $A_{f,NRZ}\approx0.7$  for single-bit NRZ feedback and a large input signal.

To easily compare the different feedback pulses, the jitter suppression efficiency  $\eta_j$  was defined in [26] as a measure of how efficiently the white jitter is suppressed in an arbitrary DAC compared to a RZ DAC. Using (3.5) to calculate the IBN due to jitter for RZ and NRZ pulses, the jitter suppression efficiency of NRZ feedback is found as

$$\eta_j = 10 \log_{10} \frac{IBN_{j,NRZ}}{IBN_{j,RZ}} = 10 \log_{10} \frac{A_{f,NRZ}}{A_{f,RZ}} \approx -4.6 \text{dB}.$$

(3.6)

Consequently, NRZ feedback shows somewhat better jitter performance and is usually preferred in the first DAC.

#### 3.2.4 REDUCING THE EFFECT OF CLOCK JITTER

This section presents several existing methods that reduce the effect of clock jitter in CT DSMs.

#### **MULTI-BIT FEEDBACK**

The simplest way to improve the jitter performance in CT DSMs is to use multi-bit feedback. Jittered NRZ and RZ multi-bit waveforms are shown in Fig. 3.11. The NRZ waveform transitions only by one least significant bit (LSB) at most which reduces the charge errors compared to the single-bit case. This benefit is further enhanced for increased number of bits where every bit yields approximately 6 dB of jitter suppression [45]. The RZ pulses also benefit from multi-bit feedback but less than NRZ pulses. This is since the transitions are signal dependent and are usually larger than 1 LSB.

The problem with multi-bit feedback is the degraded linearity of the DACs due to mismatch. This has to be addressed in a practical implementation and will be discussed later in this chapter.

#### **MODIFICATION OF THE NTF**

In 3.2.3 it was discussed that modulation between the jitter and the quantization noise increases the IBN. Since the NTF shapes the quantization noise, the IBN due to jitter depends on the NTF. Thus a CT DSM can be made less sensitive to jitter by designing an appropriate NTF. This was examined in [39] and the analysis was further extended in [43]. The IBN due to jitter is primarily determined by the behaviour of the NTF outside the signal band since the NTF is small within the signal band. For the commonly used maximally flat NTFs, the OBG is used to fully characterize the out of band behaviour. Although an increased OBG would reduce the in-band quantization noise, the opposite is true for the out of band quantization noise which modulates with the jitter and degrades the IBN. This suggests that there is a trade-off between the in-band quantization noise and jitter and an optimum OBG exists that results in an NTF with least jitter sensitivity.

3.2. Clock jitter 29

Fig. 3.11: NRZ and RZ multi-bit pulses affected by clock jitter.

Another option is to use other NTFs than the maximally flat. These can be designed with the same in-band behaviour as the maximally-flat NTFs but different out of band behaviour which can improve the jitter sensitivity.

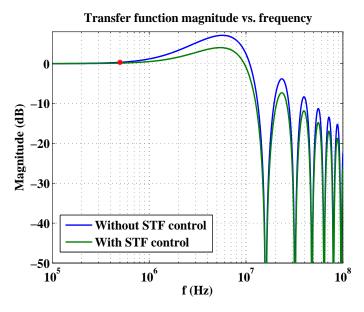

#### **EXPONENTIALY DECAYING FEEDBACK PULSES**

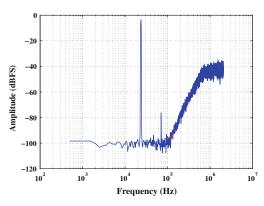

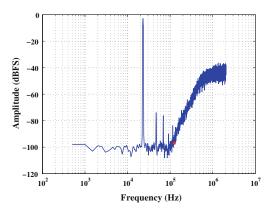

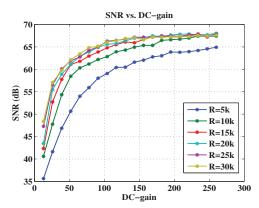

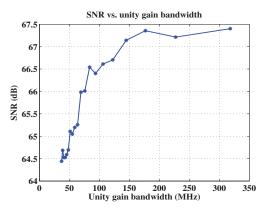

The idea behind exponential feedback in CT DSMs is to mimic the exponential discharge that takes place in DT DSMs as shown earlier in Fig. 3.6a. The charge errors due to clock jitter are significantly reduced by the shape of the pulse which accounts for the low jitter sensitivity of DT DSMs. By using the technique in at least the first DAC in CT DSMs, the white PW jitter is suppressed and the same jitter performance as in DT DSMs can be achieved [37]. Thus if the DACs are affected by accumulated jitter, the suppression of the usually dominating white jitter component would reveal the noise skirts due to PP jitter which resembles the sampling jitter in DT DSMs.