#### **Vertical InAs Nanowire Devices and RF Circuits**

| Berg, Martin |  |  |  |

|--------------|--|--|--|

2015

#### Link to publication

Citation for published version (APA):

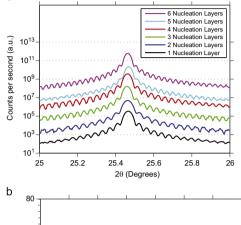

Berg, M. (2015). Vertical InAs Nanowire Devices and RF Circuits. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Lund University.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Vertical InAs Nanowire Devices and RF Circuits

Martin Berg

Doctoral Thesis Electrical Engineering Lund, September

Academic thesis which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Weekday, September 29, 2015, at  $10^{15}$  a.m. in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers väg 3, 223 63 Lund, Sweden, for the degree of Doctor of Philosophy in Electrical Engineering. The academic thesis will be defended in English.

Faculty opponent is Dr. Walter M. Weber, NaMLab, Dresden, Germany.

| Organization: LUND UNIVERSITY | Document name:                                      |

|-------------------------------|-----------------------------------------------------|

|                               | DOCTORAL THESIS                                     |

| Department of Electrical and  |                                                     |

| Information Technology        | Date of issue:                                      |

| Ole Römers väg 3              | September 2015                                      |

| 223 63 Lund                   |                                                     |

| Sweden                        | Sponsoring organisation(s):                         |

|                               | The Swedish Foundation for Strategic Research (SSF) |

| Author:                       | VINNOVA                                             |

| Martin Berg                   | The Swedish Research Council (VR)                   |

|                               | The Knut and Alice Wallenberg Foundation            |

Title and subtitle:

Vertical InAs Nanowire Devices and RF Circuits

#### Abstract.

Recent decades have seen an exponential increase in the functionality of electronic circuits, allowing for continuous innovation, which benefits society. This increase in functionality has been facilitated by scaling down the dimensions of the most important electronic component in modern electronics: the Si-based MOSFET. By reducing the size of the device, more transistors per chip area is possible. Smaller MOSFETs are also faster and more energy-efficient. In state of the art MOSFETs, the key dimensions are only few nanometers, rapidly approaching a point where the current scaling scheme may not be maintained. Research is ongoing to improve the device performance, mainly focusing on material and structural improvements to the existing MOSFET architecture. In this thesis, MOSFETs based on nanowires, are investigated. Taking advantage of the nanowire geometry, the gate can be wrapped all-around the nanowires for excellent control of the channel. The nanowires are made in a high-mobility III-V semiconductor, InAs, allowing for faster electrons and higher currents than Si. This device type is a potential candidate to either replace or complement Si-based MOSFETs in digital and analogue applications. Single balanced down-conversion mixer circuits were fabricated, consisting of three vertically aligned InAs nanowire MOSFETs and two nanowire resistors. These circuits are shown to operate with voltage gain in the GHz-regime. Individual transistors demonstrated operation with gain at several tens of GHz. A method to characterise the resistivity and metal-semiconductor contact quality has been developed, using the transmission line method adapted for vertical nanowires. This method has successfully been applied to InAs nanowires and shown that low-resistance contacts to these nanowires are possible. To optimise the performance of the device and reach as close to intrinsic operation as possible, parasitic capacitances and resistances in the device structure need to be minimised. A novel self-aligned gate-last fabrication method for vertical InAs nanowire transistors has been developed, that allows for an optimum design of the channel and the contact regions. Transistors fabricated using this method exhibit the best DC performance, in terms of a compromise between the normalised transconductance and sub-threshold swing, of any previously reported vertical nanowire MOSFET.

#### Keywords:

MOSFET, Metal-oxide-semiconductor field-effect transistor, Transistor, Vertical, InAs, III-V semi-conductor, Nanowire, Fabrication, DC, Resistor, TLM, RF, Mixer, Circuit.

| Classification system and/or index terms (if any):                       | Language:<br>English                     |                      |  |

|--------------------------------------------------------------------------|------------------------------------------|----------------------|--|

| Supplementary bibliographical information (if any)                       | ISBN (digital):<br>978-91-7623-382-5     |                      |  |

| Key title and ISSN:<br>Series of licentiate and doctoral theses, 1654-79 | ISBN (printed):<br>978-91-7623-381-8     |                      |  |

| Recipient's notes:                                                       | Number of pages:<br>160                  | Price:<br>Cost price |  |

|                                                                          | Security classification:<br>Unclassified |                      |  |

#### General Permissions:

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature: Mustin Hun

Date: 2015-08-27

# Vertical InAs Nanowire Devices and RF Circuits

Martin Berg

Doctoral Thesis Electrical Engineering Lund, September 2015

Martin Berg Department of Electrical and Information Technology Lund University Ole Römers väg 3, 223 63 Lund, Sweden

Series of licentiate and doctoral theses ISSN 1654-790X; No. 73 ISBN 978-91-7623-381-8 (printed) ISBN 978-91-7623-382-5 (digital)

#### © 2015 Martin Berg

Typeset in Palatino, Helvetica, and Goudy Initialen using  $\LaTeX 2_{\mathcal{E}}$ . Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

### **Abstract**

ECENT decades have seen an exponential increase in the functionality of electronic circuits, allowing for continuous innovation, which benefits society. This increase in functionality has been facilitated by scaling down the dimensions of the most important electronic component in modern electronics: the Si-based metal-oxide-semiconductor field-effect transistor (MOSFET). By reducing the size of the device, more transistors per chip area is possible. Smaller MOSFETs are also faster and more energy-efficient. In state of the art MOSFETs, the key dimensions are only few nanometers, rapidly approaching a point where the current scaling scheme may not be maintained. Research is ongoing to improve the device performance, mainly focusing on material and structural improvements to the existing MOSFET architecture.

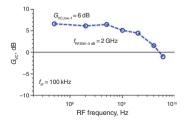

In this thesis, MOSFETs based on nanowires, are investigated. Taking advantage of the nanowire geometry, the gate can be wrapped all-around the nanowires for excellent control of the channel. The nanowires are made in a high-mobility III-V semiconductor, indium arsenide (InAs), allowing for faster electrons and higher currents than Si. This device type is a potential candidate to either replace or complement Si-based MOSFETs in digital and analogue applications. Single balanced down-conversion mixer circuits were fabricated, consisting of three vertically aligned InAs nanowire MOSFETs and two nanowire resistors. These circuits are shown to operate with voltage gain in the GHz-regime. Individual transistors demonstrated operation with gain at several tens of GHz.

A method to characterise the resistivity and metal-semiconductor contact quality has been developed, using the transmission line method adapted for vertical nanowires. This method has successfully been applied to InAs nanowires and shown that low-resistance contacts to these nanowires are possible. To optimise the performance of the device and reach as close

to intrinsic operation as possible, parasitic capacitances and resistances in the device structure need to be minimised. A novel self-aligned gate-last fabrication method for vertical InAs nanowire transistors has been developed, that allows for an optimum design of the channel and the contact regions. Transistors fabricated using this method exhibit the best DC performance, in terms of a compromise between the normalised transconductance and subthreshold swing, of any previously reported vertical nanowire MOSFET.

### Populärvetenskaplig Sammanfattning

NDER de senaste årtiondena har prestandan i elektriska kretsar växt i en rasande takt. Detta har lett till otaliga innovationer som har förbättrat samhället. Grunden till denna utveckling grundar sig i två uppfinningar: transistorn och den integrerade kresten.

Till skillnad från många andra grundläggande elektroniska komponenter har en transistor tre elektroder. En elektrisk ström skickas mellan två av elektroderna, såsom i ett motstånd, medans den tredje elektroden används för att styra hur stor denna ström ska vara. Det är detta styre, även kallad gate, som gör det möjligt att använda transistorn till digitala beräkningar, som är grunden i datorer, och till analoga applikationer, såsom radiosändare och mottagare. I en integrerad krets tillverkas idag miljardtals transistorer sida vid sida i halvledarmaterialet kisel. Att tillverka transistorerna på detta sätt är väldigt kostnadseffektivt och gör det möjligt att tillverka stora kretsar, såsom processorer. Under åren har tillverkningsmetoderna av integrerade kretsar utvecklats och lett till en förminskning av transistorernas storlek. De minsta dimensionerna i en modern transistor motsvarar idag ett par tiotal atomer i bredd. Ytterligare miniatyrisering är komplicerad och detta har lett till mycket forskning kring alternativa material och transistorstrukturer.

I detta arbete studeras användandet av halvledande nanotrådar i transistorer. Nanotrådar är cylindriska pelare i nanometerskalan. Genom att linda styret kring den nanotråden kan styrningen av strömmen göras effektivare än i konventionella transistorer. Nanotrådar kan byggas av flera halvledarmaterial, där indiumarsenid är ett av de materialen som har högst rörlighet för elektroner. Genom att kombinera materialegenskaperna av indiumarsenid med fördelarna av att nyttja en nanotråd, har välfungerande transistorer tillverkats. Under arbetets gång har InAs-transistorerna flyttats till kisel för att visa på ett kostnadseffektivt sätt att tillverka högprestandatransistorer.

### Acknowledgments

ESEARCH is not the one-man show that it was in past times. Several people have contributed to the work presented in this thesis and I would like to take this opportunity to acknowledge them.

Lars-Erik, my main supervisor; you have helped me immensely by teaching me how to see the larger picture of our research and guided me in new and exciting directions. My supervisor Erik, I thank you for sharing your gigantic knowledge about semiconductor devices and helping me to be mindful of the details. Johannes, you may not have been one of my official supervisors, but you have largely functioned as one. You deserve much recognition for your innovative ideas, making it possible to do interesting research.

My fellow PhD students in the nanoelectronics group have all contributed to this work in some way, either through fruitful discussions or in tighter collaborations. I thank you for maintaining a great research environment and would consider it an honour to work with you all again in the future. My gratitude also extends to teachers, lab staff and co-workers I have had the pleasure of encountering over the years.

Especially I would like to thank my friend Kristofer Jansson. During our years of PhD studies, you have been a great help in always offering invaluable office discussions and off-work future studies. For me, it is evident that you have all the characteristics of a true scientist. I regret that we never co-wrote a paper, but I hope that we can work together in the future and make it so.

Finally, my thoughts go to my family and my girlfriend. You have made me the person I am today and encouraged me to pursue my dreams. Your support during these years have been invaluable and even though you have not seen much of me at times, you are always with me.

Peace and long life, Martin Berg

### Contents

| Abstract                                               | 111   |

|--------------------------------------------------------|-------|

| Populärvetenskaplig Sammanfattning                     | V     |

| Acknowledgments                                        | vii   |

| Contents                                               | ix    |

| Preface                                                | xiii  |

| Structure of the Thesis                                | xiii  |

| Included Papers                                        | xiv   |

| Extraneous Papers                                      | xvi   |

| Funding Organisations                                  | xvii  |

| Abbreviations and Symbols                              | xix   |

| Abbreviations                                          | xix   |

| Greek Symbols                                          | xxi   |

| Latin Symbols                                          | xxi   |

| Functions and Operators                                | cxiii |

| INTRODUCTION                                           | 1     |

| 1: Background                                          | 3     |

| 1.1: The Emergence of Semiconductor Electronics        | 3     |

| 1.2: Metal-Oxide-Semiconductor Field-Effect Transistor | 4     |

|    | 1.3: Moore's law                                             | 6  |

|----|--------------------------------------------------------------|----|

|    | 1.4: MOSFET Evolution                                        | 6  |

|    | 1.4.1: Geometry of Transistor Channel                        | 7  |

|    | 1.4.2: Semiconductor Materials                               | 8  |

| 2: | MOSFET Parasitics and Performance Metrics                    | 11 |

|    | 2.1: Parasitics                                              | 11 |

|    | 2.1.1: Resistances                                           | 11 |

|    | 2.1.2: Capacitances                                          | 13 |

|    | 2.2: DC Metrics                                              | 13 |

|    | 2.2.1: Transconductance                                      | 13 |

|    | 2.2.2: Threshold Voltage                                     | 14 |

|    | 2.2.3: Sub-threshold Swing                                   | 15 |

|    | 2.2.4: Output Conductance                                    | 15 |

|    | 2.2.5: On-Resistance                                         | 16 |

|    | 2.2.6: Q                                                     | 16 |

|    | 2.3: RF Metrics                                              | 17 |

|    | 2.4: Normalisation                                           | 19 |

| 3: | Vertical Nanowire MOSFET Fabrication                         | 21 |

|    | 3.1: Nanowire Fabrication Technologies                       | 21 |

|    | 3.2: Progression of the Vertical Nanowire MOSFETs            | 23 |

|    | 3.3: Self-Aligned Gate-Last Fabrication Process              | 24 |

|    | 3.3.1: Nanowire Definition and Growth                        | 25 |

|    | 3.3.2: Top Metal Definition                                  | 26 |

|    | 3.3.3: Bottom Spacer                                         | 28 |

|    | 3.3.4: Channel Control                                       | 29 |

|    | 3.3.5: Gate Electrode and Drain Contact                      | 29 |

|    | 3.4: Layout                                                  | 30 |

| 4: | MOSFET Characterisation                                      | 31 |

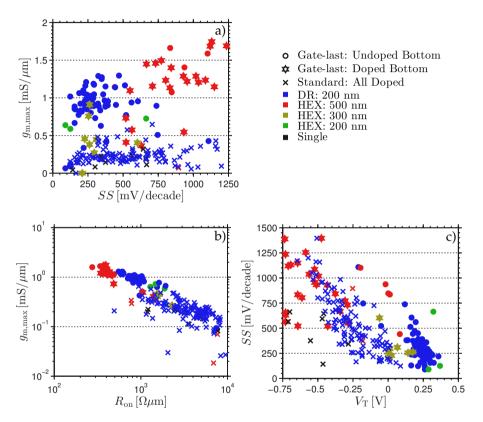

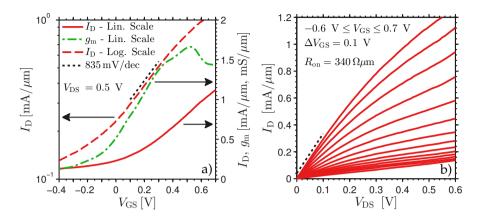

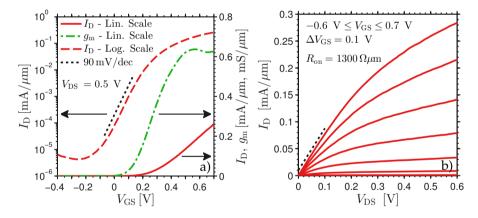

|    | 4.1: Decoupling the Transconductance and Sub-Threshold Swing | 31 |

|    | 4.2: Comparison of Three Device Architectures                | 33 |

|    | 4.3: Benchmarking                                            | 35 |

|    | 4.4: Possible Improvements                                   | 37 |

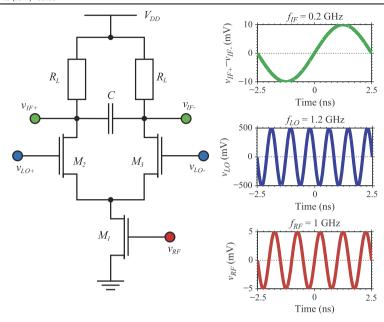

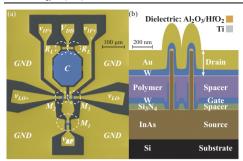

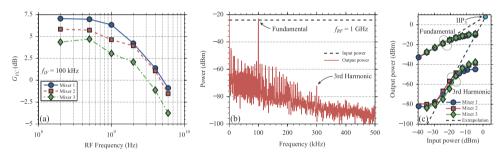

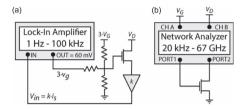

| <b>5:</b> ] | Mixer Circuit                                           | 39 |

|-------------|---------------------------------------------------------|----|

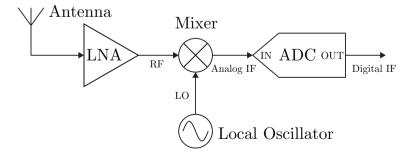

|             | 5.1: RF Front End                                       | 39 |

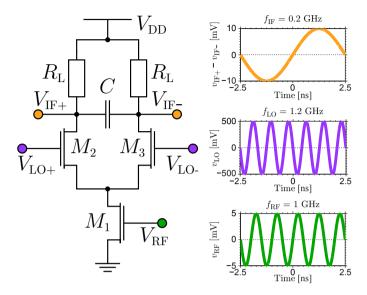

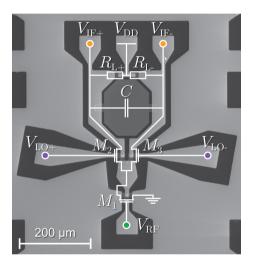

|             | 5.2: Single Balanced Down-Conversion Mixers             | 40 |

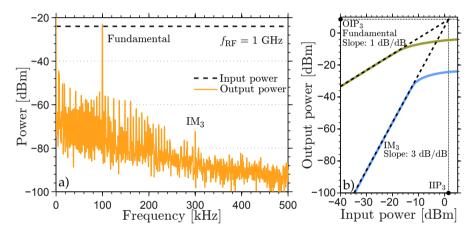

|             | 5.3: Non-Linearity                                      | 42 |

|             | 5.4: Design                                             | 43 |

|             | 5.5: Passive Components                                 | 44 |

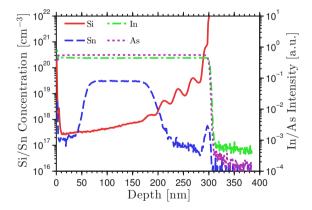

| <b>6:</b> ] | Material characterisation                               | 45 |

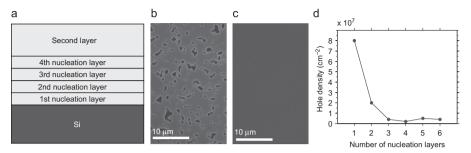

|             | 6.1: InAs Epitaxial Layers on Silicon                   | 45 |

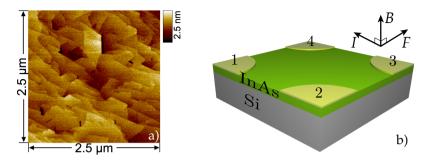

|             | 6.2: Hall Measurements Using the Van der Pauw Technique | 46 |

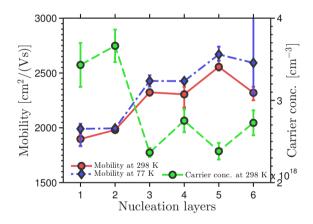

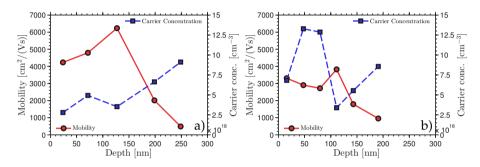

|             | 6.2.1: Hall Measurements on InAs Epitaxial Layers       | 47 |

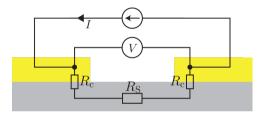

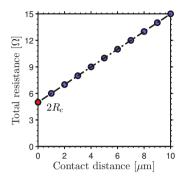

|             | 6.3: Standard TLM Model                                 | 50 |

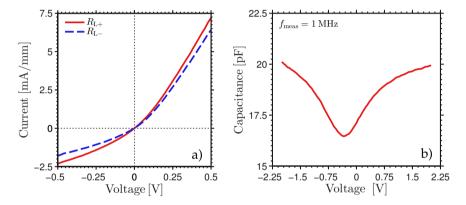

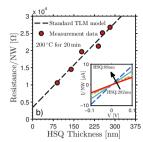

|             | 6.3.1: TLM Characterisation of InAs Epitaxial Layers    | 51 |

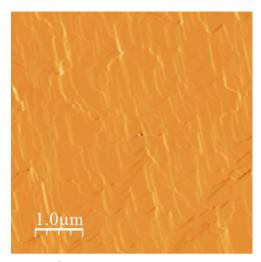

|             | 6.4: TLM on Vertical Nanowires                          | 52 |

|             | 6.4.1: TLM in the Cylindrical Geometry                  | 53 |

|             | 6.4.2: Nanowire Resistor Fabrication                    | 54 |

|             | 6.4.3: Determination of HSQ Thickness                   | 54 |

|             | 6.4.4: Results                                          | 56 |

|             | 6.4.5: Proposed Improvements For the Vertical TLM       | 56 |

| 7: (        | Conclusion and Outlook                                  | 59 |

| Bil         | oliography                                              | 61 |

| ΑF          | PPENDICES                                               | 69 |

| A:          | MOSFET Fabrication Using the Self-Aligned Gate-Last     |    |

|             | Process                                                 | 71 |

|             | A.1: Substrate                                          | 71 |

|             | A.2: Buffer Layer Growth                                | 71 |

|             | A.3: Catalyst Particle Definition                       | 72 |

|             | A.4: Nanowire Growth Preparation                        | 73 |

|             | A.5: Nanowire Growth                                    | 74 |

|             | A.6: Gate Mask Definition                               | 74 |

|             | A.7: Top Metal Formation                                | 74 |

|             | A.8: Indium Arsenide Source Pad Definition              | 75 |

| A.9: Bottom Spacer                              | 76  |

|-------------------------------------------------|-----|

| A.10: Thinning Down Channel and Gate Dielectric | 77  |

| A.11: Gate Edge Definition                      | 77  |

| A.12: Gate Pad Formation                        | 78  |

| A.13: Top Spacer Fabrication                    | 79  |

| A.14: Formation of Vias                         | 79  |

| A.15: Top Metal Deposition and Definition       | 80  |

| PAPERS                                          | 83  |

| I: Paper Title                                  | 85  |

| II: Paper Title                                 | 91  |

| III: Paper Title                                | 97  |

| IV: Paper Title                                 | 105 |

| V: Paper Title                                  | 109 |

| VI: Paper Title                                 | 119 |

| VII: Paper Title                                | 127 |

### **Preface**

HIS thesis marks the final part of five years work towards the understanding and development of nanowire-based devices and circuits. The work has been performed within the nanoelectronics group at Lund University under the supervision of Professor Lars-Erik Wernersson and Associate Professor Erik Lind.

#### STRUCTURE OF THE THESIS

This thesis is divided into three main parts: introduction, appendix, and the included papers.

#### INTRODUCTION

In this part, common concepts within the research field is defined, and explained towards the goal of further understanding the papers that are included in the thesis. The content of the different chapters are stated below.

#### 1: Background

In this chapter, a historical background to the semiconductor field is presented with the main emphasis of important innovations that are still heavily influencing the research field. The basic operation of a MOSFET is briefly discussed together with the main motivations for the work.

#### 2: MOSFET Parasitics and Performance Metrics

This chapter defines and introduces the parameters commonly used to establish the DC and RF-performance of MOSFETs. Furthermore, the typical parasitic contributions for vertical nanowire

transistors are presented.

#### 3: Vertical Nanowire MOSFET Fabrication

In this chapter, the fabrication of vertical nanowire transistors are discussed. Existing technologies before the thesis work and competing technologies is presented together with newly invented fabrication methods.

#### 4: MOSFET Characterisation

The transistor performance for several types of nanowire transistors, fabricated using different approaches are compared to highlight the importance of minimising parasitic contributions. The latest transistor results are finally benchmarked against competing technologies.

#### 5: Mixer Circuit

The importance and basic operation of a mixer circuit is explained. Specifically, the nanowire-based mixer implementation is presented and its performance metrics are defined.

#### 6: Material characterisation

This chapter presents some standard semiconductor characterisation metods, often used to characterise planar semiconductor devices. These methods are implemented on InAs epitaxial layers on silicon (Si). Furthermore, a new method for the characterisation of metal contacts on vertical nanowires are presented and discussed.

#### 7: Conclusion and Outlook

The introduction part is ended with the main conclusions from the work together with an outlook for the future of the research field and semiconductor industry.

#### APPENDICES

Further details on various aspects of the work can be found in the appendices.

## A: MOSFET Fabrication Using the Self-Aligned Gate-Last Process The exact fabrication steps for the latest generation of vertical InAs nanowire MOSFETs are reproduced.

#### PAPERS

The included papers are reproduced in the back of the thesis.

#### **INCLUDED PAPERS**

The following papers are included in this thesis and the respective published or draft versions are appended at the back of this thesis.

- Paper I: M. Berg, K.-M. Persson, O.-P. Kilpi, J. Svensson, M. Hellenbrand, E. Lind, and L.-E. Wernersson, "Gate-Last Fabrication of Enhancement Mode Vertical InAs Nanowire Transistors," *IEEE Electron Device Lett.* Manuscript

- ightharpoonup I co-fabricated the devices, collaborated on the measurements, did most of the analysis, and wrote most of the paper.

- Paper II: M. Berg, J. Svensson, E. Lind, and L.-E. Wernersson, "A transmission line method for evaluation of vertical InAs nanowire contacts," *Appl. Phys. Lett.*. Submitted manuscript in June 2015, undergoing review

- ▶ I performed almost all of the work on this paper.

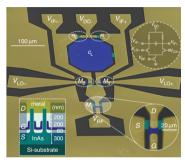

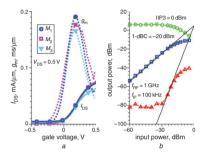

- **Paper III:** M. Berg, K.-M. Persson, J. Wu, H. SJÖLAND, E. LIND, AND L.-E. WERN-ERSSON, "InAs nanowire MOSFETs in three-transistor configurations: single balanced RF down-conversion mixers," *Nanotechnology*, vol. 25, no. 48, Dec. 2014.

- ▶ I co-fabricated the devices, did the RF and DC measurements in collaboration, did half of the analysis, and wrote the paper.

- **Paper IV:** K.-M. Persson, M. Berg, H. Sjöland, E. Lind, and L.-E. Wernersson, "InAs nanowire MOSFET differential active mixer on Si-substrate," *Electron. Lett.*, vol. 50, no. 9, pp. 682–+, Apr. 2014.

- ▶ I co-fabricated the devices, did the RF and DC measurements in collaboration, did half of the analysis, and co-edited the article.

- Paper V: K.-M. Persson, M. Berg, M. B. Borg, J. Wu, S. Johansson, J. Svensson, K. Jansson, E. Lind, and L.-E. Wernersson, "Extrinsic and Intrinsic Performance of Vertical InAs Nanowire MOSFETs on Si Substrates," *IEEE Trans. Electron Dev.*, vol. 60, no. 9, pp. 2761–2767, Sep. 2013.

- ▶ I co-fabricated the devices, collaborated on the RF and DC measurement, and co-edited the article.

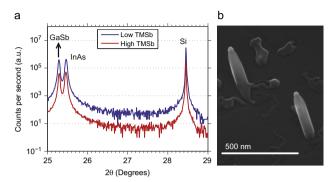

- **Paper VI:** S. G. Ghalamestani, M. Berg, K. A. Dick, and L.-E. Wernersson, "High quality InAs and GaSb thin layers grown on Si (111)," *J. Cryst. Growth*, vol. 332, no. 1, pp. 12–16, Oct. 2011.

- ► I fabricated Hall devices, did all electrical characterization and analysis, and co-wrote the article.

- **Paper VII:** S. Johansson, M. Berg, K.-M. Persson, and E. Lind, "A High-Frequency Transconductance Method for Characterization of High-κ Border Traps in III-V MOSFETs" *IEEE Trans. Electron Dev.*, vol. 60, no. 2, pp. 776–781, Feb. 2013.

- ► I co-fabricated the nanowire MOSFETs characterized and co-edited the article.

#### **EXTRANEOUS PAPERS**

The following papers are not included in the thesis, but summarise related work which I have contributed to.

- Paper viii: M. Berg, K.-M. Persson, O.-P. Kilpi, J. Svensson, E. Lind, and L.-E. Wernersson, "Self-Aligned, Gate-Last Process for Vertical InAs Nanowire MOSFETs on Si," in 2015 IEEE International Electron Devices Meeting (IEDM), Dec. 7-9, 2015, Accepted for oral presentation.

- Paper ix: M. Berg, K.-M. Persson, E. Lind, H. Sjöland, and L.-E. Wernersson, "Single Balanced Down-Conversion Mixer Utilizing Indium Arsenide Nanowire MOSFETs," in 26th Int. Conf. on Indium Phosphide and Related Materials (IPRM), May. 11-15, 2014, presented.

- Paper x: M. Berg, J. Svensson, S. G. Ghalamestani, E. Lind, and L.-E. Wernersson, "Doping Control in InAs Epitaxial Layers on Si," 39th International Symposium on Compound Semiconductors (ISCS), Aug. 27-30, 2012, poster presentation.

- **Paper xi:** K.-M. Persson, M. Berg, M. Borg, J. Wu, H. Sjöland, E. Lind, and L.-E. Wernersson, "Vertical InAs Nanowire MOSFETs with  $I_{DS}=1.34$  mA/ $\mu$ m and  $g_m=1.19$  mS/ $\mu$ m at  $V_{DS}=0.5$  V," in 70th Annual Device Research Conf. (DRC), Jun. 18-20, 2012, pp. 195–196.

- **Paper xii:** K.-M. Persson, M. Berg, E. Lind, and L.-E. Wernersson, "1/f-noise in Vertical InAs Nanowire Transistors," in 25th Int. Conf. on Indium Phosphide and Related Materials (IPRM), May. 19-23, 2013.

- Paper xiii: J. Wu, K. Jansson, A. S. Babadi, M. Berg, E. Lind, AND Wernersson, "RF-Characterization Vertical L.-E. of Wrapgated InAs/high-k Nanowire Capacitors," IEEE Trans. Elec-Dev., vol. 59, no. 10, 2733–2738, 2011. pp. Submitted manuscript in August 2015, undergoing review

- Paper xiv: S. Johansson, M. Egard, S. G. Ghalamestani, M. Borg, M. Berg, L.-E. Wernersson, and E. Lind, "RF Characterization of Vertical InAs Nanowire Wrap-Gate Transistors Integrated on Si Substrates," *IEEE Trans. Microw. Theory Tech.*, vol. 59, no. 10, pp. 2733–2738, Oct. 2011.

- Paper xv: S. Johansson, S. G. Ghalamestani, M. Egard, M. Borg, M. Berg, L.-E. Wernersson, and E. Lind, "High frequency vertical InAs nanowire MOSFETs integrated on Si substrates," in *Physica Status Solidi C*, vol. 9, no. 2, 2012.

#### **FUNDING ORGANISATIONS**

This work was supported in part by the Swedish Foundation for Strategic Research (SSF), in part by VINNOVA, in part by the Knut and Alice Wallenberg Foundation, and in part by the Swedish Research Council (VR).

### Abbreviations and Symbols

#### **ABBREVIATIONS**

ADC Analogue-to-digital converter AFM atomic force microscopy ALD atomic layer deposition Ar argon As arsenic AsH<sub>3</sub> arsine Au gold

**BDEAS** bis(diethylamino)silane **BOE** buffered oxide etch

**CB** conduction band **CVD** chemical vapour deposition

**DIW** de-ionized water **DR** double-row array

**EBL** electron beam lithography **EOT** effective oxide thickness

**GAA** gate all-around **Ge** germanium

HBT heterojunction bipolar transistor HEMT high-electron-mobility transistor HEX hexagonal array HSQ hydrogen silsesquioxane ICP-RIE inductively coupled plasma reactive-ion etching

**IF** intermediate frequency

In indium

InAs indium arsenide

InGaAs indium gallium arsenide

InP indium phosphide

**InSb** indium antimonide

**IPA** 2-propanol

ITRS international technology roadmap for semiconductors

LNA low-noise amplifier

LO local oscillator

MESFET metal-semiconductor field effect transistor

MIBK methyl isobutyl ketone

MOSFET metal-oxide-semiconductor field-effect transistor

MOVPE metalorganic vapour phase epitaxy

N<sub>2</sub> nitrogen

Ni nickel

**NW** nanowire

O oxygen

Pd paladium

PEALD plasma-enhanced atomic layer deposition

**PMMA** poly(methyl methacrylate)

**RF** radio frequency

**RIE** reactive-ion etching

**SEM** scanning electron microscopy

Si silicon

**SIMS** secondary ion mass spectrometry

Sn tin

TDMAHf tetrakis(dimethylamino)hafnium

TDMATi tetrakis(dimethylamido)titanium

**TESn** tetraethyltin

Ti titanium

**TLM** transmission line model

TMA trimethylaluminium

TMAH tetramethylammonium hydroxide

```

TMIn trimethylindium

```

**UV** ultraviolet

VLS vapor-liquid-solid

W tungsten

#### **GREEK SYMBOLS**

```

\epsilon_0~({\rm A}^2{\rm s}^4{\rm kg}^{-1}{\rm m}^{-3}) Vacuum permittivity: approximately equal 8.854\cdot 10^{-12} \epsilon_{\rm r} (unitless) Relative permittivity  \mu~({\rm m}^2/({\rm Vs}))~{\rm Mobility}  \mu_{\rm e}~{\rm Electron~mobility}  \mu_{\rm p}~{\rm Hole~mobility}  \eta (unitless) Ideality factor  \rho~(\Omega{\rm m}^2)~{\rm Resistivity}  \rho_{\rm c}~{\rm Specific~contact~resistivity}  \rho_{\rm s}~{\rm Semiconductor~resistivity}

```

#### **LATIN SYMBOLS**

```

A_{\text{VOC}} (unitless) Open-circuit voltage gain. Transistor self-gain.

```

- B (T) Magnetic field

- C (F) Capacitance

*C*<sub>DS</sub> Drain-soue capacitance

C<sub>GD</sub> Gate-drain capacitance

C<sub>GS</sub> Gate-source capacitance

$C_{\text{ox}}$  Gate oxide capacitance

**e** (unitless) Euler's number: approximately equal to 2.71828  $E_{\mathbf{g}}$  (J) Band gap energy

f (Hz) Frequency  $f_{IF}$  Intermediated frequency  $f_{LO}$  Local oscillator frequency  $f_{max}$  Maximum oscillation frequency  $f_{RF}$  Radio frequency (often input signal)

$f_{\rm T}$  Transition frequency

F (N) Lorentz force

g (S) Conductance

gd Output conductance

$g_{\rm m}$  Transconductance

$g_{m,i}$  Intrinsic transconductance

$g_{m,max}$  Maximum transconductance

$g_{m,RF}$  Transconductance of the RF-transistor

G<sub>VC</sub> (unitless) Voltage conversion gain

$h_{21}$  (unitless) Current gain from hybrid parameter

I (A) Current

*I*<sub>DS</sub> Drain-source current

*I*<sub>D</sub> Drain current

Ioff Off-current

Ion On-current

IIP<sub>3</sub> (W) Input referred third-order intercept point

IM<sub>3</sub> (W) Third-order intermodulation product

$k \text{ (m}^2 \text{ kg s}^{-2} \text{ K}^{-1}) \text{ Boltzmann constant}$

L (m) Length

Lc Contact length

L<sub>G</sub> Gate length

L<sub>T</sub> Transfer length

n (m<sup>-3</sup>) Carrier concentration

$n_s$  (m<sup>-2</sup>) Sheet carrier concentration

OIP<sub>3</sub> (W) Output referred third-order intercept point

$P_{\text{in,-1dB}}$  (W) Input referred 1 dB-compression point

q (As) Elementary charge

Q (kS dec./(Vm)) Quality factor,  $g_{m,max}/SS_{min}$

$r_{\rm NW}$  (m) Nanowire radius

$R(\Omega)$  Resistance

$R_c$  Contact resistance

**R**<sub>D</sub> Drain resistance

R<sub>G</sub> Gate resistance

R<sub>L</sub> Load resistance

**R**<sub>NW</sub> Nanowire resistance

Ron On-resistance

$R_s$  Semiconductor resistance

Rs Source resistance

$R_{SH}$  Sheet resistance

$R_{\text{tot}}$  Total resistance

s (m) Width of the center conductor in a co-planar waveguide

SS (mV/decade) Sub-threshold swing

SS<sub>min</sub> Minimum sub-threshold swing

t (m) Thickness

$t_{ox}$  Gate dielectric thickness

$t_{\rm s}$  Semiconductor thickness

T (K) Temperature

**U** (unitless) Unilateral power gain

$v_{\rm inj,e}$  (m/s) Electron injection velocity

V (V) Voltage

V<sub>DD</sub> Supply voltage

$V_{DS}$  Drain-source voltage

$V_{GS}$  Gate-source voltage

V<sub>H</sub> Hall voltage

Vout Output voltage

$V_{RF}$  AC voltage at the gate of the RF-transistor

V<sub>T</sub> Threshold voltage

w (m) Gap distance between the center conductor and the ground plane in a co-planar waveguide

$W_{\rm s}$  (m) Width of semiconductor resistor

Y (S) Admittance

Y<sub>11</sub> Short-circuit input admittance parameter

Y<sub>12</sub> Short-circuit reverse transfer admittance parameter

Y<sub>21</sub> Short-circuit forward transfer admittance parameter

$Y_{22}$  Short-circuit output admittance parameter

#### **FUNCTIONS AND OPERATORS**

**coth(·)** hyperbolic cotangent

$ln(\cdot)$  logarithm with the base e

$log_{10}(\cdot)$  logarithm with the base 10

$Re(\cdot)$  Real part of a complex number

### **INTRODUCTION**

### Background

OR many decades, the semiconductor technology have seen a tremendous dous development, with continuous improvements to established ideas or the invention of completely new devices or applications. This development has had a great impact on society through high data rate communications and computing.

This chapter consists of an overview of semiconductor history, recent developments in the field, and an introduction to the main concepts that serves as motivation for the work presented in this thesis.

#### 1.1 THE EMERGENCE OF SEMICONDUCTOR ELECTRONICS

The first transistor was fabricated in 1947 at Bell Lab [1], with the work later being awarded with the Nobel physics prize 1956. In that effort, the research team led by William Shockley tried to produce the first functioning field-effect transistor, which was already conceived on a theoretical level decades earlier. The integrated circuit was invented by Kilby in 1958 and patented in 1959 [2], with the idea that all the electronic building blocks could be fabricated on the same semiconductor substrate with metals connecting them, forming circuits. This new fabrication method allowed for many components to be manufactured simultaneously while at the same time connecting them to form more complex circuits than had previously been produced using individually package components. The vast majority of transistors used in today's integrated circuits are metal-oxide-semiconductor field-effect transistors (MOSFETs), which were invented in 1959 and patented in the following year [3].

#### 1.2 METAL-OXIDE-SEMICONDUCTOR FIELD-EFFECT TRANSISTOR

The active region of the MOSFET is called the channel and is made in a semiconductor material, with silicon (Si) being the most commonly used. Semiconductors are intrinsically highly resistive materials as they, compared to metals, have few free electrons that can flow with an applied voltage. This stems from the energy band gap  $(E_g)$  for semiconductors. The band gap, depicted in Figure 1.1a, is a range of energies, which no electrons can occupy. In an intrinsic semiconductor, almost all electrons occupy states in the valence band, but in order for the electrons to contribute to a current, they have to be excited to the conduction band. By heating or illuminating the semiconductor, electrons can absorb energy which can give them enough potential energy to instead occupy a free state in the conduction band. Another way to control the conductivity, is by a process called doping, in which atoms in the crystal lattice are substituted by atoms with more or fewer valence electrons, resulting in ndoping and p-doping, respectively. The resulting crystal thus have a surplus of mobile charges in the conduction or valence band for n-type or p-type semiconductors, respectively. One way to characterise how the semiconductor is doped, is by using the Fermi level, which illustrates the highest occupied energy level at the absolute zero temperature with some spreading occurring at elevated temperatures [4]. The Fermi levels for three types of dopings are illustrated in Figure 1.1a, denoted by  $E_{\rm Ei}$ ,  $E_{\rm En}$ , and  $E_{\rm Ep}$  for an intrinsic (undoped), n-type, and p-type semiconductor, respectively.

In a MOSFET, the semiconductor channel is covered by a conductive electrode, called the gate, which is usually made using a metal. The gate and the channel are electrically isolated from each other by an insulating dielectric layer, often an oxide, and thus building up the metal-oxide-semiconductor (MOS) structure. The semiconductor channel is contacted to two terminals at either end of the device, called the source and the drain. With an applied voltage between drain and source,  $V_{\rm DS}$ , a current,  $I_{\rm DS}$ , can flow between the electrodes, similar to a resistor. MOSFETs come in two main types: n-type, where electrons are the main charge carriers flowing in the conduction band; and p-type, where instead holes are transported in the valence band.

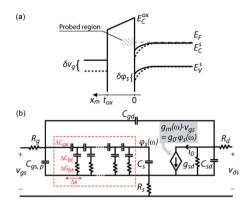

The magnitude of  $I_{\rm DS}$  is controlled, in part by  $V_{\rm DS}$ , but also with the third electrode, the gate. The MOS-structure give rise to a capacitance, which makes it possible to control the potential and thus the energy of the channel as illustrated in Figure 1.1b) for an n-type device. For a constant  $V_{\rm DS}$ , an electric field exists between the drain and source. The mobile electrons in the conduction band will flow against the field, achieving lower potential energy, i.e. flowing from source to drain. By varying the gate voltage ( $V_{\rm GS}$ ), and thus the conduction band energy alignment to the source, it is possible to tune the height of the energy barrier between the drain and source. By increasing  $V_{\rm GS}$ ,

**Figure 1.1:** a) Band diagram of a semiconductor depicting the band gap between the valence and conduction bands. Also depicted is three Fermi level energies corresponding to n-type (red), intrinsic (black), and p-type semiconductors (green). b) The on- and off-states illustrated along the nanowire channel as an energy band diagram for an n-type transistor with an applied  $V_{\rm DS}$ . Only the conduction band (CB) is shown as negligible transport occurs in the valence band.

the potential barrier is lowered, resulting in that more electrons reaches the drain and thus an increased current. If instead  $V_{\rm GS}$  is lowered, the energy barrier is raised, thus turning the transistor off [5]. This switching between the on- and off-states can be done in a very energy-efficient way in a well-designed MOSFET.

Compared to other types of transistors the MOSFET offer low leakage currents from the gate electrode, due to the insulating layer between gate and semiconductor. Other types of field-effect transistors, like high-electron-mobility transistors (HEMTs) and metal-semiconductor field effect transistors (MESFETs), uses a semiconductor barrier or a Shottky barrier, respectively, instead of an insulating oxide [6]. These barriers offer less insulation than popular gate dielectrics, which results in higher gate currents [7]. The combined properties of energy-efficient on/off-switching and low gate leakage allows for low-power computing.

#### 1.3 MOORE'S LAW

The framework established by the invention of the integrated circuit allowed for shrinking, also called scaling, of device dimensions, with the main driving force of the shrinking being more functionality per chip area and faster MOSFET switching speed. The rate of the dimension scaling led to the famous prediction coined by Gordon E. Moore in 1965 [8]. He stated that the number of transistors per chip area would double every year, which eventually was restated as a doubling in transistor count every two years in 1975 [9]. This prediction, often referenced as Moore's law, was estimated to hold for the following decade and was quickly adopted by industry as a self-fulfilling prophecy that guided the investments and goals for the semiconductor industry. The clock frequency, which roughly translates to the speed of the integrated circuit, doubled about every three years, originating from the shortening of the gate length  $(L_G)$ . This was sustained up until about 2003, when the amount of power dissipated as heat of a processor reached close to 100 W cm<sup>-2</sup>, resulting in too high requirements of circuit cooling for many commercial applications. State of the art MOSFETs could potentially run at much higher clock frequency than the 3 to 4GHz of today's highperformance processors.

Moore's law continued, but instead of clock frequency scaling, the performance increase was accomplished by increasing the number of processor "cores" on the same chip. The performance increase with the number of cores is decided by how much of the calculations that can be performed in parallel for a specific software application [10]. The prediction set up by Moore endured until about 2010, with the current scaling rate now following closer to a doubling of the number of transistors every two and a half years.

#### 1.4 MOSFET EVOLUTION

Over the decades, the MOSFET has evolved by implementing new technologies and fabrication methods when the need was present, in order to maintain Moore's scaling law. During device scaling of the gate length,  $L_{\rm G}$ , and other dimensions, the oxide capacitance,  $C_{\rm ox}$ , is increased to maintain electric field patterns within the device [11]. One way to accommodate this is by a decrease in the oxide thickness,  $t_{\rm ox}$ , evident from

$$C_{\rm ox} = \frac{\epsilon_0 \epsilon_{\rm r}}{t_{\rm ox}}.\tag{1.1}$$

At thicknesses of just a few nm, however, quantum mechanical tunnelling of charge carriers through the oxide becomes noticeable, resulting in higher off-state leakage and thereby less energy efficient computing. One way to solve the tunnelling problematic is by increasing the relative permittivity,  $\epsilon_r$ , of the oxide layer, allowing for a thicker oxide layer.

Indeed, the problem with tunnelling was observed during the 1990s, which saw the evolution from  $SiO_2$ , with  $\epsilon_r = 3.9$ , to  $SiO_xN_y$ , which has a  $\epsilon_r$  ranging between 3.9 and 7.8 with the higher numbers obtained with high nitride content. In the years following 2007, materials with even higher  $\epsilon_r$ , such as  $HfO_2$ , were implemented and continually used by industry. The relative dielectric constant may also be denoted by  $\kappa$ , thus the term high- $\kappa$  dielectrics.

#### 1.4.1 GEOMETRY OF TRANSISTOR CHANNEL

Until 2011, MOSFETs were more or less planar devices with a gate controlling the channel potential from one direction, similar to the schematic illustration of Figure 1.2a.

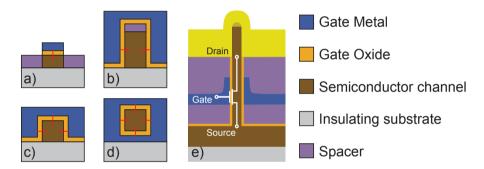

**Figure 1.2:** Schematic cross-sectional illustration of different nanowire channel geometries: a) Single-sided gate, b) Fin-, c) Tri-gate-, d) lateral gate-all-around, and e) vertical gate-all-around MOSFET. The red arrows illustrate the direction of the electric field at the different surfaces. For the first four lateral architectures, the source and drain regions are situated normal to the paper.

The last couple of years have seen the introduction of multi-gate devices, in which the gate controls the channel potential from several surfaces. Such a device offers better electrostatic control of the semiconductor channel as the capacitance to channel volume ratio is larger. Furthermore, the extra gate area have only a small impact on the device area as seen from the top, i.e. the footprint area, resulting in a large performance boost per device area. A multigate device, with gate control from two sides, is called a Fin-FET (Figure 1.2b), with the name originating from the shape of the semiconductor channel sticking up from the planar substrate. A tri-gate MOSFET (Figure 1.2c), is a similar device but the gate also operates on the top side. Compared to a Fin-FET, a tri-gate is almost symmetrical in terms of the length of the gating

sidewalls. The tri-gate structure has recently been introduced in industrial fabrication.

The best electrostatic gate control is obtained by surrounding the gate around the entire semiconductor channel [12,13], often referred to as a gate all-around (GAA) design. In this gate architecture the semiconductor is referred to as a nanowire, which can either be aligned laterally or vertically, with the lateral version illustrated in Figure 1.2d. The potential benefit of using a vertical structure is the possibility of designing  $L_G$  and metal contact lengths without affecting the device footprint area. A vertical nanowire MOSFET is shown in Figure 1.2e with an overlay of the circuit symbol to illustrate the different electrodes.

#### 1.4.2 SEMICONDUCTOR MATERIALS

There is a number of material properties that determine the intrinsic performance of the transistors. For a long-channel device ( $L_G$  longer than the mean free path) an important parameter is the charge carrier mobility,  $\mu$ , which is a measure of how easily mobile charges are transported in the material. With an applied electric field, the charges are accelerated to a certain velocity, with charges in a material with high mobility reaching higher velocities. For a short-channel device, where ballistic carrier transport dominates, the velocity is instead set by the injection velocity. The velocity of the charges correlate roughly to the current flowing through the device.

In today's semiconductor industry, MOSFETs are based on Si, which has been extensively used for over 50 years with its main advantage over many other semiconductors being the formation of a native oxide with a good oxide-semiconductor interface. Germanium (Ge) is used in industry [14,15] in the contact regions to achieve a higher channel mobility, and therefore higher currents. Si and Ge does not, however, have the highest mobilities for all semiconductors as observed in Table 1.1.

Here, the electron and hole mobilities are provided together with the electron injection velocity for a number of semiconductors extensively studied in transistors. The highest electron mobilities,  $\mu_{\rm e}$ , can be found in compound semiconductors, consisting of group III and group V elements, such as indium antimonide (InSb) and indium arsenide (InAs) with values of about  $70\,000\,{\rm cm^2\,V^{-1}\,s^{-1}}$  and  $40\,000\,{\rm cm^2\,V^{-1}\,s^{-1}}$ , respectively. Both of these semiconductors have narrow band gaps and a light electron mass, which translates to fast carriers under an applied electric field. Generally, hole mobilities,  $\mu_{\rm p}$ , are much lower than the electron mobilities with Ge having the highest hole mobility at about  $1900\,{\rm cm^2\,V^{-1}\,s^{-1}}$ . At small semiconductor dimensions, as in ultra-scaled MOSFETs, the surface to volume ratio is large, which results in increased surface scattering. For these small dimensions, the

| J. 111/j/c                            |                                                                           | <u>, , , , , , , , , , , , , , , , , , , </u>                                                                                                                                   |

|---------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mu_{\rm e}$ $[{ m cm}^2/({ m Vs})]$ | $\frac{\mu_{\rm p}}{[{\rm cm}^2/({\rm Vs})]}$                             | $v_{\rm inj,e}$ at $L_{\rm G}$ = 30 nm [cm/s]                                                                                                                                   |

| 1400                                  | 450                                                                       | $1.2\cdot 10^7$                                                                                                                                                                 |

| 40000                                 | 500                                                                       | $3.7 \cdot 10^{7}$                                                                                                                                                              |

| 12000                                 | 300                                                                       | $2.8 \cdot 10^{7}$                                                                                                                                                              |

| 3900                                  | 1900                                                                      |                                                                                                                                                                                 |

| 70000                                 | 1000                                                                      |                                                                                                                                                                                 |

| 7000                                  | 1000                                                                      |                                                                                                                                                                                 |

| 8500                                  | 400                                                                       |                                                                                                                                                                                 |

|                                       | μ <sub>e</sub> [cm <sup>2</sup> /(Vs)]  1400 40000 12000 3900 70000 70000 | $\begin{array}{c c} \mu_e & \mu_p \\ [cm^2/(Vs)] & [cm^2/(Vs)] \\ \hline 1400 & 450 \\ 40000 & 500 \\ 12000 & 300 \\ 3900 & 1900 \\ 70000 & 1000 \\ 7000 & 1000 \\ \end{array}$ |

**Table 1.1:** Intrinsic semiconductor parameters where  $\mu_e$  is the electron mobility,  $\mu_p$  is the hole mobility, and  $v_{\text{inj},e}$  is the electron injection velocity [16].

mobility is much smaller than the bulk values reported in Table 1.1, but the general trend still applies. It is therefore assumed that higher performance, in terms of speed and energy efficiency, can be expected by utilizing these high-mobility materials [17].

III-V semiconductors are expected to be introduced in the large-scale semi-conductor industry in a couple of years with the International Technology Roadmap for Semiconductors (ITRS) predicting the introduction occuring already in 2018 [18]. The III-V semiconductors would be utilized for the n-type transistor with its p-type companion probably based on Ge. An expected speed boost of 50% and 40% lower switching energy compared to high-performance Si, is expected for this change of material. It is likely that trigate MOSFETs will be the geometry of choice with a possibility for GAA nanowires a few years later.

# MOSFET Parasitics and Performance Metrics

N order to characterise MOSFET devices, different standardised metrics have been established. Some of the metrics are shared with other types of transistors, whereas others are mostly attributed only to field-effect transistors. Characterisation and the extraction of various performance metrics are integral to the general understanding of the intrinsic device and its limitations. Furthermore, it allows for benchmarking to other similar devices [19], and imperative for circuits design. The performance of a transistor is always limited by parasitic elements [20]. By analysing the transistor characteristics and by device modelling, knowledge about these parasitics can be extracted, and in turn making it possible to limit their impact.

In this chapter, an overview of the parasitics in vertical nanowire MOSFETs is presented followed by a walkthrough of some of the most important MOSFET performance metrics, used throughout the thesis.

#### 2.1 PARASITICS

In vertical nanowire MOSFETs, the main parasitic contributions come from resistances and capacitances in series or in parallel with the active device. The vertical architecture has been shown, through modelling, to be highly competitive compared to alternative device layouts for highly scaled device dimensions [21].

#### 2.1.1 RESISTANCES

Parasitic resistances connected to the active device limit the effective voltage drops across the device. Their effect on the transistor performance can vary depending on their linearity, at what frequency the device is run at, and

#### temperature.

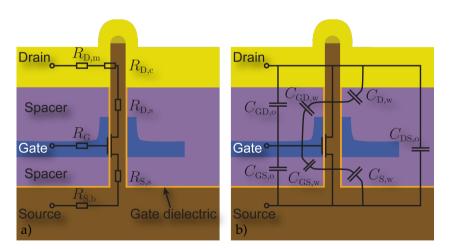

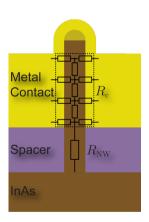

The major parasitic resistance contributions for a vertical nanowire MOS-FET can be seen in Figure 2.1a. Several resistive elements are positioned in series with the intrinsic transistor, resulting in voltage division and therefore a lower effective  $V_{\rm DS}$  over the channel. On the drain side, the resistance can be divided into three elements  $R_{\rm D,m}$ ,  $R_{\rm D,c}$ , and  $R_{\rm D,s}$ ; corresponding to resistive paths in the metal electrode, the metal-semiconductor interface, and the ungated spacer segment, respectively. Similar elements can be found on the source side, where the ungated spacer and the bottom electrode (in this case the same semiconductor as the nanowire), are the main contributors. At high frequency operation, the gate resistance  $R_{\rm G}$  can have an impact on the performance. It should be noted that these resistive elements are not necessarily linear in terms of their *I-V* characteristics. Especially metal-semiconductor contacts often exhibit non-ohmic behaviour.

One of the main benefits of a vertically aligned MOSFET is the potential for longer metal contacts without affecting the footprint area. This applies to contacts implemented on both the top and bottom part of the nanowire. An additional benefit originates from the growth of nanowires, where high-quality materials of different lattice constants can be grown on top of each other. This allows for the use of specific materials for ungated or contact regions in order to minimise the series resistances.

**Figure 2.1:** Schematic images of a vertical nanowire MOSFET with an overlay illustrating the effective transistor together with a) parasitic resistance elements and b) parasitic capacitances. In the subscripts; s, m, b, w, and o, denotes contact, metal, bottom, wire, and overlap, respectively.

#### 2.1.2 CAPACITANCES

Capacitances in the vertical nanowire architecture can be divided into two groups: overlap capacitances and fringing capacitances between electrodes or between electrode and nanowire (Figure 2.1b). The overlap capacitances can easily be calculated by the overlapping area, the permittivity of the spacer layers and their thicknesses, assuming a parallel-plate model. More complicated is the calculation of fringing capacitances, but approximative analytical calculations are easily performed [22]. For accurate determination of the capacitances, the entire electric field need to be solved numerically [23].

The parasitic capacitances can be minimised by a large spacing between electrodes, resulting in thick spacer layers and instead large series resistances. An optimum spacer layer thickness exist which is dependent on the permittivity of the spacer layer and resistivity of the ungated regions. The best possible spacer is air, with its low relative permittivity of close to 1. Other materials are, however, usually used for mechanical stability, such as SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>. The overlap capacitance is most effectively minimised by the reduction of the overlap between source, gate, and drain. This was successfully performed in [24] using electron beam lithography (EBL).

#### 2.2 DC METRICS

The drain current,  $I_{\rm D}$ , of a MOSFET is, in common-source configuration, dependent on both the gate-source voltage,  $V_{\rm GS}$ , and the drain-source voltage,  $V_{\rm DS}$ . One way to depict  $I_{\rm D}$ , would be as three-dimensional graphs with  $V_{\rm DS}$  and  $V_{\rm GS}$  occupying the two remaining axes. Three-dimensional graphs are, however, more difficult to grasp than their two-dimensional counterparts. Commonly, the current is instead illustrated using two different two-dimensional graphs: the output characteristics,  $I_{\rm D}$  represented as a function of  $V_{\rm DS}$  at a constant  $V_{\rm GS}$ , and the transfer characteristics,  $I_{\rm D}$  as a function of  $V_{\rm GS}$  at a constant  $V_{\rm DS}$ .

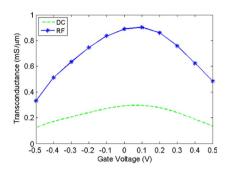

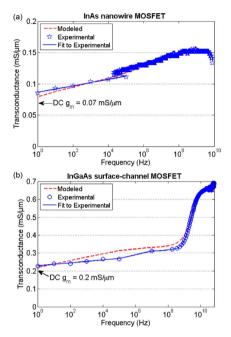

#### 2.2.1 TRANSCONDUCTANCE

An important transistor metric, especially in radio frequency (RF) applications, is the transconductance,  $g_{\rm m}$ . It is defined as the partial derivative of the drain current with respect to the gate-source voltage, defined as

$$g_{\rm m} \equiv \frac{\partial I_{\rm D}}{\partial V_{\rm GS}}.\tag{2.1}$$

From this definition, the transconductance can be understood as the current amplification acquired with a small-signal voltage on the gate electrode. In a circuit, the resulting current can drive some load, e.g. a resistor, and thus

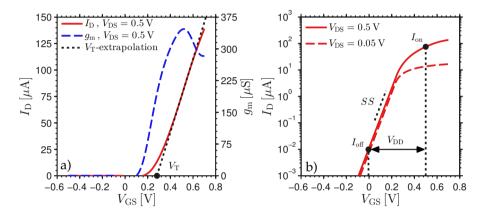

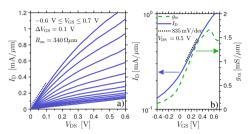

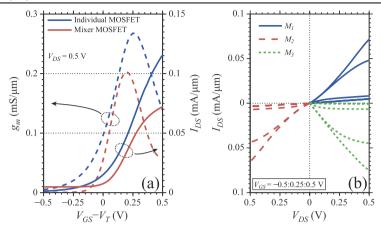

give rise to a voltage or power at the load. A high transconductance is favourable in RF-circuits as it allows for high low-frequency gain. For digital applications, a high  $g_{\rm m}$  is important since a lower supply voltage,  $V_{\rm DD}$ , could be used while maintaining a certain drive current. A typical transconductance curve, together with its corresponding transfer characteristics, is illustrated in Figure 2.2a. A clear peak is observed, often denoted as  $g_{\rm m,max}$ .

**Figure 2.2:** Transfer characteristics of a MOSFET in linear scale, a), and logarithmic scale, b). The MOSFET characteristics are calculated from a simple MOSFET-model with added series resistances on both the source and drain side. a)  $g_{\rm m}$  is shown together with  $I_{\rm D}$  and  $V_{\rm T}$  is extrapolated from  $g_{\rm m,max}$ . b) The sub-threshold characteristics are seen as the linear slope for  $V_{\rm GS} < 0.2\,\rm V$ . SS corresponds to the slope of the exponentially increasing current in logarithmic scale. Also plotted in b) are  $I_{\rm off}$  corresponding to  $100\,\rm nA\,\mu m^{-1}$  and its related  $I_{\rm on}$  for a  $V_{\rm DD}$  of  $0.5\,\rm V$

#### 2.2.2 THRESHOLD VOLTAGE

The threshold voltage,  $V_{\rm T}$ , signifies the gate-source voltage in which the transistor transitions between the on-state and the off-state. This transition does not occur abruptly and its extraction from measurement data can thus be somewhat arbitrary. One popular extraction method is to linearly extrapolate the current in the saturation region as a function of  $V_{\rm GS}$ . The transfer characteristics does not, however, necessarily follow a linear relation to  $V_{\rm GS}$  and often the maximum transconductance peak is used as the anchor point for the extrapolation. An example of a  $V_{\rm T}$ -extraction can be seen in Figure 2.2a.

#### 2.2.3 SUB-THRESHOLD SWING

One of the most important MOSFET metrics for digital applications is the sub-threshold swing (SS). At gate voltages below the threshold voltage,  $I_D$  increases exponentially with  $V_{GS}$  as seen in Figure 2.2b. On a logarithmic scale, the linear current increase is called the sub-threshold slope which is the inverse of the sub-threshold swing. SS is modelled as a thermionic injection over a potential barrier and expressed as

$$SS = \frac{1}{\log_{10}(e)} \frac{\eta kT}{q}.$$

(2.2)

Here q is the elementary charge, k is the Boltzmann constant, T is the temperature, e is Euler's number and  $\eta$  is the ideality factor, which can vary from the ideal value of 1 to higher values. For an ideal MOSFET, with  $\eta = 1$ , an SS of 60 mV decade<sup>-1</sup> is obtained at room temperature. The sub-threshold current increases by a factor of 10 (one decade) over a  $V_{GS}$  range of 60 mV.

SS determines the effectiveness of the MOSFET as a switch. A steep subthreshold slope results in a large ratio between the on-current,  $I_{\rm on}$ , and the off-current,  $I_{\rm off}$ . If SS deviates too much from the ideal  $60\,\mathrm{mV}$  decade<sup>-1</sup>, either the off-state leakage increases or on-state current decreases dependent on the choice of threshold voltage. An increased off-state leakage current results in high power dissipation, which is unacceptable for large circuits, e.g. a processor, or circuits aimed for low-power applications. The international technology roadmap for semiconductors (ITRS) states a maximum  $I_{\rm off}$  of  $10\,\mathrm{nA}\,\mathrm{\mu m}^{-1}$  for high-performance devices, whereas MOSFETs aimed for low-power implementations have maximum  $I_{\rm off}$  of  $10\,\mathrm{nA}\,\mathrm{\mu m}^{-1}$  [18].  $I_{\rm on}$  is determined by the supply voltage, and is ideal as high as possible for faster switching or higher operation frequency of the MOSFETs.

#### 2.2.4 OUTPUT CONDUCTANCE

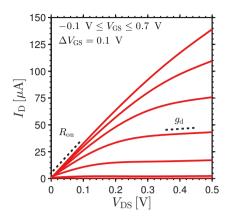

A typical MOSFET output characteristic can be seen in Figure 2.3. The output conductance,  $g_d$ , is defined in the same way as  $g_m$ , as a partial derivative, but now instead with respect to  $V_{DS}$ ,

$$g_{\rm d} \equiv \frac{\partial I_{\rm D}}{\partial V_{\rm DS}}.$$

(2.3)

The output conductance is important to consider for RF applications. In a common-source stage, e.g. in an amplifier, the low-frequency open-circuit voltage gain,  $A_{V,OC}$ , can be calculated as

$$A_{\text{V,OC}} = \frac{-g_{\text{m}}}{g_{\text{d}}}.$$

(2.4)

**Figure 2.3:** Output characteristics of a MOSFET, based on the same model as depicted in the transfer characteristics of Figure 2.2.  $g_d$  is defined as the derivative of the output characteristics, with  $R_{on}$  being defined only in linear region.

The ratio of (2.4) is commonly referred to as the transistor self gain and can be utilised to find optimum biasing conditions or benchmarking against other MOSFETs. Ideally, the saturation current is independent of  $V_{\rm DS}$ , resulting in infinite  $A_{\rm V,OC}$ , but is in reality finite for scaled MOSFETs due to the influence of the drain voltage on the potential in the channel.

#### 2.2.5 ON-RESISTANCE

The current in a MOSFET is very dependent on its extrinsic series resistances. One way to estimate the magnitude of these resistances is to extract the on-resistance,  $R_{\rm on}$ , which is defined as the inverse output conductance at a  $V_{\rm DS}$  of 0 V. For ohmic series resistances, the contribution of the extrinsic resistances to the total device resistance is higher for larger  $V_{\rm GS}$ . As seen in the output characteristics of Figure 2.3,  $R_{\rm on}$  varies as a function of  $V_{\rm GS}$  but approaches, for large voltages, a saturated value corresponding to the total series resistance of the device.

#### 2.2.6 Q

One popular performance metric, that takes both on- and off-performance into account, is the quality value [25],

$$Q \equiv \frac{g_{\text{m,max}}}{SS_{\text{min}}} = \left[\frac{\text{mS/mm}}{\text{mV/dec.}}\right] = \left[\frac{\text{kS dec.}}{\text{Vm}}\right]. \tag{2.5}$$

The metric is usually presented without a unit and it is understood that the

units and normalisation used during its calculations is defined as in (2.5).

#### 2.3 RF METRICS

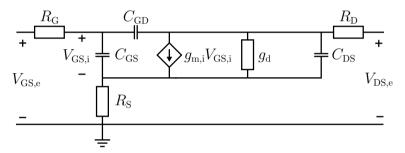

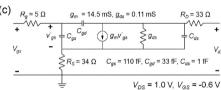

A transistor is very much a non-linear component but can be linearised if the operation window is small enough. This means that a transistor biased at some fixed DC voltages with superposed time-varying signals of very small amplitudes, can be described by linear circuit elements, such as resistors, capacitors etc. One such simple model is depicted in Figure 2.4 [26–28].

**Figure 2.4:** A small-signal model of a MOSFET built up by linear circuit elements. The device is illustrated as a 2-port with the input between gate and source (left), and output between drain and source (right). Due to series resistances, the extrinsic voltages ( $V_{\rm GS,e}$  and  $V_{\rm DS,e}$ ) are not identical to the intrinsic voltages ( $V_{\rm GS,i}$  and  $V_{\rm DS,i}$ ). More circuit elements can be incorporated for a more accurate description of the high-frequency performance.

At the core of the transistor is the voltage-controlled current source with a parallel series resistor,  $g_d$ . With transistors operating at high frequencies, capacitances start to affect the performance of the device. Dependent on the device architecture, these capacitances can sometimes be lumped together into three elements situated between the three electrodes:  $C_{GS}$ ,  $C_{GD}$ , and  $C_{DS}$ . In series with the device, out towards the electrodes are the three series resistances ( $R_G$ ,  $R_D$ , and  $R_S$ ) situated, which together with the capacitances affect the internal voltage nodes and, in turn, the performance. The values for all these components vary with the chosen DC bias and some, like  $g_m$ , can potentially be frequency dependent.

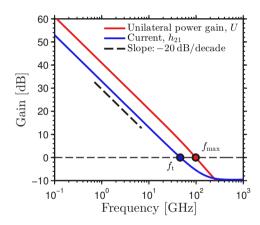

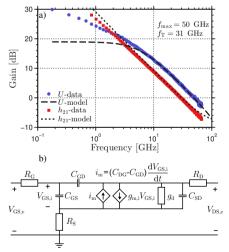

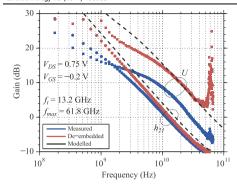

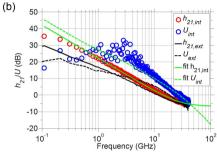

For high-frequency MOSFET characterisation, mainly two metrics are important in terms of benchmarking:  $f_T$  and  $f_{max}$ . The first,  $f_T$ , is the transition frequency, which is defined as the frequency, at which the current gain reaches unity, i.e. 0dB. It can be estimated using (2.6) or extracted from a measurement of the device scattering parameters (S-parameters) followed by calculation of the hybrid parameter  $h_{21}$ , i.e. the current gain, with an

extraction illustrated in Figure 2.5. The current gain is observed to fall with a constant decay of 20 dB decade<sup>-1</sup>, originating from the first order filtering of the RC-network.

$$\frac{1}{2\pi f_{\rm T}} = \frac{C_{\rm GS} + C_{\rm GD}}{g_{\rm m,i}} + \frac{(C_{\rm GS} + C_{\rm GD})(R_{\rm S} + R_{\rm D})g_{\rm d}}{g_{\rm m,i}} + (R_{\rm S} + R_{\rm D})C_{\rm GD} \qquad (2.6)$$

$$f_{\rm max} = \frac{1}{2} \sqrt{\frac{f_{\rm T}}{2\pi C_{\rm GD}(R_{\rm S} + R_{\rm G}) + \frac{g_{\rm d}(R_{\rm S} + R_{\rm G})}{f_{\rm T}}}} \qquad (2.7)$$

$$f_{\text{max}} = \frac{1}{2} \sqrt{\frac{f_{\text{T}}}{2\pi C_{\text{GD}} (R_{\text{S}} + R_{\text{G}}) + \frac{g_{\text{d}}(R_{\text{S}} + R_{\text{G}})}{f_{\text{T}}}}}$$

(2.7)

Figure 2.5: Current gain and unilateral power gain as a function of frequency, calculated using the small-signal MOSFET model shown in Figure 2.4, with the correspondingly extracted  $f_T$  and  $f_{max}$ .

The second important RF-metric is the maximum oscillation frequency,  $f_{\text{max}}$ . It is defined as the frequency at which the unilateral power gain,  $U_{\gamma}$ reaches 0 dB. The maximum oscillation frequency can roughly be calculated from  $f_{\rm T}$  using (2.7). The unilateral power gain is defined as the power gain when any feedback path for the power is neglected. From measured Sparameters, transformed to Y-parameters, U can be calculated as

$$U = \frac{|Y_{21} - Y_{12}|^2}{4 \left( \text{Re}(Y_{11}) \text{Re}(Y_{22}) - \text{Re}(Y_{12}) \text{Re}(Y_{21}) \right)},$$

(2.8)

with an example characteristic illustrated in Figure 2.5.

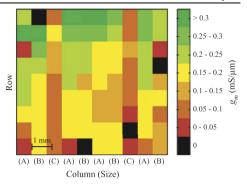

#### 2.4 NORMALISATION

In benchmarking of transistors, the metrics such as  $g_{m,max}$  and  $I_{on}$ , are often normalised to the gate width. For a planar surface channel MOSFET architecture, the transistor performance and footprint area scales linearly with the width of the device. In this case, for a fixed gate length, this corresponds to a normalisation to the gate area. Often in industrial applications, it is the performance per unit area that matters, which means that vertical stacking of lateral transistors or vertically aligned nanowires have competitive advantages compared to other device architectures.

In multi-gate MOSFET architectures, the normalisation is performed in the same way, to the gate width. For nanowire MOSFETs, normalisation is performed with the circumference, and for tri-gate MOSFETs, using the sum of the three gates, as though they have surface channels. For these multi-gate devices, the gating from different sides extends through the semiconductor so that more of the current is transported deeper in the semiconductor. When comparing a tri-gate to a GAA device, the electrostatic control is improved in the GAA-case. This improvement is, however, less than the added gated width [12], resulting in an underestimated performance for GAA devices.

# Vertical Nanowire MOSFET Fabrication

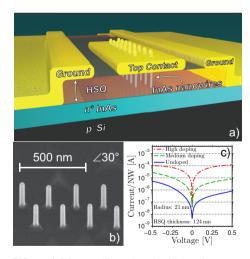

ERTICAL nanowires allow a possible development path for future ultrascaled MOSFETs, promising a high scalability in terms of metal contacts and gate lengths. In this chapter, an overview of established techniques for the fabrication of vertical nanowire MOSFETs is given, followed by a brief description of the improvements established during the thesis work. In the main part of the chapter, the fabrication steps of a self-aligned gate-last process for vertical nanowires are presented.

#### 3.1 NANOWIRE FABRICATION TECHNOLOGIES

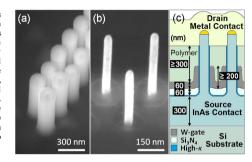

Nanowires can be formed either using various epitaxial growth methods or etching processes. One popular way is to grow nanowires using metalorganic vapour phase epitaxy (MOVPE), exploiting the vapor-liquid-solid (VLS) growth mechanism. Using this method, metallic catalyst particles, usually gold (Au), are positioned on a semiconductor substrate, serving as a template with the same crystal direction as the one wanted for nanowire growth. Growth is initiated by the introduction of metal-organic precursor molecules at elevated temperatures. At some specific temperatures and pressures, the liquid catalyst particle absorbs more vapour-phase semiconductor material than what is possible in equilibrium, making the metal catalyst go into a supersaturated state. Due to this unstable state, precipitation of solid semiconductor material is started and a nanowire is grown from the semiconductor template [29].

Another way of growing nanowires is through selective area growth. Small openings are made in a dielectric mask down to the semiconductor substrate and, similarly as when using catalyst particles, precursor molecules are

utilised at elevated temperatures with growth only taking place inside the openings [30,31]. An extension of the same approach is to grow the nanowires inside dielectric tubes [32].

Instead of growth, nanowires can also be formed by wet or dry etch procedures. One possible way is to start from a high-quality substrate, which could consist of various doping profiles and different semiconductors. An etch mask is deposited onto this substrate, defined using high-resolution lithography such as EBL. The etch mask is easiest created in a positive resist, such as hydrogen silsesquioxane (HSQ) [33, 34]. Finally, the substrate is etched using a highly anisotropic dry etch process, forming the nanowires underneath the etch mask [35].

All of these nanowire fabrication technologies are applicable to silicon (Si) substrates, which is required for low-cost device fabrication [36], but consideration has to be taken to the bottom contact to the nanowire devices. If III-V nanowires are used on Si, which also functions as a bottom contact, charge transport will occur over a potential barrier at the III-V/Si heterojunction [30,31]. This appear as a highly non-linear resistance in series with the active device, limiting  $I_{\rm D}$  and increasing  $g_{\rm d}$ . A potential barrier can also arise from other substrates than Si, e.g. indium phosphide (InP). The heterojunction barrier can, however, be avoided altogether by fabricating a metal bottom contact to the nanowires [37] or by growing the nanowires on a planar buffer layer, on top of Si, of the same material as the nanowires [28].

The most studied materials for vertical nanowire MOSFETs are Si, InGaAs, and InAs. Si has the main advantage of being directly compatible with established fabrication technologies in large-scale nanoelectronics. InGaAs and InAs are of interest, together with many other III-V semiconductors, for their advantageous transport properties, thus allowing for faster and more energy efficient electronic circuits.

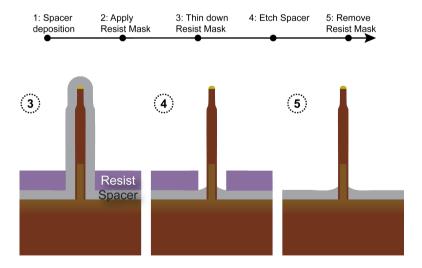

Fabrication of vertical MOSFET devices distinguishes itself from lateral device fabrication in that the device, in general, has to be built up from the bottom to the top. After establishing the bottom contact scheme, i.e. using a metal socket or contacting via the substrate, a spacer is formed using an organic (e.g. a baked photoresist), a dielectric (e.g.  $SiO_2$  [38]), an exposed HSQ [39] or a high- $\kappa$  oxide film [34]. This spacer should be thin in order to minimise the access resistance, although thick enough to not limit the device high frequency operation by parasitic capacitances [23]. For devices optimised for DC performance, using a high- $\kappa$  is an attractive choice as it requires no extra fabrication steps other than those already needed to deposit the gate stack. After high- $\kappa$  deposition, a gate metal is formed and the gate length defined either using an etch mask [40] or by the deposition thickness [38]. Before the top contact is fabricated, a second spacer is needed that usually consist of an organic spin-on resist [31, 34, 38, 40] or electron-beam defined

HSQ [39].

In lateral fabrication, device dimensions, such as the gate length, contact regions etc., are defined through lithographic processes. In a vertical geometry, however, these geometries roughly translates to the thickness of the different layers constituting the device. The thickness precision of evaporation, sputtering, atomic layer deposition (ALD), and chemical vapour deposition (CVD) can be very good, but this does not necessarily translate to the thickness precision close to the nanowires. Dependent on the deposition method, nanowires can shadow their surroundings due to the high aspect ratio of the structure. Often material deposition on the nanowire sidewalls is unwanted and need to be removed, resulting in extra fabrication steps. As a general observation, vertical fabrication is more challenging than lateral because of less developed fabrication methods.

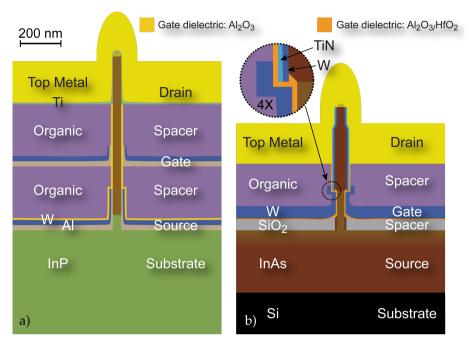

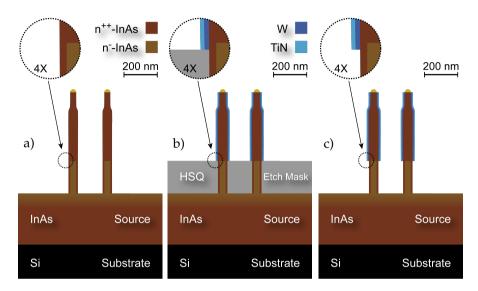

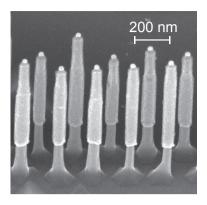

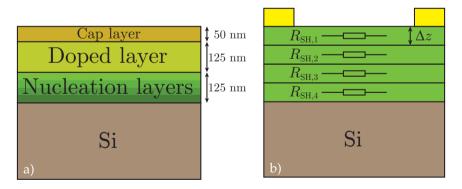

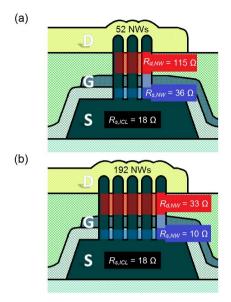

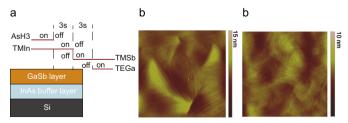

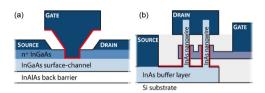

#### 3.2 PROGRESSION OF THE VERTICAL NANOWIRE MOSFETS

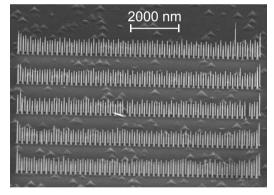

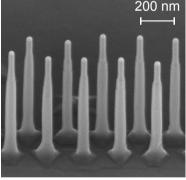

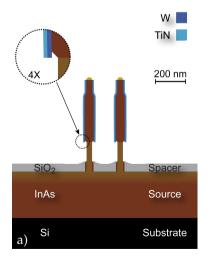

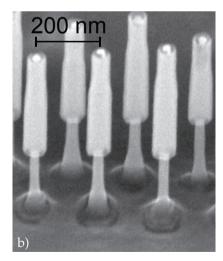

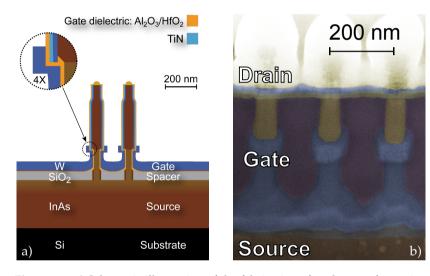

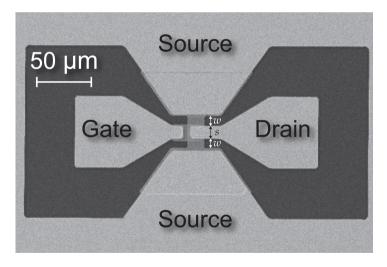

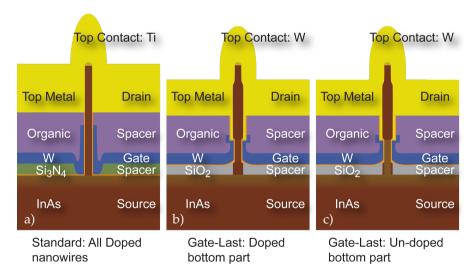

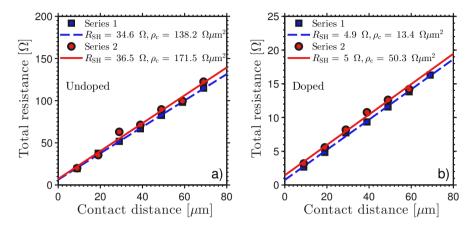

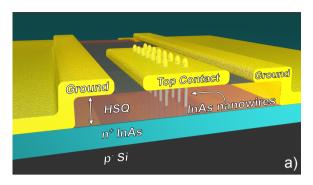

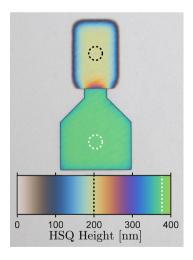

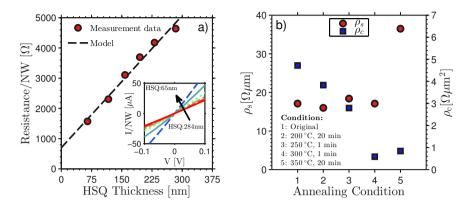

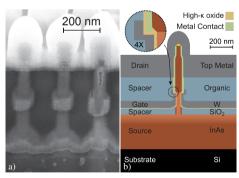

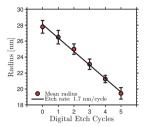

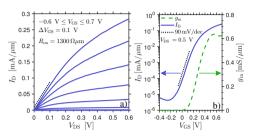

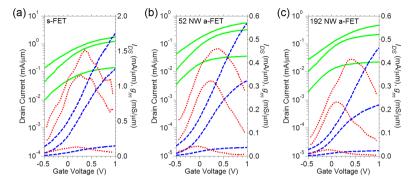

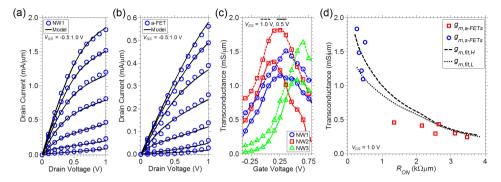

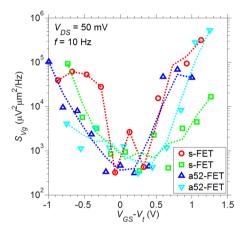

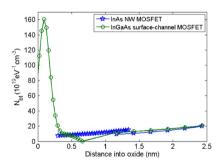

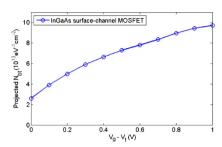

At the start of the work leading up to this thesis, vertical InAs nanowire MOSFETs had already been fabricated with an RF-compatible layout [37,38,41,42], with the cross-sectional device architecture illustrated in Figure 3.1a. This is compared to a newer version of the same MOSFET in Figure 3.1b. The overall structure of the two types is the same: one source contact in the bottom, a drain contact in the top, and the gate situated in the middle with spacer layers in-between.