#### **Integrated Control and Real-Time Scheduling**

Cervin, Anton

2003

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Cervin, A. (2003). Integrated Control and Real-Time Scheduling. [Doctoral Thesis (monograph), Department of Automatic Control]. Department of Automatic Control, Lund Institute of Technology (LTH).

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 18. Dec. 2025

### Integrated Control and Real-Time Scheduling

# Integrated Control and Real-Time Scheduling

Anton Cervin

Department of Automatic Control Lund Institute of Technology Lund, April 2003

Department of Automatic Control Lund Institute of Technology Box 118 SE-221 00 LUND Sweden

ISSN 0280-5316 ISRN LUTFD2/TFRT--1065--SE

$\ \odot$  2003 by Anton Cervin. All rights reserved. Printed in Sweden by Bloms i Lund Tryckeri AB. Lund 2003

### **Abstract**

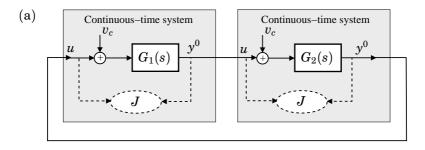

The topic of the thesis is codesign of flexible real-time control systems. Integrating control theory and real-time scheduling theory, it is possible to achieve higher resource utilization and better control performance. The integration requires new tools for analysis, design, and implementation.

The problem of scheduling the individual parts of a control algorithm is studied. It is shown how subtask scheduling can reduce the input-output latency in a set of control tasks. Deadline assignment under different scheduling policies is considered.

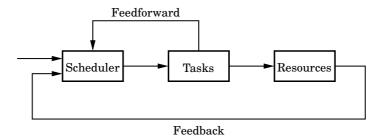

A feedback scheduling architecture for control tasks is introduced. The scheduler uses feedback from execution-time measurements and feedforward from workload changes to adjust the sampling periods of a set of control tasks so that the combined performance of the controllers is optimized.

The Control Server, a novel computational model for real-time control tasks, is presented. The model combines time-triggered I/O with dynamic, reservation-based task scheduling. The model provides short input-output latencies and minimal jitter for the controllers. It also allows control tasks to be treated as scalable real-time components with predictable performance.

Two MATLAB-based toolboxes for analysis and simulation of real-time control systems have been developed. The Jitterbug toolbox evaluates a quadratic cost function for a linear control system with timing variations. The tool makes it possible to investigate the impact of delay, jitter, lost samples, etc., on control performance. The TrueTime toolbox facilitates detailed cosimulation of distributed real-time control systems. The scheduling and execution of control tasks is simulated in parallel with the network communication and the continuous process dynamics.

### Acknowledgments

First, I would like to thank my supervisor Karl-Erik Årzén. He, together with Klas Nilsson and Ola Dahl, wrote the original proposal for the research project "Integrated Control and Scheduling". Never short on good ideas, Karl-Erik has been an excellent advisor since the day I started my graduate studies. He has also been a constant supplier of good music over the years.

This thesis would not have turned out half as good without the help from several of my fellow PhD students and colleagues. Johan Eker is the co-author of a staggering 50% of my publications. Together, we have worked on the simulator, feedback scheduling, and, most recently, the Control Server. Dan Henriksson has been the main implementer of the new version of the simulator, called TrueTime. Bo Lincoln has implemented the Jitterbug analysis toolbox. Thank you all for the great work!

It has been wonderful to work at the Department of Automatic Control in Lund, where the people are always friendly and helpful. The professors, the secretaries, and the technical staff keep the department running very smoothly. I would especially like to thank the founder of the department, Karl Johan Åström, who lured me into the field of automatic control and encouraged me to become a PhD student. Also, I would like to thank my co-supervisors Bo Bernhardsson and Per Hagander.

During my studies, I have had the opportunity to visit colleagues abroad. I would like to thank Professor Lui Sha at the Department of Computer Science, University of Illinois at Urbana-Champaign for much inspiration and visits on two separate occasions. I would also like to thank Professor Edward Lee at the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley for a research visit in 2001.

This research project has been a collaboration between the Department of Automatic Control and the Department of Computer Science at Lund Institute of Technology. It has been a pleasure to work together with Klas Nilsson, Patrik Persson, and Sven Gestegård Robertz.

The work in this thesis has been supported by ARTES, a real-time research network in Sweden funded by SSF. I have enjoyed visits to several summer schools, graduate student conferences, and other activities organized by ARTES over the past five years.

ARTES has provided funding for several conference trips and research visits. A travel grant from the Royal Physiographic Society in Lund is also gratefully acknowledged.

Finally, I would like thank my family, friends, fellow lindy hoppers, poker buddies, etc., for making my life so enjoyable! A special thank you goes out to Matilda for her love and inspiration.

Anton

# Contents

| 1. | Intr | oduction                                | 11 |  |  |  |

|----|------|-----------------------------------------|----|--|--|--|

|    | 1.1  | Motivation                              | 11 |  |  |  |

|    | 1.2  | The Codesign Problem                    | 12 |  |  |  |

|    | 1.3  | Goals and Contributions                 | 14 |  |  |  |

|    | 1.4  | An Introductory Example                 | 17 |  |  |  |

|    | 1.5  | Outline and Publications                | 29 |  |  |  |

| 2. | Bacl | Background                              |    |  |  |  |

|    | 2.1  | Introduction                            | 33 |  |  |  |

|    | 2.2  | Real-Time Scheduling Theory             | 35 |  |  |  |

|    | 2.3  | Control Loop Timing                     | 41 |  |  |  |

|    | 2.4  | Control and Scheduling Codesign         | 50 |  |  |  |

| 3. | Sub  | task Scheduling                         | 52 |  |  |  |

|    | 3.1  | Introduction                            | 52 |  |  |  |

|    | 3.2  | Task Models                             | 55 |  |  |  |

|    | 3.3  | Deadline Assignment                     | 56 |  |  |  |

|    | 3.4  | Latency Analysis                        | 59 |  |  |  |

|    | 3.5  | Implementation                          | 61 |  |  |  |

|    | 3.6  | An Example                              | 62 |  |  |  |

|    | 3.7  | Conclusion                              | 66 |  |  |  |

| 4. | Feed | dback Scheduling                        | 67 |  |  |  |

|    | 4.1  | Introduction                            | 67 |  |  |  |

|    | 4.2  | A Feedback Scheduling Architecture      | 70 |  |  |  |

|    | 4.3  | Case Study 1: Hybrid Controllers        | 72 |  |  |  |

|    | 4.4  | Optimal Resource Distribution           | 81 |  |  |  |

|    | 4.5  | Case Study 2: Linear Controllers        | 85 |  |  |  |

|    | 4.6  | EDF as a Feedback Scheduling Mechanism? | 94 |  |  |  |

|    | 47   | Conclusion                              | 95 |  |  |  |

#### Contents

| <b>5.</b> | The (  | Control Server                   | 96  |

|-----------|--------|----------------------------------|-----|

|           | 5.1    | Introduction                     | 96  |

|           | 5.2    | The Model                        | 98  |

|           | 5.3    | Control and Scheduling Codesign  | 101 |

|           | 5.4    | CS Tasks as Real-Time Components | 104 |

|           | 5.5    | Feedback Scheduling              | 107 |

|           | 5.6    | Implementation                   | 109 |

|           | 5.7    | Control Experiments              | 112 |

|           | 5.8    | Conclusion                       | 114 |

| 6.        | Analy  | ysis Using Jitterbug             | 116 |

|           | 6.1    | Introduction                     | 116 |

|           | 6.2    | System Description               | 117 |

|           | 6.3    | Internal Workings                | 123 |

|           | 6.4    | Examples                         | 126 |

|           | 6.5    | Conclusion                       | 138 |

| 7.        | Simu   | lation Using TrueTime            | 139 |

|           | 7.1    | Introduction                     | 139 |

|           | 7.2    | Overview                         | 141 |

|           | 7.3    | The Kernel Block                 | 142 |

|           | 7.4    | The Network Block                | 149 |

|           | 7.5    | Examples                         | 153 |

|           | 7.6    | Conclusion                       | 161 |

| 8.        | Conc   | lusion                           | 164 |

| ••        | 8.1    | Summary                          | 164 |

|           | 8.2    | Suggestions for Future Work      | 166 |

| Ap        | pendix | K                                | 168 |

|           | _      | Calculation in Example 3.1       | 168 |

|           |        | of Theorem 4.2                   | 170 |

| Rot       | forona |                                  | 179 |

# 1

### Introduction

#### 1.1 Motivation

Real-time control plays an important part in modern technology. For example, a CD or DVD player could never operate without its feedback control system. Engine management systems in modern cars rely heavily on real-time computations and feedback control to improve performance, reduce fuel consumption, and minimize the amount of pollutant emissions. As the capacity of microcontrollers is increasing and the cost is decreasing, more and more functionality is realized in software. In an embedded control system, a control task is typically executing in parallel with several other tasks, including other control tasks. This puts focus on scheduling, i.e., the choice of which task to execute at a given time. Since the beginning of the 1970s, the academic interest in real-time scheduling has been very large. Very little of this work has, however, focused on control tasks. On the other hand, digital control theory, with its origin in the 1950s, does not address the problem of shared and limited resources in the computing system. Instead, it is commonly assumed that the controller executes as a simple loop in a dedicated computer.

Real-time scheduling is sometimes dismissed as a non-problem. With ever more powerful computers, it can be argued that most timing problems can be solved by upgrading the CPU to a later and faster model. While this might be true in some cases, developers of embedded systems will testify that they are always struggling to add yet another function to an already heavily loaded processor. To keep production costs down, manufacturers of consumer products tend, of course, to use the most inexpensive hardware possible. Only in extreme applications, such as nuclear power plants, can the cost of the computing hardware be neglected in the overall development costs.

This work aims at achieving the best possible control performance from limited computing resources. To accomplish this goal, integration of the control design and the real-time scheduling design is necessary. Today, the design of a real-time control system is typically a two-step procedure: control design followed by real-time design. Moreover, the steps are often carried out in relative isolation and by engineers with different backgrounds. The control engineer designs and evaluates the control algorithms assuming a very simple model of the computing platform. The computer scientist schedules the controllers together with other tasks and makes design trade-offs without really knowing the controller timing requirements. The isolated development introduces conservatism and leads to non-optimal solutions.

There is a strong trend towards flexibility in real-time control. In the past, developers have relied on static analysis and design, knowing that the controllers would execute on deterministic hardware and in a predictable environment. Today, both hardware and operating systems tend to be commercial-off-the-shelf (COTS) products, sometimes poorly specified, and typically optimized for high average-case performance rather than predictable worst-case performance. Controllers are more frequently being treated as software components, expected to work in different configurations and being subject to on-line upgrades. Furthermore, modern control systems are often distributed systems, where sensors, controllers, and actuators are located in different nodes in a network. A distributed system is more flexible in nature but also more nondeterministic. Communication protocols may introduce timing variations that influence both the control performance and the task scheduling in the various computer nodes.

#### 1.2 The Codesign Problem

Successful development of a real-time control system requires codesign of the computer system and the control system. The computing platform must be dimensioned such that all functionality can be accommodated, and the controllers must be designed taking the hardware limitations into account. The computer system has many important aspects (numerics, memory, I/O, network, power consumption, etc.). This thesis focuses on the scheduling of control tasks in the CPU.

The *control and scheduling codesign problem* can be informally stated as follows:

Given a set of processes to be controlled and a computer with limited computational resources, design a set of controllers and schedule them as real-time tasks such that the overall control performance is optimized.

An alternative view of the same problem is to say that we should design and schedule a set of controllers such that the least expensive implementation platform can be used while still meeting the performance specifications.

The nature and the degree of difficulty of the codesign problem for a given system depend on a number of factors:

- The real-time operating system. What scheduling algorithms are supported? How is I/O handled? Can the real-time kernel measure task execution times and detect execution overruns and missed deadlines?

- The scheduling algorithm. Is is time-driven or event-driven, priority-driven or deadline-driven? What analytical results regarding schedulability and response times are available? How are task overruns handled? What scheduling parameters can be changed on-line?

- The controller synthesis method. What design criteria are used? Are the controllers designed in the continuous-time domain and then discretized or is direct discrete design used? Are the controllers designed to be robust against timing variations? Should they actively compensate for timing variations?

- The execution-time characteristics of the control algorithms. Do the algorithms have predictable worst-case execution times? Are there large variations in execution time from sample to sample? Do the controllers switch between different internal modes with different execution-time profiles?

- Off-line or on-line optimization. What information is available for the off-line design and how accurate is it? What can be measured online? Should the system be able to handle the arrival of new tasks? Should the system be re-optimized when the workload changes? Should there be feedback from the control performance to the scheduling algorithm?

The problems studied in this thesis will assume a real-time operating system that supports dynamic scheduling algorithms (fixed-priority or earliest-deadline-first scheduling). We will mainly consider scheduling of linear controllers whose performance is evaluated by quadratic cost functions. When on-line optimization is introduced, it will be assumed that the execution times of the tasks can be measured, and that the scheduling parameters can be changed on-line.

#### 1.3 Goals and Contributions

Control theory and real-time systems theory have evolved as separate fields during the last couple of decades. There is clearly a lack of common understanding between the two research communities and no well-defined design interface. In the control community, the real-time system is viewed as a platform on which the controller can be trivially implemented. In the real-time systems community, a controller is viewed as a piece of code characterized by three fixed parameters: a period, a computation time, and a deadline. This thesis aims at bridging the gap between the two research areas. For this purpose, new tools and techniques for analysis, design, and implementation are needed. The goals and contributions of the thesis are outlined below.

#### **New Analysis Tools**

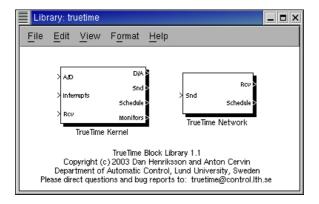

There is a need for better understanding of what happens when a controller is implemented and scheduled as a real-time task. For this purpose, two MATLAB-based analysis tools have been developed: TrueTime<sup>1</sup> and Jitterbug<sup>2</sup>. The tools can be used at early design stages to determine how sensitive controllers are to scheduling-induced delays and jitter. They can also be used at the implementation stage for trade-off analysis between the tasks.

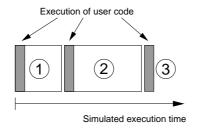

TrueTime, which is based on MATLAB/Simulink, is used for detailed co-simulation of the computer system and the control system. In the tool, time is added as a new dimension to the control algorithms. The controllers are executed in a real-time operating system, which is simulated in parallel with the continuous-time plant dynamics. An arbitrary scheduling algorithm can be used, and the code can be simulated on a time-scale of choice. The tool is very general and can be used to investigate, for instance, the influence of various scheduling algorithms on the control performance. Although it falls outside the main scope of this thesis, TrueTime can also be used to simulate distributed control systems and evaluate different communication protocols from a control perspective.

Simulation is a very useful tool for control systems design but there are limitations. The user may lack exact knowledge of task execution in the target system. Also, very long simulation times may be needed to draw conclusions about performance and stability. As an alternative, Jitterbug can be used for analysis of simple models of real-time control systems. In the tool, the timing variations introduced by the real-time operating system are modeled by statistical delay distributions. Given a

<sup>&</sup>lt;sup>1</sup>Available at http://www.control.lth.se/~dan/truetime/

<sup>&</sup>lt;sup>2</sup>Available at http://www.control.lth.se/~lincoln/jitterbug/

linear control system and a timing model, the tool analytically computes a quadratic performance index, or *cost function*. By evaluating the cost function for a wide range of timing parameters, the designer can investigate how sensitive the control loop is to timing variations. Jitterbug also supports frequency-domain analysis in the form of spectral density calculations.

#### More Detailed Scheduling Analysis

For a given system, the analysis tools above may indicate that controller timing is a critical issue. The implementation may introduce latency and jitter that deteriorate the performance and force the developer to use a more expensive CPU. It can then be valuable to perform a more detailed scheduling analysis in order to reduce the latencies. The remaining delay can be compensated for using control theory.

One way to reduce the input-output latency in a controller is to split the control algorithm into two parts: Calculate Output and Update State. The Calculate Output part should only contain the operations necessary to produce a control signal, while the rest of the operations should be postponed to the Update State part. In the thesis, it is shown how the two parts can be scheduled as subtasks in order to reduce the input-output latency for a set of controllers. The control performance improvements come at the expense of a slightly more complex implementation.

#### Introduction of Feedback in the Computing System

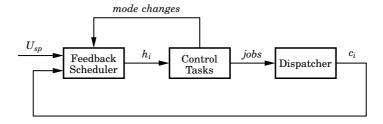

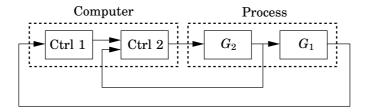

Real-time systems are typically designed using static (off-line) analysis techniques, even if dynamic scheduling algorithms are used in the target system. To guarantee that all deadlines are met, the analysis is based on worst-case assumptions about task arrival rates and execution times. In systems where the workload changes over time, this approach may lead to low average resource utilization. By the introduction of feedback in the computing system, a less pessimistic analysis can be carried out on-line, allowing the computing resources to be better exploited. An illustration of a general feedback scheduling structure is given in Figure 1.1.

In the thesis, we study controllers whose computational demands vary over time. A traditional, static worst-case analysis would in these cases lead to low average-case CPU utilization and possibly poor control performance. A feedback mechanism is proposed that rescales the sampling periods of the controllers based on execution-time measurements. A feedforward path is also introduced, such that the control tasks can inform the scheduler that they are about to consume more resources. The controllers may adjust their parameters according to the current timing conditions. The proposed mechanism could be implemented in a standard operating system, provided that it supports execution-time measurements.

Figure 1.1 A general feedback scheduling structure. The resources are distributed among the tasks based on feedback from the actual resource use. The tasks can be use feedforward to notify the scheduler about changes in their resource demands.

#### A Novel Computational Model

The scheduling techniques outlined above are mainly based on the fixed-priority scheduling algorithm, which is the standard scheduling mechanism in commercial real-time operating systems (RTOS). This algorithm has several drawbacks, however, from both control and scheduling points of view. First, it introduces very irregular and hard-to-analyze delay patterns in the control loops. Second, the processor cannot be fully utilized, and the utilization bound depends on the task parameters in a non-trivial way. All of this makes for an extremely complicated control and scheduling codesign problem. In practice, the true performance of the controller cannot be known until it is running in the target system.

To remedy this problem, we propose a novel computational model for real-time control tasks, called the Control Server. The model assumes a real-time operating system that supports the earliest-deadline-first (EDF) scheduling algorithm, an optimal algorithm, which has yet to gain wide-spread use in commercial real-time operating systems. Interesting properties of the model include small jitter, short input-output latencies, and isolation between unrelated tasks. A control task has a single adjustable parameter—the CPU utilization factor—that uniquely determines both the control performance and the schedulability of the task. The utilization factor serves as a simple interface between the control design and the real-time design.

Controllers executing under the Control Server model can be viewed as *scalable real-time components* with well-defined control and scheduling properties. The model can ideally be combined with a feedback scheduling mechanism that optimizes the overall control performance as the system workload changes. The simple interface between the control and the scheduling design makes for a reasonably simple codesign problem to be solved on-line.

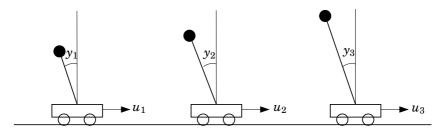

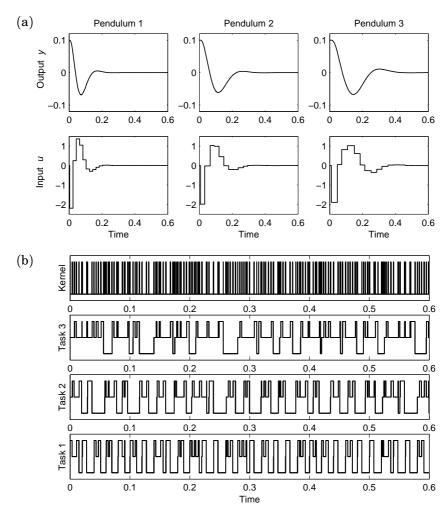

Figure 1.2 Three inverted pendulums should be stabilized using one computer.

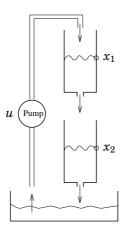

#### 1.4 An Introductory Example

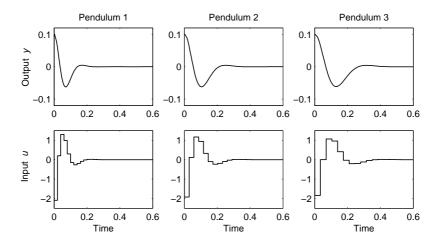

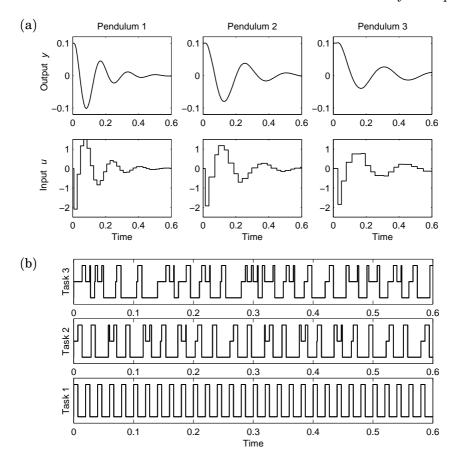

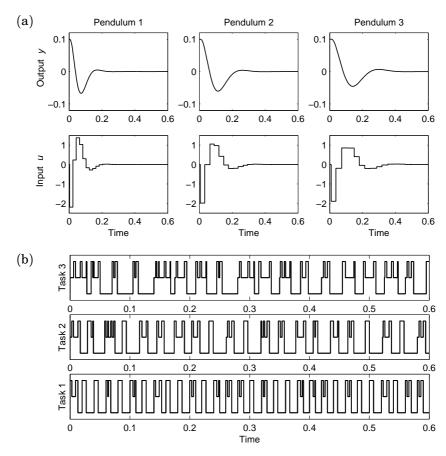

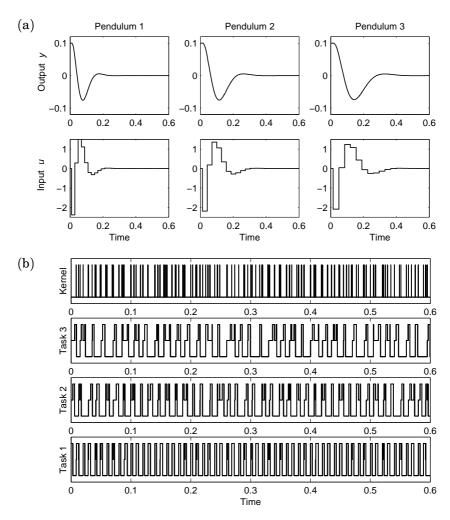

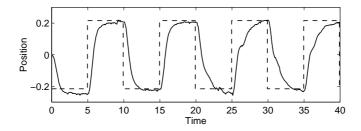

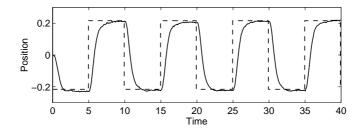

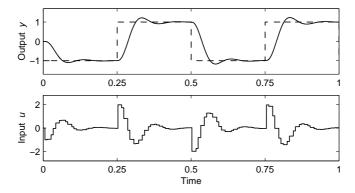

As an introductory example, and to illustrate some of the contributions of the thesis, we will study the toy control problem depicted in Figure 1.2. Three inverted pendulums of different lengths should be controlled by a computer with (very) limited computational resources. A linear digital controller is designed for each pendulum (the details are given in Section 3.5). The pendulum lengths motivate different sampling intervals for the different controllers:  $h_1$ ,  $h_2$ ,  $h_3 = 20$ , 29, 35 ms. An ideal simulation of the control system where the execution of the control algorithm is disregarded is shown in Figure 1.3. It is seen that all pendulums are quickly stabilized.

Figure 1.3 Ideal simulation of the inverted pendulum system.

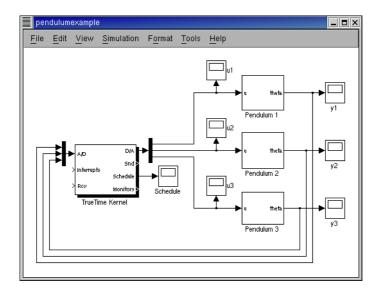

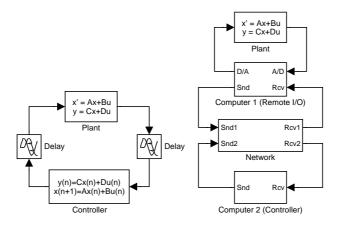

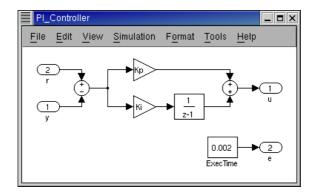

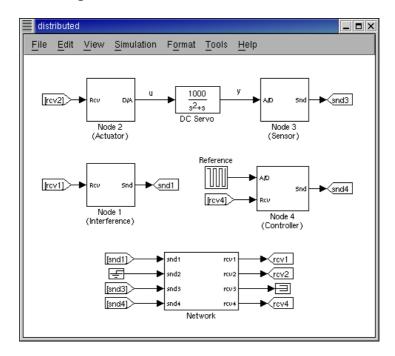

**Figure 1.4** TrueTime simulation model of the inverted pendulum system. The TrueTime Kernel block simulates a real-time operating system that executes user-defined tasks.

#### Simulation Using TrueTime

The previous simulation of the inverted pendulum system did not capture the true performance of the controllers. First, the execution time of the control algorithm was disregarded. Second, the fact that the three controllers are executing as real-time tasks in the same CPU was ignored. To capture the true, timely behavior of the controllers executing in a real-time operating system, the TrueTime simulator can be used. A TrueTime model of the inverted pendulum system is shown in Figure 1.4. The TrueTime Kernel block simulates a full real-time operating system that executes user-defined tasks. The block has connections for analog inputs and outputs, external interrupts, network communication, etc. There is also a Schedule output that displays a trace of the executing tasks.

In the simulator, the execution time of the control algorithm is specified to  $C=7\,\mathrm{ms}$ . It is assumed that rate-monotonic scheduling is used, i.e., the task with the highest rate (shortest period) is assigned the highest priority. The utilization of the task set is

$$U = \sum \frac{C}{h_i} = 0.79,$$

so the CPU is not overloaded. A simple schedulability test (see Section 2.2) shows that all deadlines will be met (assuming a relative deadline equal

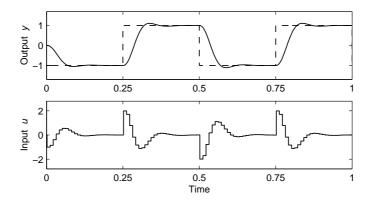

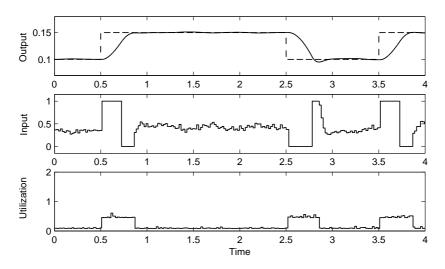

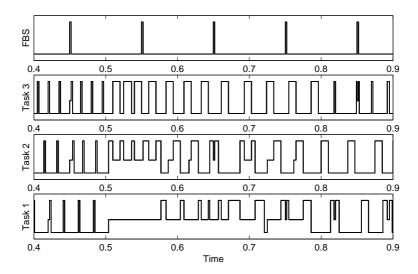

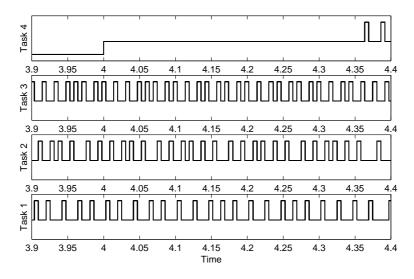

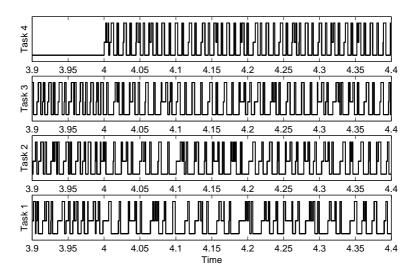

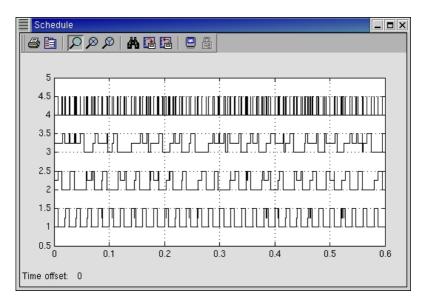

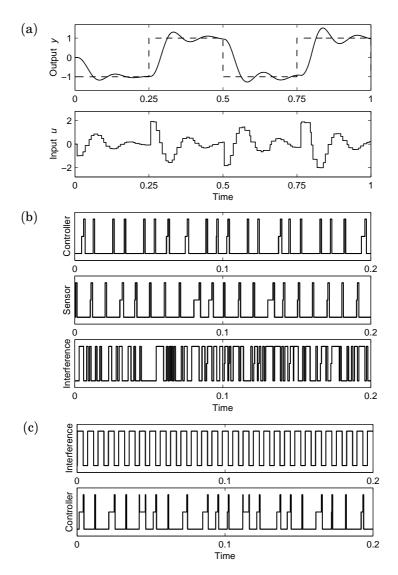

**Figure 1.5** TrueTime simulation of the inverted pendulum system under rate-monotonic scheduling: (a) control performance, and (b) task schedule. The scheduling-induced latencies in the control loops deteriorate the performance. (In the schedule plots, a high level means that the task is running, a medium level that it is preempted, and a low level that it is sleeping.)

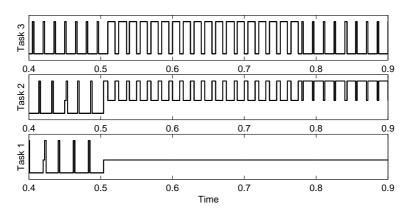

to the task period for all tasks). A simulation of the system when the tasks are released simultaneously at time zero is shown in Figure 1.5. The performance of the controllers is quite poor due to the scheduling-induced latency in the control loops. It is seen that Task 3 has a very irregular execution pattern due to preemption from Tasks 1 and 2.

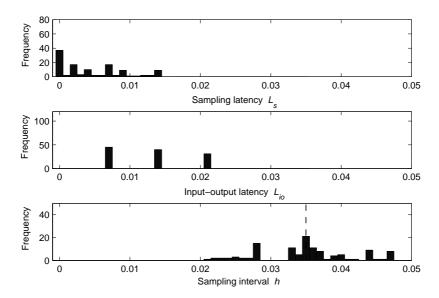

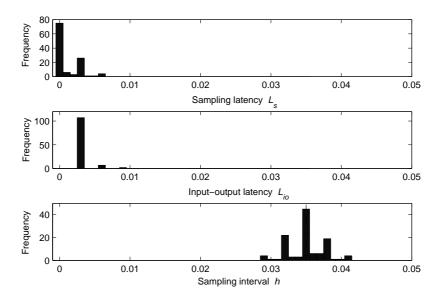

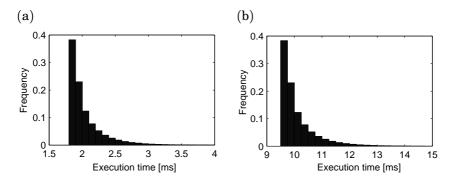

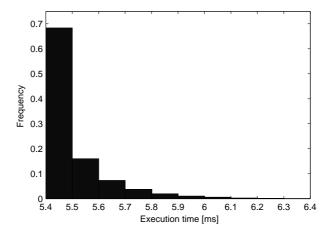

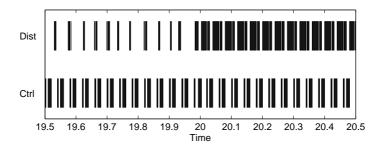

From a longer simulation, it is possible to gather statistics about various relevant task timing intervals. Figure 1.6 shows the distribution of three such intervals for Task 3. The first interval,  $L_s$ , is the *sampling latency*. This is the time from the release of the task (i.e., when the task

**Figure 1.6** Distribution of the sampling latency, the input-output latency, and the sampling interval for Task 3 under rate-monotonic scheduling. The controller is designed for the sampling interval h = 0.035.

is placed in the ready queue) to the actual start of the task (i.e., when the task becomes running), at which point the plant is assumed to be sampled. The second interval,  $L_{io}$ , is the *input-output latency*. This is the time from the sampling operation to the actuation operation. The third interval, h, is the sampling interval, i.e., the time between two successive sampling operations. It is seen that the rate-monotonic scheduling algorithm introduces quite large variations in all of these intervals.

#### **Analysis Using Jitterbug**

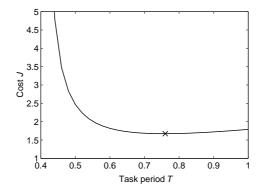

The TrueTime simulation of the control system showed that the performance deteriorated under rate-monotonic scheduling. One way to quantify the control performance degradation is to use a *cost function*. We could for instance measure the stationary variance of the pendulum angle y,

$$J = \mathbf{E} \ y^{2}(t) = \lim_{T \to \infty} \frac{1}{T} \int_{0}^{T} y^{2}(t) \, dt, \tag{1.1}$$

assuming that the plant is disturbed by white noise. The cost function could be evaluated numerically using very long simulations in TrueTime. A better alternative is to use Jitterbug, where cost functions of the type above can be computed analytically.

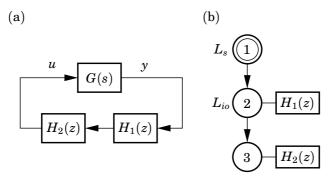

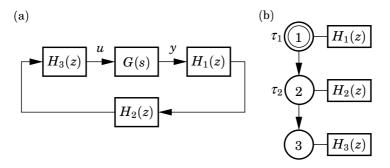

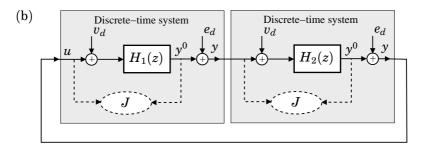

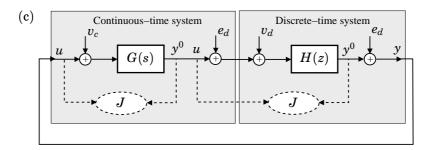

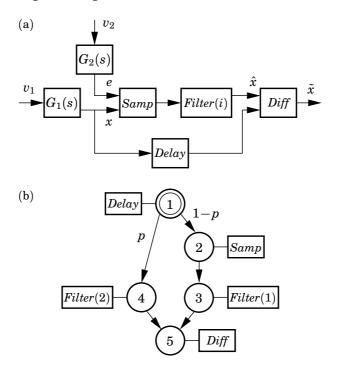

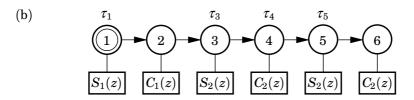

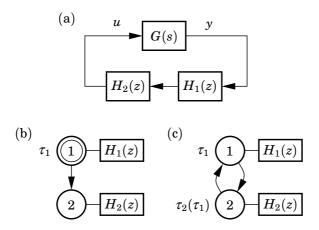

Figure 1.7 Jitterbug model of the inverted pendulum controller: (a) signal model, and (b) timing model.

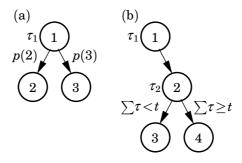

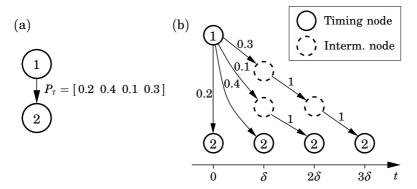

A Jitterbug model the inverted pendulum controller is shown in Figure 1.7. The signal model consists of three connected linear systems. The pendulum process is described the continuous-time system G(s) and is assumed to be disturbed by white input noise with unit variance. The controller is described by two discrete-time blocks,  $H_1(z)$  and  $H_2(z)$ . The first block models the sampling operation, while the second block models the computation and actuation of the control signal. The associated timing model consists of three nodes. The first node is periodic and represents the release of the control task. There is a random delay  $L_s$  until the second node where  $H_1$  is updated, and another random delay  $L_{io}$  until the third node where  $H_2$  is updated.

To evaluate the performance of Task 3 in the ideal case, the delays are set to zero in the timing model ( $L_s=0$ ,  $L_{io}=0$ ). In this case, Jitterbug evaluates the cost function (1.1) to J=0.37. Under rate-monotonic scheduling, we assume the probability distributions of  $L_s$  and  $L_{io}$  from Figure 1.6. In this case, the cost is computed to J=0.68, i.e., the variance of the pendulum angle is considerably larger.

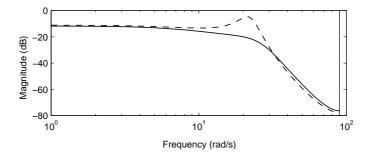

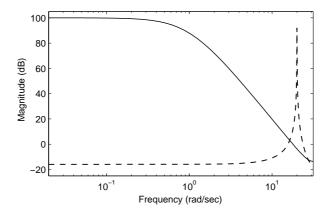

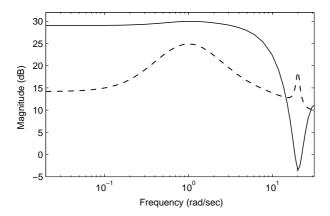

Jitterbug can also be used for frequency-domain analysis. In Figure 1.8, the spectral density of the output of Pendulum 3 has been computed in the ideal case and the rate-monotonic scheduling case. The resonance peak in the rate-monotonic case agrees with the oscillatory behavior seen in Figure 1.5.

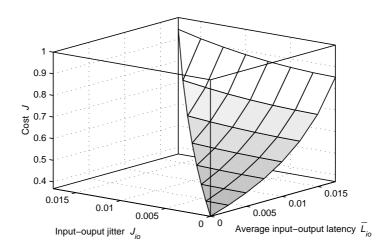

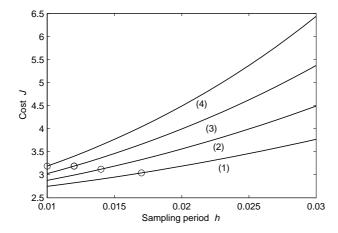

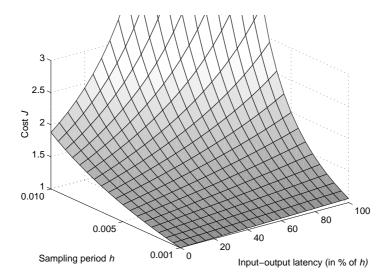

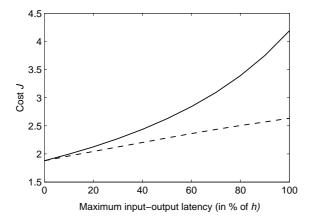

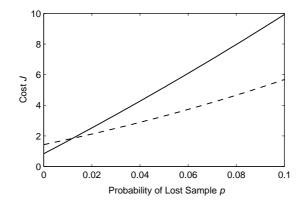

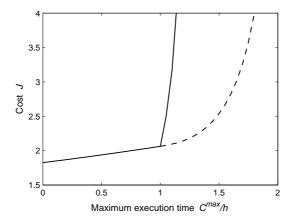

In most cases, exact knowledge of timing distributions will not be available at early design stages. Instead, Jitterbug can be used to estimate the timing sensitivity of a controller by sweeping various timing parameters and plotting the results. The resulting diagrams can be used as a guide in the later real-time design. In Figure 1.9, the cost function (1.1) for Task 3 has been calculated for various amounts of input-output latency

**Figure 1.8** Spectral density of the output of Pendulum 3 in the ideal case (full) and in the rate-monotonic scheduling case (dashed). The resonance peak in the rate-monotonic case agrees with the oscillatory behavior seen in Figure 1.5.

and input-output jitter. In the timing model, we have assumed zero sampling latency ( $L_s=0$ ) and a uniformly distributed input-output latency  $L_{io}$  between  $\bar{L}_{io}-J_{io}/2$  and  $\bar{L}_{io}+J_{io}/2$ , where  $\bar{L}_{io}$  denotes the average latency and  $J_{io}$  denotes the jitter. It is seen that the controller is quite sensitive to input-output latency but not very sensitive to jitter.

#### Subtask Scheduling

The example so far has shown that schedulability of task does not guarantee any level of control performance. From a control perspective, it is

**Figure 1.9** Cost as a function of the average input-output latency and the input-output jitter for Task 3. The cost increases more rapidly in the latency direction than the jitter direction.

not only important to finish the computations before the end of the period. It is also of importance that the sampling and actuation operations are performed regularly and with a short input-output latency. For this purpose, more detailed scheduling models can be used, where the different parts of the control algorithm are scheduled individually.

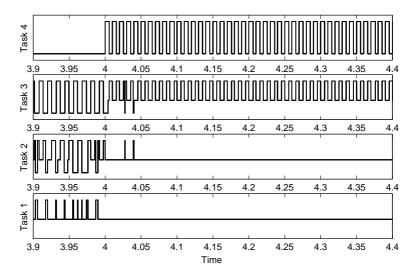

A typical control loop can be implemented as shown in Listing 1.1. Here, the control algorithm has been split into two parts: Calculate Output and Update State. Calculate Output contains only the operations needed to produce a control signal, while the rest of the computations are postponed to Update State. The idea of subtask scheduling is to assign different priorities to Calculate Output (which is the time-critical part) and Update State (which only has to finish before the end of the period).

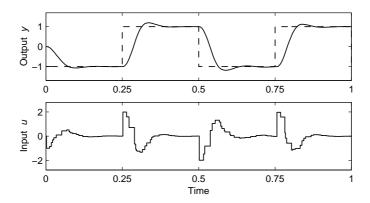

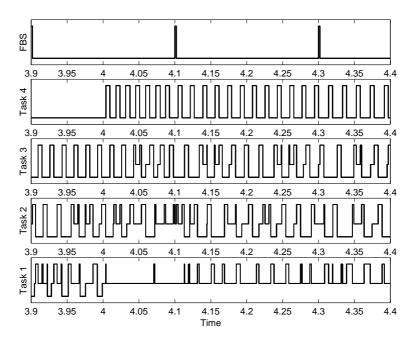

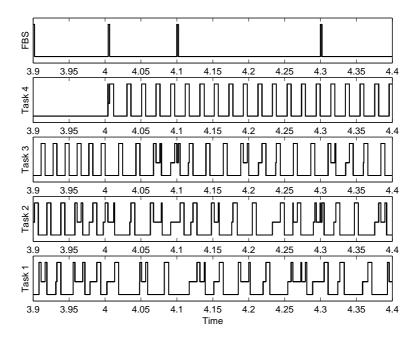

To continue the example, we assume that the execution time of the first part is 3 ms and the execution time of the second part is 4 ms. A subtask scheduling analysis shows that, in this case, it is possible to assign the highest priorities to the Calculate Output parts, while the Update State parts are given lower priorities. A new simulation of the inverted pendulum system is shown in Figure 1.10. It can be seen that the control performance is considerably improved. This is due to the reduction of latency and jitter in the control loops. The improvement is particularly large for Task 3, which was the lowest-priority controller under rate-monotonic scheduling. The new distributions of  $L_s$ ,  $L_{io}$  and h for Task 3 are shown in Figure 1.11.

The improved level of performance for Task 3 can also be verified by a new Jitterbug calculation. Inserting the distributions from Figure 1.11 into the timing model gives a cost of J=0.41, which is quite close to the cost in the ideal case.

**Listing 1.1** Typical implementation of a control loop. The control algorithm is split into two parts: Calculate Output and Update State.

```

LOOP

ReadInput;

CalculateOutput;

WriteOutput;

UpdateState;

WaitForNextPeriod;

END;

```

**Figure 1.10** TrueTime simulation of the inverted pendulum system under subtask scheduling: (a) control performance, and (b) task schedule. The performance is very close to the ideal case (see Figure 1.3). The scheduling strategy increases the number of context switches compared to rate-monotonic scheduling (see Figure 1.5).

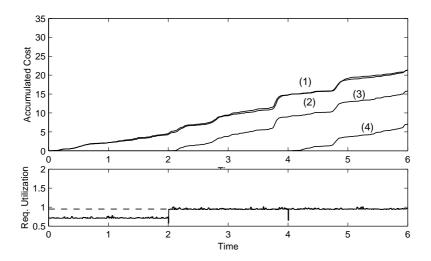

#### Feedback Scheduling

Scheduling analysis is normally applied off-line, assuming that values for all scheduling parameters (periods, deadlines, and worst-case computation times) are known. This is the appropriate approach for *hard* real-time systems, where it must be guaranteed, a priori, that all deadlines are met. For many control systems, this is an overly rigid approach. A single missed deadline does not mean system failure. This fact can be exploited to create more dynamic real-time control systems, where the resources are better utilized. However, in such systems, transient CPU overloads may occur, and the scheduler must keep the overload intervals

**Figure 1.11** Distribution of the sampling latency, the input-output latency, and the sampling interval for Task 3 under subtask scheduling. Compared with the rate-monotonic scheduling case (Figure 1.6), the latencies are shorter and the sampling interval is more closely centered around the nominal interval h = 0.035.

as short as possible.

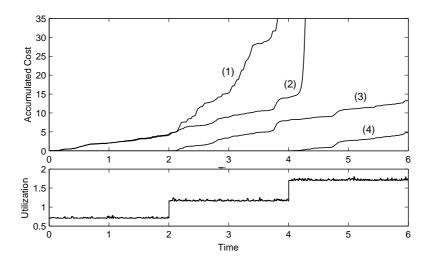

To continue the example, suppose that the execution time of the control algorithm has been underestimated. The designer believes that the execution time is 7 ms, while the true execution time is 10 ms. Using the same sampling periods as before, the CPU utilization is now

$$U = \sum \frac{C}{h_i} = 1.13,$$

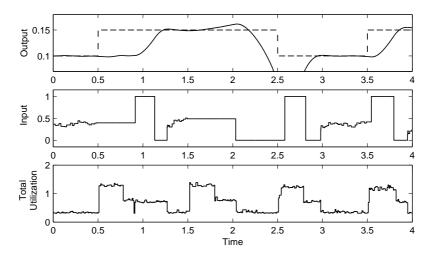

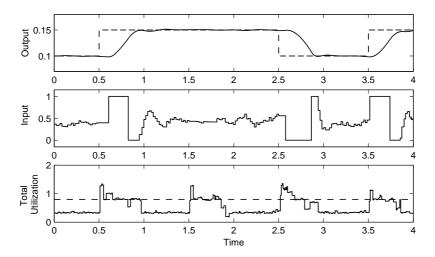

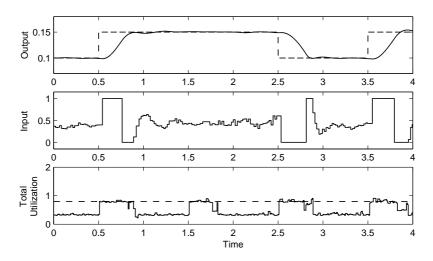

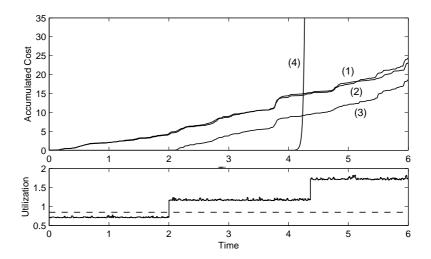

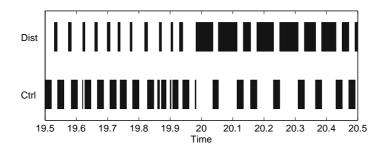

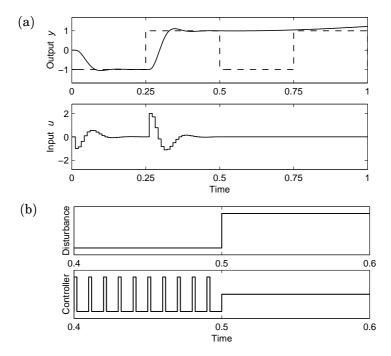

i.e., the processor is overloaded. A simulation of the system under ratemonotonic scheduling is shown in Figure 1.12. Due to the overload, Task 3 is blocked most of the time, causing the control loop to be destabilized.

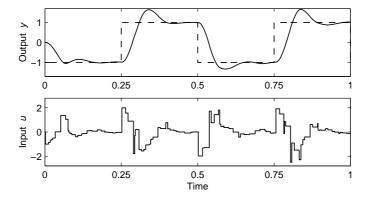

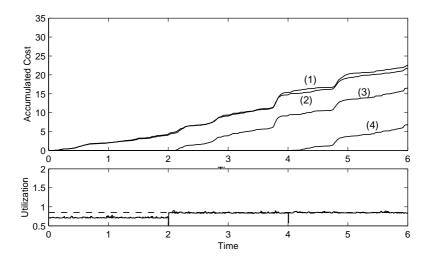

Next, a feedback scheduler is introduced. The scheduler attempts to control the CPU utilization to 80% by rescaling the sampling periods of the controllers. The feedback scheduler is implemented as a high-priority task that regularly collects execution-time measurements from the control tasks and estimates the CPU load. Based on the load estimate, new sampling periods are communicated to the control tasks. A simulation of the inverted pendulum system under feedback scheduling is shown in Figure 1.13. Task 3 is blocked during an initial transient until the feed-

**Figure 1.12** TrueTime simulation of the inverted pendulum system under rate-monotonic scheduling and an overloaded CPU: (a) control performance, and (b) task schedule. Task 3 is preempted most of the time, causing the control loop to be destabilized.

back scheduler has detected the overload and controlled the utilization to below 100%.

#### The Control Server

The example so far has assumed rate-monotonic scheduling of the control tasks. We have seen that this type of scheduling introduces unpredictable latency patterns in the control loops (although the magnitude of the latencies can be reduced using subtask scheduling). This problem becomes even more pronounced during CPU overloads, where a low-priority task can become completely blocked.

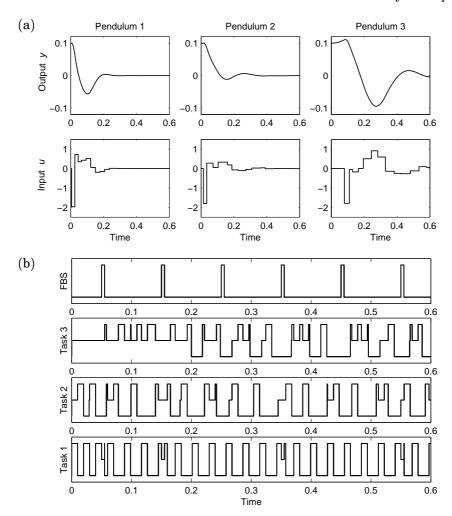

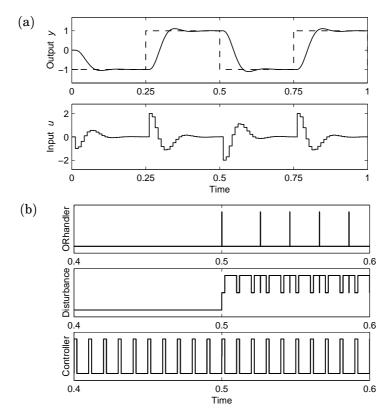

**Figure 1.13** TrueTime simulation of the inverted pendulum system under feedback scheduling: (a) control performance, and (b) task schedule. The feedback scheduler (FBS) regularly adjusts the sampling periods of the controllers, resolving the initial overload situation.

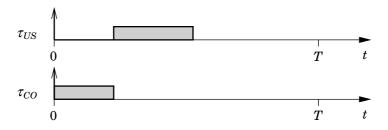

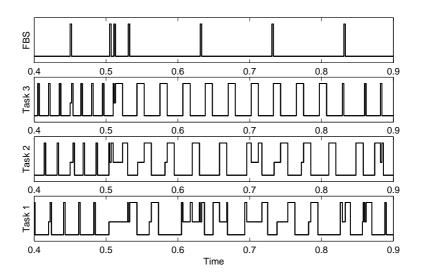

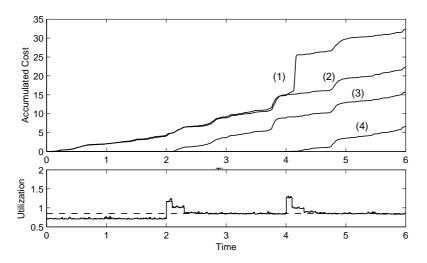

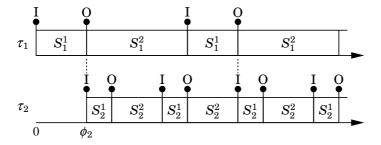

Under the Control Server (CS) model, each task is *guaranteed* a certain fraction of the CPU time, using server-based scheduling. Furthermore, the sampling and actuation instants are statically scheduled (i.e., handled by the kernel) in order to minimize the jitter. Combined, these two properties give a CS task a completely predictable behavior.

Since the Control Server is based on EDF, the CPU can be fully uti-

**Figure 1.14** TrueTime simulation of the inverted pendulum system under the Control Server model: (a) control performance, and (b) task schedule. The performance is very close to the ideal case (see Figure 1.3). The kernel handles the I/O operations of all the control tasks.

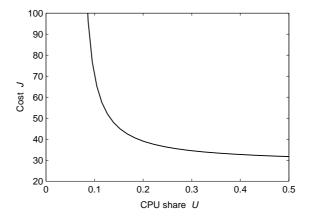

lized. In the inverted pendulum example, this means that shorter sampling periods can be used. Each controller will have a constant inputoutput latency (shorter than the period), which can be compensated for in the controller design. A simulation of the inverted pendulum system under the Control Server model is shown in Figure 1.14. The performance is very close to the ideal case (see Figure 1.3).

#### 1.5 Outline and Publications

The outline of the thesis is given below, together with references to related publications.

#### Chapter 2: Background

An introduction to real-time scheduling theory is given, followed by an overview of control loop timing. A brief survey of existing control and scheduling codesign approaches is given.

#### **Publications**

- Årzén, K.-E., B. Bernhardsson, J. Eker, A. Cervin, K. Nilsson, P. Persson, and L. Sha (1999): "Integrated control and scheduling." Technical Report ISRN LUTFD2/TFRT--7586--SE. Department of Automatic Control, Lund Institute of Technology, Sweden.

- Årzén, K.-E., A. Cervin, J. Eker, and L. Sha (2000): "An introduction to control and scheduling co-design." In *Proceedings of the 39th IEEE Conference on Decision and Control*. Sydney, Australia.

- Cervin, A. (2000): "Towards the integration of control and real-time scheduling design." Licentiate Thesis ISRN LUTFD2/TFRT--3226--SE. Department of Automatic Control, Lund Institute of Technology, Sweden.

The Bluetooth jitter compensation example appears in

Eker, J., A. Cervin, and A. Hörjel (2001): "Distributed wireless control using Bluetooth." In *Proceedings of the IFAC Conference on New Technologies for Computer Control*. Hong Kong, P.R. China.

#### **Chapter 3: Subtask Scheduling**

This chapter considers scheduling of simple controllers where the control algorithm has been split into two parts: Calculate Output and Update State. The goal is to reduce the input-output latencies in the control loops. Subtask deadline assignment under fixed-priority and earliest-deadline first scheduling is treated. The control performance improvements are verified in an inverted pendulum example.

#### **Publications**

Cervin, A. (1999): "Improved scheduling of control tasks." In *Proceedings* of the 11th Euromicro Conference on Real-Time Systems. York, UK.

#### **Chapter 4: Feedback Scheduling**

A scheduling architecture is proposed, where the CPU load is controlled by adjusting the sampling intervals of a set of controllers. The goal is to maintain high utilization and good control performance in spite of large variations in execution time. Feedforward from mode changes is used to further improve the regulation. A heuristic approach is discussed first, where simple rescaling of the nominal sampling periods to reach the utilization setpoint is used. The approach is exemplified on a set of hybrid controllers. It is later shown that simple period rescaling is in fact optimal for controllers with certain cost functions. Overloaded open-loop EDF scheduling is also discussed, and it is shown that overloaded EDF is equivalent to linear period rescaling.

#### **Publications**

- Cervin, A. and J. Eker (2000): "Feedback scheduling of control tasks." In *Proceedings of the 39th IEEE Conference on Decision and Control.* Sydney, Australia.

- Persson, P., A. Cervin, and J. Eker (2000): "Execution-time properties of a hybrid controller." Technical Report ISRN LUTFD2/TFRT--7591--SE. Department of Automatic Control, Lund Institute of Technology, Sweden.

- Cervin, A., J. Eker, B. Bernhardsson, and K.-E. Årzén (2002): "Feedbackfeedforward scheduling of control tasks." *Real-Time Systems*, **23:1/2**.

A preliminary study of feedback scheduling of model predictive controllers is presented in

Henriksson, D., A. Cervin, J. Åkesson, and K.-E. Årzén (2002): "Feedback scheduling of model predictive controllers." In *Proceedings of the 8th IEEE Real-Time and Embedded Technology and Applications Symposium.* San Jose, CA.

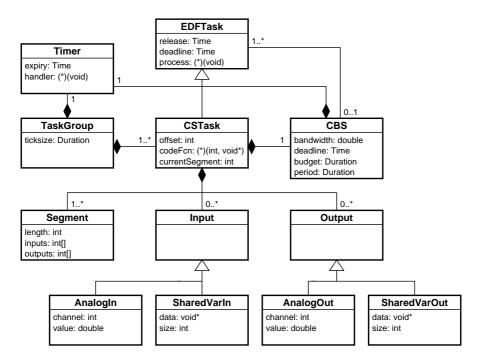

#### **Chapter 5: The Control Server**

A new computational model for real-time control tasks is presented, with the primary goal of simplifying the control and scheduling codesign problem. The model combines time-triggered I/O and inter-task communication with dynamic, reservation-based task scheduling. To facilitate short input-output latencies, a task may be divided into several segments. Jitter is reduced by allowing communication only at the beginning and at the end of a segment. A key property of the model is that both schedulability and control performance of a control task will depend on the reserved utilization factor only. This enables controllers to be treated as scalable

real-time components. The model has been implemented in a public domain real-time kernel and validated in control experiments.

#### **Publications**

Cervin, A. and J. Eker (2003): "The Control Server: A computational model for real-time control tasks." In *Proceedings of the 15th Euromicro Conference on Real-Time Systems*. Porto, Portugal. (To appear in June 2003.)

#### **Chapter 6: Analysis Using Jitterbug**

The MATLAB-based toolbox Jitterbug is presented. The tool allows the user to compute a quadratic performance index for a control loop under various timing conditions. The control system is built from a number of continuous- and discrete-time linear systems, and the execution of the controller is described by a stochastic timing model. The toolbox is also capable of computing the spectral densities of the signals in the system. Using the tool, it is easy to investigate the impact of delays, jitter, lost samples, aperiodic execution, etc., on the control performance. A number of examples are given.

#### **Publications**

Lincoln, B. and A. Cervin (2002): "Jitterbug: A tool for analysis of realtime control performance." In *Proceedings of the 41st IEEE Conference* on *Decision and Control*. Sydney, Australia.

Cervin, A. and B. Lincoln (2003): "Jitterbug 1.1—Reference manual." Technical Report ISRN LUTFD2/TFRT--7604--SE. Department of Automatic Control, Lund Institute of Technology, Sweden.

(There are also two publications that describe both Jitterbug and True-Time, see below.)

#### **Chapter 7: Simulation Using TrueTime**

The MATLAB/Simulink-based simulator TrueTime is presented. The simulator allows detailed co-simulation of continuous plant dynamics, real-time scheduling, control task execution, and message transmission in distributed real-time control systems. The TrueTime Kernel block is described in detail, and a number of examples are given.

#### **Publications**

Henriksson, D., A. Cervin, and K.-E. Årzén (2002): "TrueTime: Simulation of control loops under shared computer resources." In *Proceedings*

- of the 15th IFAC World Congress on Automatic Control. Barcelona, Spain.

- Henriksson, D. and A. Cervin (2003): "TrueTime 1.1—Reference manual." Technical Report ISRN LUTFD2/TFRT--7605--SE. Department of Automatic Control, Lund Institute of Technology, Sweden.

- Both Jitterbug and TrueTime are described in

- Cervin, A., D. Henriksson, B. Lincoln, and K.-E. Årzén (2002): "Jitterbug and TrueTime: Analysis tools for real-time control systems." In *Proceedings of the 2nd Workshop on Real-Time Tools*. Copenhagen, Denmark.

- Cervin, A., D. Henriksson, B. Lincoln, J. Eker, and K.-E. Årzén (2003): "How does control timing affect performance?" *IEEE Control Systems Magazine*. (To appear in June 2003.)

- An old version of the simulator is described in

- Eker, J. and A. Cervin (1999): "A Matlab toolbox for real-time and control systems co-design." In *Proceedings of the 6th International Conference on Real-Time Computing Systems and Applications.* Hong Kong, P.R. China.

- Cervin, A. (2000): "The real-time control systems simulator—Reference manual." Technical Report ISRN LUTFD2/TFRT--7592--SE. Department of Automatic Control, Lund Institute of Technology, Sweden.

#### **Chapter 8: Conclusion**

The contents of the thesis are summarized and suggestions for future work are given.

## Background

#### 2.1 Introduction

In textbooks on real-time systems, e.g., [Burns and Wellings, 2001; Liu, 2000; Buttazzo, 1997; Krishna and Shin, 1997], control systems are used as the prime example of *hard real-time systems*. In a hard real-time system, the computer must respond to events within specified deadlines—otherwise, the system will fail. In the case of a control system, the computer must respond to incoming measurement signals, producing new control signals fast enough to keep the plant within its operational limits.

The controller is often just one component among many in an embedded computer system. There may be several more controllers executing on the same unit, together with communication tasks, operator interfaces, tasks for data logging, etc. The concurrent activities are typically implemented on a microprocessor using a sequential programming language such as C together with a real-time operating system, or using a more modern language such as Ada or Java that has direct support for concurrent programming.

In an embedded system, the processor (CPU) time is a shared resource for which the various tasks compete. To guarantee, a priori, that all tasks will meet their deadlines, static (off-line) schedulability analysis must be performed. The analysis assumes a certain task model and that the relevant task attributes are known. The traditional view in the hard real-time scheduling community is that a digital controller can be modeled as a task that has

- · a fixed period,

- a hard deadline equal to the period, and

- a known worst-case execution time (WCET).

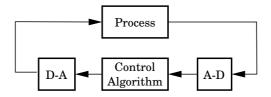

**Figure 2.1** A computer-controlled system. The control task consists of three distinct parts: input data collection (A-D), control algorithm computation, and output signal transmission (D-A).

While this simple model is appropriate for some control applications, there are also a number of cases where it is either too simplistic or too rigid.

First, the model is only concerned with the scheduling of the pure control computations. However, a control task generally consists of three distinct operations: input data collection, control algorithm computation, and output signal transmission, see Figure 2.1. The timing of the input and output operations are crucial to the performance of the controller. A delay (or latency) between the input and the output decreases the stability margin of the control loop. Jitter in the inputs and outputs also causes the performance to degrade. Since the input and output operations are neglected in the task model, there are no means of controlling the latency and the jitter in the scheduling design.

Second, the model assumes that worst-case estimates of the controller execution times are available. In practice, it is very difficult to obtain a tight bound on the WCET. Very few analytical tools are available, and the ones that exist cannot handle all the features of modern computing hardware, such as multi-level caches, pipelines, and speculative branching. The net result is that WCET estimates tend to be very pessimistic. Furthermore, some control algorithms have varying execution-time demands. One example is hybrid controllers that switch between different internal modes. Another example is model predictive controllers (MPCs) that solve an optimization problem in each sample. Basing the analysis on the WCETs of these controllers may lead to very low average utilization of the processor.

Third, the model assumes that all controller deadlines are hard. This this is only a simplifying assumption, however. The sampling rate of a controller is typically chosen to be several times faster than what is dictated by Shannon's sampling theorem and pure stability concerns. A single missed deadline only means that the current sampling interval becomes somewhat longer. The net effect can be interpreted as a small disturbance acting on the process. Only in the case of longer CPU overloads will the stability of the plant be endangered.

In the following chapters of the thesis, modifications to the simple task model that remedy some of the problems above will be given. More detailed task models allow better control of latency and jitter in the control loops. Relaxing the requirements on known WCETs and hard deadlines allows the computing resources to be used more efficiently. Accepting some degree of non-determinism in real-time control systems also permits the use of COTS hardware and software. This can lead to lower development costs for embedded systems.

The rest of this chapter contains background material on real-time scheduling theory, control loop timing, and related work in the area of control and real-time scheduling codesign.

# 2.2 Real-Time Scheduling Theory

Real-time scheduling theory is used to predict whether the tasks in a real-time system will meet their individual timing requirements. Given a task model and a scheduling algorithm, off-line analysis is performed to check, for instance, whether all deadlines will be met during runtime.

Two main design approaches exist: static scheduling and dynamic scheduling. Static scheduling is an off-line approach that uses optimization-based algorithms to generate a cyclic executive. An execution table states the order in which the different tasks should execute and for how long they should execute. An advantage of the cyclic executive is that it is very simple to implement. The approach also has many drawbacks [Locke, 1992]. First, there is the difficulty of constructing the schedule itself. Second, it is hard to incorporate sporadic and aperiodic tasks. Third, tasks with long execution times may have to be split in many small pieces, making the code error-prone and difficult to read. Fourth, very long tables may be needed if the schedule incorporates tasks with period times that are relative prime. Due to these drawbacks, we will mainly consider dynamic scheduling in the sequel.

There exist a large number of dynamic scheduling policies. Here we will focus on the *fixed-priority* (FP) and the *earliest-deadline-first* (EDF) scheduling policies, both introduced in the seminal paper [Liu and Layland, 1973]. In the scheduling analysis, a basic task model is assumed, where each task  $\tau_i$  is described by

- a period (or minimum inter-arrival time)  $T_i$ ,

- a relative deadline  $D_i$ , and

- a worst-case execution time  $C_i$ .

Furthermore, in the simplest case, it is assumed that the tasks are independent (i.e., they do not communicate or share other resources than the CPU), and that there is no kernel overhead.

## **Fixed-Priority Scheduling**

Fixed-priority (FP) scheduling is the most common scheduling policy and is supported by most commercial real-time operating systems. Under FP scheduling, each task  $\tau_i$  is assigned a fixed priority  $P_i$ . If several tasks are ready to run at the same time, the task with the highest priority gets access to the CPU. If a task with higher priority than the running task should become ready, the running task is preempted by the other task.

**Priority Assignment.** Fixed-priority scheduling design consists of assigning priorities to all tasks before runtime. In [Liu and Layland, 1973] it was shown that the rate-monotonic (RM) priority assignment is optimal when  $D_i = T_i$  for all tasks. Each task is assigned a priority based on its period: the shorter the period, the higher the priority. The scheme is optimal in the sense that, if the task set is not schedulable under the rate-monotonic priority assignment, it will not be schedulable under any other fixed-priority assignment. By rate-monotonic scheduling, we mean fixed-priority scheduling where the tasks have been assigned rate-monotonic priorities.

In many cases, it is desirable to specify deadlines that are shorter than the period. In the case where  $D_i \leq T_i$  for all tasks, the *deadline-monotonic* (DM) priority assignment scheme is optimal (in the same sense as above) [Leung and Whitehead, 1982]. Each task is assigned a priority based on its relative deadline: the shorter the deadline, the higher the priority. Note that the RM priority assignment is merely a special case of the DM priority assignment.

**Schedulability Analysis.** Given a task set with known attributes (periods, deadlines, execution times, and priorities), a number of different tests can be applied to check whether all tasks will meet their deadlines. Assuming the rate-monotonic priority assignment, a sufficient (but not necessary) schedulability test is obtained by considering the utilization of the task set [Liu and Layland, 1973]. Assuming a set of n tasks, all tasks will meet their deadlines if

$$U = \sum_{i=1}^{n} \frac{C_i}{T_i} \le n(2^{1/n} - 1). \tag{2.1}$$

As the number of tasks becomes large, the utilization bound approaches  $\ln 2 \approx 0.693$ .

An exact schedulability test under FP scheduling is performed by computing the *worst-case response time*  $R_i$  of each task [Joseph and Pandya, 1986]. The response time of a task is defined as the time from its release to its completion. The maximum response time of a task occurs when all other tasks are released simultaneously. The worst-case response time of a task  $\tau_i$  is given by the recursive equation

$$R_i = C_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j \tag{2.2}$$

where hp(i) is the set of tasks with higher priority than  $\tau_i$  and  $\lceil x \rceil$  denotes the ceiling function. The task set is schedulable if and only if  $R_i \leq D_i$  for all tasks.

**Extensions.** Many extensions to the theory of FP scheduling exist, e.g., [Klein *et al.*, 1993]. The analysis has been extended to handle for instance common resources, release jitter, tick scheduling, nonzero context-switching times, and clock interrupts.

The analysis behind the schedulability conditions is based on the notion of the critical instant. This is the situation when all tasks are released simultaneously. If the task set is schedulable for this worst case, it will be schedulable also for all other cases. In many cases, this assumption is unnecessarily restrictive. Tasks may have precedence constraints that make it impossible for them to arrive at the same time. For independent tasks it is sometimes possible to introduce release offsets, to avoid the simultaneous releases. If simultaneous releases can be avoided, the schedulability of the task set may increase [Audsley et al., 1993]. Formulas for exact response-time calculations for tasks with static release offsets is given in [Redell and Törngren, 2002]. Schedulability analysis for tasks with dynamic offsets is discussed in [Gutierrez and Harbour, 1998]. A number of alternative scheduling models based on serialization of task executions in different ways have been suggested. These include the multi-frame model [Baruah et al., 1999b] and the serially executed subtask model [Harbour et al., 1994].

Recently, formulas for the best-case response time of tasks under fixed-priority scheduling have been derived [Redell and Sanfridson, 2002]. Knowing both the worst-case and the best-case response time of a task gives a measure of the response-time jitter. In its simplest form, the best-case response time  $R_i^b$  of task  $\tau_i$  is given by the recursive equation

$$R_{i}^{b} = C_{i}^{b} + \sum_{j \in hp(i)} \left\lceil \frac{R_{i}^{b} - T_{j}}{T_{j}} \right\rceil C_{j}^{b}$$

(2.3)

where  $C_i^b$  denotes the best-case execution time of task  $\tau_i$ .

## **Earliest-Deadline-First Scheduling**

Under EDF scheduling, the task with the shortest time to its deadline is chosen for execution. The absolute deadline of a task can hence be interpreted as a dynamic priority. Because of its more dynamic nature, EDF can schedule a larger set of task sets than the FP scheduling policy can. Despite its theoretical advantages, EDF has so far mainly been used in experimental real-time operating systems. A reason for this may be that EDF also has a number of potential drawbacks compared to FP scheduling [Burns and Wellings, 2001]:

- The implementation of EDF is slightly more complex; the dynamic priority incurs a larger runtime overhead and requires more storage.

- It may be difficult to assign artificial deadlines to tasks that have no explicit deadlines.

- During overloads, all tasks tend to miss their deadlines (this is known as the *domino effect*).

The arguments above should not be taken too seriously. It can be argued that it is more difficult to assign meaningful priorities than deadlines in a real-time system. Furthermore, control tasks running under EDF scheduling actually tend to behave better in overload situations than under FP scheduling (see Chapter 4).

**Schedulability Analysis.** In the case where  $D_i = T_i$  for all tasks, the schedulability of a task set under EDF is exactly determined by the processor utilization [Liu and Layland, 1973]. All tasks will meet their deadlines if and only if

$$U = \sum_{i=1}^{n} \frac{C_i}{T_i} \le 1. \tag{2.4}$$

Note that this test is much simpler than the exact schedulability test under FP scheduling (which requires that the response times are computed). Also note that the processor can be fully utilized under EDF.

For the case  $D_i \leq T_i$ , the analysis becomes more difficult. A very general schedulability test under EDF involves computing the *loading factor* of the tasks (see [Stankovic *et al.*, 1998]). The analysis is performed as follows. Given an arbitrary set of tasks, let each job (task instance)  $j_k$  be described by a computation time  $C_k$ , a release time  $r_k$ , and an absolute deadline  $d_k$ . Define the *processor demand* of the task set on a time interval  $[t_1, t_2]$  as

$$h[t_1, t_2] = \sum_{r_k \ge t_1 \land d_k \le t_2} C_k. \tag{2.5}$$

Next, define the *loading factor u* of the tasks as

$$u = \max_{0 \le t_1 < t_2} \frac{h[t_1, t_2]}{t_2 - t_1},\tag{2.6}$$

where the maximization is performed over all possible time intervals. The task set is schedulable under EDF if and only if  $u \le 1$ .

**Response-Time Analysis.** Worst-case response-time analysis under EDF scheduling is more difficult than under FP scheduling. The main problem is that there is no well-defined critical instance at which the task will experience its maximum interference. Nevertheless, formulas have been derived for response-time calculations under EDF, see [Stankovic *et al.*, 1998].

## Server-Based Scheduling

Many types of tasks do not fit the simple periodic task model. These include *aperiodic* and *soft* real-time tasks. To retain the guarantees of the hard real-time tasks, these types of tasks can be incorporated in the real-time system using *servers*. The main idea of the server-based scheduling is to have a special task, the server, for scheduling the pending aperiodic workload (emanating from one or several aperiodic tasks). The server has a budget that is used to schedule and execute the pending jobs. The aperiodic tasks may execute until they finish or until the budget has been exhausted. Several servers have been proposed. The *priority-exchange server* and the *deferrable server* were proposed in [Lehoczky *et al.*, 1987]. The *sporadic server* was introduced in [Sprunt *et al.*, 1989]. The main difference between the servers concerns the way the budget is replenished and the maximum capacity of the server.

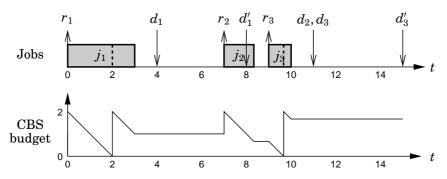

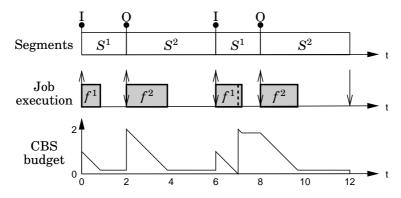

The above servers have been developed for the fixed-priority case. Similar techniques also exist for the dynamic-priority case (i.e., EDF), see, e.g., [Spuri and Buttazzo, 1996]. An EDF-based server with especially interesting properties is the *constant bandwidth server* (CBS) [Abeni and Buttazzo, 1998]. Since the server will be used in Chapter 5, it is described in detail below.

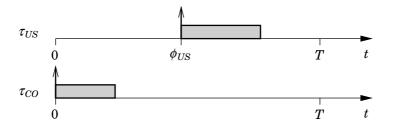

**The Constant Bandwidth Server.** A CBS creates the abstraction of a virtual CPU with a given capacity (or bandwidth)  $U_s$ . Tasks executing within the CBS cannot consume more than the reserved capacity. Hence, from the outside, the CBS will appear as an ordinary EDF task with a maximum utilization of  $U_s$ . The time granularity of the virtual CPU abstraction is determined by the  $server\ period\ T_s$ .

Associated with the server are two dynamic attributes: the server budget  $c_s$  and the server deadline  $d_s$ . Jobs that arrive to the server are placed

**Figure 2.2** Example of a constant bandwidth server (CBS) with the bandwidth  $U_s = 0.5$  and the period  $T_s = 4$  serving aperiodically arriving jobs. The up arrows indicate job arrivals, and the down arrows indicate deadlines.

in a queue and are served on first-come, first-served basis. The first job in the queue is always eligible for execution (as an ordinary EDF task), using the current server deadline  $d_s$ . The server is initialized with  $c_s := 0$  and  $d_s := 0$ . The rules for updating the server are as follows:

- 1. During the execution of a job, the budget  $c_s$  is decreased at unit rate.

- 2. Whenever  $c_s = 0$ , the budget is recharged to  $c_s := U_s T_s$  and the deadline is postponed one server period:  $d_s := d_s + T_s$ .

- 3. If a job arrives at a time r when the server queue is empty, and if  $c_s \geq (d_s r)U_s$ , then the budget is recharged to  $c_s := U_sT_s$  and the deadline is set to  $d_s := r + T_s$ .

The above rules limit the server processor demand in any time interval  $[t_1, t_2]$  to  $U_s(t_2 - t_1)$ . The third rule is used to "reset" the server after a sufficiently long idle interval. Note that postponing the deadline corresponds to lowering the dynamic priority of the server.

An example of CBS scheduling is given in Figure 2.2. The server is assumed to have the bandwidth  $U_s=0.5$  and the period  $T_s=4$ . At t=0, the server is empty and job  $j_1$  arrives. The budget is charged to  $U_sT_s=2$  and the job is served with the deadline  $d_1=r_1+T_s=4$  (rule 3). At t=2, the budget is exhausted. The budget is recharged to  $U_sT_s=2$ , and the remainder of  $j_1$  (one time unit) is served using the postponed deadline  $d_1'=d_1+T_s=8$  (rule 2). At t=7, job  $j_2$  arrives. Rule 3 is in effect, causing the budget to be recharged and the deadline to be set to  $d_2=r_2+T_s=11$ . At t=9, job  $j_3$  arrives. Rule 3 is not in effect, so the job is served with the old server deadline  $d_3=d_2=11$ . At t=9.7, the budget is once again exhausted. The budget is recharged, and the remainder of the job (0.3 units) is served using the postponed deadline  $d_3'=d_3+T_s=15$ .

Figure 2.3 Controller timing.

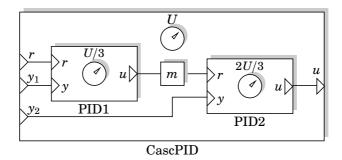

# 2.3 Control Loop Timing

A control loop consists of three main parts: input data collection, control algorithm computation, and output signal transmission. In the simplest case the input and output operations consist of calls to an external I/O interface, e.g., A-D and D-A converters or a field-bus interface. In a more complex setting the input data may be received from other computational blocks, such as noise filters, and the output signal may be sent to other computational blocks, e.g., other control loops in the case of set-point control. The complexity of the control algorithm may range from a few lines of code implementing a PID (proportional-integral-derivative) controller to the iterative solution of a quadratic optimization problem in the case of model predictive control (MPC). In most cases the control is executed periodically with a sampling interval that is determined by the dynamics of the process that is controlled and the requirements on the closed-loop performance. A typical rule-of-thumb [Åström and Wittenmark, 1997] is that the sampling interval h should be selected such that

$$\omega_c h = 0.2 - 0.6,$$

(2.7)

where  $\omega_c$  is the bandwidth of the closed-loop system. A real-time system where the product  $\omega_c h$  is small for all control tasks will be less sensitive to scheduling-induced latencies and jitter, but it will also consume more CPU resources.

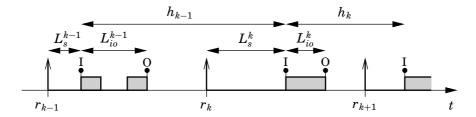

# **Timing Parameters**

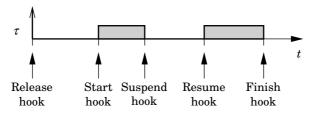

Ideally, the control algorithm should be executed with perfect periodicity, and there should be zero delay between the reading of the inputs and the writing of the outputs. This will not be the case in a real implementation, where the execution and scheduling of tasks introduce latencies. The basic timing parameters of a control task are shown in Figure 2.3. It is assumed that the control task is *released* (i.e., inserted into the ready queue of the

real-time operating system) periodically at times given by  $r_k = hk$ , where h is the nominal sampling interval of the controller. Due to preemption from other tasks in the system, the actual start of the task may be delayed for some time  $L_s$ . This is called the sampling latency of the controller. A dynamic scheduling policy will introduce variations in this interval. The sampling jitter is quantified by the difference between the maximum and minimum sampling latencies in all task instances,

$$J_s \stackrel{\text{def}}{=} L_s^{max} - L_s^{min}. \tag{2.8}$$

Normally, it can be assumed that the minimum sampling latency of a task is zero, in which case we have  $J_s = L_s^{max}$ . Jitter in the sampling latency will of course also introduce jitter in the sampling interval h. From the figure, it is seen that the actual sampling interval in period k is given by

$$h_k = h - L_s^{k-1} + L_s^k. (2.9)$$

The sampling interval jitter is quantified by

$$J_h \stackrel{\text{def}}{=} h^{max} - h^{min}. \tag{2.10}$$

We can see that the sampling interval jitter is upper bounded by

$$J_h \le 2J_s. \tag{2.11}$$

After some computation time and possibly further preemption from other tasks, the controller will actuate the control signal. The delay from the sampling to the actuation is the *input-output latency*, denoted  $L_{io}$ . Varying execution times or task scheduling will introduce variations in this interval. The *input-output jitter* is quantified by

$$J_{io} \stackrel{\text{def}}{=} L_{io}^{max} - L_{io}^{min}. \tag{2.12}$$

The impact of input-output latency, input-output jitter, and sampling jitter on the control design and the scheduling design is discussed below.

# Input-Output Latency

**Control Design.** It is well known that a constant input-output latency decreases the phase margin of the control system, and that it introduces a fundamental limitation on the achievable closed-loop performance. The resulting sampled-data system is time-invariant and of finite order, which allows standard linear time-invariant (LTI) analysis to be used (see e.g.,

[Åström and Wittenmark, 1997]). For a given value of the latency, it is easy to predict the performance degradation due to the delay. Furthermore, it is straightforward to account for a constant latency in most control design methods. From this perspective, a constant input-output latency is preferable over a varying latency.

**Scheduling Design.** The scheduling-induced input-output latency of a single control task can be reduced by assigning it a higher priority (or, alternatively, under EDF scheduling, a shorter deadline). This approach will of course not work for the whole task set.

Another option is to use non-preemptive scheduling. This will guarantee that, once the task has started its execution, it will continue uninterrupted until the end. The disadvantages of this approach are that the scheduling analysis for non-preemptive scheduling is quite complicated (e.g., [Klein *et al.*, 1993; Stankovic *et al.*, 1998]), and that the schedulability of other the tasks may be compromised.

A standard way to achieve a short input-output latency in a control task is to separate the algorithm calculations in two parts: *Calculate Output* and *Update State*. Calculate Output contains only the parts of the algorithm that make use of the current sample information. Update State contains the update of the controller states and precalculations for the next period. Update State can therefore be executed after the output signal transmission, hence, reducing the input-output latency. Further improvements can be obtained by scheduling the two parts as subtasks. This is the topic of the next chapter of the thesis.

## **Input-Output Jitter**

**Control Design.** A control system with a time-varying input-output latency is quite difficult to analyze, since the standard tools for LTI systems cannot be used. If the statistical properties of the latency are known, then theory from jump linear systems can be used to evaluate the stability and performance of the system (in the mean sense), see [Nilsson, 1998a]. A similar approach is taken in the Jitterbug toolbox (see Chapter 6), where the latency is described by a random variable that is assumed to be independent from sample to sample.

Often, it is not possible to have exact knowledge of the input-output latency distribution. A simple, sufficient stability test for systems where only the range of the latency is known is given in [Lincoln, 2002b]. Assuming zero sampling jitter, the test can guarantee stability for *any* input-output latencies in a given interval (whether they are time-varying, dependent, etc.).

One approach to deal with jitter in the control design is to explicitly

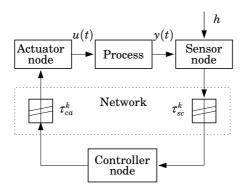

**Figure 2.4** Distributed digital control system with network communication delays  $\tau_k^{sc}$  and  $\tau_k^{ca}$ . From [Nilsson, 1998a].

design the controller to be robust, i.e., the delay is treated as a parametric uncertainty. Many robust design methods can be used, such as  $H_{\infty}$ , quantitative feedback theory (QFT) and  $\mu$ -design.

Another approach is to let the controller actively compensate for the delay in each sample. An optimal, jitter-compensating controller was developed in [Nilsson, 1998a]. The controller compensates for time-varying delays in a control loop, which is closed over a communication network. The setup is shown in Figure 2.4. The sensor node samples the process periodically, sending the measurements over the network to the controller node. The controller node is event-driven and computes a new control signal as soon as a measurement arrives. The control signal is sent to the event-driven actuator node, which outputs the signal to the process. The LQ (linear-quadratic) state feedback control law has the form

$$u(k) = -L(\tau_{sc}^k) \begin{pmatrix} x(k) \\ u(k-1) \end{pmatrix}, \qquad (2.13)$$

where the feedback gain L depends on the sensor-to-controller delay  $\tau_{sc}^k$  in the current sample. The computation of the gain vector L is quite involved and requires that the probability distributions of  $\tau_{sc}$  and  $\tau_{ca}$  are known.

The above approach cannot be directly applied to scheduling-induced delays. The problem is that the delay in the current sample (i.e., the current input-output latency) will not be known until the task has finished (and by then it is too late to compensate). A simple scheme that compensates for delay in the previous sample is presented in [Lincoln, 2002a]. The compensator has the same basic structure as the well-known Smith predictor, but allows for a time-varying delay.

**Figure 2.5** The inverted pendulum used in the Bluetooth network example. The pendulum is attached the end of a rotating arm.

Many other heuristic jitter compensation schemes have been suggested, e.g., [Hägglund, 1992; Albertos and Crespo, 1999; Marti *et al.*, 2001]. Yet another scheme (based on [Nilsson, 1998a]) is given in the following example.

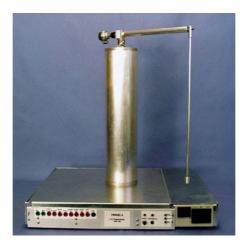

#### Example 2.1—Input-Output Jitter in a Bluetooth Network

Consider a distributed control system where a rotating inverted pendulum (see Figure 2.5) should be controlled over a Bluetooth network. The example is taken from [Eker *et al.*, 2001], where experiments on a laboratory setup were reported.

The objective of the control is to stabilize the pendulum in the upright position by applying a torque to the rotating arm. The control design is based on a linearized, fourth-order model of the process. The full state vector (the arm and pendulum angles and their derivatives) is measurable on the process.

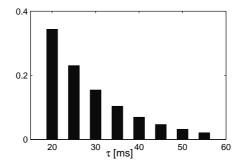

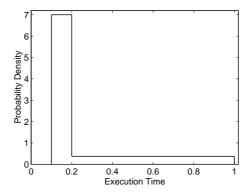

The control system is configured according to the setup in Figure 2.4. Due to disturbances and retransmissions in the wireless Bluetooth network, long random delays are introduced in the control loop. The total network delay  $\tau = \tau_{sc} + \tau_{sa}$  is assumed to have the probability distribution shown in Figure 2.6.

It can be noted that delay compensation in the distributed system works better the shorter the controller-to-actuator delay is compared to the sensor-to-controller delay. If the controller is located *at* the actuator, the delay in the current sample can be known exactly and compensated

Figure 2.6 The input-output latency distribution in the Bluetooth example.

Figure 2.7 Optimal state feedback gains (full lines) and affine approximations (dashed lines).

for accordingly. Modifying the setup is of course not a real solution, but using an intelligent I/O node (containing both the sensor node and the actuator node) with only very limited computational resources, we will see that ideal case can be closely emulated.

Assuming a sampling interval of h=60 ms, a state feedback controller on the form (2.13) is derived. The resulting optimal gain vector for different values of the total delay  $\tau$  is shown in Figure 2.7. It is noted that the optimal gain vector can be closely approximated by an affine function of  $\tau$ . A Taylor approximation of (2.13) around a nominal delay  $\tau_0$  gives

$$u(k) \approx -\left(L(\tau_0) + \frac{\partial}{\partial \tau}L(\tau_0)(\tau - \tau_0)\right) \begin{pmatrix} x(k) \\ u(k-1) \end{pmatrix}.$$

(2.14)

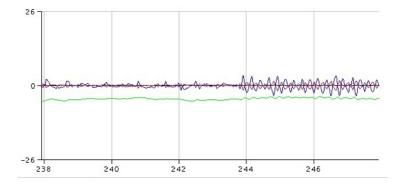

**Figure 2.8** Experiment on the Bluetooth-pendulum setup with random communication delays. At t=244, the jitter compensation is turned off, causing a large increase in the state variance.

In the controller node, x(k) and u(k-1) are known, but the value of  $\tau$  is still unknown. However, the controller can precompute

$$\hat{u}(k) = -L_0 \begin{pmatrix} x(k) \\ u(k-1) \end{pmatrix}, \qquad (2.15)$$

and

$$\alpha(k) = -\frac{\partial}{\partial \tau} L(\tau_0) \begin{pmatrix} x(k) \\ u(k-1) \end{pmatrix}. \tag{2.16}$$

These two scalars are then sent to the actuator node. Assuming that the I/O keeps track of the round-trip delay  $\tau$ , it can do the simple adjustment

$$u(k) = \hat{u}(k) + \alpha(k)(\tau - \tau_0),$$

(2.17)

before applying the control signal to the process.

The compensation scheme was tested on a laboratory Bluetooth-pendulum setup. The random delays in the experiments were not due to actual retransmissions in the network but were injected in the control loop on purpose. The result of an experiment with and without jitter compensation in shown in Figure 2.8. It is seen that jitter compensation reduces the variance of the measured states considerably.

**Scheduling Design.** One way to minimize scheduling-induced inputoutput jitter is to introduce a dedicated, high-priority task (or interrupt handler) for the output operation. The task is released in such a way that