# HILP80

# A High Level Programming Language for Intel 8080

Aspernäs, Jan-Eric

1976

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Aspernäs, J.-E. (1976). HILP80: A High Level Programming Language for Intel 8080. (Research Reports TFRT-3136). Department of Automatic Control, Lund Institute of Technology (LTH).

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or recognise.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 20. Dec. 2025

HILP 80

A HIGH LEVEL PROGRAMMING LANGUAGE

FOR INTEL 8080

J. E. ASPERNÄS

Report 7626 (C) May 1976 Department of Automatic Control Lund Institute of Technology

TILLHÖR REFERENSBIBLIOTEKET UTLANAS EJ

# HILP 80.

A HIGH LEVEL PROGRAMMING LANGUAGE FOR INTEL 8080.

Author Jan-Eric Aspernäs

Supervisors Leif Andersson

Johan Wieslander

# CONTENTS.

- 1. INTRODUCTION

- 2. SYNTAX OF HILP 80

- 3. SEMANTICS OF THE LANGUAGE HILP 80

- 1. General rules

- 2. Abbreviations

- 3. Head

- 4. Bank address manipulation

- 5. Register operation

- 6. Double register operation

- 7. Procedure calls with arguments

- 8. Conditions in HILP 80

- 9. INC and DEC statements

- 10. Hardware register usage

- 11. Error reports

- 12. List of language words

### APPENDIX

- A. Optimization technique

- B. Direct load and store in single precision

- C. Test program in HILP 80

This report describes a High Level Programming Language, HILP 80, for micro processors. This version of HILP 80 is made for INTEL 8080, but could be changed to fit any simular micro processor.

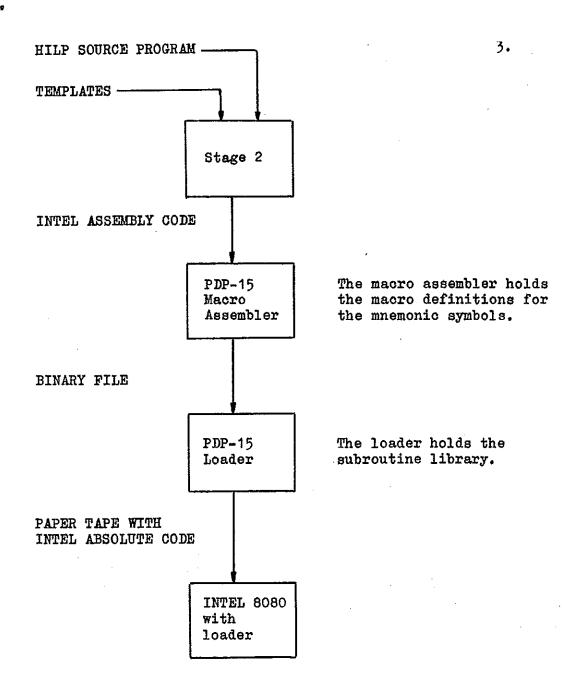

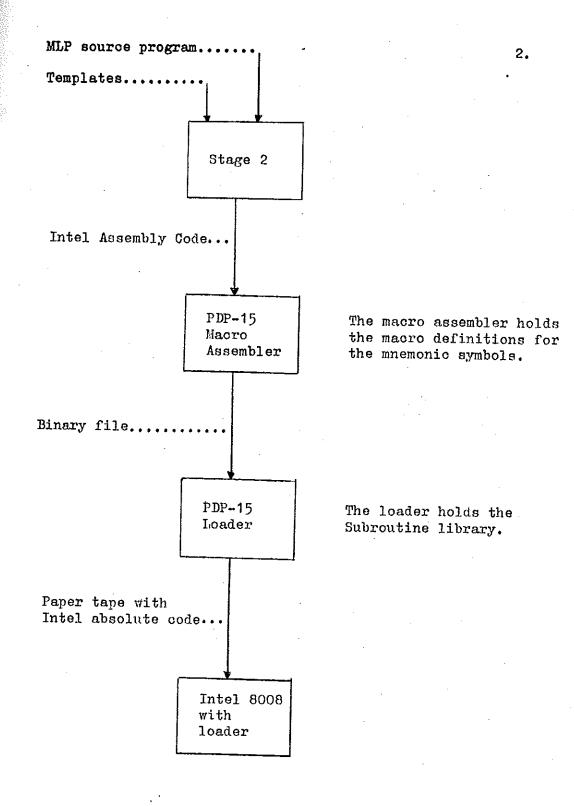

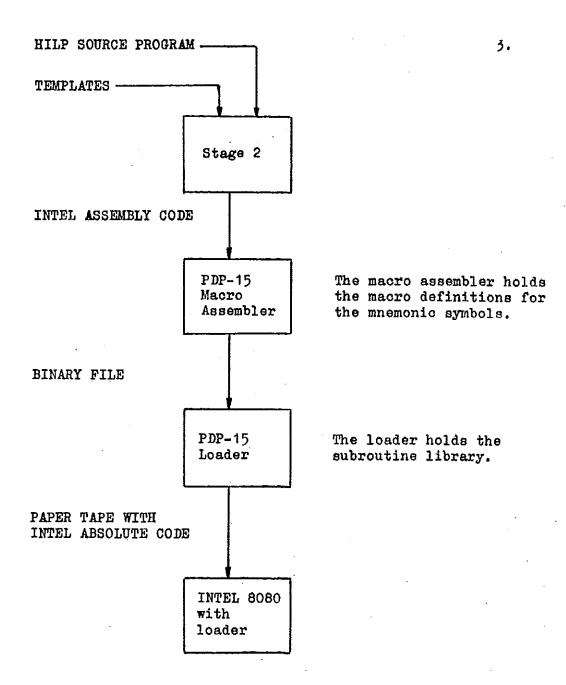

The compiler is based on STAGE 2 (Waite, 1973). The compiler generates assembly code. A flow diagram (fig 1) shows the way from HILP 80 source program to a running Intel 8080.

The compilation is intended to take place on a host machine. At Lund Institute of Technology (LTH), a PDP-15 is used as a host machine. The compiler is almost machine independent, and could be implemented on other computers. The macro processor STAGE 2 requires about 3 K of core, and the templates need about 12 K with high degree of packing. The translation time for the in appendix given exemple was about 65 seconds.

The language HILP 80 could be used at different levels down to assembly code. The medium and low level statements are valuable to increase the efficiency e.g. in loops.

Improvals of the limited data structures and arithmetic facilities are under discussion.

# EFFICIENCY OF HILP 80.

The main responsibility for the efficiency of the generated code lies in the hands of the user. Thus it is up to the user to decide e.g. whether registers should be used instead of address references in order to increase the efficiency. It is hard to measure the efficiency of HILP 80 depending on the various levels of the statements. However it is always possible to generate a code with very high degree of efficiency.

When addressing the data, INTEL 8080 uses register pair H&L, where H contains the high address (= bank) and L contains the low address. However, the A register could be loaded and stored directly using a two word address or loaded and stored indirectly using register pairs B&C or D&E. The different addressing facilities and the hardware usage of register pair H&L as an accumulator in double precision makes it hard to control the addressing in an efficient way. However, HILP 80 mostly solves this problem for the user, but in some cases the user could act in order to increase the efficiency. For this purpose HILP 80 has two "Bank manipulation statements".

### REFERENCE.

Waite, W.M., 1973, Implementing Software for Non-Numeric Applications, Prentice-Hall.

fig 1. From HILP 80 source to loaded INTEL 8080.

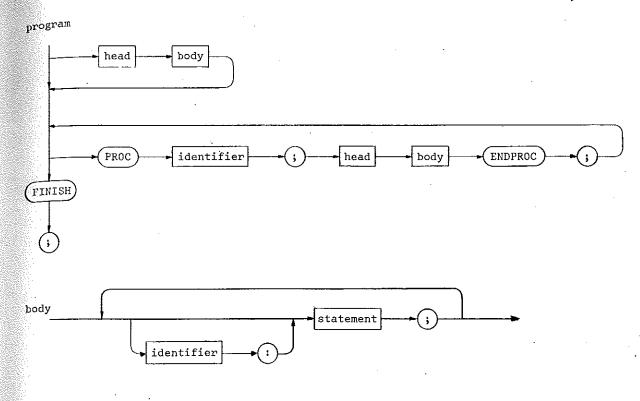

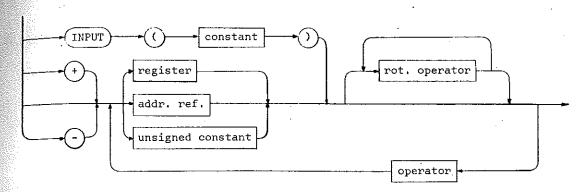

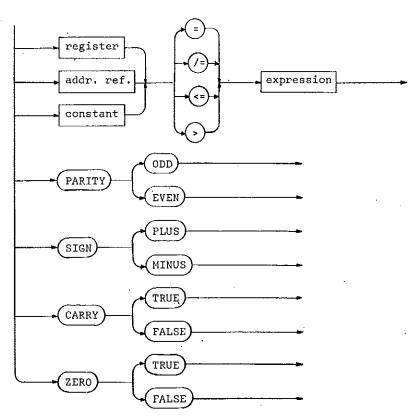

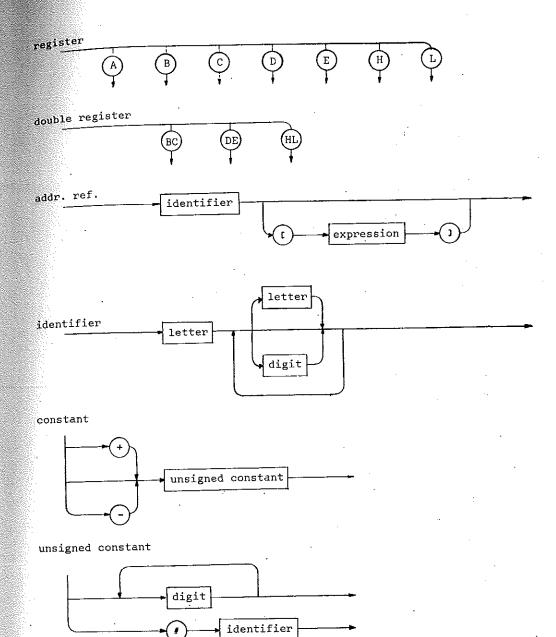

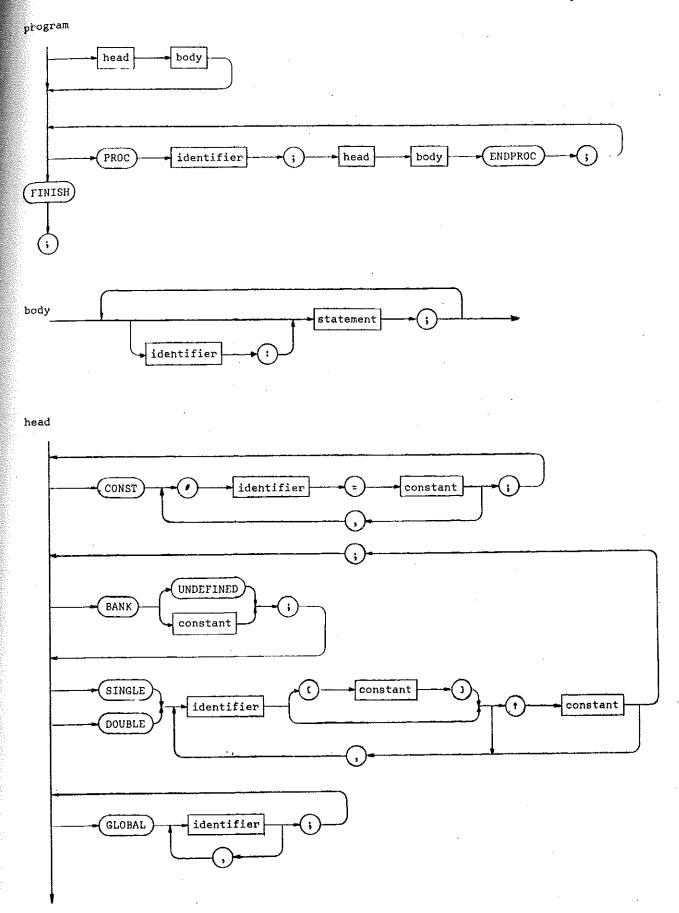

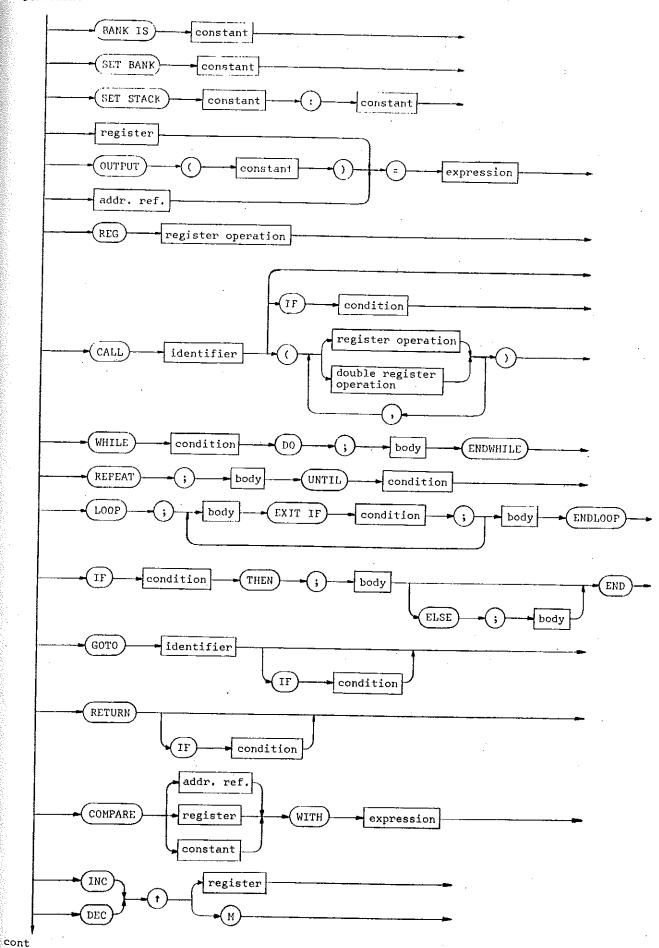

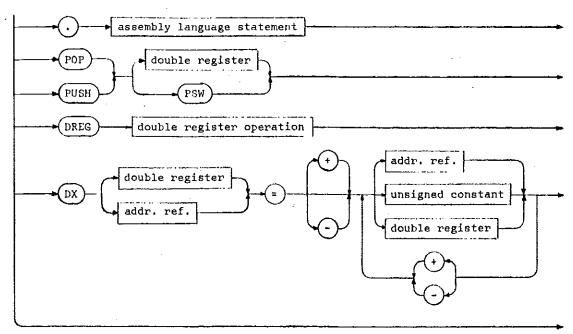

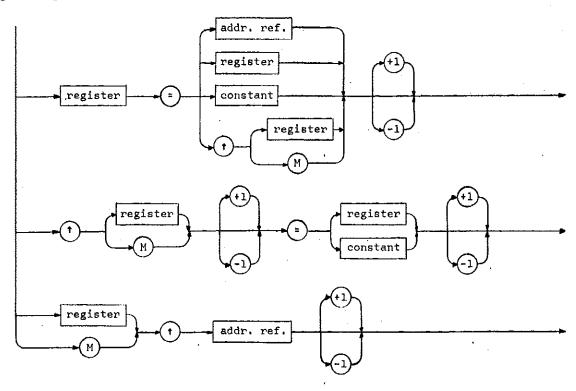

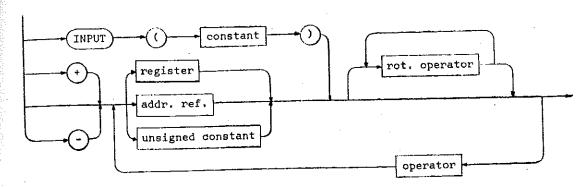

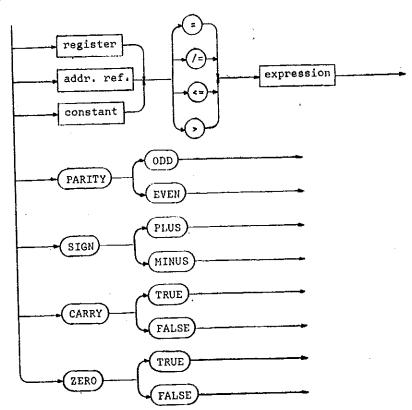

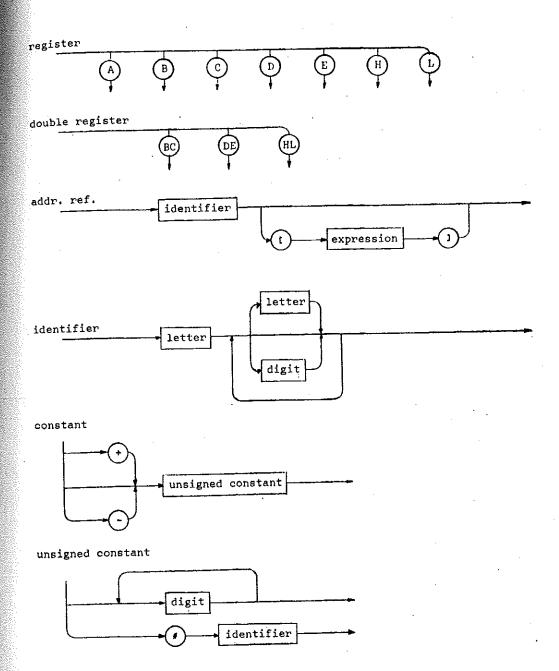

The syntax of HILP 80 is described in flow diagram form. The terminal symbols of the language are enclosed by circles or by ovals e.g. (REPEAT). The nonterminal symbols are written with small letters and enclosed by rectangles e.g. identifier.

The semicolon is the "end of statement" marker.

In the actual source program it has the following equivalent forms (2 denotes carriage return):

- 1. ; 2

- 2. 1

- 3. ; Any sequence of characters 2

statement consțant BANK IS SET BANK constant SET STACK constant constant register [expression OUTPUT constant addr. ref. register operation REG [IF condition register operation CALL identifier double register operation WHILE condition DO ENDWHILE body REPEAT body (UNTIL condition LOOP body EXIT IF condition body ENDLOOP IF THEN condition body END ELSE GOTO identifier condition RETURN IF) condition addr. ref. COMPARE WITH register expression constant INC register M DEC

cont

# statement continued

# register operation

# condition

### 3.1 GENERAL RULES.

Main rules for statements in HILP:

- 1 Only one statement is allowed per line.

- 2 Leading tabs and spaces are allowed. HILP words should be separated by one space. Logical operators, +, -, ., = should not be separated by spaces.

- Comments may be used in HILP:

a) ; comment string

b) statement; comment string

- Names may consist of up to six characters, starting with a letter, and for constants starting with #.

- 5 Empty lines may be used.

- 6 Numbers are interpreted as octal if they start with  $\emptyset$  and decimal otherwise.

- 7 Integers in HILP should be within the ranges:

SINGLE: -128 to +127

-0200 to +0177

DOUBLE: -32768 to +32767

-0100000 to +077777

### 3.2 ABBREVIATIONS.

register (A,B,C,D,E,H,L) r constant C identifier id address reference (=id, id[expression]) rac either r or a or c above either r or a above ra ro either r or c above Intel assembly code code memory location addressed by H and L M double register (BC, DE, HL) dr

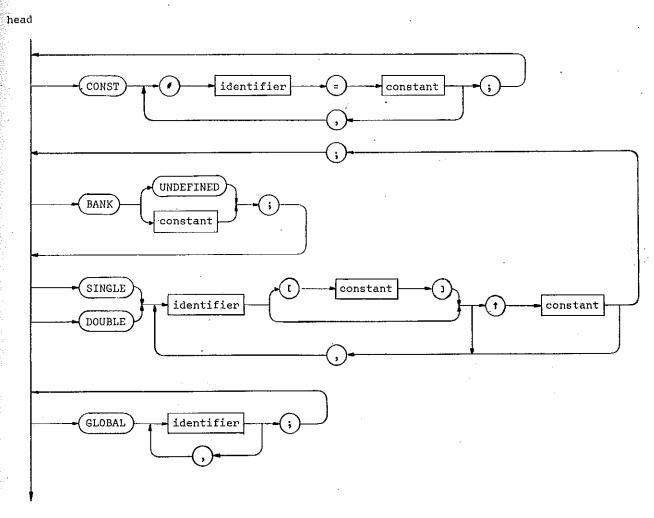

# a) CONST declaration.

The user may define constants, which will be replaced by the assembler with their current values. The constants could be useful e.g. in the bank declaration.

# b) VARIABLE declaration.

#### 1. BANK c

Variables used in the program must be declared and their bank addresses specified. The bank number given in the declaration is valid until another bank declaration is made.

SINGLE declaration. DOUBLE declaration.

The user may define addresses for the variables by stating to after the variables in the list, or state to for the first variable and then let the others be defined consecutively until another address is stated. The first word declared in a bank is given the address \$\phi\$ if the user does not give a start address. No error report will be given if the user declares addresses greater than 255 (\$\phi 377\$).

#### 2. BANK UNDEFINED

This bank declaration could be used in procedures, where the variables define different memory locations (different high addr., same low addr.) depending on the actual value in the H register.

SINGLE declaration as above. DOUBLE declaration as above.

# c) GLOBAL declaration.

If references are made to names in other programs, the loader program has to know that these names are global, otherwise the loader will not be able to set up common addresses for these names.

#### d) SET STACK c:c.

As HTLP implicitly uses the stack, this statement must always be given. The first constant is the bank address and the second is the low address.

NOTE: Array index runs from Ø to i-1.

Only one dimensional arrays are allowed.

No variables may be preset.

# a) GENERAL.

HILP translates the source program statement by statement going once from top to bottom. This technique causes some optimization problems when a label is generated by HILP e.g. in loop statements. The problems mentioned arise from the fact that when a label is jumped to during the execution, the translation path is different from the execution path.

For optimization during the translation, HILP uses internal variables:

LASTA last value of the A register.

LASTM last memory reference addressed by M (H&L).

LASTH last bank value in the H register.

As for LASTH, when M is to be set to an address of a variable, HILP will be able to check LASTH against the bank address of that variable and if equal not update the H register. In case of BANK UNDEFINED, LASTH is not used since the user in this case is supposed to take full responsibility for the bank address setting (HILP will always assume that the H register is correctly set).

#### BANK ADDRESS MANIPULATION STATEMENTS.

SET BANK c.

The constant c is loaded into the H register if LASTH is different from c.

BANK IS c.

This statement sets LASTH to c. It is an information to the translator and will never generate any code.

# 1) GENERAL PROGRAMMING.

HILP 80 will take full responsibility for the bank address manipulation. Thus the user does not have to care about the internal usage of LASTH. Some optimization of the bank address setting could be obtained, especially if all the variables are specified in the same bank. See Appendix A.

# 2) THE USAGE OF POINTER OPERATIONS.

The statements: REG † ... = ...

REG ...= † ...

INC † ...

DEC † ...

will assume that the H register is correctly set. To prevent errors, HILP 80 will generate an error report (NO BANK IN THE H REGISTER) if LASTH has been destroyed when one of the above mentioned statements is reached. In this case the user must give:

- 1. SET BANK c if the value of H is uncertain.

- 2. BANK IS c if the value of H is the desired bank address.

LASTH will be destroyed in the following statements:

REG H=... H=expression POP HL DREG HL=... DREG dr=a,+a,-a  $(\pm 1,2)$ DX ...=... .code when H is changed. When \*M is incremented or decremented. label: PROC CALL REPEAT LOOP ENDLOOP (See Appendix A for further details) WHILE ENDWHILE END Ħ

NOTE: Some statements containing variables will implicitly set the bank address in the H register. See Appendix B for further details.

This type of bank declaration could be used e.g. in procedure declarations. All variables declared in the head must refer to BANK UNDEFINED. The user must garantee that the H register is updated before using statements containing variables with their bank addresses unspecified.

No error report will be given if LASTH is destroyed in following statements:

REG ...= 1...

REG ...= 1...

INC 1...

DEC 1...

In double precision the DX statement is reduced to the following allowed types when variables with their bank addresses unspecified are used:

DX a=dr

DX dr="expression with dr and c. The expression may start with a, +a, -a."

NOTE: For internal procedures, where the main program has specified bank addresses for the variables, a reference to such a variable could cause an adjustment of the H register according to the rules for addressing given in Appendix B.

# d) NO VARIABLES DECLARED.

This type of head could be used e.g. in procedure declarations. No error report will be given if LASTH is destroyed in following statements:

REG ...=1...

INC †...

DEC †...

NOTE: For internal procedures, where the main program has specified bank addresses for the variables, a reference to such a variable could cause an adjustment of the H register according to the rules for addressing given in Appendix B.

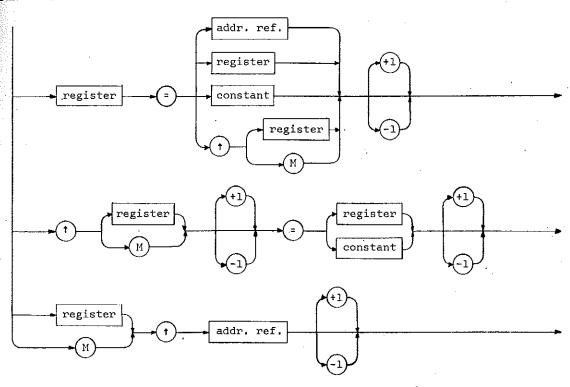

a) r<sub>1</sub>=r<sub>2</sub>ac(±1)

Register r<sub>1</sub> will be loaded with the value of r<sub>2</sub>ac, then r<sub>1</sub> will be incremented or decremented if necessary.

b) rfa(±1)

Register r will be loaded with the low address of a, a-1, a+1.

c) Mia(±1)

Register L will be loaded with the low address of a. The bank address of a is loaded into the H register.

Register H&L is incremented or decremented if necessary.

d)  $t_1(\pm 1) = r_2 c(\pm 1)$

The value of  $r_1$  is moved to register L. Register L is incremented or decremented if necessary. The value of  $r_2c(\pm 1)$  is moved to the memory.

e) 1M(±1)=r2c(±1)

Register H&L is incremented or decremented if necessary. The value of  $r_2c(\pm 1)$  is moved to the memory.

f)  $r_1 = r_2(\pm 1)$

The value of  $r_2$  is moved to register L. Register L is incremented or decremented if necessary. Register  $r_1$  will be loaded from the memory.

g) r<sub>1</sub>=**†**M(±1)

Register H&L is incremented or decremented if necessary. Register  $r_1$  will be loaded from the memory.

NOTE: Any memory reference d) to g) above will assume that the H register is correctly set.

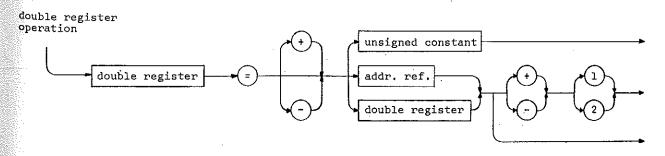

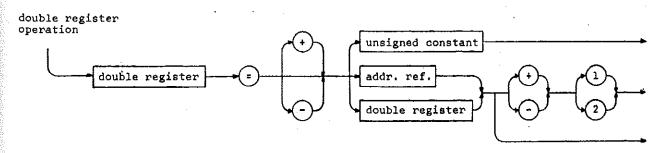

a) dr.=c

The constant will be loaded into double register dr.

b) dr<sub>1</sub>=dr<sub>2</sub>,a (±1,2)

Double register dr, will be loaded with the value of dr<sub>2</sub>, a. Then if necessary, dr, will be incremented or decremented once or twice.

c) dr<sub>1</sub>=-dr<sub>2</sub>,a (±1,2)

The value of dr<sub>2</sub>, a is complemented via the A register before loaded into dr<sub>1</sub>. Then dr<sub>1</sub> will be incremented or decremented once or twice if necessary.

# 3.7 PROCEDURE CALLS WITH ARGUMENTS.

Arguments are register operations or double register operations, which are carried out before the procedure is called. The same procedure could be called with any number of arguments.

Example: CALL SUB(A-B, DE=07745) is equivalent to:

REG A=B

DREG DE=07745

CALL SUB

### 3.8 CONDITIONS IN HILP 80.

The conditions refer to the state of the four flip-flops: ZERO, CARRY, SIGN and PARITY. These flip-flops may be affected by:

COMPARE rac WITH expression expression evaluating Assembly code Increment or decrement instructions

In the COMPARE statement the flip-flops are set:

ZERO If (expr. - rac) = 0

If (expr. - rac) < 0

# 3.9 INC and DEC statements.

CARRY

These statements shall be interpreted as: Set up the pointer to the memory, then increment or decrement the value addressed by M.

# a) SINGLE PRECISION.

The <u>A register</u> is used to evaluate expressions and is therefore overwritten when a statement containing an expression is used, except for:

ra=c (c≠0) a=a+1 a=a-1 a=r

NOTE: The INPUT statement loads the A register.

The OUTPUT statement takes the value from A.

M (H&L) will be overwritten when a memory reference is made, except for special cases. See Appendix B.

# b) DOUBLE PRECISION.

Any address reference in double precision will use HL.

In the DX statement HL is used to evaluate expressions. DE is used for temporary storage when address references or constants # 11,2 are used.

Since the hardware only allows double add to HL, subtractions of address references and double registers will be carried out via complementing in the A register.

# 3.11 ERROR REPORTS.

ILLEGAL SYNTAX

ILLEGAL CONDITION

IF/END DIFF =

LOOP/ENDLOOP DIFF =

REPEAT/UNTIL DIFF =

WHILE/ENDWHILE DIFF =

NO EXIT IN LOOP/ENDLOOP

NO BANK IN H REGISTER

MISSING DECLARATION OF

MISSING BANK DECLARATION

REMOVE TRAILING SPACE FROM

NOTE: HILP does not check that the declared data type is used in the program, e.g. both ARR and ARR(3) will be accepted.

HILP does not check if any array references exceed their permitted size.

```

Alphabet (A-Z)

```

Integers (0-9)

Spaces

1 #

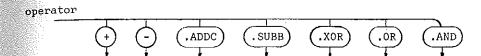

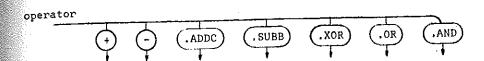

Operators: + - .ADDC .SUBB .XOR .OR .AND

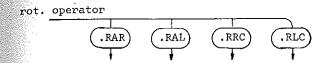

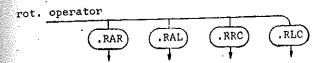

Rotate operators: .RAR .RAL .RRC .RLC

Comparators: = /= <= >

Flip-flops: ZERO CARRY SIGN PARITY

States: TRUE FALSE PLUS MINUS ODD EVEN

Register: A B C D E H L

Double register: BC DE HL

M

CONST

BANK

SINGLE

DOUBLE

GLOBAL

BANK IS

UNDEFINED

SET BANK

SET STACK

OUTPUT

INPUT

REG

CALL (IF)

GOTO (IF)

RETURN (IF)

WHILE DO ENDWHILE

REPEAT UNTIL

LOOP EXIT IF ENDLOOP

IF THEN ELSE END

COMPARE WITH

POP PUSH

PSW

INC DEC

DREG

DX

PROC ENDPROC

FINISH

# 1. REGISTER USAGE.

The usage of registers instead of address references will increase the efficiency, which is very valuable in loops.

Consider the following example, where V and I refer to bank 1.

| Source code. |       | Generated code. |            |

|--------------|-------|-----------------|------------|

| <b>T</b> 0   |       |                 |            |

| I=0          |       | XRA             | A          |

| •            |       | STA             | 0400+I     |

| REPEAT       | XR1=. |                 |            |

| ALIJ=0       |       | LDA             | 0400+I     |

| • .          |       | ADI             | ▼          |

|              |       | MOV             | L,A        |

|              |       | MVI             | H,1        |

|              |       | XRA             | <b>A</b> . |

|              |       | MOA             | M, A       |

| I=I+1        |       | MVI             | L,I        |

|              |       | INR             | M          |

| UNTIL I=031  |       | MVI             | A,031      |

|              |       | CMP             | M          |

|              |       | JNZ             | XR1        |

|              |       |                 |            |

| SET BANK 1   |       | MVI             | H,1        |

| REG LTV[0]-1 |       | MVI             | L,V-1      |

| REG ATV[030] |       | HVI             | A,V+030    |

| REPEAT       | XR1=. |                 | ,,.,.      |

| BANK IS 1    |       |                 |            |

| REG 1 L+1=0  |       | INR             | Li.        |

| •            |       | MVI             | M,0        |

| UNTIL L=A    |       | CMP             | L          |

|              |       | JNZ             | XR1        |

|              |       | 4               |            |

a) STATEMENTS WHICH IMPLICITLY DESTROY LASTH.

Label

The label could be jumped to with different banks in the H register.

Incrementing or decrementing 1M.

As H&L is incremented or decremented in this case, the H register also could be adjusted.

CALL

The procedure may have changed the H register.

PROC

The procedure could be called with different bank values in the H register.

END (from IF THEN)

LASTH will be destroyed if LASTH after the condition is evaluated, is different from LASTH just before END.

END (from IF THEN ELSE)

LASTH will be destroyed if LASTH just before ELSE is different from LASTH just before END.

REPEAT

LASTH just before REPEAT could differ from LASTH after the condition in UNTIL is evaluated.

LOOP

LASTH just before LOOP could differ from LASTH just before ENDLOOP.

ENDLOOP (Two or more EXITs in the LOOP)

LASTH after the condition evaluating in the EXITs could differ.

WHILE

LASTH just before WHILE could differ from LASTH just before ENDWHILE.

ENDWHILE

LASTH will be destroyed unless the condition evaluating in WHILE will set LASTH.

When a label is generated by HILP, LASTH will be destroyed. Thus an adjustment of the H register will take place when M is to be set to a variable. This updating of the H register could be unnecessary if the value is equal to the value of H when the jump takes place. To inhibit an unnecessary adjustment of the H register, the user may give a BANK IS c statement after the following statements:

label:

PROC

CALL

REPEAT

LOOP

ENDLOOP

WHILE

ENDWHILE

In this case the user must garantee that:

The problems discussed under a) could not occur. The H register already holds the value c. The SET BANK c statement could be used to update the H register.

Consider the following example, which is the same as given in 1). V and I are specified in bank 1.

| Source code. |       | Generated | code.  |

|--------------|-------|-----------|--------|

| I=O          |       | XRA       | A      |

|              |       | STA       | 0400+1 |

| SET BANK 1   |       | MVI       | H,1    |

| REPEAT       | XR1=. |           |        |

| BANK IS 1    |       |           |        |

| V(I1=0       |       | LDA       | 0400+I |

|              |       | ADI       | ٧      |

| •            |       | MOA       | L, A   |

|              |       | XRA       | A      |

|              |       | MOA       | M, A   |

| I=I+1        |       | MVI       | L,I    |

| •            |       | INR       | M      |

| UNTIL I=031  |       | MVI       | A,031  |

|              |       | CMP       | M      |

|              |       | JNZ       | XR1    |

Compared to the example given in 1) the improval is that the instruction "MVI H,1" is moved outside the loop. The technique given is most valuable when all the variables are specified in the same bank.

# APPENDIX B.

# DIRECT LOAD AND STORE IN SINGLE PRECISION.

Most memory references use H&L (M), when addressing variables, but the A register could be loaded and stored directly without using M. In this case the instructions LDA and STA are used instead of MOV A,M and MOV M,A.

Definition: simple addr = id or id[c].

Direct load and store of the A register will be used:

- When the expression has no address references, except that it may start with a simple addr.

- 2 Simple addr=expression

- 3 REG A=simple addr(±1)

### APPENDIX C.

# GENERATED CODE. HILP 80 STATEMENTS.

```

CONST 08K1=011, 08K2=19, 0STRK=3

%BK1=011

%BK2=023

%STBK=03

PANK DBK1

SINGLE X1+96, Y1, Z1, V1[10], TEMP1+0377

X1 = 0140

Y1=X1+71

Z1=Y1+01

V1=Z1+01

TEMP1=0377

BANK PRK2

SINGLE V2[9], X2, Y2, Z2

V2=0

x2=V2+011

Y2=X2+01

Z2=Y2+01

DOUBLE DV2(6), DX2, DY2+0350, DZ2

DV2=Z2+01

DX2=DV2+06+06

DY2=0350

DZ2=DY2+01+01

SINGLE TEMP2+0377

TEMP2=0377

GLOBAL SUB, LABEL

.GLOBL SUB, LABEL

SET STACK PSTBK:255

SP, %STBK * 0400 + 0377

LXI

:*** REGISTER OPERATIONS ***

REG A=0

MVI

A . 0 .

REG A=B

MOV

A,B.

REG B=8-1

DCR

REG C=V1[6]

LXI

H,%BK1*0400+V1+06

VOM

C,M

REG C=V2(X1-X2)-1

%BK1*0400+X1

LDA

LXI

H,%BK2*0400+X2+0

М

SUB

ADI

٧2

VOM

L,A

MOV

C, M

C

DCR

REG M+Y1

H, %BK1 *0400+Y1+0

LXI

REG L+Y2

MVI

L,Y2

SET BANK DBK1

```

```

C2.

REG C=+C-1

L,C

MOV

()CR

L

VOM

C, M

REG +L+1=D+1

INR

M \cdot D

MOV

М

INR

SET BANK OBK2

H, %8K2

MVI

DEC +B

MOV

L,B

DCR

;*** ASSIGNMENTS OF EXPRESSIONS ***

V2[X1]=V2[X1]-1

%BK1*0400+X1

LDA

ADI

٧2

VOM

L,A

DCR

М

V1(0)=V2(X1)+Y1

VOM

A.M

H,%BK1*0400+Y1+0

LXI

ADD

%8K1*0400+V1+0

STA

XRA

%BK1*0400+Z1

STA

72=7

LXI

H,%BK2*0400+Z2+0

MVI

M,07

Y1=B

H, %BK1 #0400+Y1+0

LXI

MOV

M,B

C = D

C, D

VOM

AS[5]=0

%BK2*0400+V2+02

STA

OUTPUT(6)=INPUT(15)+X1

017

LN

MVI

L, X1+0

ADD

М

OUT

06

V2[C.AND X2]=-25+Y1.ADDC Y2.RAR-V1[Y2.OR V2[V1[Y1]]]

MVI

A_{i} - 031

MVI

L, Y1+0

ADD

М

H, %BK2*0400+Y2+0

LXI

ADC

RAR

PSW

PUSH

A,M

MOV

PSW

PUSH

%BK1*0400+Y1

LDA

ADI

٧1

MOV

L,A

H, %BK1

MVI

A,M

MOV

٧2

ADI

MOV

L,A

PSW

POP

MVI

H, %BK2

М

ORA

٧1

ADI

```

```

03.

```

```

миу

L,A

PSW

POP

чVТ

H,%BK1

SUP

PSW-

PUSH

M()V

A,C

H, %8K2*0400+X2+0

LXI

ANA

۸5

401

MOV

L,A

P)P

PSW

MOV

Μ,Δ

:*** IF STM, GOTO STM, LOOPS ***

IF U=V2(X1) THEN

LDA

%8K1*0400+X1

ADI

٧S

MOV

L,A

VON

A,M

CPI

ij

JVZ

X 1

X1 = X1 - 1

H, %BK1 * 0400 + X1+0

LXI

DÇQ

FLSE

JMp

Χ2

X1=.

V2[X1]=0

X \, R \, \Lambda

À

M , A

MOV

/

X2=.

END

GOTO LABEL IF Z1=0

XRA

H,%BK1*0400+Z1+0

LXI

CMP

JZ,

LABEL

GOTO L

JMP

L

L:

LOOP

[=.

XL3=.

A=A.RAR

RAR

EXIT IF CARRY TRUE

JC .

XL4

A = - A

CMA

133

EXIT IF SIGN PLUS

JP.

X \perp 4

ENDLOOP

JMP

XL3

X \bot 4 = .

WHILE B<=A DO

X % 5 = .

CMP

В

ΧĢ

JM

REG A=A-1

DÇR

A

V1 [ A ] = A

PUSH

PSW

ADI

٧Ţ

VOM:

L,A

```

```

C4.

```

```

PSW

POP

H,%BK1

HVI

M , A

моу

ENDWHILE

X 35

JMP

y6=.

REPEAT

yh7=.

V2(0)=V2(0)+1

A, D

\mathcal{M}(\mathcal{W})

٧2

AUL

L,A

HOV

H.%BK2

MVI

17/18

LOUP

/

XL8=.

EXIT | F V2101=0

XRA

H,%BK2*0400+V2+0

LXI

CMP

XL9

JZ

SET BANK BBK1

4,%BK1

MVI

DEC +B

L,B

MUV

\mathbb{D}\mathbb{C}B

M

EXIT IF C=030

MVI

A,030

CMP

XF3

JZ

ENDLOOP

X \perp \aleph

JMD

XL9=.

])

, INR

Ü

\{ \forall R

UNTIL 6=D

A,D

VCM

CP L

06 -

JXZ

XR7

; *** SUPROUTINE CALLS ***

CALL SUB

SUB

CALL

CALL SUB IF B=INPUT(6)

06

-1 N

В

CHP

SUH

CZ

CALL SUB(A=B, 8=17, DE=DV2[6], M+X1)

VOM

\Lambda , B

B,021

HV |

%3K2*04U0+DV2+06+06

LHLD

D.H

MOV

чо∨

E,L

н,%8К1*040п+X1+0

LXI

SUB

CALL

;*** DOUBLE PRECISION***

DREG DE=BC-2

D,B

MOV

E,C

HOV

DCX

D

Ð

ÐÇX

DREG BC=DV2[0]-1

%8K2*0400+0V2+0+0

LHLD

ΨUV

8,H

C.L

MOV

```

```

C5.

```

```

ncx

15

DREG BC=DV2(X1)

%8K1*0400+x1

LUA

A \downarrow_{I = I}

D V 2

ADI

L,A

MajV

MVI

4,%882

MOV

日,日

TNR

L

C \bullet \mathsf{M}

V(\mathcal{M})

DREG BO=-DE

MUV

A , i)

CMA

м()V

B.A

A,E

VCM

CMA

C,A

M()V

B

] VX

DX DX2=-DY2+8C-1337+DV2[Z1]

%BK2*0400+0Y2+0+0

LHLD

моу

A,4

ÇMA

HOV

Η, 4

VÇM

A,L

ChA

\mathsf{M} \cup \mathsf{V}

L,A

H

1 4 X

DAD

D,-02471

LXI

()

GAG

PUSH

H

%8K1*0400+71

AGJ

ADD

٨

DV2

ADT

MOV

L,A

MVI

H, %BF2

моу

[), M

198

E,M

O(10)

464

Н

DAD

D

SHLD

%8K2*0400+DX2+0+0

DX DV2[X1]=DE-BC-DV2[Y1]

MON

H,D

MOV

L,E

ΜÚV

A , 3

CMA

0.4

HOV

УСИ

A.C.

CMA

E,A

MOA

LNX

D

DAD

D

PUSH

%BK1*0400+Y1

LDA

ADD

DV2

ADI

ипΛ

L,A

MVI

H, %BK2

۷рм

A,M

CMA

иоу

D, A

\{\lambda | R

Į_

MOA

A,M

```

```

Ç6.

CHA

пол

E,A

ΝX

D

q_{\Gamma}q

14

TIAT

p

XCHG

1, 11

%3K1*04U0+X1

T^T L_L \Lambda

٨

DVS

Abl

V(jk)

L,A

H,%BK2

MVI

MOV

M_{\bullet}H

NR

L

VOM

M,E

;*** INTERNAL PROC DECLARATION ***

PROC GARP

GARB=.

BANK UNDEFINED

SINGLE TEMP+0377

TEMP=0377

:THE BANK IS SET BEFORE GARB IS CALLED

TEMP=INPUT(4)

0.4

IN

MVI

L,TEMP+0

\mathbb{M} \cup \mathsf{M}

M,A

RETURN IF TEMP<=7

MVI

A,07

G MP

М

ВÞ

TEMP=7

M()V

M, A

ENDPROC

RET

FINISH

.END

```

MEDIUM LEVEL PROGRAMMING LANGUAGES

FOR MICRO PROCESSORS.

Author Jan-Eric Aspernas Supervisors Leif Andersson Johan Wieslander

# ABSTRACT.

This report of master thesis describes two programming languages for micro processors namely:

MLP for Intel 8008 developed at C.E.R.L., Great Britain and HILP 80 for Intel 8080 developed as master thesis at Lund Institute of Technology.

The compilers generate assembly code and are intended to be implemented on a host computer. The compilers are based on the macro processor STAGE 2, and need about 15 K of core on a PDP-15. The report is written in two parts, which could be read separately.

Detta examensarbete beskriver två programmeringsspråk för mikro-processorer nämligen:

MLP för Intel 8008 utvecklat vid C.E.R.L., Great Britain och HILP 80 för Intel 8080 utvecklat som ett examensarbete vid Lunds Tekniska Högskola.

Kompilatorerna genererar assembler kod och är avsedda att implementeras på en värd-dator. Kompilatorerna är baserade på makro processorn STAGE 2, och kräver ungefär 15 K minne på en PDP-15. Rapporten är skriven i två delar, vilka kan läsas separat.

THE MEDIUM LEVEL PROGRAMMING LANGUAGE MLP FOR THE MICRO PROCESSOR INTEL 8008.

Author Jan-Eric Aspernäs Supervisors Leif Andersson Johan Wieslander

## CONTENTS.

## A INTRODUCTION

## B. 1 THE WORK WITH MLP AT LTH

- B.1.1 GENERAL

- B.1.2 DATA DECLARATIONS

- B.1.3 INDIRECT REGISTER CONTROL

- B.1.4 LOOPS

- B.1.5 SUBROUTINES WITH ARGUMENTS

- B.1.6 OTHER CHANGES OF MLP

## B.2 MLP FOR INTEL 8008

- B.2.1 GENERAL FORMAT

- B.2.2 ABBREVATIONS

- B.2.3 DATA DECLARATIONS

- B.2.4 REGISTER CONTROL

- B.2.5 INDIRECT REGISTER CONTROL

- B.2.6 ASSIGNMENTS FOR EXPRESSIONS

- B.2.7 IF STATEMENTS

- B.2.8 LOOPS

- B.2.9 LABLES, BRANCHES, SUBROUTINE DECLARATIONS

- B.2.10 SUBROUTINE CALLS

- B.2.11 OTHER INSTRUCTIONS IN MLP

- B.2.12 CONDITIONS IN MLP

- B.2.13 ERROR REPORTS

- B.2.14 HARDWARE REGISTER USAGE

- B.2.15 LIST OF LANGUAGE WORDS

- B.2.16 DETAILED SYNTAX

## APPENDIX C TESTPROGRAM IN MLP

This report describes a medium level language for the micro computer Intel 8008. The language is called MLP and is developed at C.E.R.L Great Britain.

This report is based on a part of master thesis at Lund Institute of Technology (LTH), Sweden. The aim of the work at LTH was to test MLP and make it fit a PDP-15, which is the host machine used at LTH. The aim was also to try to improve MLP and increase the efficiency of the generated assembly code.

The next page shows the way from MLP source program to a loaded Intel 8008 Computer.

Chapter B.1 contains a discussion of the work at LTH.

The semantics of MLP is described in part B.2.

Appendix C contains an MLP program, which shows the generated code from some of the MLP statements.

fig 1. From MLP to Intel 8008.

## B. 1. 1. GENERAL

The original MLP from C.E.R.L used PROM banks for the data. As the usage of RAM banks for the data would increase the efficiency of the bank address manipulation, the whole part of the data declaration has been rewritten.

For optimization of the bank address setting during the translation, MLP has an internal variable LASTH, which holds the bank value from the last memory reference. When a new memory reference is made, MLP could check LASTH against the bank address of the variable, and if necessary generate a "LHI instruction". Because of this technique MLP got the opportunity to test for undeclared variables.

## B. 1. 2. DATA DECLARATIONS.

All the variables used must be declared and their bank addresses specified. The above mentioned optimization could be further increased if all the variables are declared in the same bank. In this case LASTH will not be destroyed after a label, as when the jump to the label takes place, the last bank address must be equal to the bank address at the label. For this purpose a SAME BANK statement should be given and could be used provided that, when all statements generating labels are reached, the H register holds the desired bank address. Used subroutines must not change the H register when SAME BANK is valid.

Experience has shown that many applications require very much address manipulation. The indirect register control allows the user to work with addresses in an efficient way. This extension of the original MLP has proved to be very useful.

## B.1.4. LOOPS

The programming language PASCAL has given the idea to the three loops implemented.

# B.1.5. SUBROUTINES WITH ARGUMENTS.

The usage of arguments gives a technique to give entry values to registers before calling a subroutine.

The arguments are register operations, which are carried out before the subroutine is called. The subroutine could be called with any number of arguments.

# B. 1.6. OTHER CHANGES OF MLP.

In some statements of the original MLP the optimization has been improved, why the efficiency of the generated code has increased.

Every digit in the source program is converted to octal by MLP. This is because of the PDP-15 assembler.

Some minor errors in the original MLP templates have also been corrected.

## B.2.1 GENERAL FORMAT.

The general format of the language is:

Declarations Statements Subroutine declarations FINISH

Main rules for statements in MLP:

- Only one MLP statement is allowed per line, except for IF statements.

- 2 Leading tabs and spaces are allowed.

MLP words should be separated with one space.

Logical operators,+,-,= should not be separated

by spaces.

- Two types of comments may be used:

a) comment string

b) statement; comment string

- 4 Names may consist of up to six characters, starting with a letter.

- 5 Empty lines may be used.

- 6 Octal digits are defined by starting with  $\phi$ .

- 7 Integers in MLP should be within the ranges:

-128 to 255 or -\$2\$\$\text{0}\$ to \$377.

Note: Integers >= 128 will set the sign bit,

and therefore be equal to a negative number.

## B. 2. 2 ABBREVATIONS.

r = registers (A,B,C,D,E,H,L or M) c = numeric constant

id = identifier

a = address reference: id, id(id), id(rc)

rac = either of r, a, c ra = either of r, a

mo machine code

M = memory location addressed by H and L

Variables used in the program must be declared and their bank addresses specified:

BANK (constant)

WORDS (list of id or id(c) separated by commas)

The user may define addresses for the words by setting idîc or id(c)îc freely in the list. The words are defined consecutively. The first word is defined Ø if the user does not declare a start address.

GLOBAL (list of id separated by commas)

If you make references to names in other programs, the loader program has to know these names as global, otherwise the loader may not be able to set up a common address for these names.

SAME BANK

This statement is used when all the words are specified in the same bank.

BANK IS (constant)

This statement must be given if SAME BANK is used, and generates a LHI instruction.

Note; Array index runs from \$\noting\$ to i-1.

Only one-dimensional arrays are allowed.

No variables may be preset.

# Datadeclarations of separately compiled subroutines.

What is said above about main programs is valid. In special cases when the H-reg is set in the main program and the subroutine does not change the H-reg, the data declaration should be:

Words statement as above SAME BANK

REG r1=r2ac

Loads r, with the contents of r, ac.

REG r=ra+1

Loads r with the contents of ra and increments r.

REG r=ra-1

Loads r with the contents of ra and decrements r. a=REG r

Loads a memory location with the contents of r.

M=a

Loads the address of a into H and L.

MASK (expression) WITH rac

The expression is evaluated and loaded into A-reg., which then is masked with rac.

## B.2.5 INDIRECT REGISTER CONTROL. (r / M)

REG riac

REG rta+c

REG rta-c

r will be loaded with an address

REG Tr = r c

REG 1r1+1=r20

REG 1r -1=r20

The address specified by  $r_1$ ,  $r_1+1$ ,  $r_1-1$  will be loaded with  $r_2$ c.

REG r1=1r2

REG r1=1r2+1

REG r<sub>1</sub>=1r<sub>2</sub>-1

The contents specified by the address specified by  $r_2$ ,  $r_2+1$ ,  $r_2-1$  will be loaded into  $r_1$ .

PUSH 1r+1=list of rc separated by comma

PUSH Îr-1=list of rc separated by comma

Takes each element in the list and loads them into the address specified by r and then increments or decrements r.

POP list of r= îr2+1

POP list of r=1r2-1

Decrements or increments  $r_2$  and then loads r from the address specified by  $r_2$ . This is carried out for each element in the list.

SET ra=expression ra=expression

The expression may start with an INPUT-statement or an unconditional CALL-statement.

Allowed operators in expressions:

+

\_ ^ ~

• OR

.XR

. AND

. Rotate Instruction in machine code

No brackets are allowed in expressions.

## B.2.7 IF-STATEMENTS.

IF condition THEN

statements on separate lines

ELSE

statements on separate lines

END

IF condition THEN

statements on separate lines

END

IF condition THEN statement ELSE statement END

IF condition THEN statement END

## B.2.8 LOOPS.

REPEAT

statements on separate lines

UNTIL condition

WHILE condition DO

statements on separate lines

ENDWHILE

LOOP

statements on separate lines

EXIT IF condition

statements on separate lines

ENDLOOP

## B. 2.9 LABLES, BRANCHES, SUBROUTINE DECLARATIONS.

Label:statement

Label:

The label is set at the beginning of a line.

GOTO label Unconditional branch to a label.

GOTO label IF condition Conditional branch to a label.

PROC label Subroutine heading

ENDPROC

Subroutine end.

RETURN

Unconditional exit from a subroutine.

RETURN IF condition

Conditional exit from a subroutine.

## B.2.10 SUBROUTINE CALLS.

## a) With Arguments:

Arguments are in fact register operations, which are carried out before calling the subroutine. List of allowed arguments:

REG r=rac

REG r=ra+1

REG rlac

REG rtate

REG Tr=ro

REG frt1=ro

REG r=fr

REG r=fr±1

Note: In this version of MLP "REG" must be omitted.

CALL label (list of arguments)

Unconditional branch to a subroutine

CALL label dist of arguments IF condition Conditional branch to a subroutine.

## b) With expression.

The expression is first evaluated and then loaded into the A-reg.

CALL label (expression)

Unconditional branch to a subroutine.

CALL label (expression) IF condition Conditional branch to a subroutine.

CALL label

Unconditional branch to a subroutine.

CALL label IF condition Conditional branch to a subroutine.

## B.2.11 OTHER INSTRUCTIONS IN MLP.

ra=INPUT(ch)

ra is loaded from input-chanel ch. Ch is a digit between  $\emptyset$  and  $\emptyset$ 7

OUTPUT(ch) = expression

The value of the expression is sent to chanel ch. Ch is a digit between  $\emptyset$  and  $\emptyset$ 27.

HALT

Halts the computer.

CODE list of machine code separated by commas.

The instructions are directly transfered to the generated code.

FINISH

This statement must be given at the end of the source-program.

TITLE character string

This statement makes newpage and the string

is printed on top of every new page.

## B.2.12 CONDITIONS IN MLP.

The conditions refere to the state of the four flip-flops ZERO, CARRY, SIGN, PARITY. These flip-flops may be affected by:

COMPARE expression WITH rac MASK expression WITH rac SET ra=expression Machine code instructions Increment or decrement instructions

In the COMPARE statement the flip-flops sets as follows:

ZERO If expression is equal to rac CARRY If expression is less than rac SIGN If the result of an expression has bit 8 set PARITY If the result of an expression has even parity

- a) condition)::=<flip-flop) TRUE/<flip-flop) FALSE</pre>

- b) Condition: =PARITY OF expression IS ODD/ PARITY OF expression IS EVEN

c) condition ::= expression comparator rac comparator ::=/= / # / > / < .

When the comparators  $\geqslant$  and < is used, the numbers are considered to be positive ( $\emptyset$  to 255), with the exception of  $< \emptyset$  where the numbers are considered to be a signed integer (-128 to +127).

## B.2.13 ERROR REPORTS.

- 1 ILLEGAL SYNTAX

- 2 ILLEGAL CONDITION

- 3 IF/END DIFF.= ....

- 4 LOOP/ENDLOOP DIFF. = ....

- 5 REPEAT/UNTIL DIFF. = ....

- 6 WHILE/ENDWHILE DIFF. = ....

- 7 ILLEGAL USE OF REG ....

- 8 MISSING DECLARATION OF ....

Note: MLP does not check if any array references exceeds its permitted size.

MLP does not check that the declared data type is used in the program, i.e. both Arr and Arr(3) will

## B.2.14 HARDWARE REGISTER USAGE.

be accepted.

## A-reg

The A-reg is used to evaluate expressions and is therefore overwritten when a statement containing an expression is used, except when expression is A.

Note: The SET instruction does not use the A-reg when the expression is a constant \( \nabla \).

The INPUT instruction loads the A-reg with the input signal.

#### E-reg

The E-reg will be overwritten when an array reference is made, except for id(c).

#### M-reg

The M-reg will be overwritten when a memory reference is made. It will also be used in indirect register control except for:

REG rîc REG rîa (-c)(+c), when a is id or id(c)

#### B, C, D-reg

Will never be implicity used by MLP.

Alphabet (A-Z)

Numeral  $(\emptyset-9)$

Spaces

Integer or Octal Arithmetic

Operators: +, -, ., .OR, .XR, .AND

Comparators: =, ≠, ≥, <

Flip-flops: ZERO/CARRY/SIGN/PARITY

States: ODD/EVEN/TRUE/FALSE

Registers: A/B/C/D/E/H/L/M

PARITY OF IS

CODE

COMPARE WITH

REG

OUTPUT

INPUT

SET

IF THEN ELSE END

CALL (IF)

RETURN (IF)

GOTO (IF)

REPEAT UNTIL

WHILE DO ENDWHILE

LOOP EXIT IF ENDLOOP

TALH

PROC ENDPROC

WORDS

BANK

SAME BANK

BANK IS

TITLE

GLOBAL

FINISH

DETAILED SYNTAX OF MLP IN RACKUS NURMAL FORM (NAUR, 1960). 13.

CPRUGRAM>: 1 =

CHATA DEC LIST> STATEMENT LIST> SUBROUTINE LIST> CEND STATEMENT>

STATEMENT LIST>::=

<STATEMENT><NL><STATEMENT LIST>/<NULL>

SUBROUTINE LIST>::=

<SUPROUTINE><SUPROUTINE LIST>/<NULL>

KEND STATEMENT>: :=

FINISH

<subrout | NE>::=

PROC < IDENTIFIER><NL><SUBROUTINE STATEMENT LIST>ENDPROC

KSUBROUTINF STATEMENT LISI>::=

<STATEMENT><NL><SUBROUTINE STATEMENT LIST>/<RETURN STATEMENT>

<NL><SUBROUTINE STATEMENT LIST>/<NULL>

<DATA DEG LIST>::=

CRANK DEC>CHORDS DEC LIST>CSAME BANK STATEMENT>CBANK STATEMENT>

<SAME BANK STATEMENT>::=

SAME BANK<NL>/<NULL>

<BANK DEC>::=

BANK < INTEGER> < NL>/ < NULL>

<BANK STATEMENT>::=

BANK IS CINTEGER>(NL>/(NULL)

<words dec List>::=

WORDS <ADDRESS DEC LIST><NL>/<NULL>

<ADDRESS DEC LIST>::=

<!DENTIFIER>+<!NTEGER>,<ADDRESS DEC LIST>

/<!DENTIFIER>(<!NIFGER>)+<!NTEGER>, <AUDRESS DEC LIST>

/<!DENTIFIER>, <ADDRESS DEC LIST>

/<ldentifier>[<!NIEGER>], <address | Dec LIST>

/<!DENTIFIER>[<!NTEGER>]/<!DENTIFIER>

<STATEMENT>:!=

<SIMPLE STATEMENT>/<BASIC STATEMENT>

/<INDIRECT STATEMENT>/\*<CUMMENT STRING>/HALT

<SIMPLE STATEMENT>::=

<LABEL>:<SIMPLE STATEMENT>/<SIMPLE STATEMENT>;<COMMENT STRING>

/<GUTU STATEMENT>/<COALL STATEMENT>/<ASSIGN STATEMENT>

/<LOOP STATEMENT>/<CONDITIONAL STATEMENT>/<INPUT STATEMENI>

/<OUTPUT STATEMENI>/<NULL>

CHASIC STATEMENI>::=

<LAREL>:<BASIC STATEMENT>/<REGISTER LOAD>/<REGISTER CHANGE>

/<MEMORY REGISTER LOAD>/<MEMORY LOCATION LOAD>/<MASK STATEMENT>

/<COMPARE STATEMENT>/<MASHINE CODE LIST>/<NULL>

<!NDIRECT STATEMENT>::=

LABEL: <INDIRECT STATEMENT>/<INDIRECT REGISTER LOAD>

<COMMENT STRING>::=

<CHAR><COMMENT SIRING>/<NULL>

<LOOP STATEMENT>::=

REPEAT<NL><STATEMENT LIST>UNTIL <CONDITION>

/WHILE <CONDITION> DO<NL><STATEMENT LIST>ENDWHILE

/LOOP<NL><STATEMENT LIST>EXIT IF <CONDITION><NL>

<STATEMENT LIST>ENDLOOP

<GOTO STATEMENT>::=

GUTO (LABEL)/GOTO (LABEL) IF (CONDITION)

CCALL STATEMENT>::=

CALL <IDENTIFIER>/CALL <IDENTIFIER> IF <CONDITION>

/CALL <IDENTIFIER>(<ARGUMENT LIST>)

/CALL <IDENTIFIER>(<ARGUMENT LIST>) IF <CONDITION>

CCONDITIONAL STATEMENT>::=

IF <CONDITION> THEN <STATEMENT LIST> ELSE <STATEMENT LIST>FND

/IF <CONDITION> THEN <STATEMENT LIST>END

KASSIGN STATEMENT>::=

SET <STORE>=<EXPRESSION>/<STORE>=<EXPRESSION>

KINPUT STATEMENT >::=

<SIORE>=[NPUT(<!NPUT CHANNEL>)

**KOUTPUT STATEMENT>::=**

OUTPUT(<OUTPUT CHANNEL>)=<EXPRESSION>

KREGISTER LOAD>::=

REG (USER REGISTER)=(PRIMARY)

KMEMORY LUCATION LOADS::=

<SIORE>=REG <USER REGISTER>

KMEMORY REGISTER LUAD>::=

M=<ADDRESS REFERENCE>

<REGISTER CHANGE>:;=

REG <USER REGISTER>=<USER REGISTER><ARITH OPERATOR>1

CCOMPARE STATEMENT>::=

COMPARE (EXPRESSION) WITH (PRIMARY)

KMASK STATEMENT>::=

MASK CEXPRESSIONS WITH CPRIMARYS

KINDIRECT REGEISTER LOAD>::=

REG <REGISTER>+<ADDRESS REFERENCE>

/REG <REGISTER>+<ADDRESS REFERENCE><ARITH OPERATOR>1

/REG <REGISTER>+<CONSTANT>

/REG <REGISTER>=+<REGISTER>

/REG <REGISTER>=+<REGISTER><ARITH OPERATOR>1

KINDIRECT MEMORY LOCATION LOAD>::=

REG +<REGISTER>=<CONSTANT>

/REG +<REGISTER><ARITH OPERATOR>1=<CONSTANT>

/REG +<REGISTER>#<REGISTER>

/REG +<REGISTER><ARITH OPERATOR>1=<REGISTER>

<STACK OPERATION>::=

```

PUSH t<REGISTER><ARITH OPERATOR>1=<LIST OF RC> /POP <LIST OF REGISTER>=+<REGISTER><ARITH OPERATOR>1

```

<ARGUMENT>!!=

<REGISTER LOAD>/<REGISTER CHANGE>

/<INDIRECT REGISTER LOAD>

/<INDIRECT MEMORY LOACTION LOAD>

<LIST OF RC>::=

<RFGISTER>,<LIST OF RC>/<REGISTER>

/<CONSTANT>,<LIST OF RC>/<CONSTANT>

<LIST OF REGISTER>::=

<REGISTER>,<LIST OF REGISTER>/<REGISTER>

<CONDITION>::=

<SIATUS FLAG><TRUTH STATE>

/<EXPRESSION><COMPARATOR><PRIMARY>

/PARITY OF <EXPRESSION> IS <PARITY STATE>

<STORE>::=

<USER REGISTER>/<ADDRESS REFERENCE>

<EXPRESSION>::=

<CALL STATEMENT><ARITH OPERATOR><ORDINARY EXPRESSION>

/<CALL STATEMENT>.<CODE STATEMENT><ORDINARY EXPRESSION>

/<INPUT STATEMENT><ARITH OPERATOR><ORDINARY EXPRESSION>

/<INPUT STATEMENT>.<CODE STATEMENT><ORDINARY EXPRESSION>

/<ORDINARY EXPRESSION>

<URDINARY EXPRESSION>::=

<TERM>/<ARITH OPERATOR><TERM>

/<ORDINARY EXPRESSION><ARITH OPERATOR><TERM>

<PRIMARY>::=

<USER REGISTER>/<ADDRESS REFERENCE>/<CONSTANT>

<CODE STATEMENT STRING>::=

<CODE STATEMENT>,<CODE STATEMENT STRING>

/<CODE STATEMENT>

<TERM>::=

<PRIMARY>/<PRIMARY>.<CODE STATEMENT>

<LABEL>::=

<LETTER DIGIT STRING>

<ADDRESS REFERENCE>!!=

<!UENTIFIER>/<!DENTIFIER>(<!NDEX>)

<!NDEX>::=:

<CONSTANT>/<REGISIFR>/<IDENTIFIER>

<!DENTIF [ER>li=

<LETTER><LETTER blg|! STRING>/<NON-REGISTER LETTER>

<CONSTANT>::=

<!NTEGER>/<ARITH OPERATOR><!NTEGER>/"<CHAR>"

<POSITIVE CONSTANT>::=

<INTEGER>/+<INTEGER>/"<CHAR>"

<REGISTER>::=

A/9/C/D/E/H/L

<STATUS FLAG>::=

ZERU/CARRY/SIGN/PARITY

<FRUTH STATE>::=

TRUE/FALSE

<PARITY STATE>::=

ODD/EVEN

<arith operator>::=

+/-

<NON-REGISTER LETTER>::=

F/G/I/K/O.../Z

<nL>::=

START NEW LINE

<NULL>::=

```

HANK 1

WURUS P1+25,01,R1+050,S1+100,TEMP[50],T1

P1=031

01 = 032

R1=050

51=0144

TEMP=0145

T1=0227

GLOBAL SUB, SUB4

.GLOBL SUB, SUB4

SAME BANK

BANK IS 1

01

LHI

***** PEGISTER CONTROL ****

REG 8=25

LBI

031

REG C=D+1

LCD

INC

REG D=TEMP(24)+1

LLI

TEMP+030

LUM

IND

REG D=TEMP[T1]-1

LLI

Ti

LAM

ADI

TEMP

LLA

LUM

DCD

TEMP[012]=REG A

LLI

TEMP+012

LMA

M=TEMP[P1]

P1

LLI

LAM

ADI

TEMP

LLA

MASK 24+QI WITH 255

030

LAI

LLI

Q1

ADM

NOT

0377

***** INDIRECT REGISTER CONTROL *****

REG B+TEMP(200]+8

TEMP+0310+010

TR1

REG B+TEMP[Q1]-077

LAM

ADI

TEMP-077

LBA

REG +D=8 ...

LLD

LWb

REG +L+1=9

INL

LMI

011

REG +8-1=0

LLK

DCL

```

```

LMC

C2.

REG B=+C

LLC

LBN

REG C=+L+1

INL

LCM

REG D=+B-1

LLR

DUL

LDM

PUSH +8+1=0,25,0

LLB

LMI

INR

LLB

LMI

031

INR

LLB

LMC

1118

POP A,P,C=+L-1

DCL

LAM

DCL

LBH

ncu

LCM

**** ASSIGNMENTS ****

SET A,P,C=U

XKV

LBA

LOX

SET T1=-P1+7

LLI

P1

SUM

ADT

U7

LLI

11

LMA

SET TEMP[7]=-8

LLI

TEMP+07

LMI

-010

SET TEMP(U1)=TEMP(P1)-TEMP(T1)

LLI

Ρ1

LAM

ADI

TEMP :

LLA

LAM

LEA

LLI

11

LAM

ADI

TEMP -

LLA

LAE

SUM

LEA

LLI

U1

LAM

TEMP.

ADT

LLA

LAE

LMA

SET B=[NPU1(5)+S1

```

```

5*2+101

03.

S1

LLI

ADM

LBA

SET C=CALL SUB+19

CAL

SUB

ADI

023

LUA

**** LABLES, GOTO-STM., IF-STM.

LAB1:

LAB1=.

LAB2:

GUTO LAB! .

LAB2=.

JHP

LAB1

GUTO LAB1 IF PARITY OF Q1 IS ODD

LLI

Q1

LAM

CPI

0

JIP

LAB1

IF PIKO THEN U1=0

LLI

Р1

LAM

CPI

0

JFS

X1

XRA

LLI

U1

LMA

ELSE S1=0 END

JMP

X 2

X1=.

XRA

LLI

S1

LHA

X2=.

IF PIKO THEN

LLI

P1

LAM

CPT

Ü

JFS

XЗ

IF Q1=0 THEN R1=0

LLI

01

LAM

CPT

0

JF 7.

X 4

XRA

LLI

R1

LMA

S1=0

LLI

S1

LMA

ELSE T1=0

JMP

X5

X4=.

XHA

1.1.1

T1

LHA

END

X 5 = .

ELSE

4KL

Х6

X3=.

P1=0

```

XRA

## HILP 80.

A HIGH LEVEL PROGRAMMING LANGUAGE FOR INTEL 8080.

Author Jan-Eric Aspernäs Supervisors Leif Andersson Johan Wieslander

## CONTENTS.

- 1. INTRODUCTION

- 2. SYNTAX OF HILP 80

- 3. SEMANTICS OF THE LANGUAGE HILP 80

- 1. General rules

- 2. Abbreviations

- 3. Head

- 4. Bank address manipulation

- 5. Register operation

- 6. Double register operation

- 7. Procedure calls with arguments

- 8. Conditions in HILP 80

- 9. INC and DEC statements

- 10. Hardware register usage

- 11. Error reports

- 12. List of language words

## APPENDIX

- A. Optimization technique

- B. Direct load and store in single precision

- C. Test program in HILP 80

This report describes a High Level Programming Language, HILP 80, for micro processors. This version of HILP 80 is made for INTEL 8080, but could be changed to fit any simular micro processor.

The compiler is based on STAGE 2 (Waite, 1973). The compiler generates assembly code. A flow diagram (fig 1) shows the way from HILP 80 source program to a running Intel 8080.

The compilation is intended to take place on a host machine. At Lund Institute of Technology (LTH), a PDP-15 is used as a host machine. The compiler is almost machine independent, and could be implemented on other computers. The macro processor STAGE 2 requires about 3 K of core, and the templates need about 12 K with high degree of packing. The translation time for the in appendix given exemple was about 65 seconds.

The language HILP 80 could be used at different levels down to assembly code. The medium and low level statements are valuable to increase the efficiency e.g. in loops.

Improvals of the limited data structures and arithmetic facilities are under discussion.

## EFFICIENCY OF HILP 80.

The main responsibility for the efficiency of the generated code lies in the hands of the user. Thus it is up to the user to decide e.g. whether registers should be used instead of address references in order to increase the efficiency. It is hard to measure the efficiency of HILP 80 depending on the various levels of the statements. However it is always possible to generate a code with very high degree of efficiency.

When addressing the data, INTEL 8080 uses register pair H&L, where H contains the high address (= bank) and L contains the low address. However, the A register could be loaded and stored directly using a two word address or loaded and stored indirectly using register pairs B&C or D&E. The different addressing facilities and the hardware usage of register pair H&L as an accumulator in double precision makes it hard to control the addressing in an efficient way. However, HILP 80 mostly solves this problem for the user, but in some cases the user could act in order to increase the efficiency. For this purpose HILP 80 has two "Bank manipulation statements".

## REFERENCE.

Waite, W.M., 1973, Implementing Software for Non-Numeric Applications, Prentice-Hall.

fig 1. From HILP 80 source to loaded INTEL 8080.

The syntax of HILP 80 is described in flow diagram form. The terminal symbols of the language are enclosed by circles or by ovals e.g. (REPEAT). The nonterminal symbols are written with small letters and enclosed by rectangles e.g. identifier.

The semicolon is the "end of statement" marker.

In the actual source program it has the following equivalent forms (2 denotes carriage return):

- 1. ; 2

- 2. 2

- 3. ; Any sequence of characters 2

statement

### statement continued

### register operation

## expression

## condition

## 3.1 GENERAL RULES.

Main rules for statements in HILP:

- 1 Only one statement is allowed per line.

- Leading tabs and spaces are allowed. HILP words should be separated by one space. Logical operators, +, -, ., = should not be separated by spaces.

- Comments may be used in HILP:a) :comment string

- b) statement; comment string

- A Names may consist of up to six characters, starting with a letter, and for constants starting with #.

- 5 Empty lines may be used.

- Numbers are interpreted as octal if they start with  $\phi$  and decimal otherwise.

- 7 Integers in HILP should be within the ranges:

SINGLE: -128 to +127

-0200 to +0177

DOUBLE: -32768 to +32767

-0100000 to +077777

### 3.2 ABBREVIATIONS.

register (A,B,C,D,E,H,L) r constant С identifier id address reference (=id, id[expression]) 8 rac either r or a or c above either r or a above ra either r or c above ro Intel assembly code code memory location addressed by H and L M double register (BC, DE, HL) dr

3.3 <u>HEAD</u>. 11.

## a) CONST declaration.

The user may define constants, which will be replaced by the assembler with their current values. The constants could be useful e.g. in the bank declaration.

## b) VARIABLE declaration.

### 1. BANK c

Variables used in the program must be declared and their bank addresses specified. The bank number given in the declaration is valid until another bank declaration is made.

SINGLE declaration. DOUBLE declaration.

The user may define addresses for the variables by stating to after the variables in the list, or state to for the first variable and then let the others be defined consecutively until another address is stated. The first word declared in a bank is given the address of if the user does not give a start address. No error report will be given if the user declares addresses greater than 255 (\$\phi\_{377}\$).

#### 2. BANK UNDEFINED

This bank declaration could be used in procedures, where the variables define different memory locations (different high addr., same low addr.) depending on the actual value in the H register.

SINGLE declaration as above. DOUBLE declaration as above.

### c) GLOBAL declaration.

If references are made to names in other programs, the loader program has to know that these names are global, otherwise the loader will not be able to set up common addresses for these names.

## d) SET STACK c:c.

As HILP implicitly uses the stack, this statement must always be given. The first constant is the bank address and the second is the low address.

NOTE: Array index runs from Ø to i-1.

Only one dimensional arrays are allowed.

No variables may be preset.

## a) GENERAL.

HILP translates the source program statement by statement going once from top to bottom. This technique causes some optimization problems when a label is generated by HILP e.g. in loop statements. The problems mentioned arise from the fact that when a label is jumped to during the execution, the translation path is different from the execution path.

For optimization during the translation, HILP uses internal variables:

LASTA last value of the A register.

LASTM last memory reference addressed by M (H&L).

LASTH last bank value in the H register.

As for LASTH, when M is to be set to an address of a variable, HILP will be able to check LASTH against the bank address of that variable and if equal not update the H register. In case of BANK UNDEFINED, LASTH is not used since the user in this case is supposed to take full responsibility for the bank address setting (HILP will always assume that the H register is correctly set).

#### BANK ADDRESS MANIPULATION STATEMENTS.

SET BANK C.

The constant c is loaded into the H register if LASTH is different from c.

BANK IS c.

This statement sets LASTH to c. It is an information to the translator and will never generate any code.

## 1) GENERAL PROGRAMMING.

HILP 80 will take full responsibility for the bank address manipulation. Thus the user does not have to care about the internal usage of LASTH. Some optimization of the bank address setting could be obtained, especially if all the variables are specified in the same bank. See Appendix A.

## 2) THE USAGE OF POINTER OPERATIONS.

The statements: REG † ... = ...

REG ... = † ...

INC † ...

DEC † ...

will assume that the H register is correctly set. To prevent errors, HILP 80 will generate an error report (NO BANK IN THE H REGISTER) if LASTH has been destroyed when one of the above mentioned statements is reached. In this case the user must give:

- 1. SET BANK c if the value of H is uncertain.

- 2. BANK IS c if the value of H is the desired bank address.

LASTH will be destroyed in the following statements:

REG H=... H=expression POP HL DREG HL ... DREG dr=a,+a,-a (11,2) DX ...=... .code when H is changed. When \*M is incremented or decremented. label: PROC CALL REPEAT LOOP (See Appendix A for further details) ENDLOOP WHILE ENDWHILE END

NOTE: Some statements containing variables will implicitly set the bank address in the H register. See Appendix B for further details.

This type of bank declaration could be used e.g. in procedure declarations. All variables declared in the head must refer to BANK UNDEFINED. The user must garantee that the H register is updated before using statements containing variables with their bank addresses unspecified.

No error report will be given if LASTH is destroyed in following statements:

REG ...= ...

REG ...= 1...

INC 1...

DEC 1...

In double precision the DX statement is reduced to the following allowed types when variables with their bank addresses unspecified are used:

DX a=dr

DX dr="expression with dr and c. The expression may start with a, +a, -a."

NOTE: For internal procedures, where the main program has specified bank addresses for the variables, a reference to such a variable could cause an adjustment of the H register according to the rules for addressing given in Appendix B.

# d) NO VARIABLES DECLARED.

This type of head could be used e.g. in procedure declarations. No error report will be given if LASTH is destroyed in following statements:

NOTE: For internal procedures, where the main program has specified bank addresses for the variables, a reference to such a variable could cause an adjustment of the H register according to the rules for addressing given in Appendix B.

a) r<sub>1</sub>=r<sub>2</sub>ac(±1)

Register  $r_1$  will be loaded with the value of  $r_2$  ac, then  $r_1$  will be incremented or decremented if necessary.

b) rfa(±1)

Register r will be loaded with the low address of a, a-1, a+1.

c) Mia(±1)

Register L will be loaded with the low address of a. The bank address of a is loaded into the H register. Register H&L is incremented or decremented if necessary.

d)  $f_{r_1}(\pm 1) = r_2 c(\pm 1)$

The value of  $r_1$  is moved to register L. Register L is incremented or decremented if necessary. The value of  $r_2$ o( $\pm 1$ ) is moved to the memory.

e) M(±1)=r2c(±1)

Register H&L is incremented or decremented if necessary. The value of  $r_2c(\pm 1)$  is moved to the memory.

f) r<sub>1</sub>=**f**r<sub>2</sub>(±1)

The value of  $r_2$  is moved to register L. Register L is incremented or decremented if necessary. Register  $r_4$  will be loaded from the memory.

g)  $r_1 = \uparrow M(\pm 1)$

Register H&L is incremented or decremented if necessary. Register  $\mathbf{r_4}$  will be loaded from the memory.

NOTE: Any memory reference d) to g) above will assume that the H register is correctly set.

a) dr,=c

The constant will be loaded into double register dr.

b) dr<sub>1</sub>=dr<sub>2</sub>,a (±1,2)

Double register dr, will be loaded with the value of dr<sub>2</sub>,a. Then if necessary, dr, will be incremented or decremented once or twice.

c)  $dr_1 = -dr_2$ , a (±1,2)

The value of dr<sub>2</sub>, a is complemented via the A register before loaded into dr<sub>1</sub>. Then dr<sub>1</sub> will be incremented or decremented once or twice if necessary.

#### 3.7 PROCEDURE CALLS WITH ARGUMENTS.

Arguments are register operations or double register operations, which are carried out before the procedure is called. The same procedure could be called with any number of arguments.

Example: CALL SUB(A=B, DE=07745) is equivalent to:

REG A=B

DREG DE=07745

CALL SUB

#### 3.8 CONDITIONS IN HILP 80.

The conditions refer to the state of the four flip-flops: ZERO, CARRY, SIGN and PARITY. These flip-flops may be affected by:

COMPARE rac WITH expression expression evaluating Assembly code Increment or decrement instructions

In the COMPARE statement the flip-flops are set:

ZERO If (expr. - rac) = 0 CARRY If (expr. - rac) < 0

#### 3.9 INC and DEC statements.

These statements shall be interpreted as: Set up the pointer to the memory, then increment or decrement the value addressed by M.

#### a) SINGLE PRECISION.

The A register is used to evaluate expressions and is therefore overwritten when a statement containing an expression is used, except for:

ra=c (c≠0) a=a+1 a=a-1 a=r

NOTE: The INPUT statement loads the A register.

The OUTPUT statement takes the value from A.

M (H&L) will be overwritten when a memory reference is made, except for special cases. See Appendix B.

#### b) DOUBLE PRECISION.

Any address reference in double precision will use HL.

In the DX statement HL is used to evaluate expressions. DE is used for temporary storage when address references or constants # ±1,2 are used.

Since the hardware only allows double add to HL, subtractions of address references and double registers will be carried out via complementing in the A register.

#### 3.11 ERROR REPORTS.

ILLEGAL SYNTAX

ILLEGAL CONDITION

IF/END DIFF =

LOOP/ENDLOOP DIFF =

REPEAT/UNTIL DIFF =

WHILE/ENDWHILE DIFF =

NO EXIT IN LOOP/ENDLOOP

NO BANK IN H REGISTER

MISSING DECLARATION OF

MISSING BANK DECLARATION

REMOVE TRAILING SPACE FROM

NOTE: HILP does not check that the declared data type is used in the program, e.g. both ARR and ARR(3) will be accepted.

HILP does not check if any array references exceed their permitted size.

```

Alphabet (A-Z)

```

Integers (0-9)

Spaces

1 #

Operators: + - .ADDC .SUBB .XOR .OR .AND

Rotate operators: .RAR .RAL .RRC .RLC

Comparators: = /= <= >

Flip-flops: ZERO CARRY SIGN PARITY

States: TRUE FALSE PLUS MINUS ODD EVEN

Register: A B C D E H L

Double register: BC DE HL

M

CONST

BANK

SINGLE

DOUBLE

GLOBAL

BANK IS

UNDEFINED

SET BANK

SET STACK

OUTPUT

INPUT

REG

CALL (IF)

GOTO (IF)

RETURN (IF)

WHILE DO ENDWHILE

REPEAT UNTIL

LOOP EXIT IF ENDLOOP

IF THEN ELSE END

COMPARE WITH

POP PUSH

PSW

INC DEC

DREG

DΧ

PROC ENDPROC

FINISH

# 1. REGISTER USAGE.

The usage of registers instead of address references will increase the efficiency, which is very valuable in loops.

Consider the following example, where V and I refer to bank 1.

| Source code. |       | Generated code. |            |

|--------------|-------|-----------------|------------|

| I=0          |       | XRA             | A          |

|              |       | STA             | 0400+I     |

| REPEAT       | XR1=. |                 |            |

| V[I]=O       |       | LDA             | 0400+I     |

|              |       | ADI             | <b>v</b>   |

|              |       | MOV             | L, A       |

| •            |       | MVI             | H,1        |

|              | ,     | XRA             | <b>A</b> . |

|              |       | MOV             | M, A       |

| I∞I+1        | •     | MVI             | L,I        |

|              |       | INR             | M          |

| UNTIL I=031  |       | MVI             | A,031      |

|              |       | CMP             | M          |

|              |       | JNZ             | XR1        |

|              |       |                 |            |

| SET BANK 1   |       | IVM             | H,1        |

| REG LTV[0]-1 | -     | MVI             | L, V-1     |

| REG ATV[030] |       | MVI             | A,V+030    |

| REPEAT       | XR1=. |                 |            |

| BANK IS 1    |       | •               |            |

| REG † L+1≖O  |       | INR             | L          |

| -            |       | MVI             | M,O        |

| UNTIL L=A    | •     | CMP             | L          |

| •            |       | JNZ             | XR1        |

a) STATEMENTS WHICH IMPLICITLY DESTROY LASTH.

Label:

The label could be jumped to with different banks in the H register.

Incrementing or decrementing fM.

As H&L is incremented or decremented in this case, the H register also could be adjusted.

CALL

The procedure may have changed the H register.

PROC

The procedure could be called with different bank values in the H register.

END (from IF THEN)

LASTH will be destroyed if LASTH after the condition is evaluated, is different from LASTH just before END.

END (from IF THEN ELSE)

LASTH will be destroyed if LASTH just before ELSE is different from LASTH just before END.

REPEAT

LASTH just before REPEAT could differ from LASTH

after the condition in UNTIL is evaluated.

LOOP

LASTH just before LOOP could differ from LASTH just before ENDLOOP.

ENDLOOP (Two or more EXITs in the LOOP)

LASTH after the condition evaluating in the EXITs could differ.

WHILE

LASTH just before WHILE could differ from LASTH

just before ENDWHILE.

ENDWHILE

LASTH will be destroyed unless the condition evaluating in WHILE will set LASTH.

When a label is generated by HILP, LASTH will be destroyed. Thus an adjustment of the H register will take place when M is to be set to a variable. This updating of the H register could be unnecessary if the value is equal to the value of H when the jump takes place. To inhibit an unnecessary adjustment of the H register, the user may give a BANK IS c statement after the following statements:

label:

PROC

CALL

REPEAT

LOOP

ENDLOOP

WHILE

ENDWHILE

In this case the user must garantee that:

The problems discussed under a) could not occur. The H register already holds the value c. The SET BANK c statement could be used to update the H register.

Consider the following example, which is the same as given in 1). V and I are specified in bank 1.

| Source code. |       | Generated | code.     |

|--------------|-------|-----------|-----------|

| I=O          |       | XRA       | <b>.A</b> |

|              |       | STA       | 0400+I    |

| SET BANK 1   |       | MVI       | н, 1      |

| REPEAT       | XR1=. |           |           |

| BANK IS 1    |       |           |           |

| V(II=O       |       | LDA       | 0400+I    |

|              |       | ADI       | ν         |

|              |       | MOV       | L, A      |

|              |       | XRA       | A         |

|              |       | MOV       | M, A      |

| I=I+1        |       | MVI       | L,I       |

|              |       | INR       | M         |

| UNTIL I=031  |       | MVI       | A,031     |

| •            |       | CMP       | M         |

| •            |       | JNZ       | XR1       |

Compared to the example given in 1) the improval is that the instruction "MVI H,1" is moved outside the loop. The technique given is most valuable when all the variables are specified in the same bank.

### APPENDIX B.

## DIRECT LOAD AND STORE IN SINGLE PRECISION.

Most memory references use H&L (M), when addressing variables, but the A register could be loaded and stored directly without using M. In this case the instructions LDA and STA are used instead of MOV A,M and MOV M,A.

Definition: simple addr = id or id[c].

Direct load and store of the A register will be used:

- When the expression has no address references, except that it may start with a simple addr.

- 2 Simple addr=expression

- 3 REG A=simple addr(±1)

#### APPENDIX C.

# GENERATED CODE. HILP 80 STATEMENTS.

```

CONST 08K1=011,08K2=19,0STPK=3

%8K1=011

%8K2=023

%STBK=03

PANK ORKI

SINGLE X1+96, Y1, Z1, V1(10), TEMP1+0377

X1=0140

Y1 = X1 + 01

21 = Y1 + 01

V1 = Z1 + 01

TEMP1=0377

BANK BRK2

SINGLE V2[9], X2, Y2, Z2

V 2 = 0

X2=V2+011

Y2=X2+01

nouble Dv2(6),DX2,DY2+0350,D72

22=Y2+01

DV2=22+01

DXS=DAS+09+09

DY2=0350

DZ2=DY2+01+01

SINGLE TEMP2+0377

TEMP2=0377

GLOBAL SUB, LABEL

.GLOBL SUB.LABEL

SET STACK OSTBK:255

SP, %STRK #0400+0377

LXI

**** REGISTER OPERATIONS ***

REG A=0

\Lambda , 0

MVI

REG A=R

A,B

MOV

REG B=8-1

В

DCR

REG C=V1[6]

H,%BK1*0400+V1+06

LXI

C,N

۷ОМ

REG C=V2[X1-X2]-1

%8K1*0400+X1

LDA

H,%BK2*0400+X2+0

LXI

รบจ

٧2

ADI

L,A

VOM

C.M

VCM

С

DÇR

REG M+Y1

H,%BK1*0400+Y1+0

LXI

REG L+Y2

L, Y2

HVI

SET BANK DRK1

```

```

REG C=+C-1

C2.

L,C

MOV

DCR

L

MOV

C,H

REG +L+1=D+1

INR

M, D

MOV

INR

М

SET BANK OPKS

H,%BK2

MVI

DEC +B

L,A

VOM

М

DOR

: *** ASSIGNMENTS OF EXPRESSIONS ***

V2[X1]=V2[X1]-1

%BK1*0400+X1

LDA

ADI

٧2

VUM

L,A

DCR

М

V1[0]=V2[x1]+Y1

VOM

H,%8K1*0400+Y1+0

LXI

ADD

%BK1*0400+V1+0

STA

21=0

XRA

A

%BK1*0400+71

STA

7.2 = 7

H, %BK2*0400+Z2+0

LXI

MVI

M,07

Y1=8

H, %BK1 * 0400 + Y1 + 0

LXI

M,R

MOV

C=D

C,D

MOV

A5(5)=0

STA

%BK2#0400+V2+02

OUTPUT(6) = INPUT(15) + X1

017

IN

MVI

L , X1+0

М

ADD

OUT

06

V2[C.AND X2]=-25+Y1.AUDC Y2.RAR-V1[Y2.OR V2[V1[Y1]]]

MVI

A,-031

L, Y1+0

MVI

ADD

H, %BK2*0400+Y2+0

LXT

ADC

RAR

PUSH

PSW

MOV

A,M

PSW

PUSH

%BK1*0400+Y1

LDA

٧1

ADI

L,A

MOV

H, %BK1

MAI

MOV

A,M

٧2

ADI

MOV

L,A

PSW

POP

H, %BK2

MVI

ORA

М

٧1.

ADI

```

```

03,

```

```

L,A

- MAY

POP

PSW

H, XHK1

1.14

SU₽

Μ.

PSW

PUSH

VOM

A,C

H,%8K2*0400+X2+0

LXI

ANA

М

ADI

۸5

MOV

L,A

P()P

PSW

VOM

M \cdot A

:*** | F STM, GOTO, STM, LOOPS ***

JIF 0≠V2[X1] THEN

%RK1*0400+X1

LDA

٧2

ADI

MOV

L,A

A,M

VOM

0

CPI

X1

7.12

X1 = X1 - 1

H,%BK1*U4U0+X1+0

LXI

М

DCR

FLSE

X 2

JWb

X1=.

V2[X1]=0

XRA

M,A

MOV

END

X2=.

GOTO LABEL IF 71=0

XRA

H, %8 K1 * 040 N + Z1 + 0

LXI

CMP

LABEL

JZ

GOTO L

JMP

L:

LOOP

L=.

XL3=.

A=A.RAR

RAR

EXIT IF CARRY TRUE

J¢

XL4

A = -A

CMA

INR

FXIT IF SIGN PLUS

XL4

JP

ENDLOOP

9MP

XL3

XL4=.

WHILE P<=A DO

XW5=.

CMP

8

X 6

JΜ

REG A=A-1

DCR

A

V1[A]=A

PSW

PUSH

V1

ADI

MÓV

L . A

```

```

C4.

PSW

H,%BK1

M \cdot A

ENDWHILE

X 45

REPEAT

V2(D)=V2(D)+1

A,D

٧2

L,A

H,%BK2