# LUND UNIVERSITY

## **Exploring Processor and Memory Architectures for Multimedia**

Iranpour, Ali

2012

Link to publication

Citation for published version (APA): Iranpour, A. (2012). Exploring Processor and Memory Architectures for Multimedia. [Doctoral Thesis (compilation), Department of Computer Science].

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

# **Exploring Processor and Memory** Architectures for Multimedia

Ali R. Iranpour

Lund 2012

LUND UNIVERSITY

This thesis is submitted to the Board of Research: FIME --- Physics, Informatics, Mathematics and Electrical Engineering --- at Faculty of Engineering, Lund University, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering.

ISBN 978-91-976939-6-7 ISSN 1404-1219 Dissertation 38 ,2012 LU-CS-DISS:2012-1

Department of Computer Science Lund University P.O. Box 118 SE-221 00 Lund Sweden

## Abstract

Multimedia has become one of the cornerstones of our 21<sup>st</sup> century society and, when combined with mobility, has enabled a tremendous evolution of our society. However, joining these two concepts introduces many technical challenges. These range from having sufficient performance for handling multimedia content to having the battery stamina for acceptable mobile usage. When taking a projection of where we are heading, we see these issues becoming ever more challenging by increased mobility as well as advancements in multimedia content, such as introduction of stereoscopic 3D and augmented reality.

The increased performance needs for handling multimedia come not only from an ongoing step-up in resolution going from QVGA (320x240) to Full HD (1920x1080) a 27x increase in less than half a decade. On top of this, there is also codec evolution (MPEG-2 to H.264 AVC) that adds to the computational load increase. To meet these performance challenges there has been processing and memory architecture advances (SIMD, out-of-order superscalarity, multicore processing and heterogeneous multilevel memories) in the mobile domain, in conjunction with ever increasing operating frequencies (200MHz to 2GHz) and on-chip memory sizes (128KB to 2-3MB). At the same time there is an increase in requirements for mobility, placing higher demands on battery-powered systems despite the steady increase in battery capacity (500 to 2000mAh). This leaves negative net result interms of battery capacity versus performance advances.

In order to make optimal use of these architectural advances and to meet the power limitations in mobile systems, there is a need for taking an overall approach on how to best utilize these systems. The right trade-off between performance and power is crucial. On top of these constraints, the flexibility aspects of the system need to be addressed. All this makes it very important to reach the right architectural balance in the system.

The first goal for this thesis is to examine multimedia applications and propose a flexible solution that can meet the architectural requirements in a mobile system. Secondly, propose an automated methodology of optimally mapping multimedia data and instructions to a heterogeneous multilevel memory subsystem. The proposed methodology uses constraint programming for solving a multidimensional optimization problem.

Results from this work indicate that using today's most advanced mobile processor technology together with a multi-level heterogeneous on-chip memory subsystem can meet the performance requirements for handling multimedia. By utilizing the automated optimal memory mapping method presented in this thesis lower total power consumption can be achieved, whilst performance for multimedia applications is improved, by employing enhanced memory management. This is achieved through reduced external accesses and better reuse of memory objects. This automatic method shows high accuracy, up to 90%, for predicting multimedia memory accesses for a given architecture.

## Contents

| Abstra  | Abstractiii                                             |    |  |

|---------|---------------------------------------------------------|----|--|

| Conter  | nts                                                     | v  |  |

| Prefac  | e                                                       | ix |  |

| Ackno   | wledgements                                             | xi |  |

| 1 Intro | duction                                                 |    |  |

| 1.1     | Background                                              |    |  |

| 1.2     | Motivation                                              |    |  |

| 1.3     | Structure of the thesis                                 |    |  |

| 2 Chal  | lenges with Multimedia Applications in Embedded Systems |    |  |

| 2.1     | Embedded Architectures for Video and Audio              | 21 |  |

| 2.2     | Multimedia Processing                                   |    |  |

| 2.3     | Multimedia Memory                                       |    |  |

| 3 Relat | ted work                                                |    |  |

| 3.1     | Processing                                              |    |  |

| 3.2     | Memory                                                  |    |  |

| 4 Pape  | rs Survey                                               | 47 |  |

| 5 Cont  | ributions                                               |    |  |

| 6 Conc  | clusions and Future Trends                              | 53 |  |

| 7 Bibli | ography                                                 | 57 |  |

| 8 Inclu | ided Papers                                             | 67 |  |

|         | uation of SIMD Architecture Enhancement in Embedded Pr  |    |  |

| 1.1     | Introduction                                            | 70 |  |

| 1.1     | Media applications impact on embedded architectures     |    |  |

| 1.3     | Baseline architecture                                   |    |  |

| 1.4   | Methodology                 | 75 |

|-------|-----------------------------|----|

| 1.5   | Experiments and Discussion  | 77 |

| 1.6   | Related work                | 83 |

| 1.7   | Conclusions and future work | 84 |

| Refer | ences                       | 84 |

###

|       | Introduction              |     |

|-------|---------------------------|-----|

|       | ARM Architecture          |     |

| 2.3   | MPEG-4 Application        |     |

| 2.4   | Methodology               |     |

| 2.5   | Experimental Results      |     |

| 2.6   | Discussion of the Results |     |

| 2.7   | Conclusion                | 100 |

| Refer | ences                     | 100 |

####

| 3.1  | Introduction                        | 104 |

|------|-------------------------------------|-----|

| 3.2  | Video Application                   | 105 |

|      | Processor Architecture              |     |

| 3.4  | Memory Architecture                 | 107 |

|      | Methodology                         |     |

| 3.6  | Experimental Results and Discussion | 109 |

| 3.7  | Related Work                        | 118 |

| 3.8  | Conclusions                         | 119 |

| Refe | rences                              | 119 |

|      |                                     |     |

####

|      | **********************************  |     |

|------|-------------------------------------|-----|

| 4.2  | Video Application                   | 125 |

| 4.3  | Processor Architecture              |     |

| 4.4  | Methodology                         | 128 |

|      | Experimental Results and Discussion |     |

|      | Related work                        |     |

| 4.7  | Conclusions                         |     |

| Refe | rences                              | 137 |

|      |                                     |     |

| 5.1   | Introduction               | 140 |

|-------|----------------------------|-----|

| 5.2   | Related Work               | 141 |

|       | Our Approach               |     |

| 5.4   | Experiments and Evaluation | 144 |

| 5.5   | Conclusions                | 154 |

| Refer | ences                      | 154 |

## Preface

This thesis summarizes the results of my academic work in the Embedded Systems Design Laboratory (ESDlab) at the department of Computer Science, Lund University, for the Ph.D. degree in Computer Science. The main contributions of this thesis are derived from the following publications;

- Evaluation of SIMD Architecture Enhancement In Embedded Processors for MPEG-4, in Proc. Symposium on Digital Systems Design (DSD-04), Rennes, France, August 31 September 3, 2004

- Analysis of Embedded Processors for Streaming Media Applications, in Proc. of the 8th Workshop on Computer Architecture Evaluation using Commercial Workloads (CAECW-8), San Francisco, USA, February. 12, 2005.

- *Memory Architecture Evaluation for Video Encoding on Enhanced Embedded Processors*, in Proc. Embedded Computer Systems: Architectures, MOdeling, and Simulation (SAMOS VI), Samos, Greece, July 17-20, 2006.

- Performance Improvement for H 264 Video Encoding using ILP Embedded Processor, in Proc. of the 9th Euromicro Conference on Digital System Design, Cavtat/Dubrovnik, Croatia, August 30th - September 1st, 2006.

- Design Space Exploration for Optimal Memory Mapping of Data and Instructions in Multimedia Applications to Scratch-Pad Memories, in Proc. of 7<sup>th</sup> ESTIMedia 2009, Grenoble, France, October 15-16, 2009.

## Acknowledgements

Thanks to contributors goes here.

Lund, xxxx 2011 Ali R. Iranpour

# Introduction

"Who Dares Wins"

## Chapter 1

## Introduction

In this chapter, we present a brief overview of the context and motivations behind the work presented in this thesis.

## 1.1 Background

Processor and memory architectures are fundamental components when exploring the design space in embedded and other resource limited systems. This resource limitation is in terms of power and energy as well as performance and cost, with the consequence of being a never ending trade-off between these factors. The ultimate goal is to get good enough performance in a reasonable power envelop. Taking a historic look at the evolution of a category of battery operated embedded systems, mobile terminals or handset, one can see an interesting transformation. These devices started as voice only with very limited computation performance, where at best they included a microcontroller, such as Zilog Z80 (8-bit microprocessor). This small processor was combined with other hardwired ASICs to handle the GSM communication protocol. These systems where often build on a printed wire board (PWB) where discrete ASICs, and other radio components where combined into a handset. The next generation of devices saw an integration of the digital discrete components to baseband ASICs and the radio components into RF ASICs. The digital basebands often included CPU, DSP and accelerators.

Around the time when second generations of mobile SoCs were introduced into handheld devices, the mobile CPUs were ARM7s and ARM9s, which became the dominant choice of processor, with their 32-bit RISC architecture and small caches. These processors provided enough processing power to not only handle the increased needs from the GSM data protocol, but also to handle the introduction of larger displays, multichannel audio, etc. The next big step was the introduction of many CPU/DSP systems with more memory, where each processor handled a predefined set of tasks and applications. These systems have further evolved into heterogeneous

multicore systems with symmetrical multi processing (SMP) cores, multiple DSPs, GPUs and multilevel heterogeneous memory system (caches and dedicated memory) where the entire systems is connected through a high bandwidth interconnect networkon-chip (NoC). Adding to this SoC system complexity and exponential increase in memory bandwidth needs the introduction of technologies, such as wide IO will create challenges in other areas, such as silicon technology maturity, manufacturing, standardization and overall costs.

Multimedia is an ever increasing focus area for all embedded systems on handheld devices. This multimedia centric view will drive development of multitude of applications that will manipulate multiple steams of real-time data, creating high computational demands resulting in increased system ramifications.

When combining the complexity of multimedia applications and resource limitations of embedded systems, the resulting system design provides some very interesting challenges, ranging from hardware and software partitioning to creating new system bottlenecks requiring handling of new trade-offs. Thus in order for achieving an optimal system design, a systematic exploration of the design space is needed.

In this thesis, we address design space exploration and analyze system requirements for handling multimedia applications in handheld embedded systems, such as advance smart-phones or PDAs. The first notion to take into account is "handheld" that basically means battery driven with all the constraints and limitations it poses on the system. The second notion is "embedded system" which means working in a resource limited environment. Sustained high computational performance cannot be achieved due to lower available power and energy budget compared to desktop system.

Audio and video processing are two major functionalities in multimedia applications today. They have many similarities, such as working on data streams with set of consecutive processing steps. Audio and video enhancements are the driving force behind many multimedia applications. Providing optimized system architecture to enable these processing needs will provide a well balanced multimedia embedded system.

Almost all multimedia algorithms work solely on fixed integer point arithmetic. At the same time video and audio differ in terms of computational complexity, in terms of algorithms and amount data being processed. Audio applications have come further in their evolution and maturity compared to video standards, where the algorithms used are often more computationally complex. The newer an application standard is, the less development time has been put in, making it less optimized, thus often requiring heavier computation and putting more demand on the memory architecture. Another aspect one needs to take into account is that applications not only evolve to more complex applications but can also move "back" to less complex, when introducing new features and other enhancements, such as post processing, etc. This increases the demand for the being able to handle and reuse generated data even further. Audio

applications have come further in their evolution, making it possible for having significantly more post processing enhancements compared to the video applications. In the case of video, many of the fundamental issues for handling data has not been fully solved, thus focusing on post processing is not where the main research effort has been up now.

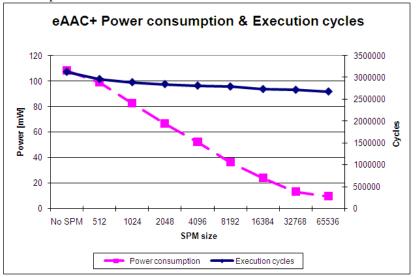

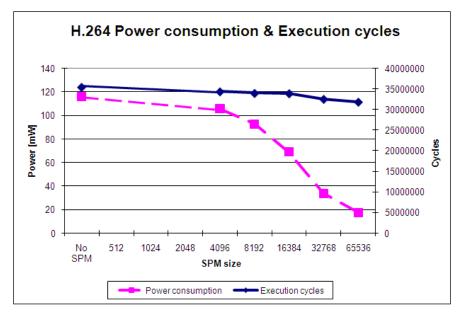

As mentioned previously, in order to handle multimedia, there is a need for system design that is well balanced both in terms of power as well as performance. At the same time it gives the desired flexibility for being able to handle different algorithms and different multimedia applications. The two hardware components which are critical for achieving a well balanced embedded system are processing and memory demands. One needs the computational power to run the algorithms, but at same time the memory design needs to be able to feed the processing elements. The required processing differs significantly between audio and video applications. In some cases this can be a magnitude higher for video compared to audio, for example when comparing eAAC+ audio codec with H.264 video codec. The memory requirements differ both in terms of footprint but also in terms of bandwidth.

The power consumption is also a key factor along with performance for battery operated devices. When it comes to power consumption it is not only processing but also memory that needs to be considered. Often design decisions are made where the focus is on reducing the processing power consumption. This can be a costly approach as this is often paid for in increased memory traffic, potentially resulting in worse overall power consumption. Good designers need to take into account the entire system.

When it comes to processing and the potential speedups there are two approaches for multimedia applications. The first and most used for multimedia is data level parallelism (DLP). The other much less used in multimedia is instruction level parallelism (ILP). The straightforward approach would be to parallelize all potential available parallelism in the application by widening the data paths and increasing the number of processing elements. This however is not the most efficient usage of silicon nor is it power efficient, as not all parallel parts of the application are heavy contributors to the overall computational workload. The power consumption increase comes from over-usage of the memory system, interconnects and external memory accesses. Additionally, the complexity of multimedia algorithms could result in even worst overall performance as it is very easy to get penalized by wrong partitioning due to increased memory accesses.

There are a number of ways to get the DLP in multimedia. Single instruction multiple data (SIMD) is one common approach that can be utilized. This is often designed as instruction set extensions to vector instructions existing processor designs. Another approach is using digital signal processors (DSPs). Yet another approach is to increase the number of processor cores, such as in symmetrical multi-processors (SMPs). Depending on the multimedia application algorithm and data usage one approach maybe more suitable than another.

In the case of ILP, both very long instruction word (VLIW) and superscalar architectures are often used. The concept of superscalar design basically means by increasing the width of the processor and enabling multi instruction dispatch, and execution in every clock cycle thus increasing the overall throughput of the processor. In the case of VLIW architectures, multiple 32bits instructions are combined in to a single VLIW instruction which could be up to 128- or even 256-bits long.

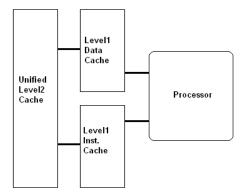

Memory design for multimedia is very much connected to application algorithms and their behavior, as these factors directly control the access patterns and bandwidth requirements. The memory designs range from homogeneous designs with fully dedicated memory, to fully cache based design or heterogeneous memories, utilizing multilevel memory hierarchy. Depending on the chosen architecture, there are different trade-offs to be made, involving memory sizes, types of memories, number of levels in the hierarchy and number of memory ports. When it comes to type of memories there are different caches with different associativity and policies. There are also scratch pad (SPM) or tightly coupled memories (TCM), called in ARM architectures, and content addressable memories (CAM). The SPM is memory design often used in real time and multimedia applications due to its low latency and predictability, as SPM are managed by software. CAMs are on the other hand used when memory speeds are essential, for example in high-speed network switches, as CAMs can search the entire memory in a single operation. The CAMs work in "reverse", basically unlike standard memory, in which the address is given and then the content is returned. In CAMs the data is supplied and the memory returns the address if the data is in the memory.

This thesis answer the following questions: how can we in an optimal way map data and instructions to a particular architecture memory? This is combinatorial problem with discrete set of solutions, where we are looking for the best solution for a specific architecture given a set of memory objects. There are different techniques for solving this, either by using heuristics or complete methods, such as constraint based approaches.

This thesis also addresses another important question, the exploration of the processing and memory design for any given multimedia applications. The important aspect of the multimedia application when looking into system architecture using design space exploration is the abilities of the application itself. Basically evaluate the application in realistic fashion with real world needs so that simulations are as close to reality as it can be. This can be very difficult to achieve, given the real world complexities. So it is very important to use real state-of-the-art world multimedia application for design space exploration.

## **1.2 Motivation**

Multimedia has become one of the most important factors in our day to day lives. It has been one of the main driving forces behind the last century's rapid evolution of human society. What started in the beginning of the last century as rudimentary moving pictures and recorded music has evolved in to today's high definition multimedia content. On top of this evolution there has been as accelerated exponential grows in the last decades that involves the concept of mobility. A notion that enables anyone to use and generate multimedia contents any where at anytime.

The question to ask is what technical advancements have made this possible? What kind of technical trade-offs were made to get to this point? Also what are the hurdles and challenged that lie ahead? An "always connected" society is the major reason for this growing multimedia appetite, major reason being the mobility and flexibility that the devices offered. This led to a consumer appetite for non-stop multimedia content. The device performance, usability and durability were also a huge contributing factor for this growth. This phenomenon involves a wide variety of reasons from cultural to technical reasons, in this thesis we focus on how multimedia content is handled, with emphases on processing and memory for handheld battery powered device. The target is to be efficient in terms of power as well as performance with as flexible architectures as possible. This is a classical computer architecture trade-off problem where the task is to find the right balance when taking in all different factors into consideration.

In the case of processing, as stated earlier, multimedia applications have specific properties that exhibit various parallelisms. These are not only data level parallelism DLP but, depending on the specific algorithms, also instruction level parallelism ILP. In order to get the most out of DLP and ILP there are a number of techniques and architectures that can be utilized, such as SIMD, VLIW, SMP, superscalarity. The architecture we focus on in this work was SIMD together with superscalarity, as this provided both flexible architecture and gave enough performance in the right power envelop for handling multimedia.

As mentioned in the previous section, there are many options for memory architectures for multimedia. They range from straightforward cache based to more complex solutions with different dedicated memory buffers and combinations of the two. Keeping in mind that not only performance but flexibility of being able to execute different kind of applications, both multimedia and others, are intended to use the same memory system, a balanced memory system was necessary. The architecture choices and the complexity of multimedia applications raise the question, what memory architecture suites the multimedia scenario? This can be done with many different approaches and methods. In this thesis we propose a systematic approach to find an optimal mapping of data to heterogeneous memory architecture, consisting of a level1 SPM with multilevel cache hierarchy.

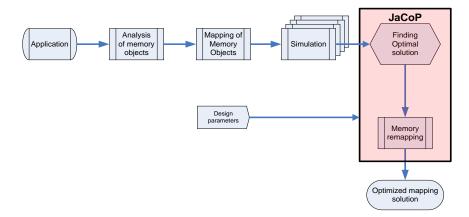

Looking at different approaches for optimization, and specifically optimal mapping of data, one of the best known is integer linear programming, were the problem is modeled using integer valued variables and linear inequalities. Another approach is heuristic based algorithms. The approach chosen in this case is based on constraint programming (CP), where by using constraint specific reasoning methods, a problem is formalized and a model of the problem is created. This is then used as input to a solver

that can find one or many solutions for the specified problem. The constraint solver used in this thesis was JaCoP [1]. The problem we are solving here can be broken down to a combinatorial optimizations knapsack problem. The work in this thesis is one of the first using constraint programming for this kind of problems. The main benefit when using CP compared to other method is that we can state the problem in a flexible way and obtain the optimal data mapping solution for specific memory architecture.

## **1.3** Structure of the thesis

The thesis comprises of two parts. The first part gives an overview of the area, background and motivation behind the work. The second part consists of collection of published papers. Chapter 2 presents the challenges in embedded system with multimedia. Chapter 3 discusses related work and in chapter 4 the published papers are briefly presented. Chapter 5 and 6 gives a list of contribution, conclusions and future trends.

## Chapter 2

# Challenges with Multimedia Applications in Embedded Systems

## 2.1 Embedded Architectures for Video and Audio

There are many challenges that lay ahead when designing today's multimedia embedded systems. These range from designing a system that needs to work in a diverse environment, where frequently many different types of tasks and applications need to be handled, to being at the same time designed with power limitations of battery operation. These challenges are often contradicting with constraints, such as performance and power consumption but also cost and time to market. Breaking down these constraints, certain design areas stand out, such as processing and memory.

The different architectural approaches for handling the processing and memory requirements depend on the selected applications, such as video, graphics and audio. In this thesis, we have focused on video and audio applications, more specifically on block based video codecs, MPEG-4, H.263 and H.264. For audio we have focused on compression codec eAAC+, which is a sub-band codec operating in the frequency domain.

An important factor when doing research on design space exploration in the embedded domain, especially for multimedia applications, is to use realistic applications representing industry state-of-the-art implementations. It cannot be emphasized enough. This is important both in terms of avoiding kernels for system evaluations but also avoiding sub-optimal code, which is often the case in reference applications provided by standards. In most cases design choices made, based on these applications or kernels, are not relevant or even erroneous. Often the focus lays in speeding up parts of applications or kernels, which at first glance seem too computationally intensive.

However in real applications these parts can been solved by more sophisticated algorithms with less computational intensity or even be avoided altogether.

The main architectural solution that has been proposed in embedded domain, targets the inherent parallelism present in multimedia applications. In terms of architectures for processing, these solutions range from using standalone dedicated hardware to using fully software based solutions based on general purpose processors (GPP). The memory solutions used in embedded domain for multimedia applications address mainly throughput issues that are caused by bandwidth limitations. The solutions utilize different on chip memory designs, such as hardware controlled buffers, different type of caches and scratch pad memories (SPM).

In this thesis, the aim has been to address multimedia (video and audio) applications for processing and memory addressing constraints that exist in embedded domain. This has also included a need to propose a method for optimal mapping of memory objects to a specific architecture.

## 2.2 Multimedia Processing

The digital workload for handheld devices, such as Smartphones, including all control, data and signal processing activities, is nearly 100 Giga operations per second (GOPS). This workload increases by an order of magnitude every 5 years [2]. Keeping in mind that all these functions have to run for hours on a single battery charge, and standard Li-ion battery has around 4.5Wh of energy (1200mAh at 3.7V), this is extremely challenging. This basically means we have a tight total power budget, not taking thermal issues into consideration. The cellular transmitter (GSM, UMTS or LTE) takes on average 1-2 W. The rest is what is available for the digital workloads. Comparing the CPU in a Smartphone with a PC, it has to run more than two orders of magnitude more power efficient, 0.2 W vs. 30W [2].

Looking at processing 100GOPS, the thought of using a single processor to handle this is out of a question as it implies running a processor at 100GHz! Looking at the other side of running 1000 cores at 100MHz is also unreasonable with all the overhead traffic and costs. The only way forward is using a heterogeneous architecture based on programmable cores and hardwired functional accelerators.

Multimedia applications are major contributor to the 100GOPS workload. These applications put huge demands in terms of processing on any system, especially on resource constrained embedded systems. Regardless whether these systems are hardwired or fully flexible, the entire system (computation units, buses, memories) is often pushed to peak performance edges. What kind of processing solution is chosen is often a trade-off between required performance, flexibility, available power budget and available technology.

All processing solutions address parallelism present in multimedia applications. This can be achieved through different approaches, such as dedicated hardware solutions, or

programmable solutions, where they can either be homogeneous architectures, such as multicore architectures, or heterogeneous systems, where programmable cores are combined with hardwired solutions. Further a heterogeneous system where dedicated hardwired solutions are present can either be loosely or tightly coupled. What is meant by loosely coupled is where, for example, a system is designed around a general purpose processor (GPP) with dedicated hardwired blocks for specific accelerations. A tightly couple system is a GPP enhanced with instruction set architecture (ISA) extensions, such as SIMD style extensions.

Dedicated hardware solutions for multimedia are often designed to perform single or very few specific tasks. They can range from performing parts of computationally heavy algorithms, to executing entire applications, such as encoding a specific H.264 bit stream. The key here lay in performing a predefined task with high performance but at expense of flexibility.

Using either general purpose processors (GPP) or digital signal processors (DSP) is a common approach for achieving flexibility with limited performance requirements. GPPs are designed traditionally to enable efficient execution flow and DSPs are designed to perform well for constant-rate data flow applications. Together, GPPs and DSPs can also be combined to processing engines for a wide variety of multimedia applications and products. These processor based solutions can be used for wide variety of applications, but their flexibility comes at a cost of being limited in terms of performance. For example, in the video encoding and decoding, when the resolution is above a certain level, such as high definition (HD), the performance is not enough.

An approach which can provide better performance compared to above solution is when GPPs are combined with dedicated hardware in a loosely coupled heterogeneous architecture. Here specific computationally heavy blocks are connected together with GPPs via buses or interconnects. This is a very simple and straightforward hardware approach but has limitations in terms of flexibility. This hardware simplicity comes at expense of software complexity, making programmability of these systems difficult and many times inefficient due to potential hardware software overhead costs and traffic.

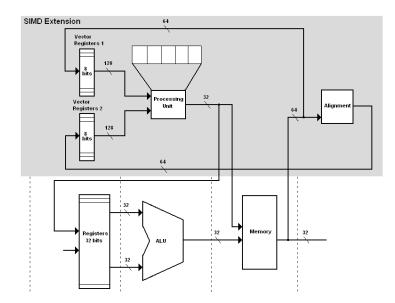

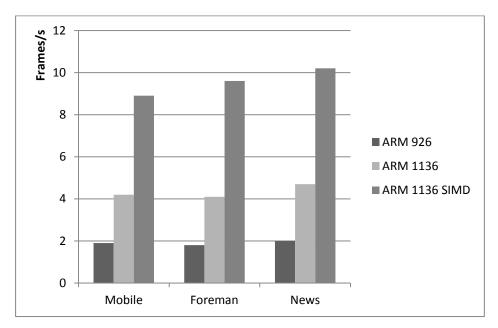

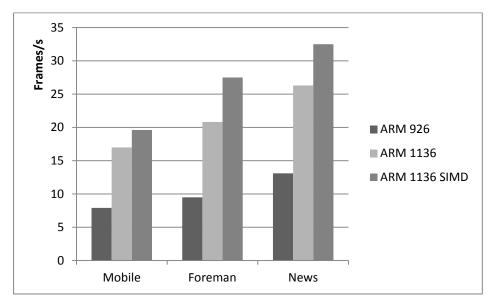

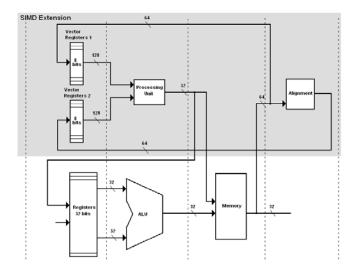

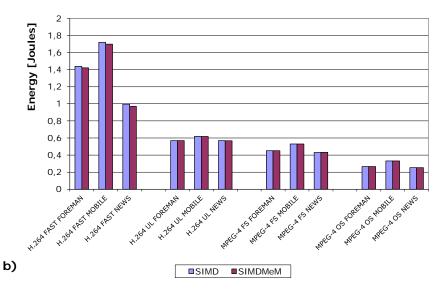

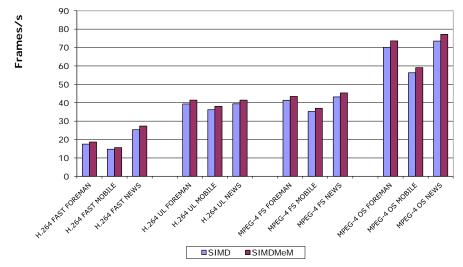

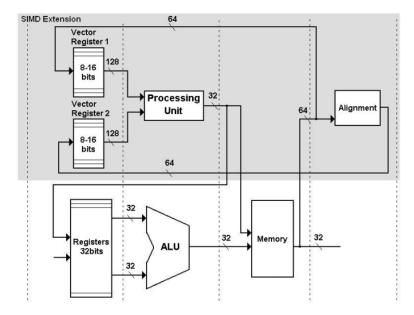

In order to keep high flexibility but provide multimedia capability, microprocessor manufacturers have introduced tightly coupled heterogeneous extensions to their instruction set architectures (ISA) that enhance the performance of multimedia applications. These ISA extensions operate in a SIMD fashion to exploit data level parallelism (DLP) in multimedia applications. SIMD enabled microprocessors increase the processing capability while offering the low power consumption required by handheld, battery powered devices.

Multimedia applications typically operate on narrow words (primarily 8- and 16-bits) and spend a significant portion of execution time in loops that have a high degree of processing regularity. Packing several small data elements into a wider data-path

enables simultaneous processing of separate data elements. Such SIMD instructions are available for several arithmetic and logic operations in addition to special media operations, such as sum-of-absolute differences (SAD). SIMD capabilities enable more efficient software implementation of high-performance media applications such as audio and video codecs. Processors, such as ARM NEON, MIPS MDMX and Intel Architecture MMX and SSE, provide SIMD style instructions.

For example, ARM as one of the major embedded processor providers, introduced NEON [3], a combined 64- and 128-bits wide general purpose SIMD extension to the ARM instruction set architecture to accelerate multimedia applications, such as video and audio encoding/decoding. NEON is tightly coupled with the ARM core providing single instruction stream with unified view of memory. NEON supports 8-, 16-, 32- and 64-bit integer and single-precision (32-bit) floating-point data and operates with up to 16 operations at the same time. NEON is capable of delivering between 60-150% performance improvements for specific multimedia codecs [3].

Another closely related aspect to take into account regarding multimedia processing is that most research has been focusing on the data centric parts of the applications. This has resulted in neglecting of the potential parallelism available in the control parts. The importance of these parts is becoming even more critical as multimedia applications are evolving towards more advance control dominated applications [4]. This trend can, for example, be seen in the evolution of video codecs, MPEG2, MPEG4 and H.264. This potential parallelism can be exploited by instruction level parallelism (ILP) through the usage of different architectures, such as very long instruction word (VILW) and superscalarity.

As mentioned in the previous section a specific solution depends very much on the selected applications. More specifically the processing of video and audio has similarities but also many differences. Audio is a data dominated application making it easily parallelized, which is often performance enhanced by parallel architectures, such as DSPs, SIMD and parallel dedicated hardware. Video on the other hand is not as strait forward as audio in mapping. It has parts that are data dominated and have significant parallelism, such as block filtering and motion estimation. But when it comes to compression and decompression this is control dominated [5]. It is essential to understand which type, data or control dominated an application is.

Processing needs differ therefore significantly between audio and video. Audio applications have significant lower processing, almost a magnitude lower, less than 100 Mega cycles, compared to video processing. There are two main reasons for this, first the amount of data being processed is significantly lower for audio applications. Second audio applications work on one dimensional data arrays making audio applications much easier to process and predict. Video applications can be seen as two dimensional arrays.

In the subsequent sections we will discuss, in more details, video and audio processing.

### 2.2.1 Video processing

The main multimedia video trend in handheld, battery operated devices is an increased complexity of the video codecs, an increased number of supported video codecs and an increased resolution for both cameras as well as displays. This has led to a significant increase in processing demands.

Processing requirements for video applications are significantly higher than audio applications as the amount of data needed to be processed is higher. In addition, the compression efficiency of newer codecs, such as H.264/AVC, has significantly improved. This has come at a cost of computational complexity and memory access bandwidth. For example, for HD720p video (1280x720@30fps, ±128-pel search range, 2 ref frames) encoding the required off-chip memory bandwidth with level C scheme is 1071MByte/s [6]. Comparing the number of pixels for a standard definition (SD480p) to a full high definition (HD1080p) this about 6 times more pixels per frame for the HD (350000 vs. 20000000 pixels/frame). This equals to a processing need of over 3200 Mega-cycles/s for HD1080p and 550 Mega-cycles for SD480p for a H.264 video stream.

To understand better video codecs functionality and their processing requirements we will discuss H.264 codec in more details. The main blocks in H.264 encoder and decoder are illustrated in figure 1. As seen in figure 1 the entire H.264 decoder is a subset of the H.264 encoder. The major processing demanding blocks are motion compensation and motion estimation. Other parts in H.264 encoder include the selection between intra- and inter-coding for block-shaped regions of each picture. Intra-coding uses various spatial prediction modes to reduce spatial redundancy in the source signal for a single picture. Inter-coding (predictive or bi-predictive) uses motion vectors for block-based inter-prediction to reduce temporal redundancy among different pictures. Motion vectors and intra-prediction modes may be specified for a variety of block sizes in the picture. Finally, the motion vectors or intra-prediction modes are combined with the quantized transform coefficient information and encoded using entropy code such as context-adaptive variable length codes (CAVLC) or context adaptive binary arithmetic coding (CABAC).

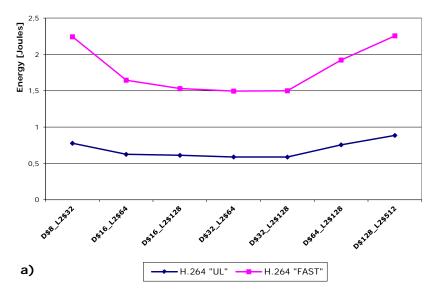

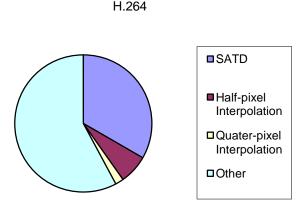

Consider for example, parallel arithmetic instructions, such as sum of absolute difference (SAD), a multi-cycle operation that is often pipelined for accelerating motion estimation in video compression codecs. These instructions are used to perform parallel half-word or byte wise arithmetic operations. This is used in motion estimation, which is one of the most critical components in a video coding system, and it also dominates the major part of the computation complexity and memory bandwidth. Depending on implementation, in straightforward dedicated hardware implementation, motion estimation is an I/O bound problem rather than a computation bound one [7]. Looking at motion compensation the most computationally demanding parts are half-pixel interpolation, which is done by using a 6-tap FIR filter, and quarter-pixel interpolation is done by averaging two half-pixel values. These three operations, SAD,

half- and quarter-pixel interpolation can easily stand for up to 40% of the overall H.264 encoding time [8].

Figure 1. Block diagram of H.264 algorithm encoder and decoder.

When looking at video codecs, the encoders have more flexibility to do trade-offs with performance. The SADs for a motion estimation search in the encoder, can assign the motion search within each of a range of reference frame to a unique thread, thus increasing the possibility of parallel execution. Looking at video data, it is represented in most applications as 8 bit resolution. The size of parameters and coefficients are

coded in 16 or fewer bits. The filters coefficients and algorithms of H.264 and many other popular video codecs are chosen to ensure that even intermediate values of calculations will not overflow 16-bit arithmetic's operations within processors [7,9]. The adders, shifters, ALUs, multipliers and other data processing elements within programmable video processors are typically 16-bits wide, which will directly impact the system architectures.

Other important aspect of video processor is the pixel rate requirements of the application that must be met as it is directly connected to amount of data needed to be processed. The pixel rate is the product of height, width and rate at which full frames are displayed. For many video coding standards the worst case time difference is at least a magnitude greater than the typical sequences.

Another factor to bear in mind is the explosion in supporting higher and higher screen resolutions which has come at same time as an increase in codec complexity when comparing H.263 with H.264. An increase from H.263 at QCIF to H.264 at SD has a computational complexity increase of about 65 times [4]. This has resulted in huge changes in video system architecture. In the mobile domain, there is also an increased number of video codecs that need to be supported. Here is a short list of codecs that are mandatory, MPEG2, MPEG4, H.263, H.264, VC-1, RV, DivX, VP6/7, Sorenson Spark and AVS 1.0. With this increased number of codecs has come increased computational complexity as well, for example, comparing H.263 with H.264 on the same resolution and frame-rate H.264 is 2.5x more complex [4]. At the same time, the fast pace of mobile handheld device development has meant that there has always been a request for supporting multimedia codecs that were not available when the chips were designed. All these requirements lead to a need for a flexible video processing architecture with high performance.

The biggest trade-off in video hardware systems is flexibility/programmability versus dedicated hardware. This flexibility allows late adaptations and development of new multimedia applications, but it also gives the opportunity for increased differentiation by enabling new unique features and improvements to be added later. This increased flexibility comes often at price of increased power and area and in some cases of decreased performance. As mentioned in the previous section, the common denominator for all video processing solutions is exploiting the inherent parallelism that exists in multimedia applications and especially video applications. The main architectures range from fully dedicated hardware solutions, to the full programmable general purpose multicores. In between one can find more or less programmable solutions with specific hardwired architectures. These categories of architectures include heterogeneous uniprocessor solution with SIMD extensions, which we have focused on in the work presented in this thesis.

Fully dedicated hardware is designed to perform a predefined function, resulting in inflexibility for handling new video codecs with updated requirements. Programmable processors on the other hand provide flexibility but at increased power and lower

performance. The implications of this provided flexibility, is the possibility of performing complex functions by combining various simple functions in the order specified by a software program. This leads to many more reads and writes that are performed in a programmable processor, than in a dedicated hardware. Each read and write takes time, reduces overall throughput, and consumes power, wastes energy and generates excess heat. For motion estimation algorithm dedicated hardware solutions often adopt full search block matching algorithm (FSBMA) [10] because of predictability and regularity of the computations. This however requires maximum computation load and memory bandwidth. The reason for the large computational load is due to a need for working with a large set of candidate blocks that needs to be matched. Also the huge memory bandwidth results from loading the reference pixels for candidate blocks. Dedicated hardware logic yields best performance per cost, but keeping in mind the need for supporting multiple coding standards, handling new proprietary functions, and future changes to application requirements a programmable processor is preferred solution.

Programmable processors are preferred for applications that support many standards and in areas where new standards evolve in a fast pace, such as in video. A closely related factor that needs to be taken into account is porting an existing solution into new release of operating system. This is significantly easier for more flexible solutions.

Another aspect regarding fully programmable processor solutions is the requirement of having sufficient internal storage to efficiently perform its most demanding video processing functions. This consumes large silicon area, resulting in greater manufacturing costs.

A heterogeneous architecture (mix of hardwired and programmable core) achieves best balanced solution and is probably the most dominating solution for video processing. For achieving a robust and balanced architecture a carefully made partitioning between the hardwired and programmable cores needs to be made [4], as this is to reduce the hardware software interactions to minimum to achieve a good level of efficiency. Basically, the hardwired accelerators should be used for processing large chunks of data. This also relives the memory system as memory burst are optimal for external memory bandwidth. This results in architecture, where the only tasks left for the programmable part is control code. Looking at different design options for the programmable part, a general purpose CPU is much better choice compared to a DSP or a VLIW, as neither is optimal for handling control code [4]. Many newer video codecs, such as H.264, have different control flow in the algorithms, depending on if some of codec features, for example flexible macroblock ordering (FMO) etc. is used or not. Also post processing is another area which is very difficult to implement in hardwire, as algorithms for these tasks are very application specific and could often have complex control code thus requiring significant programmability.

Programmable video processor architectures achieve best performance through the use of parallelism at the data-, instruction-, and task-level. This is usually implemented

using SIMD, VLIW and multicore. On top of these an optimally sized ALU, multiplier, and load/store data paths is essential. In programmable video processors, video processing functions that are commonly accelerated with specialized hardwired logic include, multi-pixel sum of absolute differences (SAD) for motion estimation and filtering such as for inter-pixel interpolation (FIR) and deblocking filters. Where the video processing algorithm has data parallelism the performance of a processor is greater if the processor has single instruction multiple data (SIMD) instruction that, with the execution of a single instruction, operate on adjacent data elements in parallel. SIMD extensions have been added to almost all commercial general purpose processors table1.

| Architecture | Extension | SIMD Width<br>(Bits) |

|--------------|-----------|----------------------|

| ARM          | NEON      | 64-128               |

| MIPS         | MDMX      | 64                   |

| Scorpion     | VeNum     | 128                  |

| Intel        | SSE       | 128-256              |

| AMD          | 3DNow!    | 128-256              |

| PowerPC      | AltiVec   | 128                  |

**Table 1**. List of SIMD extensions on different general purpose processors.

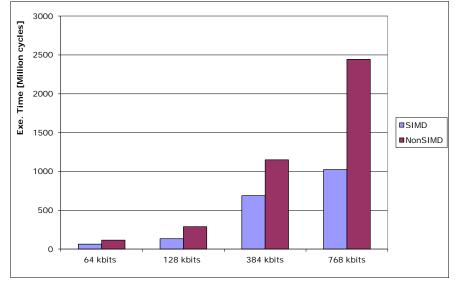

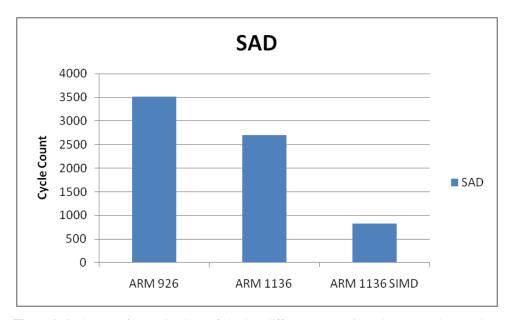

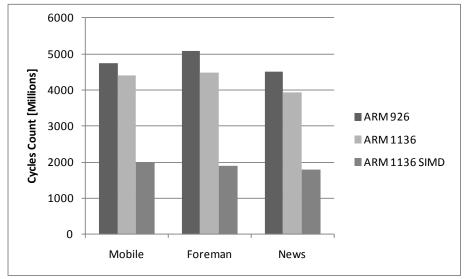

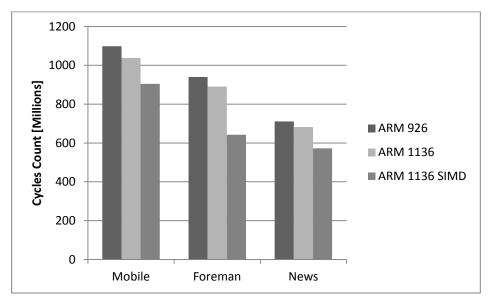

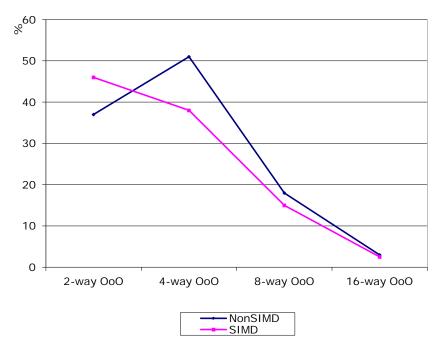

SIMD extensions accelerate multimedia applications by exploiting data level parallelism (DLP). An important aspect with SIMD is that performance does not scale with increased media execution resources, as there are several bottlenecks in SIMD style media processing and that it is not possible to achieve significant additional performance improvement by making the processor wider to extract more parallelism. This is mainly due to overhead of supporting instructions that need to be significantly increased to scale with the increased SIMD width to keep the efficiency high.

For example, looking at table 1 a SIMD processor performing 16-bit operations on eight ways SIMD data will yield the best performance with 128 bits wide registers. At same time a processor designed for a coding standard that operates on 8x8 blocks with 8x8 transform matrices yield better performance with eight ways SIMD parallelism and 128 bits registers. This due to, eight ways SIMD parallelisms make full use of datapaths without cycles of unused datapath bandwidth. Also the registers within the processor must be large enough to hold a range of SIMD data values. An important issue to keep in mind is greater SIMD parallelism improves the average case but yields little performance improvements when processing a worst case stream. This depends on whether the applications used, for example if codec is based on 4x4 blocks then best performance is based on 64-bit registers. But in case of 8x8 blocks then 128-bit registers yield best performance. The ideal design keeps the processing elements fed

with data to avoid stalls, but if the design is wider than necessary this has no performance benefits. In the case of VLIW and SIMD both are high-performance and power-efficient designs but are usually well suited for only very specific types of application codes with large numbers of independent operations that can found by compilers or the programmer.

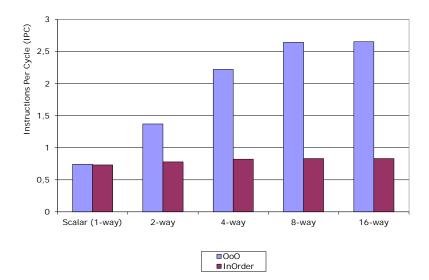

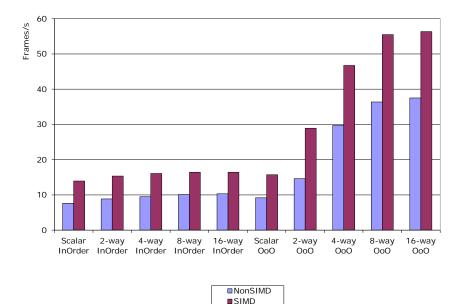

Another approach for getting better overall performance is through exploiting the instruction level parallelism (ILP) that exists in multimedia applications. There are many approaches, such as superscalarity or VLIW. Superscalarity means simultaneous execution of instructions on multiple parallel pipes in the processor. The main difference with other approaches, such as VILW, is allocating instructions to execution unit at run time. The added cost of superscalarity comes through utilization of hardware for achieving better parallel execution. There are two design approaches either an inorder or an out-of-order execution. The later is performance wise much better but is also more hardware complex. The out-of-order execution is crucial in getting the performance benefits of superscalar design as it makes runtime execution dependencies irrelevant, which was shown in paper IV [8]. An in-order superscalar processor on the other hand doesn't fully utilize the added hardware but still require more hardware complexity for a smaller performance benefits than is achieved by instruction level parallelism of a VLIW, which relies on the allocation of instructions to execution units at compile time. Superscalar out-of-order is also a direction which ARM processors have taken and in their Cortex-A9 architecture embraced this [11].

ILP can also be achieved, as stated above, through the use of VLIW. The mayor difference between the two designs is the hardware software trade-off. VLIW relies heavily on the compiler to effectively utilize the parallelism. This could be acceptable but it depends on the runtime execution predictability of the application. Multimedia applications and especially video codec's are highly runtime dependent making it difficult at compile time schedule optimal instruction execution order.

A direction that many chip vendors have taken in recent years is to offer parallel machines, or single chip multicore microprocessors. There are many reasons for this but one major reason being that in order for sustaining and keeping up with Moore's law scaling. There is up to certain level you can push a single core until the power consumption and core complexity gets too high. As the single core is pushed higher and higher in clock frequency the power required to do this grows in faster rate, leading to design that are very complex and power hungry. There are a number of different ways to define multicore and multi-processors. One definition is looking at the processing cores. The multicore system can be homogeneous multiprocessing as in symmetrical multiprocessors (SMP), where there are a number of identical cores tightly connected together. They can also be heterogeneous multiprocessors like in asymmetrical multiprocessor (AMP), where there are different type of cores connected via interconnect on the same die.

The main advantage of using multicore is that the required performance can come from increased number of cores compared to increase in frequency. However there are many challenges that need to be handled in order to get the promised performance. They range from designing multicore system, to efficiently writing parallel applications that utilize the system capabilities. Programming multicore system remains very challenging. The problem of how to take a piece of sequential code and optimally partition it across multiple cores remains unsolved [12]. A key factor is how well all the existing serial algorithms can be redesigned to take advantage of multicore systems. Algorithm designers need to understand the characteristics, including both advantages and limitations, of multicore to create algorithms that best match the platform.

Looking at video processing, an efficiently way for utilizing multicores is by using a single frame slicing that, for example, exists in H.264. By mapping the slices to a specific core a good distribution is achieved. If one on the other hand maps frames to different cores the communication and data synchronization overheads could lead to worst overall performance.

## 2.2.2 Audio processing

The other key applications in the multimedia domain are audio codecs and audio applications. Audio processing mostly focuses on different filter algorithms, such as Fast Fourier Transform (FFT), Discrete Cosine Transform (DCT), Finite Impulse Response (FIR) and other digital signal processing filters. In the case of audio content, the MPEG-4 High-Efficiency Advanced Audio Coding v2 profile (HE-AAC v2) has proven to be one of the most efficient audio compression schemes [13]. This is one of the main codecs chosen for mobile handsets in 3GPP [14] and used in our research paper V [15]. The MPEG Advance Audio Codec (AAC) was designed to be the successor of the MP3 format. AAC generally achieves better sound quality than MP3 at similar bit rates. It is widely used and supported by almost all handheld devices.

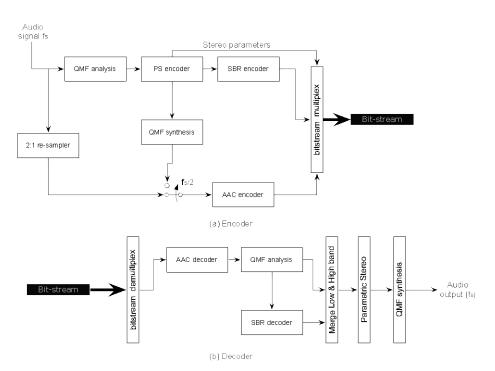

How a decoder is designed and implemented is of significant importance especially in handheld devices. The computational complexity and memory requirements of the decoder are major factors in choosing the codecs in real-world applications. As these are directly related to power consumption and implementation cost. HE-AAC version 2 is a lossy data compression scheme for digital audio, consisting of three technologies. It is an extension of Low Complexity AAC (AAC LC) optimized for low-bitrate applications such as streaming audio. This is coupled with Spectral Band Replication (SBR), to enhance the compression efficiency in the frequency domain, and Parametric Stereo (PS) to enhance the compression efficiency of stereo signals as illustrated in figure 2.

Figure 2. Block diagram of HE-AAC v2 encoder and decoder.

The main challenge in audio processing lies in finding the right balance between compression efficiency, audio quality and codec's computational complexity. By introducing SBR and PS the compression efficiency is significantly improved but this comes at expense of increased computational complexity for the HE-AAC decoder.

In most cases running audio applications could be performed in software on a general purpose processor, as even the most demanding audio applications with added post processing require less than 100 mega processor cycles per audio channel. Most often the addition of a VLIW or SIMD unit to the processor core provides even better computation power ratio, since audio applications have high degree of data parallelism. By increasing the number of audio channels the amount of processing workload increases quite linearly. For example, a true stereo audio has two times the workload of a single audio channel. This means audio workload can easily start adding up when the number of channels goes to 6 or even 8 surround. Another important difference between audio and video codecs, is that audio applications and codecs work in one dimension, making them easier to handle these applications in terms of processing and predictability.

## 2.2.3 **Power constraints for processing**

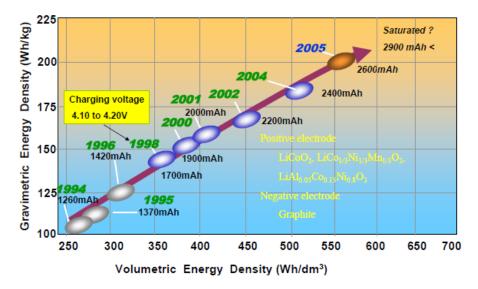

One of the technically fundamental constraints in embedded handheld systems is power or energy, since many of these systems are often battery powered [16]. This is closely related to the other constraint in embedded systems, performance. These two constrains, power and performance, often follow each other as in many cases they are closely correlated. They set the bases for design choices and trade-offs both in hardware and software. These design trade-offs range from choosing the silicon process, low power (LP) or high performance (G), to choosing different design libraries and hardware design tool settings. The design constraints bottom line is energy, how long operating time is directly connected to how much capacity there is in the batteries and how much power the system consumes for different use cases, which at the end determine end user experiences. The limitation in overall performance on the other hand is mainly due to silicon technology, die area and design choices (interconnect width, number of memory interfaces, etc.). On the power supply side, the slow increase in battery capacity in handheld portable devices has tightly constraint power consumption as shown in figure 3.

### High-energy densities more than 550 Wh/dm<sup>3</sup> or 200 Wh/kg

Figure 3. Energy density curve of lithium Ion battery development [17].

Looking at typical embedded handheld devices, such as Smartphones the typical operating voltage is around 3,7V. For different use cases the overall current consumptions vary significantly. For example, video playback uses 200-300mA, while

a voice call consumes 350mA. On top of this there are major power consuming peripherals, such as displays, cameras and different set of sensors. For example, a typical current consumption for a display is above 120 mA. Thus there is clear reason to distinguish between active power consumption (when the device is actively being used by an end user) and standby power consumption (when the device is in operational mode but the end user not actively working with the device). The standby typically have background activities running, such as keeping the cellular communication alive (~4mA), monitoring the subscription services, Facebook, email etc. (20-30mA) that the end user uses.

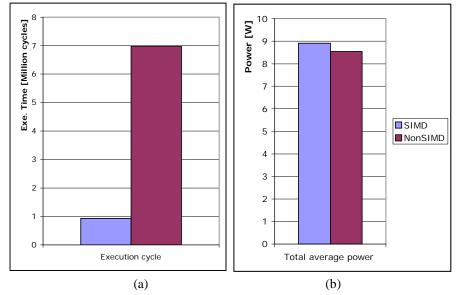

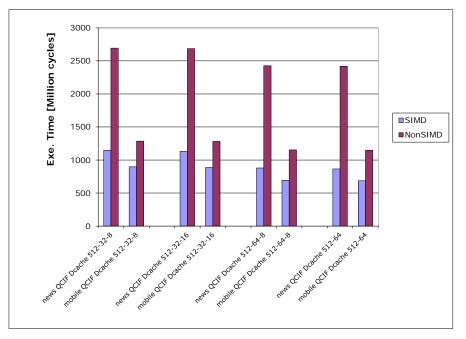

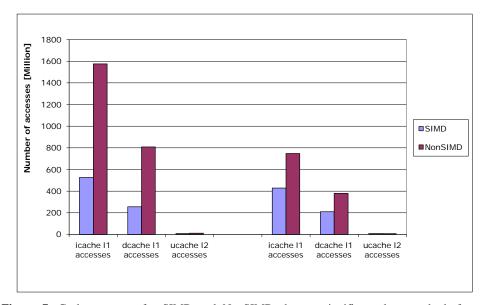

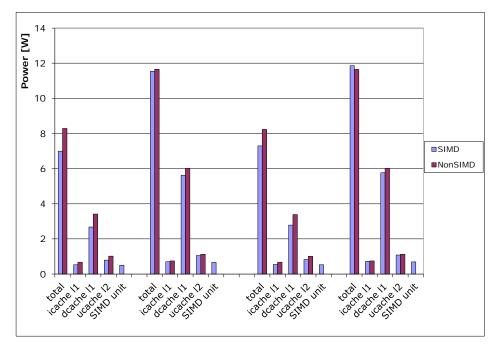

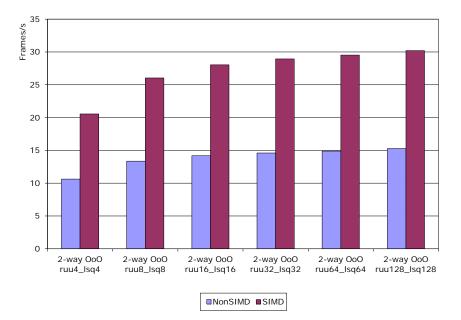

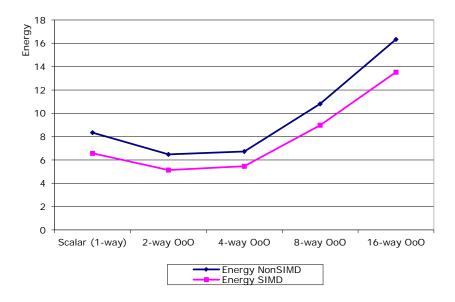

These parameters are essential in achieving the battery capacity constraints for handheld portable devices. Also, as the silicon have shrunk passed 65nm technology node, the overall leakage is quite significant. These lead to having a need to control and manage both dynamical as well as static power consumption. These include dividing the design in 10-20 different power domains in a hierarchical fashion, using clock and power gating, forward and reveres body biasing, and above all using dynamic voltage and frequency scaling. In this work, the main focus has been on dynamic power consumption for processing multimedia applications. Comparing the power benefits of SIMD enabled processors with non-SIMD processors [18], the main conclusion was that with added hardware for SIMD unit the power benefits through faster and more efficient execution, outweigh the added cost of the SIMD unit. This was true in terms of power consumption, hardware complexity and silicon area. Another major contributing factor for overall power consumptions is memory and external off-ship accesses which will be discussed in the next section.

Overall, looking at processing efficiency in terms of energy, depends thus on many factors, such as the chosen architecture and silicon technology, use cases the embedded device need to operate and how sophisticated power management is implemented in the system. For example, in many cases the peak power (up to 700-800 mW) is not the issue but rather for how long the sustained power consumption is the critical issue. This could be a major issue not only in terms of energy consumption for a battery operated device but also thermal limitations can become a limiting factor.

## 2.3 Multimedia Memory

One of the key factors that drives the cost and power dissipation of an embedded system on-chip is the memory architecture. The memory subsystem is a major contributor to the performance, power and area of a complex embedded system [19]. The memory subsystem can constitute a large part, up to 70% of the silicon area. This figure is expected to grow even further to over 90% by 2014 [20]. The main reason for this is the relative small design cost per area unit in terms of both manpower and time to market. Another reason is related to power consumption, since the heat dissipation per area unit is lower for memories than for logic. Thus, on-chip memory can be used to add functionality with smaller impact on system heat dissipation [21]. The key

challenge is to define a memory system that combines and satisfies the processor data requirements for executing efficiently, whilst minimizing cost and power consumption. In many multimedia intensive embedded systems, the overall area and power consumed by the memory subsystem (on-chip as well as off-chip) is up to 10 times greater than of processing, making memory a critical component of the design [22]. Thus, data placement and memory mapping is crucial for achieving good performance and optimal memory utilization. This can be achieved by optimally utilizing the on-chip memory, which can be SRAM, ROM and/or embedded DRAM/SRAM that is similar to off-chip DRAM.

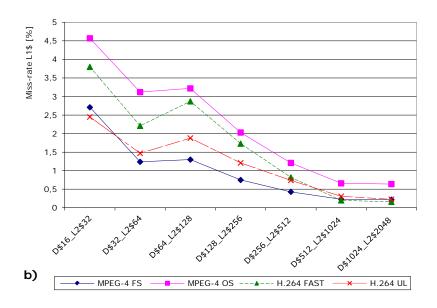

In the field of memory architecture and memory management, there are two main approaches when dealing with multimedia applications. The first one uses dedicated zero wait state memories, often referred to as scratch pad memories (SPM). This approach requires often rewriting the applications to best fit these memory architectures. The second approach uses multilevel caches and this approach does not require rewriting the code but through careful optimizations based on a standard memory hierarchy, it is possible to get additional improvements.

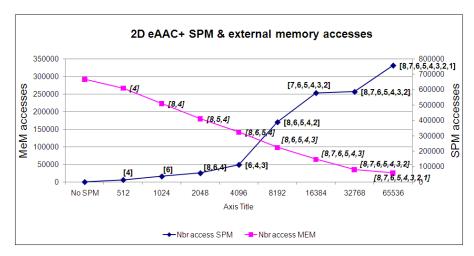

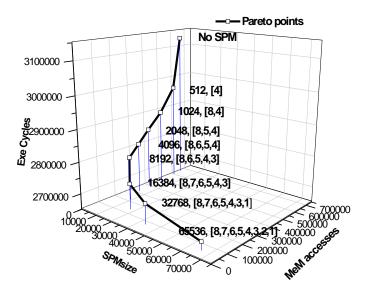

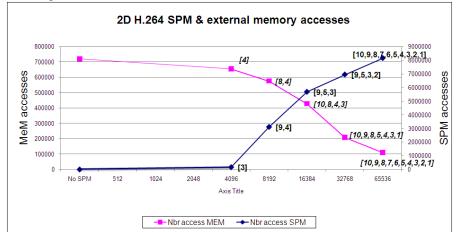

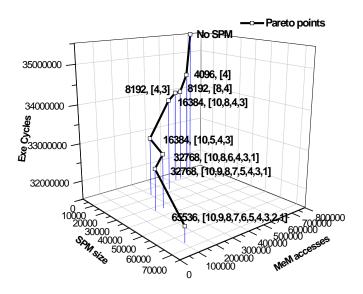

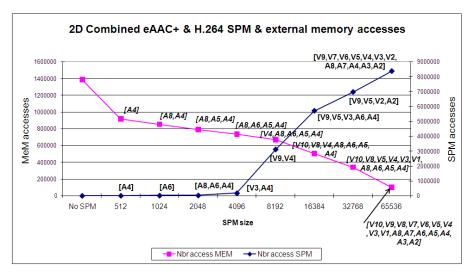

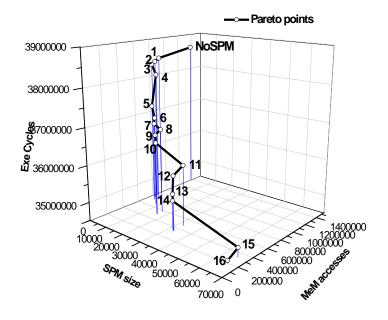

The question that arises is how does the combination of the two memories, SPM and cache, behave and how should we best optimize and utilize the system, software and hardware. This is a typical trade-off, where we have a multidimensional optimization problem. In our work, presented in paper V [15], we introduce a methodology for mapping data and instructions to heterogeneous memory architectures consisting of SPM and multilevel caches. In that method, we define the problem as knapsack problem [23]. We show significant gains in lowering off-chip memory access by selectively mapping data and instruction to SPM, which provide an optimal solution for a given architecture. Our solution could either, minimize external memory accesses, minimize execution cycles or maximize SPM accesses.

Common for audio and video applications memory requirements are that they often work on streams of data. In the audio case the memory accesses are very regular, meaning one can predict the next data read quite accurately. In the video case this much more difficult, as the runtime dependency makes the data accesses much more irregular. Also, the amount of data being processed in video applications is at least an order of magnitudes larger compared to audio applications. A straightforward approach cannot be taken with video applications, as can be done with audio, especially due to memory bandwidth limitations in embedded systems. On top of this, in the video case, the encoding is execution dependent, meaning that selection of data for processing cannot be done at compile time. Instead the focus can be shifted to instructions of the algorithm and deciding what instruction sequences should be mapped to specific memory, such as SPM at compile time.

The SPM is organized into multiple memory banks, preferably in smaller memory banks, as these consume lesser power per access than larger memories. This presents an opportunity to place most frequently accessed data in smaller bank sizes. To obtain good performance and few memory stalls, the data buffers of the application need to be placed carefully in different types of memory. This is typically done manually and hence takes a significant amount of time, up to several man months.

Memory management for multimedia applications especially video applications is thus an important area to focus on as huge amount of data is being processed. The result is heavy congestion of the memory subsystem, with the potential of breaking the system. Thus, there is a need to focus on algorithms for reducing amount of processed data as much possible, especially for encoding and decoding multimedia streams. This results in the situation where not all data is relevant for processing. Instead only a small portion of data is useful for processing and the rest can be disregarded. For example, the motion estimation algorithm is very selective in choosing the right data for processing, which leads to reduction in applications bandwidth needs.

Another key area when dealing with memory and multimedia applications is the applications themselves. Researchers have too often used non optimized reference code, where the overall behavior of the application is not the same as for the optimized code. For example, if a critical part of an application, which was computationally complex with high memory utilization and took up to 50% of the overall execution time, in the non optimized reference code, in an optimized real application, this part has been reduced to less than 15%. We showed this in paper III [18], where we compare real life code with standard codecs often used in research papers proposing solutions to speed up these applications.

#### 2.3.1 Memory bandwidth requirements

As semiconductor process technology shrinks, it is feasible to design chips with greater data processing capability. The data rates and bandwidths for transferring data between chips do not increase at the same rate as data processing requirements. This result in performance of processors on video applications is constrained by memory bandwidth to off-chip DRAM memory devices in ever more applications. Bandwidth requirements for video applications are typically high and will further increase as resolutions, bit depths, and frame rates increase. For example, a SD video stream of 25fps consumes 15.6MB/s and for HD RGB12bit stream at frame rate of 120Hz consumes 1120 MB/s.

There are three different accesses types to off-chip memory: Bit stream (encoder writes, decoder reads), uncompressed frames (encoder reads, decoder writes), and reads of stored frame buffer(s) data for motion estimation or compensation. Because the bit stream is compressed, it consumes a negligible amount of bandwidth in most video applications. Reading and writing the uncompressed frame has significant impact on the memory bandwidth, resulting in a need for lowering it. This is one of the main reasons why the reads required for motion compensation or good motion quality motion estimation is essential as they account for most of the bandwidth consumed in typical video processor. As mentioned previously most dedicated hardware solutions

for video processing use full search block matching algorithm (FSBMA) leading to high memory bandwidth utilization.

The storage requirements and data access patterns of video functions have huge impact on system design and architecture. For example, most video codecs employ temporal algorithms, which require access to previous frames when processing a frame. This is important as it directly affects the memory storage needs. Required frame memory for HD H.264 decoding is around 15MB (YUV4:2:0, 8bit) which is not cost effective to have as on-chip memory of around  $7mm^2$  per MB in 65nm technology. This gives a total area of  $105mm^2$  for 15MB. Embedded DRAM would be alternative as it has higher density than SRAM but requires additional mask layers for manufacturing which adds to cost.

The bit stream accesses are both regular and irregular, depending what functional part of the codec is in use. For example, scaling and rotation have regular access patterns. Whereas other parts, such as decoding, encoding and interlacing use motion compensation, which is technique used for block prediction, has very irregular access pattern. This result in caches cannot alone reduce memory bandwidth to off-chip memory. For example, the motion compensation traffic in H.264 decoding is typically 100-200MB/s for SD resolution and 500-900MB/s for HD resolution content. For SoCs handling video content the typical accumulated memory bandwidth requirements is around 1-6GB/s. The processors are typically latency sensitive but by using a side buffer, such as SPM etc. can alleviate this latency sensitivity.

The importance of external memory bandwidth reduction cannot be over emphasized. For example, in video compression algorithms there are there type of frames intra coded frames (I), predicted frames (P) and bi-directional frames (B). For video encoders that perform motion estimation search for P and B frames, it greatly reduces off-chip memory bandwidth if an on-chip level-2 cache is implemented to store not only the current SAD block but also surrounding data. Motion search algorithms tend to have a large amount of overlap between successive or parallel SAD operations. So by having the adjacent data to SAD block it will often eliminate the need to access off-chip data for the next SAD. Coding video with I frames instead of P and B frames requires less compression processing and fewer off-chip memory accesses both of which save energy, but leads to significantly larger size bit streams.

Taking into consideration both memory constraints and media constraints, a need for a systematic methodology for memory management is required. In this thesis, a method for mapping of a heterogeneous, SPM and multilevel cache is proposed in paper V [15]. The applications used are both a video (H.264) and an audio (eAAC+) application.

## **Chapter 3**

# **Related work**

#### 3.1 Processing

In the broad area of multimedia processing there has been made huge contributions. It has meant taking on the problem of processing from many different angles, from direct approaches, such as focusing on processing elements, to different hardware parallelizations. Other indirect approaches for enhancing multimedia processing work on limiting bandwidth requirements, optimizing memory architecture and interconnect/bus design, software enhancements, algorithmic improvements, compiler enhancements and overall system improvements.

Now focusing on work done on the processing unit for multimedia, these can range from fully programmable, to configurable and to hardwire solutions. In this work, we focus mainly on programmable cores but will give some remarks on other architectures as well. The programmable core can either be a general purpose CPU [24,25,26,27,28] or a digital signal processor DSP or very long instruction word VLIW, such as in [4,29,30,31,32,33,34,35,36,37,38] or a GPGPU general purpose graphical processing unit [39,40,41,42,43,44,45,46].

In many of studies using CPUs, these are combined with SIMD unit either as extensions to the main processor through ISA enhancements, much like NEON, MMX, Altivec [24,26,27], or use coprocessors [25,29]. The main difference is that in the later case the SIMD unit is not as tightly coupled with CPU as it is the case with ISA extensions. This is also an architecture often used when the focus is not on processing unit, but rather something else, such as special memory architectures [7] or software and complier enhancements [47]. In [26], the authors evaluated execution characteristic of multimedia applications on ARM architectures enhanced by SIMD. The authors of [24] focus on different media benchmark kernels and applications, such as DCT, motion estimation kernel, speech, and jpeg encoding applications. They use the results from their evaluations to propose architecture for the media applications they have

selected. They report good SIMD utilization for their applications but there is a need to take care of parallelism existing outside main loops and kernels. In their conclusions, they state that conventional ILP techniques need at least 8 or 16-way superscalar processor to provide improvements. The work in [25] focuses on proposing a low power mobile applications chip for Full-HD multi standard video codec. This design includes not only CPU but also DSP and streaming processor for execution of parts of the video codec. The target is to combine flexibility, provided by the CPU, and streaming processor for higher performance, in a heterogeneous multiprocessor architecture.

The other main approach is using DSP or VLIW processors for multimedia processing. These could also be combined with SIMD unit as in [4,29,31,33,37]. In [29] a 3-way 128bits VLIW is combined with a SIMD style VCP vector co-processing unit with three asymmetric parallel pipelines used for SAD, mean calculations and other kernel filter calculations. The VCP provides a performance boost that can handle up to HD video processing. The work presented in [30] proposes a new instruction set architectures based on variable VILW (32bit-128bit). The aim is to combine high performance with general purpose programmability. In [31] focus is on mapping motion estimation algorithm to a VLIW style DSP. The aim of [32] is to use a parallel Kahn process network KPN model on a VLIW DSP for H.264 encoding enhancement by low level algorithmic optimizations (motion compensation and estimation) with focus on potential instruction level parallelism ILP provided by the compiler. A vector micro-SIMD VLIW architecture is proposed in [33] for H.264 kernel, where the DLP regions of video encoder are improved so that the ILP regions become dominant. In [34], a reconfigurable function unit (RFU) is added to a VLIW architecture is proposed and evaluated for video compression speedups using a reference code. [4] presents a coprocessor chip for mobile baseband chips, using among others DSP to control a set of hardwired functional units for H.264 video compression. The combination of DSP and hardwired processing units gives good flexibility and is nice trade-off between the two extremes, with only using fully programmable verses hardwired design. In [36], a system on chip SoC is proposed and implemented. It combines two multimedia DSPs with CPU for video compression applications. A high performance VLIW DSP architecture is proposed, where the main feature is a flexible data path for using general purpose registers and SIMD units.

Another more resent approach has been to combine CPUs with GPUs for video processing and compression. In [44], they propose a approach where CPU and GPU work in parallel to accelerate video decoding in the PC environment. The GPU is used for part of the motion compensation while the rest of video decoding is done in the CPU. In [43] the focus is on the motion estimation search algorithm which one of the most important differentiating areas between a good and a great encoder. In [45,46] they propose using GPU for improving video encoding performance and at same time deriving the algorithms to be more suitable for GPU implementations. This is an ongoing trend, where the more recent work [48,49] aims to focus on GPU only rather

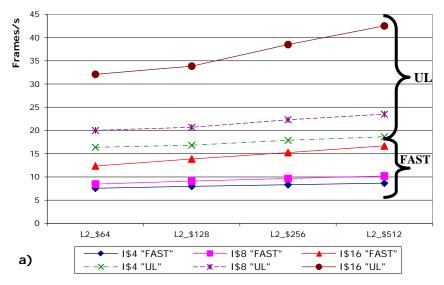

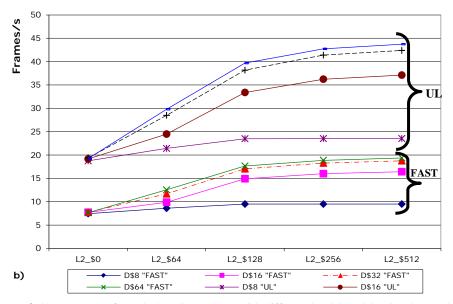

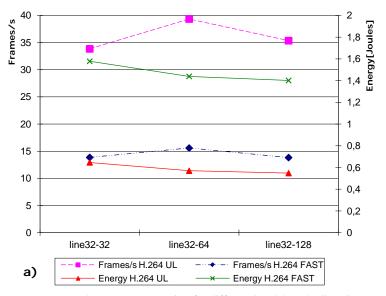

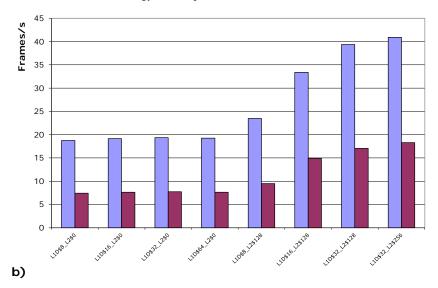

than investigating the optimal partition between GPU and CPU. But one important limitation with GPUs is that they can only perform identical computation concurrently on different stream processors. This makes overlapping different computations (prediction and reconstruction) very difficult [50]. In [51], they instead work on interframe parallelization which is much more suitable for GPUs. In [52] proposes new image analysis algorithms for parallel implementation on GPUs. Another approach for using GPUs and CUDA compute unified device architecture a multi-threaded programming model (hides the architecture from programmer) is used in [42,53,54] for video motion estimation and motion compensation is presented. This is a programming model proposed by nVidia [55] is gaining in popularity as it make the GPGPU much easier to program. Open Computing Language (OpenCL) [56] is the wide industry supported framework for programming for heterogeneous architectures consisting of GPU, CPU and other processor. There are a number of different mobile GPU architectures, such as ARMs Mali [57] and Imagination Technologies POWERVR SGX cores [58], supporting OpenCL,