# LUND UNIVERSITY

#### **Electron Tunneling and Field-Effect Devices in mm-Wave Circuits**

Egard, Mikael

2012

#### Link to publication

*Citation for published version (APA):* Egard, M. (2012). *Electron Tunneling and Field-Effect Devices in mm-Wave Circuits*. [Doctoral Thesis (compilation), Solid State Physics]. Lund University.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

### Electron Tunneling and Field-Effect Devices in mm-Wave Circuits

#### **Mikael Egard**

**Doctoral Thesis**

Supervisor: Professor Lars-Erik Wernersson

> Faculty opponent: Professor Iain Thayne Glasgow University Great Britain

## LUND UNIVERSITY

Department of Physics Division of Solid State Physics Lund, Sweden 2012

Academic Dissertation which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, May 11th, 2012 at 13.15 in Lecture Hall B, Sölvegatan 14A, Lund, for the degree of Doctor of Philosophy in Engineering

| P.O. Box 118<br>SE-221 00 Lund                                                                                                                                                                                                                                                                                                                                                                             | Sponsoring organization                                                                                                                                                  | on                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)<br>Mikael Egard                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                          |                                                                                                                                                        |

| Title and subtitle                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                          |                                                                                                                                                        |

| Electron Tunneling and Field-Effe                                                                                                                                                                                                                                                                                                                                                                          | ect Devices in mm-Wave                                                                                                                                                   | Circuits                                                                                                                                               |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                          |                                                                                                                                                        |

| Short high-frequency electromagnetic pulses, al<br>short-range impulse based ultra-wideband appli<br>and localization. This thesis investigates field-e<br>operation in millimeter-wave (mm-wave) impul<br>the demonstration of a novel high performance                                                                                                                                                   | cations, such as communication<br>ffect and tunneling based semic<br>se transceivers. The main resea                                                                     | n, imaging, radar, spectroscopy,<br>conductor devices and their<br>rch contribution of this work is                                                    |

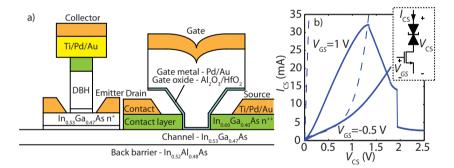

| The first topic of this thesis is the design and fal<br>of the GTD is the ability to switch it between pr<br>differential output conductance (NDC). This ma<br>functionality.                                                                                                                                                                                                                              | ositive differential output condu                                                                                                                                        | ictance (PDC) and negative                                                                                                                             |

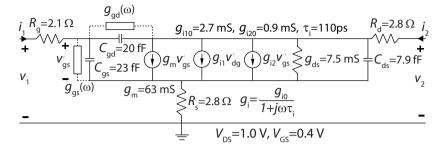

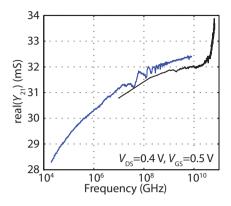

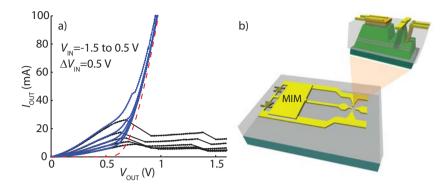

| The second topic is the design and fabrication of<br>architecture was developed with the aim of min<br>and extrinsic transconductance (gm,ext.). A 55-<br>V and VDS=1 V, Ron=199 $\Omega\mu$ m, an extrapolat<br>is analyzed by constructing a small-signal mode<br>band-to-band tunneling, and the wideband frequ<br>gate-all-around nanowire MOSFETs integrated<br>mS/µm, fmax=9.3 GHz, and ft=14.3 GHz. | imizing the on-resistance (Ron)<br>nm-gate length MOSFET yield<br>ed fmax of 292 GHz, and ft of 2<br>el, which includes the influence<br>nency response of gate oxide bo | to increase the on-state current<br>s gm,ext.=1.9 mS/µm at VGS=0.5<br>244 GHz. The device performance<br>of impact ionization,<br>rder traps. Vertical |

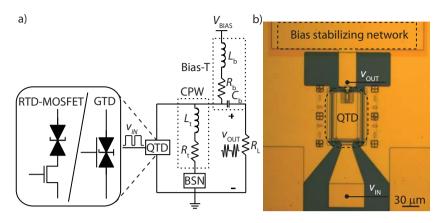

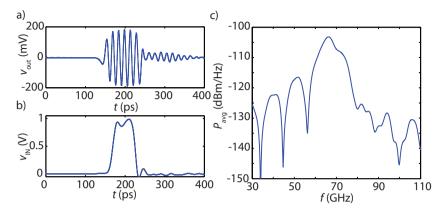

| The regrown MOSFET is furthermore combined<br>integrated in parallel to an inductive coplanar w<br>the RTD-MOSFET between NDC and PDC it is<br>produce mm-wave wavelets. The wavelet gener<br>power of 7 dBm at a rate of 15 Gpulses/s. The w                                                                                                                                                              | aveguide to form an oscillator of<br>s possible to kick-start and rapid<br>ator delivers coherent 41-ps-sho                                                              | circuit. By switching the output of<br>dly quench the oscillator to<br>ort wavelets with a peak output                                                 |

| Key words: Wavelet generator, MOSFET, in<br>negative differential conductant                                                                                                                                                                                                                                                                                                                               | mpulse radio, ultra-wideband,<br>ce oscillator, nanowire, high fi                                                                                                        | resonant tunneling diode,<br>requency characterization                                                                                                 |

| Classification system and/or index termes (if any                                                                                                                                                                                                                                                                                                                                                          | <i>d</i> ):                                                                                                                                                              |                                                                                                                                                        |

| Supplementary bibliographical information:                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                          | Language                                                                                                                                               |

| ISSN and key title:                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                          | ISBN<br>978-91-7473-309-9                                                                                                                              |

| Recipient's notes                                                                                                                                                                                                                                                                                                                                                                                          | Number of pages<br>158                                                                                                                                                   | Price                                                                                                                                                  |

Document name

Date of issue

DOCTORAL DISSERTATION

April 2, 2012

Distribution by (name and address) Division of Solid State Physics, Lund University, Box 118, 221 00 Lund I, the undersigned, being the copyright owner of the abstract of the above-mentioned dissertation, hereby grant to all reference sources permission to publish and disseminate the abstract of the above-mentioned dissertation.

Signature UUUU GUL Date 02-04-2012

Date

Security classification

Signature\_\_\_\_\_

Organization LUND UNIVERSITY

Department of Physics Division of Solid State Physics

## Electron Tunneling and Field-Effect Devices in mm-Wave Circuits

Mikael Egard

Lund 2012

**Doctoral Thesis**

LUND UNIVERSITY

Division of Solid State Physics Department of Physics Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

ISBN 978-91-7473-309-9

© Mikael Egard 2012. Produced using LATEX Documentation System. Printed in Sweden by *Media Tryck*, Lund. April 2012.

## Abstract

Short high-frequency electromagnetic pulses, also referred to as wavelets, are considered for use in various short-range impulse based ultra-wideband applications, such as communication, imaging, radar, spectroscopy, and localization. This thesis investigates field-effect and tunneling based semiconductor devices and their operation in millimeter-wave (mm-wave) impulse transceivers. The main research contribution of this work is the demonstration of a novel high performance InGaAs MOSFET and its integration in a wavelet generator.

The first topic of this thesis is the design and fabrication of a gated tunnel diode (GTD) device. The main feature of the GTD is the ability to switch it between positive differential output conductance (PDC) and negative differential output conductance (NDC). This makes it a versatile element, which can be used to improve circuit functionality.

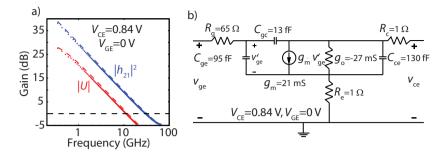

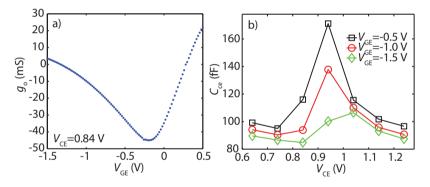

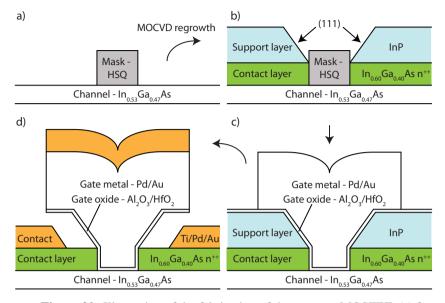

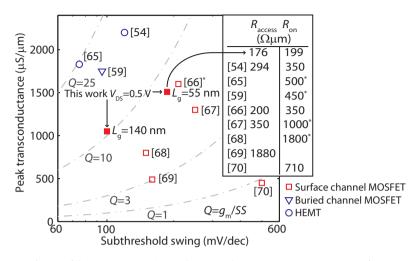

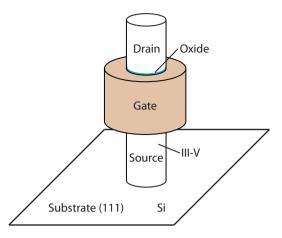

The second topic is the design and fabrication of an epitaxially regrown InGaAs MOSFET. The device architecture was developed with the aim of minimizing the on-resistance ( $R_{\rm on}$ ) to increase the on-state current and extrinsic transconductance ( $g_{\rm m,ext.}$ ). A 55-nm-gate length MOSFET yields  $g_{\rm m,ext.}$ =1.9 mS/ $\mu$ m at  $V_{\rm GS}$ =0.5 V and  $V_{\rm DS}$ =1 V,  $R_{\rm on}$ =199  $\Omega\mu$ m, an extrapolated  $f_{\rm max}$  of 292 GHz, and  $f_{\rm t}$  of 244 GHz. The device performance is analyzed by constructing a small-signal model, which includes the influence of impact ionization, band-to-band tunneling, and the wideband frequency response of gate oxide border traps. Vertical gate-all-around nanowire MOS-FETs integrated on a Si platform are also investigated and exhibit  $g_{\rm m,ext.}$ =0.155 mS/ $\mu$ m,  $f_{\rm max}$ =9.3 GHz, and  $f_{\rm t}$ =14.3 GHz.

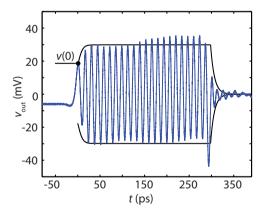

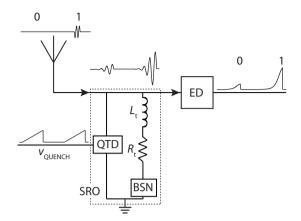

The regrown MOSFET is furthermore combined with an RTD to form a switchable NDC component, which is integrated in parallel to an inductive coplanar waveguide to form an oscillator circuit. By switching the output of the RTD-MOSFET between NDC and PDC it is possible to kick-start and rapidly quench the oscillator to produce mm-wave wavelets. The wavelet generator delivers coherent 41-ps-short wavelets with a peak output power of 7 dBm at a rate of 15 Gpulses/s. The wavelets are generated at an energy consumption of 1.9 pJ/pulse.

## Populärvetenskaplig sammanfattning

Arbetet i denna avhandling berör elektroniska komponenter och hur de kan användas i kretsar för trådlös kommunikation. Den huvudsakliga slutsatsen av arbetet är att innovativa och icke konventionella komponenter kan bidra till att förbättra presentanda och minska effektförbrukningen i system för kommunikation på Framförallt har en korta avstånd. krets tillverkats som genererar extremt korta och högfrekventa elektromagnetiska pulser med frekvens upp till 100 GHz, pulslängd ner till 33 ps och med en repetitionshastighet på upp till 15 Gbit/s. För att möjliggöra detta så har en ny typ av transistor utvecklats. Den främsta egenskapen hos denna transistor är att den opererar vid en väldigt hög hastighet samtidigt som den konsumerar mycket lite energi.

Första gången människan kommunicerad trådlöst, om man bortser från liud och skrift, var när Guglielmo Marconi skickade elektromagnetiska pulser genom luften år 1894. Dessa pulser skapades genom elektromagnetiska urladdningar som kopplades via en sändande antenn ut i etern och vidare till en mottagande antenn där signalen registrerades. Sedan dess har den trådlösa teknologin utvecklats i rasande takt och har gett upphov till olika produkter så som radar, television och mobiltelefoni. Metoderna har förfinats och gjorts allt mer raffinerade och idag kan man trådlöst skicka mer information per sekund än som kunde lagras totalt på en persondator i början av 1990talet.

För att fortsätta utvecklingen så krävs nya elektroniska komponenter som kan operera vid högre hastighet och vid mindre effektförbrukning. I detta arbete har fyra olika komponenter studerats. De första två är transistorer byggda från material i grupp 13 och 15 i det periodiska systemet, dessa material benämns även som grupp III och V och har egenskaper som gör att det går att tillverka snabbare och strömsnålare transistorer än med konventionell kiselteknologi. Användningen av III-V material gör att nya komponentstrukturer måste utvecklas. I denna avhandling undersöks en transistor där extra ledande material har tillförts för att minska effektförbrukningen och en transistor där den kontrollerande elektroden omsluter hela den kanal där strömmen färdas, vilket gör att strömmen går att styra på ett mycket effektivt sätt.

Den tredje komponenten baseras på det kvantmekaniska fenomenet tunnling, som innebär att en ström kan flyta genom en region där den enligt klassisk mekanik inte borde kunna existera. Den fjärde komponenten baseras på samma fenomen, men där har en tredje elektrod integrerats för extra funktionalitet.

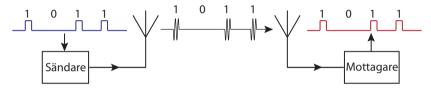

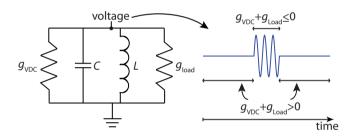

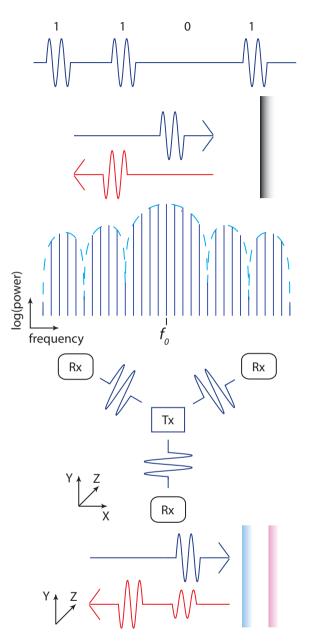

Tunnlingskomponenterna besitter negativ resistans vilket gör att de kan användas för att tillföra energi i en krets. Genom att integrera en tunnlingskomponent i en resonanskrets så kan en elektromagnetisk svängning produceras. Arbetet i denna avhandling visar att genom att använda en transistor i serie med tunnlingskomponenten så kan svängningen strypas på ett effektivt sätt när transistorn slås mellan lågt och högt motstånd. Resultatet blir då korta högfrekventa pulser som kan användas för att skicka data mellan en sändare och mottagare, vilket illustreras av Fig. 1. Den framtagna kretsen kan även användas i en mottagare genom att rekonfigurera den elektriska styrsignalen till kretsen. Detta gör att sändare och mottagare kan bestå av samma krets, vilket minskar storleken på systemet och tillverkningskostnaden.

De korta högfrekventa pulserna som sändaren producerar kan även användas i system som mäter avstånd, position, eller som används för att se genom objekt som inte är transparenta för synligt ljus.

**Figure 1:** Illustration av hur kretsen som utvecklats i detta arbete kan användas i ett system för trådlös kommunikation.

## Preface

This thesis summarizes my academic work for the Doctoral degree in Physics. The work has been done within the Nanoelectronics group at Lund University. The content of this thesis is divided into two parts. The first part serves as an introduction to the second part which constitute of the research papers included in this thesis.

#### List of papers

I. M. Egard, M. Ärlelid, E. Lind, G. Astromskas, and L.-E. Wernersson, "20 GHz Wavelet Generator using a Gated Tunnel Diode", *Microwave and Wireless Components Letters, IEEE*, vol. 19, no. 6, pp. 386-388, June 2009.

I did the circuit design, fabrication, measurements, modeling, and I wrote the paper.

II. M. Ärlelid, M. Egard, E. Lind, and L.-E. Wernersson. "Coherent V-Band Pulse Generator for Impulse Radio BPSK", *Microwave and Wireless Components Letters, IEEE*, vol. 20, no. 7, pp. 414-416, July 2010.

I did the fabrication and took part in writing the paper.

III. M. Ärlelid, M. Egard, L. Ohlsson, E. Lind, and L.-E. Wernersson. "Impulse-Based 4 Gbps Radio Link at 60 GHz", *Electronic Letters*, vol. 47, no. 7, pp. 467-468, March 2011.

I did the fabrication and took part in writing the paper.

IV. M. Egard, M. Ärlelid, E. Lind, and L.-E. Wernersson. "Bias Stabilization of Negative Differential Conductance Circuits Operated in Pulsed Mode", *Transactions on Microwave Theory and Techniques, IEEE*, vol. 59, no. 3, pp. 672-677, March 2011.

I did the circuit design, fabrication, measurements, modeling, and I wrote the paper.

V. M. Ärlelid, **M. Egard**, L. Ohlsson, E. Lind, and L.-E. Wernersson. "A 400 Msamples/s Super-Regenerative Receiver", manuscript.

I did the fabrication and took part in writing the paper.

VI. M. Egard, L. Ohlsson, B. M. Borg, F. Lenrick, R. Wallenberg, L.-E. Wernersson, and E. Lind "High Transconductance Self-Aligned Gate-Last Surface Channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET", *International Electron Devices Meeting*, *IEDM 2011, IEEE*, pp. 13.2.1-13.2.4, Dec. 2011.

I planned and coordinated the project, did the device design, fabrication, measurements, modeling, and I wrote the paper. VII. M. Egard, L. Ohlsson, M. Ärlelid, B. M. Borg, F. Lenrick, R. Wallenberg, L.-E. Wernersson, and E. Lind "High-Frequency Performance of Self-Aligned Gate-Last Surface Channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET", *Electron Device Letters*, *IEEE*, vol. 33, no. 3, pp. 369-371, March 2012.

I planned and coordinated the project, did the device design, fabrication, measurements, modeling, and I wrote the paper.

VIII. M. Egard, M. Årlelid, L. Ohlsson, E. Lind, and L.-E. Wernersson. "In 0.53Ga0.47As RTD-MOSFET mm-Wave Wavelet Generator", in press *Electron Device Letters*, *IEEE*, 2012.

I planned and coordinated the project, did the circuit design, fabrication, measurements, modeling, and I wrote the paper.

IX. **M. Egard**, S. Johansson, A.-C. Johansson, K.-M. Persson, A. Dey, B. M. Borg, C. Thelander, L.-E. Wernersson, and E. Lind. "Vertical InAs Nanowire Wrap Gate Transistors With  $f_t > 7$  GHz and  $f_{max} > 20$  GHz", *Nano Lett.*, vol. 10, no. 3, pp. 809-812, Feb. 2010.

I did the measurements, modeling, and I wrote the paper.

X. S. Johansson, M. Egard, S. Ghalamestani, M. Borg, M. Berg, L.-E. Wernersson, and E. Lind. "RF-Characterization of Vertical InAs Nanowire Wrap Gate Transistors Integrated on Si Substrates", *Transactions on Microwave Theory and Techniques, IEEE*, vol. 59, no. 10, pp. 2733-1738, Oct. 2011.

I did the S-parameter measurements, modeling, and I wrote parts of the paper.

The following lists other contributions to scientific journals, conferences, or patent applications that are related to the topic of this thesis. However, they have not been included here as they are beyond the scope of this thesis or have overlapping content with the previous listed articles. The author changed his last name from Nilsson to Egard during the course of his PhD studies.

- M. Ärlelid, M. Nilsson, G. Astrsomskas, E. Lind and L.-E. Wernersson. "High Tuning-Range VCO Using a Gated Tunnel Diode", oral presentation at the *International Conference on Solid State Materials and Devices 2007*, pp. 798-799 Sept. 2007.

- M. Nilsson, M. Ärlelid, E. Lind, G. Astromskas and L.-E. Wernersson. "20 GHz Gated Tunnel Diode Based UWB Pulse Generator", oral presentation at the *International Symposium on Compound Semiconductors 2008*, pp. Tu 1.6.1-1.6.2, Sept. 2008.

- L.-E. Wernersson, M. Ärlelid, M. Egard, and E. Lind. "Gated Tunnel Diode in Oscillator Applications with High Frequency Tuning", *Solid-State Electronics*, vol. 53, no. 3, pp. 292-296, March 2009.

- M. Egard, M. Ärlelid, E. Lind, G. Astromskas, and L.-E. Wernersson. "20 GHz Gated Tunnel Diode Based UWB Pulse Generator", *Physica Status Solidi* (c), vol. 6, no. 6, pp. 1399-1402, April 2009.

- M. Egard, M. Ärlelid, E. Lind, P. Caroff, G. Astromskas, M. Borg, and L.-E. Wernersson. "60 GHz Wavelet Generator for Impulse Radio Applications", oral presentation at the *38th European Microwave Conference, EuMC 2009, IEEE*, pp. 1908-1911, Sept. 2009.

- M. Årlelid, M. Egard, E. Lind, and L.-E. Wernersson. "60 GHz Ultra-Wideband Impulse Radio Transmitter", oral presentation at the *International Conference* on Ultra-Wideband, ICUWB 2009, IEEE, pp. 185-188, Sept. 2009.

- M. Egard, M. Ärlelid, E. Lind, and L.-E. Wernersson. "A 12.5 Gpulses/s 60 GHZ Bi-Phase Wavelet Generator", oral presentation at the 34th International European Workshop on Compound Semiconductor Devices and Integrated Circuits, WOCSDICE 2010, pp. 51-52, May 2010.

- M. Egard, M. Ärlelid, E. Lind, and L.-E. Wernersson. "Gated Tunnel Diode with a Reactive Bias Stabilizing Network for 60 GHz Impulse Radio Implementations", oral presentation at the 68th International Device Research Conference, DRC 2010, IEEE, pp. 161-162, Aug 2010.

- L.-E. Wernersson, M. Egard, M. Ärlelid, and E. Lind. "Tunneling-Based Devices and Circuits", invited presentation at the 68th International Conference on IC Design and Technology, ICICDT 2010. IEEE, pp. 190-193, July 2010.

- M. Ärlelid, M. Egard, E. Lind, and L.-E. Wernersson. "A 60 GHz Superregenerative Oscillator for Implementation in an Impulse Radio Receiver", best student paper award presentation at the *International Conference on Ultra-Wideband, ICUWB 2010, IEEE*, pp. 1-4, Sept. 2010.

- M. Ärlelid, M. Egard, L. Ohlsson, E. Lind, and L.-E. Wernersson. "60 GHz Impulse Radio Measurements", oral presentation at the *International Conference on Ultra-Wideband, ICUWB 2011, IEEE*, pp. 536-440, Sept. 2011.

- D. Sjöberg, M. Egard, M. Ärlelid, G.P. Vescovi, and L.-E. Wernersson. "Design and Manufacturing of a Dielectric Resonator Antenna for Impulse Radio at 60 GHz", oral presentation at the *3rd European Conference on Antennas and Propagation, EuCAP 2009, IEEE*, pp. 3549-3553, March 2009.

- L. Ohlsson, D. Sjöberg, M. Ärlelid, M. Egard, E. Lind, and L.-E. Wernersson. "Admittance Matching of 60 GHz Rectangular Dielectric Resonator Antennas for Integrated Impulse Radio", poster presentation at the *Loughborough Antennas & Propagation Conference, LAPC 2010, IEEE*, pp. 253-256, Nov. 2010.

- 24. M. Egard, L. Ohlsson, B. M. Borg, L.-E. Wernersson, and E. Lind "Self-Aligned Gate-Last Surface Channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET with Selectively Regrown Source and Drain Contact Layers", late news presentation at the 69th International Device Research Conference, DRC 2011, IEEE, pp. 1-2, June 2011.

- E. Lind, M. Egard, S. Johansson, A.-C. Johansson, K.-M. Persson, A. Dey, B. M. Borg, C. Thelander, and L.-E. Wernersson. "High Frequency Performance of Vertical InAs Nanowire MOSFET", oral presentation at the 22nd International Conference on Indium Phosphide and Related Materials, IPRM 2010, IEEE, pp. 1-4, July 2010.

- S. Johansson, S. G. Ghalamestani, M. Egard, B. M. Borg, M. Berg, L.-E. Wernersson, and E. Lind. "High-Frequency Vertical InAs Nanowire MOSFETs Integrated on Si Substrates", oral presentation at the 38th International Symposium on Compound Semiconductors, ISCS 2011, IEEE, pp. 471-472, May 2011.

- S. Johansson, M. Egard, S. G. Ghalamestani, B. M. Borg, M. Berg, E. Lind, and L.-E. Wernersson. "High-Frequency Characterization of Vertical InAs Nanowire Wrap-Gate FETs on Si(111) Substrates", late news presentation at the 38th International Conference on Solid State Materials and Devices, SSDM 2011, pp. KM-4-3, Sep. 2011.

- S. Johansson, S. G. Ghalamestani, M. Egard, B. M. Borg, M. Berg, L.-E. Wernersson, and E. Lind. "High-Frequency Vertical InAs Nanowire MOSFETs Integrated on Si Substrates", *Physica Status Solidi* (c), vol. 9, no. 2, pp. 350-353, Feb. 2012.

Patent applications

- M. Egard, E. Lind, and L.-E. Wernersson. "Process for Manufacturing a Semiconductor Device and an Intermediate Product for the Manufacture of a Semiconductor Device", Patent Cooperation Treaty (PCT) application EP2011/059190, submitted to *European Patent Office (EPO)*, June 2011.

- M. Egard, M. Ärelid, and L.-E. Wernersson. "Transceiver Module", Patent Cooperation Treaty (PCT) application EP2011/058847, submitted to *European Patent Office (EPO)*, May 2011.

- L.-E. Wernersson, E. Lind M. Ärlelid, M. Nilsson. "Ultrabredbandig Sändare och Mottagare", Swedish patent application SE 0700531-7, submitted to *Patent* och Registreringsverket, Feb. 2007.

## Contents

| Absti  | act                                                                                                                                          |                                                                                                                                                                           | iii                                                                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Popu   | lärv                                                                                                                                         | etenskaplig sammanfattning                                                                                                                                                | v                                                                                                         |

| Prefa  | ce                                                                                                                                           |                                                                                                                                                                           | vii                                                                                                       |

| Cont   | ents                                                                                                                                         |                                                                                                                                                                           | xi                                                                                                        |

| Ackn   | owle                                                                                                                                         | edgments                                                                                                                                                                  | xiii                                                                                                      |

| List o | of Ac                                                                                                                                        | cronyms                                                                                                                                                                   | XV                                                                                                        |

| List o | of Sy                                                                                                                                        | ymbols                                                                                                                                                                    | xvii                                                                                                      |

| Intro  | duct                                                                                                                                         | tion                                                                                                                                                                      | 1                                                                                                         |

| 2      | <ol> <li>1.1</li> <li>1.2</li> <li>The</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>The</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ol> | kground and Motivation       60 GHz ultra-wideband communication         1.1.1       Ultra-wideband impulse radio communication         High frequency wavelet generators | 1<br>2<br>4<br>6<br>9<br>10<br>14<br>17<br>17<br>18<br>21<br>21<br>25<br>27<br>32<br>32<br>33<br>36<br>37 |

|        |                                                                                                                                              | InGaAs MOSFET and RTD                                                                                                                                                     | 41                                                                                                        |

| 5      |                                                                                                                                              | Wavelet Generator                                                                                                                                                         | <b>43</b><br>44<br>46<br>50<br>57                                                                         |

| 5.2 Super regenerative oscillator detector                                                                                          | 57  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6 Conclusions and Outlook                                                                                                           | 59  |

| A Calculation of Current Density Through the DBH                                                                                    | 61  |

| References                                                                                                                          | 63  |

| Paper I - 20 GHz Wavelet Generator Using a Gated Tunnel Diode                                                                       | 73  |

| Paper II - Coherent V-Band Pulse Generator for Impulse Radio BPSK                                                                   | 79  |

| Paper III - Impulse-Based 4 Gbps Radio Link at 60 GHz                                                                               | 85  |

| Paper IV - Bias Stabilization of Negative Differential Conductance Circuits<br>Operated in Pulsed Mode                              | 89  |

| Paper V - A 400 Msamples/s Super-Regenerative Receiver                                                                              | 97  |

| Paper VI - High Transconductance Self-Aligned Gate-Last Surface Channel $In_{0.53}Ga_{0.47}As$ MOSFET                               | 103 |

| Paper VII - High-Frequency Performance of Self-Aligned Gate-Last Surface<br>Channel In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET | 109 |

| Paper VIII - $In_{0.53}Ga_{0.47}As$ RTD-MOSFET mm-Wave Wavelet Generator                                                            | 115 |

| Paper IX - Vertical InAs Nanowire Wrap Gate Transistors With $f_{\rm t} >$ 7 GHz and $f_{\rm max} >$ 20 GHz                         | 121 |

| Paper X - RF-Characterization of Vertical InAs Nanowire Wrap Gate Transis-<br>tors Integrated on Si Substrates                      | 127 |

## Acknowledgments

Five years goes by in a hurry, but looking at what I have experienced during this period it rather feels like a very long time. I have many people to thank for these experiences and I would like to acknowledge a few of all of you that have been a part of my life during this time.

I started my PhD studies in spring of 2007 when professor Lars-Erik Wernersson gave me the opportunity to look into the exciting field of nanoelectronics. The first project was the gated tunnel diode, which you, Lars-Erik, started to develop during your own PhD studies, and I could actually feel that it was almost as you handed me your baby to look after and take care of. Many projects later I would like to thank you for your expertise, inspiration, and encouragement.

My assistant supervisor Erik Lind is the second person that deserves a special recognition. I have really enjoyed working with you, especially on the MOSFET projects were you have been a solid rock that I, among others, have relied on. To quote one of you former master students "Erik is the best that FTF has ever produced". I would also like to thank my second assistant supervisor, professor Henrik Sjöland, for sharing your wisdom regarding high-frequency electronics.

Mats Ärlelid, dear colleague, I have heard people describing us as an old married couple, arguing and finishing each other sentences. Family is very important to me and I am really happy that we will be able to continue working together.

Lars Ohlsson, you have been an extremely valuable addition to the Wavelet generator team and it has been great working with you. You also deserve extra credit for not complaining when I ask you to run tests in the laboratory, one idea stupider than the other.

Mattias Borg, Gvidas Astromskas, Philippe Caroff, and Johannes Svensson, you have all contributed to the work of this thesis with your expertise in epitaxial growth, and as always, no device is better than the material it is fabricated from. A great example of this are the Nanowire MOSFETs, and I would like to thank Karl-Magnus Persson, Sofia Johansson, Anil Dey, Ann-Charlotte Johansson, Sepideh Ghalamestani, Martin Berg, and Claes Thelander for developing such great devices.

Apart from assisting in the diploma work of Lars Ohlsson I have also been assisting Giuliano Vescovi, Kristveig Thorbergsdottir, Johannes Bengtsson, and Elvedin Memisevic. You have all contributed to the research at the department in an excellent way and I would like to take the opportunity to thank the teachers, fellow PhD students, and staff at Solid State Physics for producing such great students. It has been a fantastic environment to work in, with extremely intelligent and productive people wherever I have turned. I would especially like to recognize Kristian Storm for always being eager to help me with challenges that I have faced during this work, which are mostly related to the painstaking task of semiconductor device fabrication. Fortunately, I have always had the staff of the Lund Nano Lab to assist me; it has been a pleasure to work in such great facilities. Now to the persons that have helped me staying sane during this work. Whether it is a lively after work, barbecue at the beach, road trip to Hamburg, or chilling in a hot tube in the back of your garden, you, my friends, always make me feel at ease. The same goes for my in-laws Ann and Nils-Gustav, and my parents Gunnel and Jan who have always been there for me. I cannot thank my younger brothers Robert and Tommy enough, you are the best, and both of you have actively helped me with the work presented in this thesis, which I think is really cool.

I have understood that I give a very calm and professional impression at the department. The person that makes this possible is my wife Jessika, as she gets to deal with the opposite sides of my personality at home. Isabelle and Jessika, you are the love and joy of my life.

Mikael Egard

- Det ser ut som om någon har slirat med moppen på ditt prov Robert Nilsson age 15 during his "prao" at Solid State Physics

# List of Acronyms

| BER     | Bit error rate                                      |

|---------|-----------------------------------------------------|

| BSN     | Bias stabilizing network                            |

| BTBT    | Band-to-band-tunneling                              |

| CPW     | Coplanar Waveguide                                  |

| DBH     | Double barrier heterostructure                      |

| EBL     | Electron beam lithography                           |

| ED      | Energy detector                                     |

| EII     | Electron impact ionization                          |

| EIRP    | Equivalent isotropically radiated power             |

| EOT     | Equivalent oxide thickness                          |

| FCC     | Federal Communications Commission                   |

| GAA     | Gate all around                                     |

| GTD     | Gated tunnel diode                                  |

| HEMT    | High electron mobility transistor                   |

| HBT     | Heterojunction bipolar transistor                   |

| IR      | Impulse radio                                       |

| ITRS    | International Technology Roadmap for Semiconductors |

| MBE     | Molecular beam epitaxy                              |

| MIM     | Metal-insulator-metal                               |

| mm-wave | Millimeter wave                                     |

| MOCVD   | Metalorganic chemical vapor deposition              |

| MOSFET  | Metal-oxide-semiconductor field-effect transistor   |

| NDC     | Negative differential conductance                   |

| NW      | Nanowire                                            |

| OFDM    | Orthogonal frequency-division multiplexing          |

|         |                                                     |

| PA   | Power amplifier                   |

|------|-----------------------------------|

| PDC  | Positive differential conductance |

| PRF  | Pulse repetition frequency        |

| QTD  | Quenchable tunnel diode           |

| RTD  | Resonant tunneling diode          |

| S    | Scattering                        |

| SCR  | Space charge region               |

| SNR  | Signal to noise ratio             |

| SRO  | Super-regenerative oscillator     |

| UWB  | Ultra-wideband                    |

| VLSI | Very-large-scale integration      |

| VNA  | Vector network analyzer           |

| WLAN | Wireless local area network       |

## **List of Symbols**

| $A_{\rm RTD}$       | Resonant tunneling diode area                     |

|---------------------|---------------------------------------------------|

| $C_{\rm ce}$        | Collector emitter capacitance                     |

| $C_{\rm gp1}$       | Contact layer-to-gate overlap capacitance         |

| $C_{\rm gp2}$       | Contact-to-gate fringing capacitance              |

| $C_{\rm ox}$        | Gate oxide capacitance                            |

| $C_{\rm s}$         | Bias stabilizing capacitance                      |

| $C_{\rm sc}$        | Semiconductor capacitance                         |

| $D_{\rm it}$        | Interface trap density                            |

| $\Delta I$          | Peak to valley current difference                 |

| $\Delta V$          | Peak to valley voltage difference                 |

| $\epsilon_{\rm ox}$ | Oxide permittivity                                |

| $E_{\rm p}$         | Energy consumption per wavelet                    |

| $f_0$               | Fundamental oscillation frequency                 |

| $f_{\rm max}$       | Maximum oscillation frequency                     |

| $f_{\rm t}$         | Current gain cut-off frequency                    |

| $g_{ m L}$          | Load conductance                                  |

| $g_{ m m}$          | Intrinsic transconductance                        |

| $g_{\rm m,ext}$     | Extrinsic transconductance                        |

| $G_{\rm o}$         | DBH large signal output conductance               |

| $g_{\rm o}$         | DBH small signal output conductance               |

| $g_{i1}$            | Transconductance related to gate-drain potential  |

| $g_{\mathrm{i}2}$   | Transconductance related to gate-source potential |

| $g_{ m o,min}$      | DBH minimum small signal output conductance       |

| $h_{21}$            | Current gain                                      |

| $I_{\rm off}$       | Off-state current                                 |

|                     |                                                   |

| $I_{\rm on}$        | On-state current                      |

|---------------------|---------------------------------------|

| $J_{\rm p}$         | RTD peak current                      |

| $J_{\rm v}$         | RTD valley current                    |

| $k_{\rm B}$         | Boltzmann constant                    |

| $L_{\rm c}$         | Contact length                        |

| $L_{\rm b}$         | Bias inductance                       |

| $L_{\rm g}$         | Gate length                           |

| $L_{\rm gc}$        | Gate to contact spacing               |

| $L_{\rm tw}$        | Gate overhang length                  |

| $L_{\rm t}$         | Coplanar waveguide inductance         |

| $m^*$               | Effective mass                        |

| $N_{\rm bt}$        | Border trap density                   |

| $P_{\rm peak}$      | Peak output power                     |

| $Q_{\mathrm{tank}}$ | Tank circuit quality factor           |

| $R_{\rm access}$    | Access resistance                     |

| $R_{\rm c}$         | Collector resistance                  |

| $R_{\rm cn}$        | Contact resistance                    |

| $R_{\rm e}$         | Emitter resistance                    |

| $R_{\rm g}$         | Gate resistance                       |

| $R_{\rm gc}$        | Gate to contact resistance            |

| $R_{\rm on}$        | On-resistance                         |

| SS                  | Subthreshold swing                    |

| $t_{\rm c}$         | Contact layer thickness               |

| $	au_{\mathrm{i}}$  | Time constant related to EII and BTBT |

| $T_{\rm L}$         | Lattice temperature                   |

| $t_{\rm ox}$        | Oxide thickness                       |

| $t_{ m r}$          | Support layer height                  |

| $\mu$               | Mobility                              |

| U                   | Unilateral power gain                 |

| v(0)                | Oscillator initial condition          |

|                     |                                       |

| $V_{\rm DBH}$ | Voltage drop across the DBH |

|---------------|-----------------------------|

| $V_{\rm dd}$  | Supply voltage              |

| $v_{\rm inj}$ | Injection velocity          |

| $V_{\rm p}$   | RTD peak current voltage    |

| $V_{\rm v}$   | RTD valley current voltage  |

| $V_{\rm th}$  | Threshold voltage           |

| $W_{\rm g}$   | Gate width                  |

| $\omega_0$    | Angular frequency           |

$Y_{\rm xy}$  Admittance

# Introduction

## Introduction

#### **Chapter 1**

#### **Background and Motivation**

Electromagnetic wireless communication has been around since the discovery of wireless telegraphy back in the 19th century [1]. This marked the beginning of an era, which to present day has given us innovations such as television, radar, mobile phone, etc. The impact of these technologies on our society cannot be underestimated, with that said, we have just started to see the possibilities that wireless data communication will be able to provide. In the recent decade, new technologies for high data rate communication at short distances have emerged. Bluetooth and wireless local area network (WLAN) are two examples. These solutions have given us a glimpse of what a truly wireless environment would bring, an environment where all our gadgets talk to us and to each other, without the inconvenience of wires. Bluetooth marked the beginning of this era with its data rate of 1 Mbit/s, WLAN has pushed the rate to more than 100 Mbit/s. In the search for new technologies that will increase the bit rate and lower the power consumption, spread spectrum techniques such as Ultra-wideband (UWB) communication are highly interesting and are explored in the industry, at universities, and at research institutes. UWB communication in the 3.1-10.6 GHz band now delivers 480 Mbit/s, and with the new IEEE standard for the 60 GHz band, UWB will offer data rates of 2 Gbit/s and higher [2].

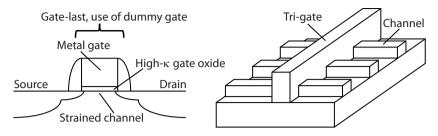

One factor that has made it possible to increase the speed of wireless communication is the increase in transistor performance. Faster transistors translate into higher data rates and lower power consumption per bit. Microelectronics, and in recent years nanoelectronics, has provided us with generation after generation of high performance transistors. However, conventional Si transistor technology is running out of steam and that is why novel device concepts are being investigated. The resonant tunneling diode (RTD), the gated tunnel diode (GTD), the regrown metaloxide—semiconductor field-effect transistor (MOSFET), and the nanowire (NW) MOSFET presented in this thesis are examples of such devices. This thesis especially focuses on the use of these devices in circuits generating wavelets, which is a short burst of electromagnetic energy that can be used as the basis for UWB communication. The outline of this thesis is;

Chapter 1 presents the concept of ultra-wideband communication and how the wavelet

generator contributes to this field of research.

**Chapter 2** introduces the theory of resonant tunneling diodes and describes the operation, fabrication, and characterization of the gated tunnel diode.

**Chapter 3** gives an introduction to the field of III-V MOSFETs. Device architecture considerations are discussed in detail and related to the fabrication of a regrown MOS-FET. This chapter also covers high-frequency characterization of electronic devices.

**Chapter 4** describes the series integration of a resonant tunneling diode and the regrown MOSFET.

**Chapter 5** covers the design and fundamental operation of the wavelet generator. Measurement results are accompanied by analytical modeling of the circuit operation.

**Chapter 6** summarizes the thesis and discusses future applications and challenges for the wavelet technology.

#### 1.1 60 GHz ultra-wideband communication

As given by the name "Ultra-Wideband" communication, this technique of transmitting data makes use of a very wideband frequency spectrum. This is in contrast to conventional narrow band carrier modulation methods. According to Shannon's law

$$C = BW \log_2(1 + \frac{S}{N}),\tag{1}$$

which describes the channel capacity C (bit/s), either an increase in the signal power S (W) or the bandwidth BW (Hz) gives an increased upper bound on the data rate when transmitting in an channel with white additive Gaussian noise N (W). Equation (1) further states that for a fixed signal to noise ratio (S/N) the upper bound on the data rate is proportional to the bandwidth. This is why huge channel capacities can be achieved without utilizing higher order modulations that require large S/N ratios. This illustrates one of the benefits of UWB communication.

Besides the achievable data rates, one very interesting benefit of spreading the transmitted energy over a large bandwidth is that it reduces the interference to other communication systems, as the signal power at one discrete spectral component is low. How much power an UWB signal is allowed to carry at a certain frequency is regulated by the Federal Communication Commission (FCC) in the US, and corresponding authorities in the rest of the world. For the 3.1 to 10.6 GHz band the FCC decided in 2002 that a signal is considered UWB if its bandwidth exceeds 500 MHz or 20% of its center frequency, and that it is not allowed to exceed -41.3 dBm/MHz at any frequency in this band [3]. UWB communication in the 3.1 to 10.6 GHz band has not been the expected success, much due to additional constraints imposed by the regulatory document. The maximum achievable data rate that is targeted as of now is 480 Mbit/s [2, 4]. Instead, industry and the research community is turning their attention

|               | Unlicensed spectrum (GHz) |

|---------------|---------------------------|

| North America | 57-64                     |

| Europe        | 59-66                     |

| Australia     | 59.4-62.9                 |

| Korea         | 57-64                     |

| Japan         | 59-66                     |

| 1             |                           |

Table 1: Available unlicensed spectrum at 60 GHz

to the 60 GHz band with its 5 GHz of almost worldwide unlicensed bandwidth [5,6], which is listed in Table 1. Besides the band being worldwide unlicensed and accepted, the high frequency decreases the critical dimensions of the antennas to millimeter size. Combining several antennas and controlling the phase among the multiple outputs provides the possibility to only transmit power in the desired direction [2]. This decreases intersymbol interference, interuser interference, and destructive interference (fading) from multipath components [7].

At 60 GHz the free-space path loss

$$L = 20 \log_{10} \frac{4\pi d}{\lambda},\tag{2}$$

where d is the distance and  $\lambda$  is the wavelength, is 28 dB larger than at the 2.4 GHz WLAN band, and combined with an increased material attenuation at higher frequencies restricts the targeted 60 GHz communication scenarios to line-of-sight and in-the-room [5]. Examples of applications where 60 GHz communication could have, and already has, a great impact are simple docking solutions for downloading high definition content or wireless connection to a display.

When UWB communication was first introduced the idea was to generate short pulses in the time domain that translates into a wideband signal in the frequency domain, this is known as UWB Impulse Radio (IR) communication. However, the regulation describing the transmission of UWB signals allows for the transmission of any signal that fulfills the emission regulations, which makes techniques such as Orthogonal Frequency Division Multiplexing (OFDM) interesting [5]. OFDM uses the robustness of standard digital coding to modulate a continuous carrier signal, the data is then transmitted in N different sub-channels using orthogonal carrier signals to avoid interference. Two frequencies are considered orthogonal when they are separated by  $\Delta f = 1/T_0$ , where  $T_0$  is the time it takes to transmit a symbol on the corresponding carrier [8]. Designing the subchannels correctly will make the transmitted signal as a whole fulfill the requirements for a signal to be considered UWB. The OFDM way of UWB communication is a complex solution as it deals with the parallel transmission in N subchannels. This requires sophisticated transmitter and receiver circuits, which

have large power consumption, but high bit rates, high spectral efficiency, and low bit error rate (BER) [7].

#### 1.1.1 Ultra-wideband impulse radio communication

UWB IR communication is based on the transmission of short pulses representing the data, much like the first spark radio transmitters designed by Marconi [1]. The benefit of UWB IR communication is that high bit rates may be achieved using lowcomplexity transmitter layouts with a very low power consumption. The duration of the transmitted pulses are typically a few hundred picoseconds long [8] and one or several pulses can be used to represent each bit, a higher energy per bit decreases the BER. Different techniques to modulate the data using IR UWB exist, examples are pulse position modulation (PPM), pulse amplitude modulation (PAM), and phase shift keying (PSK). The simplest system relies on non-coherent receiver schemes where energy detection is used, PSK implementations requires coherent systems, which decreases the BER, but requires more complex receiver structures.

It should also be mentioned that UWB IR is relatively immune to multipath fading, as compared to continuous wave carrier based narrow band radio, which experience deep fades. The reason is that the transmitted UWB IR pulses are very short in time and space, hence the multipath reflections will not overlap the main part of the pulse [9, 10].

Besides high speed data communication, UWB IR is considered for applications

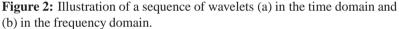

**Figure 3:** Illustration of 4 different wavelet generator implementations, (a) upconversion of a baseband pulse, (b) filtering a baseband pulse, (c) passing a continuous oscillator signal through a series of switches, and (d) switching an oscillator on and off.

in radar [11], spectroscopy [12], localization [13], and imaging [14]. Different applications have different requirements when it comes to range, pulse length, and pulse repetition time, but they are all based on the same basic circuit topology.

#### 1.2 High frequency wavelet generators

Two different types of techniques are commonly used for generating pulses in UWB IR systems, the first category includes pulses generated by digital circuits. These pulses are created by controlling the delay among individual baseband signals and combining them into the desired output waveform [15]. Compact pulse generators may be created using this technique, it is however challenging to obtain high output power in the 60 GHz band [16, 17].

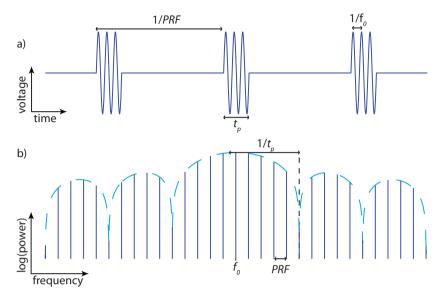

The second category of UWB IR signals consists of pulses, or wavelets as they are also denoted, which are generated from a carrier signal. An illustration of such a signal is shown in Fig. 2(a). The spectral shape is given by the center frequency of the carrier signal  $f_0$ , the pulse length  $t_p$ , and the pulse repetition frequency (PRF), as given by Fig. 2(b). The spectral shape is also determined by the envelope of the pulse in the time domain.

Different examples of wavelet generators are illustrated in Fig. 3. The input signal to all different types of wavelet generators is a baseband pulse and the wavelet is delivered to a power amplifier (PA) or directly to an antenna. Figure 3(a) describes the solution presented by Wentzloff *et al.* in [18], where a baseband or Gaussian pulse is upconverted to the desired center frequency. This gives good control of the output wavelet characteristics such as the center frequency. A second alternative is to generate a very short baseband pulse that has frequency components in the targeted band [19–21], as illustrated in Fig. 3(b). This pulse is then passed through a filter with the appropriate characteristics to form the high frequency wavelet. Figure 3(c) describes another option, which is to pass a continuously running oscillator signal through a series of switches, which may include gain [14, 22]. High frequency pulses are generated by turning these switches on and off, using the baseband signal to represent the data that is to be transmitted.

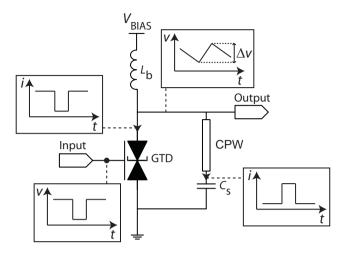

The wavelet generator investigated in this thesis belongs to the group which are illustrated in Fig. 3(d). These wavelet generators operate by using the baseband signal to switch a circuit between an oscillating state and a non-oscillating state. Example of other implementations that fall in the same category are given in reference [23–26].

When comparing the solutions, presented in Fig. 3, it is possible to identify benefits of the implementation illustrated in Fig. 3(d):

- No need for any high frequency upconversion. Designing high frequency mixers that has a high conversion efficiency is a challenging task.

- No need for high frequency band pass filtering, which would add insertion loss or increase the power consumption.

| 6    |                                    |       |             |                     |             |

|------|------------------------------------|-------|-------------|---------------------|-------------|

|      |                                    | $f_0$ | $t_{\rm p}$ | $P_{\mathrm{peak}}$ | $E_{\rm p}$ |

| Туре | Technology                         | (GHz) | (ps)        | (dBm)               | (pJ/pulse)  |

| В    | InP130nm HEMT [19] <sup>1,2</sup>  | 82.5  | 80          | -22                 | 63          |

| С    | SiGe BiCMOS130nm [22] <sup>2</sup> | 60.5  | 350         | 9                   | (150mW)     |

| С    | SiGe BiCMOS130nm [14]              | 90    | 26          | <17.2               | (450mW)     |

| D    | CMOS65nm SOI [23] <sup>1,2</sup>   | 56    | 250         | 5.3                 | 12.6        |

| D    | CMOS65nm SOI [26] <sup>1</sup>     | 60    | 500         | 5                   | 5.0         |

| D    | GaAs Paper II <sup>1</sup>         | 60    | 33          | -13                 | 4.6         |

| D    | InP Paper VIII <sup>1</sup>        | 70    | 41          | 7                   | 1.9         |

Table 2: State of the art mm-wave wavelet generators

<sup>1</sup>Coherent signal. <sup>2</sup>Baseband generator included.

Figure 4: Switchable oscillator circuit.

- No need for high frequency switches. To get enough attenuation of the signal typically several switches are required, each consuming power.

- All the generated energy is synthesized directly at the RF frequency, no energy is lost in filters, mixers or switches. This gives the possibility to realize efficient transmitters.

These benefits are further accentuated in Table 2, which lists state of the art mmwave wavelet generators based on the techniques described in Fig. 3. The benchmarking contains center frequency  $(f_0)$ , wavelet length  $(t_p)$ , wavelet peak output power  $(P_{\text{peak}})$ , and energy consumption per wavelet  $(E_p)$ . Table 2 also indicates if the wavelet generators produce coherent signals, which is required to retain phase information, and if the baseband signal generator is included in  $E_p$ . The wavelet generators considered in this thesis are represented by Paper II and Paper VIII, they compare favorably, especially when a short  $t_p$  is required.

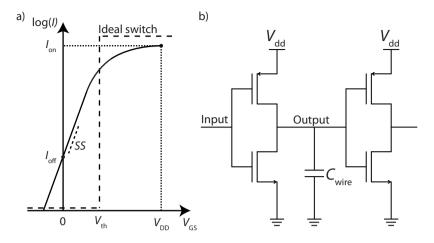

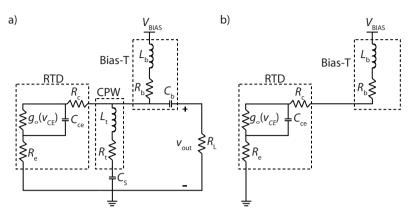

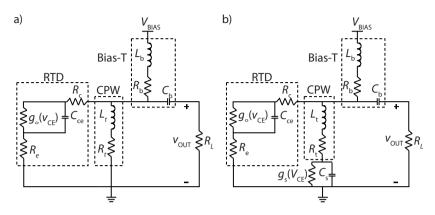

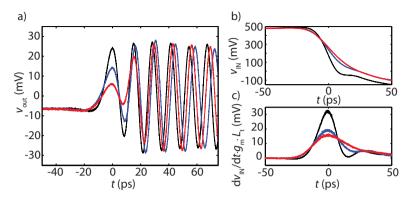

The wavelet generators developed in this work are thoroughly analyzed in Chap-

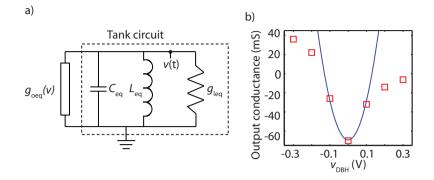

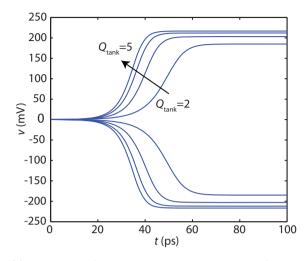

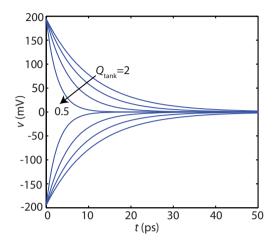

ter 5, a brief introduction to the concept is given here and is illustrated by Fig. 4. The generalized circuit consists of two reactive elements, one inductor (*L*) and one capacitor (*C*), a load given by  $g_{\text{load}}$ , and a variable conductance ( $g_{\text{VDC}}$ ), which may be switched between negative and positive differential conductance. When  $g_{\text{VDC}}$  is switched to negative values such that it compensates for resistive losses in the circuit, i.e.  $g_{\text{VDC}}+g_{\text{load}}<0$ , the circuit will be unstable and oscillations are produced. The frequency of the oscillation is determined by the resonance frequency of the reactive elements, which is given by

$$f_0 = \frac{1}{2\pi\sqrt{LC}}\tag{3}$$

Switching  $g_{VDC}$  to a positive value will add loss to the circuit and the oscillation will decay, hence, the circuit in Fig. 4 has the functionality of the wavelet generator in Fig. 3(d).

This thesis mainly focuses on developing devices with the property of the variable conductance in Fig. 4. These devices are based on the negative differential conductance of a resonant tunneling diode, which is the first topic of the next chapter.

### Chapter 2

#### **The Gated Tunnel Diode**

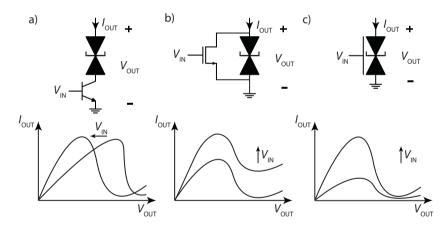

The gated tunnel diode (GTD) considered in this chapter is an example of a variable conductance device that can be used in wavelet generating circuits. It is based on the negative differential conductance (NDC) property of a resonant tunneling diode, which has been utilized in various electronic circuits such as high frequency oscillators [27], low power memory cells [28], and analog to digital converters [29]. In order to make the RTD more flexible as a circuit element it may be combined with a transistor, which provides the possibility to tune the NDC property. Examples are given in [30] where a RTD has been integrated in series with a heterojunction bipolar transistor, and in [31] where the RTD has been integrated in parallel with a field effect transistor.

**Figure 5:** (a) and (b) shows the circuit layout and output characteristics of a series and parallel integration of a transistor and an RTD, respectively. (c) Symbol representing the GTD together with an illustration of its output characteristics.

A schematic layout of these devices and their corresponding output characteristics are shown in Fig. 5(a) and (b). These configurations require performance matching of the transistor and the RTD, and design for additional voltage drop across the transistor. The GTD presented here controls the conducting area of an RTD by an integrated

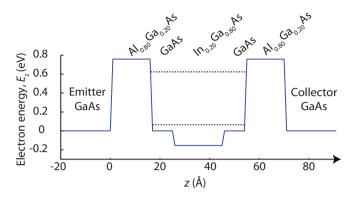

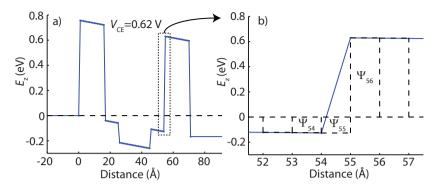

**Figure 6:** Conduction band diagram of the GaAs DBH used in this thesis, the complete epitaxial structure is given in Table 3.

metal gate, which provides the possibility to directly modulate the output conductance, as illustrated in Fig. 5(c).

This chapter describes the basic principle and operation of an RTD, and the fabrication and modeling of the GTD. The GTD is further analyzed in Chapter 5, where the possibility of switching the output conductance between positive and negative values is used to generate wavelets.

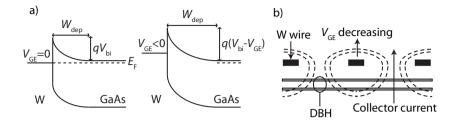

#### 2.1 The resonant tunneling diode

A resonant tunneling diode consists of a double-barrier heterostructure (DBH). The conduction band diagram of the GaAs based DBH that are considered in this thesis is given in Fig. 6. The confinement potential, formed by the conduction band offset between the materials of the DBH, creates quasi-bound states at certain energies  $E_n$ , these are indicated by the dashed lines in Fig. 6. Resonant tunneling from the emitter to the collector through the DBH may occur when the energy of an electron outside the DBH coincide with that of a quasi bound state inside the DBH.

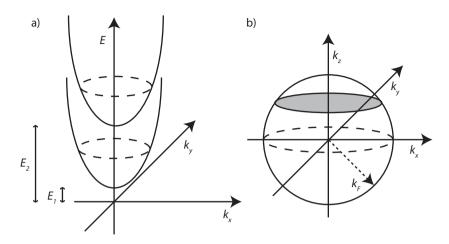

In the simple model considered here the wavefunction of an electron outside the DBH is represented by a plane wave with a crystal momentum vector  $\bar{k}$ , the spatial coordinate vector  $\bar{r}$ , and the amplitude vector A. If a translation invariant DBH is considered it is possible to separate the motion in the x and y plane into plane waves that are independent of the wavefunction in the z direction [32]. This makes it possible to write the wavefunction as

$$\Psi = a \cdot e^{(ik_{\rm x}x)} b \cdot e^{(ik_{\rm y}y)} \phi(z) \tag{4}$$

with the energy

$$E(\bar{k}) = \frac{\hbar^2 (k_{\rm x}^2 + k_{\rm y}^2)}{2m^*} + E_{\rm n}, \ n = 1, 2, 3...$$

(5)

**Figure 7:** (a) Illustration of the available energies inside the potential confinement. (b) The shaded surface represents electronic states available for transmission through the DBH at a certain energy  $E_z$ .  $k_F$  is the Fermi wavenumber corresponding to the Fermi energy.

Here,  $m^*$  is the effective mass of the electron and a and b are the amplitude of the plane waves in the x and y direction, respectively. In this model  $k_x$  and  $k_y$ , which are the lateral crystal momentums, are conserved together with  $E_z$ . This implies that the restriction on the crystal momentum in the z-direction

$$k_{\rm z} = \frac{\sqrt{2m^*E_{\rm n}}}{\hbar},\tag{6}$$

has to be fulfilled in order to have transmission through the DBH. Figure 7(a) shows an illustration of the available energies between the barriers, as a function of  $k_x$  and  $k_y$ . The electronic states that are available for tunneling at  $E_n$  are depicted in Fig. 7(b).

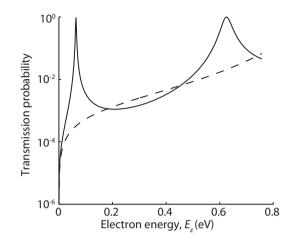

The probability for an electron to be transmitted from the emitter side to the collector side, through the DBH structure in Fig. 6, can be calculated using the transfer matrix approach [33]. Details regarding the calculations are presented in appendix A and the result is shown in Fig. 8, where it is seen that the transmission probability approaches unity for energies corresponding to a resonant state. Off resonance the probability instead approaches that of the tunneling probability through a barrier with a thickness corresponding to the total thickness of the two barriers forming the potential confinement of the DBH. This is represented by the dashed trace in Fig. 8, which was also calculated using the transfer matrix method. Thus, a resonant tunneling structure resembles a Fabry-Perot interferometer where constructive interference leads to a transmission maximum. Here it is the wavefunctions of the tunneling electrons that interfere constructively to give a transmission maximum. A more thorough introduction to the resonant tunneling phenomena may be found in [34], and for a

**Figure 8:** The solid trace shows the result of the calculation of the transmission probability through the DBH given in Fig. 6, the method used is described in more detail in appendix A. The transmission through a 3.2-nm-thick  $Al_{0.8}Ga_{0.2}As$  barrier is illustrated by the dashed line.

deeper understanding of the theory [33] is recommended.

The current density through the DBH may be calculated using the Esaki-Tsu formula:

$$J = \frac{m^* e k_B T_L}{2\pi^2 \hbar^3} \int_0^\infty dE_z T(E_z, V_{\rm DBH}) \ln\left(\frac{1 + e^{(\mu_E - E_z)/k_B T_L}}{1 + e^{(\mu_E - E_z - eV_{\rm DBH})/k_B T_L}}\right)$$

(7)

Here,  $T_{\rm L}$  is the temperature,  $k_{\rm B}$  is the Boltzmann constant,  $V_{\rm DBH}$  is the voltage applied across the DBH, and  $\mu_{\rm E}$  and  $\mu_{\rm C}$  are the chemical potentials at the emitter and collector side, respectively. Equation (7) includes two terms that are integrated with respect to  $E_{\rm z}$ , the first is the transmission probability considered earlier and the second is a function which accounts for the net amount of carriers available for tunneling at a certain  $E_{\rm z}$ . Both these terms are functions of the applied bias  $V_{\rm DBH}$ .

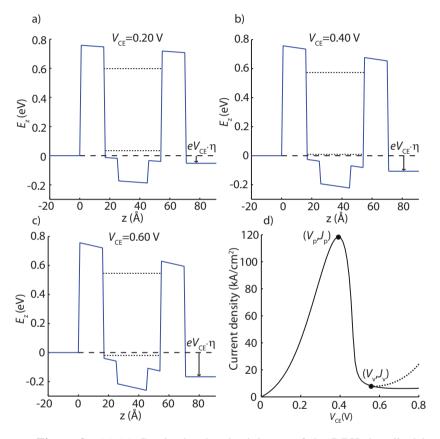

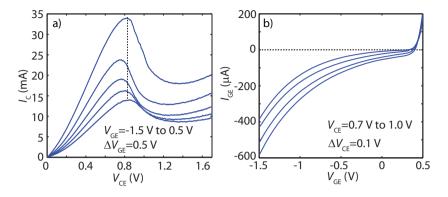

Figure 9 shows the conduction band diagram under different bias conditions and the corresponding current density transmitted through the RTD for the DBH structure defined in Fig. 6. A factor  $\eta$ =0.27 has been used to relate  $V_{\rm DBH}$  to  $V_{\rm CE}$ , which is the voltage drop across the DBH and the adjacent spacer layers. The value of  $\eta$  was estimated from 2D simulations using the software ATLAS by Silvaco. As the bias is increased the energy difference between the resonant level and the conduction band edge on the emitter side is decreased, as depicted in Fig. 9(a). Figure 9(b) illustrates the DBH at  $V_{\rm CE}$ =0.40 V, increasing the bias beyond this point will cause the resonant level to be below the energy of electrons eligible for transmission from the emitter to the collector. This is when the current starts to decrease and the NDC property of the RTD presents itself, as seen in Fig. 9(d).

**Figure 9:** (a)-(c) Conduction band minimum of the DBH described in Fig. 6, the resonant states are indicated by dashed lines. The corresponding current density is shown in (d).

Important metrics of an RTD is the peak current density  $(J_p)$  and peak voltage  $(V_p)$ , which are indicated in Fig. 9(d). The transfer matrix method is useful to predict the peak current density (the experimental value for this structure is  $J_p=120 \text{ kA/cm}^2$ ), but as the solution is not made self-consistent it does not predict  $V_p$  in a good way. Also, the transfer matrix method does not include scattering, which is why the current remains essentially flat as the first resonant level is pulled below the conduction band edge on the emitter side. The dashed trace in Fig. 9(d) illustrates the increase in current experimentally observed, and the definition of the valley current density  $(J_v)$  and the valley voltage  $(V_v)$ .

When designing high speed RTDs several factors needs to be considered and tradeoffs have to be made. The most important parameters used to evaluate RTDs are listed below. These parameters are chosen based on their influence on the performance of high frequency oscillators incorporating RTDs, which will be further discussed in Chapter 5.

- The peak to valley current difference ( $\Delta I = I_{\rm p} I_{\rm v}$ ) and voltage difference ( $\Delta V = V_{\rm v} V_{\rm p}$ ) both need to be large in order to maximize the output power from the RTD. However, the output conductance  $g_{\rm o} \approx \Delta I / \Delta V$  needs to be large enough to compensate for losses in the circuit.

- The output capacitance of the device, C<sub>ce</sub>, should be as small as possible to maximize the oscillation frequency.

- $V_{\rm p}$  should be as small as possible to limit the DC power consumption.

A large  $\Delta I$  requires a large  $J_{\rm p}$ , which is obtained by decreasing the thickness of the DBH barriers to maximize the tunneling current, and by increasing the amount of electrons available for tunneling, i.e. increasing the doping on the emitter side. However, it is important to make sure that  $J_{\rm v}$  is not severely deteriorated as a result of increased scattering due to nonuniformity in the epitaxial layers forming the DBH.

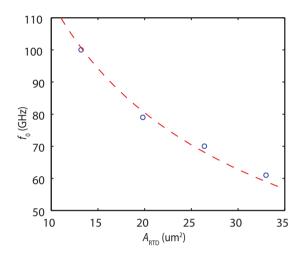

One important trade-off when considering the parameters listed above is that the RTD area  $(A_{\rm RTD})$  should be large to provide high output power, but small to enable a high oscillation frequency. The capacitance per area unit  $(C_{\rm ce}/A_{\rm RTD})$  is minimized by having a thick space charge region (SCR) layer on the collector side of the DBH, but this in turn increases  $V_{\rm p}$ , as there will be an additional voltage drop across the SCR. The In<sub>0.2</sub>Ga<sub>0.8</sub>As notch included in the design of the DBH presented here acts to lower  $V_{\rm p}$ , as the notch lowers the first bound state of the DBH. Several more trade-offs and considerations needs to be taken into account when designing RTDs and a detailed discussion is found in [34].

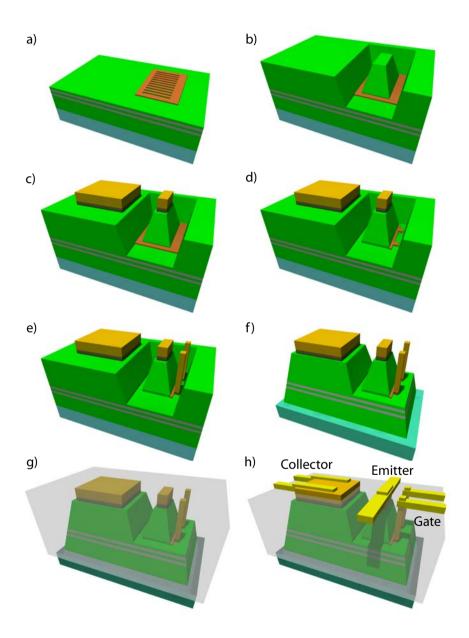

## 2.2 Fabrication of the gated tunnel diode

As mentioned earlier, it is possible to gain additional circuit functionality from an RTD if a third terminal is integrated with the RTD. The gated tunnel diode (GTD) presented in this section is such a device. The device processing is illustrated in Fig. 10

| T             |                                        |               | $D_{1}$ (1 1 ( $-3$ )      |

|---------------|----------------------------------------|---------------|----------------------------|

| Layer         | Material                               | Thickness (Å) | Dopant level (cm $^{-3}$ ) |

| Contact layer | $In_{0.5}Ga_{0.5}As$                   | 300           | $3 \cdot 10^{19}$          |

| Contact layer | $In_xGa_{(1-x)}As^*$                   | 300           | $3 \cdot 10^{19}$          |

| Emitter       | GaAs                                   | 4000          | $2 \cdot 10^{18}$          |

| Tungsten gate |                                        |               |                            |

| Emitter       | GaAs                                   | 100           | $2 \cdot 10^{17}$          |

| Emitter       | GaAs                                   | 200           | $5 \cdot 10^{17}$          |

| Spacer        | GaAs                                   | 50            | $2 \cdot 10^{16}$          |

| Barrier       | $Al_{0.8}Ga_{0.2}As$                   | 16            | $2 \cdot 10^{16}$          |

| Well          | GaAs                                   | 9             | $2 \cdot 10^{16}$          |

| Notch         | In <sub>0.2</sub> Ga <sub>0.8</sub> As | 20            | $2 \cdot 10^{16}$          |

| Well          | GaAs                                   | 9             | $2 \cdot 10^{16}$          |

| Barrier       | Al <sub>0.8</sub> Ga <sub>0.2</sub> As | 16            | $2 \cdot 10^{16}$          |

| Spacer        | GaAs                                   | 50            | $2 \cdot 10^{16}$          |

| SCR           | GaAs                                   | 1000          | $2 \cdot 10^{17}$          |

| Collector     | GaAs                                   | 10000         | 5·10 <sup>18</sup>         |

| 0             | GaAs                                   | Substrate     | S.I.                       |

Table 3: Epitaxial structure

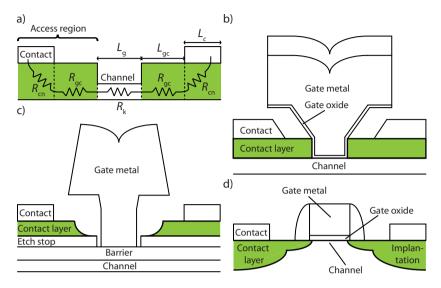

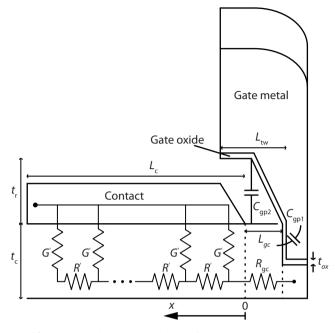

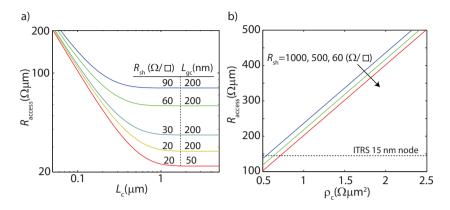

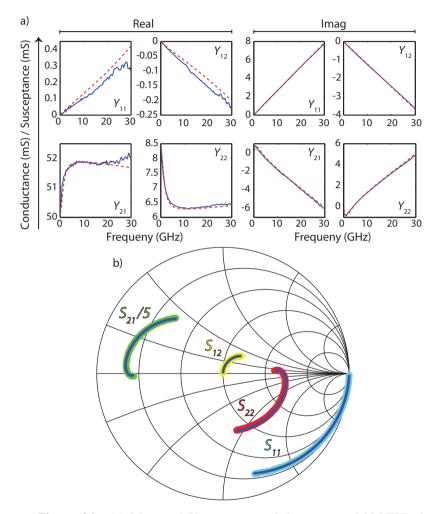

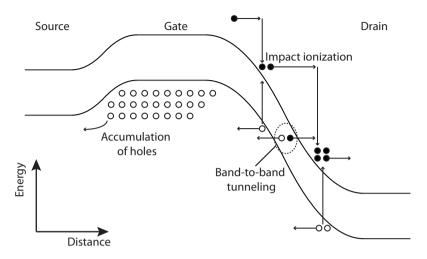

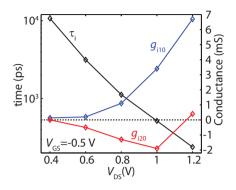

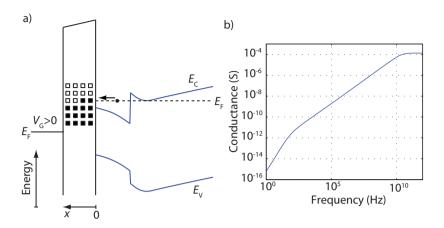

\* $x = 0 \rightarrow 0.5$  linearly graded.