# LUND UNIVERSITY

### Semiconductor Nanowires: Epitaxy and Applications

Mårtensson, Thomas

2008

Link to publication

Citation for published version (APA): Martensson, T. (2008). Semiconductor Nanowires: Epitaxy and Applications. [Doctoral Thesis (compilation), Solid State Physics]. Solid State Physics.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

# Semiconductor Nanowires: Epitaxy and Applications

200.5

### Thomas Mårtensson

Doctoral Thesis

Solid State Physics Faculty of Engineering Lund University

# Semiconductor Nanowires: Epitaxy and Applications

Doctoral Thesis Thomas Mårtensson

> Principal Supervisor: Prof. Lars Samuelson

Faculty opponent: Prof. Chennupati Jagadish, Australian National University, Canberra

### LUND UNIVERSITY

Division of Solid State Physics Department of Physics Sweden 2008

Akademisk avhandling för avläggande av teknologie doktorsexamen vid tekniska fakulteten vid Lunds universitet. Avhandlingen kommer att offentligen försvaras fredagen den 10 oktober 2008 kl. 10.15, hörsal B, Fysiska Institutionen, Sölvegatan 14.

© Thomas Mårtensson 2008

Division of Solid State Physics Department of Physics Lund University P.O. Box 118 SE-221 00 Lund Sweden http://www.nano.lth.se/

This document was produced using  $\mbox{\sc larger} X \, 2_{\mbox{\sc c}}$  Printed in Sweden by Media-Tryck, Lund, September 2008

ISBN 978-91-628-7572-5

Life is too important to be taken seriously. — Oscar Wilde iv

# Abstract

Semiconductor nanowires are nanoscale objects formed by bottom-up synthesis. In recent years their unique properties have been exploited in fields such as electronics, photonics, sensors and the life sciences.

In this work, the epitaxial growth of nanowires and their applications were studied. Metal-organic vapour phase epitaxy was used for nanowire growth, and both particle-assisted and particle-free nanowire growth were employed.

The first specific contribution of this work to nanowire synthesis is heteroepitaxial growth of III-V nanowires on silicon substrates. This may enable direct band gap materials for optoelectronic devices, as well as high-mobility, low-contact resistance materials for electronics, to be integrated directly on the Si platform. Furthermore, gold-free nanowire synthesis on Si was demonstrated, which offers an advantage in terms of compatibility with established Si processing.

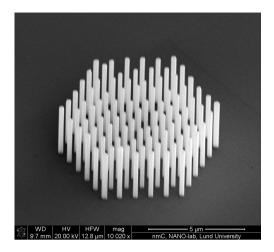

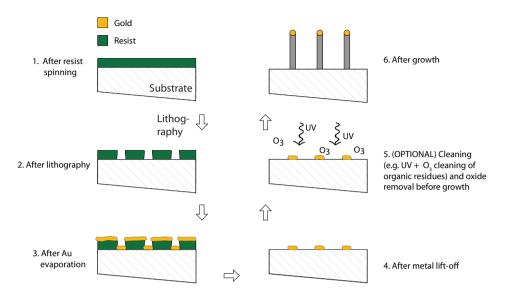

The second specific contribution to nanowire growth is controlled synthesis by employing lithography. This combination of established "top-down" planar processing, and "bottom-up" nanowire growth, enables deterministic synthesis with individual nanowire site control. The process was first demonstrated with electron beam lithography and later extended to nanoimprint lithography, which is a parallel, high-throughput method, suitable for commercial volumes.

Nanowire applications were demonstrated by three examples:

(i) Vertical light-emitting diodes (LEDs) based on GaAs/InGaP core/shell nanowires, epitaxially grown on GaP and Si substrates. LED functionality was established on both kinds of substrates, and the devices were evaluated in terms of temperature-dependent photoluminescence and electroluminescence. This provided a direct demonstration of light-emitting devices on Si made possible by heteroepitaxial III-V nanowire growth on Si.

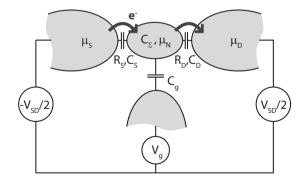

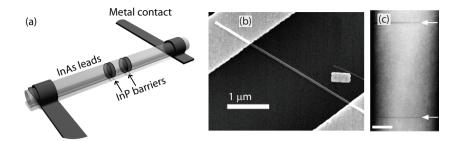

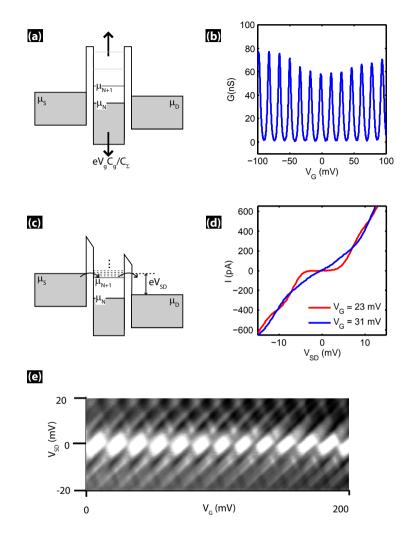

(*ii*) A single-electron transistor constructed from a heterostructured nanowire with an InAs island sandwiched between two InP barriers. The narrow diameter of the nanowire provides the lateral confinement, and the tunnel barrier resistances are tunable by varying the InP barrier thickness. The island was  $\approx 100$  nm long with a diameter of  $\approx 55$  nm. Coulomb oscillations and Coulomb blockade with a charging energy of approximately 4 meV were observed.

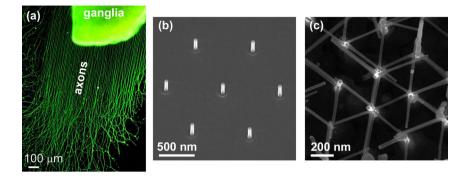

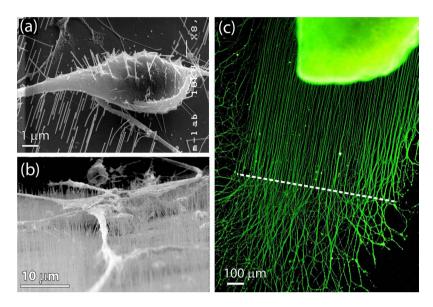

(*iii*) Sensory nerve cell interactions with nanowires. Substrates covered with 2.5  $\mu$ m long and 50 nm diameter nanowires supported cell adhesion and axonal outgrowth. The cells interacted closely with the nanostructures, and viable cells penetrated by wires were observed, as well as wire bending due to forces exerted by the cells.

# Preface

This thesis is the result of postgraduate studies at the Department of Physics at Lund University during the period 2003 - 2008. I joined the division of Solid State Physics just after some pioneering work had been done on nanowire growth and nanowire heterostructures. Thus, although I was not among the very first, I still had the privilege to join a leading group early in a in a rapidly expanding field, namely semiconductor nanowires. I have also been privileged to have taken part in some of the first efforts to commercialize nanowire technology. This has been both sobering, as I realised the tremendous amount of work between a scientific discovery and a final product, as well as highly inspiring, as I was able to to see what a focused team can achieve.

The main topic of the thesis is epitaxy. Epitaxy is difficult, and although I and my fellow workers always set up well-thought-out experiments, the results were a mixture of success and (often) total failure. Perhaps this only reflects the beauty of the subject; we try to gain knowledge in order to control and predict, but we are constantly surprised by nature and forced to revise our views.

The second topic of the thesis is nanowire applications. This combination of applications and epitaxy has been thrilling, and it has been important for me to "see the big picture" and to be interdisciplinary. In this sense, nanowires and nanotechnology have been a way of satiating my curiosity in physics.

It is my hope that this work has made a small contribution to the field (there is much left to do indeed). In any event, I enjoyed doing it.

THOMAS MÅRTENSSON Lund, August 2008 viii

# Acknowledgements

Conducting research for a doctorate is a fairly lengthy process, and you quickly come to realise that you can achieve very little alone. Teamwork is crucial, and over the years you become indebted to many people. These people are far to many to be listed here, and I can only say — thank you all. Nonetheless, I would like to give my special thanks to a few people.

First, I would like to thank my supervisors, Prof. Lars Samuelson, Prof. emeritus Werner Seifert, Dr. Jonas Ohlsson and Dr. Anders Mikkelsen. Lars Samuelson has been my principal supervisor and a never-ending source of inspiration and scientific ideas. From the very first day he treated me as an equal. At times, it created great stress to reach those standards, but in the end helped me develop tremendously. Werner Seifert taught me epitaxy, and for the first three years, he was an almost daily source of knowledge, practical know-how, valuable discussions and humour. He was also the head of the epitaxy group, and I and many others benefited from his leadership and long experience in epitaxy. Jonas Ohlsson was my Master's dissertation advisor and has continued to play a central role as supervisor and, for the last two years, as a colleague during my industrial endeavours at QuNano AB. Apart from his scientific contribution, I would also like to thank him for being a person of great humanity and passion. Anders Mikkelsen was my supervisor during the later half of my studies. Surface science became a major part of my studies and his contribution was crucial. In the busy world of academia, I admire his ability to always find time for me; I am indebted to him for much good advice and valuable discussions. (Hongqi Xu, I never got around to doing that photonic crystal. If I had, I am confident that I would have enjoyed great support and supervision from you.)

Before I leave my supervisors, I would also like to extend my gratitude the senior PhD students who acted as mentors when I began my PhD studies. Among those I count Ann Persson, Magnus Borgström, Claes Thelander and Mikael Björk.

Most of my time was spent in the lab doing epitaxy, and without the help of talented and friendly colleagues, things would have taken twice the time (or not have been possible at all), and would only have been half as fun. Among the people I collaborated with in the epitaxy lab are Kimberly Dick Thelander, Philippe Caroff, Niklas Sköld, Brent Wacaser, Linus Fröberg, Patrik Svensson, Bernhard Mandl, Vilma Zela, Jonas Johansson and Prof. Knut Deppert. Being part of this group is what really made this thesis possible. Martin Karlsson and Zsolt Geretovszky are acknowledged for producing the aerosol particles I needed for nanowire growth.

To become really interesting, epitaxy usually has to be married with other disciplines, such as advanced characterization, processing, device design or physics. I had the benefit of collaborating with skilled people: Patric Carlberg is acknowledged for performing the nanoimprint lithography as well as for a enjoyable and fruitful cooperation, Johanna Trägårdh and Christina Larsson are acknowledged for their optical measurements, and Emelie Hilner is acknowledged for her work in scanning tunnelling microscopy. High-quality transmission electron microscopy is hard to come by, and Anders Gustafsson, Magnus Larsson and Jakob Wagner are acknowledged for their work.

I would like to thank Carl Rehnstedt, Claes Thelander and Prof. Lars-Erik Wernersson for allowing me to take (a small) part in the nanowire field effect transistor project.

I also made a short excursion into the bioworld during my studies, and Waldemar Hällström and Christelle Prinz are acknowledged for a good collaboration as well as for teaching me virtually all I know about cells (which is still fairly limited).

I also enjoyed cooperation with other universities, and especially Kristian Mølhave and Christian Kallesøe from the Technical University of Denmark (DTU), and Jiming Bao from Harvad University, are acknowledged for their collaboration.

The technical staff is the backbone of any lab, and I would like to express my gratitude to them. Especially, Ivan Maximov, Lena Timby and Mariusz Graczyk are acknowledged for their direct contributions to this work. I would also like to thank my roommate Sören Jeppesen for technical support, and for many interesting conversations about science and the workings of the world.

I would like to express my gratitude to all the people at QuNano AB, where I have worked part-time during the final two years of my studies, with the aim of commercializing nanowire technology. It has been an interesting ride and it is my hope that it will continue to be so. My special thanks go to my colleagues in the epi-team: Zhaoxia Bi, Patrik Svensson, Giuliano Vescovi and Rafal Ciechonski.

Claes Thelander, Waldemar Hällström, Christelle Prinz, Jonas Johansson, Philippe Caroff and Sören Jeppesen are acknowledged for their critical remarks on the thesis manuscript.

I would like to thank my parents and brother for their continuous support for whatever I have undertaken in life so far. You have always been a strong foundation. Finally, I would like to thank my love Hanna for her endless support and love during this time. You are my role model.

xii

## List of Papers

This thesis is based on the following papers, which will be referred to in the text by their Roman numerals. The papers, together with short summaries and accounts of the author's contributions, are appended at the end of the thesis.

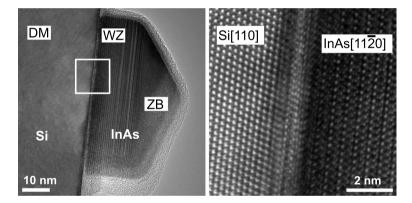

- I. Epitaxial III-V nanowires on silicon T. Mårtensson, C. P. T. Svensson, B. A. Wacaser, M. W. Larsson, W. Seifert, K. Deppert, A. Gustafsson, L. R. Wallenberg and L. Samuelson Nano Letters 4, 1987-1990 (2004) doi:10.1021/n10487267

- II. Epitaxial growth of indium arsenide nanowires on silicon using nucleation templates formed by self-assembled organic coatings T. Mårtensson, J. B. Wagner, E. Hilner, A. Mikkelsen, C. Thelander, J. Stangl, B. J. Ohlsson, A. Gustafsson, E. Lundgren, L. Samuelson and W. Seifert Advanced Materials 19, 1801-1806 (2007) doi:10.1002/adma.200700285

- III. Fabrication of individually seeded nanowire arrays by vapour-liquid-solid growth T. Mårtensson, M. Borgström, W. Seifert, B. J. Ohlsson and L. Samuelson Nanotechnology 14, 1255-1258 (2003) doi:10.1088/0957-4484/14/12/004

- IV. Nanowire arrays defined by nanoimprint lithography T. Mårtensson, P. Carlberg, M. Borgström, L. Montelius, W. Seifert and L. Samuelson Nano Letters 4, 699-702 (2004) doi:10.1021/nl035100s

### V. Monolithic GaAs/InGaP nanowire light emitting diodes on silicon C. P. T. Svensson, T. Mårtensson, J. Trägårdh, C. Larsson, M. Rask, D. Hessman, L. Samuelson and J. Ohlsson Nanotechnology 19, 305201 (2008) 10.1088/0957-4484/19/30/305201 VI. Single-electron transistors in heterostructure nanowires C. Thelander, T. Mårtensson, M. T. Björk, B. J. Ohlsson, M. W. Larsson, L. R. Wallenberg and L. Samuelson Applied Physics Letters 83, 2052-2054 (2003) doi:10.1063/1.1606889 VII. Gallium phosphide nanowires as a substrate for cultured neurons

W. Hällström, T. Mårtensson, C. Prinz, P. Gustavsson, L. Montelius,

L. Samuelson and M. Kanje

Nano Letters 7, 2960-2965 (2007) doi:10.1021/nl070728e

### Papers Not Included in this Thesis

I contributed to the following papers which are not included due to overlapping contents, or because they are beyond the scope of this thesis. They are listed in chronological order.

viii.

# Synthesis of branched 'nanotrees' by controlled seeding of multiple branching events

K. A. Dick, K. Deppert, M. W. Larsson, T. Mårtensson, W. Seifert, L. R. Wallenberg and L. Samuelson Nature Materials **3**, 380-384 (2004) doi:10.1038/nmat1133

ix.

## Growth of GaP nanotree structures by sequential seeding of 1D nanowires

K. A. Dick, K. Deppert, T. Mårtensson, W. Seifert and L. Samuelson Journal of Crystal Growth **272**, 131-137 (2004) doi:10.1016/j.jcrysgro.2004.09.004

$\operatorname{xiv}$

#### x.

#### Semiconductor nanowires for 0D and 1D physics and applications

L. Samuelson, C. Thelander, M. T. Björk, M. Borgström, K. Deppert, K. A. Dick, A. E. Hansen, T. Mårtensson, N. Panev, A. I. Persson, W. Seifert, N. Sköld, M. W. Larsson and L. R. Wallenberg Physica E 25, 313-318 (2004) doi:10.1016/j.physe.2004.06.030

#### xi.

#### Growth of one-dimensional nanostructures in MOVPE

W. Seifert, M. Borgström, K. Deppert, K. A. Dick, J. Johansson,

M. W. Larsson, T. Mårtensson, N. Sköld, C. P. T. Svensson, B. A. Wacaser,

L. R. Wallenberg and L. Samuelson

Journal of Crystal Growth 272, 211-220 (2004)

doi:10.1016/j.jcrysgro.2004.09.023

#### xii.

## Failure of the vapor-liquid-solid mechanism in Au-assisted MOVPE growth of InAs nanowires

K. A. Dick, K. Deppert, T. Mårtensson, B. Mandl, L. Samuelson and W. Seifert Nano Letters 5, 761-764 (2005) doi:10.1021/nl050301c

#### xiii.

#### Mass transport model for semiconductor nanowire growth

J. Johansson, C. P. T. Svensson, T. Mårtensson, L. Samuelson and W. Seifert Journal of Physical Chemistry B 109, 13567-13571 (2005) doi:10.1021/jp051702j

#### xiv.

#### Structural properties of (111)B-oriented III-V nanowires

J. Johansson, L. S. Karlsson, C. P. T. Svensson, T. Mårtensson, B. A. Wacaser, K. Deppert, L. Samuelson and W. Seifert Nature Materials 5, 574-580 (2006) doi:10.1038/nmat1677

#### xv.

#### Au-free epitaxial growth of InAs nanowires

B. Mandl, J. Stangl, T. Mårtensson, A. Mikkelsen, J. Eriksson, L. S. Karlsson,

G. Bauer, L. Samuelson and W. Seifert

Nano Letters 6, 1817-1821 (2006) doi:10.1021/n1060452v

#### xvi.

Strain and shape of epitaxial InAs/InP nanowire superlattice measured by grazing incidence X-ray techniques J. Eymery, F. Rieutord, V. Favre-Nicolin, O. Robach, Y. M. Niquet, L. Fröberg, T. Mårtensson and L. Samuelson Nano Letters 7, 2596-2601 (2007) doi:10.1021/n1070888q

#### xvii.

The structure of <111>B oriented GaP nanowires. J. Johansson, L. S. Karlsson, C. P. T. Svensson, T. Mårtensson, B. A. Wacaser, K. Deppert and L. Samuelson Journal of Crystal Growth **298**, 635-639 (2007) doi:10.1016/j.jcrysgro.2006.10.175

#### xviii.

# Optical properties of rotationally twinned InP nanowire heterostructures

J. M. Bao, D. C. Bell, F. Capasso, J. B. Wagner, T. Mårtensson, J. Trägårdh and L. Samuelson Nano Letters 8, 836-841 (2008) doi:10.1021/n1072921e

#### xix.

#### Selective etching of III-V nanowires for molecular junctions

C. Kallesøe, K. Mølhave, T. Mårtensson, T. M. Hansen, L. Samuelson and P. Bøggild Microelectronic Engineering **85**, 1179-1181 (2008) doi:10.1016/j.mee.2007.12.023

xx.

# Surface-enhanced Raman scattering of rhodamine 6G on nanowire arrays decorated with gold nanoparticles

J. Chen, T. Mårtensson, K. A. Dick, K. Deppert, H. Q. Xu, L. Samuelson and H. Xu

Nanotechnology 19, 275712 (2008) doi:10.1088/0957-4484/19/27/275712

#### xxi.

#### Axonal guidance on patterned free-standing nanowire surfaces C. Prinz, W. Hällström, T. Mårtensson, L. Samuelson, L. Montelius and M. Kanje Nanotechnology **19**, 345101 (2008) doi:10.1088/0957-4484/19/34/345101

xvi

#### xxii.

#### Vertical InAs nanowire wrap gate transistors on Si substrates

C. Rehnstedt, T. Mårtensson, C. Thelander, L. Samuelson and L. Wernersson accepted for publication in IEEE Transactions on Electron Devices (2008)

#### xxiii.

#### Development of a vertical wrap-gated InAs FET

C. Thelander, C. Rehnstedt, L. E. Fröberg, E. Lind, T. Mårtensson, P. Caroff, T. Löwgren, B. J. Ohlsson, L. Samuelson and L. Wernersson accepted for publication in IEEE Transactions on Electron Devices (2008)

#### xxiv.

Fabrication of nanogaps using heterostructure III-V-nanowires C. Kallesøe, K. Mølhave, T. Mårtensson, M. Borgström, T. M. Hansen, L. Samuelson and P. Bøggild submitted to Nanotechnology

### **Patent Applications**

The following patent applications were made in combination with the above publications.

Precisely positioned nanowhiskers and nanowhisker arrays and method for preparing them

L. I. Samuelson, B. J. Ohlsson and T. M. I. Mårtensson US2005011431 (2005)

Formation of nanowhiskers on a substrate of dissimilar material

L. I. Samuelson and T. M. I. Mårtensson WO2006000790 (2006)

Method for metal-free synthesis of epitaxial semiconductor nanowires on Si

L. Samuelson, T. Mårtensson, W. Seifert, B. Mandl and A. Mikkelsen PCT SE2007/050131 (2007)

**Title not yet made public** L. Samuelson, T. Mårtensson and J. Ohlsson SE 0702402-9 (2007) xviii

## Abbreviations and Symbols

| 1D, 2D, 3D            | one-, two-, three-dimensional                               |  |  |  |

|-----------------------|-------------------------------------------------------------|--|--|--|

| a                     | lattice constant                                            |  |  |  |

| AFM                   | atomic force microscopy                                     |  |  |  |

| APD                   | anti-phase domain                                           |  |  |  |

| CMOS                  | complementary metal oxide semiconductor                     |  |  |  |

| EBL                   | electron beam lithography                                   |  |  |  |

| $E_a$                 | activation energy                                           |  |  |  |

| $E_F^{u}$             | Fermi energy                                                |  |  |  |

| $E_q$                 | energy band gap                                             |  |  |  |

| -g EL                 | electroluminescence                                         |  |  |  |

| fcc                   | face-centred cubic                                          |  |  |  |

| FET                   | field-effect transistor                                     |  |  |  |

| hcp                   | hexagonal close-packed                                      |  |  |  |

| III-V                 | compound comprised of one group-III element and             |  |  |  |

|                       | one group V-element of the periodic system                  |  |  |  |

| LED                   | light-emitting diode                                        |  |  |  |

| LOR                   | lift-off resist                                             |  |  |  |

| MOVPE                 | metal-organic vapour phase epitaxy                          |  |  |  |

| MBE                   | molecular beam epitaxy                                      |  |  |  |

| NIL                   | nanoimprint lithography                                     |  |  |  |

| NW                    | nanowire                                                    |  |  |  |

| PL                    | photoluminescence                                           |  |  |  |

| PMMA                  | poly(methyl methacrylate)                                   |  |  |  |

| SAE                   | selective-area epitaxy                                      |  |  |  |

| SEM                   | scanning electron microscopy                                |  |  |  |

| SET                   | single-electron transistor                                  |  |  |  |

| STM                   | scanning tunnelling microscopy                              |  |  |  |

| TEM                   | transmission electron microscopy                            |  |  |  |

| TMGa                  | trimethyl gallium                                           |  |  |  |

| TMIn                  | trimethyl indium                                            |  |  |  |

| $\mu$                 | chemical potential                                          |  |  |  |

| $\Delta \mu$          | supersaturation                                             |  |  |  |

| $\Xi_{\mu}$ UHV       | ultrahigh vacuum                                            |  |  |  |

| VLS                   | vapour-liquid-solid                                         |  |  |  |

| (hkl)                 | Miller index notation for                                   |  |  |  |

| (1000)                | a specific plane, e.g., $(1\overline{1}0)$                  |  |  |  |

| $\{hkl\}$             | a family of equivalent planes, e.g., $\{1\overline{10}\}$   |  |  |  |

| [hkl]                 | a specific direction, e.g., $[1\overline{10}]$              |  |  |  |

| $\langle hkl \rangle$ | a family of equivalent directions, e.g., $<1\overline{1}0>$ |  |  |  |

| <1000 ×               | a family of equivalent differious, e.g., <110>              |  |  |  |

# Contents

| 1 | Intr                 | roduction                                                            | 1  |  |  |  |  |  |

|---|----------------------|----------------------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1                  | Materials Science                                                    | 1  |  |  |  |  |  |

|   | 1.2                  | Semiconductors                                                       | 1  |  |  |  |  |  |

|   | 1.3                  | Nanotechnology                                                       | 3  |  |  |  |  |  |

|   |                      | 1.3.1 Nanowires                                                      | 3  |  |  |  |  |  |

|   | 1.4                  | Thesis Outline                                                       | 4  |  |  |  |  |  |

| 2 | Epitaxy and Crystals |                                                                      |    |  |  |  |  |  |

|   | 2.1                  | Thermodynamics of Crystal Growth                                     | 5  |  |  |  |  |  |

|   | 2.2                  | Crystal Structures                                                   | 6  |  |  |  |  |  |

|   | 2.3                  | Atomistic View of Epitaxy                                            | 9  |  |  |  |  |  |

|   | 2.4                  | MOVPE                                                                | 10 |  |  |  |  |  |

| 3 | Nar                  | nowire Epitaxy                                                       | 13 |  |  |  |  |  |

|   | 3.1                  | Particle-Assisted Growth                                             | 14 |  |  |  |  |  |

|   | 3.2                  | Particle-Free Growth                                                 | 17 |  |  |  |  |  |

|   | 3.3                  | Heterostructures                                                     | 19 |  |  |  |  |  |

|   | 3.4                  | Comparison of Particle-Assisted and Particle-Free Growth             | 20 |  |  |  |  |  |

| 4 | III-                 | V Nanowires Integrated on Silicon                                    | 23 |  |  |  |  |  |

|   | 4.1                  | Planar Growth of III-Vs on Si                                        | 24 |  |  |  |  |  |

|   | 4.2                  | Nanowire Growth of III-Vs on Si                                      | 26 |  |  |  |  |  |

|   |                      | 4.2.1 The Si(111) Surface                                            | 27 |  |  |  |  |  |

|   |                      | 4.2.2 Particle-Assisted Growth of GaAs/InGaP Nanowires on Si .       | 28 |  |  |  |  |  |

|   |                      | 4.2.3 Particle-Free Growth of InAs Nanowires on Si                   | 30 |  |  |  |  |  |

|   |                      | 4.2.4 Electrical Properties of the Si/III-V Heterointerface $\ldots$ | 32 |  |  |  |  |  |

| 5 | Litł                 | nographically Aided Formation of Nanowires                           | 35 |  |  |  |  |  |

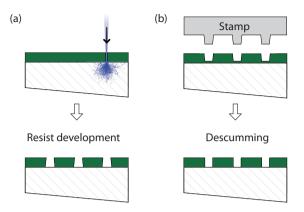

|   | 5.1                  | Site Control of Seed Particles using Lithography                     | 36 |  |  |  |  |  |

|   |                      | 5.1.1 Electron Beam Lithography                                      | 37 |  |  |  |  |  |

|   |                      | 5.1.2 Nanoimprint Lithography                                        | 39 |  |  |  |  |  |

|   | 5.2                  | Nanowire Growth from Lithographic Gold Patterns                      |    |  |  |  |  |  |

| 6                                        | Nanowires in Photonics, Electronics and Life Sciences |       |                                                |    |  |

|------------------------------------------|-------------------------------------------------------|-------|------------------------------------------------|----|--|

|                                          | 6.1                                                   | Nanow | vire Light-Emitting Diodes                     | 46 |  |

|                                          |                                                       | 6.1.1 | LED principles                                 | 47 |  |

|                                          |                                                       | 6.1.2 | Nanowire LEDs                                  | 47 |  |

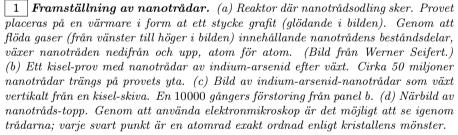

|                                          |                                                       | 6.1.3 | Monolithic GaAs/InGaP Nanowire LEDs on silicon | 48 |  |

|                                          |                                                       | 6.1.4 | Outlook — Nitride Nanowire LEDs                | 51 |  |

| 6.2 Nanowire Single-Electron Transistors |                                                       |       |                                                |    |  |

|                                          |                                                       | 6.2.1 | Energy Structure and Charge Transport in a SET | 54 |  |

|                                          |                                                       | 6.2.2 | Nanowire Heterostructure SET                   | 56 |  |

|                                          | 6.3                                                   | Nanow | vires as a Biological Interface                | 59 |  |

| 7                                        | Out                                                   | look  |                                                | 63 |  |

| Re                                       | efere                                                 | nces  |                                                | 65 |  |

| Po                                       | Populärvetenskaplig Sammanfattning                    |       |                                                |    |  |

## Chapter 1

# Introduction

This thesis describes the subject of nanowires, which is highly multidisciplinary. Below an introduction to the principal concepts of this thesis is given. A thesis outline is provided at the end of this chapter.

### 1.1 Materials Science

Materials science has been at the core of many of the technological breakthroughs made by man. Metal working, for example, was considered so important that it was used to describe periods in history (the Bronze Age and the Iron Age), while steel was an important part of the industrial revolution. In the 20<sup>th</sup> century, the invention and development of semiconductor technology enabled the information technology revolution. Computers, the internet, and mobile phones are now integral parts of daily life.

Today we face new challenges, not least environmental challenges. Efficient and inexpensive materials for clean "combustion" by fuel cells, energy production by solar cells (photovoltaics) and solid state lighting (LEDs) for energy-saving illumination, need to be developed. Just as semiconductors play a central role in computer technology, they are also used for the last two applications, photovoltaics and LEDs. Semiconductor nanostructures are also the materials used in the current work.

### 1.2 Semiconductors

In Figure 1.1 the elements of the most commonly used semiconductors are shown. Silicon is the most important semiconductor material and is found in nearly all

electronics.

|    |    | IV | V  | VI | _ |

|----|----|----|----|----|---|

|    | В  | С  | Ν  | 0  |   |

| Ш  | AI | Si | Ρ  | S  |   |

| Zn | Ga | Ge | As | Se |   |

| Cd | In | Sn | Sb | Те |   |

|    |    |    |    |    |   |

Figure 1.1: Part of the periodic system showing the elements of the III-V and group IV semiconductors. Si and Ge are single-element semiconductors, whereas the III-Vs are binary materials, for example, GaAs and InP.

A semiconductor exhibits a *band gap*, which is an energy interval in which no electron states are allowed. In a semiconductor the states below the gap are fully occupied by electrons, and the states above the gap are empty. Since completely filled bands (or empty bands) carry no net current, these materials are insulators at absolute zero [1]. However, at room temperature these materials have a finite conductance that can be controlled by introducing impurity atoms (doping) and applying electrical fields. The ability to "tune" a material between a conducting-and a non-conducting state forms the basis of a transistor, from which computer logic is constructed. In a semiconductor transistor, doping is introduced during fabrication, and electrical fields are then applied during operation to control the conductance. The so called complimentary metal oxide semiconductor (CMOS) technology is the core of current computer technology.

The so-called III-V semiconductors are compound materials composed of elements from groups III and V of the periodic system (Fig. 1.1), for example, GaAs and InP. These are more expensive than Si, and the degree of perfection of the material is lower. However, these materials have functionality that Si does not posses. The most important difference is perhaps that most of them exhibit a so-called *direct band gap*, meaning that electrons can relax to lower energy states (recombine with holes) with conserved momentum and emit light (photons) in the process. Thus, III-Vs are used in light-emitting applications such as LEDs and lasers.

### 1.3 Nanotechnology

In recent years, nanotechnology<sup>1</sup> has emerged as a subdiscipline to materials science, or in many cases a discipline of its own. In nanotechnology matter is controlled on the atomic and molecular scale to fabricate features or devices with at least one dimension smaller than 100 nanometres. A central theme in nanotechnology is the so called "bottom-up" [4] approach, meaning that nanostructures are constructed by adding atoms in a controlled way, rather than removing material from a larger piece of starting material, as is done in the so-called "top-down" approach, which currently dominates in industry.

When dimensions shrink to nanoscale dimensions the material properties may change drastically: melting points are depressed [5], magnetic materials may undergo a phase transition from ferromagnetic to superparamagnetic, materials with an indirect band gap in the bulk may change to a direct band gap [6], otherwise inert metals can become highly catalytically active [7], and quantum confinement effects appear [8]. These effects provide new opportunities, as well as challenges.

Today, nanotechnology is a major scientific field with numerous sub-fields. Semiconductor nanostructures comprise a large class of objects, including, for example, quantum dots, carbon nanotubes, nanoribbons and nanowires. The last structure is studied in this work.

#### 1.3.1 Nanowires

Semiconductor nanowires (NWs) have a diameter < 100 nm, whereas the axis is considerably longer, typically in the  $\mu m$  range. The interest in NWs emanates from their, in many regards, unique properties. In recent years substantial effort has been devoted to understanding their synthesis, and electrical and optical and mechanical properties, and how these properties can be exploited in fields such as electronics, photonics, sensing applications and life sciences. A few examples are given here. (Optoelectronics) 1D heterostructures can be used to form quantum dots embedded in the NW which function as single-photon sources [9]. NWs can act as laser cavities [10]. Important optical materials, which are difficult to synthesize in their bulk forms without defects, can be fabricated as perfect crystals in the form of NWs, for example, GaN and AlGaN [11]. A further opportunity is the integration of light-emitting materials on Si, as studied in this work in Papers I and V. *(Electronics)* NWs provide an ideal geometry for field-effect transistors (FETs) with a wrap-gate around the NW active channel [12]. Singleelectron transistors (Paper VI) and multiple tunnel junction memories [13] have been realized in NWs employing heterostructure technology. NWs may act as 3D interconnects and form networks with new functionality for future generations of

<sup>&</sup>lt;sup>1</sup>see e.g. refs [2, 3] for a popular introduction to nanotechnology

ultra-dense electronics [14]. (*Chemical sensors*) The large surface to volume ratio of NWs makes them suitable for chemical sensing applications with ultra-high sensitivity [15]. An overview of NW synthesis, properties and devices was recently given in *Functional Nanowires*, MRS Bulletin [16].

### 1.4 Thesis Outline

This thesis is organized in seven chapters, which provide background and further discuss the findings of the published papers.

A introduction to epitaxial growth of NWs is provided in Chapters 2 and 3; the general concepts of crystal structures and crystal growth are introduced in Chapter 2 and described in terms of NW growth in Chapter 3.

Chapters 4 and 5 describe the specific contributions made to NW growth in this work: III-V NWs integrated on Si substrates, and site-controlled NW growth.

Chapter 6 describes three examples of NW applications. These were made possible partly by the developments in NW growth described in the previous chapters.

Chapter 7 provides a brief outlook of the field.

The thesis is written in English, but a popular summary, "Populärvetenskaplig sammanfattning", is provided in Swedish at the end.

### Chapter 2

# **Epitaxy and Crystals**

This chapter provides the background for Chapters 2-5 and starts by introducing the thermodynamics of crystal growth. The structures of crystals are also discussed. The atomistic view of epitaxy and the technique of metal-organic vapour phase epitaxy (MOVPE) are then described.

### 2.1 Thermodynamics of Crystal Growth

The first question is: When is crystal growth energetically possible? A crystal is always in contact with its environment, for example a gas, with which it interacts. At constant pressure and temperature, a system strives to attain minimum Gibbs free energy, G [17]. The energy required to add  $\Delta n$  particles to a system at constant pressure p and constant temperature T is the *chemical potential*,

$$\mu = \left(\frac{\partial G}{\partial n}\right)_{p,T} \tag{2.1}$$

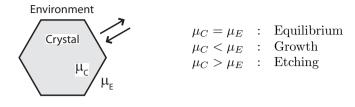

Depending on the chemical potentials of the crystal and its environment, the crystal will either be (i) etched, (ii) in equilibrium with its environment, or (iii) growing (Fig. 2.1). Thus, the difference in chemical potential between two phases, called the *supersaturation*

$$\Delta \mu_{AC} = \mu_E - \mu_C \tag{2.2}$$

is an important quantity. The subscripts E and C denote Environment and Crystal, respectively. For example,

Figure 2.1: Crystal–environment interactions. Depending on the chemical potentials of the different phases, the crystal will either be in equilibrium with its environment, etched, or growing. Figure adapted from reference [21].

the supersaturation for a single-component crystal in contact with an ideal gas of the same component is given by:

$$\Delta \mu = RT \ln \left(\frac{P}{P_0}\right) \tag{2.3}$$

where R is the universal gas constant, P is the pressure of the gas phase, and  $P_0$ is the crystal vapour pressure at the given temperature [18]. Equation 2.3 applies, for example, to molecular beam epitaxy (MBE) growth of Si. It is seen that if the temperature is increased while maintaining the same equivalent beam pressure P, at some point, the growth rate becomes zero, and ultimately becomes negative (the crystal evaporates). The reason is that  $P_0$  increases exponentially with temperature, and  $\Delta\mu$  goes through the sequence  $P_0 < P \Rightarrow \Delta\mu > 0$ : crystal growth,  $P_0 = P \Rightarrow \Delta\mu = 0$ : cessation of crystal growth,  $P_0 > P \Rightarrow \Delta\mu < 0$ : evaporation of the crystal (etching). The supersaturation also controls more complex growth behaviour such as the crystalline structure of NWs [19, 20]. The supersaturation is, however, difficult to calculate for many complex systems (such as III-V NWs grown by MOVPE) and is often used conceptually rather that calculated quantitatively.

Besides thermodynamics, an atomistic view of the crystal and its kinetic processes is required for a full understanding of crystal growth.

### 2.2 Crystal Structures

A crystal exhibits long-range ordering of the material. Well-known examples of crystals are diamonds and rock salt, but most metals also have a crystalline structure. This is in contrast to *amorphous* materials, for example, polymers, which do not have long-range ordering. Crystals may be insulators, semiconductors or metals, depending on their energy band structure [1]. The materials studied in this work are semiconductor crystals.

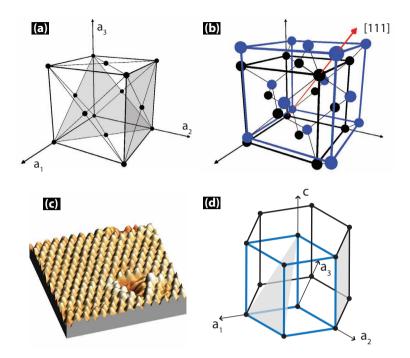

**Figure 2.2:** Crystal structures. (a) The fcc unit cell. The (111) and (010) planes are shaded grey. (b) The zinc blende crystal structure. The zinc blende crystal structure is constructed from the fcc lattice and a basis at each lattice point. The basis consist of a group III atom at the origin (black) and a group V atom translated  $\frac{1}{4}a$  in the [111] direction (blue). If the two basis atoms are the same, for example, silicon, the structure is denoted diamond. (c) Crystal structures can be observed directly with experimental techniques. Here a scanning tunnelling microscopy (STM) image of an InAs(111)B (1x1) surface is shown. Each peak corresponds to an As atom and a triangular defect (hole) is also observed. (Image courtesy of Emelie Hilner and Anders Mikkelsen.) (d) The simple hexagonal unit cell spanned by  $\mathbf{a}_1, \mathbf{a}_2$  and  $\mathbf{c}$  is shown in blue. The larger cell shown in black is often used for easier viewing. The (1011) and (1100) planes are shaded grey.

An ideal crystal is made up of units repeated infinitely and regularly in space. In the simplest case the unit (also called motif or more correctly basis) consists of a single atom. The units are placed at the lattice points of an infinite, regular lattice, a so-called *Bravais lattice*. A Bravais lattice has translational symmetry meaning that the lattice appears exactly the same from whichever point in the lattice it is viewed [1]. In three dimensions there are 14 different Bravais lattices, and in the two lattices most relevant to this thesis are shown in Figure 2.2(a,d): the face-centred cubic (fcc) and the simple hexagonal. *Miller indices* are used to denote crystal planes and crystal directions. The Miller indices, (hkl) (note round brackets), of a certain plane can be constructed by noting the plane's intersections with the basis axes, then removing any common factor, and finally taking the reciprocal values. In Figure 2.2(a), the (111) and (001) planes of the cubic system are shown. Crystal directions are given in the basis vectors with the notation (note square brackets):

$$[hkl] = h\mathbf{a}_1 + k\mathbf{a}_2 + l\mathbf{a}_3 \tag{2.4}$$

Many planes and directions are equivalent due to the symmetry of the crystal. A collective notation is then used for equivalent planes,  $\{hkl\}$  (curly brackets), and equivalent directions,  $\langle hkl \rangle$  (angle brackets). For example, the eight sides of the fcc cubic unit are equivalent and form the set:

$$\{001\} = \{(001), (00\overline{1}), (010), (0\overline{1}0), (001), (00\overline{1})\}$$

(2.5)

For the hexagonal system, *Miller–Bravais* indices (hkil) are commonly used. These are constructed in the same way as described above for the Miller indices, but because four basis axes are used, the first three indices are linearly dependent such that i = -(k + l). The advantage of using four indices is that equivalent planes have similar indices, which is not the case if three indices are used for the hexagonal system [22]. The indices of the six edge planes in Figure 2.2(d) are, for example, constructed by permuting 1 and  $\overline{1}$  over the first three indices. To simplify the notation, a letter is often assigned to a certain set of equivalent planes. The six edge planes discussed above are the *m* planes:

$$m = \{1\overline{1}00\} = \{(10\overline{1}0), (\overline{1}010), (0\overline{1}10), (1\overline{1}00), (10\overline{1}0), (01\overline{1}0)\}$$

(2.6)

As discussed above, crystal structures are constructed from a Bravais lattice and a basis. The constructions of the crystal structures of interest in this work are described below: the cubic structures diamond and zinc blende, and the hexagonal structure wurtzite.

The cubic structures can be constructed from the Bravais lattice and a basis in the following way. Consider the fcc lattice in Figure 2.2(a). Place a basis, consisting of a group III atom (black) and a group V atom translated  $\frac{1}{4}a$  in the [111]-direction (blue), at each lattice point. This is the zinc blende structure (also denoted sphalerite) of the III-V materials (Fig. 2.2(b)). If the two atoms are the same, for example, two Si atoms, the crystal has the diamond structure.

The hexagonal wurtzite structure is based on the hexagonal close-packed structure (hcp), which in turn is constructed from two intersecting simple hexagonal lattices (Fig. 2.2(d)), one being displaced  $\frac{2}{3}\mathbf{a}_1 + \frac{1}{3}\mathbf{a}_2 + \frac{1}{2}\mathbf{c}$  from the other. To form the wurtzite structure, a basis consisting of a group III atom at the origin and a group V atom at  $\frac{3}{8}$ **c**, is placed at each hcp lattice point. Real materials will deviate slightly from the ideal value of  $\frac{3}{8}$ .

The zinc blende and wurtzite crystal structures described above are closely related. NWs are observed to grow in both crystal structures, for example, zinc blende InP and wurtzite InP [20]. Along certain growth directions, especially the [111]B, a mixture of the two crystal structures is sometimes observed in the same NW, a phenomena denoted polytypism. Polytypism and its effects on the optical properties of nanowires were examined in references [xiv, xvii, xviii], but this large topic is beyond the scope of this thesis.

Some crystal orientations are polar, meaning that the planes are terminated by either group III or group V atoms. The cubic <111> and hexagonal <0001> directions used for NW growth are polar. For zinc blende, the facets terminated by group III atoms are denoted  $\{111\}A$ , and group V terminated facets are denoted  $\{111\}B$ . As described in the next chapter, the most common growth direction for NWs is the [111]B direction. For Si, which has a diamond structure and only contains one atom species, polar surfaces cannot exist, and all <111> directions are equivalent.

### 2.3 Atomistic View of Epitaxy

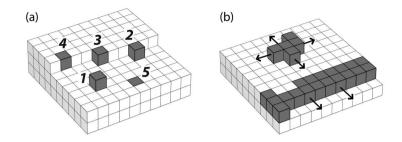

Epitaxy<sup>1</sup> can intuitively be understood as building a crystal "block-by-block". The word epitaxy itself originates from the Greek words  $\varepsilon \pi \iota$  – "on", and  $\tau \alpha \xi \iota \sigma$  – "in order" [18]. Many aspects of epitaxy can be illustrated by the *Terrace-Ledge-Kink* model (also called the Kossel model) [18]. In a Kossel crystal (simple cubic crystal) each atom is represented by a cube, and each face of the cube can bind to its nearest neighbour (Fig. 2.3). Growth species are supplied to the growing crystal from the vapour phase or as a molecular beam if high-vacuum conditions are used. Atoms that land on the surface diffuse and are incorporated into the crystal, or desorb again. The so-called adatoms (labelled "1" in the image) are loosely attached and only bind to one nearest neighbour. The adatoms are incorporated into the crystal when they diffuse to a more energetically favourable site, such as the kink position ("3"), or are embedded in the step ("4").

A Kossel crystal can also be used to understand different growth modes. The most commonly used planar growth mode is *step-flow growth*, where atoms are incorporated at a step, which then continuously advances forward (Fig. 2.3(b)). Wafers are often bought "miscut", meaning that they are cut a small angle from the exact crystal plane (a so-called vicinal surface), so as to contain steps and support

<sup>&</sup>lt;sup>1</sup>Epitaxy and crystal growth are sometimes used interchangeably, e.g., nanowire growth and nanowire epitaxy. However, strictly speaking, *epitaxy* refers to the method of depositing a monocrystalline film on a monocrystalline substrate, whereas *crystal growth* is the more generic term.

Figure 2.3: Kossel crystals. (a) Five surface atom positions are possible. Socalled adatoms ("1") are loosely attached to the surface by only one nearest neighbour and may diffuse across the surface and be incorporated into the crystal at more favourable positions (3 - 5). (b) The most commonly used planar growth mode is step-flow growth where atoms are incorporated at the step, which then advances forwards. Growth can also take place at a smooth facet via nucleation, the so-called birth-and-spread growth mode.

step-flow growth. Vicinal (001) surfaces with a few degrees of miscut are the most commonly used surface for commercial purposes [23]. This enables high-quality epitaxy using step-flow growth mode.

Crystal growth may also take place on an atomically smooth crystal face (terrace) where no steps are present. Adatoms diffusing on the surface may come together to form clusters. If the cluster reaches a certain critical size, it becomes stable and forms a nucleus. The nucleus now provides both steps and kinks for continued growth (Fig. 2.3(b)). This growth mode is often referred to as *birth-and-spread*. Particle-assisted NW growth as described in Section 3.1 is believed to take place by a birth-and-spread mechanism [xvii][19].

Several epitaxial techniques can be used, such as liquid phase epitaxy (LPE), halide vapour phase epitaxy (HVPE), chemical beam epitaxy (CBE), molecular beam epitaxy (MBE) and metal-organic metal vapour phase epitaxy (MOVPE). MOVPE was used in this work.

### 2.4 MOVPE

Metal-organic vapour phase epitaxy (MOVPE) dates back to the late 1960s and the work of Manasevit and co-workers [24]. It is today the commercially most important epitaxy growth method for III-V semiconductors, and its products range from blue laser diodes (AlGaInN material) to high-speed electric devices (e.g. in the GaInAsP material system).

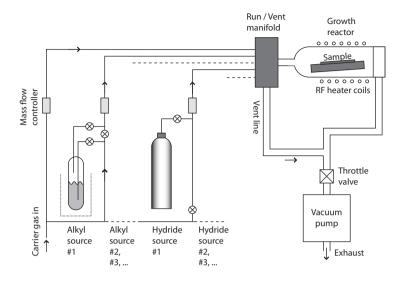

Figure 2.4: Schematics of a MOVPE system.

MOVPE takes place at atmospheric or low pressures (typically 100 mbar). An inert carrier gas is passed over a sample, which rests on a heater. The material for crystal growth is supplied in the form of precursor molecules that flow over the sample together with the carrier gas. For the growth of gallium arsenide, used as an example here, trimethyl gallium (TMGa) and arsine (AsH<sub>3</sub>) are commonly used precursors. The precursors decompose at the elevated temperatures used for epitaxy, typically 600 - 700 °C for planar GaAs epitaxy, and the elemental species, Ga and As, are incorporated into the GaAs crystal. Although the detailed chemistry is highly complex, the net reaction for GaAs epitaxy is:

$$Ga(CH_3)_{3_{(gas)}} + AsH_{3_{(gas)}} \longrightarrow GaAs_{(solid)} + 3CH_{4_{(gas)}}$$

(2.7)

In the ideal case the methyl groups desorb from the surface, leaving low residual carbon levels in the GaAs crystal. A thorough description of MOVPE processes has been given by Stringfellow [23].

In Figure 2.4 a simplified scheme of a typical MOVPE system is shown. Hydrogen is a commonly used carrier gas because it is available at extremely high purity through palladium diffuser purification, but nitrogen may also be used. The alkyl sources for the group III elements (e.g., TMGa, TMIn, TEGa and TMAI) are in liquid or solid form and are extracted through their vapour pressures by the carrier gas. The hydrides are gaseous and are transported by their own bottle overpressure. The gas flows of the different sources are controlled by mass flow controllers and transported separately to a gas manifold before the growth cell. Here, they are either sent to the growth reactor, "run line" or bypassed to the exhaust, "vent line". The sample rests on a susceptor that is heated. In Figure 2.4 a solution that employs RF heating (inductive heating) is shown. Resistive heating and heating by infra-red lamps are also common. A vacuum pump downstream from the growth reactor controls the reactor pressure through a throttle valve. Toxic components are removed from the exhaust by filters or combustion. The epitaxy system is computer-controlled, and a "growth recipe" is executed. Such a recipe contains detailed information on the flows of the different gases, temperature, pressures, and so forth. The duration of a growth run ranges from  $\sim 30$  min to several hours.

## Chapter 3

# Nanowire Epitaxy

In the present chapter, nanowire epitaxy and its special merits compared with planar epitaxy are described. The two main growth modes, particle-assisted and particle-free, as well as nanowire heterostructures, are briefly reviewed.

Nanowire epitaxy involves quasi-1D growth with a NW diameter < 100 nm. On this scale, many differences compared with bulk start to appear: surface energies make a significant contribution to the total energy of the structure, and strain and defect properties are different to those of bulk. Many NWs are reported to be ideal crystals, free of defects, and may crystallize in a structure different from the stable bulk phase (e.g., wurtzite InAs). Moreover, NW epitaxy offers greater freedom in the design of complex structures compared with planar epitaxy.

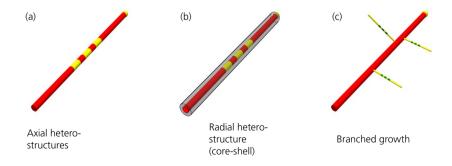

Figure 3.1: NW heterostructures and growth modes.

In Figure 3.1 three different NW structures are shown. Heterostructures, axial (a) and radial (b), are crucial for many devices, and in the axial direction,

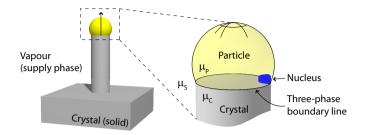

Figure 3.2: Schematic image of particle-assisted NW growth. Crystal growth takes place selectively at the particle/crystal interface.

the NW geometry offers the possibility of new material combinations due to its small cross-section (see Section 3.3). A third type of structure, a branched NW, is shown in panel (c). Branched nanowires can be created by employing particle deposition on NW "stems" and subsequent particle-assisted NW growth to form the branches [viii][25]. A third generation ("leaves") can be formed by further deposition and growth. From these three basic structures, more advanced building blocks can be formed, illustrating the flexibility of NW epitaxy.

#### 3.1 Particle-Assisted Growth

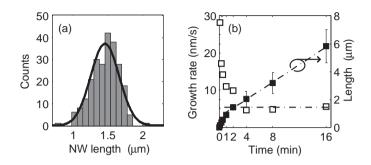

In particle-assisted NW growth, a growth catalyst particle is used to induce 1D growth at the site of the particle. Growth proceeds orders of magnitude faster at the particle/crystal interface than on surrounding surfaces (Fig. 3.2), which results in virtually one-dimensional growth. The size of the particle determines the wire diameter, and reported diameters range from 3 nm [26] up to several 100  $\mu$ m [27]. The length is controlled by the growth period (at a certain growth rate).

Particle-assisted whisker growth was observed already in the 1950s (see [28] and references therein) and silicon whiskers catalysed by gold particles were systematically studied by Wagner et al. in the 1960s [29]. Together with the group led by Givargizov [30] they pioneered Au-assisted growth of predominantly Si whiskers. Hiruma and co-workers further explored Au-assisted growth of III-V nanowhiskers in the 1990s [31, 32], and at the end of the 1990s and beginning of 2000, several groups initiated work on NW synthesis employing gold particles (see e.g. [33–36]).

In a typical process for NW growth, metal particles (often Au) are deposited on a crystalline semiconductor surface. These particles can, for example, be prepared in the form of aerosols, and filtered to provide a narrow size distribution [37]. The gold-decorated substrate is then transferred to a growth system, for example, a MOVPE system. During heating to the growth temperature, the particles interact

with the substrate, and surface oxides desorb. Growth is then initiated when the source gases are introduced into the chamber.

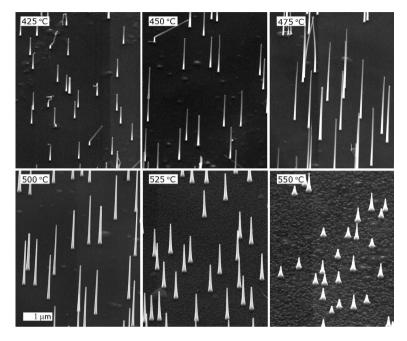

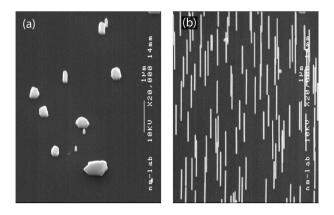

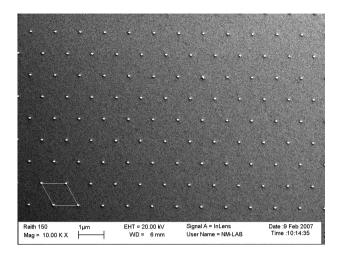

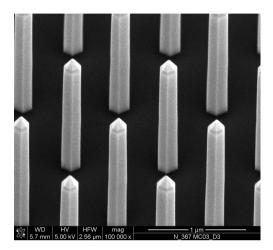

Figure 3.3: Scanning electron microscopy (SEM) images of a growth temperature series of particle-assisted GaP NW. NWs grown on GaP(111)B substrates at a density of  $1 \times 10^8$  cm<sup>-2</sup>. Molar fractions of TMGa and PH<sub>3</sub> were  $9 \times 10^{-6}$  and  $7 \times 10^{-3}$ , respectively, i.e. a V/III ratio of  $\approx 760$ . The pressure was 100 mbar in a 6 000 sccm hydrogen carrier gas flow. The growth time was 4 min. Image tilt is  $45^{\circ}$ .

Figure 3.3 shows a temperature series of particle-assisted GaP NW growth. The NWs grow epitaxially in the [111]B direction at normal angles to the GaP(111)B substrate. At low temperatures the wires are short and rod-shaped. With increasing temperature, tapering as well as the axial growth rate increase. The length of the NWs peaks at 475  $^{\circ}$ C and decreases again for higher temperatures.

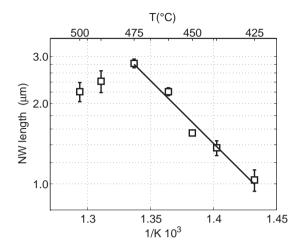

Figure 3.4 shows the axial growth rate for the GaP NWs displayed in Figure 3.3. The axial growth rate, R, of nanowires is often observed to follow an Arrhenius dependence for low temperatures, that is,  $\ln(R)$  depends linearly on 1/T with a negative slope (see e.g. refs [xi][30, 36]). Arrhenius behaviour is expected for any process where the rate constant, k, in the rate-limiting step follows a relation of the type  $k = Ae^{-\frac{E_a}{k_B T}}$ , where  $E_a$  is the activation energy,  $k_B$  the Boltzmann constant, T the temperature and A the exponential prefactor. This growth regime is referred to as *kinetically limited*. The rate-limiting step has, for example, been reported to

**Figure 3.4:** Length of GaP NWs after 4 min growth (cf. Fig. 3.3). A linear fit in the temperature interval 425 - 475 °C gives an activation energy,  $E_a$ , of  $89 \text{ J} \cdot \text{mol}^{-1}$ .

be the cracking of precursors [36, 38] or the crystal growth at the particle/crystal interface itself [30]. At higher temperatures (here  $\geq 475$  °C), the axial NW growth rate decreases due to the onset of competing growth on NW side facets and the substrate surface. These conditions, which also favour radial growth, can be used to grow a shell structure around the NW [39, 40].

The mechanism of particle-assisted NW growth is still an topic of considerable interest. The most often cited growth model is the so-called vapour–liquid–solid (VLS) mechanism, which was first described by Wagner and Ellis in 1964 [27]<sup>1</sup> to explain the growth of silicon whiskers employing a gold growth catalyst. The original description of the VLS mechanism was based on the properties of the gold-silicon phase diagram, and the concept of a liquid gold droplet that becomes supersaturated with Si supplied by the gas phase. As the drop becomes supersaturated, Si will precipitate in solid form at the liquid/solid interface, and crystal growth will take place selectively under the Au particle.

Some inconsistencies in the VLS model have recently been pointed out, and the need for a more complete model has become apparent. The particle may, for example, be in the solid form and still support NW growth [xii][41, 42], and surface diffusion of growth species often makes a strong contribution to NW growth [xiii][43], neither of which is accounted for in the original VLS model.

What are the main effects causing NW growth? The particle has been reported to

<sup>&</sup>lt;sup>1</sup>This original paper alone had been cited more than 1600 times as of August 2008.

behave as a true chemical catalyst<sup>2</sup> that catalyses precursor decomposition [38, 44] and it could thus support a higher supersaturation in the particle than outside. Although this is an important effect, it cannot be a *necessary* requirement for NW growth, because in many reports, the activation energy for NW growth is the same as for planar epitaxy [36, 45]. Furthermore, NWs can still be grown even if precursor cracking is not involved, for example, using MBE [46].

Also, in the absence of an irreversible step at the particle surface (such as precursor decomposition), the particle cannot sustain a local supersaturation higher than its environment. The chemical potential of the supply phase (e.g., the vapour phase in MOVPE),  $\mu_S$ , must be higher than the chemical potential of both the particle,  $\mu_P$ , and the crystal,  $\mu_C$ , for growth to take place (cf. Fig. 3.2). Furthermore, the growing phase, that is, the crystal, must have the lowest chemical potential, thus:

$$\mu_C < \mu_P < \mu_S \tag{3.1}$$

From this equation it follows that the supply-to-crystal supersaturation,  $\Delta \mu_{SC} = \mu_S - \mu_C$ , is always higher than the particle-to-crystal supersaturation,  $\Delta \mu_{PC} = \mu_P - \mu_C$ , that is,

$$\Delta \mu_{PC} < \Delta \mu_{SC} \tag{3.2}$$

Thus, if supersaturation alone determines the growth rate, 2D growth on the substrate should be faster than axial wire growth [47].

Additional effects seem to be needed for a generic model of NW growth, and recent models also focus on a lowering of the nucleation barrier at the particle/crystal interface [19, 47]. The surface under the particle is different from the surrounding crystal/vapour surfaces. It may, for example, have a different surface reconstruction or different step energies. The growth rate may be locally enhanced under the particle if these differences are such that the nucleation barrier is lowered. Nucleation is furthermore believed to take place at the edge of the particle/crystal interface at the three-phase boundary line [xiv][19, 47], where the nucleation barrier is lower [19]. That is, growth proceeds by a birth-and-spread mechanism initiated at the three-phase boundary line. It should be noted that publications providing quantitative calculations on nucleation barriers at the different interfaces are still lacking in the literature.

#### 3.2 Particle-Free Growth

Recently, NW growth without foreign growth catalysts has been reported. Several different types of growth mechanisms exist, and they are fundamentally different from the particle-assisted route. It has, for example, been reported that when

<sup>&</sup>lt;sup>2</sup>A chemical catalyst lowers the activation energy,  $E_a$ , of a rate-limiting step without being consumed.

certain oxide precursors are used, a passivating oxide shell forms, which promotes 1D NW growth. This is referred to as oxide-assisted NW growth [48]. The catalysing effect of a thin  $\text{SiO}_x$  film, as well as patterned  $\text{SiO}_x$  particles, on NW growth has also been reported [xv]. Comprehensive reviews of different synthesis methods and materials systems have been made by Xia [49] and Rao [50].

The formation of one-dimensional objects by controlling the growth rate of different crystal facets is described next. A prerequisite for facet-controlled formation of 1D objects appears to be anisotropy in the crystal structure. Polar materials such as GaN [51–53] and ZnO [54, 55], are often reported to grow in columnar structures. Conversely, covalent materials such as Si have not been reported to grow as 1D structures without the aid of a growth catalyst or passivating shell [48].

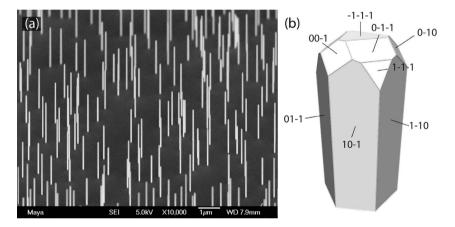

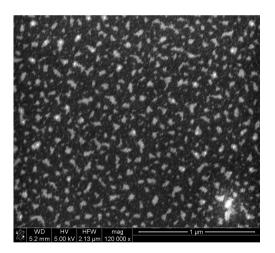

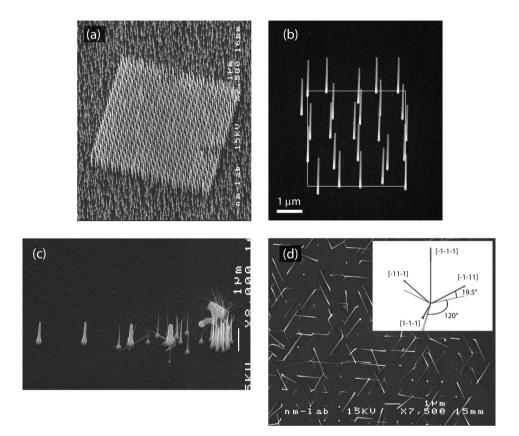

**Figure 3.5:** Particle-free NW growth. (a) InAs NWs grown on a Si(111) substrate (Paper II). Image tilt 45°. (b) Schematic image of a NW with  $\{\overline{1}10\}$  side facets. The tip is bounded by the slow-growing tip facets (most commonly the low-index facets).

How can a one-dimensional crystal shape form? First, it is important to realise that NW growth is a process far from equilibrium, and that Wulff's theorem [56] cannot be used to explain the one-dimensionality of a NW. In the common case for crystal growth of convex shapes, the fast-growing facets "grow out", and the crystal is left bounded by its slow growing facets [57]. However, if the slowest growing facets are all parallel to a crystal axis (e.g., the  $\{\overline{1}10\}$  facets parallel to the  $(\overline{1}\overline{1}1)$ axis as shown in Fig. 3.5(b)), they cannot completely bound the crystal. The result is that the fast-growing tip facets can continue to grow without reducing their area. In this way, one-dimensional growth can be sustained and NWs formed. For NW growth with  $\{\overline{1}10\}$  side facets (cf. Paper II), the requirement for one-dimensional growth can be written as:

$$R_{\{\overline{1}10\}} < R_{[\overline{1}11]}, R_{\{110\}}, R_{\{\overline{1}00\}}, R_{\{\overline{1}11\}}, R_{higher index tip facets}$$

(3.3)

where R denotes the growth rate of the different facets. For MOVPE growth of III-V materials, this low growth rate of the side facets is usually obtained with a low V/III ratio<sup>3</sup> and a high temperature [58, 59]. The tip shape is determined by the relative growth rates of the different tip facets. Flat tips [xv][58, 59], as well as rounded or pointed tips (Paper II and [54, 55]), have been reported<sup>4</sup>.

#### 3.3 Heterostructures

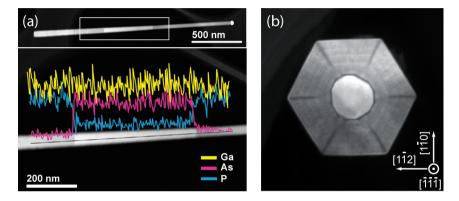

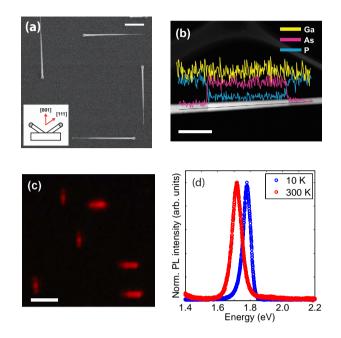

In Figure 3.6 two examples of NW heterostructures are shown, *axial* and *radial*. Axial heterostructures in the InAs/InP material system were essential for the formation of a central InAs island with InP barriers in Paper VI (see Section 6.2), and radial heterostructures were key for forming the light-emitting diode (LED) structure described in Paper V (see Section 6.1).

Axial heterostructures can be fabricated if the growth precursors are alternated during axial NW growth [32, 60–62]. For example, a GaP/GaAs<sub>1-x</sub>P<sub>x</sub>/GaP double heterostructure can be achieved if the group V source is switched from phosphine to arsine and back [63]. A unique feature of the small NW cross-section is the ability to grow axial heterostructures of materials that are normally incompatible due to a large difference in their lattice constants. The lattice mismatch between two materials is defined as:

$$f = \frac{a_u - a_o}{a_u} \tag{3.4}$$

where a is the lattice constant of the materials, and the indices u and o denote underlayer and overlayer, respectively.<sup>5</sup> In the case of conventional 2D planar layers, interface defects are difficult to avoid even for small mismatches. For a mismatch f = 2 %, it is expected that defects form already after the growth of a 10 nm thick overlayer (Ge<sub>0.5</sub>Si<sub>0.5</sub>/Si [64]). The situation is different for the NW geometry because the small cross-section allows strain to be relaxed also radially. Ertekin et al. used an equilibrium energy minimization approach to determine the critical radius for dislocation formation; it was found that the critical radius for axial heterostructures is approximately one order of magnitude larger than the corresponding critical thickness for planar growth [65]. Experimental observations suggest that the critical radius may be even larger in, for example, the InAs/InP system [60, 66]. A heterostructure similar to the axial forms during growth of

<sup>&</sup>lt;sup>3</sup>Flow of group V precursor / flow of group III precursor

$<sup>^{4}</sup>$ It should be noted that these profiles are observed *ex situ* after cooling to room temperature, and that the shape of the tip may have changed from that during growth.

<sup>&</sup>lt;sup>5</sup>For materials with more dissimilar crystal structures, this expression must be generalized.

NWs on a dissimilar substrate, for example, GaP or InAs on Si (Papers I and II, see Section 4.2).

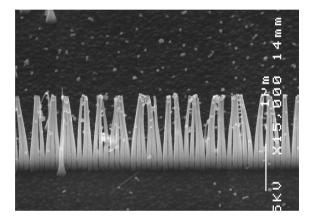

The second type of heterostructure is the radial, or *core-shell*, heterostructure (Fig. 3.6(b)) [39, 40]. A shell can be grown around the core if the growth parameters are changed to also favour growth on the NW side facets. Such a shell is often important for NW devices; the shell moves detrimental surface states away from the active region where charge transport or radiative recombination take place.

Figure 3.6: TEM images of NW heterostructures. (a) Light-emitting GaAsP segments incorporated into a GaP NW during growth. The sharpness of the interfaces is visible from the X-ray energy dispersive spectroscopy line scan. (b) Cross-section, looking down the axis, of a GaAs/AlGaAs core-shell NW. The GaAs core appears bright with a surrounding AlGaAs shell. The darker regions at the hexagon vertices are Al-rich regions [40].

## 3.4 Comparison of Particle-Assisted and Particle-Free Growth

Both particle-assisted and particle-free NW growth have their merits and drawbacks. A brief comparison is made here.

#### $\Box$ Materials

Polar materials (III-Vs and II-VIs) can be grown particle-free due to their asymmetry in crystal structure. Covalent materials such as Si and Ge have not been reported in particle-free growth mode. Particle-assisted growth does not suffer from this limitation and has been reported for a wealth of materials, see, for example, Rao et al. [50].

#### $\Box$ Growth uniformity

Both particle-free and particle-assisted NWs can be synthesized with good control of site, diameter and composition (cf. [43, 58]). For lithographic arrays, particle movement may cause distortion in the designed pattern (see Section 5.2), which does not occur for NWs grown by selective-area epitaxy [58]. Moreover, tapered wires are commonly observed with particle-assisted NW growth, whereas untapered wires are usually reported with particle-free growth.

#### $\Box$ Scalability

Some applications require very small NW diameters, which presents a challenge. NWs with diameters as small as 3 nm have been reported [26] with particle-assisted growth. Using particle-free growth via lithographic selected area epitaxy, the minimum size is determined by the hole size [58]. For lithographic particle-assisted arrays, a thin metal disc may reshape upon heating to a more compact shape with smaller diameter, thus enabling wire diameters below the lithography resolution limit.

#### $\Box$ Axial heterostructures

There are a multitude of reports on high-quality axial heterostructures using particle-assisted NW growth (see e.g. [32, 60–62]. For particle-free growth, the number of reports is fewer, and a problem appears to lie in achieving highly selective axial growth with no radial growth.

#### $\Box$ Radial heterostructures

High-quality core-shell structures have been reported for both growth modes (see e.g. [40, 67]). The absence of a particle may, however, be an advantage as the particle is passive during radial growth and may present a complication.

#### $\Box$ Growth temperature

In general, the growth temperature is lower for particle-assisted growth, for example  $\sim 100$  °C in the InAs system [xii]. A higher growth temperature often result in better crystal quality and less incorporation of carbon impurities. However, a high temperature may be problematic concerning integration with other processes.

#### $\Box$ CMOS compatibility

There are two major concerns regarding compatibility with CMOS: temperature and contamination.

(i) CMOS back-end-of-line processes can only tolerate temperatures  $\lesssim 420\ ^{\circ}\mathrm{C},$

which favours the lower temperatures needed for particle-assisted NW growth. NW growth may also be performed front-end-of-line, where much higher temperatures are acceptable. However, contamination problems then become more severe.

(*ii*) Gold is a deep-level contaminant in Si [68], effectively preventing its introduction into modern CMOS fabrication facilities. This may be resolved by using other catalyst materials, which are CMOS compatible. However, the particle-free method presents a simpler solution.

## Chapter 4

# III-V Nanowires Integrated on Silicon

Papers I and II describe how III-V nanowires can be grown epitaxially on Si substrates. In this chapter a background is first given to the topic of III-Vs on Si; particle-assisted growth of GaAs/InGaP nanowires on Si, and particle-free growth of InAs nanowires on Si, are then described.

The III-Vs do not have many of the shortcomings of Si (see Table 4.1 for a comparison of properties). For photon-emitting devices, Si is a "dead" material due to its indirect band gap.<sup>1</sup> Most III-Vs have a direct band gap and are the choice for applications such as telecom lasers (GaInAsP), blue laser diodes for optical storage (AlGaInN) and high-brightness light-emitting diodes (AlGaInN or AlGaInP). For electronics, the high electron mobility of, for example, InAs and InSb could enable high-speed, low-power devices; the high mobility allows a low drive voltage with maintained drive current [69]. Moreover, both photonic and electronic devices benefit from the advanced heterostructure technology available for the III-Vs. Heterostructure technology is also the key component for multijunction photovoltaics [70].

Although the III-Vs appear be the preferred choice for many applications, Si will probably remain the preferred platform for many applications for several reasons: it is available as large area wafers of extremely high purity and crystal quality, the material has good mechanical stability, it has a stable  $SiO_2$  oxide, it is an extremely well-characterized material, and simply because immense investments

<sup>&</sup>lt;sup>1</sup>Si can be made to emit photons by, for example, introducing rare earth dopants, using very small crystal sizes, or using stimulated Raman emission. However, these technologies yet have to be proven for commercial applications.

|                                        | Si                               | III-Vs                                                      |  |  |

|----------------------------------------|----------------------------------|-------------------------------------------------------------|--|--|

| Band gap<br>(eV)                       | indirect<br>1.12                 | generally direct<br>wide span, InSb 0.163, AlN 6.02         |  |  |

| Electron mobility $(cm^2/Vs)$          | 1900                             | InSb: 78 000                                                |  |  |

| Hole mobility $(cm^2/Vs)$              | 500                              | GaAs: 400                                                   |  |  |

| Thermal conductivity $(mW/cm \cdot K)$ | 1240                             | GaAs: 560                                                   |  |  |

| Wafer cost (111) orient. $(EUR/cm^2)$  | $\approx 0.2 \ (4 \ {\rm inch})$ | $\approx 8~({\rm GaAs}~2~{\rm inch})$                       |  |  |

| Heterostructure technology             | $\mathrm{Si/Ge}$                 | device-grade lattice-matched<br>technology well-established |  |  |

Table 4.1:

Selected material properties for Si and III-V semiconductors.

Values at room temperature.

IVALUE

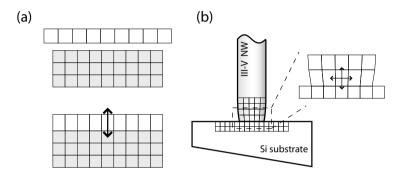

have been made in Si-based technology. Opportunities lie instead in the successful combination of the two material systems. However, for reasons discussed below, it has been difficult to achieve monolithic integration of III-Vs on Si. The small footprint of the nanowire/substrate interface may help to overcome many of these difficulties. If III-V NWs could be integrated on Si chips, they could provide standard CMOS with new functionality and could, for example, become a key component in fast on-chip optical communication [71, 72].

### 4.1 Planar Growth of III-Vs on Si

Much effort has been invested in achieving high-quality planar growth of III-Vs on Si [73, 74], and planar layers with defect densities as low as  $10^4 \text{ cm}^{-2}$  have been reported for GaAs on Si [75]. However, defect densities of  $\sim 10^6 - 10^9 \text{ cm}^{-2}$  are more commonly reported [74]. For comparison,  $\sim 10^5 \text{ cm}^{-2}$  is desirable for solar cell applications [74]. The high defect density is due to the difficulties encountered with planar layers in terms of mismatch in lattice parameters and thermal expansion, as well as anti-phase domain (APD) formation, which are described below.

First, if the lattice constant of the epilayer is not the same as that of the underlying substrate, the epilayer will initially try to adapt to the substrate lattice by changing its own natural bond lengths (pseudomorphic growth). However, as the epilayer grows thicker the energy stored in the strained epilayer will increase to a point where it is energetically more favourable to form crystal defects. The thickness at which this occurs is referred to as the *critical layer thickness*, and is of the order of 10 nm for a mismatch of 2 % (50 % Ge) in the Ge<sub>x</sub>Si<sub>1-x</sub>/Si system [64].

**Table 4.2:** Lattice mismatch of the III-Vs to Si (cf. eq. 3.4) and linear coefficient of thermal expansion. The lattice constant of Si is 5.43 Å. Comparison at 300 K, data from references [76, 77].

|                           | Si  | GaP  | GaAs | InP | InAs | GaSb | InSb |

|---------------------------|-----|------|------|-----|------|------|------|

| Lattice mism. (%)         | -   | 0.4  | 4.1  | 8.1 | 11.6 | 12.2 | 19.3 |

| Therm. exp. $(10^{-6}/K)$ | 2.6 | 4.65 | 5.73 | 4.6 | 4.52 | 7.75 | 5.37 |

Second, mismatch of the thermal expansion coefficients of the substrate material and the epilayer causes problems similar to those of lattice mismatch. Epitaxy often takes place at high temperatures (typically 500 to 1100 °C), and thermal expansion mismatch between substrate and epilayer may cause severe strain upon subsequent cooling to room temperature, resulting in crystal defects and wafer bowing.

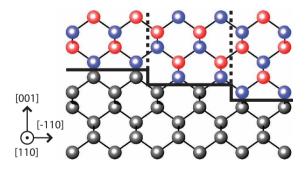

Figure 4.1: Anti-phase domain formation. APDs forming on a Si(001) surface with monoatomic steps. If the first deposited layer of the polar material consist of one species (coloured blue), APDs are created at the steps, as shown by the vertical dashed lines. Adapted from Kroemer et al. [78].

Third, APD defects may arise during the growth of polar materials on non-polar materials. APDs may be explained as follows. The Si diamond crystal structure can be described by two fcc sublattices displaced  $\frac{a}{4}$ [111] from one another, where Si atoms occupy both sublattices. This is in contrast to the zinc blende structure

of GaAs (used as an example here), where Ga and As atoms occupy one sublattice each. For the first deposited GaAs layer on the polar Si surface, there is an ambiguity concerning the sublattice on which the Ga atoms should reside. If two domains where the Ga atoms reside in different sublattices grow together, the boundary will be defective with Ga–Ga and As–As bonds (anti-phase) (Fig. 4.1) [73, 79, 80].

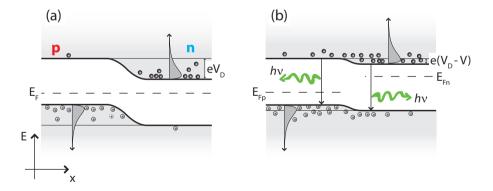

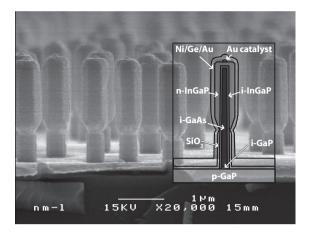

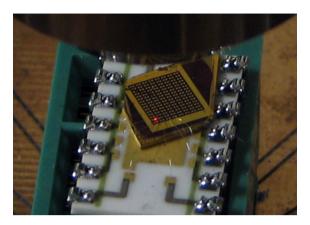

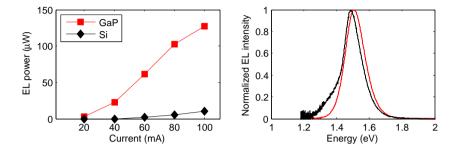

As will be discussed below, NWs can partly circumvent the above three problems due to their small footprints.