#### Flexible Receivers in CMOS for Wireless Communication

| 2015                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link to publication                                                                                                                                                                                   |

| Citation for published version (APA): Nejdel, A. (2015). Flexible Receivers in CMOS for Wireless Communication. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. |

| Total number of authors:                                                                                                                                                                              |

#### General rights

Neidel Anders

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or recognise.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 20. Dec. 2025

# Flexible Receivers in CMOS for Wireless Communication

## Anders Nejdel

Doctoral Dissertation Lund, October 2015

Department for Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

ISSN 1654-790X, no.75 ISBN 978-91-7623-415-0 (print) ISBN 978-91-7623-416-7 (pdf) Series of licentiate and doctoral dissertations.

© Anders Nejdel 2015. Produced using L<sup>A</sup>T<sub>E</sub>X Documentation System. Printed in Sweden by *Tryckeriet i E-huset*, Lund. October 2015.

### **Abstract**

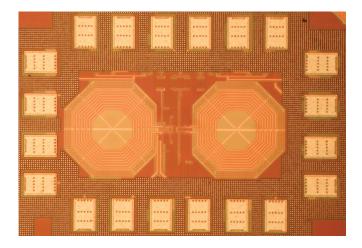

Consumers are pushing for higher data rates to support more services that are introduced in mobile applications. As an example, a few years ago video-on-demand was only accessed through landlines, but today wireless devices are frequently used to stream video. To support this, more flexible network solutions have merged in 4G, introducing new technical problems to the mobile terminal. New techniques are thus needed, and this dissertation explores five different ideas for receiver front-ends, that are cost-efficient and flexible both in performance and operating frequency. All ideas have been implemented in chips fabricated in 65 nm CMOS technology and verified by measurements.

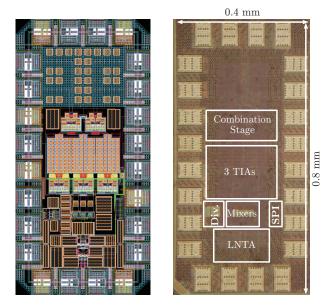

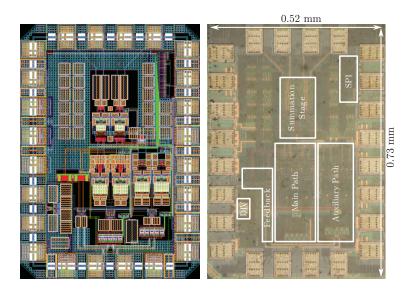

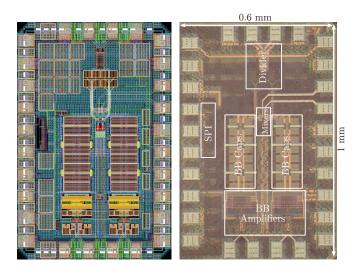

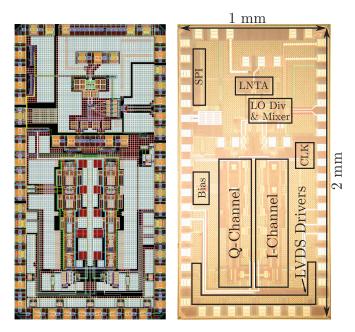

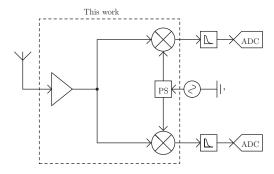

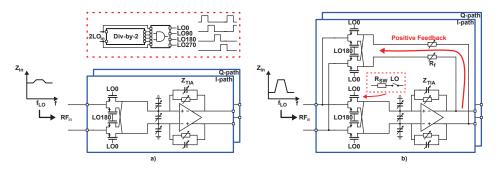

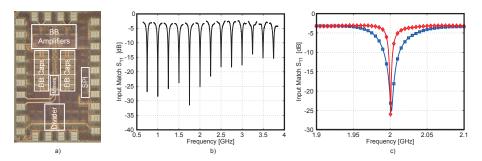

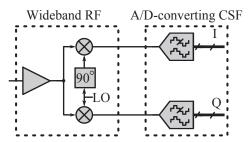

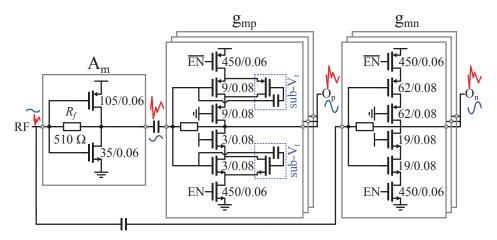

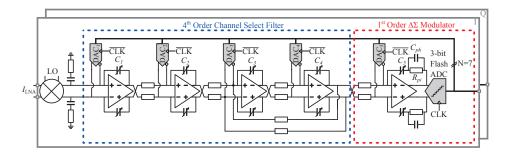

Paper I explores a voltage-mode receiver front-end where sub-threshold positive feedback transistors are introduced to increase the linearity in combination with a bootstrapped passive mixer. Paper II builds on the idea of 8-phase harmonic rejection, but simplifies it to a 6-phase solution that can reject noise and interferers at the 3<sup>rd</sup> order harmonic of the local oscillator frequency. This provides a good trade-off between the traditional quadrature mixer and the 8phase harmonic rejection mixer. Furthermore, a very compact inductor-less low noise amplifier is introduced. Paper III investigates the use of global negative feedback in a receiver front-end, and also introduces an auxiliary path that can cancel noise from the main path. In paper IV, another global feedback based receiver front-end is designed, but with positive feedback instead of negative. By introducing global positive feedback, the resistance of the transistors in a passive mixer-first receiver front-end can be reduced to achieve a lower noise figure, while still maintaining input matching. Finally, paper V introduces a full receiver chain with a single-ended to differential LNA, current-mode downconversion mixers, and a baseband circuity that merges the functionalities of the transimpedance amplifier, channel-select filter, and analog-to-digital converter into one single power-efficient block.

# Populärvetenskaplig sammanfattning

Tänk dig att du står i en gymnastiksal och ska prata med en person som står på andra sidan rummet. Den andra personen pratar med låg röst och du måste verkligen koncentrera dig för att höra. Låter det svårt? Tänk dig nu att en tredje person står bredvid dig och skriker så mycket den kan samtidigt som du ska försöka höra den andra personen. Detta är vardagen för vad mobiltelefonerna måste klara av för att kunna kommunicera.

I vardagen och i media pratas det mycket om digital kommunikation och analog kommunikation ses som en gammal teknik. Det var till exempel inte många år sedan det analoga TV-nätet stängdes ner och ersattes helt av det digitala. Den analoga tekniken finns dock fortfarande kvar. Även om informationen i moderna kommunikationssystem är digital är själva överföringen och därmed kommunikationen analog. Därför behövs det analoga kretsar som hanterar överföringen och efter dessa så görs signalen om till en digital signal. Vi har idag mängder av olika typer av system för trådlös kommunikation där informationen skickas på olika våglängder eller frekvenser.

Ett viktigt begrepp inom all kommunikation är bandbredd. Bandbredden beskriver hur mycket information som kan skickas med en viss modulering och optimeras hela tiden för att få plats med så mycket information som möjligt. Människan kan till exempel höra ljud med en frekvens mellan 50 hertz och 20 kilohertz vilket sätter bandbredden för hur mycket information vi kan höra. För att skicka trådlös informationen används en så kallad bärvåg som vanligtvis har mycket högre frekvens än informationen. Ett exempel på detta är FM-radio, där bärvågen är cirka 100 megahertz medan informationen är hörbart ljud, alltså en mycket låg frekvens. För mobil kommunikation är bärvågen mellan 400 megahert och nästan 4 gigahertz. och informationen kan vara 100 megahertz.

Bärvågen med information skickas genom luften från din telefon till en basstation i närheten och skickas vidare till telefonen som signalen ska fram till. Då den kommer fram till slutdestinationen är signalen väldigt svag. Problemet är nu att telefonen som tar emot signalen på samma gång skickar signaler tillbaka till basstationen. Som jämförelse kan skillnaden i styrka mellan den skickade signalen och den mottagna signalen vara lika stor som skillnaden i effekt mellan Ringhals kärnkraftverk och en LED-lampa! Detta gör det svårt för telefonen att "höra" informationen.

Denna avhandling innehåller fem vetenskapliga artiklar som beskriver konstruktionen av radiomottagare. Eftersom större krav ställs i och med nyare

trådlösa system så som fjärde generationens mobilnät så behövs flexibla lösningar som enkelt kan ändras från en konfiguration till en annan. Ett annat problem är att storleken på transistorerna, som används för att bygga de integrerade kretsarna, hela tiden blir mindre för att optimeras för digitala kretsar. För de analoga funktionerna är detta negativt och tyvärr så skalar inte storleken lika mycket på de passiva komponenterna (spolar och kondensatorer). Fyra av artiklarna innehåller därför lösningar för att ta bort spolar i mottagarkedjan. Alla fem artiklar är baserade på resultat från tillverkade integrerade kretsar, i en 65nm CMOS process, och visar på olika lösningar för flexibla mottagare. De fyra första behandlar den analoga delen som består av en lågbrusförstärkare, blandare som tar ner frekvensen från radiofrekvens till basbandsfrekvens samt basbandskretsar, medan den femte behandlar konstruktionen av en mottagare hela vägen från radiofrekvensingången till den digitala utgången.

Doktorandtjänsten har finansierats av Stiftelsen för strategisk forskning inom ramen för DARE (Digitally-Assisted Radio Evolution) och Marie Curieprojektet ATWC (Adaptive Transceivers for Wireless Communication). Kretstillverkningen har sponsrats av STMicroelectronics.

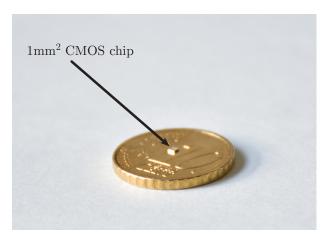

Jämförelse mellan ett  $1 \mathrm{mm}^2$  CMOS chip och ett  $\in \! \! 0.1$  mynt.

## Contents

| Abstract                                               | Ū.                                                                                                                                                                                                                                                                                                                                                                                                                    | iii                                                                            |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Populär                                                | vetenskaplig sammanfattning                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{v}$                                                                   |

| Content                                                | S                                                                                                                                                                                                                                                                                                                                                                                                                     | vii                                                                            |

| Preface                                                |                                                                                                                                                                                                                                                                                                                                                                                                                       | xi                                                                             |

| Acknow                                                 | ledgments                                                                                                                                                                                                                                                                                                                                                                                                             | xiii                                                                           |

| List of A                                              | Acronyms                                                                                                                                                                                                                                                                                                                                                                                                              | $\mathbf{x}\mathbf{v}$                                                         |

| List of S                                              | ymbols                                                                                                                                                                                                                                                                                                                                                                                                                | xix                                                                            |

| Introduc                                               | ction                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                              |

| 1.1<br>1.2<br>1.3<br>2 The<br>2.1<br>2.2<br>2.3<br>2.4 | Wireless Communication The Radio Frequency Application Specific Integrated Circuit Outline  Radio Receiver Standards and Wireless Spectra Architectures for RX  2.2.1 Superheterodyne 2.2.2 Homodyne Sensitivity Desensitization 2.4.1 Gain Compression 2.4.2 Cross-modulation 2.4.3 2 <sup>nd</sup> Order Non-Linearity 2.4.4 3 <sup>rd</sup> Order Non-Linearity LO Leakage Reciprocal Mixing 2.6.1 Harmonic Mixing | 1<br>2<br>4<br>5<br>5<br>8<br>8<br>9<br>10<br>10<br>11<br>12<br>14<br>15<br>15 |

|                                                        | ceiver Building Blocks  LNA  3.1.1 Inductively Degenerated Common-Source LNA  3.1.2 Common-Gate LNA  3.1.3 Noise-Cancelling CG LNA  3.1.4 Noise Analysis of the CG LNA in Paper II  3.1.5 Shunt-Shunt Feedback LNA                                                                                                                                                                                                    | 19<br>19<br>20<br>21<br>22<br>23<br>24                                         |

viii Contents

|                  | 3.1.6 Noise-Cancelling Shunt-Shunt Feedback LNA    |

|------------------|----------------------------------------------------|

|                  | 3.1.7 Noise Analysis of the FB LNA in Paper V      |

| 3.2              | Passive Mixer                                      |

|                  | 3.2.1 Noise in Passive Mixer                       |

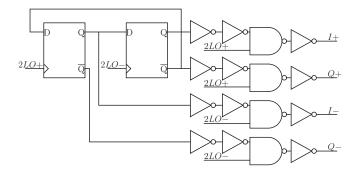

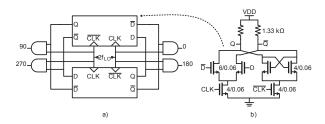

| 3.3              | LO Divider                                         |

|                  | 3.3.1 25 % Duty cycle                              |

|                  | 3.3.2 16 % and 33 % Duty cycle                     |

| 3.4              | OPAMP                                              |

|                  | stem Level Considerations                          |

|                  | Harmonic Down-Conversion                           |

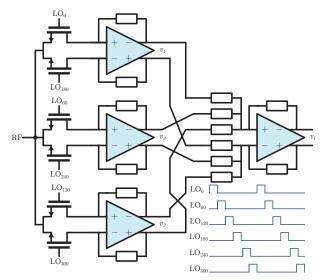

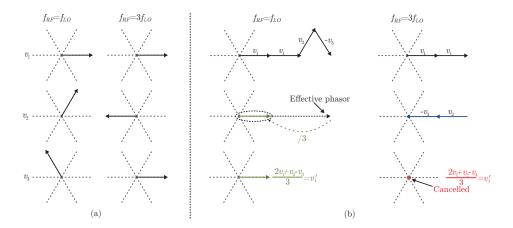

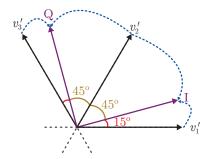

| 1.1              | 4.1.1 8-Phase Harmonic Rejection Mixer             |

|                  | 4.1.2 6-Phase Harmonic Rejection Mixer             |

| 4.2              | Global Negative Feedback                           |

| 7.2              | 4.2.1 Noise-Cancelling Receiver Front-End          |

| 43               | Global Positive feedback                           |

|                  | Analog-to-Digital Converting Channel-Select Filter |

| 7.7              | 4.4.1 Continuous Time $\Delta \Sigma M$            |

|                  | 4.4.2 Co-Design with Channel Select Filter         |

|                  |                                                    |

| 5 Pa             | per Summary and Conclusions                        |

| $6  \mathrm{Di}$ | scussion and Future Work                           |

| Refe             | rences                                             |

|                  |                                                    |

| Paper I          |                                                    |

| I                | Introduction                                       |

| II               | Receiver front end overview                        |

| III              | Low Noise Amplifier                                |

|                  | A LNA Design                                       |

|                  | B RFC                                              |

| IV               | Passive Mixer                                      |

|                  | A LO signal generation                             |

| V                | Results                                            |

| VI               |                                                    |

| Refer            | rences                                             |

| Tecres           | telices                                            |

| Paper I          | I                                                  |

| I                | Introduction                                       |

| II               | Receiver Front End Design                          |

| 11               | A LNTA                                             |

|                  | B Mixer and LO-Generation                          |

| III              | Harmonic Rejection                                 |

| IV               | Measurement Results                                |

| V                | Conclusion                                         |

| V                | COUCHISIOH                                         |

Contents ix

| Refer   | rences                                                          | 106 |

|---------|-----------------------------------------------------------------|-----|

| Paper I | II                                                              | 109 |

| I       | Introduction                                                    | 111 |

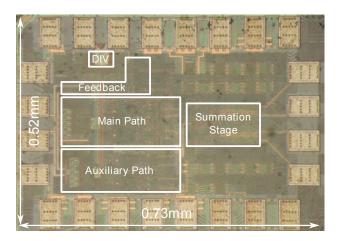

| II      | Wideband Receiver front-end                                     | 112 |

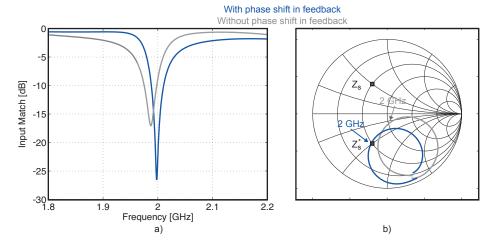

|         | A Phase adjustment of frequency translational negative feedback | 114 |

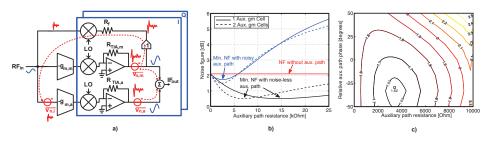

| III     | Noise Cancellation                                              | 116 |

| IV      | Circuit Implementation                                          | 118 |

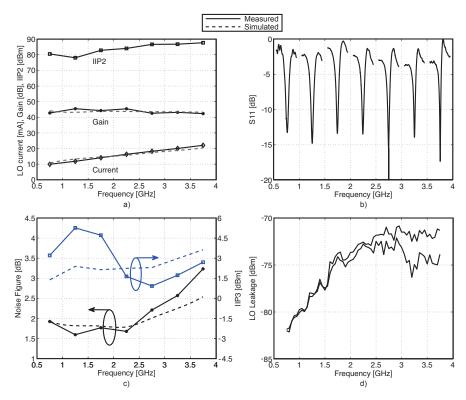

| V       | Experimental Results                                            | 121 |

| VI      | Conclusion                                                      | 128 |

| , -     | rences                                                          | 130 |

| Paper I | V                                                               | 135 |

| I       | Introduction                                                    | 137 |

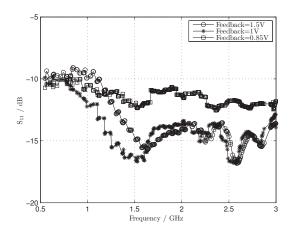

| II      | Passive mixer first receiver                                    | 137 |

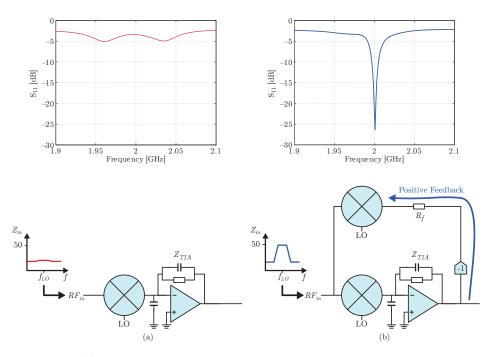

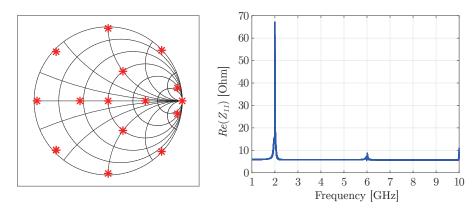

| III     | Passive mixer first receiver with positive feedback             | 138 |

| IV      | Circuit implementation                                          | 139 |

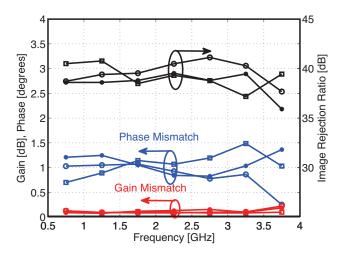

| V       | Measurement Results                                             | 140 |

| VI      | Conclusions                                                     | 142 |

| Refer   | rences                                                          | 143 |

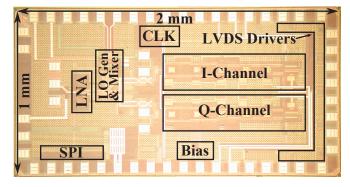

| Paper V | T.                                                              | 147 |

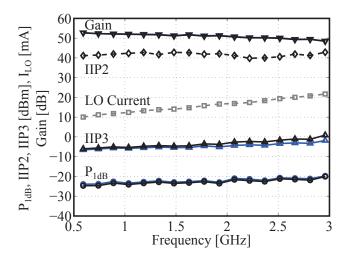

| I       | Introduction                                                    | 149 |

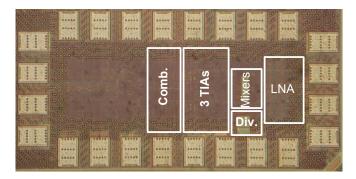

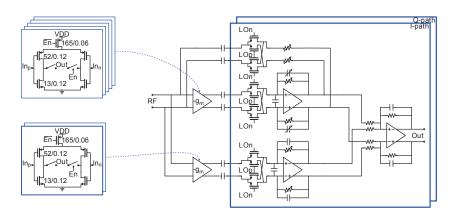

| II      | RF front end                                                    | 149 |

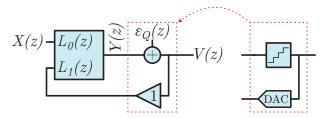

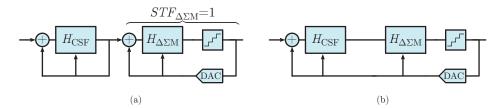

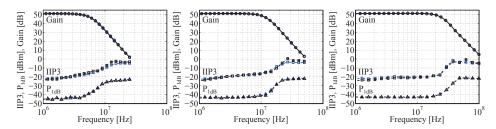

| III     | ADCSF Implementation                                            | 151 |

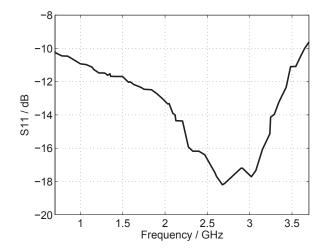

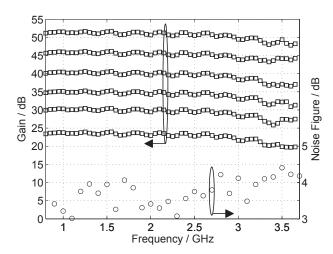

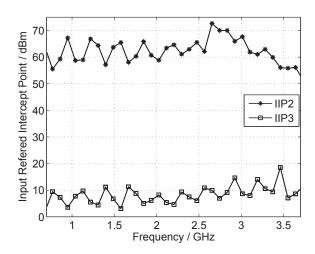

| IV      | Experimental Results                                            | 152 |

| V       | Conclusions                                                     | 156 |

| Refer   | rences                                                          | 158 |

## **Preface**

This dissertation summarizes my academic work for the Ph.D.-degree in Circuit Design at the Analog RF-group, Department of Electrical and Information Technology, Lund University, Sweden. The studies took place from January 2012 until November 2015. The dissertation is divided into two parts, where the first part has six chapters that contains an introduction to the research field whereas the second part consists of five attached research papers.

#### **Included Research Papers**

The main contributions are derived from the following publications:

- [1] A. Nejdel, M. Törmänen, and H. Sjöland, "A 0.7 to 3 GHz wireless receiver front end in 65-nm CMOS with an LNA linearized by positive feedback," in *Springer Analog Integrated Circuits and Signal Processing*, vol. 74, no. 1, pp. 49–57, Jan. 2013.

- [2] A. Nejdel, M. Törmänen, and H. Sjöland, "A 0.7 3.7 GHz Six Phase Receiver Front-End With Third Order Harmonic Rejection," in *Proceedings of IEEE European Solid-State Circuits Conference*, Bucharest, Romania, Sep. 16–20 2013, pp. 279–282.

- [3] A. Nejdel, H. Sjöland, and M. Törmänen, "A Noise-Cancelling Receiver Front-End With Frequency Selective Input Matching," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 5, pp. 1137 –1147, May. 2015.

- [4] A. Nejdel, M. Abdulaziz, M. Törmänen, and H. Sjöland, "A Positive Feedback Passive Mixer-First Receiver Front-End," in *Proceedings of IEEE Radio Frequency Integrated Circuits Symposium*, Phoenix, USA, May. 16–20 2015, pp. 79–82.

- [5] A. Nejdel, X. Liu, M. Palm, L. Sundström, M. Törmänen, H. Sjöland and P. Andreani, "A 0.6—3.0 GHz 65 nm CMOS Radio Receiver with ΔΣbased A/D-Converting Channel-Select Filters," in *Proceedings of IEEE European Solid-State Circuits Conference*, Graz, Austria, Sep. 14–18 2015, pp. 299–302.

The research was funded by the Swedish Foundation for Strategic Research (SSF) under the Digitally Assisted Radio Evolution project (DARE)

xii Preface

#### Related publications

The publications listed below contain complementary, and overlapping material, but are not considered as a part of this dissertation.

- [6] A. Nejdel, M. Törmänen, and H. Sjöland, "A Linearized 1.6-5 GHz Low Noise Amplifier Using Positive Feedback in 65 nm CMOS," in *Proceeding* of NORCHIP, Lund, Sweden, Nov. 14–15 2011, pp. 1–4.

- [7] M. Abdulaziz, A. Nejdel, M. Törmänen, and H. Sjöland, "A 3.4mW 65nm CMOS 5th Order Programmable Active-RC Channel Select Filter for LTE Receivers," in *Proceedings of IEEE Radio Frequency Integrated Circuits Symposium*, Seattle, USA, June. 2–4 2013, pp. 217–220.

- [8] A. Nejdel, M. Törmänen, and H. Sjöland, "A Noise Cancelling 0.7-3.8 GHz Resistive Feedback Receiver Front-End in 65 nm CMOS," in Proceedings of IEEE Radio Frequency Integrated Circuits Symposium, Tampa, USA, June. 1–2 2013, pp. 35–38.

- [9] W. Ahmad A. Nejdel, M. Törmänen, and H. Sjöland, "Fully Integrated Radio over Fiber Downlink for Distributed Multi-antenna Systems in 65nm CMOS," in *Proceedings of IEEE New Circuits And Systems Con*ference, Trois-Rivières, Canada, June. 22–25 2014, pp. 353–353.

## Acknowledgments

This work would not have been possible without the help and support from many.

First of all, I want to thank my supervisor Henrik Sjöland for his support during these years and for giving me the opportunity to pursue the Ph.D.-degree. You are truly an expert and having a discussion with you always gives me a lot of new insights. Thanks to my co-supervisor Markus Törmänen, especially for all the more practical aspects of circuit design; your valuable knowledge has been very important. Thanks to Johan Wernehag for all our discussions. I am also very grateful for all the advice from Pietro Andreani, especially during the design of the circuit that resulted in the final attached paper.

A special thanks go to all the current and former Ph.D.-students of the analog RF-group, for all the cooperation and company during late tapeout-evenings and also for your friendship and interesting discussions during coffee breaks, travels and lunches. Being a part of the DARE project, headed by Pietro, has been very nice and I am grateful to all my teammates. You have all challenged me to understand other design aspects than only analog RF-design. Another big thanks goes to all other PhD-students, current and former, at EIT for keeping me company during my time here at the department! I am also grateful for all the support from EIT in general, both administrative and technical. To all the people at Ericsson in Lund who have helped me: Thanks; especially to Magnus Nilsson, Sven Mattisson and Lars Sundström.

During my third year, I got the opportunity to do an internship at Marvell in Pavia, Italy. I learned a lot during this time and I am grateful to Paolo Rossi, Giuseppe de Pinto, Marika Tedeschi and Luca Fanori for providing me with some industry experience.

To my family: thank you for your unconditional support! Finally, I am ever grateful to my fiancée Jennie. Without you, this work would not have been possible and I can never express my gratitude for your support, patience and love during the past four years.

This work has been supported by: Swedish Foundation for Strategic Research within the DARE project, Seventh Framework Programme within the ATWC project, traveling to some conferences has been supported by the Ericsson Research Foundation, and chip manufacturing has been supported by STMicroelectronics.

Andes Nejdel

## List of Acronyms

Second Generation Mobile Network

Third Generation Mobile Network

Fourth Generation Mobile Network

**AC** Alternating Current

ACS Adjacent Channel Selectivity

ADC Analog-to-Digital Converter

ADCSF Analog-to-Digital Converting Channel-Select Filter

**AM** Amplitude Modulation

**ASW** Antenna Switch

ATWC Adaptive Transceivers for Wireless Communication

**BOM** Bill Of Materials

**CCC** Capacitive Cross Coupling

CF Correction Factor

CG Common Gate

CIFB Cascade-of-Integrators-in-Feedback

CML Current Mode Logic

CMOS Complementary Metal Oxide Semiconductor

CS Common Source

CSF Channel-Select Filter

CW Continuous Wave

**DAC** Digital-to-Analog Converter

DARE Digitally Assisted Radio Evolution

Div. RX Diversity Receiver

${f DSM}$  or  ${\Delta\Sigma M}$  Delta Sigma Modulator  ${f DSP}$  Digital Signal Processor

**DTV** Digital TV

**ENOB** Equivalent Number of Bits

FB LNA Shunt-Shunt Feedback Low Noise Amplifier

FDD Frequency Division Duplex

**GSM** Global System for Mobile Communications

**HRM** Harmonic Rejection Mixer

IC Integrated Circuit

IDCS Inductively Degenerated Common Source

IM2 Second Order Intermodulation Distortion

IM3 Third Order Intermodulation Distortion

IP2 Second Order Intercept PointIP3 Third Order Intercept Point

IRR Image Rejection RatioLNA Low Noise Amplifier

LNTA Low Noise Transconductance Amplifier

LO Local Oscillator

LTE Long Term Evolution

MIMO Multiple Input Multiple Output

MOSFET Metal Oxide Semiconductor Field Effect Transistor

**NF** Noise Figure

NTF Noise Transfer Function

**OFDM** Orthogonal Frequency-Division Multiplexing

OPAMP Operational Amplifier

OSR Oversampling Ratio

OTA Operational Transconductance Amplifier

PA Power Amplifier

PCB Printed Circuit Board

PMU Power Management Unit

PPF Poly Phase Filter

Prim. RX Primary Receiver

Q-Factor Quality Factor

QAM Quadrature Amplitude Modulation

List of Acronyms xvii

**QVCO** Quadrature Voltage-Controlled Oscillator

**QPSK** Quadrature Phase-Shift Keying

REFSENS Reference Sensitivity

RF Radio Frequency

**RF-ASIC** Radio Frequency Application Specified Integrated Circuit

RSSI Received Signal Strength Indication

RX Receiver

**SAW** Surface Acoustic Wave

SNDR Signal-to-Noise-and-Distortion Ratio

SNR Signal-to-Noise Ratio

SPI Serial Peripheral Interface

SSF Swedish Foundation for Strategic Research

STF Signal Transfer Function

SX Frequency Synthesizer

TDD Time Division Duplex

TD-SCMA Time Division-Synchronous Code Division Multiple Access

TIA Transimpedance Amplifier

TSPC True Single Phase Clocked

TX Transmitter

UE User Equipment

UHF Ultra High Frequency

VCO Voltage Controlled Oscillator

VHF Very High Frequency

W-CDMA Wideband Code Division Multiple Access

XTAL Crystal

## List of Symbols

BBandwidth [Hz]  $C_{qs}$ Gate-to-Source Capacitance [F]  $\Delta f$ Offset Frequency [Hz] Quantization Noise  $\epsilon_Q$ Local Oscillator Frequency [Hz]  $f_{LO}$  $f_{RF}$ Frequency of a Radio Frequency tone Receiver Frequency [Hz]  $f_{RX}$  $f_s$ Clock/sampling frequency [Hz]  $f_{TX}$ Transmitter Frequency [Hz] Gamma Factor, >2/3 for short-channel MOSFET  $\gamma$ Transconductance [S]  $g_m$ Boltzmann's constant,  $\approx 1.381 \times 10^{-23} \, [\mathrm{J/K}]$ k $L(\Delta\omega)$ Phase noise at an offset of  $\omega$  [dBm/Hz]  $L_g$ Gate Inductor  $[\Omega]$  $L_s$ Source Inductor  $[\Omega]$  $M_x$ Transistor x NNumber of phases in mixer Self Resonance Frequency [rad/s]  $\omega_0$ Transit Frequency [rad/s]  $\omega_T$  $R_L$ Load Resistor  $[\Omega]$  $R_s$ Source Resistance  $[\Omega]$ TTemperature [k]  $\overline{v^2}$ Noise Power  $V_{\rm th}$ MOS transistor threshold voltage [V]  $Z_s$ Source Impedance  $[\Omega]$ 1 dB Noise Compression Point  $P_{1 dB}$

## Introduction

## Chapter 1

#### Motivation

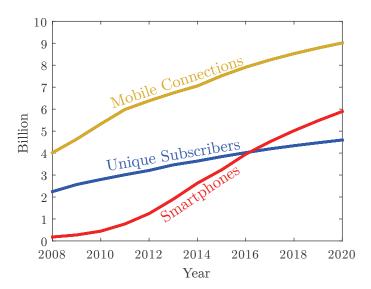

Figure 1: Number of mobile connections, unique subscribers and smartphones from 2008–2014 and estimates from 2015–2020 [10].

Communication and exchange of information is an important part of almost every person's life. Due to the rapid growth of cellular communication, more people communicate through cellular devices and the smartphone is a gadget many people use on a daily basis. It is estimated by GSMA that in 2020 there will be 4.6 billion cellular subscribers, 9 billion cellular connections (excluding machine-to-machine connections) and close to 6 billion smartphones [10], see figure 1. With more smartphones, and more services such as video-on-demand, the wireless internet traffic will also increase. It is estimated by Cisco that the mobile internet traffic will increase from an annual total of 30 exabytes  $(30\cdot10^{18}$  or 30 trillion bytes) in 2014 to 292 exabytes in 2019 [11]. In the end, cheaper communication devices will be beneficial to both customers and company share holders.

Figure 2: Illustration of wireless communication of digital data from transmitter to receiver.

#### 1.1 Wireless Communication

After a wireless signal reaches the antenna, it passes through the radio frequency (RF) receiver, where the analog radio signal is converted into a digital signal which is then demodulated and decoded and sent to a central processor. This reception of data is called the downlink. The same occurs but in the other direction when information is transmitted (uplink); digital information is coded and converted into a modulated analog signal, which in turn is converted into a radio signal and sent to the antenna, see figure 2.

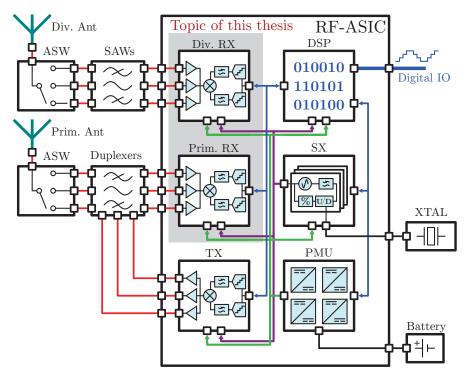

## 1.2 The Radio Frequency Application Specific Integrated Circuit

In order to have a cost-effective platform performing these tasks, the functions are implemented on a single integrated circuit or chip, normally called the Radio Frequency Application Specific Integrated Circuit (RF-ASIC). This chip consists of several important blocks, depicted in figure 3. The transceiver is here assumed to be able to operate at three different frequency bands. The signal is received by the antenna and an antenna switch (ASW) is used to steer the signal to one of three duplexers. The duplexers are used to isolate the receiver from the transmitter, where the strong transmitted signal otherwise would desensitize the receiver. After the duplexer the signal enters the RF-ASIC in the primary receiver (Prim. RX). The first task is to amplify the weak received signal while adding as little noise as possible, executed by a low noise amplifier (LNA). After the amplification the signal is down-converted in frequency by a mixer. Lastly, out-of-band interferers that are left after the down-conversion are removed, or heavily attenuated, in a channel-select filter (CSF) and the remaining signal is converted to digital form by an analog-todigital converter (ADC) and processed by the digital signal processor (DSP).

In order to perform frequency down-conversion the mixer needs a local oscillator (LO) signal which is generated by a frequency synthesizer (SX). This circuit uses a very clean and accurate low-frequency reference, typically provided by an off-chip crystal (XTAL), to generate a high precision frequency

Figure 3: High-level view of a modern transceiver with RF-ASIC and important off-chip components.

LO signal. Supply voltages are provided through a Power Management Unit (PMU) that converts the voltage of the battery to desirable levels for the circuitry.

Parallel to the primary receiver is a diversity receiver (Div. RX). This is connected to a second antenna which can provide reliable communication in environments with fast local fading. For the diversity receiver only SAW filters (very sharp filters to attenuate out-of-band blockers), i.e. no duplexer is used since the transmitter is connected to the primary antenna only. The circuitry of the diversity receiver can, however, be a replica of the primary receiver.

The data to be transmitted is first coded and modulated in the DSP and then fed to the transmitter (TX) circuitry, where digital-to-analog conversion is performed and the analog signal is filtered, frequency up-converted and amplified before being sent to the transmit port of the duplexer, which is connected to the primary antenna. In figure 3 it is assumed that the power amplifier (PA) of the TX is on-chip, but it might also be on a separate chip in a different semiconductor technology.

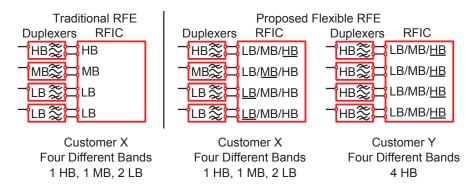

The fourth generation of mobile communication (4G) called Long Term

Evolution (LTE) is currently the most advanced cellular communication standard and poses new technical challenges. One challenge is the large number of RF bands that are introduced, ranging from 450–3800 MHz. The cellular transceiver depicted in figure 3 can only handle a few bands. At the same time, several of these bands use frequency division duplex (FDD) to be able to transmit and receive information at the same time on different frequencies. This means that there are very strong interferers, i.e. the own transmission, that can cause problems when trying to receive weak signals. This calls for flexible/re-configurable/adaptive circuity. In this dissertation the focus is on the receiver part of the RF-ASIC where papers I-IV present novel RF front-ends and building blocks while paper V presents a full receiver circuit.

#### 1.3 Outline

- **Chapter 1** presents a motivation and organization for the dissertation.

- Chapter 2 introduces the modern radio receiver and presents commonly used performance metrics.

- Chapter 3 describes and analyzes the building blocks used in the receiver front-ends.

- Chapter 4 presents some architecture-level implementation aspects.

- Chapter 5 gives summaries and conclusions of the included papers along with the author's contribution.

- Chapter 6 provides a discussion with suggestions for future work.

- Paper I presents design and measurements of a wideband receiver with an LNA that uses positive feedback transistors, biased in sub-threshold to improve linearity of the LNA.

- Paper II presents a technique to reject third order harmonic down-conversion by using six LO phases. Measurements are also included.

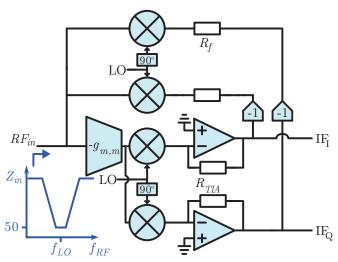

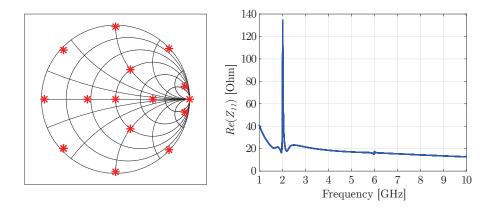

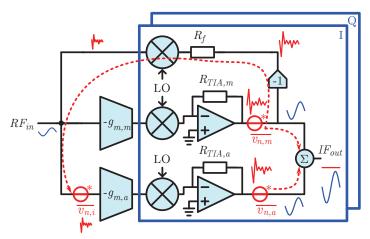

- **Paper III** presents the implementation and measurements of a wideband flexible noise-cancelling receiver front-end based on negative shunt-shunt feedback from baseband to RF input.

- **Paper IV** presents implementation and measurements of a mixers-first receiver front-end where the noise figure is reduced by increasing the switch sizes and introducing positive feedback.

- Paper V presents implementation and measurements of a wideband receiver with a noise-cancelling LNA and the complete baseband section including ADC. In order to increase power efficiency, a so called analog-to-digital converting Channel-Select Filter (ADCSF) is used.

## Chapter 2

#### The Radio Receiver

This chapter describes the radio receiver system and introduces common performance metrics that are used to evaluate the analog performance of radio receiver front-ends. In order to understand the importance of the metrics, explanations of problems that can occur due to the imperfections are also explained.

#### 2.1 Standards and Wireless Spectra

There are several wireless standards for cellular communication, where the most common globally used ones are 2G (GSM), 3G (W-CDMA and TD-SCDMA) and 4G (LTE). LTE was introduced to be able to receive a peak data rate of 1 Gbps and has more flexible bandwidth scaling compared to the previous generations. By introducing orthogonal frequency-division multiplexing (OFDM) and using a sub-carrier spacing of 15 kHz, the number of sub-carriers, grouped into resource blocks of 180 kHz, can be chosen to match different bandwidths between 1.4 and 20 MHz, see table I.

Table I: Bandwidths, corresponding number of resource blocks and effective bandwidth for LTE release 12.

| Channel BW [MHz] | Number of resource blocks | Effective BW [MHz] |

|------------------|---------------------------|--------------------|

|                  | (12 sub-carriers)         |                    |

| 1.4              | 6                         | 1.08               |

| 3                | 15                        | 2.7                |

| 5                | 25                        | 4.5                |

| 10               | 50                        | 9                  |

| 15               | 75                        | 13.5               |

| 20               | 100                       | 18                 |

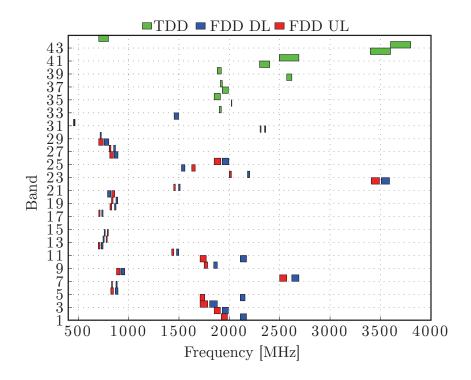

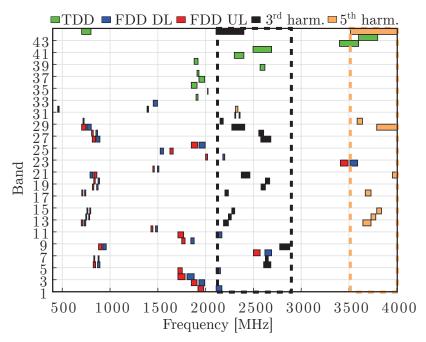

Figure 4: TDD and FDD frequency bands for LTE rel. 12.

Thanks to the flexible bandwidth, there are different configurations used in different RF bands. This creates an efficient way of using all frequency content available in the different bands. As an example, some bands are only a few MHz wide and they can either be configured as a single LTE20 channel or as several more narrow channels.

There are several different bands that are available for LTE, see figure 4, and they are divided into two different groups: time division duplex (TDD) bands and frequency division duplex (FDD) bands. The first bands (band 1–32) use FDD where the user equipment (UE) can receive and transmit signals at the same time, at different frequencies. The downlink can either be at a higher or at a lower frequency compared to that of the uplink. Two current exceptions are band 29 and 32 that are only used for downlink and are assumed to be used in carrier aggregation scenarios<sup>1</sup>. Band 33–44 are used for TDD where transmission and reception takes place at the same frequency but at different time instances. This relaxes some of the compression requirements of

<sup>&</sup>lt;sup>1</sup>Carrier aggregation introduces even more flexibility to LTE by combining data from different bands (inter-band), or from within the same band (intra-band).

the receiver, since the strong uplink is not active while receiving signals. There are, however, still several blockers, such as adjacent channels and signals from other standards that can desensitize the receiver.

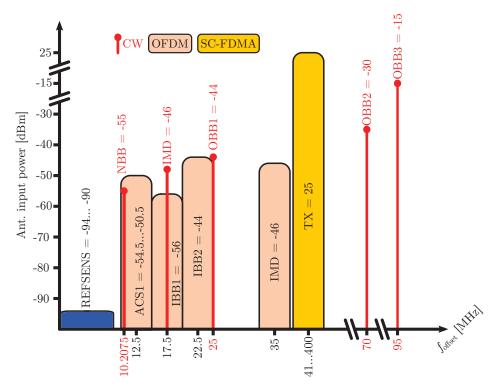

To exemplify this, figure 5 shows a blocker mask with both modulated blockers and continuous wave blockers for an LTE 20 MHz channel with respect to channel center frequency offset. The reference sensitivity (REFSENS), which is the minimum signal the receiver should be able to receive and process with a 95 % throughput, is between -94 dBm and -90 dBm depending on the band. Assuming the effective bandwidth is 18 MHz, according to table I, the inchannel thermal noise power is about -101.5 dBm. Furthermore, according to the standard documentation [12] the target coding rate is 1/3, for a QPSK modulated signal, which requires a signal to noise ratio (SNR) of between -1 dB [13] and -3 dB [14]. This means that the minimum signal at the antenna input can ideally be -102.5 to -104.5 dBm, which gives a margin of about 10 dB for antenna interface losses, and receiver noise figure, assuming no antenna

Figure 5: Example of blockers for an LTE20 channel in LTE rel. 12. Wideband signals are 5 MHz wide OFDM signals while the TX is a SC-FDMA signal that has lower peak to average ratio compated to OFDM.

gain. Just next to the receive signal, the adjacent channel can have a power of REFSENS+39.5 dB at 12.5 MHz offset.

The worst case power of the adjacent channel can be as strong as -25 dBm when the signal to be received is -50.5 dBm. The next strong blocker is the in-band blocker that can be -44 dBm at a 22.5 MHz offset. The narrowband IMD signal at 17.5 MHz offset, present at the same time as the wideband IMD at 35 MHz offset, will cause intermodulation distortion due to finite third order linearity as will be described later in this chapter. Another very strong blocker is the device's own transmitter which can supply a signal as strong as +25 dBm to the antenna, resulting in about +27 dBm at the TX output when accounting for losses in the duplexer. Thankfully, this off-chip duplexer attenuates the signal by about 50 dB [15,16]. These are, however, just a few of the signals that are present at the antenna input that causes problems when designing the receiver. The power of the blockers and frequency offsets depends on RF band and channel bandwidth. There are also some relaxed requirements on the number of resource blocks used, such as in band 20 where the duplex distance is the smallest for an LTE20 bandwidth.

#### 2.2 Architectures for RX

There are two general architectures for receiver front-ends: the homodyne and the superheterodyne. Both of them have benefits and disadvantages which are discussed below.

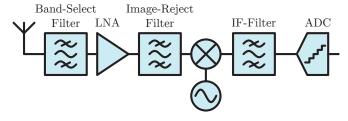

#### 2.2.1 Superheterodyne

In the superheterodyne receiver [17] the received signal is down-converted to an intermediate frequency (IF). The unwanted image frequency response is suppressed by using a bandpass filter. The advantages of this structure are high image rejection if the bandpass filter has a high Q-factor, immunity to even order intermodulation distortion (primarily IM2) and DC offset, no need for quadrature mixing and LO generation, and low LO leakage to the antenna. Disadvantages are the required high Q-factor image reject and IF filter and

Figure 6: Superheterodyne receiver.

Figure 7: Homodyne receiver.

the associated integration of these components. Using a typical modern integrated process, such as the 65 nm CMOS process used for the circuits in this dissertation, the Q-value of inductors is typically limited to about 10-20 and in order to provide reasonable attenuation of the image frequency the intermediate frequency would have to be very large. There are ways of solving this by introducing active filtering such as high frequency  $G_m$ -C filters, but this usually increases the power consumption of the receiver. In even more advanced processes such as 28 nm, where the 1/f noise (flicker) noise is very high, the superhetrodyne architecture has gained new attention since no information is located close to DC.

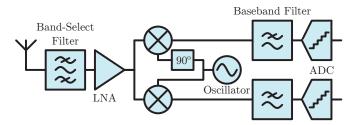

#### 2.2.2 Homodyne

In the homodyne [18], zero-IF or direct-conversion receiver, the problem with the image frequency is solved by down-converting the channel to a center frequency of zero. Since the image frequency is then the opposite of the receive signal, rejection of the image is simple [19], as unlike the superheterodyne receiver the image is not significantly stronger than the signal to receive. Still some image rejection is necessary to be able to distinguish positive frequencies from negative. For this purpose, to provide orthogonality between two outputs, a 90° phase shift is introduced in the LO signal to one of the down-conversion mixers resulting in a so called complex mixer. Since the output frequencies are centered around zero, the blocks after the mixer such as the CSF and ADC can operate at a minimum frequency, thus power-efficiency is optimized and CSFs can be implemented by using active-RC based architectures where high loop-gain can be exploited for linearity. The architecture has a few drawbacks: DC-offset, sensitivity to second order distortion of the down-conversion stage, and in modern processes sensitivity to 1/f noise [20]. Moreover, since the LO frequency is put in the center of the channel to be received, LO leakage is not attenuated by a image reject filter and becomes critical. LO leakage can cause DC offsets and cross-modulation with other blockers. The architecture, despite its drawbacks, is the most common solution in modern wireless integrated receivers and all included papers are therefore based on this structure.

Figure 8: The 1 dB cross-compression point is defined as the power of the blocker when the small signal gain is decreased by 1 dB.

#### 2.3 Sensitivity

Radio communication receivers are basically limited by two things: sensitivity and selectivity. The sensitivity determines how weak signal can be received and selectivity determines how strong signals can be that interfere with the received signal. Sensitivity is determined by the noise figure of the receiver, the required signal to noise ratio needed to demodulate the information and the bandwidth of the signal. Assuming and a temperature of 290 K the equation for the sensitivity in dBm is given by (1).

$$P_{sens} = -174 + NF + SNR_{min} + 10log_{10}(B) \tag{1}$$

The noise of the receiver is limited by the noise figure of the RF-ASIC, but also the insertion losses due to external SAW filters/duplexers and antenna switches. A typical noise figure of a modern RF-ASIC is about 3 dB [21–25].

#### 2.4 Desensitization

At the input of the RF-ASIC there are more signals than the wanted one present. For instance, there are often adjacent channels in the same band and if an FDD system is being used, the device's own transmitted signal will also be present at the input of the receiver. All these interferers can cause desensitization of the receiver and relaxing the requirements of the off-chip filters and duplexers can worsen the situation by further increasing the power of the interferers.

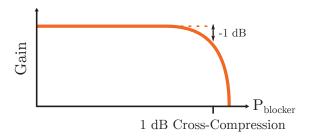

#### 2.4.1 Gain Compression

If a strong enough blocker is present the small signal gain of the receiver will eventually be degraded. A common metric is the 1 dB compression point, defined as the blocker power level where the small signal gain has decreased 2.4 Desensitization 11

by 1 dB, see figure 8. This compression is also sometimes called 1 dB crosscompression point, to distinguish the small signal compression of the in-band signal from the large signal compression of the blockers. There can also be large signal compression if the wanted signal itself is too large. To illustrate this, the input signal in typical wireless standards can be between -100 and -25 dBm. If the gain of the receiver is set to maximum, to minimize the noise figure, a -25 dBm input signal can compress the system. This is solved by introducing a block called the received signal strength indicator (RSSI) that can tune the gain of the receiver for a given scenario; if a strong wanted signal is present the gain can be reduced and even if the noise figure is increased the SNR is still sufficient for demodulation. For cross-compression the wanted signal is at -100 dBm, and a maximum gain is needed to have a minimum noise figure, but the small signal gain is decreased by an out-of-channel blocker. The blocker causing this degradation can be the transmitter in an FDD scenario, but can also be other external blockers originating from other devices, or from other standards in the same terminal. Such an example is the coexistence of WiFi, Bluetooth and LTE that can cause problems [26, 27]. It should be noted that if the small signal gain is decreased the noise will also increase, thus the most accurate way of measuring the desensitization due to a single blocker would be to look at the 1 dB degradation of SNR or signal to noise and distortion ratio (SNDR).

#### 2.4.2 Cross-modulation

Another cause of desensitization is cross-modulation. Consider an amplitude modulated (AM) blocker at  $f_{mod}$  together with a continuous wave (CW) signal at  $f_1$ . If the signals are amplified by a system that exhibits third order nonlinearity, the AM will "move" from the modulated blocker to the pure sinusoidal carrier. This is further explained in (2) where the two signals are amplified by the cubic term of the receiver. The final expression contains two terms where C is signals at frequencies that are not of interest, but the other term is at  $f_1$ , with amplitude modulation due to m(t).

$$y_3 = a_3(A_1\cos(2\pi f_1) + A_2(1+m(t))\cos(2\pi f_{mod})^3 =$$

$$= B + 3a_3A_1A_2^2(1+m(t))^2\cos(2\pi f_1)\cos^2(2\pi f_{mod})$$

$$= C + \frac{3}{2}a_3A_1A_2^2(1+m(t))^2\cos(2\pi f_1)$$

(2)

The resulting power of the cross-modulation is then  $P_{crossmod} = C_{factor} + 2P_{f_{mod}} + P_{f_1} - 2IIP3$ , where  $C_{factor}$  depends on the modulation of the blocker. In [28]  $C_{factor}$  is 7.4 dB for the WCDMA TX signal and 2.4 dB for a narrowband blocker.

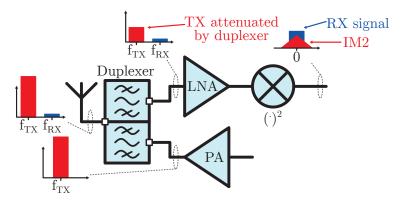

Figure 9: Due to finite IIP2 in the mixer, IM2 from the TX will be present in the receive band and will decrease the sensitivity.

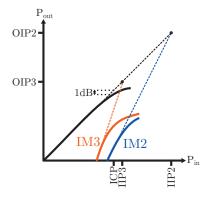

Figure 10: Definitions of both input referred and output referred IP2, IP3 and 1 dB compression point.

#### 2.4.3 2<sup>nd</sup> Order Non-Linearity

Consider a signal that has some kind of amplitude modulation, this can be either pure AM or a more complex modulation such as QAM, present at the input of the receiver. To simplify the analysis the AM signal is modeled by two tones,  $f_1$  and  $f_2$ , closely spaced. If the receiver has second order non-linearity, corresponding distortion will be present at the output. Of special interest is the intermodulation at  $|f_1 - f_2|$  as this will be at a baseband frequency, assuming close spacing of the two tones. If this occurs in the LNA, it is less of a problem since the LNA is working at a high frequency and the low frequency distortion can be filtered out by placing a capacitor between the LNA and the mixer. But for the mixer it is a problem since both the wanted information and the second order intermodulation distortion is present at the output at

2.4 Desensitization 13

baseband frequencies [29,30]. After this point, it is hard to distinguish between the information and intermodulation, and the intermodulation can be seen as extra noise which will degrade the sensitivity, see figure 9. There are ways of removing part of the IM2 components in the digital domain [31–33], but these methods will not be further considered in this dissertation.

The most common way of measuring second order intermodulation (IM2) performance of a receiver is to use the second order intercept point (IP2), found by extrapolating the IM2 power and the fundamental power with respect to the input power, all in logarithmic scales, and then see where the extrapolated lines intercept, figure 10. The IP2 can be referred either to the input or to the output of the receiver and in a receiver typically the input referred second order intercept point (IIP2) is used as the performance metric for second order linearity. IIP2 is calculated as (3), where  $P_{in}$  is the input power of both the wanted signal ( $P_{fund}$  in the baseband) and the two tones that will cause the IM2 product  $P_{IM2}$ . A higher IIP2 thus indicates a more linear receiver.

$$IIP2_{2t} = P_{in} + P_{Output\ fund} - P_{OIM2} = 2P_{in} - P_{IIM2}$$

(3)

All units must be in logarithmic scale and typically dBm is used. It should be noted that modeling the AM input as two tones as is a worst case condition and realistic scenarios are less severe. A correction factor should thus be added, since the IM2 information is spread beyond the wanted channel's bandwidth. This correction factor depends on several circumstances, such as the standard being used and the channel bandwidth. As an example how the standards can differ is that 3G uses WCDMA for the uplink whereas LTE uses SC-FMDA. Another circumstance that sets the correction factor for LTE is the bandwidth of the downlink. More information about how to derive the correction factors can be found in [34,35].

According to [34], the most challenging IIP2 requirement for LTE occurs when using band 4 (2110–2155 MHz for the downlink) and the signal bandwidth is 1.4 MHz. In this band the sensitivity defined by the standard is -104.7 dBm [12]. By using (4), where  $P_{TX}$  is the transmitted power at the TX output (generally  $+23\pm2+IL_{TX}$  dBm [12]),  $R_{dup}$  is the duplexer isolation (typically about 50 dB [15,16]),  $\Delta_M$  is a margin to the sensitivity, and  $\Delta$  is a margin to determine how much of the sensitivity level that is determined by IM2.

$$IIP2 = 2(P_{TX} + R_{dup}) - P_{sens} + \Delta_M + SNR + IL_{RX} + \Delta$$

(4)

$$IIP2_{2t} = IIP2 - CF \tag{5}$$

The resulting IIP2 is then about 70 dBm for band 4 and 1.4 MHz bandwidth. After correcting for the modulation correction factor (CF) in (5) the required two tone IIP2 is however about 60 dBm. Generally, the correction factor for LTE is between 9 and 11 dB. In a perfectly matched (symmetrical)

differential circuit the even order distortion will be cancelled. An IIP2 of more than 60 dBm is, however, challenging to reach without calibration and thus it is very important to spend great effort in making the LO distribution and mixer layout as symmetrical as possible.

The previous statement that the second order non-linearity of the LNA is neglectable is not true if carrier aggregation is being used. Assume a carrier aggregation scenario with one carrier at  $f_x$  and another one at approximately  $2f_x$ , and the uplink allocated to the uplink frequencies of the second carrier. An example of this can be when using a combination of band 12 (RX of 729–746 MHz) and band 11 (TX of 1427.9–1447.9 MHz). A blocker at  $f_{TX,B11} - f_{RX,B12}$  can then modulate with  $f_{TX,B11}$  and cause a tone at  $f_{TX,B11} - (f_{TX,B11} - f_{RX,B12}) = f_{RX,B12}$ .

# 2.4.4 3rd Order Non-Linearity

Another important scenario where blocking can occur is when a strong signal is located, at a frequency  $f_1$ , between the received signal and the transmitted signal,  $f_2$ . This blocker will reach the input and generate third order intermodulation at  $2f_1 - f_2$ , i.e. at the same frequency as the wanted signal, figure 11. The same problem occurs when a blocker at  $f_3$ , twice the TX offset frequency, is present. Similar to IIP2, the input referred third order intercept point can be calculated as (6)

$$IIP3 = P_{in} + \frac{P_{Ofund} - P_{OIM3}}{2} = \frac{3P_{in} - P_{IIM3}}{2} \tag{6}$$

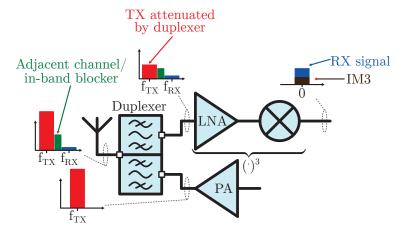

Figure 11: Due to finite IIP3 in the receiver, a blocker at half duplex distance can together with the strong TX signal create an IM3 component that can degrade the sensitivity.

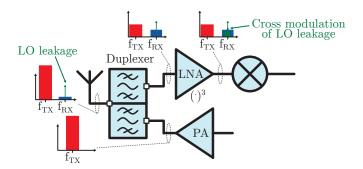

Figure 12: If there is LO leakage at the antenna input, an AM modulation can be cross-modulated in the LO leakage and desensitise the receiver.

# 2.5 LO Leakage

An important parameter that is becoming critical with the introduction of passive mixer-first receivers is the LO leakage. In more common architectures the LNA is isolating the RF input to the LO. The amount of isolation depends on several parameters such as the type of LNA and LO routing. As an example a common gate LNA has higher isolation than an inductively degenerated common source stage and use of a cascode in the LNA can further reduce the LO leakage. For a passive mixer-first topology or other similar N-path filters, the LNA is removed and the mixer is placed directly at the RF input.

The LO leakage can cause several problems; the first is not to exceed the spurious emission levels allowed by the standard and regulations. For a passive mixer the LO leakage is in the order of -60 to -80 dBm, which can be on the limit of what is tolerated from the spurious emissions point of view, which is -57 to -47 dBm for LTE. Another problem is the DC offset caused by the LO leakage. When a sinusoidal signal is mixed with itself, the resulting output is DC and a second harmonic tone. This DC is then amplified by the subsequent baseband blocks in the receiver and when reaching the ADC the offset can be several 100 mV, which decreases the resolution of the ADC. Thus DC offset calibration loops should be used if a large LO leakage is anticipated [36–38]. The third problem with LO leakage is cross-modulation. As described above and explained in (2), the LO leakage is a sinusoidal blocker that can be cross-modulated by the TX leakage and cause an increased noise floor.

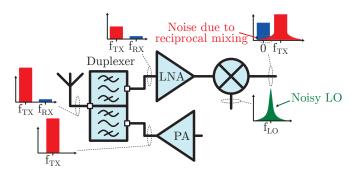

# 2.6 Reciprocal Mixing

Another problem in cellular receivers is reciprocal mixing. The LO signal that is used to drive the mixer is not a perfect single tone signal, but has some phase noise. As an example, if the phase noise of the LO signal is  $-160 \, \mathrm{dBc/Hz}$  at an offset of 100 MHz, a 0 dBm blocker at 100 MHz offset will then not

Figure 13: Phase noise of the LO can cause severe desensitisation when a strong blocker is present. Since the mixer will also down-convert the TX to RX baseband frequencies due to the noisy LO, the resulting in band noise is increased.

only produce a strong signal at 100 MHz baseband frequency, but there will also be noise from the TX in the receive band with an input referred power of -160 dBm/Hz, see figure 13. Assuming an LTE20 signal, the total noise due to reciprocal mixing is now -90 dBm which is close to the reference sensitivity level of the receiver, increasing the noise figure. Assuming that a receiver with a sensitivity level of -174dBm/Hz, the additional excess noise factor due to reciprocal mixing,  $F_{RM}$ , would be (7), where  $P_b$  is the blocker power and  $L(\Delta\omega_b)$  is the receiver LO phase noise at the blocker frequency offset.

$$F_{RM} = 10^{(P_b + L(\Delta\omega_b))/10} \tag{7}$$

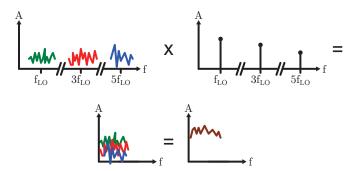

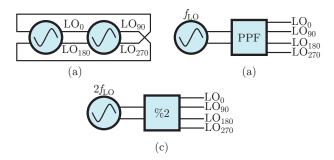

## 2.6.1 Harmonic Mixing

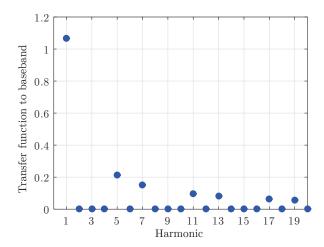

Since the use of the passive mixer has become widespread the most common LO signals are square waves. Square waves are easy to generate and distribute on-chip, since digital gates as inverters have a high speed and can work in a power-efficient way in modern CMOS technologies. One problem with square wave signals is, however, the harmonic content. Since a square wave signal contains all odd harmonics of the fundamental frequency, noise and signal at these harmonics can be down-converted, figure 14. When the receiver is wideband without explicit filtering after amplification, all thermal noise is fed to the down-conversion stage. This will increase the noise figure by close to 1 dB, according to (8).

$$NF_{harm.\ mix.} = 10log_{10} \left( 1 + \sum_{k=1}^{\infty} \frac{1}{(2k+1)^2} \right) = 10log_{10} \left( \frac{\pi^2}{8} \right) \approx 0.91 \text{ dB}$$

(8)

Figure 14: If a square wave signal is used in the mixer, noise and signals at odd harmonics will get down-converted and this will increase the noise floor in the baseband.

# Chapter 3

# Receiver Building Blocks

This chapter describes radio receiver front-end building blocks and presents some of the design challenges.

# 3.1 LNA

Usually, the first block at the radio input of an RF-ASIC is the LNA. The LNA is placed at the input of the RF-ASIC and will interface to the off-chip components. To make sure all the power from the antenna and off-chip component with impedance  $Z_S$  is transferred into the RF-ASIC, the LNA should provide a real input impedance  $Z_L$ . If there is a mismatch between the two impedance levels a reflection factor  $\Gamma$ , equation (9), will determine how much power is reflected back to the antenna. Usually this is presented by the input reflected power ratio  $S_{11}$ , which typically should be maintain to below -10 dB.

$$\Gamma = \frac{E^{-}}{E^{+}} = \frac{Z_{L} - Z_{S}}{Z_{L} + Z_{S}}, \quad S_{11} = 20 \cdot log_{10}(|\Gamma|)$$

(9)

Furthermore, since the total noise factor of the receiver, equations (10) and (11) where F is the noise and G is the gain, is dominated by the first block, the noise figure of the LNA should be as low as possible.

$$F = \frac{SNR_{\text{input}}}{SNR_{\text{output}}} \tag{10}$$

$$F = F_1 + \sum_{i=2}^{N} \frac{F_i - 1}{\prod_{j=1}^{i-1} G_j} = F_{LNA} + \frac{F_{other} - 1}{G_{LNA}}$$

(11)

At the same time, the noise from the subsequent blocks is attenuated by the gain of the LNA and the gain should thus be as high as possible without introducing too much distortion. These requirements poses high challenges when designing a high-performing LNA for a cellular receiver. There are mainly three different types of LNAs which are described in this section.

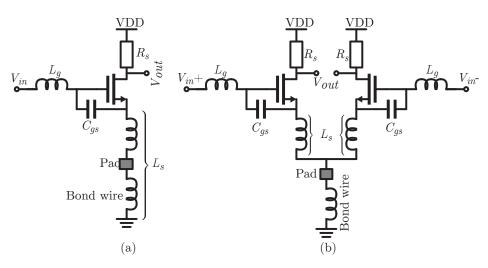

Figure 15: Schematic of the IDCS LNA. (a) The single-ended IDCS is sensitive to added inductance from bond wires. (b) Differential IDCS requires two inputs and twice the current compared to the single-ended version, but is more robust in terms of parasitics and has less even order non-linearities.

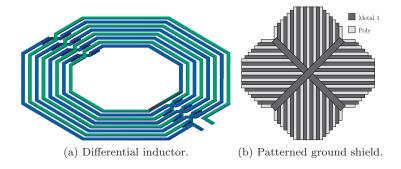

# 3.1.1 Inductively Degenerated Common-Source LNA

The inductively degenerated common-source (IDCS) LNA is a high performance LNA capable of very low noise figure. Since the noise figure is proportional to  $\omega_0/\omega_T$  the performance increases with more advanced process nodes [39–41]. The low noise is achieved using a passive input network that will amplify the signal voltage before reaching the input transistor, thus reducing the noise contribution from the MOSFET. The idea behind the IDCS LNA is to use an inductor between the source of the device and the ground, see figure 15, to create a series resonance circuit and thus a resistive part of the input impedance. By adding an extra inductor at the gate,  $L_g$ , the input reactance can be cancelled at the frequency of operation. This gate inductor is providing most of the passive voltage gain before the signal reaches the MOSFET. The input impedance is given by (12), and the resonance frequency by (13).

$$Z_{in} = s(L_g + L_s) + \frac{1}{sC_{gs}} + \omega_T L_s \tag{12}$$

$$\omega_0 = \frac{1}{\sqrt{(L_g + L_s)C_{gs}}} \tag{13}$$

The main problem with the IDCS LNA is the narrow frequency operation associated with the inductors. A very wide frequency range of operation is required in modern cellular receivers and since the IDCS LNA is tuned to

3.1 LNA 21

resonate at a certain frequency, wideband performance is hard to implement. In order to benefit the most from the voltage gain advantage of the input network, the resulting Q-value of the network needs to be high and the input match will thus be narrow. The high Q-value for the series network is limited by the performance of on-chip inductors and since the performance of these might be insufficient, bulky off-chip inductors may be required. There are ways of mitigating the problem of the narrow frequency range by using banks of inductors and by introducing capacitive tuning [21,22], but the area overhead might be very large.

In advanced processes, since the value of the source inductor  $L_s$  is inversely proportional to the value of  $\omega_T$  (12), the source inductor becomes very small. The small value of inductance can cause problems together with the parasitic inductance from bond wires and package. Thus EM simulations and estimation of all parasitics of the ground is important, see figure 15(a). On chip decoupling can also be used, keeping most of the RF current on-chip, but still the inductance may be significant compared to  $L_s$ . The problem of parasitic inductors can be alleviated by the use of a differential structure, see figure 15(b), keeping the current in the bond wires constant (DC only).

To decrease the small source inductance and to reach a lower noise figure by reduction of gate induced noise there is often an explicit capacitance placed in parallel with  $C_{gs}$  [40]. This increases the effective capacitance, and thus increases the value of  $L_s$ , and at the same time decreases the value of  $L_g$  making it more suitable for on-chip implementation. Even though, since high-performance inductors are needed, the IDCS LNA was not considered in any of the circuit implementations presented in the attached papers of this dissertation.

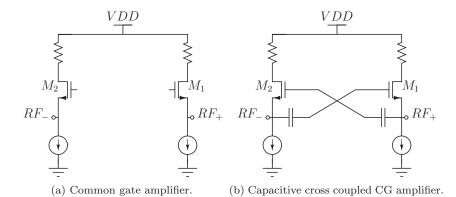

#### 3.1.2 Common-Gate LNA

The common-gate (CG) LNA, figure 16(a), can ideally (assuming no capacitance, output impedance, nor any contribution from  $g_{mb}$ ) provide a pure resistive input match that equals to  $Z_{in}=1/g_m$ . The key advantages of this amplifier are the wideband frequency range, high linearity, and low power consumption whereas the main shortcoming is the limited noise performance. Another disadvantage is the matching condition of  $Z_{in}=1/g_m$ , i.e.  $g_m$  can't be arbitrary chosen to set performance of the LNA. This puts a lower limit on the achievable noise factor of the CG LNA at  $F=1+\gamma$  or  $NF\approx 3$  dB, when in matched condition and used in its standard configuration. The thermal noise coefficient,  $\gamma$ , is equal to 2/3 at low electric field, but can be considerably higher in short-channel devices [42, 43].

To improve the noise performance of the CG LNA a feed-forward gain of -A can be introduced from the input (source node) to the gate, increasing the effective  $g_m$  of the amplifier by a factor of (1 + A), see figure 16. To maintain

Figure 16: (a) The CG LNA provides a very wideband input match but suffers from restrictions in selection of  $g_m$ . (b) By introducing amplification from input to the gate the noise figure can be reduced.

the input match  $g_m$  should then be reduced by the factor (1 + A) which will result in a 1 + A times less channel noise contribution from the transistor. The minimum noise factor then becomes  $F = 1 + \gamma/(1 + A)$  [44,45].

There are several ways of implementing this feed-forward gain, but if an active device is used as a feed-forward amplifier [46] the noise of that amplifier will also affect the noise performance. An attractive solution is thus passive amplification, either by using capacitive cross coupling (CCC), which will limit the feed forward gain to unity and provide  $F = 1 + \gamma/2$ , or by using transformers, where the mutual coupling ratio between the inductors can be chosen to obtain more voltage gain and less noise, at the cost of reduced linearity [47].

Another way to increase the freedom in selecting the parameters of the CG LNA is to introduce positive feedback [48, 49]. In a similar way as the feed forward path can increase the effective  $g_m$  and decrease the input impedance, the positive feedback can instead increase the effective input impedance. By using both techniques in combination the performance can be set within wider bounds, still ensuring input matching and stability (limited by the positive feedback). The LNAs in papers I and II are based on the CG topology.

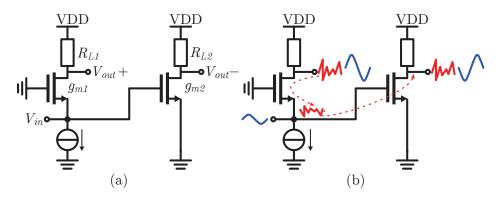

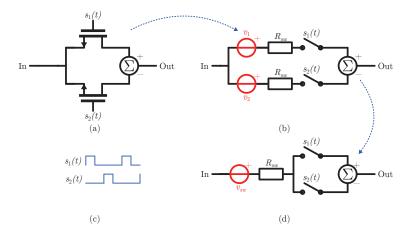

# 3.1.3 Noise-Cancelling CG LNA

One way of reducing the noise of the CG LNA is to use noise-cancellation [50], depicted in figure 17(a). In addition to the CG LNA in figure 16, a CS stage has been introduced in parallel with the same input signal as the CG stage. This enables a single-ended to differential conversion by exploiting the inverting transfer function of the CS amplifier in combination with the non-inverting CG configuration. Channel current noise of the CG stage will introduce a voltage

3.1 LNA 23

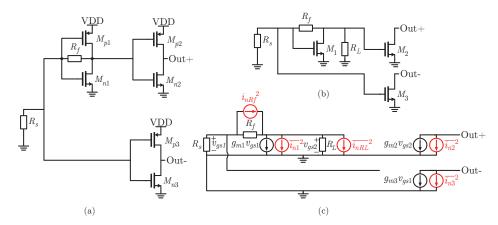

Figure 17: (a) Schematic of a noise-cancelling CG amplifier. (b) Conceptual schematic of how the channel noise of the CG stage is sensed by the CS stage and appears in common-mode at the output.

at the output that is in anti-phase with the corresponding voltage noise at the input, see figure 17(b). The noise at the input is then sensed by the CS stage and amplified to the negative output  $V_{out}$ . Now, if the outputs are balanced by  $g_{m1}R_{L1} = g_{m2}R_{L2}$ , the noise of the CG stage appears in phase and with the same amplitude at both outputs, i.e. it is cancelled at the differential output. This is very beneficial, since  $g_{m2}$  can be arbitrarily set, and it can be increased to decrease the remaining transistor noise, the contribution of the CS stage.

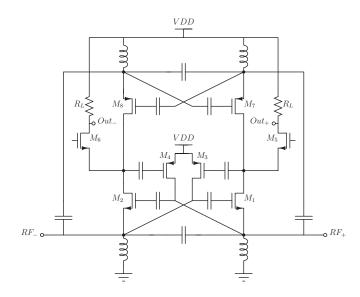

# 3.1.4 Noise Analysis of the CG LNA in Paper II

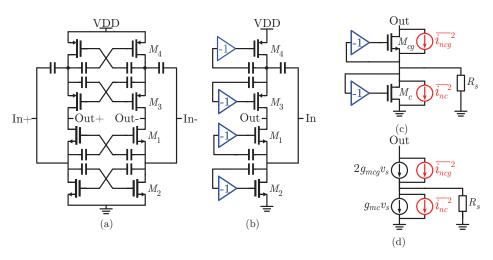

The schematic of the LNA in paper II can be seen in figure 18(a) and consists of a differential complementary CCC-CG input stage  $(M_1, M_3)$  and negative-resistance current sources  $(M_2, M_4)$ . The effective  $g_m$  of  $M_1$  and  $M_3$  is doubled due to the CCC providing A = -1. The differential stage can be simplified to the half-circuit in figure 18(b). Due to the complementary structure the circuit can be further simplified by folding to figure 18(c), where the PMOS devices are replaced by NMOS devices. The input resistance of this structure is given by (14), where  $g_{mcg} = g_{m1} + g_{m3}$  and  $g_{mc} = g_{m2} + g_{m4}$ .

$$Z_{in} = \frac{1}{2g_{mcg} - g_{mc}} \tag{14}$$

To calculate the noise performance, the circuit in figure 18(d) can be analyzed where the two noise sources  $\overline{i_{neg}^2}$  and  $\overline{i_{ne}^2}$  will be the contributors to the noise factor (15).

Figure 18: (a) Schematic of the LNA in paper II. (b) Half-circuit simplification. (c) Folded simplification with noise sources. (d) Noise analysis.

$$F = 1 + \frac{\gamma (R_s g_{mc} - 1)^2}{g_{mcg} R_s (2R_s g_{mcg} - R_s g_{mc} + 1)^2} + \gamma g_{mc} R_s = 1 + \frac{\gamma (R_s g_{mc} - 1)^2}{4g_{mcg} R_s} + \gamma g_{mc} R_s, \text{ if } R_s = Z_{in}$$

(15)

An interesting feature of this LNA is that if  $g_{mcg} = g_{mb} = 1/R_s$  mS, the noise of the CG transistors will not reach the output, but circulate inside the MOSFETs and will not contribute to the noise figure. The reason for this can be explained by calculating the transfer function from  $\overline{i_{ncg}^2}$  to a noise source at the input,  $\overline{i_{icg}^2}$ , of the CG stage as (16). When  $g_{mb} = 1/R_s$  mS the resistance seen by the CG stage is infinite, thus all noise will circulate.

$$\frac{\overline{i_{icg}^2}}{\overline{i_{ncg}^2}} = \left(\frac{1}{1 + \frac{2g_{mcg}}{-g_{mb} + \frac{1}{R_s}}}\right)^2 \tag{16}$$

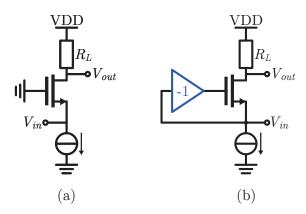

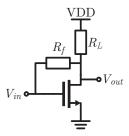

#### 3.1.5 Shunt-Shunt Feedback LNA

The shunt-shunt feedback LNA (FB LNA), figure 19, uses negative feedback<sup>2</sup> to decrease the input impedance seen from the ideally open gate input of the MOSFET [51]. The equation for the input impedance is given by (17).

<sup>&</sup>lt;sup>2</sup>In this dissertation only resistive feedback is considered, but capacitive feedback is also possible.

3.1 LNA 25

Figure 19: By introducing a resistive feedback, the high open loop input impedance will decrease and matching can be accomplished.

$$Z_{in} = \frac{R_f + R_L}{1 + q_m R_L} \tag{17}$$

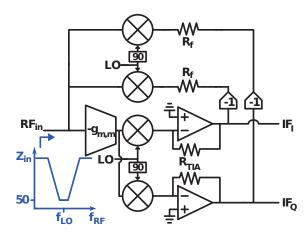

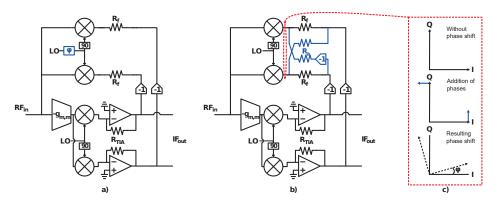

Assuming a very high load resistance the input impedance approaches  $1/g_m$ , the same as for the CG LNA, since the input transistor looks like a diode-connected transistor. However, in real implementations, the load resistance cannot approach infinity, but is at least limited to  $1/g_{ds}$  of the transistor, typically in the range of  $\sim 1~\text{k}\Omega$ . The large benefit of the FB LNA is the simple structure and the absence of inductors. A disadvantage is that it relies on a voltage output and requires voltage gain for the feedback to be operational. In order to work as an low noise transconductance amplifier (LNTA), i.e. an amplifier with a current output, either by current steering in a single stage as presented in [52] or using a cascade of a shunt-shunt feedback LNA and a  $g_m$ -stage can be used as in the implementation of the LNA in paper V.

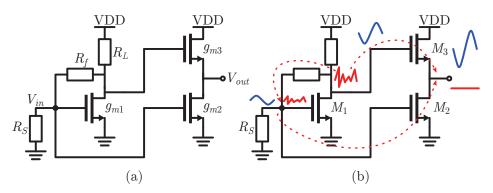

# 3.1.6 Noise-Cancelling Shunt-Shunt Feedback LNA

Noise-cancellation can also be used in the FB LNA to reduce the noise figure. The schematic of one such noise-cancelling LNA is shown in figure 20(a), where a second stage has been introduced with a CS amplifier and a source follower at the top [53]. The transistor channel noise of the FB LNA will be present at the output of the FB LNA, and it will also be fed back to the input through resistive voltage division between  $R_f$  and  $R_s$ , see figure 20(b). This noise is sensed by the CS stage, consisting of  $M_2$ , and the noise is amplified with an inverting transfer function. At the same time, the noise from the FB LNA is also fed to the source follower,  $M_3$ , where it is amplified with unity gain and non-inverting transfer to the output. The noise voltages, perfectly correlated since they originate from the same noise source, will cancel at the output if  $g_{m3} = g_{m2}/A_{v1}$ , where  $A_{v1}$  is the voltage gain of the shunt-shunt feedback input stage.

Figure 20: (a) Schematic of a noise-cancelling FB LNA. (b) Conceptual schematic of how the channel noise of the left CS stage is sensed by the right CS stage and then cancelled at the output.

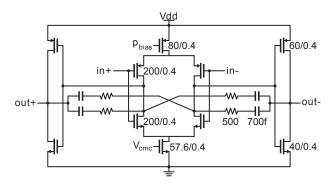

### 3.1.7 Noise Analysis of the FB LNA in Paper V

Paper V introduces a wideband single-ended to differential noise-cancelling FB LNA, and a simplified schematic is presented in figure 21(a). The amplifier consists of two parallel paths. The first path consists of an shunt-shunt feedback input stage to provide input match, and a second stage provides an output current and signal inversion. The total gain of this path is  $g_m = (1 - R_f/R_s)(-g_{m2})$ , where  $g_{m2}$  is the total transconductance from  $M_{n2}$  and  $M_{p2}$ . In the parallel second path, a  $g_m$ -stage with a total transconductance of  $g_{m3} = g_{mMn3} + g_{mMp3}$  is used, and the gain of this path can be selected to match that of the first path for balanced signals. The LNA is further simplified in figure 21(b) where the complementary structure is folded to an equivalent NMOS structure and the parallel output resistance of the devices in the input stage is replaced by  $R_L$ .

A nice feature of this LNA is that channel noise from  $M_1$  and noise from  $R_L$  can be cancelled. Assuming that these noise sources will cause a voltage at the output of the shunt-shunt feedback stage, this voltage will be amplified to the positive output by  $g_{m2}$ , but the voltage is also fed back to the input by the resistive voltage division of  $R_s/(R_s+R_f)$  and amplified to the negative output by  $g_{m2}$ . If (18) is met, noise is thus cancelled at the differential output.

$$\frac{g_{m3}}{g_{m2}} = 1 + \frac{R_f}{R_s} \tag{18}$$

The full expression of noise factor of the LNA (19) is calculated by analyzing figure 21(c) and assuming perfect common-mode suppression. It is possible to decrease the noise figure further by increasing the value of  $R_f$  beyond its optimum value for input matching.

3.2 Passive Mixer 27

Figure 21: (a) Schematic of the LNA in paper V. (b) Simplified schematic with folding. (c) Schematic for noise analysis.

$$F = 1 + \frac{4R_{f} (R_{L}g_{m2}(R_{s}g_{m1} + 1) + R_{s}g_{m3})^{2}}{R_{s} (R_{L}R_{s}g_{m1} + R_{L} + R_{f} + R_{s})^{2} \left(\left(1 - \frac{R_{f}}{R_{s}}\right)(-g_{m2}) + g_{m3}\right)^{2}} + \frac{4R_{L}^{2}\gamma g_{m1} \left((R_{f} + R_{s})g_{m2} - R_{s}g_{m3}\right)^{2}}{R_{s} (R_{L}R_{s}g_{m1} + R_{L} + R_{f} + R_{s})^{2} \left(\left(1 - \frac{R_{f}}{R_{s}}\right)(-g_{m2}) + g_{m3}\right)^{2}} + \frac{4R_{L} \left((R_{f} + R_{s})g_{m2} - R_{s}g_{m3}\right)^{2}}{R_{s} \left(R_{L}R_{s}g_{m1} + R_{L} + R_{f} + R_{s}\right)^{2} \left(\left(1 - \frac{R_{f}}{R_{s}}\right)(-g_{m2}) + g_{m3}\right)^{2}} + \frac{4\gamma g_{m3}}{R_{s} \left(\left(1 - \frac{R_{f}}{R_{s}}\right)(-g_{m2}) + g_{m3}\right)^{2}}$$

$$(19)$$

In paper V the main single noise contributor, accounting for 10 % of the total output noise power (including the noise from the source resistance which accounted for 75 %), was  $R_f$  and the total noise figure was simulated to below 1.6 dB.

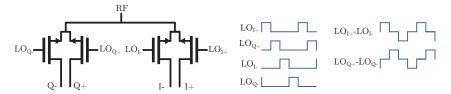

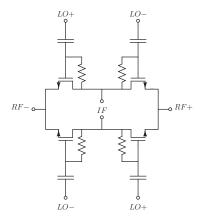

#### 3.2 Passive Mixer

The passive mixer usually consists of a number of CMOS switches that are controlled by square wave signals at a frequency of  $f_{LO}$  [54], figure 22. Usually, the LO signals are divided into N non-overlapping phases where each phase has a frequency of  $f_{LO}$  and a duty cycle of 1/N. Each of the square wave

Figure 22: Circuit implementation of a single-balanced passive mixer together with the LO signals.

signals can be seen as a pulse train and can be expanded into a Fourier series equivalent (20), with coefficients according to (21) for the periodic signal.

$$x(t) = a_0 + \sum_{n=1}^{\infty} a_n \cos(2\pi f t n) + \sum_{n=1}^{\infty} b_n \sin(2\pi f t n)$$

(20)

$$a_{0} = \frac{1}{T} \int_{-T/2}^{T/2} x(t)dt, \ a_{n} = \frac{2}{T} \int_{-T/2}^{T/2} x(t)cos\left(\frac{2\pi tn}{T}\right)dt$$

$$b_{n} = \frac{2}{T} \int_{-T/2}^{T/2} x(t)sin\left(\frac{2\pi tn}{T}\right)dt$$

(21)

Assuming the signal x(t) is an square wave signal, the coefficients becomes (22).

$$a_0 = 1/M, \ a_n = \frac{1}{M} sinc\left(\frac{\pi n}{M}\right), \ b_n = 0$$

(22)

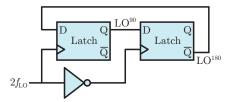

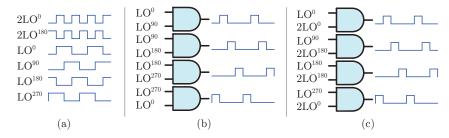

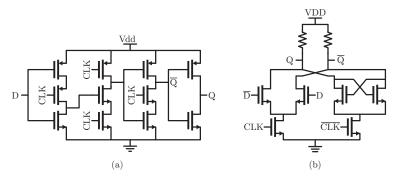

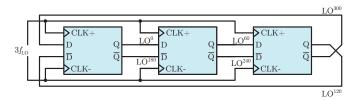

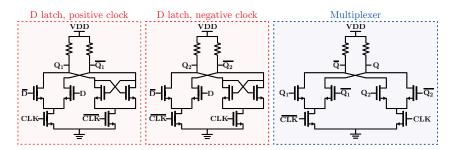

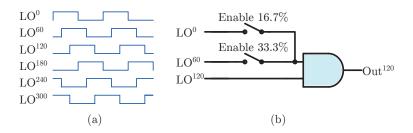

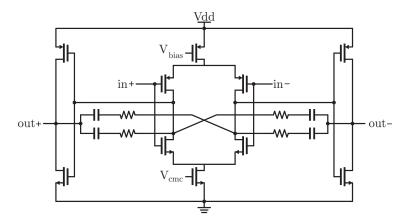

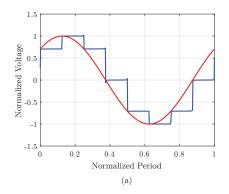

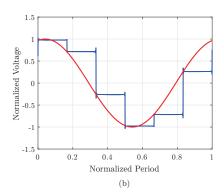

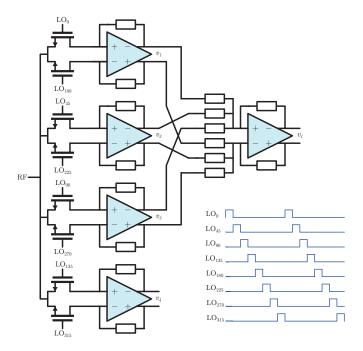

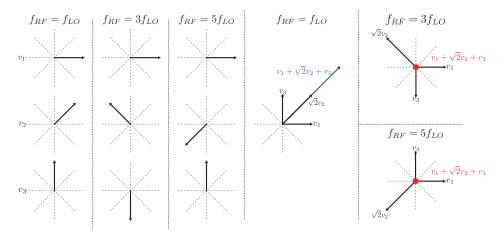

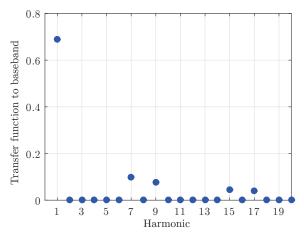

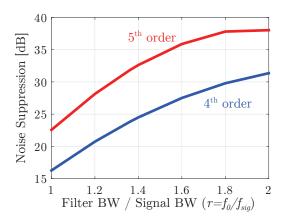

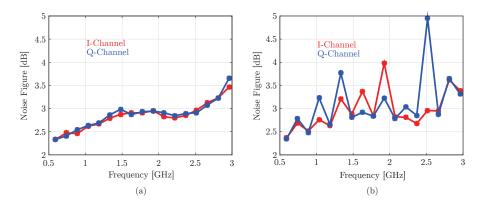

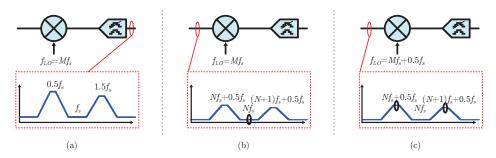

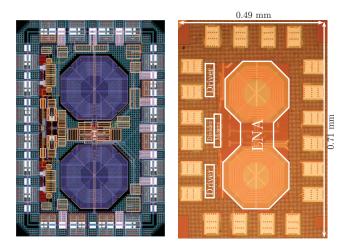

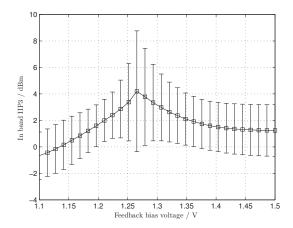

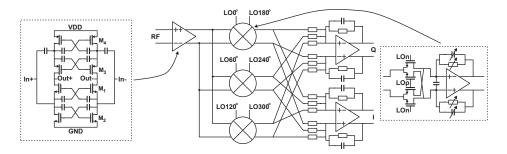

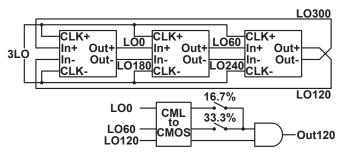

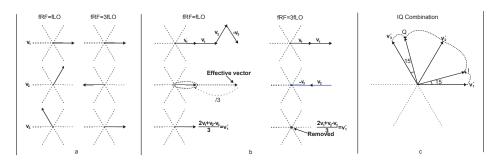

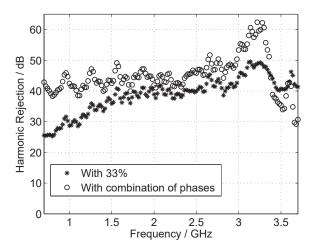

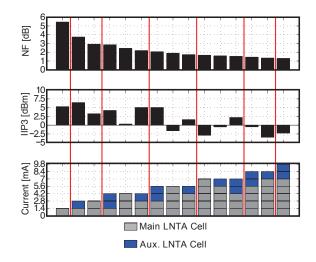

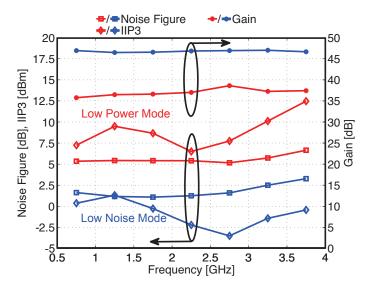

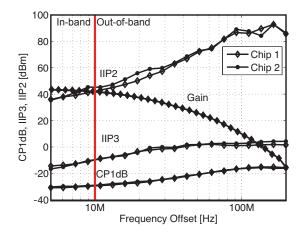

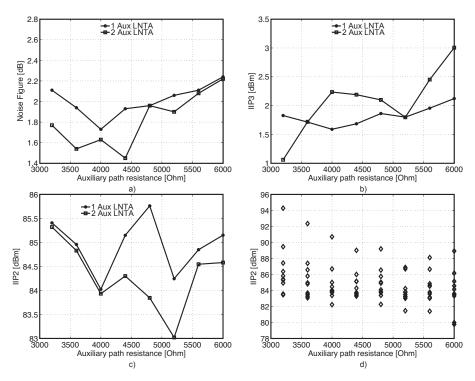

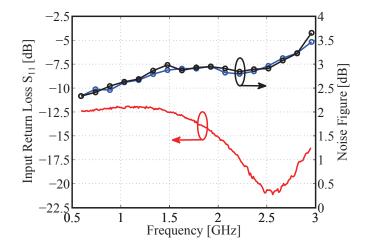

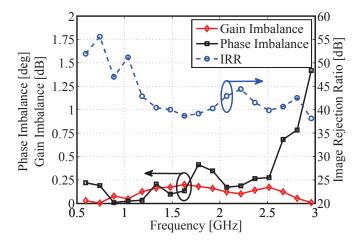

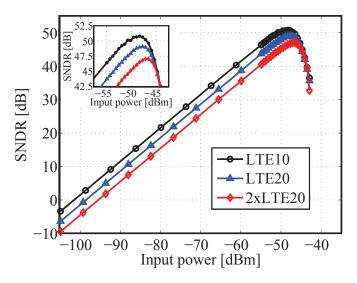

An input tone at frequency  $n \cdot f$  is multiplied with the coefficient  $a_n$  (the coefficient at  $n \cdot f$ ) and the resulting output tone resides at the difference, and at the sum, of the two frequencies. This, however, also means that noise at  $n \cdot f$  is down-converted to baseband as described in (8). The gain of the mixer of however described by the coefficient of the fundamental harmonic, i.e.  $a_1$ .