#### **Linearity Enhancements of Receiver Front-end Circuits for Wireless Communication**

Abdulaziz, Mohammed

2016

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Abdulaziz, M. (2016). *Linearity Enhancements of Receiver Front-end Circuits for Wireless Communication*. [Doctoral Thesis (compilation), Department of Electrical and Information Technology].

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

**PO Box 117** 221 00 Lund +46 46-222 00 00

**Doctoral Dissertation**

# Linearity Enhancements of Receiver Front-End Circuits for Wireless Communication

Mohammed Abdulaziz

Series of licentiate and doctoral dissertations

Department of Electrical and Information Technology

ISSN 1654-790X

No.82

ISBN 978-91-7623-693-2 (print)

ISBN 978-91-7623-694-9 (pdf)

http://www.eit.lth.se

# Linearity Enhancements of Receiver Front-End Circuits for Wireless Communication

# Mohammed Abdulaziz

Doctoral Dissertation Lund, May 2016

Department for Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

ISSN 1654-790X, no.82 ISBN 978-91-7623-693-2 (print) ISBN 978-91-7623-694-9 (pdf) Series of licentiate and doctoral dissertations.

© Mohammed Abdulaziz 2016. Produced using LaTeX Documentation System. Printed in Sweden by  $Tryckeriet\ i\ E$ -huset, Lund. May 2016.

# Abstract

Technology scaling in advanced CMOS nodes has been very successful in reducing the cost and increasing the operating frequency, however, it has also resulted in reduced transistor intrinsic gain and increased thermal noise coefficient, and most importantly, deteriorated linearity performance. At the same time, advanced wireless communication standards offer ever increasing data rates and pose more stringent requirements on coexistence, leading to very stringent linearity requirements.

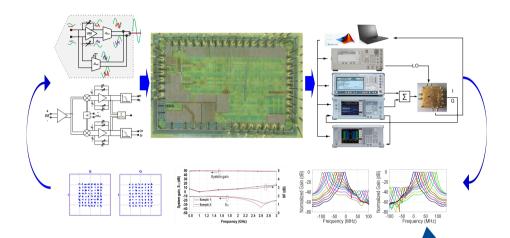

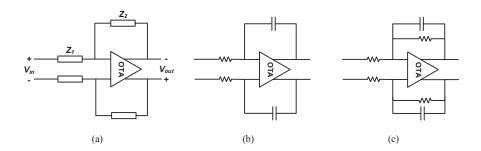

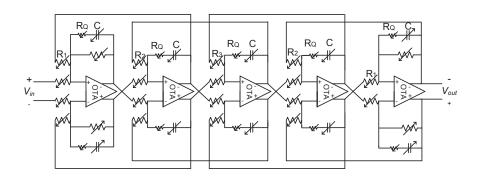

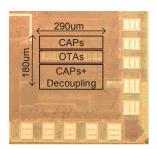

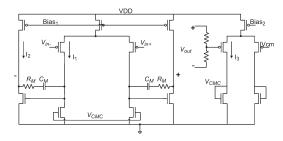

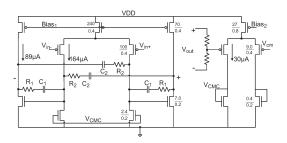

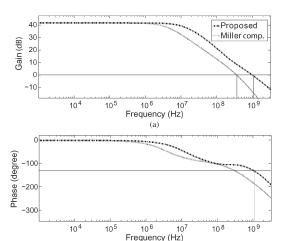

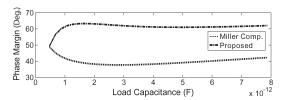

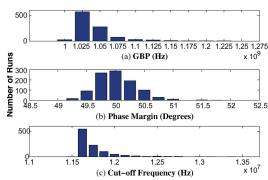

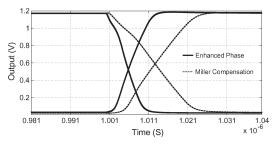

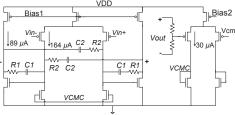

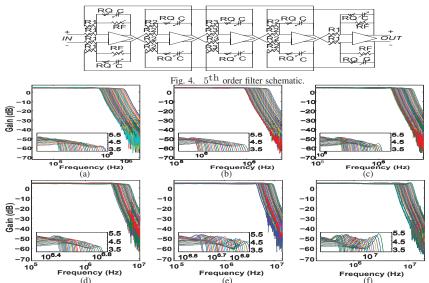

The objective of this dissertation is therefore to investigate techniques for enhancing the linearity of the receiver front-end in CMOS technology. The bandwidth of two-stage operational transconductance amplifiers (OTAs) in closed loop configuration is addressed in paper I and a compensation technique is proposed using positive feedback RC links. Analysis shows that this introduces two left hand plane zeros and two high frequency parasitic poles. In paper II the compensated OTA is used in a fifth order active-RC channel select filter (CSF) for LTE-Rel 8. The filter's power consumption measures only 3.4mW, and the linearity at the band edge and out-of-band is not deteriorated.

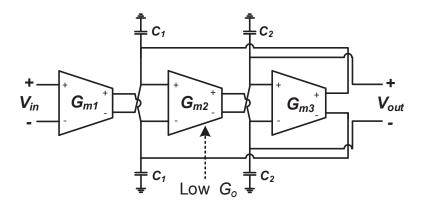

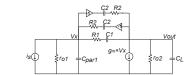

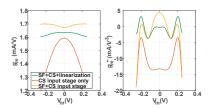

In paper III, the linearity of the well-known triode OTA with feedback amplifiers is investigated, and feedforward linearization is proposed instead of using feedback amplifiers. Not only are the amplifiers removed along with their power consumption, but also state-of-the-art linearity is achieved.

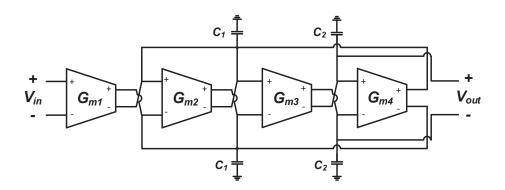

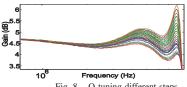

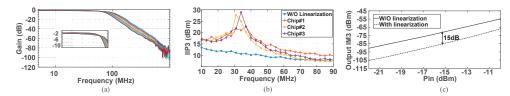

Paper IV proposes a novel linearization technique suitable for high frequency OTAs. The linearization draws no bias current and measurements show that it is robust to mismatch as well as temperature and voltage variations. A low noise amplifier is simulated and a fourth order OTA-C filter was measured, demonstrating the performance of the technique.

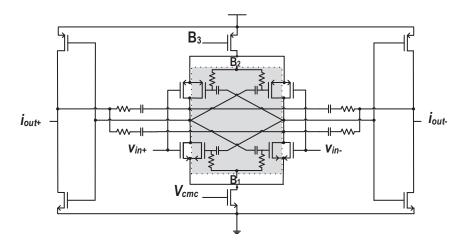

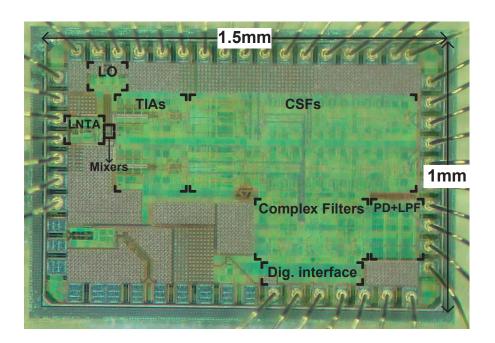

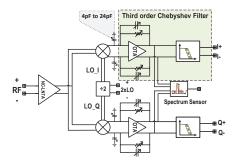

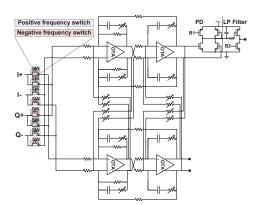

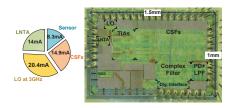

Finally, in paper V a fully integrated receiver front-end with spectrum sensing is presented, including measurements with LTE signals. Different blocker scenarios were measured and it is concluded that spectrum sensing is very beneficial for blocker handling, resulting in significantly improved performance. Furthermore, the effect of noise cancellation and improvements of the OTA linearity are demonstrated on the overall front-end performance.

# Populärvetenskaplig Sammanfattning

The consumer demands on the performance of high-end wireless handsets (e.g. smart phones) are ever increasing. A smart phone for example needs to be very fast at download and upload of data, at the same time it needs to be energy efficient, which is bench-marked by the time it can be used without the need of recharging the battery. Added to that, the phone user needs to be connected all the time, even in rural areas where signal is weak.

Next generation wireless standards must satisfy customer demands on speed, which is complicated by the band fragmentation. The cellular frequencies are divided between different operators, but the frequencies assigned to one operator are not necessarily close to each other. In other words, two contiguous channels don't necessarily belong to the same operator. This means that increasing the channel bandwidth requires special measures where several narrow channels are combined, called carrier aggregation. This will add to the complexity of the hardware.

To be able to integrate millions of transistors on the same chip performing advanced functions at high speed and low power consumption, extensive research is directed towards technology scale down. Unfortunately reducing the size of the devices also implies reducing the supply voltage, which directly limits the largest signal that can be linearly processed. Linearly processed means that the wanted signal is not distorted significantly. Therefore, technology scale down improves the operation speed and power consumption, but has negative impact on signal quality.

The linearity issue in advanced technologies is very challenging because distortion due to interfering signals appears and contaminates the desired signal due to nonlinearity. The strong signals can also saturate the receiver preventing reception of the wanted signal. This problem is similar to trying to listen to one talking while foghorn is sounding at the same time. Unless the one we want to listen to raises his/her voice or the other sound becomes quieter, it is very difficult to listen and understand.

In this dissertation, the problem of receiving weak signals in the presence of strong interference is addressed. Three channel select filters are designed and implemented with improved linearity, and a full receiver front-end for carrier aggregation with spectrum sensing is also implemented. These solutions are analyzed and simulated, and chips are fabricated and measured to verify the performance and compare to the analysis.

This work was supported by the Swedish foundation for strategic research (SSF) and the chips fabrication was sponsored by ST-Microelectronics.

# Contents

| Abstract                                 |                                                                                                                                                                                                                                                                                         | $\mathbf{v}$                                               |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Populärv                                 | retenskaplig Sammanfattning                                                                                                                                                                                                                                                             | vii                                                        |

| Contents                                 |                                                                                                                                                                                                                                                                                         | ix                                                         |

| Preface                                  |                                                                                                                                                                                                                                                                                         | xiii                                                       |

| Acknowle                                 | $\operatorname{edgments}$                                                                                                                                                                                                                                                               | $\mathbf{x}\mathbf{v}$                                     |

| List of A                                | cronyms                                                                                                                                                                                                                                                                                 | xvii                                                       |

| List of Sy                               | ymbols                                                                                                                                                                                                                                                                                  | xix                                                        |

| Introduc                                 | tion                                                                                                                                                                                                                                                                                    | 1                                                          |

| 1.1<br>1.2<br>2 The<br>2.1<br>2.2<br>2.3 | Motivation of the Work Outline of the Thesis  Cellular Radio Receiver The Homodyne Receiver Dynamic Range 2.2.1 Small Signal Performance 2.2.2 Receiver Linearity 2.2.3 Large Signal Performance Wide-Bandwidth Receiver Impairments 2.3.1 Image Rejection 2.3.2 Error Vector Magnitude | 1<br>1<br>3<br>5<br>5<br>6<br>7<br>7<br>7<br>9<br>10<br>10 |

| 3.1<br>3.2<br>3.3<br>3.4                 | eiver Circuit Implementations       LNAs         LNAs          3.1.1 Linearized LNA          3.1.2 Differential Noise Canceling LNTA          Mixers          LO Generation          The TIA          3.4.1 Loop Gain and Stability Analysis          3.4.2 Z <sub>in</sub> Analysis    | 15<br>15<br>17<br>18<br>20<br>21<br>22<br>23<br>26         |

| 4 OT 4.1 1 4.2                           | A Linearization and Filter Implementations  MOS Nonlinearity                                                                                                                                                                                                                            | 31<br>31<br>34<br>34                                       |

Contents

|       | 4.2.2 Derivative Superposition                                      |

|-------|---------------------------------------------------------------------|

|       | 4.2.3 Triode OTA                                                    |

|       | 4.2.4 Triode Multiplier Linearization                               |

|       | 4.2.5 Negative Feedback                                             |

|       | 4.2.6 Other Linearization Techniques                                |

| 4.3   | Channel Select Filter Architectures                                 |

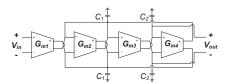

|       | 4.3.1 OTA-C Filters                                                 |

|       | 4.3.2 Active-RC Filters                                             |

|       | OTA Requirements                                                    |

|       | OTA Compensation                                                    |

|       | OTA Linearity                                                       |

|       | 4.3.3 Complex Active-RC Filters and Spectrum Sensors $$ .           |

| 5 Su  | mmary and Scientific Contribution of Included Papers                |

| 5.1   | Paper I: A Compensation Technique for Differential Two-             |

|       | Stage OTAs                                                          |

|       | Summary                                                             |

|       | Scientific Contributions                                            |

| 5.2   | Paper II: A 3.4mW 65nm CMOS 5 <sup>th</sup> Order Programmable      |

|       | Active-RC Channel Select Filter for LTE Receivers                   |

|       | Summary                                                             |

|       | Scientific Contributions                                            |

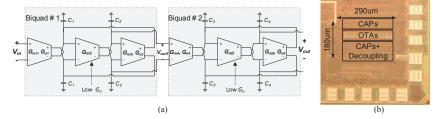

| 5.3   | Paper III: A 4 <sup>th</sup> Order Gm-C Filter with 10MHz Bandwidth |

|       | and 39dBm IIP3 in 65nm CMOS                                         |

|       | Summary                                                             |

| F 1   | Scientific Contributions                                            |

| 5.4   | Paper IV: A Linearization Technique for Differential OTAs           |

|       | Summary                                                             |

| 5.5   | Scientific Contributions                                            |

| 5.5   | ing                                                                 |

|       | Summary                                                             |

|       | Scientific Contributions                                            |

| 6 F   | ture Perspectives                                                   |

| ъ с   |                                                                     |

| Keter | rences                                                              |

| A Con | apensation Technique for Two-Stage Differen-                        |

|       | OTAs                                                                |

| _     | 1                                                                   |

| I A 3 | .4mW 65nm CMOS 5 <sup>th</sup> Order Programmable                   |

| Acti  | ve-RC Channel Select Filter for LTE Receivers                       |

Ι

Contents xi

| III A $4^{ m th}$ Order Gm-C Filter with 10MHz Bandwidth and 39dBm IIP3 in 65nm CMOS | 91  |

|--------------------------------------------------------------------------------------|-----|

| IV A Linearization Technique for Differential OTAs                                   | 99  |

| V A Cellular Receiver Front-End with Blocker Sensing                                 | 109 |

# **Preface**

This work was funded by SSF - the Swedish foundation for strategic research. In this dissertation my work as a PhD student is presented.

#### **Included Research Papers**

The main research activities, analysis, and results reported are from the papers attached at the end of this thesis and are listed below:

- [1] M. Abdulaziz, M. Törmänen, and H. Sjöland, "A Compensation Technique for Two-Stage Differential OTAs," *IEEE Transactions on Circuits and Systems—Part II: Express Briefs*, vol. 61, no. 8, pp. 594–598, Aug. 2014.

- [2] M. Abdulaziz, A. Nejdel, M. Törmänen, and H. Sjöland, "A 3.4mW 65nm CMOS 5<sup>th</sup> order programmable active-RC channel select filter for LTE receivers," in *RFIC*, Seattle, Washington, June 2–4 2013, pp. 217–220.

- [3] M. Abdulaziz, M. Törmänen, and H. Sjöland, "A 4<sup>th</sup> order Gm-C filter with 10MHz bandwidth and 39dBm IIP3 in 65nm CMOS," in *Proc. of* 40th IEEE ESSCIRC 2014, Venice, Italy, Sept. 22–26 2014, pp. 367–370.

- [4] M. Abdulaziz, W. Ahmad, M. Törmänen, and H. Sjöland, "A Linearization Technique for Differential OTAs," (Submitted).

- [5] M. Abdulaziz, W. Ahmad, A. Nejdel, M. Törmänen, and H. Sjöland, "A Cellular Receiver Front-End with Blocker Sensing," in *RFIC*, San Francisco, California, May 22–24 2016, (Accepted).

#### Related publications

I have also co-authored the following papers, which are not considered as a part of this dissertation.

- [6] W. Ahmad, M. Abdulaziz, A. Nejdel, M. Törmänen, and H. Sjöland, "CMOS Integrated Remote Antenna Unit for Fiber-fed Distributed MIMO Systems", (Submitted).

- [7] A. Nejdel, M. Abdulaziz, M. Törmänen, and H. Sjöland, "A Positive Feedback Passive Mixer-First Receiver Front-End," in RFIC, Phoenix, Arizona, May 17–19 2015, pp. 79–82.

- [8] W. Ahmad, M. Abdulaziz, M. Törmänen, and H. Sjöland, "CMOS Adaptive TIA with Embedded Single-Ended to Differential Conversion for Analog Optical Links," in *Proc. of IEEE International Symposium*

xiv Preface

- on Circuits and Systems, ISCAS'15, Lisbon, Portugal, May 24–May 27 2015, pp. 658–661.

- [9] R. Gangarajaiah, M. Abdulaziz, H. Sjöland, and L. Liu, "Digitally Assisted Adaptive Non-Linearity Suppression Scheme for RF front ends," in Proc. of 25th IEEE International Symposium on Personal, Indoor and Mobile Radio Communications, PIMRC'15, Washington DC, USA, Sept. 2–5 2015, pp. 623–627.

- [10] R. Gangarajaiah, M. Abdulaziz, H. Sjöland, P. Nilsson, and L. Liu, "A Digitally Assisted Nonlinearity Mitigation System for Tunable Channel Select Filters," *IEEE Transactions on Circuits and Systems—Part II: Express Briefs*, vol. 63, no. 1, pp. 69–73, Jan. 2016.

- [11] M. Abdulaziz, M. Shakir, P. Lu, and P. Andreani, "A 2.7GHz divider-less all digital phase-locked loop with 625Hz frequency resolution in 90nm CMOS," in *Proc. of 29th NORCHIP Conference*, Lund, Sweden, Nov. 14–15 2011.

- [12] M. Shakir, M. Abdulaziz, P. Lu, and P. Andreani, "A mixed mode design flow for multi GHz ADPLLs," in *Proc. of 29th NORCHIP Conference*, Lund, Sweden, Nov. 14–15 2011.

#### Patent applications

M. Abdulaziz, Waqas Ahmad, and Henrik Sjöland, "Amplifier, Filter, Communication Apparatus and Network Node", *International application* No. PCT/EP2015/072613, 2015

# Acknowledgments

I would like to acknowledge and express my sincere gratitude to all the people who helped and supported me during my studies.

First of all, to my supervisor Professor Henrik Sjöland: you are one of the most talented people I have seen in my life, technical discussions with you always shed the light on the matter. Your unique guidance and encouragement from idea development to manuscript thorough review are the key reason of the success of this project, you are also truly a very kind and caring person. Thank you for giving me the opportunity to pursue my PhD in Lund University, it was a great honor to work with you.

To my co-supervisor Associate Professor Markus Törmänen: for your continuous help and support, I have always knocked on your door uninvited and I was always welcome, thank you.

I would like to thank all the past and present colleagues in the RF group for the technical discussions and all friendly coffee breaks. Having you around always made the long working hours seem shorter. I would also like to thank all the colleagues in EIT department for creating such a friendly environment, especially, the digital ASIC group, the nano-electronics group, the mixed signal group, and the DARE project team headed by Professor Pietro Andreani who always was positive and open to new ideas. Also to Dr. Johan Wernehag for his technical help, reading parts of this thesis and for his kindness.

I had the chance to do a research visit at University of Twente in Netherlands, many thanks go to the friends in Twente: Professor Eric Klumprink for his very long and fruitful meetings, Professor Bram Nauta for giving me time and support that made the visit successful and Dr. Anne-Johan Annema. Also Gerdien Lammers for helping me with administrative matters. My gratitude extends to all the PhD students who gave me a very warm welcome and made me feel home, and Gerard Wienk in the CAD tools support.

I also would like to give special thanks to Dr. Lars Sundström from Ericsson research for giving me time to meet and discuss technical problems and taking the time to reply to my spam emails with very long and informative replies, and Göran Jönsson for his great help and patience in the lab and for allowing me to teach in his courses. Also the people involved in the technical support specially: Andreas Johansson for his great help in the lab and Erik Jonsson for keeping the systems up and running and fixing computer issues even at midnight, Bertil Lindvall, Stefan Molund for CAD tools support, Martin Nilsson for lab help and Lars Hedenstjerna. My gratitude extends to all the people involved in the administrative support, especially Pia Bruhn.

Finally, I would like to thank my family: my mother (Fathia), words could not describe how I feel about you, my father (Abdullah) you taught me everything I know. My wife (Ebtehal) for your limitless love, patience and support

and my wonderful son (Abood) you are the reason why I feel great about the future. My brother and best friend (Moneer) you have been the one everybody in the family depends on, thank you. My youngest brother (Hasan) and my sisters (Belqees, Sara, Amani). I would like also to acknowledge father-in-law (Ali), mother-in-low (Sayda), my friend and brother-in-low (Ahmed Al-ahsab), and Mohammed Al-kohlani. Also, to all my friends in Sweden, especially Essam, in Yemen and the ones scattered around the world. I did not mention many, so to all of you I say thank you.

In memory of Professor Peter Nilsson and Haj Abdullah Mayas.

Notarna Hood lot?

Our greatest weakness lies in giving up. The most certain way to succeed is always to try just one more time.

<sup>-</sup> Thomas A. Edison -

# List of Acronyms

ADC Analog-to-digital converter

ASIC Application specific integrated circuit

CA Carrier aggregation

CDS Complementary derivative superposition

CG Common gate

CML Current mode logic

CMOS Complementary metal oxide semiconductor

CS Common source

CSF Channel select filter

DC Direct current

DS Derivative superposition

EVM Error vector magnitude

FDD Frequency division duplex

GBP Gain bandwidth product

GE Gain error

I In-phase signal

ICP<sub>1dB</sub> Input referred 1dB compression point

IF Intermediate frequency

IIPn The n-th order input-referred intercept point

IMD Intermodulation distortion

IMn The n-th order intermodulation distortion

IP Intercept point

IPn The n-th order intercept point

IRR Image rejection ratioLNA Low noise amplifier

LNTA Low noise transconductance amplifier

LTE Long term evolution

MOS Metal oxide semiconductor

$\begin{array}{ccc} {\rm NC} & & {\rm Noise\ canceling} \\ {\rm NF} & & {\rm Noise\ figure} \end{array}$

OPAMP Operational amplifier

OTA Operational transconductance amplifier

PD Power detector

PLL Phase locked loop

PVT Process, voltage and temperature

Q Quadrature phase signal

QAM Quadrature amplitude modulation

RF Radio frequency

RX Receiver

SNR Signal-to-noise ratio

TF Transfer function

TIA Transimpedance amplifier

TX Transmitter

VCCS Voltage controlled voltage source VCO Voltage controlled oscillator

VGA Variable gain amplifier

# List of Symbols

W

$Z_{BB}$

```

A

Forward gain

A\beta

Loop gain

Voltage gain

A_v

C

Capacitance (F)

MOS transistor oxide capacitance per unit area (F/m<sup>2</sup>)

C_{ox}

The j<sup>th</sup> error vector in the received IQ symbol

e_j

Conductance (S)

g

Transistor transconductance (S)

g_m

G_m

OTA effective transconductance (S)

The n<sup>th</sup> order conductance (A/V^n)

g_n

Transistor output conductance (S)

g_o

Drain current (A)

i_D

The n<sup>th</sup> order intermodulation distortion (W)

IM_n

L

MOS transistor length (m)

L_{eff}

MOS transistor effective length (m)

L_{gyr}

Gyrator's inductance (H)

P_{avg}

Average received power (W)

P_{in}

Input power (W)

Q

Quality-factor

T

Temperature (K)

MOS drain-source voltage (V)

v_{DS}

MOS gate-source voltage (V)

v_{GS}

MOS transistor threshold voltage (V)

V_{th}

```

MOS transistor width (m) Base band impedance ( $\Omega$ )

- $Z_f$  Feedback impedance  $(\Omega)$

- $Z_{in}$  Input impedance  $(\Omega)$

- $Z_L$  Load impedance  $(\Omega)$

- $Z_o$  Output impedance  $(\Omega)$

- $\beta$  Feedback factor

- $\gamma$  The thermal noise coefficient

- $\Delta\theta$  Phase imbalance (°)

- $\epsilon$  Amplitude imbalance

- $\xi_h$  Horizontal electrical field (V/m)

- $\xi_v$  Vertical electrical field (V/m)

- $\theta$  Mobility reduction constant  $(V^{-1})$

- $\mu_n$  Average electron mobility in the channel (m<sup>2</sup>/(V·second))

- $\omega_o$  Angular resonance frequency (rad/second)

- $\omega_p$  Angular frequency of a pole (rad/second)

- $\omega_z$  Angular frequency of a zero (rad/second)

# Introduction

# Introduction

# Chapter 1

## Introduction

#### 1.1 Motivation of the Work

For battery operated consumer electronics, requirements on performance continue to expand in many dimensions. In particular, the high-end market demands have exploded. The number of wireless connectivity links as well as their data rates are ever increasing, while the power consumption must be low to increase the time between battery recharges. Most importantly, the consumer electronics market is cost driven, limiting the ASIC implementations to CMOS technology. To minimize the cost, today's radio frequency transceivers are pushed towards being integrated together with the digital base band ASIC. The number of expensive off-chip filters is also reduced [13–15], posing more stringent linearity requirements on the receiver front-end.

Recent wireless communication standards such as LTE-A are pushing towards higher data rates, which necessitates wider channel bandwidth. Added to that, simultaneous transmission and reception is also supported (also referred to as frequency duplex division (FDD)), resulting in a strong transmit signal at a small duplex frequency distance from the wanted signal. Due to the ever increasing channel bandwidth, the relative duplex distance decreases, resulting in stronger interference, further increasing the linearity requirements of the receiver front-end.

Unfortunately cellular band fragmentation limits the possibility of assigning contiguous frequency bands to the operators. As a result, intra-band non-contiguous carrier aggregation (CA) and inter-band CA are introduced. In this way several narrow band channels can be combined into a single effective wide-band channel. This significantly complicates the hardware implementation of the receiver front-end and requires more advanced digital signal processing. Especially non-contiguous CA is troublesome since a frequency gap exists between carriers which, belongs to a different operator and thus can contain strong in-

terference. A receiver front-end designed for contiguous and non-contiguous CA needs to have detailed information about which blockers are stronger, the in-gap or the out-of-band ones, motivating the need for spectrum sensing.

To be able to integrate more and more devices into a single ASIC, CMOS technology feature size has been continuously scaled down starting from a MOS device length (L) of several  $\mu$ m in 1960s, the device length is less than 20nm in today's most advanced technologies. Scaling has been very successful in reducing cost and adding more functionality. Driven by integration and speed, advanced CMOS technologies operate on reduced voltage supply and oxide thickness as well. All of this allows billions of transistors to be integrated into a single chip. Despite the great success in the performance of the scaled digital circuits, analog performance is in many cases heavily degraded. The increased vertical electrical field results in mobility reduction of the charge carriers and the horizontal electrical field results in carrier velocity saturation. As a result, the MOS devices in sub 100nm do not have square law characteristic anymore. This leads to increased distortion of the signal. Limited voltage headroom results in large signal compression which limits the maximum possible input signal and gain. At the same time, as mentioned, wireless communication trends put increasing requirement on receiver linearity.

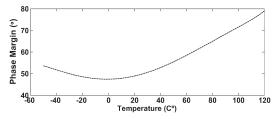

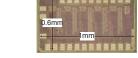

Apart from all mentioned challenges, process, voltage and temperature variations (PVT) of the circuits can result in significant shifts of their operating point. For this reason performance evaluation of the test circuits needs to be performed over supply and temperature variations (-20°C to 80°C). The fabricated chips in this dissertation did not include process variation, however, since it is a multi-project wafer run for universities and hence only one process corner is fabricated. Therefore process variations are instead extensively simulated.

MOS transistor nonlinearity limits the achievable receiver front-end performance. The two main sources of nonlinearity are the transconductance  $(g_m)$  and output conductance  $(g_o)$ , where circuit level linearization schemes need to be investigated. Linearization schemes must be robust to PVT variations to guarantee required performance under all operating conditions. As a system level technique, spectrum sensing is powerful as it provides the information needed to perform the required steps that result in optimal performance.

This dissertation is focused on the challenges faced when designing receiver front-ends for 4G cellular (LTE) applications. The main emphasis is on techniques enhancing the linearity when implementing such demanding functionality in CMOS technology. Improvement in operational transconductance amplifier (OTA) closed loop speed is investigated. OTA linearization techniques implemented in OTA-C channel select filters (CSFs), low noise amplifiers (LNAs), and feedback amplifiers are presented. Added to that, a complete receiver front-end with fully integrated spectrum sensing to detect blocker amplitude and frequency is also described.

#### 1.2 Outline of the Thesis

The dissertation started by motivating the need for linearity improvements in wireless receiver front-ends. Then the widely used homodyne receiver architecture will be described. Next, the most important performance metrics will be briefly explained, followed by circuit-level building blocks. Finally, OTA linearization techniques and CSF implementations will be described. The organizations of this thesis is as follows:

- Chapter 1 includes motivation of the work and describes major challenges of the art.

- Chapter 2 presents an introduction to high performance receiver front-ends and their key performance metrics. An overview of the performance, properties and the building blocks of cellular receiver front-ends will be provided.

- Chapter 3 describes circuit-level receiver front-end building blocks.

- Chapter 4 describes active filters and OTA linearization techniques. CSFs as well as complex filters and spectrum sensing are treated.

- Chapter 5 provides a summary of the included papers, including conclusions and scientific contributions of each paper.

- Chapter 6 is a discussion about possibilities of future work.

- **Paper I** introduces the phase enhanced compensation technique for two-stage OTAs. Detailed analysis and simulations are presented to evaluate the performance and robustness of the technique.

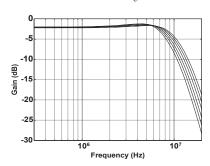

- Paper II presents an implementation of a tunable 5<sup>th</sup> order CSF with OTAs compensated using phase enhanced compensation. The performance benefits of the phase enhanced compensation technique are demonstrated by the measurement results of the filter.

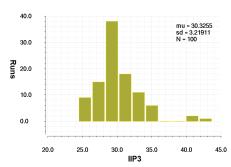

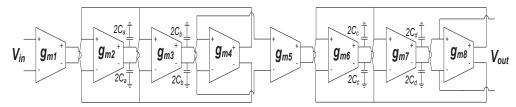

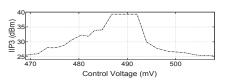

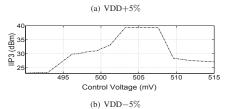

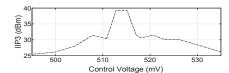

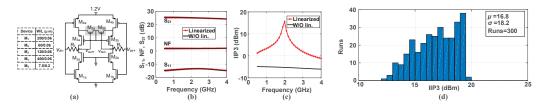

- Paper III reports the design and measured results of a highly linear 4<sup>th</sup> order OTA-C filter. In this case triode OTAs are used with capacitive feed forward for nonlinearity cancellation. Mismatch simulations, and temperature and voltage variation measurements are provided.

- Paper IV introduces a nonlinearity cancellation scheme using a triode multiplier: a circuit that generates the second order nonlinearity of the input signal, which is effectively multiplied by the signal to generate and cancel the third order nonlinearity. Simulations of a wide-band LNA and measurements of a high frequency OTA-C filter are included.

Paper V presents a highly configurable receiver front-end supporting LTE-Rel. 11 [16] CA scenarios. Low noise figure is achieved thanks to a noise canceling low noise transconductance amplifier (LNTA) and high linearity is achieved thanks to a fully differential structure and a base band linearization technique. Measurements show that spectrum sensing is very beneficial to be able to counteract the effect of large interference.

# Chapter 2

# The Cellular Radio Receiver

Many different receiver architectures have been proposed over the last century [17–20]. Currently the homodyne receiver<sup>1</sup> is widely adopted due to its simple architecture and high level of integration. In this chapter the homodyne architecture is therefore described. A brief introduction to the most important quality metrics of receivers will also be provided.

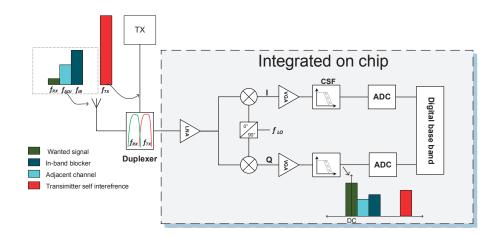

### 2.1 The Homodyne Receiver

The homodyne receiver block diagram is shown in Fig. 2.1. The signal received by the antenna contains the wanted signal at frequency  $f_{RX}$ , accompanied by adjacent channel and in-band interference signals close in frequency to the wanted signal. In communication standards such as LTE and WCDMA, FDD is supported, implying concurrent operation of the transmitter (TX) and receiver (RX). For this reason the antenna is interfaced with a duplex filter to provide isolation of RX from TX. Commercial duplexers for cellular terminals provide an isolation of about 50dB [21,22]. The remaining, still large TX selfinterference together with the received signal are then amplified by the LNA and down converted by the quadrature mixer. After the quadrature mixer the wanted signal, centered at the local oscillator frequency  $(f_{LO})$  before down conversion, is represented as two quadrature base band signals having a bandwidth equal to half the radio frequency (RF) signal bandwidth. The channel selection can thus be performed by low pass filters, suppressing interfering signals which will be located at higher frequencies. A variable gain amplifier (VGA), usually with first order filtering, is used to adapt the RX gain for optimal dynamic range together with the CSF and analog to digital converter (ADC). The CSF attenuates the interference signals further to relax the requirements of the ADC.

<sup>&</sup>lt;sup>1</sup>also known as the direct conversion receiver

Figure 2.1: Block diagram of the homodyne receiver.

#### 2.2 Dynamic Range

The signal received by the antenna contains both the wanted signal and interference. The far out-of-band interference is heavily attenuated by the duplex filter, leaving in-band interference and the attenuated TX signal. When TX is transmitting maximum power (close to 30dBm), TX signal at the RX input is close to -20dBm. This is likely to occur far from the base station, at the cell edge. The wanted signal is then very weak<sup>2</sup>, further worsening the situation. Large interferers are also expected in-band (LTE-Rel. 11 specifies -25dBm interference [16]).

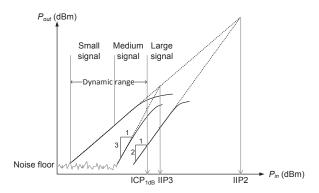

The signal and interference received can be one of three levels, small, medium, or large. Small signals will not give rise to any intermodulation distortion (IMD) products above the noise floor, in which case the performance is noise limited and more gain is desirable. Medium signals on the other hand will cause IMD products that, depending on their frequencies, may degrade the signal-to-noise ratio (SNR), in which case the gain must be reduced. Large signal levels will force the system into compression unless the gain and sensitivity are sacrificed. The effect of the different input signal levels on the receiver front-end results in corresponding performance:

- Small signal performance including sensitivity and selectivity.

- Medium signal performance related to the nonlinear behavior of the circuits, which is measured using intercept points (IP).

$<sup>^2{\</sup>rm the}$  reference sensitivity in LTE-Rel. 11 is from -96dBm to -92dBm

• Large signal performance including clipping, slewing and reciprocal mixing. This is measured by desensitization in different scenarios

#### 2.2.1 Small Signal Performance

The most important small signal performance metrics are sensitivity and selectivity. The noise performance of an RX chain is often reported using the noise figure (NF), which is defined as:

$$NF = 10\log(\frac{SNR_{in}}{SNR_{out}}) \tag{2.1}$$

where  $SNR_{in}$  and  $SNR_{out}$  are the input and output SNR, respectively. Since there are several stages in the RX chain, Friis formula [23] can be used to calculate the system NF (NF<sub>sys</sub>) as:

$$NF_{sys} = 10\log(F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1G_2} + \frac{F_4 - 1}{G_1G_2G_3} + \dots)$$

(2.2)

where  $F_n$  is the noise factor (the linear value of the NF) of the n<sup>th</sup> stage and  $G_n$  is the available power gain of that stage. Often in integrated designs, matched internal impedances are not used, therefore input noise voltage and voltage gain are used instead. Just like in (2.2), however, the result is that the first stage, the LNA, is the most important. It is seen from (2.2) that receiver NF is dominated by the LNA, given that it has sufficient gain. In modern RX chips, not only the VGA gain but also the LNA gain can be programmable to handle difficult blocking scenarios and achieve high sensitivity. In all cases the system gain should be high enough to ensure that the wanted signal is amplified and brought into the signal level range that the ADC can process.

Selectivity is a major small signal performance metric since receivers are wide-banded. The selectivity of a radio receiver is defined as the receiver ability to select the wanted signals and reject the other undesired ones. For homodyne receivers, further filtering is required after the duplex filter, see Fig. 2.1. The signal is down converted to base band, therefore low pass filters are used for channel selection for both I and Q signal paths. CSFs considerably relax the dynamic range requirements of the ADCs, which then don't have to process strong interference after filtering.

#### 2.2.2 Receiver Linearity

Linearity is the main bottleneck in today's low cost RX chips, which is a result of the CMOS technology scaling. The linearity performance is measured at medium signal levels, i.e. the system is not driven into compression, but significant intermodulation distortion is generated.

Figure 2.2: Intercept diagram with dynamic range illustration.

Input-referred intercept points (IIP) are used to characterize the linearity of the receiver and its building blocks. The second and third order IIP (IIP2 and IIP3) are widely used to bench-mark the linearity performance. Two-tone tests can be performed to simulate or measure IIP. For IIP2 two closely spaced sinusoidal signals with equal power level  $P_{in}$  at frequencies  $f_1$  and  $f_2$  are applied, and the level of the second order IMD (IM2) at frequency  $|f_1 - f_2|$  is then observed as  $P_{in}$  increases. The frequencies are chosen such that the intermodulation product falls inside the received signal band. The IIP2 is the level where the interpolation of  $P_{out}$  equals that of  $P_{IM2}$ , see Fig. 2.2. For IIP3 the IM3 component at  $2f_1 - f_2$  or  $2f_2 - f_1$  is instead observed, at the receiver output down converted by  $f_{LO}$ .

Higher order IIP can be relevant if the interference levels are high. The IIPn value can be calculated using one measured value (extrapolation point) of IMn by

$$IIPn = \frac{nP_{in} - IIMn}{n - 1} \tag{2.3}$$

where n is the order of the nonlinearity. It is, however, important to ensure that the point of extrapolation is located on a slope of n line in the intercept diagram.

The IIP2 and IIP3 curves are illustrated in an intercept diagram in Fig. 2.2. It is seen that the IMn term has a slope that is proportional to n. The IIP2 is higher than IIP3 if differential structures are adopted, as the differential circuits provide IM2 cancellation. Some mismatch is, however, always present, making the IIP2 finite but high. Differential structures are therefore adopted for all the works in this dissertation, in single ended implementations, however, IIP2 is usually lower than IIP3.

Considering an amplifier with soft nonlinearity, a Taylor series expansion

can be used to describe its transfer characteristics. Since medium signal levels and soft nonlinearity are assumed, a third order polynomial can be used

$$Y = g_0 + g_1 X + g_2 X^2 + g_3 X^3 (2.4)$$

where X is the input signal, Y is the output signal, and  $g_n$  is the  $n^{th}$  order coefficient. Letting  $X = Acos(\omega_1 t) + Acos(\omega_2 t)$  in a two-tone test, one can calculate the IIP2 and IIP3. The IIP2 is the value of A that will make the IM2 level equal to that of the fundamental tone. The IIP2 becomes

$$IIP2 = \frac{g_1}{g_2} \tag{2.5}$$

Performing similar calculations for IIP3 results in

$$IIP3 = \sqrt{\left|\frac{4g_1}{3g_3}\right|} \tag{2.6}$$

#### 2.2.3 Large Signal Performance

A fundamental limitation on the maximum signal that can be received is amplifier saturation, which is aggravated by the limited voltage headroom in deep submicron CMOS technologies. The input referred 1dB compression point (ICP<sub>1dB</sub>) is commonly used to compare the large signal performance of receiver front-ends. ICP<sub>1dB</sub> is defined as the power level where the gain is reduced by 1dB compared to the small signal case. Gain compression can result from a large wanted signal, which can be solved easily by gain reduction in the RX chain. If gain compression on the other hand results from large blockers, more actions are required. Still, in some situations with strong blockers and a weak wanted signal, reception may be interrupted. Fig. 2.2 shows the three different input power regions, indicating the gain compression at high levels of  $P_{in}$ .

Considering up to third order nonlinearity to dominate, and assuming a compressive behavior, the  $ICP_{1dB}$  can be calculated as [24]

$$ICP_{1dB} = \sqrt{\left|\frac{4g_1}{3g_3}\right|}\sqrt{0.11} = IIP3 - 9.6dB$$

(2.7)

It is seen in (2.7) that the ICP<sub>1dB</sub> is 9.6dB lower than IIP3. This relation holds for many circuits. However, if linearization techniques are employed to improve IIP3, the improvement in IIP3 does not imply improvement in ICP<sub>1dB</sub>, because signal compression is limited by the voltage headroom. Therefore medium signal linearization techniques can improve IIP3 considerably, but ICP<sub>1dB</sub> remains unchanged. A survey of common techniques that help improving the amplifier linearity is reported in [24].

Another issue related to large signals is reciprocal mixing which occurs in the presence of strong out-of-band blocker. This issue is due the non-ideal LO signals driving the mixers which also contain phase noise. Since phase noise appears as skirts around the LO tone, phase noise mixing with the strong out-of-band blockers produces noise in-band. Therefore, depending on the level of phase noise in the LO signals and the out-of-band blockers, the receiver desensitization increases.

#### 2.3 Wide-Bandwidth Receiver Impairments

Wider and wider channel bandwidths are necessary as higher data rates are supported in advanced communication standards. The increased bandwidth results in more stringent blocking requirements, because the relative frequency distance between the blocker and the wanted signal is reduced. Added to that, with their increased frequency separation the in-band signals will experience different path losses. This calls for increased quadrature accuracy of the LO generation, mixer, and base band circuits of the homodyne receiver. Increasing the requirement of the image rejection ratio (IRR).

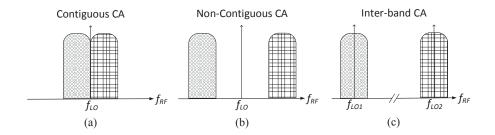

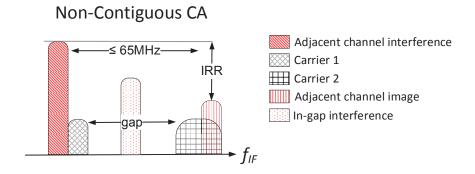

Moreover, CA concept has been introduced, where more than one carrier is received simultaneously. For LTE specifications [16] the different CA scenarios are illustrated in Fig. 2.3. Contiguous CA, Fig. 2.3(a), makes the design of the receiver front-end straight forward. If the LO frequency is placed at the center, between the carriers, out-of-band blockers remain the only ones that need to be dealt with. Non-contiguous CA, Fig. 2.3(b), on the other hand is more difficult to handle since the gap between the carriers can contain interference. Added to that, adjacent channels that have higher amplitude (an LTE test case assumes 25.5dB higher) than the wanted signal can fall on the image frequency of the carrier 2, see Fig. 2.4. The requirements, besides high out-of-band linearity, are high in-band linearity and very high IRR. The inter-band CA scenario, Fig. 2.3(c) requires two parallel receiver chains if the bands are widely spaced in frequency. Each receiver chain is conventional, but great care must be taken in the design of the LO generation circuitry to avoid disturbances due to unwanted interaction.

#### 2.3.1 Image Rejection

The homodyne receiver has inherently image rejection. The image rejection is the ability to distinguish a signal coming from a positive offset frequency from the LO from one coming from the same but negative offset. In a homodyne receiver an in-band frequency component always has a corresponding in-band frequency component (image) at the opposite sign offset frequency, i.e. the image falls in-band. To be able to distinguish between positive and negative frequencies in the wanted signal, and hence provide image rejection, quadra-

**Figure 2.3:** CA scenarios (a) contiguous, (b)non-contiguous, and (c) inter-band.

Figure 2.4: Image problem in LTE non-contiguous CA scenario.

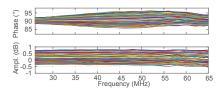

ture down conversion is used. It can be shown that perfect image rejection is achieved for perfect quadrature, i.e. exactly 90° phase shifted LO signals and identical gain in I and Q signal paths. Mismatches in the circuitry will, however, introduce phase and amplitude errors. The resulting IQ imbalance contains base band frequency independent errors which are usually due to mismatches in the mixers and LO generation, and base band frequency dependent errors due to mismatch between the CSFs bandwidth. The IQ imbalance results in power from the image frequency to leak on top of the wanted signal. The IRR is defined as the ratio of the gain for the wanted signal to the gain for the image signal. IRR can be derived as

$$IRR = \frac{(1+\epsilon)^2 + 2(1+\epsilon)cos(\Delta\theta) + 1}{(1+\epsilon)^2 - 2(1+\epsilon)cos(\Delta\theta) + 1} \approx \frac{4}{\epsilon^2 + \Delta\theta^2}$$

(2.8)

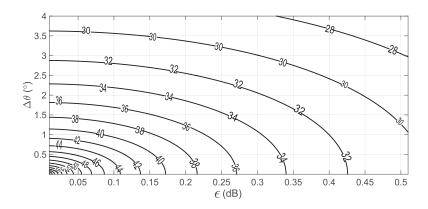

Figure 2.5: Contour of IRR vs. phase and amplitude errors.

where  $\epsilon$  is the IQ gain error and  $\Delta\theta$  is the phase error in radians. Fig. 2.5 shows IRR contours in the error plane using (2.8). As can be seen an IRR of 40dB can be achieved e.g. by a 1° phase error and an 0.1dB gain error.

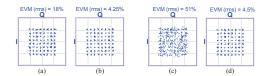

## 2.3.2 Error Vector Magnitude

Receiver front-ends are complex systems and many performance metrics are used to measure different non-ideal behaviors, however, this often results in limited insight into the overall receiver performance. For this reason there is a need for overall performance measurements in realistic scenarios.

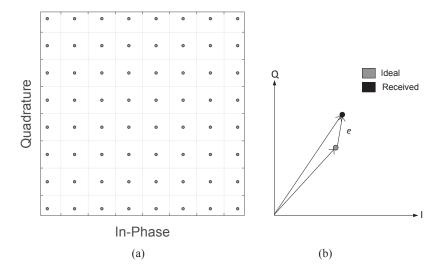

Signal constellation diagrams are used to plot all the target values of the I and Q signals. For example 64 quadrature amplitude modulation (64-QAM) is shown in Fig. 2.6. The non-idealities of the circuitry will shift the points in Fig. 2.6 from the ideal target values. Different non-idealities will have different impact on the constellation points. For example, LO phase noise will cause the points to move along an arc with a size proportional to the phase noise level and the distance from the origin. Thermal noise will randomly move the constellation points creating circular clouds. IMD terms falling in the signal band, similar to noise, will also result in corruption of the demodulated signal. The performance of the receiver front-end with all non-idealities in the signal chain can be evaluated using the error vector magnitude (EVM).

EVM is the magnitude of the vector difference between the received symbol and the ideal symbol, divided by the received average power  $(P_{avg})$ , see Fig. 2.6. The average EVM is used to evaluate the performance of the receiver and it is

**Figure 2.6:** (a) 64-QAM constellation diagram, (b) EVM measurement illustration.

given by (2.9)  $EVM_{avg} = \frac{\sum\limits_{j=1}^{N}|e_{j}|^{2}}{NP_{avg}} \tag{2.9}$

where N is the number of IQ symbols received, and e is the error vector, see Fig. 2.6(b).

# Chapter 3

# Receiver Circuit Implementations

In this chapter circuit level building blocks for receiver front-ends are introduced. It starts with different LNA topologies in section 3.1. Then the passive mixer is briefly explained in section 3.2. Frequency dividers are described in section 3.3, then the base band OTAs are introduced and the transimpedance amplifier (TIA) configuration is discussed in section 3.4.

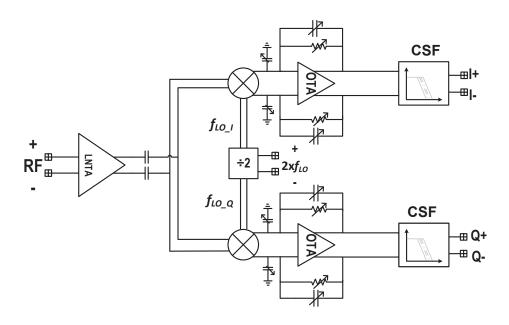

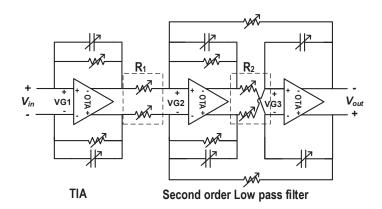

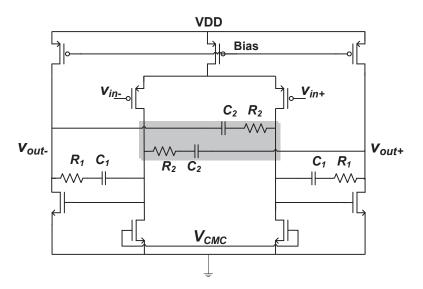

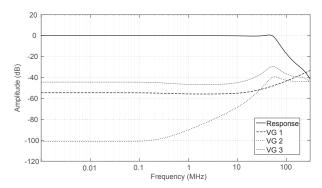

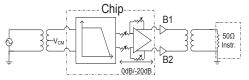

This chapter focuses on receiver front-ends operating in current domain, however, voltage domain receiver front-ends have a similar architecture except for the TIA, which is then replaced by a voltage amplifier, and the LNTA which is replaced by an LNA. The current mode receiver front-end is shown in Fig. 3.1. The output current is down converted to base band using mixers, and the capacitor at the mixer output sinks high frequency out-of-band signal current. The base band currents from the mixers are converted into voltage signals using TIAs, which also provides first order filtering. The main advantage with the current mode configuration is that the LNTA and mixer signal voltage swings are small, making the receiver front-end more linear and capable of handling larger signals.

# 3.1 LNAs

The LNTA in a current mode receiver front-end is an LNA whose output is intended to be connected to a low impedance. The design of the LNTA is crucial as it is the most important block in determining the sensitivity of the receiver front-end. The LNTA also provides an input match to the duplexer, which is important as the duplexer needs to see the correct impedance to perform as expected. Furthermore, the linearity of the receiver front-end is determined by the LNTA for out-of-band blockers.

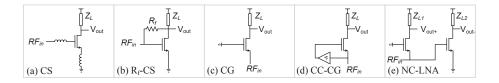

In literature, various LNA implementations are proposed (e.g. [25–29]). Fig. 3.2 shows frequently used topologies: common gate (CG), cross coupled common gate (CC-CG) [26], common source with inductive degeneration (CS), shunt feedback common source ( $R_f$ -CS), and the noise canceling common gate common source (NC-LNA) [27].

Figure 3.1: Current mode receiver front-end architecture.

Figure 3.2: Different LNA topologies.

All the LNA configurations in Fig. 3.2 can be used as LNTAs, except for the  $R_f$ -CS. The reason is that the input impedance of the  $R_f$ -CS LNA ( $Z_{in}^{LNA}$ ) is strongly dependent on the load impedance. Using the simple  $\pi$  transistor model (found in e.g. [30]) and ignoring the reactive elements for simplicity,  $Z_{in}^{LNA}$  becomes

$$Z_{in}^{LNA} = \frac{R_f + Z_L}{g_m Z_L + 1} \tag{3.1}$$

It is seen in (3.1) that if the output of the LNA is connected to low impedance (effectively making  $Z_L$  low) then  $Z_{LNAin} \approx R_f$ . Then choosing  $R_f$  for matching (50 $\Omega$ ) will result in poor NF. The input impedance of CG LNAs is also

3.1 LNAs 17

Table 3.1: Comparison of different LNA topologies.

|           | _  |           |    |       |     |

|-----------|----|-----------|----|-------|-----|

| Parameter | CS | $R_f$ -CS | CG | CC-CG | NC- |

|           |    |           |    |       | LNA |

| RF range  | Р  | G         | G  | G     | M   |

| Noise     | G  | M         | Р  | M     | G   |

| Linearity | M  | M         | G  | G     | M   |

| Current   | M  | M         | G  | G     | P   |

G=good, M=medium and P=poor

dependent on the load, fortunately the effect is less dominant than in  $R_f$ -CS LNAs.

The key performance metrics for LNAs are NF, input matching (which is quantified by  $S_{11}$ ), frequency range, power consumption, linearity, chip area and power consumption. In Table 3.1 a rough performance comparison of different LNA topologies is presented. It can be seen that an LNA that has low NF, high linearity, wide input match and RF frequency range, and consumes low power is a myth. For this reason a lot of research is performed to improve the overall performance of LNAs, especially on improving the linearity of receiver front-ends and achieve blocker resilience, see e.g. works published in [31–35]. However, with the increased channel bandwidths, the LNA linearity is becoming less and less dominant, and instead the base band circuity is becoming the linearity bottleneck. This is due to the increasing base band frequencies, which leads to reduced loop gain in the base band amplifiers and the ever reducing frequency ratio between the 3dB bandwidth and blockers, causing less blocker attenuation at the base band, so that close out-of-band interference may easily saturate the base band amplifiers.

# 3.1.1 Linearized LNA

Using CMOS technology, complementary devices in push-pull configuration is attractive. The transconductance is then doubled leading to reduced current consumption. Furthermore, the output voltages do not exceed the supply voltage which is beneficial for reliability in nanometer CMOS technologies. Cascode devices are also used to increase the reverse isolation  $(S_{12})$  and gain. Unfortunately, to function properly cascode devices require a voltage drop, reducing the signal headroom and thereby also the linearity.

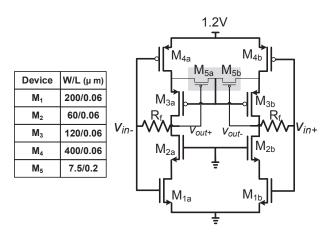

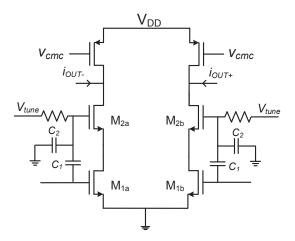

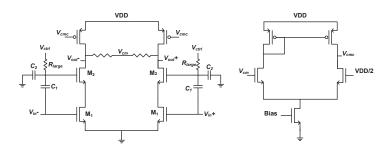

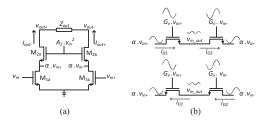

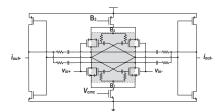

A differential complementary  $R_f$ -CS LNA with linearization is shown in Fig. 3.3 (from paper IV [4]). The devices  $(M_5)$  form a second order distortion generator whose output is connected to the gate of the cascode devices  $(M_3)$ . The cascodes  $(M_3)$  act as source followers and the drain of  $(M_4)$  is thus modulated by the second order term. Multiplication in  $M_4$  then results in third order nonlinearity cancellation as described in paper IV.

Figure 3.3: Shunt feedback LNA with linearization (biasing is omitted).

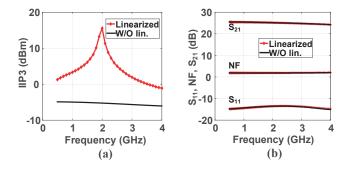

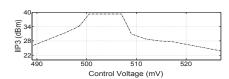

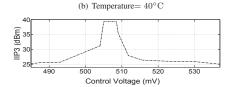

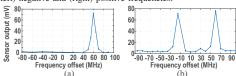

**Figure 3.4:** Simulation of the LNA (a) IIP3, (b)  $S_{21}$ ,  $S_{11}$ , and NF.

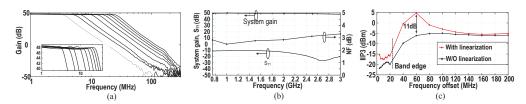

A simulation of IIP3 with linearization enabled/disabled is shown in Fig. 3.4(a). It can be seen that the IIP3 is increased significantly by the linearization, while the NF,  $S_{11}$ , and gain  $(S_{21})$  remain unaffected, see Fig. 3.4(b).

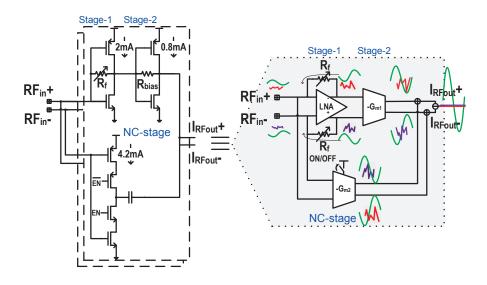

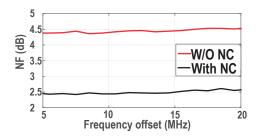

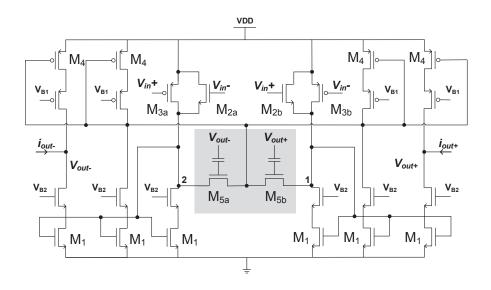

## 3.1.2 Differential Noise Canceling LNTA

To be able to use the  $R_f$ -CS in a current mode receiver front-end, a first  $R_f$ -CS amplifying stage must be followed by a second transconductance stage. Noise cancellation functionality can also be added using an auxiliary CS stage path with a gain that matches that of the main path.

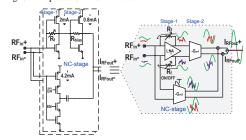

Shown in Fig. 3.5 is the differential noise canceling LNTA used in paper V [5]. Noise cancellation is achieved since the noise at the output of stage-1 is

3.1 LNAs 19

Figure 3.5: Schematic and block diagram of the noise canceling LNTA.

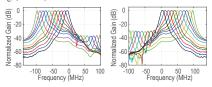

Figure 3.6: Measured NF of the receiver front-end in [5] at base band.

fed back through  $R_f$  and then amplified by the noise canceling stage. At the output the noise from the two paths will be in anti-phase. If the gain of the noise canceling-stage matches that of stage-1 and stage-2, optimal cancellation occurs. The noise canceling path can be turned off if high sensitivity is not required, resulting in 60% less current consumption. The measured NF of the receiver front-end at base band output is reported in paper V [5], see Fig. 3.6. It can be seen that when noise cancellation is activated the NF is reduced by 2dB.

The linearity of this noise canceling LNTA is limited by the  $R_f$ -CS stage, since it has a substantial voltage gain. For this reason, the use of cascode devices was avoided to obtain maximum output voltage swing.

Figure 3.7: Double balanced passive mixer with a capacitive load.

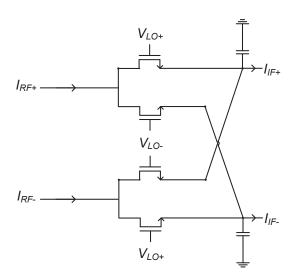

# 3.2 Mixers

The mixer multiplies the RF input signal with the LO signal to get frequency translation (down conversion for receivers). There are, two main types of MOS mixers, the first is the active mixer which can provide conversion power gain, and the second is the passive mixer which uses the MOS devices as switches. Description of active mixer properties can be found in literature (e.g. [36–38]).

Despite some unattractive properties of passive mixers, such as requiring large LO signal amplitudes, and having significant signal power loss resulting in poor NF, they are widely used in high performance transceiver chips. This is because they offer unique advantages such as high linearity and close to zero flicker noise as no DC current passes through the transistors. Passive mixers, double balanced version shown in Fig. 3.7, also offer an attractive property of impedance frequency up conversion. Since the passive mixer is a bidirectional time variant circuit, driving it with an RF current, the voltage at the RF input of the mixer is for frequencies around the LO signal shaped by the base band impedance  $(Z_{BB})$ . This means that  $Z_{BB}$ , translated in frequency by  $f_{LO}$ , is directly seen at the output of the LNTA [39,40]. A capacitive load of the mixer will then result in pass band filtering at RF, which is the core concept of N-path filters [41,42]. This results in better blocker handling and the LNTA faces less problems with compression at its output.

Smaller duty cycle LO signals are employed, and it can be shown that 25% improves the conversion gain of the mixer by 3dB compared to 50% duty

3.3 LO Generation 21

Figure 3.8: LO generation of quadrature signals with 25% duty cycle.

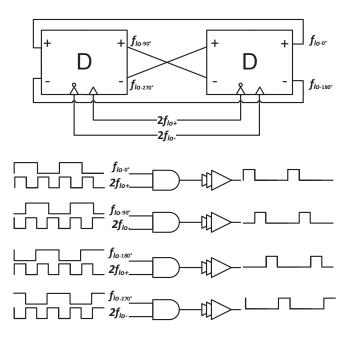

cycle LO signals [14, 43]. Having quadrature (I & Q) passive mixers, using 25% duty cycle is also a very efficient way of avoiding mixer interaction due to simultaneous conduction. Unfortunately, reducing the duty cycle requires more complex LO generation circuitry.

# 3.3 LO Generation

For passive mixers, rail-to-rail LO signals are required to multiply (down convert) the wanted signals to base band with high linearity. High spectral purity is required to avoid reciprocal mixing, and quadrature signals are needed for image rejection. Finally, shorter duty cycle results in reduced mixer conversion loss and IQ interaction. Digital circuits lend themselves well to generate such short pulses. To generate 25% duty cycle quadrature signals a divide-by-2 circuit is typically used, therefore the phase locked loop (PLL) needs to operate at twice the LO frequency. Since differential voltage controlled oscillators (VCOs) are often used in the PLL, differential divide-by-2 circuits are adopted. A divide-by-2 circuit using delay latches is shown in Fig. 3.8, also shown in the figure is the generation of the 25% duty cycle using an AND gate.

Since high RF is supported in many modern wireless communication sys-

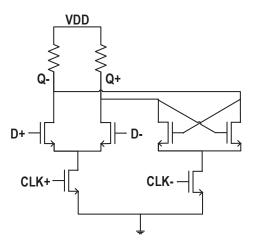

Figure 3.9: Schematic of the CML latch.

tems, high speed frequency dividers are needed, and current mode logic (CML) is frequently used to implement such dividers. The CML latch is shown in Fig. 3.9.

# 3.4 The TIA

The down converted signal current needs to be converted to voltage, then further filtering is performed before feeding the signal to the ADC. The current to voltage conversion is performed by a TIA, which can also provide first order filtering.

The TIA can be implemented using a CG stage, however, excess noise and limited linearity make this implementation suitable mainly for very low power implementations. Feedback configurations on the other hand offer very good characteristics in terms of linearity, noise, and configurability (see Fig. 3.1).

Since a MOS transistor in the active region behaves as a voltage controlled current source (VCCS), OTAs are easier to design and consume less power than true operational amplifiers (OPAMPs) with low output impedance. The amplifiers are therefore implemented as OTAs.

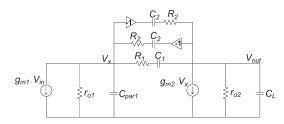

Unfortunately, single-stage OTAs in deep-submicron CMOS offer limited transconductance  $g_m$ , and a multi-stage OTA is usually needed to boost the effective transconductance  $(G_m)$  of the OTA. Multi-stage OTAs have multiple poles in the transfer function (TF), and the use of such OTAs in feedback configurations increases the risk of instability in the system. A brief introduction to compensation schemes and stability assurance of the system is discussed in chapter 4 and paper I [5] in this dissertation. For now assuming that the OTA

3.4 The TIA 23

Figure 3.10: A model of the TIA using a two-stage OTA.

is compensated for TIA configuration with enough phase margin to guarantee stable operation. The compensated OTA can be modeled by adjusted values of each stage output capacitance  $(c_o)$  which together with the output resistance  $(r_o)$  of that stage form a pole at the same frequency as the one in the compensated OTA.

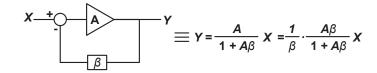

# 3.4.1 Loop Gain and Stability Analysis

A two-stage OTA provides sufficient loop gain  $(A\beta)$ , where A is the forward gain and  $\beta$  represents the feedback gain. A well-compensated OTA should have similar gain characteristic as a single-stage (single-pole) OTA at lower frequencies, which is accomplished by pushing the second pole to a high frequency.

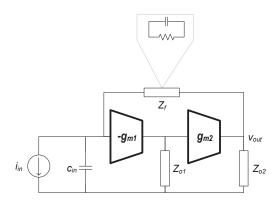

Fig. 3.10 shows a model of a TIA employing a two-stage OTA. Since the OTA is assumed to be compensated, pole spacing is increased. Shown in Fig. 3.10,  $c_{in}$  is a capacitor placed to sink the current of the out-of-band blockers,  $g_{m1}$  and  $g_{m2}$  are the transconductances of the first and second stages of the OTA, and similarly  $Z_{o1}$  and  $Z_{o2}$  are the output impedances which form the first and the second pole of the OTA. Finally,  $Z_f$  is the feedback impedance that sets the TIA gain.

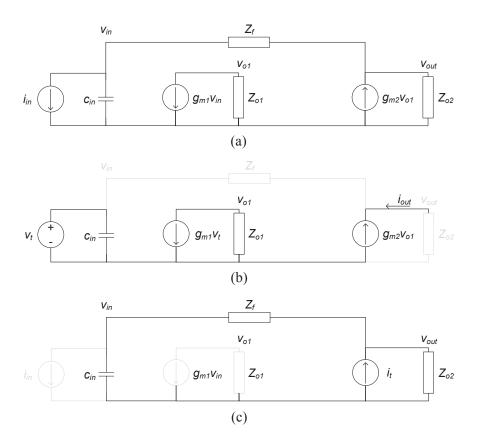

The small signal model of the TIA is shown in Fig. 3.11(a). To analyze  $A\beta$ , A is first calculated using Fig. 3.11(b), where a test voltage at the input is used to calculate the output current  $i_{out}$ . For  $\beta$ , Fig. 3.11(c) is used, where a test current  $i_t$  at the output is used to calculate the input voltage  $v_{in}$ . It can be shown that

$$A\beta = \frac{i_{out}}{v_t} \frac{v_{in}}{i_t} = -g_{m1} Z_{o1} g_{m2} Z_{o2} \frac{Z_{c_{in}}}{Z_f + Z_{c_{in}} + Z_{o2}}$$

(3.2)

**Figure 3.11:** Model of (a) two-stage OTA, (b) calculation of A, and (c) calculation of  $\beta$ .

Taking into account that  $Z_f$  consists of  $R_f$  and  $c_f$  in parallel, and  $Z_o$  of  $r_o$  and  $c_o$  in parallel, results in

$$A\beta = -g_{m1}r_{o1}g_{m2}r_{o2}\frac{R_fc_fs + 1}{As^3 + Bs^2 + Cs + 1}$$

(3.3)

where

$$A = c_f c_{in} c_{o1} R_f r_{o1} r_{o2} + c_f c_{o1} c_{o2} R_f r_{o1} r_{o2} + c_{in} c_{o1} c_{o2} R_f r_{o1} r_{o2}$$

$$(3.4)$$

$$B = c_{in}c_{o1}r_{o1}r_{o2} + c_{o1}c_{o2}r_{o1}r_{o2} + c_{f}c_{in}R_{f}r_{o2} + c_{f}c_{o1}R_{f}r_{o1} + c_{f}c_{o2}R_{f}r_{o2} + c_{in}c_{o1}R_{f}r_{o1} + c_{in}c_{o2}R_{f}r_{o2}$$

$$(3.5)$$

3.4 The TIA 25

$$C = R_f c_f + R_f c_{in} + c_{in} r_{o2} + c_{o1} r_{o1} + c_{o2} r_{o2}$$

(3.6)

Miller capacitor [30, 44] decreases the frequency of the first pole resulting in large effective  $c_{o1}$ . If  $c_{in}$  is made very large to sink the blocker currents and provide low impedance for the LNTA, the  $A\beta$  will be reduced heavily since its dominant pole frequency is

$$P_1^{A\beta_{c_{in}=large}} \approx -\frac{1}{(R_f + r_{o2})c_{in}} \tag{3.7}$$

For wide-band applications this directly impacts the in-band/close out-of-band linearity. Added to that, the two-stage OTA is a two pole system and therefore to evaluate the stability of the TIA, the effect of  $c_{in}$  on the pole spacing is important. To study the effect of  $c_{in}$  we first assume that it is removed ( $c_{in} = 0$ ). The expression for  $A\beta$  in (3.3) then reduces, and the pole frequencies become

$$P_1^{A\beta_{c_{in}=0}} = -\frac{1}{R_f c_f} \tag{3.8}$$

$$P_2^{A\beta_{c_{in}=0}} = -\frac{1}{r_{o1}c_{o1}} \tag{3.9}$$

$$P_3^{A\beta_{c_{in}=0}} = -\frac{1}{r_{o2}c_{o2}} \tag{3.10}$$

and the zero frequency remains unchanged

$$Z_1^{A\beta_{c_{in}}=0} = -\frac{1}{R_f c_f} \tag{3.11}$$

It can be seen that (3.8) and (3.11) have the same frequency and therefore cancel, and that the system has two loop gain poles identical to the poles in the forward path A. This implies that if the use of a small value of  $c_{in}$  is intended then compensating the OTA standalone will ensure stability of the TIA. It can also be concluded that the optimal value for  $c_{in}$  to improve the  $A\beta$  is zero. Unfortunately, a large  $c_{in}$  is required to suppress the tones due to LO switching at the TIA input, and to provide low impedance for out-of-band signals. The TIA input impedance  $(Z_{in})$  thus needs to be analyzed for larger values of  $c_{in}$ .

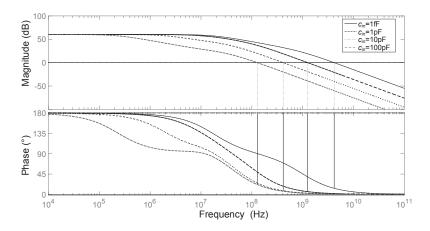

Since all the capacitors need to be considered to evaluate the stability of the TIA, the expressions for the pole frequencies become very large and an insight from the expressions is not easily gained. Instead the TIA used in [5] was modeled according to Fig. 3.10. The input capacitance  $(c_{in})$  was then swept, plotting the gain and phase, see Fig. 3.12. It can be seen that the phase margin

Figure 3.12:  $A\beta$  phase and amplitude for different  $c_{in}$  values.

reaches a minimum as  $c_{in}$  is increased, then it increases again. For this reason  $c_{in}$  needs to be carefully investigated for the minimum phase margin to ensure stability. Very large values of  $c_{in}$  will in general increase the phase margin while heavily reducing  $A\beta$ .

# 3.4.2 $Z_{in}$ Analysis

Minimizing  $Z_{in}$  is crucial to ensure high linearity and avoid LNTA output compression. Analysis of  $Z_{in}$  for both in-band and out-of-band is very important.  $Z_{in}$  in the transition between in-band to out-of-band will also be studied.

From the model in Fig. 3.10  $Z_{in}$  is calculated to

$$Z_{in} = \frac{Z_{c_{in}}(Z_f + Z_{o2})}{Z_f + Z_{o2} + Z_{c_{in}}(1 + g_{m1}g_{m2}Z_{o1}Z_{o2})}$$

(3.12)

First,  $Z_{in}$  at low frequencies is investigated, since at very low frequencies all impedances are resistive making simplifications possible, the input impedance can then be approximated by

$$Z_{inDC} \approx \frac{R_f + r_{o2}}{g_{m1}g_{m2}r_{o1}r_{o2}} \tag{3.13}$$

In (3.13) it can be seen that in-band the input impedance is inversely proportional to the OTA voltage gain, so in order to ensure low impedance the voltage gain should be maximized. As can be seen in (3.12), when  $Z_{c_{in}}$  becomes small at very high frequencies or if  $c_{in}$  is large, then  $Z_{in}$  reduces to  $Z_{c_{in}}$ .

3.4 The TIA 27

At low frequencies  $Z_{in}$  is low according to (3.13), and at very high frequencies  $Z_{in}$  is also low  $(Z_{in} \approx Z_{c_{in}})$ , at intermediate frequencies  $Z_{in}$  will first increase as  $A\beta$  starts to roll off due to limited amplifier bandwidth, then  $Z_{c_{in}}$  will start dominating causing  $Z_{in}$  to decay again. In other words,  $Z_{in}$  can be approximated by a parallel RLC resonant circuit. At resonance the magnitude of  $Z_{in}$  is maximum, and depending on the magnitude, a blocker at that frequency may heavily compress the receiver front-end.

Unfortunately, the intermediate frequencies are typically the most important ones where blockers are strongest. Analyzing (3.12), the zero frequencies are given by

$$Z_1^{Z_{in}} = -\frac{1}{r_{o1}c_{o1}} (3.14)$$

$$Z_2^{Z_{in}} = -\frac{1}{R_f \|r_{o2}(c_f + c_{o2})}$$

(3.15)

The first pole frequency is given by

$$P_1^{Z_{in}} \approx -\frac{1}{R_f c_f} \tag{3.16}$$

and the next two complex conjugate poles frequencies are

$$P_{2\&3}^{Z_{in}} \approx -\frac{1}{2R_f c_f} - \frac{1}{2r_{o2}c_f} - \frac{1}{2r_{o2}c_{in}} - \frac{1}{2r_{o1}c_{o1}} \pm i \frac{\sqrt{A_v}}{\sqrt{r_{o1}r_{o2}c_{o1}c_{in}}}$$

(3.17)

where  $A_v$  is the DC voltage gain of the OTA, given by

$$A_v = g_{m1}g_{m2}r_{o1}r_{o2} (3.18)$$

A zero in  $Z_{in}$  will cause the impedance to increase and is therefore not desirable, while a pole is desirable as it causes reduction instead. It can be seen in (3.14-3.17) that the first zero frequency is at the OTA's dominant pole frequency, which indicates that the bandwidth of the OTA should be maximized. The first pole (3.16) is determined by the feedback network  $(R_f||c_f)$ , which will counteract the zero in (3.14) if OTA's 3dB bandwidth  $\geq (c_f R_f)^{-1}$ . This condition is difficult to meet as the bandwidth continues to grow with increased data rates limiting (3.16), but in general the distance between (3.14) and (3.16) needs to be minimized. The second zero (3.15) is located at higher frequencies, causing further peaking in  $Z_{in}$ . To limit the peaking the complex conjugate poles frequency in (3.17) needs to be decreased using  $c_{in}$ .

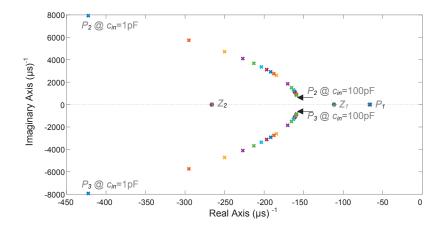

The TIA used in paper V [5] was modeled using the model shown in Fig. 3.10. In the pole-zero map with  $c_{in}$  swept from 1pF to 100pF (see Fig. 3.13), it can be seen that zero frequencies and pole frequency in (3.16) remain unchanged. The pole frequencies in (3.17) on the other hand reduced are as  $c_{in}$  increases.

**Figure 3.13:** Pole-zero map of  $Z_{in}$  for different values of  $c_{in}$ .

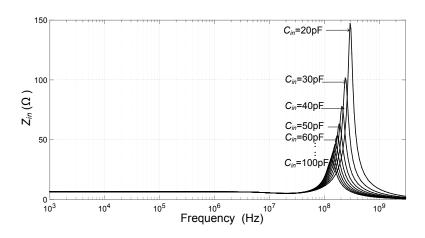

The magnitude of  $Z_{in}$  of the modeled TIA used in paper V [5], using the model in Fig. 3.10, is plotted in Fig. 3.14 for different values of  $c_{in}$ . The peak  $Z_{in}$  ( $Z_{inmax} = max(|Z_{in}|)$ ) deviates from the SPICE simulations of the TIA at high frequencies since more poles and zeros exist in the more accurate model (SPICE simulations are not shown), however, the resonance frequency ( $\omega_o$ ) of  $Z_{inmax}$  matches the SPICE simulations even at higher frequencies. It can be seen in Fig. 3.14 that increasing  $c_{in}$  decreases  $Z_{in}$ . Unfortunately,  $\omega_o$  also decreases to frequencies where large blockers are expected (100MHz to 200MHz offset in this case).

Assume that the pole in (3.16) cancels the effect of the zero in (3.14). Then left is the complex conjugate poles given by (3.17) and the zero given by (3.15) (see the example TIA pole-zero map in Fig. 3.13),  $\omega_o$  can be estimated.

The two complex conjugate poles have a high Q (notice the Y-axis scale in Fig. 3.13), resulting in peaking with a high  $Z_{inmax}$ .  $Z_{in}$  then becomes [45]

$$Z_{inapprox} \approx K \frac{s + \omega_z}{s^2 + \frac{\omega_o}{O}s + \omega_o^2}$$

(3.19)

where  $\omega_z$  is the zero frequency given by (3.15), and K is a scaling factor. The approximation of  $Z_{in}$  can also be written as

$$Z_{inapprox} \approx K \frac{s + Z_2^{Z_{in}}}{s^2 + (P_2^{Z_{in}} + P_3^{Z_{in}})s + (P_2^{Z_{in}} P_3^{Z_{in}})}$$

(3.20)

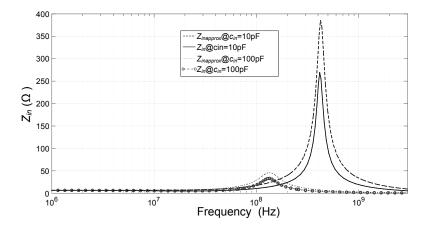

The accuracy of the  $Z_{inapprox}$  was compared to (3.12), for the TIA of paper V [5] for  $c_{in} = 10$ pF and  $c_{in} = 10$ 0pF, see Fig. 3.15. As can be seen in the figure,

3.4 The TIA 29

Figure 3.14:  $Z_{in}$  peaking for different values of  $c_{in}$ .

Figure 3.15: Modeled vs. approximated  $Z_{in}$  for two  $c_{in}$  settings.

the approximation accurately predicts  $\omega_o$ . The approximation of  $\omega_o$  becomes

$$\omega_o \approx \sqrt{\left(-\frac{1}{2R_f c_f} - \frac{1}{2r_{o2}c_f} - \frac{1}{2r_{o2}c_{in}} - \frac{1}{2r_{o1}c_{o1}}\right)^2 + \frac{g_{m1}g_{m2}}{c_{o1}c_{in}}}$$

(3.21)

The peaking in  $Z_{in}$  can be reduced by decreasing the Q of  $P_2^{Z_{in}}$  and  $P_3^{Z_{in}}$ , i.e. the ratio of the imaginary and real part. As can be seen in (3.17) this can be accomplished by increasing  $c_{in}$  or decreasing  $r_o$ . The second choice directly

impacts the performance of the OTA and is therefore not desirable. Increasing  $g_m$  helps reducing the impedance, but leads to increased current consumption.

Although an expression that accurately predicts the value  $Z_{inmax}$  is very large, a short intuitive expression can be estimated. First, (3.13) predicts the value of  $Z_{inDC}$ . The two complex conjugate poles in (3.17) will then cause the impedance at  $\omega_o$  to increase from  $Z_{inDC}$  by a factor approximately equal to their Q value [45]. The effect of the zero in (3.17) is a further increase in impedance by the ratio  $(\frac{\omega_o}{\omega_z})$ . Therefore  $Z_{inmax}$  can be approximated by

$$Z_{inmax} \approx \frac{\omega_o}{\omega_z} Z_{inDC} Q$$

(3.22)

where Q is calculated as the ratio of the imaginary and real part of (3.17).

# Chapter 4

# OTA Linearization and Filter Implementations

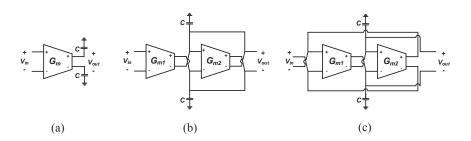

The final stage of the analog receiver front-end is the CSF, which suppresses adjacent channels and out-of-band interference signals before analog to digital conversion. The CSF linearity is a key factor that limits the receiver performance. In particular, band edge and out-of-band linearities are important.

In this chapter the dominant nonlinearities in MOS devices are first described, followed by a brief introduction to linearity enhancement methods for OTAs. Finally, the main CSF architectures are summarized.

# 4.1 MOS Nonlinearity

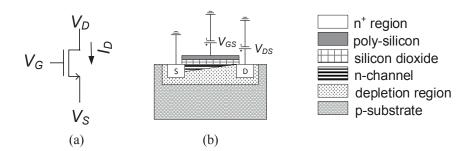

The symbol and conceptual cross section of an nMOS device operating in saturation are shown in Fig. 4.1. The different regions of operation of a MOS device and the physical description can be found in integrated circuits and semiconductor physics literature such as [30, 46, 47]. The pMOS device is the dual of the nMOS, more about nMOS and pMOS can also be found in [30, 46, 47].

The long channel approximation of the current of an nMOS device in saturation region is given by

$$i_D = \frac{\mu_n C_{ox}}{2} \frac{W}{L_{eff}} (v_{GS} - V_{th})^2 (1 + \lambda v_{DS}) \approx \frac{\mu_n C_{ox}}{2} \frac{W}{L_{eff}} (v_{GS} - V_{th})^2$$

(4.1)

where  $i_D$  is the drain current, W is the device width,  $L_{eff}$  is the effective length of the device,  $C_{ox}$  is the gate oxide capacitance per unit area,  $\mu_n$  is the electron mobility in the channel,  $\lambda$  is the channel length modulation factor,  $V_{th}$  is the threshold voltage, and  $v_{GS}$  and  $v_{DS}$  are the gate-source and drain-source voltages, respectively. From (4.1) it is clear that the second order is the highest order of nonlinearity, however, effects in submicron devices cause also higher order nonlinearities to exist. The most dominant short channel effects are:

-Velocity saturation is one of the most important effects in nanometer devices. If the voltages are not scaled at the same rate, the horizontal electric

Figure 4.1: (a) Symbol of nMOS, (b) conceptual nMOS cross section.

field  $(\xi_h)$  increases with decreased channel length, therefore the charge carrier velocity also increases. At very high  $\xi_h$ , however, the carrier velocity approaches the thermal velocity and saturates. The field strength at which the charge carrier velocity saturates is called the critical electric field  $(\xi_c)$ . The effect of velocity saturation can be modeled by a degeneration resistor  $(R_{vs})$  at the source terminal, and (4.1) becomes

$$i_{\rm D} \approx \frac{\mu_n C_{ox}}{2(1 + \mu_n C_{ox} \frac{W}{L_{eff}} R_{vs} (v_{GS} - V_{th}))} \frac{W}{L_{eff}} (v_{GS} - V_{th})^2 (1 + \lambda v_{DS})$$

(4.2)

-Mobility degradation is also an effect of high electrical field strength  $(\xi)$ , but in this case in the vertical direction of the field  $(\xi_v)$ . High  $\xi_v$  arises from high gate voltage  $V_G$ , which causes the charge carriers to be pulled towards the silicon surface, this reduces their mobility. The effective mobility can be modeled as

$$\mu_{\text{eff}} \approx \frac{\mu_n}{1 + \theta(v_{GS} - V_{th})} \tag{4.3}$$

where  $\theta$  is the mobility reduction parameter. Although the mobility degradation effect is also found in long MOS devices,  $\theta$  is inversely proportional to the oxide thickness  $t_{ox}$  making the mobility degradation worse in new CMOS technologies where  $t_{ox}$  is reduced [30, 46].

Many other effects described in literature result in more nonlinear behavior of the drain current  $i_D$  [46]. These effects on  $i_D$  can be described using Taylor series expansion [48]

$$i_{D} = I_{DC} + g_{m} v_{gs} + K_{2}^{gm} v_{gs}^{2} + K_{3}^{gm} v_{gs}^{3} \dots$$

$$g_{o} v_{ds} + K_{2}^{go} v_{ds}^{2} + K_{3}^{go} v_{ds}^{3} \dots$$

$$K_{2}^{g_{m} \delta g_{o}} v_{gs} v_{ds} + K_{3}^{g_{m}^{2} \delta g_{o}} v_{gs}^{2} v_{ds} + K_{3}^{g_{m}^{2} \delta g_{o}^{2}} v_{gs} v_{ds}^{2} \dots$$

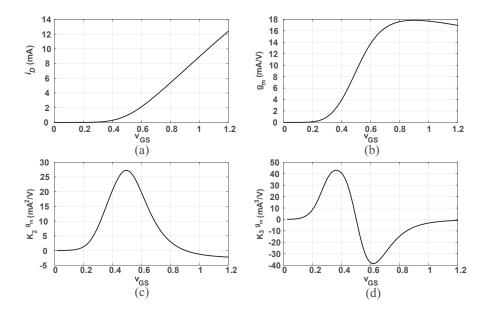

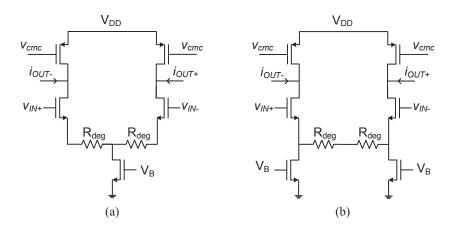

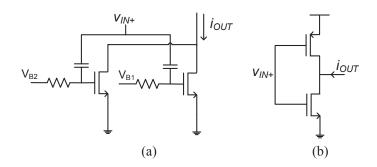

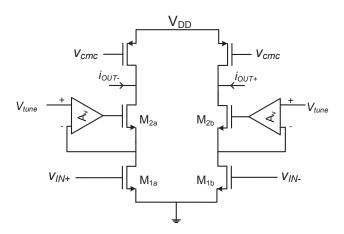

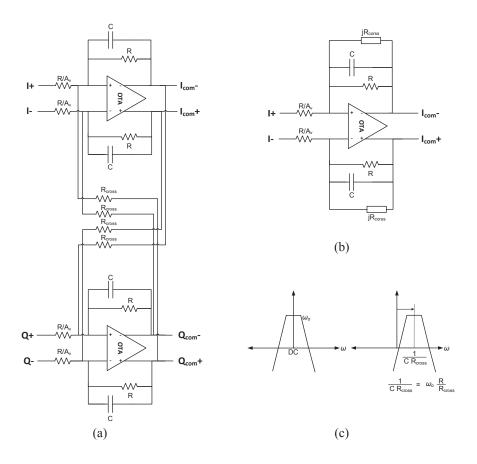

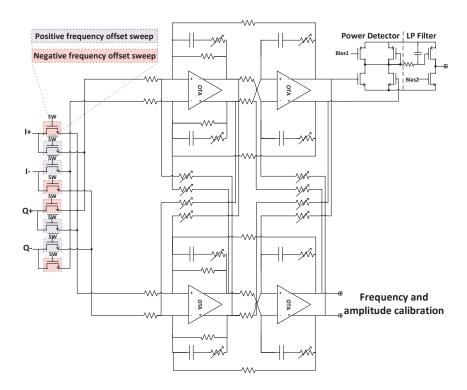

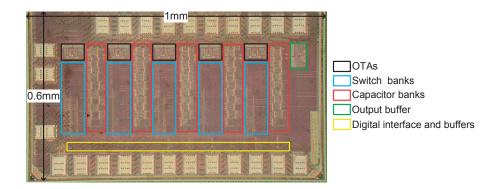

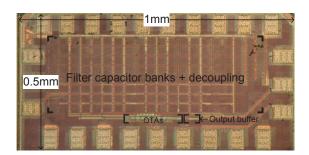

$$(4.4)$$