# Master's Thesis

# Automated modelling and optimization of a ratioed logic inverter utilizing nanowire-based transistors

Ву

Martin Berg and Kristofer Jansson (2009-12-07)

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden

"Only one who devotes himself to a cause with his whole strength and soul can be a true master. For this reason mastery demands all of a person."

- Albert Einstein

#### **PREFACE**

Before you venture further into the realm of equations and circuit diagrams, we would like to take the opportunity to say a few words about this report. This master's thesis is the ultimate culmination of 4.5 years studies in Engineering Nanoscience at Lund University. The background of the thesis is a project work in the nanoelectronics course at LTH, of which the main findings of were used as a starting point.

One of the main purposes of the thesis is to build a theoretical foundation for nanowire device characterization, in the spirit of the work on nanowires, performed at the Nanometer Structure Consortium in Lund. Measurements on some test devices were expected, but this did not come into fruition due to immature processing technology.

At the start of the work, the idea was to design a range of different test circuits based on nanowire transistors. However, the project evolved into a more focused enterprise, encompassing modelling, simulation and optimization of a ratioed logic inverter.

During the course of the project, knowledge from multiple areas was applied in order to solve the multitude of problems encountered. In addition, different bits of code developed during the course of the project, converged into a large software suite, automating large parts of the project. Although many long nights were devoted to, the work was deemed rewarding and interesting.

The authors would like to acknowledge the support of Professor Lars-Erik Wernersson and Professor Peter Nilsson, our supervisors for this project. Thanks are also extended to the participants in the nanowire group meetings and Wireless With Wires (WWW) meetings for their input and support.

Finally, the authors would like to take the opportunity to thank their respective families and friends for their undying support during the ordeals, encountered during the writing of this thesis.

Live long and prosper,

Martin Berg & Kristofer Jansson Lund, december 2009

#### **ABSTRACT**

# Automated modelling and optimization of a ratioed logic inverter utilizing nanowire-based transistors

The continuing trend of electronic miniaturization is approaching a critical limit for conventional silicon based technology. Transistors based on nanowires are an interesting concept that might extend this trend deeper into the nano-scale domain. In this work, the usage of nanowire-based transistors is studied in the context of digital circuit design.

The authors propose a complete workflow from measurement, through transistor modelling and circuit simulation to an optimized inverter design. This workflow is realized in the form a software suite, developed for this purpose. By implementing intelligent algorithms and extraction methods, this allows the workflow to be highly automated, reducing the time needed for a complete analysis from weeks to a matter of minutes.

A modified MOSFET model is introduced based on the proper deep-submicron MOSFET model. By adding a series resistance and introducing a dependence on the nanowire quantity in addition to neglecting the channel length modulation, the Jansson-Berg model is defined. The model is implemented into the software and an acceptable correspondence to measurement data is achieved. To simulate the parasitic capacitances in the transistor design, a model consisting of 21 separate capacitances is derived.

The Jansson-Berg model is analysed in the application of simulating an inverter. Due to the unavailability of p-type transistors, a ratioed logic design is proposed, utilizing only n-type transistors. As an exact analytical solution of the circuit performance is nearly impossible, it is concluded that series solutions are necessary. Although simplifications are made, the analytical solutions achieve a good correspondence to a purely numerical analysis.

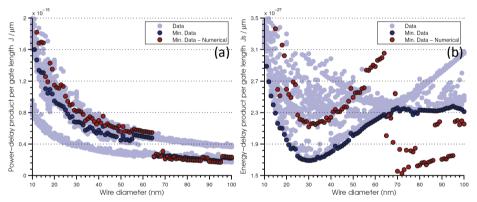

Finally, the transistor design is optimized based on the energy-delay product. This is done intelligently, by testing about 300 million transistor designs, bound by specified design rules. Based on this large data set, it is concluded that further downscaling is advisable.

# Automatiserad modellering och optimering av en inverterare med nanotrådstransistorer

Trenden för miniatyrisering av mikroelektronik närmar sig gränsen för vad som är möjligt att uppnå med konventionell kiselteknologi. En teknik, med potential att pressa utveckling mot allt mindre komponenter, är nanotrådstransistorer. I detta examensarbete studeras implementering av dessa transistorer i digitala kretsar.

En fullständig analys av en krets innebär flera påföljande steg, innefattande mätning, transistormodellering, kretssimulering och slutligen optimering. Författarna föreslår ett arbetsflöde, där de olika delarna sammanställs i form en egenutvecklad programvara. Genom implementering av intelligenta algoritmer och extraktionsmetoder är det möjligt att automatisera dessa processer och därigenom minska arbetsbördan för en komplett analys, från veckor till en fråga om minuter.

En modell för karakteriseringen av nanotrådstransistorerna implementeras genom modifiering av en enkel MOSFET-modell. Modellen modifieras för att inkorporera serieresistans och försumma kanallängdsmodulation samt att ett beroende på antalet nanotrådar införs. Genom implementering i mjukvaran av en automatiserad modellering, kan en god överensstämmelse erhållas mellan mätdata och modell. För att få en simulera de parasitiska kapacitanserna i transistordesignen, tas en modell fram som består av 21 st. separata parasitiska element.

Transistormodellen används för att numeriskt och analytiskt studera en prestanda för en digital inverterare. Eftersom inga transistorer av p-typ finns att tillgå, används en kvotbaserad logik, bestående av enbart transistorer av n-typ. En exakt tidsanalytisk lösning av en sådan inverterare är i princip omöjlig och därför är serieutvecklingar nödvändiga. Även om detta är en grov förenkling, föreligger en god överensstämmelse mellan den analytiska och numeriska analysen.

Slutligen optimeras transistordesignen utifrån produkten mellan energiförbrukning och kvadrerad stegfördröjning. Detta utförs med hjälp av en intelligent algoritm som under projektets gång testat omkring trehundramiljoner olika transistordesigner. Från denna stora datamängd dras slutsatsen att ytterligare nedskalning av transistordesignen är fördelaktig.

# Automatisierte Modellierung und Optimierung eines Nicht-Gatter basiert auf Nanodraht-Transistoren

In dieser Arbeit wurde die Verwendung von Nanodraht-basierten Transistoren, im Zusammenhang digitalen Schaltung, untersucht. Die Autoren vorschlagen einen kompletten Arbeitsablauf von der Messung, durch die Transistor-Modellierung und Schaltungssimulation, zu einem optimierten Wechselrichterdesign. Dieser Arbeitsablauf ist in der Form eines Computerprogramms realisiert, für diesen Zweck entwickelt. Ein einfaches MOSFET-Modell wurde verwendet, um eine analytische Lösung der Schaltung zu erwerben. Obwohl die Lösung vereinfacht ist, eine gute Entsprechung zu einer numerischen Analyse erreicht ist. Eine Optimierung erfolgt, basiert vom Energie-Laufzeit Produkt, und der Rückschluss wird gezogen, dass weitere Verkleinerung ratsam ist.

## La Modélisation et l'Optimisation Automatique d'un Fonction-NON Utilisation de Nanofils à base de Transistors

Dans ce travail, l'utilisation de nanofils à base de transistors est étudiée dans le cadre de la conception de circuits numériques. Les auteurs proposent un flux de travail complet de la mesure, par la modélisation et la simulation de circuits à transistors à une conception optimisée de l'onduleur. Ce flux de travail est réalisé sous la forme d'une suite logicielle, développé à cet effet. Un modèle MOSFET simple a été utilisée en vue d'acquérir une solution analytique de la performance du circuit. Même si la solution n'est pas exacte, une bonne correspondance à une analyse chiffrée est atteinte. Le processus d'optimisation se fait sur la base de l'énergie-produit de retard et il est conclu que davantage de réduction d'échelle est souhaitable.

# **ABBREVIATIONS AND SYMBOLS**

# **Abbreviations**

**DSMM** Deep SubMicron Model **EDP Energy-Delay product** FET Field-Effect Transistor HC Half-circle MOSFET Metal-Oxide-Semiconductor Field-Effect-Transistor NanoWire Field Effect Transistor **NWFET PDN** Pull-Down Network PDP Power-Delay product **PDSMM** Proper Deep SubMicron Model PΡ Parallel-plate SW Side-wall Voltage Transfer Characterization VTC

# Latin symbols

WIGFET

| A               | _ | Plate capacitor area          | $C_{DS,pp}$     | - | Drain-Source<br>overlap           |

|-----------------|---|-------------------------------|-----------------|---|-----------------------------------|

| $A_n$           | _ | Optimization                  |                 |   | capacitance                       |

|                 |   | parameter                     | $C_{GD}$        | _ | Gate-Drain                        |

| β               | _ | Noise factor                  |                 |   | capacitance                       |

| $C_{DS}$        | - | Drain-Source                  | $C_{GD,edge,x}$ | - | Gate-Drain edge                   |

|                 |   | capacitance                   |                 |   | capacitance (x)                   |

| $C_{DS,edge,x}$ | - | Drain-Source edge capacitance | $C_{GD,edge,y}$ | _ | Gate-Drain edge capacitance (y)   |

|                 |   | (x)                           | $C_{GD,fri}$    | _ | Gate-Drain fringe                 |

| $C_{DS,edge,y}$ | _ | Drain-Source                  |                 |   | capacitance                       |

|                 |   | edge capacitance<br>(y)       | $C_{GD,fri,x}$  | - | Gate-Drain fringe capacitance (x) |

Wrapped-Insulator-Gate Field-Effect

| $C_{GD,fri,y}$  | - | Gate-Drain fringe          | $C_{GS,fri,x}$             | - | Gate-Source                    |

|-----------------|---|----------------------------|----------------------------|---|--------------------------------|

| C               |   | capacitance (y) Gate-Drain |                            |   | fringe capacitance (x)         |

| $C_{GD,pp}$     | _ | overlap                    | $C_{GS,fri,y}$             | _ | Gate-Source                    |

|                 |   | capacitance                | - us,j ri,y                |   | fringe capacitance             |

| $C_{GD,wire}$   | _ | Gate-Drain wire            |                            |   | (y)                            |

| ab,wii c        |   | capacitance                | $C_{GS,pp}$                | - | Gate-Source                    |

| $C_{GD,wire,x}$ | _ | Gate-Drain wire            |                            |   | overlap                        |

|                 |   | capacitance (x)            |                            |   | capacitance                    |

| $C_{GD,wire,y}$ | _ | Gate-Drain wire            | $C_{GS,wire}$              | - | Gate-Source wire               |

|                 |   | capacitance (y)            |                            |   | capacitance                    |

| $C_{GE}$        | - | Gate-Electrode             | $C_{GS,wire,x}$            | - | Gate-Source wire               |

|                 |   | capacitance                | _                          |   | capacitance (x)                |

| $C_{GE,edge,r}$ | _ | Gate-Electrode             | $C_{GS,wire,y}$            | - | Gate-Source wire               |

|                 |   | edge capacitance           |                            |   | capacitance (y)                |

| $C_{GE,fri}$    | - | Gate-Electrode             | $C_{input}$                | _ | Input capacitance              |

|                 |   | fringe capacitance         | $C_{load}$                 | _ | Load capacitance               |

| $C_{GE,fri,r}$  | - | Gate-Electrode             | $C_N$                      | - | Effective noise                |

|                 |   | fringe capacitance         |                            |   | capacitance                    |

| 0               |   | (r)                        | $C_{ox}$                   | - | Gate-oxide                     |

| $C_{GE,pp}$     | _ | Gate-Electrode             | a                          |   | capacitance                    |

|                 |   | overlap<br>capacitance     | $C_{parasitic}$            | - | Parasitic                      |

| C               | _ | Gate-Electrode             | C                          |   | capacitance                    |

| $C_{GE,wire}$   | _ | wire capacitance           | $C_{pp}$                   | _ | Overlap                        |

| $C_{GS}$        | _ | Gate-Source                | C                          |   | capacitance                    |

| GGS             |   | capacitance                | $C_{\pi}$                  | _ | Half-circle fringe capacitance |

| $C_{GS,edge,x}$ | _ | Gate-Source edge           | C                          | _ | Sidewall                       |

| - us,euge ,x    |   | capacitance (x)            | $C_{sw}$                   |   | capacitance                    |

| $C_{GS,edge,y}$ | _ | Gate-Source edge           | $C_{top,top}$              | _ | Top-to-top                     |

| ab,cage,y       |   | capacitance (y)            | - ιυ <i>р</i> ,ιυ <i>р</i> |   | capacitance                    |

| $C_{GS,fri}$    | _ | Gate-Source                | d                          | _ | Plate capacitor                |

| y · -           |   | fringe capacitance         |                            |   | distance                       |

|                 |   |                            |                            |   |                                |

| $d_{DS}$          | _ | Drain to source             | L          | _ | Gate height                  |

|-------------------|---|-----------------------------|------------|---|------------------------------|

| 23                |   | distance                    | $L_{eff}$  | _ | Effective gate               |

| $d_{\mathit{GD}}$ | _ | Gate to drain               | ٥٫٫        |   | height                       |

|                   |   | distance                    | l          | _ | Unit cell width              |

| $d_{\mathit{GE}}$ | - | Gate to electrode           | $l_x$      | - | Unit cell width (x)          |

| 7                 |   | distance                    | $l_y$      | _ | Unit cell width (y)          |

| $d_{GS}$          | _ | Gate to source distance     | $M_{load}$ | - | Load transistor symbol       |

| E                 | - | Electron energy             | $M_{PDN}$  | _ | PDN transistor               |

| $E_C$             | _ | Conduction band             | 1 DIV      |   | symbol                       |

| Г                 |   | energy                      | m          | - | Miller effect index          |

| $E_F$             | _ | Fermi energy                | $m_{d,v}$  | - | Effective mass               |

| $E_{v,n}$         | _ | Energy level in valley      | $N_0$      | _ | 1-D density of               |

| $f_S$             | _ | Simulation data             |            |   | states                       |

| $f_D$             | _ | Measurement                 |            |   | substitution                 |

| JD                |   | data                        | $N_C$      | _ | Effective density of states  |

| $g_m$             | _ | Process                     | $N_D$      | - | Donor                        |

|                   |   | transconductance            |            |   | concentration                |

| $g_v$             | - | Valley degeneracy           | $N_{load}$ | - | Number of                    |

| Н                 | _ | Electrode height difference |            |   | nanowires in load transistor |

| $H_E$             | - | Electrode height            | $N_{PDN}$  | - | Number of                    |

| h                 | - | Planck's constant           |            |   | nanowires in pull-           |

| $I_{load}$        | _ | Load transistor             |            |   | down transistor              |

|                   |   | current                     | n          | - | Electron carrier             |

| $I_{PDN}$         | - | PDN transistor              |            |   | concentration                |

|                   |   | current                     | 0          | _ | Higher order                 |

| k                 | - | Gain factor                 | ח          |   | terms                        |

| $k_B$             | _ | Boltzmann's constant        | $P_A$      | _ | Average power dissipation    |

| k'                | _ | Process                     | Q          | - | Simulation quality           |

|                   |   | transconductance parameter  | q          | - | Elementary charge            |

|                   |   |                             |            |   |                              |

| R               | _   | Nanowire radius                         | $V_{DD}$          | - | Supply voltage                                    |

|-----------------|-----|-----------------------------------------|-------------------|---|---------------------------------------------------|

| $R_s$           | _   | Series resistance                       | $V_{DS}$          | - | Gate-Source                                       |

| S               | _   | Space between                           |                   |   | voltage                                           |

|                 |     | electrodes                              | $V_{DSAT}$        | - | Saturation voltage                                |

| T               | -   | Temperature;<br>Thickness               | $V_{GS}$          | - | Gate-Source<br>voltage                            |

| $T^{'}$         | -   | Conformal mapping                       | $V_{IH}$          | - | Input-High<br>voltage                             |

|                 |     | thickness                               | $V_{in}$          | - | Input voltage                                     |

| $T_{GE,fri}$    | -   | Gate-Electrode                          | $V_{IL}$          | _ | Input-Low voltage                                 |

| $T_{GE,fri,r}$  | _   | fringe thickness<br>Gate-Electrode      | $V_N$             | - | Thermal noise voltage                             |

|                 |     | fringe thickness<br>(r)                 | $V_{OH}$          | - | Output-High<br>voltage                            |

| $T_{GE,wire}$   | _   | Gate-Electrode                          | $V_{out}$         | _ | Output voltage                                    |

| t               | _   | wire thickness<br>Time                  | $V_{OL}$          | - | Output-Low<br>voltage                             |

| $t_{ox}$        | -   | Gate oxide                              | $V_T$             | _ | Threshold Voltage                                 |

|                 |     | thickness                               | W                 | _ | Nanowire                                          |

| $v_{sat}$       | -   | Saturation                              |                   |   | diameter                                          |

|                 |     | velocity                                | $W_E$             | - | Electrode width                                   |

| $V_C$           | _   | Critical voltage                        | $W_O$             | - | Electrode overlap                                 |

| Greek sy        | mbo | ls                                      |                   |   |                                                   |

| α               | -   | WIGFET structural parameter             | $arepsilon_{eff}$ | - | Effective permittivity                            |

| $lpha^*$        | _   | Voltage independent $\alpha$ -parameter | $arepsilon_{GE}$  | - | Gate-Electrode<br>spacer relative<br>permittivity |

| β               | _   | Noise factor                            | $arepsilon_{GS}$  | _ | Gate-Source                                       |

| γ               | _   | WIGFET empirical                        | EGS               |   | spacer relative                                   |

| ľ               |     | parameter                               |                   |   | permittivity                                      |

| $\varepsilon_0$ | -   | Permittivity of free space              | $arepsilon_r$     | - | Insulator relative permittivity                   |

| η             | - | Empirical voltage dependent parameter         | $\sigma_S$      | - | Jansson-Berg<br>saturation region<br>substitution |

|---------------|---|-----------------------------------------------|-----------------|---|---------------------------------------------------|

| λ             | - | Channel length modulation                     | τ               | _ | Delay time coefficient                            |

| $\lambda_j$   | - | WIGFET structural                             | $\tau_{0 	o 1}$ | - | Low-to-high delay                                 |

|               |   | parameter                                     | $\tau_{1 	o 0}$ | - | High-to-low delay                                 |

| $\lambda_j^*$ | - | Voltage                                       | $	au_p$         | - | Propagation delay                                 |

|               |   | independent $\lambda_j$ -parameter            | $arphi_m$       | - | Metal work function                               |

| μ             | - | Field-dependent<br>mobility                   | $arphi_{ms}$    | - | Work function difference                          |

| $\mu_0$       | - | Mobility                                      | $arphi_s$       | _ | Semiconductor                                     |

| ξ             | - | Elliptical mapping                            |                 |   | work function                                     |

|               |   | scaling parameter                             | $arphi_{th}$    | _ | Thermal voltage                                   |

| $ ho_j$       | - | WIGFET empirical                              | χ               | _ | WIGFET empirical                                  |

|               |   | parameter                                     |                 |   | parameter                                         |

| σ             | - | Jansson-Berg<br>region-                       | $\chi_m$        | - | Metal electron affinity                           |

|               |   | independent<br>substitution                   | $\chi_s$        | - | Semiconductor electron affinity                   |

| $\sigma_L$    | _ | Jansson-Berg<br>linear region<br>substitution | $\psi_T$        | - | Threshold point surface potential                 |

# **CONTENTS**

| PREFAC         | Е                                      | V    |

|----------------|----------------------------------------|------|

| <b>A</b> BSTRA | СТ                                     | VII  |

| ABBREV         | TATIONS AND SYMBOLS                    | XI   |

| Abbre          | eviations                              | xi   |

| Latin s        | symbols                                | xi   |

| Greek          | symbols                                | xiv  |

| CONTEN         | TS                                     | XVII |

| PART I         | Introduction                           | 1    |

| 1.1            | Background                             | 1    |

| 1.2            | Workflow                               | 1    |

| 1.3            | Structure                              | 2    |

| PART II        | THE NWFET                              | 3    |

| 2.1            | Transistor structure                   | 3    |

| 2.2            | Nanowire                               | 3    |

| 2.2.           | 1 Growth                               | 3    |

| 2.2.           | 2 Field-dependent mobility             | 3    |

| 2.2.           | 3 Saturation velocity                  | 4    |

| 2.3            | Gate dielectric                        | 5    |

| 2.3.           | 1 Gate capacitance                     | 5    |

| 2.4            | Contacts                               | 7    |

| 2.5            | Array configuration                    | 7    |

| 2.6            | Band structure                         | 9    |

| 2.6.           | 1 Surface potential at threshold point | 10   |

| 2.6.           | 2 Work function difference             | 10   |

| PART II        | I PARASITIC CAPACITANCES               | 13   |

| 3.1            | Capacitance types                      | 13   |

| 3.1.           | 1 General assumptions                  | 14   |

| 3.1.           | 2 Scaling rules                        | 15   |

| 3.2            | Overlap capacitances                   | 15   |

| 3.2.           | 1 Scaling                              | 16   |

| 3.3            | Wire capacitances                      | 16   |

| 3.3.           | 1 Geometrical mapping                  | 17   |

| 3.3.           | 2 The expressions                      | 17   |

| 3.4            | Fringe capacitances                    | 19   |

| 3.5     | Edge capacitances                  | 21 |

|---------|------------------------------------|----|

| 3.6     | Array size dependence              | 22 |

| 3.7     | Simplifications                    | 24 |

| PART IV | TRANSISTOR MODELLING               | 25 |

| 4.1     | MOSFET types                       | 25 |

| 4.1.1   | Majority charge carrier            | 25 |

| 4.1.2   | Enhancement and depletion mode     | 25 |

| 4.2     | Regions                            | 25 |

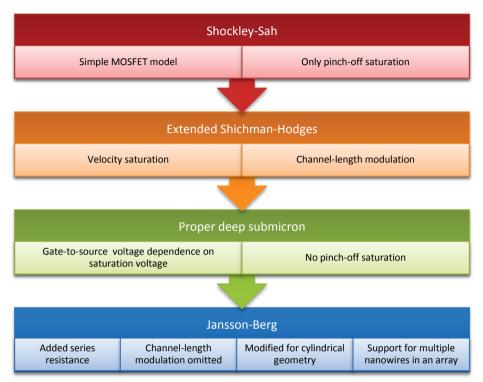

| 4.3     | MOSFET Models                      | 26 |

| 4.3.1   | Shockley-Sah                       | 26 |

| 4.3.2   | Shichman-Hodges model              | 27 |

| 4.3.3   | B Deep submicron MOSFET model      | 28 |

| 4.3.4   | Proper deep submicron MOSFET model | 29 |

| 4.3.5   | Jansson–Berg model                 | 29 |

| 4.3.6   | Summary of MOSFET models           | 30 |

| 4.4     | Semi-analytical WIGFET model       | 30 |

| 4.4.1   | Modelling                          | 31 |

| 4.4.2   | Structural parameters              | 32 |

| PART V  | MODELLING METHODS                  | 35 |

| 5.1     | Software                           | 35 |

| 5.1.1   | Data correction                    | 35 |

| 5.1.2   | Quality evaluation                 | 36 |

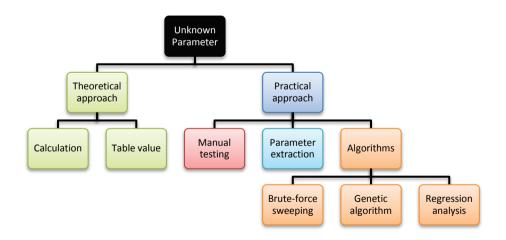

| 5.1.3   | B Parameter determination          | 36 |

| 5.2     | Parameter extraction methods       | 40 |

| 5.2.1   | Threshold voltage                  | 40 |

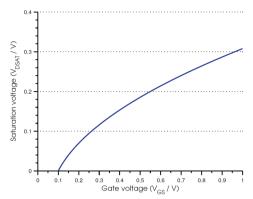

| 5.2.2   | 2 Saturation voltage               | 41 |

| 5.2.3   | Channel-length modulation          | 42 |

| 5.2.4   | Series resistance                  | 42 |

| PART VI | NWFET PARAMETERS                   | 45 |

| 6.1     | Quality of MOSFET-models           | 45 |

| 6.1.1   | Importance of series resistance    | 45 |

| 6.2     | PDSMM Characterization             | 46 |

| 6.2.1   | Analysis                           | 46 |

| 6.2.2   | The test transistor                | 47 |

| 6.2.3   | 3 Characteristics                  | 48 |

| 6.3     | WIGFET Model                       | 48 |

| 6.3.1   | Band structure                     | 49 |

| 6.3.2   | 2 Doping concentrations            | 49 |

|         | Model fitting                      | 49 |

| 6.3.4   | Quality                              | 50 |

|---------|--------------------------------------|----|

| 6.3.5   | Characteristics                      | 50 |

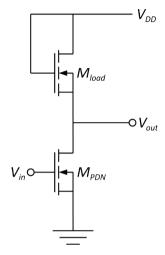

| PART VI | I CIRCUIT DESIGN                     | 53 |

| 7.1     | Logic families                       | 53 |

| 7.1.1   | CMOS                                 | 53 |

| 7.1.2   | Ratioed logic                        | 53 |

| 7.2     | The inverter                         | 53 |

| 7.3     | Figures of merit                     | 54 |

| 7.3.1   | Propagation delay                    | 54 |

| 7.3.2   | Power dissipation                    | 54 |

| 7.3.3   | Power-delay and energy-delay product | 55 |

| 7.3.4   | Regeneracy                           | 56 |

| PART VI | II CIRCUIT ANALYSIS                  | 57 |

| 8.1     | Problem formulation                  | 57 |

| 8.1.1   | Nodal analysis                       | 57 |

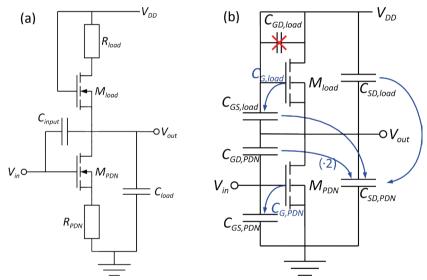

| 8.1.2   | 2 Capacitance merging                | 58 |

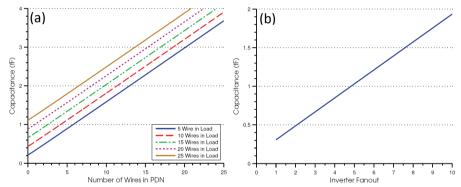

| 8.1.3   | Magnitude of parasitic components    | 59 |

| 8.1.4   | Load capacitance                     | 60 |

| 8.1.5   | Fan-out dependence                   | 60 |

| 8.2     | Numerical solution                   | 61 |

| 8.3     | Analytical solution                  | 61 |

| 8.4     | Delay times                          | 62 |

| 8.4.1   | Low-to-high                          | 62 |

| 8.4.2   | P. High-to-low                       | 63 |

| 8.4.3   | Propagation delay                    | 64 |

| 8.5     | Average power dissipation            | 64 |

| 8.6     | PDP and EDP                          | 65 |

| 8.7     | Influence of series resistance       | 65 |

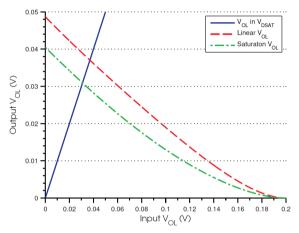

| 8.8     | Static voltage levels                | 66 |

| 8.8.1   | _                                    | 66 |

| 8.8.2   | 2 Output-low                         | 66 |

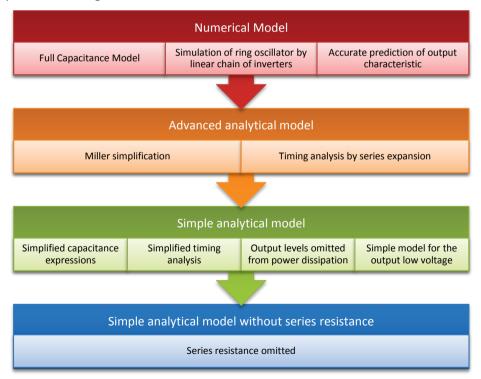

| 8.9     | Summary of circuit models            | 69 |

| PART IX | CIRCUIT SIMULATION RESULTS           | 71 |

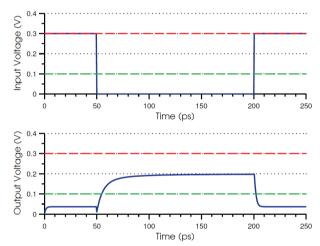

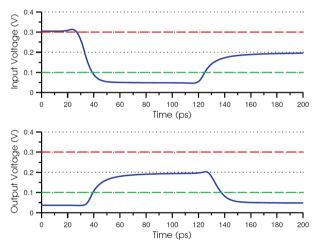

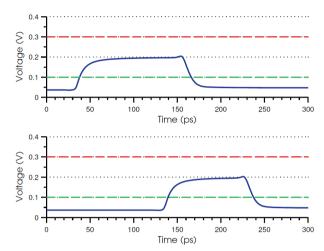

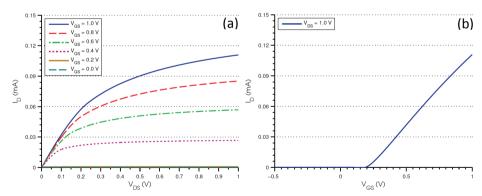

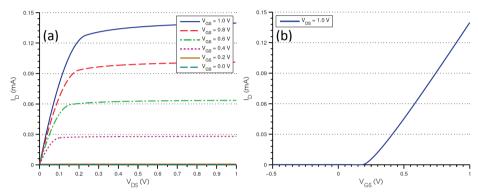

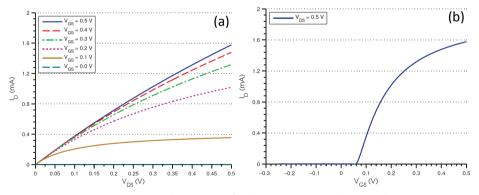

| 9.1     | Output characteristic                | 71 |

| 9.1.1   | Ideal                                | 71 |

| 9.1.2   | Self-driven                          | 72 |

| 9.1.3   | Propagation delay                    | 72 |

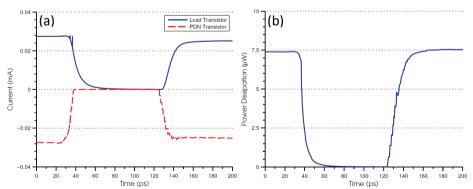

| 9.2     | Currents                             | 73 |

| 0.3     | Power dissination                    | 73 |

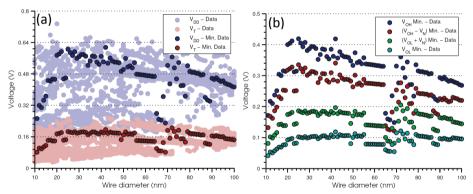

| 9.4              | Voltage levels                            | 74 |  |  |  |

|------------------|-------------------------------------------|----|--|--|--|

| 9.4.1            | Propagation delay                         | 74 |  |  |  |

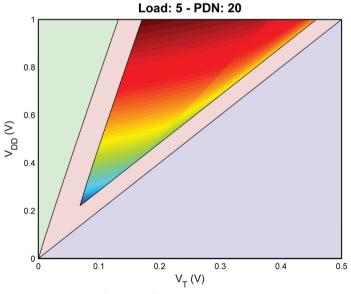

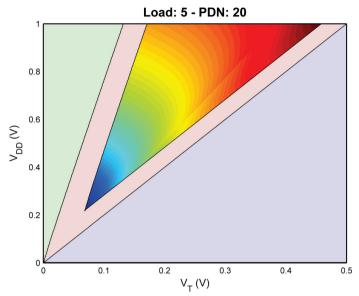

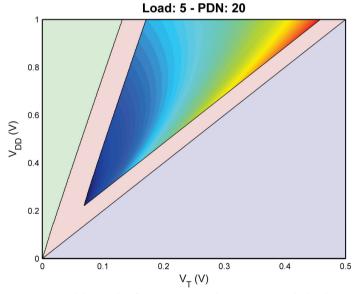

| 9.4.2            | Average power dissipation                 | 74 |  |  |  |

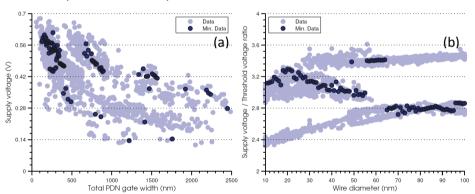

| 9.4.3            | PDP and EDP                               | 77 |  |  |  |

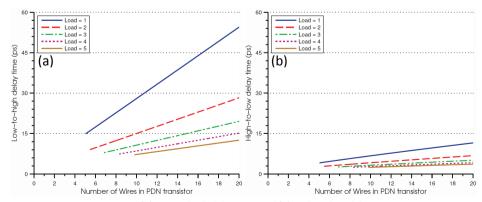

| 9.5              | Wire dependence                           | 77 |  |  |  |

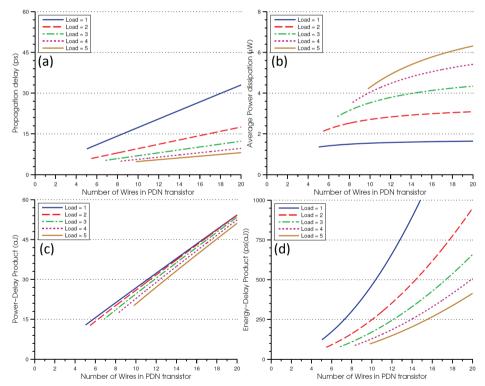

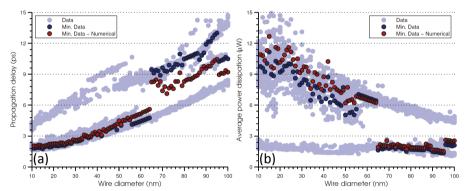

| 9.5.1            | Delay times                               | 77 |  |  |  |

| 9.5.2            | Average power dissipation                 | 78 |  |  |  |

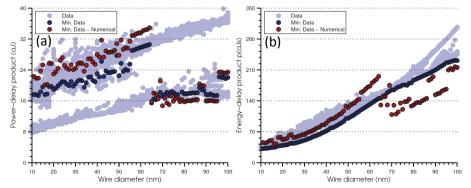

| 9.5.3            | PDP and EDP                               | 79 |  |  |  |

| PART X           | <b>OPTIMIZATION METHOD</b>                | 81 |  |  |  |

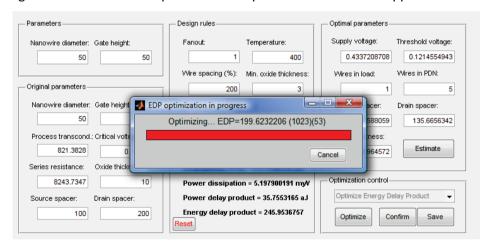

| 10.1             | Method                                    | 81 |  |  |  |

| 10.2             | Optimization variables                    | 82 |  |  |  |

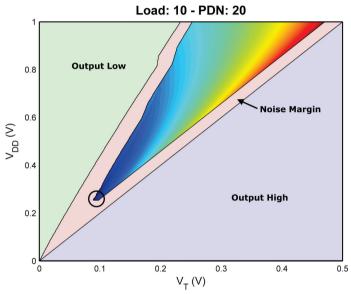

| 10.2             | 1 Voltage levels                          | 82 |  |  |  |

| 10.2             | 2 Nanowire quantity                       | 82 |  |  |  |

| 10.2             | 3 Spacer layers                           | 82 |  |  |  |

| 10.3             | Design rules                              | 82 |  |  |  |

| 10.3             | 1 Fan-out                                 | 83 |  |  |  |

| 10.3             | 2 Nanowire spacing                        | 83 |  |  |  |

| 10.3             | 3 Electrode configuration                 | 83 |  |  |  |

| 10.3             | 4 Minimum gate dielectric thickness       | 83 |  |  |  |

| 10.4             | Parameter scaling                         | 83 |  |  |  |

| 10.4             | 1 Series resistance                       | 84 |  |  |  |

| 10.4             | 2 Process transconductance parameter      | 84 |  |  |  |

| 10.4             | .3 Critical voltage                       | 84 |  |  |  |

| 10.5             | Noise                                     | 84 |  |  |  |

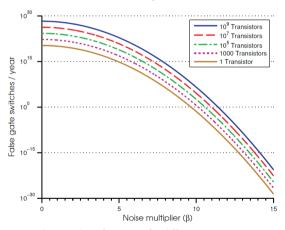

| 10.5             | 1 Regeneracy limitations                  | 85 |  |  |  |

| 10.5             | 2 Noise reduction                         | 86 |  |  |  |

| 10.5             | 3 Wire ratios                             | 87 |  |  |  |

| PART XI          | <b>OPTIMIZATION RESULTS</b>               | 89 |  |  |  |

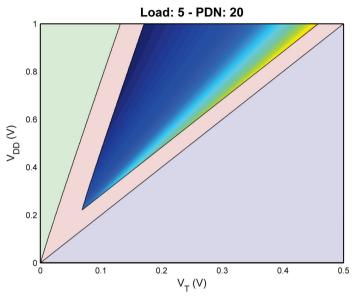

| 11.1             | Topography                                | 89 |  |  |  |

| 11.1             | 1 Spacer layers                           | 89 |  |  |  |

| 11.1             | .2 Array sizes                            | 90 |  |  |  |

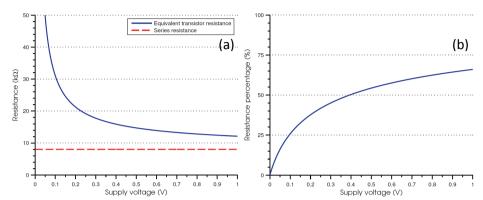

| 11.2             | Series resistance                         | 91 |  |  |  |

| 11.3             | Load capacitance                          | 91 |  |  |  |

| 11.4             | Voltage levels                            | 92 |  |  |  |

| 11.4             | 1 Supply voltage determination            | 93 |  |  |  |

| 11.4             | 93                                        |    |  |  |  |

| 11.5 Performance |                                           |    |  |  |  |

| 11.5             | 1 Propagation delay and power dissipation | 94 |  |  |  |

| 11.5             | 2 PDP and EDP                             | 94 |  |  |  |

| 11.6                               | Scaling summary                       | 97  |  |  |  |

|------------------------------------|---------------------------------------|-----|--|--|--|

| 11.6                               | 11.6.1 Model comparison               |     |  |  |  |

| 11.7                               | Optimal transistor characteristics    | 98  |  |  |  |

| 11.7                               | 7.1 Scaled EDP optimum design         | 98  |  |  |  |

| 11.7                               | 7.2 Minimum feature size transistor   | 99  |  |  |  |

| PART X                             | II Conclusions                        | 101 |  |  |  |

| 12.1                               | Modelling                             | 101 |  |  |  |

| 12.2                               | Circuit design                        | 101 |  |  |  |

| 12.3                               | Optimization                          | 102 |  |  |  |

| PART X                             | III Appendix                          | 103 |  |  |  |

| 13.1                               | Simple MOSFET sub-threshold modelling | 103 |  |  |  |

| 13.2                               | 103                                   |     |  |  |  |

| 13.3                               | 103                                   |     |  |  |  |

| 13.4 Example of a generated report |                                       | 107 |  |  |  |

| 13.5                               | Full capacitance model                | 111 |  |  |  |

| 13.5                               | 5.1 Electrode overlap Capacitances    | 111 |  |  |  |

| 13.5                               | Nanowire-coupled transistors          | 111 |  |  |  |

| 13.5                               | 5.3 Electrode fringe capacitances     | 113 |  |  |  |

| 13.5                               | 5.4 Array edge capacitances           | 115 |  |  |  |

| 13.6                               | Output-low solution                   | 116 |  |  |  |

| PART X                             | IV REFERENCES                         | 117 |  |  |  |

| PART X                             | V Index                               | 121 |  |  |  |

| 15.1                               | Figure index                          | 123 |  |  |  |

| 15 2                               | Table index                           | 126 |  |  |  |

#### Part I Introduction

## 1.1 Background

In the last decades, an ever-increasing transistor integration density has been observed. This development has led to great achievements in electrical engineering, such as the personal computer and the cell phone. There are however clear indications that the ongoing scaling of silicon-based electronics may come to a halt.

To overcome the problems that are facing the electronic industry, new and innovative solutions are needed. Some proposals are based on changes of transistor materials, e.g. going from silicon to high mobility III/V-materials, such as indium arsenide. One other major revolution is approaching sizes where quantum mechanical effects are prominent. Nanowires are an interesting concept since it incorporates both of these two concepts and much advancement have already been done in this field.

It is important to have models of high quality, in order to characterize nanowire devices, since it provides an insight into what benefits can be expected in the future. Using conventional figures of merits, derived from the models, also allows benchmarking against competing technologies.

#### 1.2 Workflow

During the course of the project, a highly automated workflow is devised. The workflow encompasses all steps from device manufacture, via device simulation and optimization back to the manufacturing of a new device. This workflow is illustrated in Figure 1.

Device manufacture and measurements are out of the scope of this thesis, but full automation of steps 3-6, by the development of specialized software is one of the main goals. This means that the only bottleneck for completing a full cycle is in the device manufacture and measurements. The result is that valuable person-hours of work can be allocated to more relevant tasks than routine and tedious modelling and optimization. The final step of the software suite is the output of a full modelling report and a proposal of a new optimized design, possibly to be put to the test at the next device manufacture.

Figure 1 – Proposed workflow, from device manufacture to report generation. All steps excluding 1 and 2 are implemented in the developed software and are highly automated.

#### 1.3 Structure

The report is divided into three main parts. The first section consists of transistor characterization, in which the transistor layout is described as well as the theory behind the modelling. This is followed by methodology and results of the modelling section. In the second main part, the transistors are implemented in an inverter utilizing ratioed logic. Timing analysis is performed and the problems with parasitic capacitances and resistances are addressed. Finally, optimization of the device is done and an analysis of what can be expected from a future downscaling of the devices will be presented.

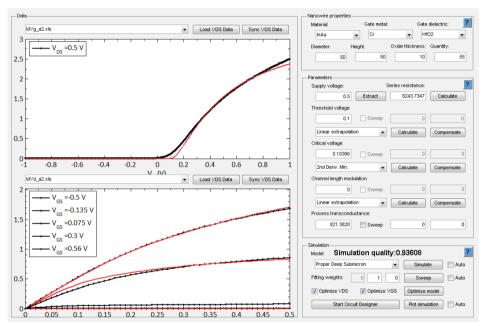

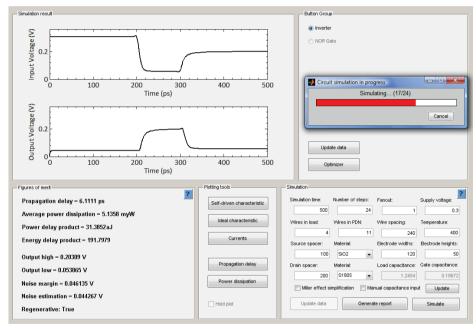

In order to provide the necessary tools for transistor modelling and circuit optimization, a computer application is developed. It features the ability to load transistor measurement data as provided from the measurement setups. By using a number of simple controls, it is possible to obtain full transistor characterization based on a range of different MOSFET models. Additionally, the software features the ability to simulate and optimize a ratioed logic inverter utilizing the previously characterized transistors.

#### Part II THE NWFET

#### 2.1 Transistor structure

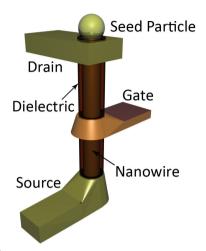

The transistor that is being studied in this thesis is based on the Wrapped Insulated Gate Field Effect Transistor (WIGFET). Unlike the conventional planar MOSFET, this transistor has a vertical structure utilizing a nanowire as channel.

#### 2.2 Nanowire

The nanowire consists of a semiconductor material, often utilizing high-mobility III/V-materials such as indium arsenide (InAs). The diameter of the nanowire is in the range of tens of nanometres and thus well in the realm of nanotechnology. In reality, the nanowire has a hexagonal cross-section area, but it is often approximated as being of a cylindrical shape.

Figure 2 – A WIGFET consisting of a single nanowire.

#### 2.2.1 **Growth**

Nanowires are often grown using standard epitaxial growth techniques, with the help of a catalytic seed particle. The seed particle is positioned with the aid of electron beam lithography, which allows for placement with a high resolution. The size of the seed particle determines the diameter of the nanowire, while the length is controlled by the growth time.

#### 2.2.2 Field-dependent mobility

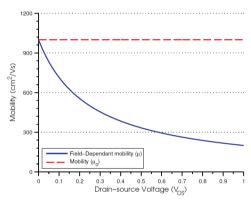

Since the nanowire acts as a MOSFET channel, is preferred to have a high mobility. In short channel devices, the mobility is highly dependent on the electrical field along the wire. In addition, it directly influences the current levels and the onset of saturation. It should be noted that this saturation is strictly due to velocity saturation, which is described in section 2.2.3.

The field-dependent mobility is often used in physical models describing the DC-characteristics of transistors. In more simple models however, it is sufficient to use the mobility at zero bias,  $\mu_0$ .

The field-dependent mobility,  $\mu$ , is given by the equation below:

$$\mu = \mu_0 \left( 1 + \frac{\mu_0 V_{DS}}{v_{sat} L} \right)^{-1} \tag{1}$$

In the above expression,  $v_{sat}$  is the saturation velocity, L the effective channel length and  $V_{DS}$  the drain to source voltage (the end terminals of the nanowire). From now on, the effective channel length is assumed equal to the height of the gate electrode. In Figure 3, the expression above characterizing the field-dependent mobility is plotted as a function of the applied voltage along the channel.

Figure 3 – Field-dependent mobility dependence on the applied voltage.

It is seen that the mobility diminishes with an increased  $V_{DS}$ . Within normal operation voltages, the mobility usually does not extend below a third of the zero-field mobility.

#### 2.2.3 Saturation velocity

In recent microelectronic technologies, the drive current is limited by velocity saturation. Under normal operation conditions, the velocity of the carriers in the channel increases with the applied electric field. However, at some point a critical electric field is reached, where the carrier velocity saturates. At this point, any excess electron energy is released by phonon emission.

If the field-independent mobility and the critical voltage,  $V_c$ , is known, it is possible to calculate saturation velocity,  $v_{sat}$ , by the following expression:

$$v_{sat} = \frac{\mu_0 V_c}{L} \tag{2}$$

#### 2.3 Gate dielectric

The nanowire is surrounded by a gate electrode, which is isolated by a dielectric material. In order to maximize the gate capacitance and minimize the leakage current between gate and channel, a high-k dielectric, such as  $HfO_2$ , is coating the nanowire. The gate dielectric is often deposited by Atomic Layer Deposition (ALD), which is a technique highly suitable for vertical structures [1].

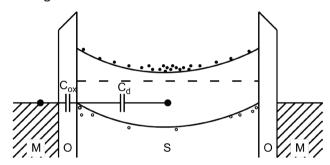

#### 2.3.1 Gate capacitance

The gate capacitance is modelled as an oxide capacitance in series with a depletion capacitance. The oxide and depletion capacitances are shown in the band diagram of Figure 4 and are described in more detail below.

Figure 4 – Band diagram along the nanowire cross section.

#### Oxide capacitance

The gate oxide capacitance,  $C_{ox}$ , is the conventional parameter to model the gate capacitance in MOSFETs. The size of the oxide capacitance parameter determines the number of carriers in the channel for a given gate to source voltage,  $V_{GS}$ . For a cylindrical geometry, which applies to a nanowire, the oxide capacitance per unit gate area,  $C_{ox}$ , can be expressed as [2], [3]:

$$C_{ox} = \frac{\varepsilon_0 \varepsilon_r}{R} \ln^{-1} \left( 1 + \frac{t_{ox}}{R} \right) \tag{3}$$

Here  $\varepsilon_0$  is the permittivity of free space,  $\varepsilon_r$  the relative permittivity of the gate oxide,  $t_{ox}$  the gate oxide thickness and R the radius of the cylindrical wire. It should be noted that the relative permittivity of the gate dielectric could vary a lot depending on the material choice and processing imperfections.

#### **Depletion capacitance**

However, the oxide capacitance is not the only capacitance affecting the channel of the nanowire. A capacitance is formed in series with the oxide capacitance. This is due to the depletion of carriers along the cross section of the wire. The depletion capacitance  $\mathcal{C}_d$ , is given by[4]:

$$C_d = \frac{4\pi\varepsilon_0\varepsilon_s}{R} \tag{4}$$

Here  $\varepsilon_s$  is the relative permittivity of the semiconductor material. From Figure 4, it is seen that the complete gate capacitance,  $C_G$ , is given as  $C_{ox}$  and  $C_d$  in series:

$$C_G = \frac{C_{ox} C_d}{C_{ox} + C_d} \tag{5}$$

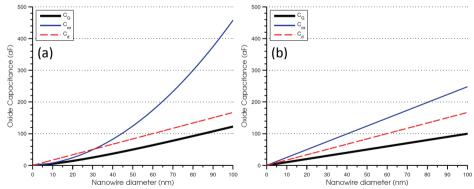

#### Scaling dependence

In Figure 5, the scaling dependence of the oxide capacitance on wire diameter is shown for two different scaling behaviours. In one case, the thickness of the dielectric scales with the nanowire diameter. Furthermore, the gate height is scaled to remain equal to the wire diameter. In the other case, the oxide thickness is held constant.

Figure 5 – Oxide capacitance with (a) non-scaling and (b) scaling oxide thickness as the nanowire geometries are scaled.

As can be easily realized, the capacitance decreases linearly with evenly scaled geometries. A more complex scaling relationship is seen when the thickness is held constant, with a behaviour that has both linear and logarithmic parts. It is also not surprising that the diameter dependence of the gate capacitance

mainly follows the smallest component. The both figures share common points at 50 nm diameter. This is expected due to the scaling having the origin at that point.

#### 2.4 Contacts

In order to maximize the gate area, providing best possible electrostatic control, the gate is wrapped around the nanowire. This is an advantage compared to planar structures, since it results in a more effective depletion of the semiconductor. Apart from the gate electrode, metal electrodes also contacts the source and drain regions. The drain is contacted at the top of the nanowire, while the source contact can be of different configurations.

In early developments of these transistors, the substrate was used as contact. This is possible thanks to the high inherent mobility of indium arsenide. More recently, however, there is a trend of actively contacting the source side of the wire. A single nanowire transistor structure, with contacted source side, is illustrated in Figure 2.

The ungated portions of the nanowire contribute heavily to the parasitic resistances. Another contribution is from the metal contacts, which exhibits Schottky barriers. The series resistance affects the operation of the devices by reducing the drive current. Also, as shown in Figure 25, the transistor characteristic shows a more resistive behaviour, which is often far from that of an ideal transistor. Both of these negative effects can be reduced by doping the nanowire and a lot of work is being done in order to make this possible.

# 2.5 Array configuration

A complete nanowire transistor can consist of either a single nanowire or an array of multiple wires. By increasing the number of nanowires in the transistor, the drive current is increased, while at the same time reducing the series resistance. On the other hand, the increased size of the array, results in higher parasitic capacitances.

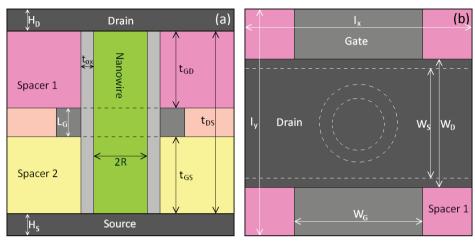

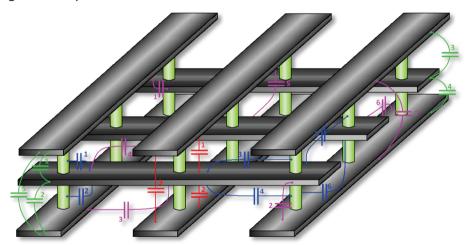

An array of multiple nanowires can be described by the unit cell, presented in Figure 6. The geometrics defined in the unit cell layout are used for the modelling of the parasitic capacitances and resistances. A full transistor array is acquired by placing multiple unit cells next to each other.

Figure 6 - Transistor unit cell (a) from the side and (b) from above.

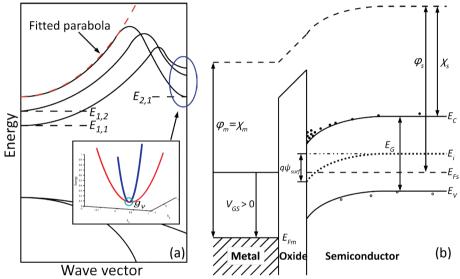

Figure 7 – A WIGFET network array consisting of multiple nanowires. The source contact is at the bottom of the array, while the drain is at the top. The gate is in a networked structure and wrapped around the individual nanowires. The transparent parts are the drain and source spacer layers respectively.

The contacts are arranged in a network formation so that each subsequent layer is perpendicular to the previous. By using a networked electrode structure, the parasitic overlap capacitances are kept low. This allows for a decrease in the thickness of the spacer layers, in turn reducing the parasitic series resistance. In order to simplify the device manufacture, the width of the

contacts may simply be set to the width of the unit cell. However, large contacts are ideally avoided due to the large parasitic capacitances inherent to such a design.

The spacer layers are used to separate the different contacts. They ideally consist of a high-stability, low-k material and most commonly  $SiO_2$  or photo resists are used to construct these layers. A typical 3x3 array is illustrated in Figure 7.

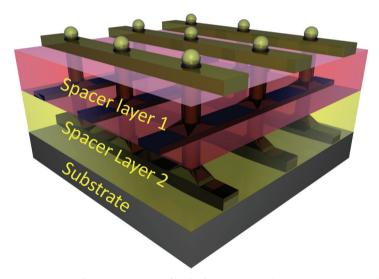

#### 2.6 Band structure

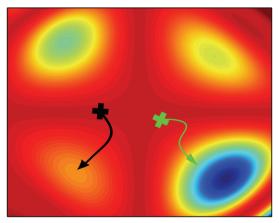

The dimensions of nanowires are on the length scale, where physics based on quantum mechanics is prominent. It is therefore expected that the band structure of the semiconductor material play a large role in description of the carrier transport characteristics. In two of the three spatial directions, the semiconductor is subject to quantum confinement and subbands are formed. These subbands, which may vary in shape, have an energy displacement in respect to each other. The local energy minima of such bands are called valleys and a subband can consist of multiple valleys. An example of a general band structure is presented in Figure 8(a).

Multiple bands contribute to the current through the nanowires. The carriers occupy states in the different subbands and the occupation shows a strong dependence on the energy. Low energy subbands will have a large contribution whereas higher subbands have a smaller one.

It is possible to derive a structural parameter,  $\varphi$ , which is used to scale the current through the transistor by adding up the contribution of all the subbands [5]:

$$\varphi = \sum_{n} \sum_{v} \left( g_{v} \sqrt{m_{d,v}} e^{-\frac{E_{v,n} - q\psi_{T}}{q\phi_{th}}} \right)$$

(6)

In the equation above,  $E_{v,n}$  is the local energy minimum v of the nth subband. The parameter  $m_{d,v}$  is the density of states effective mass of valley v and can be acquired by determining the curvature of a parabolic fitting of the affected valley. The valley degeneracy,  $g_v$ , represents the number of different contributions along k-vectors with the same relationship to the quantum

confinement. The relationship between these parameters is defined in Figure 8(b). Furthermore,  $\varphi_{th}$  is the thermal voltage, which is defined as:

$$\varphi_{th} = \frac{k_B T}{q} \tag{7}$$

Here  $k_B$  is the Boltzmann constant, T the temperature and q the elementary charge.

Figure 8 – (a) Band structure with quantum confinement, (b) Energy band diagram of a standard MOSFET.

#### 2.6.1 Surface potential at threshold point

The surface potential is defined as the band bending due to the Fermi level and the applied gate voltage. The surface potential at threshold point,  $\psi_T$ , is the band bending when the applied gate voltage is equal to the threshold voltage. Ideally, this potential should be a function only of the nanowire doping concentration [6]. However, in this case, it is also dependent on charges in the insulator interface and thus on the processing steps in the production of the transistor.

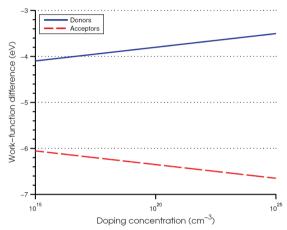

#### 2.6.2 Work function difference

The work function of a material, is the energy required to move an electron from a state at the Fermi level,  $E_F$ , to the vacuum level. The work function difference,  $\varphi_{ms}$ , between the metal (m) and the semiconductor (s), plays a

large role in the scaling of the current levels. Thus, it is often used in physical transistor models.

The work function of a metal can be acquired from tables. The work function of the semiconductor however, is highly dependent on the number of carriers in the semiconductor. The number of carriers is, in turn, dependent on the doping levels in the nanowire. Since not much is known about these levels, no calculation of the work function difference is possible. The definitions of both the relevant work functions are illustrated in Figure 8(b).

However, if the doping levels are quantified in the future, the Fermi level, and in turn the work function difference, can be calculated [7]. Two cases need to be considered: n-doped and p-doped materials. For the n-doped material,  $\varphi_{ms}$  is obtained by:

$$E_C - E_F = -kT \ln \left(\frac{N_D}{N_C}\right) \tag{8}$$

$$\varphi_{ms} = \chi_m - \left(\chi_s + (E_C - E_F)\right) \tag{9}$$

In the equations above,  $\chi$  denotes the electron affinities for the metal and semiconductor,  $N_D$  is the donor doping concentration,  $N_C$  the conduction band effective density of states (DOS),  $E_C$  the energy at the bottom of the conduction band and  $m_0$  the electron mass.

Similarly, for a p-doped material, the work function difference is given by the following set of equations.

$$E_F - E_V = -kT \ln \left( \frac{N_A}{N_V} \right) \tag{10}$$

$$\varphi_{ms} = \chi_m - \left(\chi_s + E_G - (E_F - E_V)\right) \tag{11}$$

Here, the parameter  $E_V$  is the valence band energy,  $N_A$  the acceptor dopant concentration,  $N_V$  the valence band effective DOS and  $E_G$  the bandgap energy. The one-dimensional effective density of states,  $N_{1D}$ , of both the conduction band and the valence band is calculated by the same expression:

$$\left[N_{1D} = \sqrt{\frac{m_d m_0 kT}{2\pi\hbar^2}}\right] \tag{12}$$

To acquire the density of states, the density of states effective mass is substituted by either the effective electron or hole mass, for conduction or valence band DOS respectively.

In Figure 9, the work function difference dependence on the doping concentration is shown. It is observed that the work function difference is approximately constant at -3.5 eV for n-type doping, while it is around -6.5 eV for p-type doping.

Figure 9 – Work function difference dependence on the doping concentration.

# Part III PARASITIC CAPACITANCES

There are many different capacitances associated with the transistor array configuration. These are each contributing to the total parasitic capacitance and they are all modelled and discussed in this section.

# 3.1 Capacitance types

The capacitances can be divided into four main groups, based on the geometry of their respective electric fields. These groups are overlap capacitances, wire capacitances, fringing capacitances and edge capacitances. They are here presented with their respective subscripts: o, w, f and e. The device structure that forms the basis for the modelling is presented in Figure 10, demonstrating all the modelled parasitic capacitances. The numbers in the figure are explained in Table 1.

Figure 10 – The different parasitic capacitances in a WIGFET array.

The numbers and colours are explained in Table 1.

|         | 1            | 2            | 3            | 4            | 5            | 6            | 7            |

|---------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Red     | $C_{GD,o}$   | $C_{GS,o}$   | $C_{DS,o}$   | -            | -            | -            | -            |

| Green   | $C_{GD,e,x}$ | $C_{GS,e,x}$ | $C_{GD,e,y}$ | $C_{GS,e,y}$ | $C_{DS,e,x}$ | -            | -            |

| Blue    | $C_{GD,w}$   | $C_{GS,w}$   | $C_{GD,w,y}$ | $C_{GS,w,y}$ | $C_{GD,w,x}$ | $C_{GS,w,x}$ | -            |

| Magenta | $C_{GD,f}$   | $C_{GS,f}$   | $C_{GS,f,y}$ | $C_{GD,f,y}$ | $C_{GD,f,x}$ | $C_{GS,f,x}$ | $C_{DS,f,y}$ |

TABLE 1 - THE DIFFERENT PARASITIC CAPACITANCES IN A WIGFET ARRAY.

#### 3.1.1 General assumptions

In the following sections, each capacitance type is modelled, but for the sake of simplicity, only the general expressions are presented. The full expressions can instead be found in the appendix.

Some simplifications are made in the analysis, in order to get the general expressions. The electrode widths, lengths and thicknesses are all assumed equal. This means that, when referring to the electrode E, either the source or drain can be substituted. Some capacitances are subscripted with an r, which means that the capacitances are affecting adjacent unit cells. For these capacitances, the r can be replaced by either a x or y direction.

#### Test parameter set

To produce the plots presented in this part, the parameter set in Table 2 is used. This parameter set is consistent with the transistor layout used in the modelling section. The spacing between nanowires, l, are held equal for both directions and all metal electrodes are set at the same thickness,  $W_E$ , and width,  $H_E$ . The spacer layer thicknesses, t, are also presented with their corresponding relative permittivity.

|                    | <i>l</i><br>(nm)           | $W_E$ (nm)       | <i>Н<sub>Е</sub></i><br>(nm) | $t_{GD}$ (nm)      | <i>t<sub>GS</sub></i> (nm) | <i>t<sub>DS</sub></i> (nm) |

|--------------------|----------------------------|------------------|------------------------------|--------------------|----------------------------|----------------------------|

| Test parameter set | 200                        | 100              | 50                           | 200                | 100                        | 350                        |

|                    | <i>t<sub>ox</sub></i> (nm) | <i>R</i><br>(nm) | $arepsilon_{GD}$             | $\varepsilon_{GS}$ | $\varepsilon_{ox}$         |                            |

| Test parameter set | 10                         | 50               | 4.5                          | 2.5                | 15                         |                            |

TABLE 2 - PARAMETER SET FOR CAPACITANCE COMPARISON ANALYSIS.

However, the actual spacer layer thicknesses are not used in the equations describing the parasitic capacitances below. Since multiple materials may occupy the space between electrodes, an effective spacer layer thickness, d, is calculated. This is done by using the different relative permittivities of the intermediate materials. As an example,  $d_{DS}$  is determined by scaling the drain side spacer with the relative permittivity of the source side.

#### 3.1.2 Scaling rules

It is important to study how the parasitic capacitances change during device scaling, in order to predict what could be gained in terms of performance. Scaling by two different methods is presented for all capacitances in their corresponding sections. In the first scaling method, only the parameters of the nanowire, diameter and length, are changed. However, this is a quite unrealistic case, since it is expected that a better solution would be to scale down all relevant dimensions in the same manner. In the second scaling regime, dimensions such as the electrode widths and height, are scaled linearly with the nanowire diameter.

# 3.2 Overlap capacitances

The main idea behind the use of the networked layout in Figure 10, is that it is possible to reduce some of the overlap parasitics. There are three different overlap capacitances, acting between pairs of the three metal electrodes: source, drain and gate. To model the magnitude of these capacitances, a standard parallel plate (PP) capacitor model is used.

$$C_{PP} = \frac{\varepsilon_0 \varepsilon_r A}{d} \tag{13}$$

In the equation above, A is the overlap area,  $\varepsilon_0$  the permittivity of free space,  $\varepsilon_r$  the relative permittivity of the intermediate material and d the distance between the parallel plates. By subtracting the cross-sectional area of the nanowire from the overlap of the corresponding electrodes, it is found that the capacitances can be described by the following set of equations.

$$C_{GE,o} = \frac{\varepsilon_0 \varepsilon_{GE} (W_E^2 - \pi (R + t_{ox})^2)}{d_{GE}}$$

$$C_{DS,o} = \frac{\varepsilon_0 \varepsilon_{GS} (W_E l - \pi (R + t_{ox})^2)}{d_{DS}}$$

(14)

$$C_{DS,o} = \frac{\varepsilon_0 \varepsilon_{GS} (W_E l - \pi (R + t_{ox})^2)}{d_{DS}}$$

(15)

In order for the entire spacer layer to have the same relative permittivity in the drain to source overlap capacitance, the distance between gate and drain is recalculated to obtain an effective distance,  $d_{DS}$ .

#### **3.2.1 Scaling**

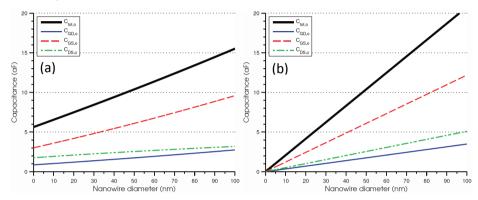

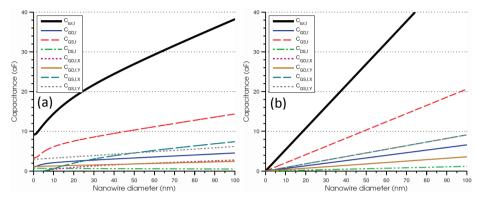

Figure 11 shows how the overlap capacitance is affected by the two different scaling methods. It is seen that the overlap capacitance is reduced with shrinking nanowires and electrodes.

Figure 11 – Overlap capacitances as a function of the nanowire diameter, without device scaling in (a) and with scaling in (b).

# 3.3 Wire capacitances

A lot of the parasitic capacitance can be attributed to the capacitance between the nanowire and the surrounding gate electrode. There are six such capacitances, as shown in Figure 10: two within the unit cell and four between adjacent unit cells. To model these capacitances, the procedure presented by [8] is used.

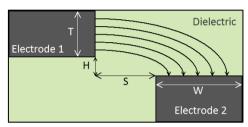

The capacitances between the nanowires and the gate electrode is modelled with the electric field lines stretching from the sidewall (SW) of one electrode to the top of another electrode. The formula used for all the wire capacitance expressions is presented in (16) and the substitution of the effective electrode height is shown in (17):

$$C_{SW} = \frac{2}{\pi} \varepsilon_0 \varepsilon_r \ln \left( \frac{H + T' + \sqrt{S^2 + T'^2 + 2HT'}}{S + H} \right)$$

(16)

$$T' = Te^{\frac{W+S-\sqrt{S^2+T^2+2HT}}{\tau W}}$$

(17)

Here  $\tau$  is an empirical parameter equal to about 3.7. All the other variables are simply geometrical parameters, which are presented in Figure 12. It is

important to note that (16) gives the capacitance per unit depth. In order to obtain the absolute capacitance, scaling with the smallest of the affected depths has to be done.

Figure 12 – Geometrical parameters for capacitance formulas.

## 3.3.1 Geometrical mapping

In order to model the wire capacitances, the gate electrode is split into two subsections: one part circumventing the wire and one part connecting to the next nanowire. The geometrical parameters are simply extracted from the unit cell, but great care has to be taken in order to ensure that the depth scaling is correctly modelled.

The capacitance part that is surrounding the wire is simply scaled with the circumference of the nanowire. However, in order to scale the section that is contacting to the next wire, it is important to realize that not all parts of the wire are affected equally, because of the curved shape. It is proposed that this is solved by first attributing relative contributions by the use of sinusoidal weighting. Thus, the contribution from the middle portion, as seen from the electrode, is one and the contributions from the outer edges are zero. These contributions are added up and scaled with the diameter of the nanowire. This kind of modelling should give a result closer to the real value, than using only the diameter as scaling depth.

# 3.3.2 The expressions

The two wire capacitances formed within the unit cell is given by (18), with the corresponding substitutions in (19). It should be noted that the depth-scaling factor, due to sinusoidal mapping, is characterized by a scaling factor of  $\pi^{-1}$  in respect to the circumference scaling.

$$C_{GE,w} = 4R\varepsilon_0\varepsilon_{GE} \left( \ln \left( \frac{a_1}{\varepsilon_{GE}} t_{ox} \right) + \frac{1}{\pi} \ln \left( \frac{a_2}{\varepsilon_{GE}} t_{ox} + \frac{W_E}{2} - R - t_{ox} \right) \right)$$

$$a_1 = T_{GE,w,1} + \sqrt{\left( \frac{\varepsilon_{GE}}{\varepsilon_{ox}} t_{ox} \right)^2 + T_{GE,w,1}^2}$$

$$a_2 = T_{GE,w,2} + \sqrt{\left( \frac{\varepsilon_{GE}}{\varepsilon_{ox}} t_{ox} + \frac{W_E}{2} - R - t_{ox} \right)^2 + T_{GE,w,2}^2}$$

(18)

$$\begin{bmatrix} a_{1} = T_{GE,w,1} + \sqrt{\left(\frac{\varepsilon_{GE}}{\varepsilon_{ox}}t_{ox}\right)^{2} + T_{GE,w,1}^{2}} \\ a_{2} = T_{GE,w,2} + \sqrt{\left(\frac{\varepsilon_{GE}}{\varepsilon_{ox}}t_{ox} + \frac{W_{E}}{2} - R - t_{ox}\right)^{2} + T_{GE,w,2}^{2}} \\ \frac{\frac{\varepsilon_{GE}}{\varepsilon_{ox}}t_{ox} + \frac{W_{E}}{2} - R - t_{ox} - \sqrt{\left(\frac{\varepsilon_{GE}}{\varepsilon_{ox}}t_{ox}\right)^{2} + d_{GE}^{2}}}{\left(\frac{W_{E}}{2} - R - t_{ox}\right)^{\tau}} \\ T_{GE,w,1} = d_{GE}e \\ \frac{\frac{\varepsilon_{GE}}{\varepsilon_{ox}}t_{ox} + \frac{l}{2} - R - t_{ox} - \sqrt{\left(\frac{\varepsilon_{GE}}{\varepsilon_{ox}}t_{ox} + \frac{W_{E}}{2} - R - t_{ox}\right)^{2} + d_{GE}^{2}}}{\left(\frac{l - W_{E}}{2}\right)^{\tau}}$$

$$(19)$$

There are four different wire capacitances between unit cells, as seen in Figure 10. These have approximately the same geometries as the ones within a unit cell, with the exception that the extra distance has to be accounted for. After derivations, it is shown that these capacitances can be modelled by:

$$C_{GE,w,r} = \frac{4R}{\pi} \varepsilon_0 \varepsilon_{GE} \ln \left( \frac{T_{GE,w,r} + \sqrt{\left(\frac{\varepsilon_{GE}}{\varepsilon_{OX}} t_{ox} + \frac{l - W_E}{2}\right)^2 + T_{GE,w,r}^2}}{\frac{\varepsilon_{GE}}{\varepsilon_{OX}} t_{ox} + \frac{l - W_E}{2}} \right)$$

(20)

$$T_{GE,w,r} = d_{GE} e^{\frac{\frac{\varepsilon_{GE}}{\varepsilon_{ox}} t_{ox} + \xi + \epsilon \sqrt{\left(\frac{\varepsilon_{GE}}{\varepsilon_{ox}} t_{ox} + \frac{l - W_E}{2}\right)^2 + d_{GE}^2}}}{\xi \tau}$$

$$\xi = \begin{cases} \frac{l - W_E}{2} & \text{if } r = y \\ \frac{W_E}{2} - R - t_{ox} & \text{if } r = x \end{cases}$$

$$\epsilon = \begin{cases} \frac{l - W_E}{2} & \text{if } r = y \\ l - \frac{W_E}{2} & \text{if } r = x \end{cases}$$

$$(21)$$

There are no modelled capacitances between the source and drain contact to their respective nanowire section, since they are approximated to be at the same potential.

# Scaling

According to the scaling graphs in Figure 13, the wire capacitances are independent on the electrode scaling. This is because the nanowire dimensions are greatly dominating the modelling up to the point where there is no electrode dependence. In reality however, the scaling of the wire capacitances is expected to be even more pronounced. This is because the nanowire starts to shield the electric field lines, when there is a small spacing between them.

Figure 13 – Wire capacitances as a function of the nanowire diameter, without device scaling in (a) and with scaling in (b).

# 3.4 Fringe capacitances

There are three different fringe capacitances inside every unit cell and a total of four between neighbouring unit cells. All but one of the fringe capacitances are due to the fringing fields between the edge of one electrode and the flat side of another. These capacitances can be described by the sidewall formula (17). The one that does not conform to the sidewall formula is  $\mathcal{C}_{DS,f}$ , which acts between the long side edges of the drain and source electrodes. These capacitances are described by[8]:

$$C_{HC} = \frac{1}{\pi} \varepsilon_0 \varepsilon_{di} \left( 1 + \frac{2W}{S} \right) \tag{22}$$

The distance, S, is realized to be  $d_{DS}$ , while W is the thickness of the electrodes. Scaling with the length of the unit cell along the long-sides of the source and drain electrodes, reveals that the capacitance is described by the following expression:

$$C_{DS,f} = \frac{2(l - W_E)}{\pi} \varepsilon_0 \varepsilon_{GS} \ln\left(1 + \frac{2H_E}{d_{DS}}\right)$$

(23)

The other fringe capacitances within the unit cell are found by obtaining the necessary metrics from the unit cell layout and applying them to (16). The two capacitances are presented below:(25)

$$C_{GE,f} = \frac{8W_E}{\pi} \varepsilon_0 \varepsilon_{GE} \ln \left( \frac{T_{GE,f} + \sqrt{d_{GE}^2 + T_{GE,f}^2}}{d_{GE}} \right)$$

$$T_{GE,f} = \frac{l - W_E}{2} e^{\frac{H_E + d_{GE} - \sqrt{d_{GE}^2 + \left(\frac{l - W_E}{2}\right)^2}}{H_E \tau}}$$

(25)

$$T_{GE,f} = \frac{l - W_E}{2} e^{\frac{H_E + d_{GE} - \sqrt{d_{GE}^2 + \left(\frac{l - W_E}{2}\right)^2}}{H_E \tau}}$$

(25)

The capacitances between adjacent unit cells are derived by the same principle. However, there are some constraints for the formulas to work, due to limitations in the original derivation. The inter unit cell capacitances are presented in the following equation:

$$C_{GE,f,r} = \frac{4W_E}{\pi} \varepsilon_0 \varepsilon_{GE} \ln \left( \frac{c}{d_{GE} + \frac{l - W_E}{2}} \right) \quad \text{If } d_{GE} > \frac{l - W_E}{2}$$

(26)

$$\begin{bmatrix} c = \frac{l - W_E}{2} + T_{GE,f,r} + \sqrt{d_{GE}^2 + T_{GE,fri,r}^2 + (l - W_E)T_{GE,f,r}} \\ T_{GE,f,r} = \left(\frac{l}{2} - R - t_{ox}\right) e^{\frac{H_E + d_{GE} - \sqrt{d_{GE}^2 + \left(\frac{l}{2} - R - t_{ox}\right)^2 + \left(\frac{l}{2} - R - t_{ox}\right)(l - W_E)}} \end{bmatrix}$$

(27)

#### Scaling

In Figure 14, the scaling of the fringe capacitance is presented. It is clear that with shrinking wire dimensions, it is better to scale the electrodes as well, instead of keeping them constant. This is a similar observation as that for the overlap capacitances.

Figure 14 – Fringe capacitances as a function of the nanowire diameter, without device scaling in (a) and with scaling in (b).

# 3.5 Edge capacitances

In a quadratic array, as shown in Figure 10, there are also some capacitances that only affect the outer unit cells. There are five such capacitances and these can be described by two different formulas.

The drain to source capacitance, at the array edge, is described by the half circle formula. By applying the corresponding geometrics, it is realized that the capacitance is described by:

$$C_{DS,e,y} = \frac{W_E}{\pi} \varepsilon_{GS} \ln \left( 1 + \frac{2H_E}{d_{DS}} \right)$$

(28)

To calculate the four remaining edge capacitances, a different approach has to be applied. This is due to the edge of the gate electrode not being directly below or above the drain or source edges. To solve this, (29) can be used instead [8].

$$C_{top,top} = \frac{\varepsilon_0 \varepsilon_{di} W}{\frac{H+T}{\alpha} + \pi W \left( \ln\left(1 + \frac{2W}{S}\right) + e^{-\frac{S+T}{3S}}\right)^{-1}}$$

(29)

$$\left[\alpha = e^{-\frac{H+T}{S+W}}\right] \tag{30}$$

By applying the appropriate geometrics, the following expression for the remaining edge capacitances is derived:

$$C_{GE,e,r} = \frac{W_E \varepsilon_0 \varepsilon_{GE}}{\pi} \frac{2H_E}{\frac{l-W_E}{\alpha_{GE,e,r}} + 2H_E \left( \ln\left(1 + \frac{2H_E}{d_{GE}}\right) + e^{-\frac{l-W_E}{6d_{GE}} \cdot \frac{1}{3}} \right)^{-1}}{\left[\alpha_{GE,e,r} = e^{-\frac{l-W_E}{2(d_{GE} + H_E)}}\right]}$$

(31)

#### Scaling

Figure 15 depicts the two scaling behaviours of the edge capacitances. As before, shrinking dimensions leads to smaller parasitic capacitances. It can thus be concluded that it is advisable, from a performance point of view, to minimize the geometrical dimensions of the nanowires and the surrounding structure.

Figure 15 – Edge capacitances as a function of the nanowire diameter, without device scaling in (a) and with scaling in (b).

# 3.6 Array size dependence

The 21 different capacitances each show different dependences on the number of nanowires, N, in a quadratic array. All the capacitances that operate within the unit cell have a simple linear characteristic. However, the wire dependence for the capacitances affecting adjacent unit cells, is found to be  $\left(N-\sqrt{N}\right)$ . The edge capacitances, as the name implies, only affect the edge unit cells and therefore has a  $2\sqrt{N}$  relationship.

By combining the nanowire quantity scaling behaviour for the different capacitances, the two expressions, (32) and (33) are obtained.

$$C_{GE} = N(C_{GE,o} + C_{GE,w} + C_{GE,f}) + 2\sqrt{N}(C_{GE,e,x} + C_{GE,e,y}) + (N - \sqrt{N})(C_{GE,w,x} + C_{GE,w,x} + C_{GE,f,x} + C_{GE,f,y})$$

$$C_{DS} = N(C_{DS,o} + C_{DS,f,y}) + 2\sqrt{N}(C_{DS,e,x})$$

(32)

$$\overline{C_{DS} = N(C_{DS,o} + C_{DS,f,y}) + 2\sqrt{N}(C_{DS,e,x})}$$

(33)

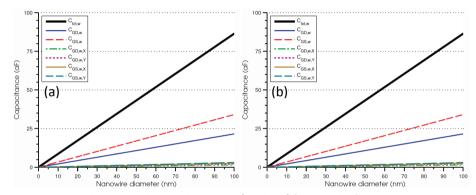

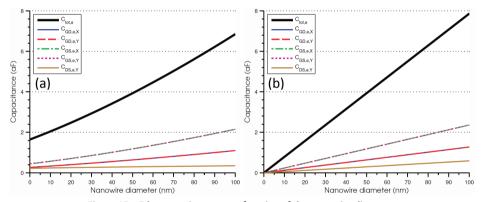

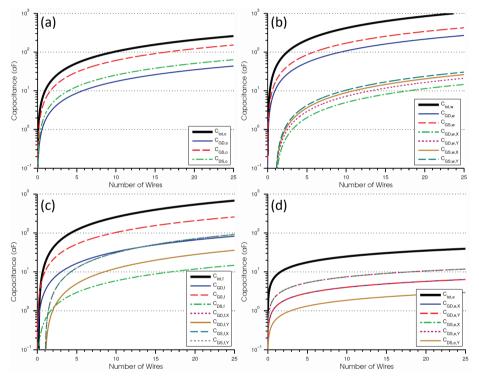

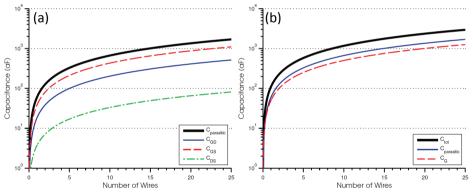

In Figure 16, the wire dependence is presented for the different capacitance groups and their respective contributions are evaluated.

Figure 16 – Comparison between the magnitudes of the different capacitances. (a) Overlap capacitances, (b) Wire capacitances, (c) Fringe capacitances and (d) Edge capacitances.

From Figure 16(a), it is apparent that the gate to source capacitance is the largest of the overlap capacitances. This is followed by the drain to source capacitance, while the gate to drain capacitance is the smallest of the three. The reason for the larger gate to source capacitance is that the spacer layer between those connectors has a higher relative permittivity.

Figure 16(b) shows the wire capacitances and it is clearly observed that the capacitances operating within a unit cell are dominating the ones between adjacent cells. This is due to the much smaller distances involved for the intracell capacitances. The shape of the curves is also differing slightly, which is due to the wire dependence in (32).

The same behaviour that describes the wire capacitances, also describes the shape of the fringing capacitances (Figure 16(c)). This is to be expected, since the same type of expression determines the magnitude of these capacitances.

Lastly, the edge capacitances are shown in Figure 16(d). These capacitances do not vary as much with N as the other capacitances. The values are also quite low, which is to be expected due to the small surfaces at the edges.

# 3.7 Simplifications

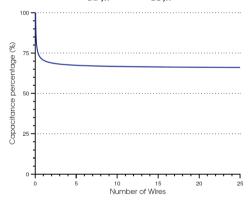

By studying Figure 16, it is realized that many simplifications is possible for the total parasitic capacitance expression. There are essentially two parasitic capacitances dominating all the other 19. These are the two wire capacitances operating within each unit cell:  $C_{GD,w}$  and  $C_{GS,w}$ .

Figure 17 – The quality of the simple analytical capacitance expressions in relation to the full capacitance model.

In Figure 17, the sum of the two capacitances and the intrinsic gate capacitance is compared to the sum of all the others. The figure shows the quality of the simplification as a function of the number of nanowires in the array. Since there is an approximately 70 % correlation between the two, it is deemed a valid approximation to only account for the two wire capacitances in the case of the test transistor. This approximation should still be valid when all transistor dimensions scale equally, since it has been shown that all capacitances scale linearly in this regime.

# Part IV TRANSISTOR MODELLING

# 4.1 MOSFET types

A MOSFET can be operated in different modes, depending on the characteristics of the transistor. Transistors are generally divided into four different main types, depending on their respective charge carrier and operation characteristics.

## 4.1.1 Majority charge carrier

A first distinction can be made between p-type and n-type devices. This distinction is made based on which charge carrier, i.e. electrons or holes, dominates the conducting channel. Effectively, this means that an n-type transistor becomes more conducting with increasing positive gate voltage, while the conductance of a p-type device increases with a more negative gate voltage.

### 4.1.2 Enhancement and depletion mode

A further distinction is made between devices that are either conducting or isolating, under zero gate voltage. An enhancement mode device needs an applied gate voltage to form a conducting channel. This is opposed to a depletion mode device, which is conducting at zero applied gate voltage. All the transistors studied in the project will be enhancement mode, n-type devices, because of limitations in the processing technology at this time.

# 4.2 Regions

The main characteristic of all the simple MOSFET models is quite similar, so the same arguments about their voltage dependences are true for all of them. All these simple models are based on a set of expressions, which govern the current for different regions. Usually three regions are identified and the region that applies depends on the voltages over the transistor.

The first is the cut-off region, in which the gate to source voltage is below the threshold voltage. The threshold voltage is defined as the gate to source voltage, above which the transistor is said to be "on" [9]. In this case, the channel is non-conducting and the current is negligible compared to the magnitude of the current in the other regions. Usually, this current is assumed to be zero, but it is possible to use a more accurate model. One example of such a model for the sub-threshold current is presented in the appendix.

However, for the remainder of this report, the sub-threshold current is disregarded.

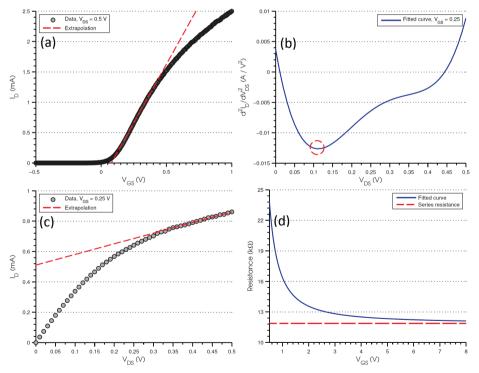

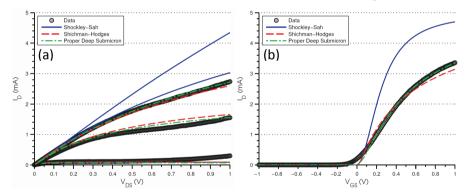

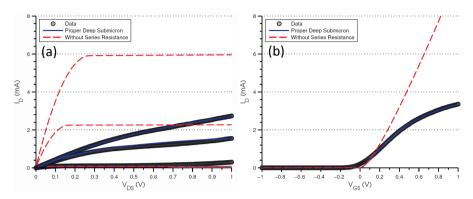

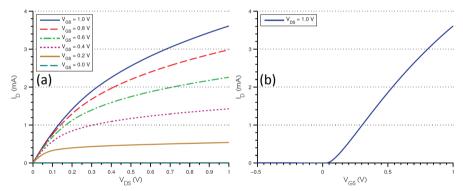

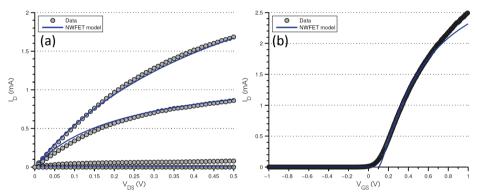

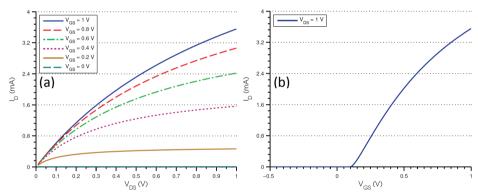

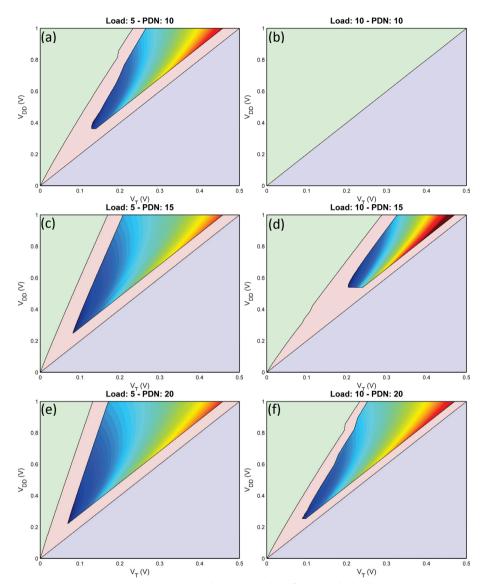

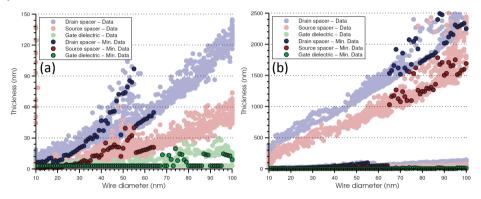

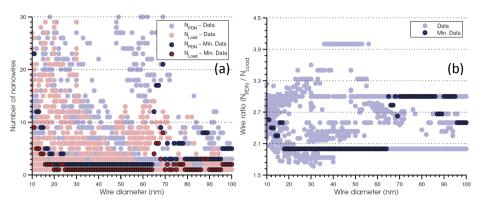

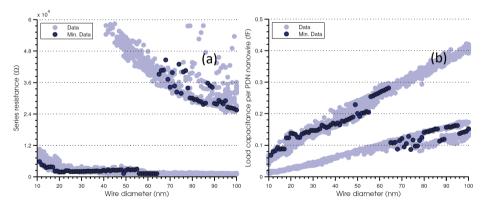

The second region shows a linear behaviour and applies to the case when  $V_{DS}$  is the main controller of the current. This linearity is due to the quadratic term being much smaller than the linear term for small voltages. Essentially, the transistor acts as a simple resistance in this region.