# Development of Wind Power Laboratory Setup

# Caspar Ralvenius

Division of Industrial Electrical Engineering and Automation Faculty of Engineering, Lund University

## **Abstract**

Wind turbines are often used on weak grids as a source of active power. There is a desire for a continuous supply of active power during variable wind speeds while also supplying reactive power to suppress grid-voltage fluctuations. These objectives are attainable using converters which are controlled with regulators.

In this project a test environment will be constructed wherein a wind turbine will be modeled and controlled using the aforementioned regulators. The wind turbine model is of a Full Rated Converter wind turbine.

The control algorithm for the regulators is developed in C and ran from a digital signal processor.

## **Table of Contents**

| 1.Introduction                                                           | 4  |

|--------------------------------------------------------------------------|----|

| 1.1 Objectives                                                           | 4  |

| 1.2 Thesis outline                                                       | 4  |

| 2 Wind energy                                                            | 5  |

| 2.1 Wind turbine                                                         | 6  |

| 2.2 Energy in wind                                                       | 7  |

| 2.3 Tip speed ratio                                                      | 8  |

| 2.4 Wind turbine power curve                                             | 9  |

| 2.5 Wind turbine architecture                                            | 10 |

| 2.5.1 Fixed-speed wind turbines                                          | 10 |

| 2.5.2 Variable-speed wind turbines                                       | 11 |

| 2.5.2.1 Variable-Speed Operation using Synchronous Generator             | 11 |

| 2.5.2.2 Variable-speed Operation using Squirrel Cage Induction Generator | 12 |

| 2.5.2.3 Variable-speed Operation using Wound Rotor Induction Generator   | 13 |

| 2.6 Desired influence on the power grid                                  | 14 |

| 3 Wind power generation                                                  | 15 |

| 3.1 Power electronics for wind turbines                                  | 15 |

| 3.1.1 Voltage source converters                                          | 15 |

| 3.1.2 Back to back VSCs                                                  | 16 |

| 3.1.3 Output filter                                                      | 16 |

| 3.2 Fully rated converter wind turbine                                   | 17 |

| 4 Voltage Source Converter Control                                       | 20 |

| 4.1 Carrier-based PWM                                                    | 20 |

| 4.2 Vector space representation                                          | 23 |

| 4.3 Clarke & Park Transformation                                         | 25 |

| 4.3.1 Clarke transformation                                              | 25 |

| 4.3.2 Parle transformation                                               | 26 |

| 4.4 Current and voltage regulators                                       | 27 |

| 4.4.1 Current regulator                                                  | 27 |

| 4.4.2 Voltage regulators                                                 | 31 |

| 4 4 3 Grid Characteristics                                               | 32 |

| 5 The laboratory setup                                       | 34 |

|--------------------------------------------------------------|----|

| 5.1 System description                                       | 34 |

| 5.2 Experimental Rack                                        | 35 |

| 5.2.1 The Digital Signal Processor (DSP) rack                | 37 |

| 5.2.2 The Voltage Source Converters                          | 40 |

| 5.2.3 The relay setup                                        | 41 |

| 5.2.4 LC Filters                                             | 42 |

| 6. The Software Description                                  | 43 |

| 6.1 ADC calibration                                          | 43 |

| 6.2 Clarke and Park transformation                           | 45 |

| 6.3 The PI regulators                                        | 47 |

| 6.3.1 Keeping DC-link voltage stable                         | 47 |

| 6.3.2 Keeping the grid voltage stable                        | 50 |

| 6.4 Protecting converters from over current and over voltage | 51 |

| 7. Experiment                                                | 52 |

| 8. Results                                                   | 53 |

| 8.1 Test without the grid voltage control                    | 53 |

| 8.2 Test with the grid voltage control                       | 54 |

| 9. Discussion                                                | 55 |

| References                                                   | 56 |

## **APPENDIX**

Source Code

Flashing the DSP

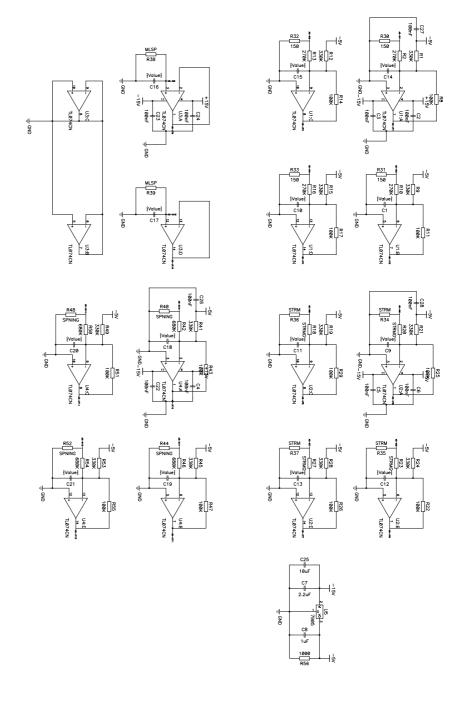

CAD Schemes of the Adjustment Card

#### 1. Introduction

The primary sources of electricity in the world are fossil fuels, corresponding to 70 % of the world electric energy production. The reason for their domination is the accessibility of fossil fuel and the high energy density when combusted. Since fossil fuels need several millions of years to form, they are considered a non-renewable energy source. This entails that at the current rate of exploitation; the sources will be depleted before they manage to form anew to meet the growing energy demands.

There is a general consensus that the combustion of fossil fuels is detrimental to the environment as the oxidization process is contributing to the greenhouse effect and the dispersing of harmful air pollutants. As citizens in industrialized countries are becoming increasingly environmentally conscious energy consumers, the demand for cleaner energy sources are growing.

In order for the alternative energy sources to be viable they have to meet certain criteria; cost competitiveness, reliability, environmentally safe and renewable energy production. Currently the dominating sources for renewable electric energy generation are hydro, solar and wind. Wind energy is one of the most exploitable of the before mentioned since it can be harnessed at an acceptable cost in both a large and a small scale. The environmental intrusion is generally lower than for hydropower plants as the main issues with wind turbines are the visual aspect while hydropower requires large damns and the cost is lower than the solar plants.

During 2009 wind power experienced a yearly growth of 38 GW or 31.7 % of capacity, bringing the total capacity to 158.5 GW. Globally the wind turbines generated 340 TWh of electricity equaling 2 % of the global electricity consumption. The trends show continuing investments in wind power and increasing installed capacity per annum [1].

#### 1.1 Objectives

The projects aims to construct a test environment where a wind turbine system can be modeled and controlled in order to feed active and reactive power out on the grid. The test environment will be used for further research concerning converter control and tests.

#### 1.2 Thesis outline

Chapter 1 provides the introduction to the thesis and the aim of the project. In chapter 2 theory for wind energy will be presented. The control strategy of the FRC is explained in chapter 3. Chapter 4 will describe the voltage source converter control strategy. Chapter 5 will describe the laboratory setup and the control structure of the power electronics. Chapter 6 will introduce the software used to control the converters. Chapter 7 will present the experiment. In chapter 8 the result will be presented and finally in chapter 9 conclusions will be drawn from the experiments.

The appendix will contain the program code, the process of flashing the DSP and CAD schemes of a adjustment card for the signals entering the DSP AD converter.

## 2 Wind energy

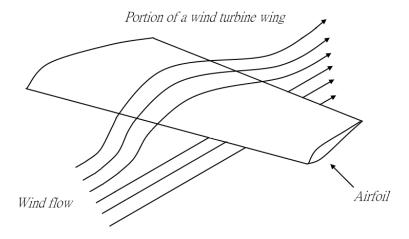

Wind flows due to atmospheric convection caused by the uneven heat patterns of the earth's surface causing different atmospheric pressures. The energy in the wind is harvested by wind turbines as the wind passes the airfoil structured blades. Airfoils are designed with a geometrical shape to generate mechanical forces as the surrounding fluid moves relative to the airfoil causing a lift and a drag force on the airfoil structure. These forces generate a net positive torque on a rotating shaft which drives an electrical generator to generate electrical energy.

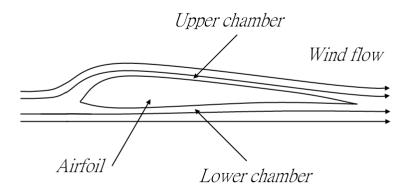

Figure 1 illustrates the principle of how the wind flow is disturbed passing the wind turbine wing blade in its path. The airfoil geometry is more closely analyzed in figure 2. Facing the wind flow direction is the leading edge of the airfoil. It cuts through the wind and forces a portion to travel below to the *lower chamber* and above to the *upper chamber*.

According to the law of continuity, the wind molecules separated by the leading edge will conjure at the same point leaving the airfoil. This phenomenon will create a pressure difference at the airfoil chambers, as the travel distance for the molecules passing the upper chamber is longer than for those passing the lower chamber. As the velocity of air increases, pressure decreases resulting in a lift force on the airfoil due to the higher pressure of the lower chamber [2].

Figure 1 The wind flow is disturbed by a wind turbine blade designed to create a lift and a drag force in order to drive the rotating shaft connected to the generator.

Figure 2 Typical airfoil principle where the wind flow is less obstructed at its lower part than it's upper to create pressure differences.

#### 2.1 Wind turbine

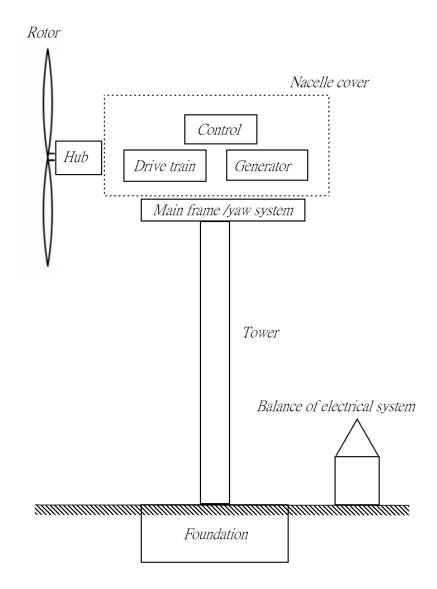

The currently prevalent wind turbine design is the horizontal axis wind turbine, which has its rotating axis in parallel to the horizon. Apart from the axis configuration, wind turbines can be classified depending upon if they have the rotor oriented in upwind or downwind, the design of the hub, rotor control operation and the alignment with the wind direction. The principal components of modern electricity generating wind turbine are (figure 3):

- Rotor; blades and supporting hub

- Drive train; generator, converters, gearbox, shafts, sensors and breaks for control.

- Wind turbine housing; nacelle cover

- Main frame/ yaw system to keep the wind turbine properly aligned with the wind direction

- Tower and tower foundation

- Balance of electrical system; cables, transformers, switchgear and converters and machine control.

Figure 3 The principle of a horizontal axis wind turbine.

## 2.2 Energy in wind

The kinetic energy in a fluid passing the rotor blades is defined by:

$$P_{fluid} = \frac{1}{2}mv^2$$

In this equation m is defined as the weight of the fluid passing the turbine's rotor per second and v the velocity of the fluid. The mass of the fluid can be calculated multiplying the density of the fluid with the volume, which is defined as the rotor blades sweep area multiplied with the distance the fluid travels in one second. This yields the following equation:

$$P_{air} = \frac{1}{2} \rho A v^3$$

Where  $\rho$  is defined as the density of the wind which is approximately 1.225 kg m<sup>-3</sup>, A is the area swept and v is the velocity.

The equation only serves to represent the kinetic energy in the wind passing the wind turbine; the actual energy conversion from wind to mechanical power is defined by the *Betz limit*. The Betz limit derives a power coefficient between the power in the wind and the power on the rotor:

$$C_p = \frac{P}{\frac{1}{2}\rho A v^3} = \frac{Power\ on\ the\ rotor}{Power\ in\ the\ wind}$$

The power coefficient,  $C_p$  is derived to 0.5926 which defines the ideal wind turbine performance conversion rate. In practice the conversion rate is lower due to inhomogeneous air flow, frictional drags on the blades, finite numbers of blades and the wind rotation caused by the blades, resulting in values from 0.25 to 0.45 [2] [3].

## 2.3 Tip speed ratio

The power coefficient is at its maximum at a certain velocity of the wind turbines blade tip relative the velocity of the surrounding wind. The tip speed ratio,  $\lambda$  defines the ratio between the parameters:

$$\lambda = \frac{\omega R}{v}$$

Where  $\omega$  is defined as the rotational speed of the rotor, R is the radius of the rotor and v is the speed of unobstructed wind flow.

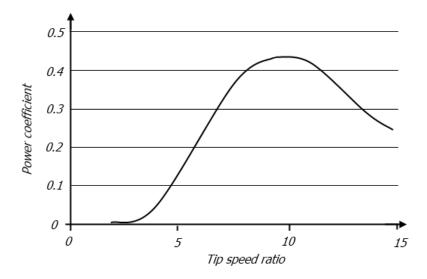

The power output is highly dependent on the wind tip speed ratio (Figure 4). Adjusting the wing tip velocity relative to the surrounding wind velocity will help to maintain a high power coefficient. Wind turbines designed to operate at a single wind speed will therefore inherently have a lower power conversion rate than those operating at variable rotational speeds as the wind velocity is in its nature non-constant [3].

Figure 4 The relation between tip speed ratio and power coefficient

## 2.4 Wind turbine power curve

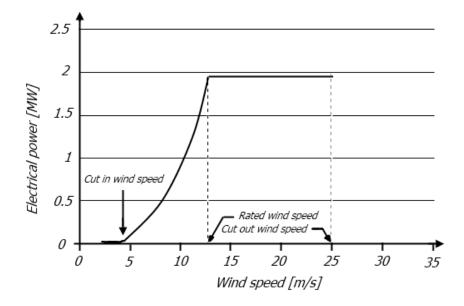

The wind turbine power output is dependent on various mechanical and electrical components performance. To be able to predict the power output during varying wind speeds, field test are undertaken to determine the wind turbines power curve [3].

Figure 5 Wind turbine power curve for a 2MW wind turbine

The key points determining the wind turbines power curve are the:

- Cut-in speed; the minimum wind velocity that the wind turbine can generate useful power

- Rated wind speed; the velocity of the wind where the wind turbine generator produces its rated output power.

- Cut-out speed; the maximum wind velocity at which the wind turbine will deliver power, which is limited by mechanical and electrical constraints.

#### 2.5 Wind turbine architecture

The wind turbine can be designed in various ways depending on its intended purpose. Currently, the most widely commercially produced wind turbine for electricity generation is designed with a three bladed rotor on a horizontal axis designed to face the wind direction. Wind turbines are thereafter constructed depending upon whether they will operate at varying-speeds or fixed-speeds.

#### 2.5.1 Fixed-speed wind turbines

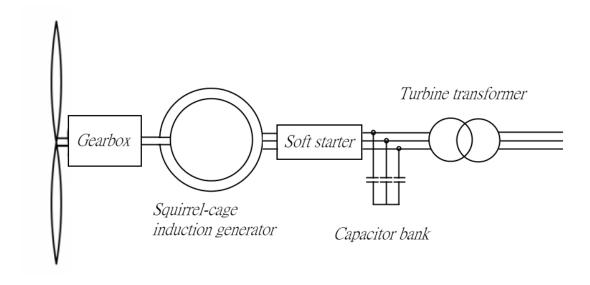

Fixed-speed wind turbines are designed to rotate at a constant speed, generating electricity at a constant frequency to match the grid frequency. Since the wind turbine velocity operating range is limited it simplifies the electronic components. The fixed-speed wind turbine can use the relatively low cost squirrel cage induction generator. To compensate for the reactive power the generator consumes, the wind turbine is fitted with a capacitor bank. A soft-starter is necessary to minimize the current transients when the generator is energized.

The mechanical part needed are a low-speed shaft connected to the wind turbine rotor and a gearbox connecting it to a high-speed shaft driving the generator. The gearbox increases the rotational speed of the rotor allowing for a lower number of poles in the machine which decreases the cost, physical dimensions and weight. The disadvantage is the added weight to the tower, the acoustic noise and the required maintenance of the gearbox [2].

Figure 6 The schematics of the fixed-speed wind turbine components

#### 2.5.2 Variable-speed wind turbines

Variable-speed wind turbines are desirable because they can generate electricity at its rated value below rated wind speed as long as the tip speed ratio is kept constant by regulating the rotor speed. This architecture will generate electricity at a high efficiency on a wide range of speeds.

Variable speed operation is possible using synchronous and induction generators. These are implemented in doubly fed induction generator (DFIG) wind turbines and fully rated converter wind turbines (FRC). The DFIG uses the Wound Rotor Induction Generator (WRIG) and FRC uses the Synchronous Generator (SG) or the Squirrel Cage Induction Generator (SQIG).

#### 2.5.2.1 Variable-Speed Operation using Synchronous Generator

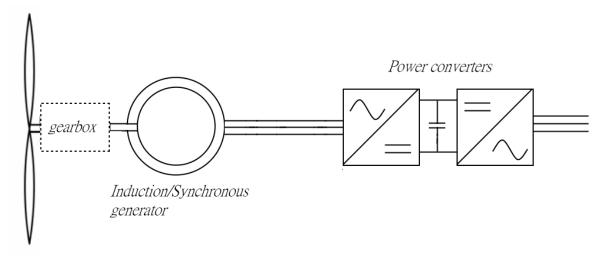

The synchronous generator can either have permanent magnets or separately excited windings creating the magnetic flux. In both cases, the frequency is dependent on the rotational speed and the number of poles and will diverge during variable speeds from the relatively static grid frequency. Variable-speed operation thus requires the output to first rectified to DC and then back to AC at grid frequency.

The wind turbine consists of the wind turbine rotor, SG, AC/DC rectifier, DC link, DC/AC inverter connected to the grid. Depending on the design, there is an option to include a gearbox connecting the wind turbine and the SG. A generator with a multiple pole design can generate power at a sufficiently high frequency without the necessity for a gearbox. The multiple pole solution has the drawback that the generator has larger dimensions and that the mechanical torque on the shaft will need to be larger to generate power at low speeds [2].

Figure 7 The schematics for both the induction and synchronous generator wind turbine architecture

#### 2.5.2.2 Variable-speed Operation using Squirrel Cage Induction Generator

SQIG driven wind turbines require electrical converters that can supply reactive power and control its rotational speed. The cost of the electrical converters and losses in the system will increase compared to the synchronous generator fitted wind turbines. The gains of the rugged and compact induction generator compared to SG fitted wind turbines are therefore relatively small.

The SQIG driven wind turbine typically consists of the wind turbine rotor, SQIG, voltage source converters (VSCs) with a DC link between them connected to the grid (figure 7). The generator side VSC supplies the SQIG with reactive power and receives active power from it. The grid side converter inverts the DC to AC at grid frequency at an appropriate voltage level.

#### 2.5.2.3 Variable-speed Operation using Wound Rotor Induction Generator

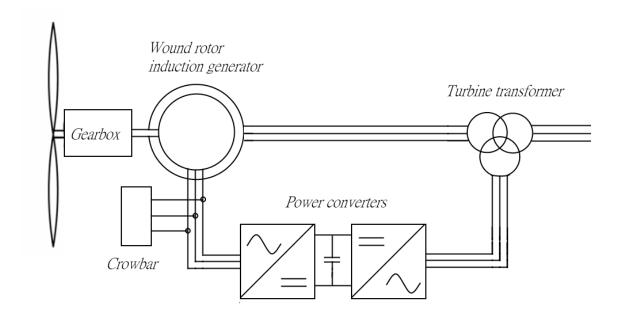

The WRIG operates similarly as the SQIG with the exception that it has copper wire windings for a rotor, rather than metal bars as the SQIG has. The implication is that the rotor can have both power injected and extracted from it using brushes and slip rings connected to the rotor.

Although the WRIG is more expensive than the SQIG, the accessibility of the rotor enables the power converters to only handle approximately one third of the power compared to SQIG driven variable-speed wind turbines. This will lower the overall cost and size of the wind turbine configuration.

As the rotor windings are accessible, the rotor the rotor slip and consequently the rotor current can be increased and decreased, allowing the generator to operate at wider velocity ranges. Increasing the rotor resistance will increase the losses and decrease the overall efficiency unless the power can be recovered, as in the DFIG.

If the wind turbine experiences higher wind speeds (super-synchronous), the excess power will flow out from the rotor and via power electronics be fed to the grid at proper frequency and voltage. If the wind speeds decrease (sub-synchronous) the power converters will absorb power from the grid and feed it to the rotor allowing it to still generate power fed to the net.

The WRIG driven wind turbine consist of the wind turbine rotor, WRIG, two VSCs with a DC link connected to the grid via a transformer. Depending on the wind turbine speeds, the grid and the generator side converters will either operate as rectifiers or as inverters. The arrangement allows the DFIG to operate at approximately 50 % below and 50 % above the synchronous speed [2] depending on the converter dimensions.

Figure 8 The schematics for the DFIG wind turbine architecture

## 2.6 Desired influence on the power grid

The wind turbine will supply the network with active power from wind energy as it's converted kinetic energy is converted via the wind turbine rotor to electrical energy using the electrical generator.

The grid code regulations vary from country to country and even from region to region specifying the frequency and voltage level for continuous operation. The code also stipulates operation during reduced grid voltage before the wind turbine is tripped off from the grid, to help sustain the grid voltage (fault ride through).

## 3 Wind power generation

This chapter describes the fully rated converter (FRC) wind turbine architecture, the principle as well as the control strategy. The power electronics involved in controlling the active power flowing out from the electrical generator as well as reactive power control on the grid side will also be explained.

#### 3.1 Power electronics for wind turbines

Power converters are versatile electrical instruments that enables the electrical power to change voltage and frequency, as well as form; AC to DC and DC to AC. Due to their wide possible applications, the power converter cost is constantly decreasing making it economically viable to install in applications such as wind turbines.

Modern power converters consist of transistors acting as valves, either fully open or fully closed, i.e. either working as closed circuits or as an open circuit. The output; voltage time area is commonly controlled using carrier wave modulation, where a signal generators triangle wave output is compared to a reference wave switching the transistors according to the comparison results.

Transistors are favorable due to the low voltage drops and the high switching frequency, containing the losses to approximately 4 % of the transferred power. Currently the most commercially common transistor used in power converters is the insulated gate bipolar transistor (IGBT), its characteristics are high efficiency and fast switching making them attractive for power electronic switches.

In variable-speed wind turbines, power converters are used to decouple the electrical generator from the grid as the frequency and the voltage at the generator terminals will not be constant due to wind speed variations.

#### 3.1.1 Voltage source converters

Voltage source converters (VSCs) are widely used in power systems. The principle of a VSC can be described with a single four-quadrant DC converter (consisting of two transistor half-bridges). In the two quadrant DC converter, the current can flow in both directions, out from the DC source, and into the DC source. The output average voltage from the four-quadrant DC converter can be both negative and positive with reference to the mid-point in the DC link [5].

Three transistor half bridges can form a three-phase converter if they are connected in parallel, with each half-bridge controlled independently. The transistors in a half-bridge are supposed to switch alternatively with one transistor conducting at a time however transistors are unable to transverse from closed to open circuits instantaneously.

There is therefore an inherent risk when switching for a short circuit in this form, there is a time delay imposed; blanking time, so that one half bridge leg in the VSC can't conduct with both switches simultaneously. There are different solutions to this problem, the principle is usually to delay the transistor on state (conducting) while its off state (open circuit) isn't. The ramification is that the average output voltage will be lower, demanding the need for an integral part in converter controllers. The principle used in this report utilizes the possibility to adjust both the on and off state in the software to avert short circuits.

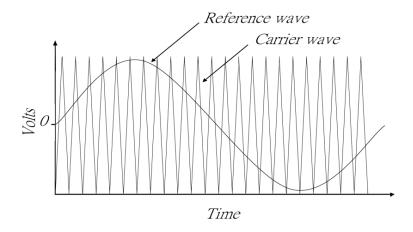

The strategy used in this report to control the VSC is the carrier based pulse width modulation (CB-PWM). The principle behind the control method is that a reference sine wave of a desired frequency

is compared with a fixed high-frequency triangle wave to obtain voltage pulses of desired width. This will be described in chapter 4.

#### 3.1.2 Back to back VSCs

Variable wind turbines are fitted with back to back VSC consisting of two voltage source converters with a common DC link between them. The voltage source converters are independently controlled by PWM signals. The configuration enables a bi directional flow of power, from the generator to the power grid.

The generator side converter (GSC) will be able to control the output current from synchronous generators controlling the electrical torque. This will result in generator speed control to generate the maximum power per generator speed according to the optimal power curve specified by the manufacturer.

The network side converter (NSC) output can be controlled to alter the power angle, providing reactive power to and from the power grid. The NSC will be regulated to maintain a constant voltage over the DC link, transferring active current to the power grid in order to maintain a constant DC-link voltage.

The control strategy of the VSCs will be described in chapter 4.

#### 3.1.3 Output filter

As the voltage output from the converters is generated using PWM, the output current needs to be filtered to remove the harmonic components. This is done applying an LC filter, with the inductive part in series with each phase and star connected shunt capacitors. The LC filter is designed to have a cut off frequency ten times the grid frequency.

## 3.2 Fully rated converter wind turbine

The typical configuration of a fully rated converter (FRC) wind turbine consists of the wind turbine rotor, connected to the generator via a gearbox or directly to the generator shaft. The generator can be asynchronous or synchronous with either wound field windings or permanent magnets (PMs) on the rotor to create the magnetic flux. If the generator is mounted on the same shaft as the wind turbine rotor the generator will need a large number of poles to generate power with a proper frequency.

If the wind turbine rotor shaft is connected to the generator shaft via a gearbox, the generator will have smaller dimensions as it will need a smaller number of poles. This will also lower the mechanical load on the wind turbine, as the wind turbine will have a high rotational speed, rather than the need to produce a large torque to generate the same amount of power [3].

The synchronous generator is generally not fitted with permanent magnets as the wound rotor enables the control of the excitation current. This enables control of the output voltage independent of the load current. The advantages with permanent magnet excitation are the lower excitation losses and that the more compact size of the generator. Additionally the generator is more robust and requires less maintenance.

As the FRC will generate electricity during variable wind speeds, the output frequency and voltage levels will not coincide with the gird frequency and voltage. The power converters will transform the generated power to fit the grid before it's transmitted to the power network. This is done with two back to back voltage source converters with a DC link between them. The FRC will have the entire generated electrical power transferred through the VSCs.

#### Fully rated converter control strategy

The control of the generator is provided through the generator side converter (GSC). The GSC decouples the mechanical speed of the generator and the power system electrical frequency, allowing variable-speed energy generation. The GSC will control the electrical generator using a reference curve for maximum power extraction per generator speed via torque control.

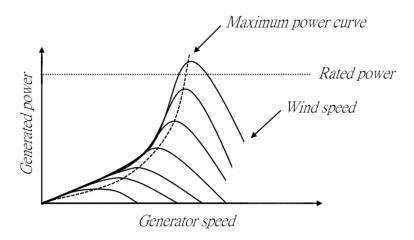

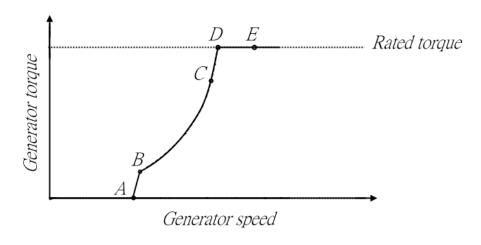

The control strategy strives to extract as much power as possible from the wind. The manufacturer of the wind turbine will design it for optimal power extraction according a curve showing generator speed to generated power. The generated power is dependent on the wind speeds per generator speed prompting the following curve (Figure 9)

Figure 9 Wind turbine characteristics plot showing generated power per wind speeds and generator speeds.

The maximum power curve is expressed in optimal torque-speed curve as the controller will be regulating the generator torque. Generally the operating point should be between point B and point C during normal operation. At low speeds, the curve is limited by the cut-in speeds, between point A and B. At high wind speeds the rotational speed is limited to reduce aerodynamic noise, increasing the torque at constant speed (C-D). If the wind speeds increase any further, the strategy is to keep the torque constant between point D and E. Generator speeds exceeding point E causes pitch regulation in the control system of the wind turbine wings to lower the aerodynamic input power [3].

Figure 10 Wind turbine characteristics plot showing optimal torque per generator speeds.

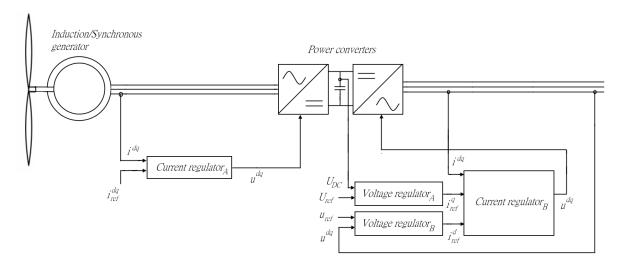

The network side converters (NSC) will control the DC-link voltage aiming to maintain a constant DC-link voltage and to keep the grid voltage stable. The generator torque is controlled manually via a current reference since the aim of the project was to construct the wind turbine model controlled via the DSP. Therefore the added implementation of sensors and measurements needed from the generator were not stressed in this project. The ramification is that the generator will not be operating at optimal torque. The control schematics are illustrated in figure 11.

Figure 11 The control strategy schematics for the FRC in this project. The optimal torque reference curve will not be used in favor of the manually controlled current reference.

## **4 Voltage Source Converter Control**

The voltage source converters (VSCs) control strategy in this report will be the Carrier-based pulse width modulation (CB-PWM). The principle behind the control method is that a reference sine wave of a desired frequency is compared with a fixed high-frequency triangle wave to obtain voltage pulses of desired width. The reference value for the VSCs is calculated using controllers implemented in the stationary dq co-ordinate system.

#### 4.1 Carrier-based PWM

Carrier-based PWM control compares a high frequency triangular wave  $V_{tri}$  with a sinusoidal reference signal  $V_{ref}$  in order to control the VSC. Whenever  $V_{tri}$  is larger than the reference wave, the upper transistor in one leg will be turned off and whenever the triangle wave magnitude is lower than the reference wave the same transistor will be turned on. The lower transistor in the same leg will be on and off inversely of the upper transistor. The equivalent setup is done for the two other legs working on their own phases [2].

The principle of obtaining transistor switch instances at the appropriate time is shown in figure 12.

Figure 12 Carrier-based PWM reference wave and triangular wave.

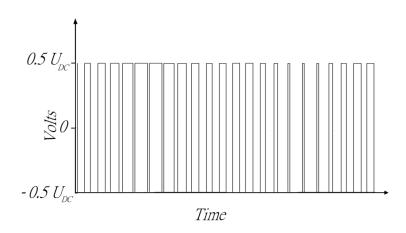

The pulse train resulting from the switch signals corresponding to those in figure 12 is shown in figure 13. The pulses are widest whenever the sinus wave peaks causing the average voltage to increase, following the sinusoidal behavior [2].

Figure 13 Carrier-based PWM pulse train resulting from a sinusoidal reference wave.

Modulation ratio is defined as:

$$m_a = \frac{\hat{V}_{ref}}{\hat{V}_{tri}}$$

The ratio is defined using the peak values. The difference between the phase potentials, i.e. the potential out from each half bridge creates the output voltage from the converter. Since the maximum output voltage that can be obtained is  $V_{DC}$  the carrier boundary value is:  $\hat{V}_{tri} = 0.5 V_{DC}$ .

Over-modulation will occur if the modulation ratio exceeds unity. The frequency modulation ratio is defined by the ratio between the frequency of the triangle wave and the reference wave. This value should be kept as high as possible to ensure proper voltage pulse width.

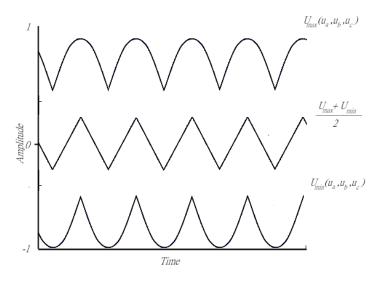

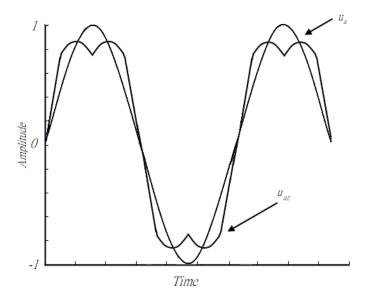

The reference waveform usually has zero-sequence component added to improve the utilization of the converter by increasing the modulation index and lowering the voltage ripple. The zero-sequence added to each phase reference will not show up in the output, as the VSC is not connected to the neutral. This process is referred to a symmetrical reference wave and provides a 15 % higher margin to over modulation than sinusoidal reference waves [5] [6].

The zero-sequence component is calculated making the most negative and the most positive reference equal but with opposite signs and it is subsequently subtracted from the reference values (figure 14 and 15).

$$u_z = \frac{\max(u_a^*, u_b^*, u_c^*) + \min(u_a^*, u_b^*, u_c^*)}{2}$$

Figure 14 The results of the maximum and minimum of the instantaneous values of the three phases as well as the sum of them.

Figure 15 The sinusoidal and symmetrical reference wave used for modulation.

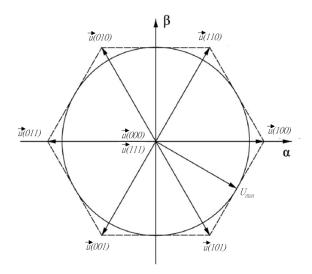

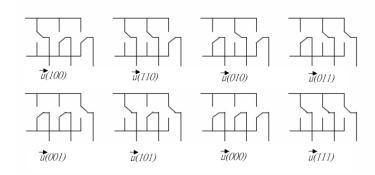

#### 4.2 Vector space representation

In this project, the two-level voltage converter uses space vector PWM switching strategy, where the switch states in the converter can be defined by the switching vector. For a three phase, two-level converter there are eight possible switch state combinations with six active and two zero vectors. The vector length of each active vector is

$$\vec{U} = \sqrt{\frac{2}{3}} \cdot U_{dc}$$

However the converter can only provide controllable voltage within the hexagon shaped frame the active vectors create. The maximum voltage vector is thus only

$$\vec{U}_{max} = \sqrt{\frac{1}{2}} \cdot U_{dc}$$

The voltage vectors for a three phase two level VSC along with the hexagonal shape illustrating the modulation ratio of 1 are illustrated in figure 16. The switch states are shown in figure 17 [6]. It can be noted that the switch states are set that only one switch will alter its state to represent the voltage vector next to it. This will lower the amounts of switching and thus increase the life of the transistors.

Figure 16 Voltage vectors for the two level three phase converter.

Figure 17 Switch states corresponding to the voltage vectors inn figure 14[7]

#### 4.3 Clarke & Park Transformation

Clarke and Park transformations are used to control electrical drives structures involving AC-motors using complex space vectors. The transformation entails the reference frame to change from a time variant three-phase axes coordinate system to a two coordinate rotating reference frame. This facilitates the control and scrutinisation of three phase voltages, currents and fluxes.

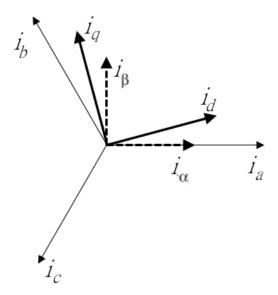

Figure 18 The relationship between the alfabeta, dq and the abc frame.

Figure 16 illustrates the relationship between the three-phase time invariant stationary reference frame, the two co-ordinate reference frame and finally the rotating reference frame dq.

#### 4.3.1 Clarke transformation

The Clarke transformation modifies the three-phase system to a two-phase orthogonal system as follows:

$$\begin{cases} i_{\alpha} = i_{a} \\ i_{\beta} = \sqrt{\frac{3}{2}} \cdot i_{b} - \frac{1}{\sqrt{2}} \cdot i_{c} \end{cases}$$

Where  $i_{\alpha}$  and  $i_{\beta}$  are components of the orthogonal reference frame.

#### 4.3.2 Park transformation

The Park transformation changes the two-phase orthogonal reference frame to a time invariant, rotating two-phase orthogonal reference frame aligned with the rotor flux. The q-axis angular displacement from  $\alpha$  axis is represented by the angle  $\theta$ .

$$\begin{cases} i_d = i_\alpha \cdot \cos(\theta) + i_\beta \cdot \sin(\theta) \\ i_q = -i_\alpha \cdot \sin(\theta) + i_\beta \cdot \cos(\theta) \end{cases}$$

Where  $i_d$  and  $i_q$  represent the currents on the *direct axis* and *quadrature axis* respectively.

The transformation back from the dq and  $\alpha\beta$  frame is done with inverse Clark and Park transformations [7].

$$\begin{cases} i_{\alpha} = i_{d} \cdot \cos(\theta) - i_{q} \cdot \sin(\theta) \\ i_{\beta} = i_{d} \cdot \sin(\theta) + i_{q} \cdot \cos(\theta) \end{cases}$$

$$\begin{cases} i_a = \sqrt{\frac{2}{3}} \cdot i_\alpha \\ i_b = -\sqrt{\frac{1}{6}} \cdot i_\alpha + \sqrt{\frac{1}{2}} \cdot i_\beta \\ i_c = -\sqrt{\frac{1}{6}} \cdot i_\alpha - \sqrt{\frac{1}{2}} \cdot i_\beta \end{cases}$$

## 4.4 Current and voltage regulators

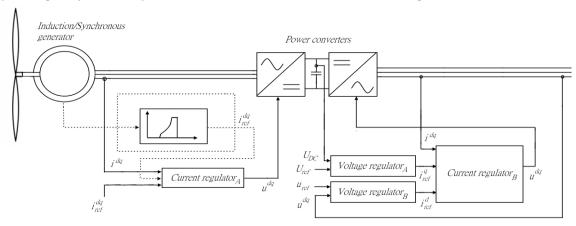

The current and voltage regulator compare values in the dq frame in order to control voltages and currents transmitted to and from Voltage Source Converters using PWM. The control strategy for the project is as illustrated in figure 19.

Current regulator A will control the generator torque with a manually set reference value. Current regulator B will control the active power flow into the grid and reactive power flow into or from the grid in order to keep a stable value over the DC-link and to contribute with reactive power to the grid in order to obtain nominal voltage levels on the grid at disturbances respectively.

Voltage regulator A compares a reference value for the DC-link voltage with the measured DC-link voltage and produces a current reference on the q axis to regulate active power. Voltage regulator B compares the nominal grid voltage value with the measured and produces a current reference on the d axis to regulate reactive power.

Figure 19 The control strategy for the FRC in this project

## 4.4.1 Current regulator

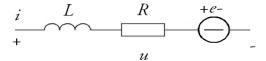

Current regulators are used to control and inject current in the grid and to control electrical drives regulating the motor torque. The regulator is derived from an ideal single-phase load model with a resistance (R), an inductance (L) and an induced emf (e) in series.

Figure 20 Generic one phase load

The equation representing the voltage across the model is given by

$$u = R \cdot i + L \cdot \frac{di}{dt} + e$$

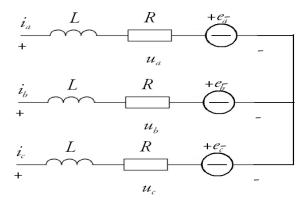

For a three-phase load model, voltages and currents are represented by symmetric vectors and symmetric resistive and reactive loads, each phase shifted by 120 degrees.

Figure 21 Generic three phase load

The voltage across each phase is given by:

$$\begin{cases} \sqrt{\frac{2}{3}} \left( u_a = R \cdot i_a + L \cdot \frac{di_a}{dt} + e_a \right) \\ \sqrt{\frac{2}{3}} \cdot e^{j\frac{2\pi}{3}} \cdot \left( u_a = R \cdot i_a + L \cdot \frac{di_a}{dt} + e_a \right) \\ \sqrt{\frac{2}{3}} \cdot e^{j\frac{4\pi}{3}} \cdot \left( u_a = R \cdot i_a + L \cdot \frac{di_a}{dt} + e_a \right) \end{cases}$$

The equation is transformed using Clarke transformation to the  $\alpha\theta$ -reference system and subsequently to the rotating dq-reference system

$$\begin{split} \vec{u}^{\alpha\beta} &= R \cdot \vec{\imath}^{\alpha\beta} + L \cdot \frac{d}{dt} \vec{\imath}^{\alpha\beta} + \vec{e}^{\alpha\beta} \\ \vec{u}^{dq} &= R \cdot \vec{\imath}^{dq} + L \cdot \frac{d}{dt} \vec{\imath}^{dq} + j\omega L \vec{\imath}^{dq} + \vec{e}^{dq} \end{split}$$

where  $\omega$  is the grid angular frequency.

By dividing the equation into its real and imaginary components will result in

$$\begin{cases} u_d = R \cdot i_d + L \cdot \frac{di_d}{dt} - \omega L i_d + e_d \\ u_q = R \cdot i_q + L \cdot \frac{di_q}{dt} + \omega L i_q + e_q \end{cases}$$

This equation is expressed in discrete-time to construct the expression for a dead-beat PI (Proportional-Integral) controller which output will be voltage references in the dq reference frame [5].

$$\begin{cases} u_{d,ref,k} = K \cdot \left( \left( i_{d,ref,k} - i_{d,k} \right) + \frac{1}{T_i} \sum_{n=0}^{k-1} \left( i_{d,ref,n} - i_{d,n} \right) \right) - K_c \cdot \frac{i_{q,ref,k} + i_{q,k}}{2} + e_{d,k} \\ u_{q,ref,k} = K \cdot \left( \left( i_{q,ref,k} - i_{q,k} \right) + \frac{1}{T_i} \sum_{n=0}^{k-1} \left( i_{q,ref,n} - i_{q,n} \right) \right) + K_c \cdot \frac{i_{d,ref,k} + i_{d,k}}{2} + e_{q,k} \end{cases}$$

Where *k* is a sample instance and

$$\begin{cases} K = \left(\frac{L}{T_s} + \frac{R}{2}\right) \\ T_i = \frac{R}{\left(\frac{L}{T_s} + \frac{R}{2}\right)} \\ K_c = \frac{\omega L}{2} \end{cases}$$

If the deviation from the reference value remains for a longer time, the integral part of the equation will grow to a large value ad saturate the output signal from the regulator. The solution is to limit the maximum integral part by giving it the value of the output signal subtracted with the proportional part. This preventative measure is referred to anti-windup.

The anti-windup function will have the following expression:

if

$$u(k) > u_{max}$$

then

$$u(k) = u_{max}$$

$$u_{int}(k) = u_{max} - K \cdot (y_{ref}(k) - y(k))$$

else if

$$u(k) < u_{min}$$

$$u(k) = u_{min}$$

$$u_{int}(k) = u_{min} - K \cdot (y_{ref}(k) - y(k))$$

end if

## 4.4.2 Voltage regulators

The Voltage regulators in this project are built using the following equations

$$e(t) = y_{ref}(t) - y(t)$$

where e(t) is the reference error,  $y_{ref}(t)$  is the reference value and y(t) is the measured value.

Adding an integral part to the reference error will reduce the steady-state error to zero

$$u(t) = K_p \cdot \left( e(t) + \frac{1}{\tau_i} \int e(t) dt \right)$$

where u(t) is the output voltage,  $K_p$  is the proportional constant and  $\tau_i$  is the time constant.

The integral part will be fitted with an anti-windup to avoid output signal saturation as with the current regulators.

The equation will be expressed in discrete-time to derive the PI controller to output voltage references in the dq frame.

$$u(k) = K_p \cdot \left( y_{ref}(k) - y(k) + \frac{T_s}{T_i} \sum_{n=0}^{n=k} \left( y_{ref}(n) - y(n) \right) \right)$$

The parameters in the voltage regulator are adjusted starting with standard voltage regulator parameter values [6].

$$K_p = 10$$

$$K_i = \frac{T_s}{T_i} = 0.5$$

#### 4.4.3 Grid Characteristics

The grid characteristics of a system operating in sinusoidal steady state are described as follows:

The apparent power flowing through the lines is a sum of the active power and the reactive power, where the reactive power is defined as the imaginary part of the complex valued apparent power.

$$S = P + jQ$$

The transfer of the apparent power from a bus to the load bus is dependent on the grid impedance as it will be the source of phase shift between the grid and the load voltage.

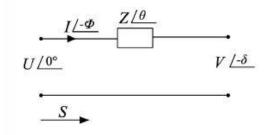

Figure 22 Principal illustration of voltage drop due to transmission line inductance.

The expression for the active and reactive power is derived from:

$$S = P + jQ = U \cdot I^* = U \left(\frac{U - V}{Z}\right)^* = U \left(\frac{U - Ve^{j\delta}}{Ze^{-j\theta}}\right) = \frac{U^2}{Z}e^{j\theta} - \frac{U \cdot V}{Z}e^{j(\delta + \theta)}$$

Where

$$P = \frac{U^2}{Z}\cos(\theta) - \frac{U \cdot V}{Z}\cos(\delta + \theta)$$

$$Q = \frac{U}{Z}\sin(\theta) - \frac{U \cdot V}{Z}\sin(\delta + \theta)$$

Expressing the impedance as a complex value where the imaginary part is defined as the line reactance and the real part as the line resistance:

$$Ze^{j\theta} = R + jX$$

Yields the expressions:

$$Vsin(\delta) = \frac{XP - RQ}{II}$$

$$U - V cos(\delta) = \frac{RP + XQ}{U}$$

Generally the resistance, R is neglected to simplify the equations as the magnitude of the impedance greatly exceeds that of the resistance. And as the power angle  $\delta$  is small the sine and cosine values can be simplified as  $\cos(\delta) \approx 1 \sin(\delta) \approx \delta$ , yielding the expressions to:

$$\delta \cong \frac{XP}{UV}$$

$$U - V \cong \frac{XQ}{U}$$

From the expressions it can be concluded that the reactive power transfer results in a voltage difference between the grid and the load. The active power transfer is dependent on the power angle [7].

## 5 The laboratory setup

In this chapter the hardware topology of the wind turbine converter is described. The choice of setup is described and discussed. Each part of the hardware and measurement system will be presented with its beneficial attributes and its limitations.

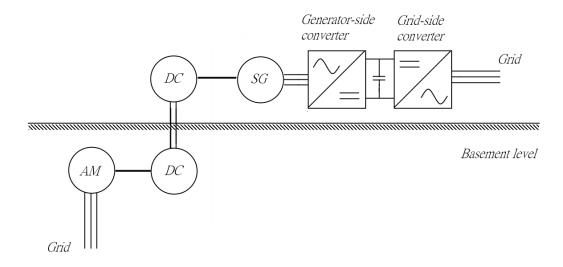

## 5.1 System description

The system uses asynchronous and DC generators placed below the laboratory level in order to save space. Below the laboratory setup is an asynchronous motor (AM) connected to the power grid. On the axis from the AM is the rotor of a DC generator. Magnetization current is fed to the DC generator and the generated power is fed to the system above ground.

Above ground, the current from the DC generator is fed to a DC motor. A field winding magnetization current is applied to the DC motor and it starts to gain speed. The nominal speed is 1500 rpm.

The following step is to magnetize a synchronous generator (SG) located on the same axis as the DC motor. This is done when a current is fed to the field winding of the SG. The output from the synchronous generator is three-phase power, which is to be fed to a voltage source converter (VSC) on the generator site. The synchronous generator rated power is 2200 VA.

Figure 23 The laboratory setup

The VSC on the generator side will feed a charging current to the DC link between both VSC: s. The VSC on the grid side will be controlling the DC link level by feeding out active power on to the net in order to maintain a stable DC-link voltage. The VSC only allows for active power to be transferred out from converter, however reactive power can travel in and out from the VSC.

The VSC on the grid side is subsequently connected to the grid at 230 V.

The reasoning behind the DC-link voltage level is to ensure that the converters could deliver enough voltage without any risk for over modulation when output per phase is set to be 127 V.

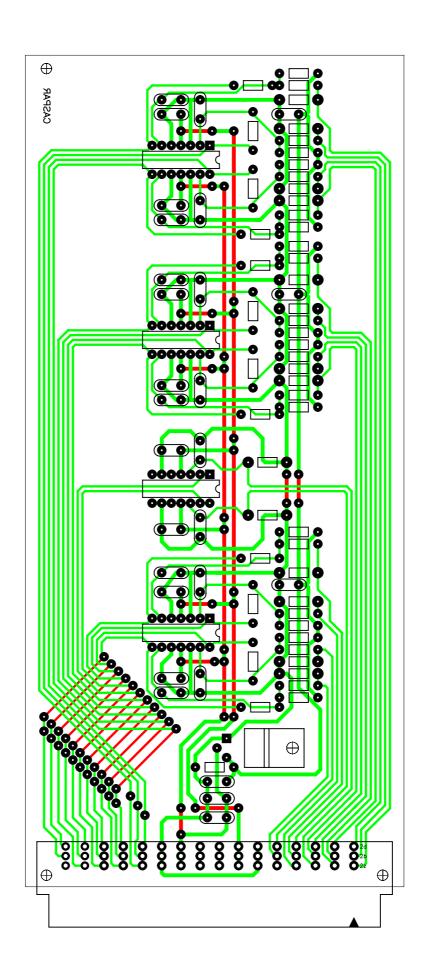

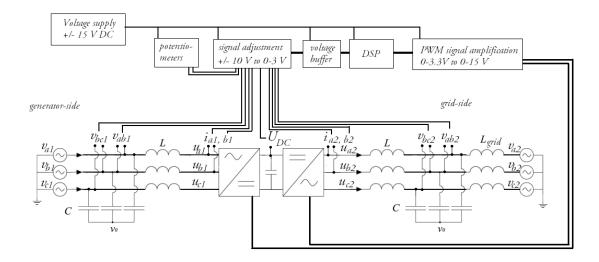

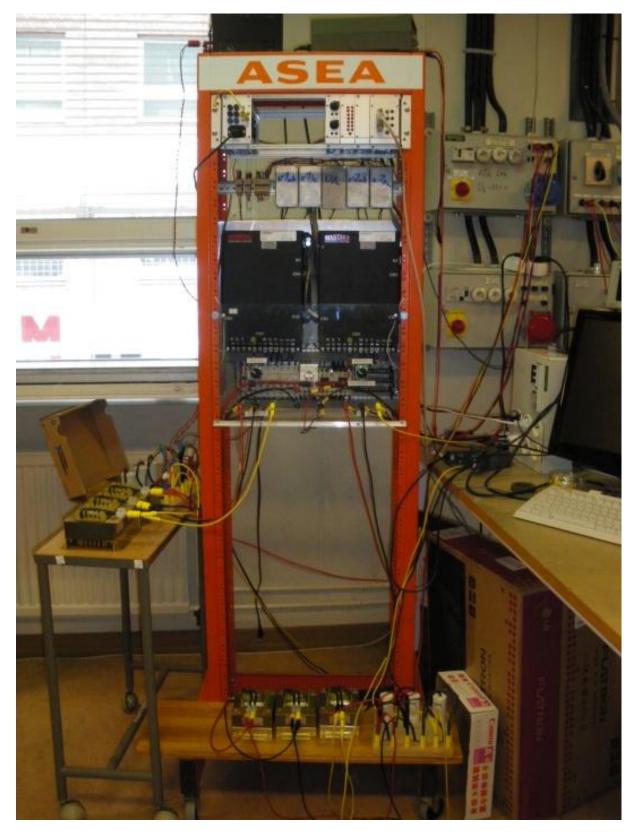

#### 5.2 Experimental Rack

The Rack in which the VSC: s, measurement instruments and digital signal processor (DSP) are situated will be explained in this chapter. The general principle will be introduced followed by a description of each part in greater detail.

At the top level of the experimental rack is the DSP, along with its power supply and signal adjustment card for the AD converter unit and the signal adjustment cards for PWM VSC control.

Directly below are the LEM modules mounted on a relay rail connected to the DSP via the signal adjustment card for the AD converter. They measure phase-to-phase voltages on both sides of the VSC: s  $v_{ab1,2}$ ,  $v_{bc1,2}$  and the DC-link voltage  $U_{dc}$ .

In the middle of the experimental rack, there are two VSC: s mounted on an aluminum plate with their heat sinks facing the plate. The built in LEM modules in the VSC: s measures the phase currents  $i_{a1,2}$ ,  $i_{b1,2}$ .

In order for the converters to avoid the large current inrush when the discharged capacitors are connected to the grid, the phase current is forced to pass through power resistors. When sufficient time has passed, i.e. the capacitors are charged up the power resistors will be bypassed. The control of the power resistors is done using timed relays.

The current from the VSC passes through LC filters to remove the harmonics from the current signal making it more sinusoidal.

Figure 24 The measured signals and the hardware required to process it.

Figure 25 Picture of the hardware and setup for the project

#### 5.2.1 The Digital Signal Processor (DSP) rack

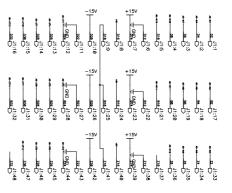

The DSP rack space is situated at the top of the VSC rack and contains the DSP with a voltage buffer, voltage supply unit, potentiometer unit, signal adjustment card for the onboard ADC and PWM signal card. Figure 26 is an illustration of which units are confided into the top rack and their order.

Voltage supply +/- 15 V DC potentio-meters signal adjustment +/- 10 V to 0-3 V PWM signal amplification buffer DSP buffer

Figure 26 The digital signal processor rack layout from left to right

The individual units are connected to each other via signal wires in the back of the top rack. The voltage supply unit feed the units to the right of it with power. The potentiometers feed an adjustable signal to the signal adjustment card which signals are fed to the DSP via the voltage buffer card. Signals from the transducers are also fed to the signal adjustment card. The signals from the DSP need to be amplified to control the PWM, which is conducted in the PWM signal amplification card.

#### The Digital Signal Processor

A digital signal processor is a central processing unit specially designed to handle tasks such as mathematical operations, digital filtering and Fourier analysis of signals in real time. The device is therefore usually several times faster than the ordinary CPU as it doesn't have general-purpose software running.

The DSP displays a predictable execution time for the processes it will perform, differentiating it from the microprocessors in modern PCs where processes can be executed at different time instances depending on programs running in the background.

The processor will be used as an embedded controller dedicated to a set number of tasks to be implemented in a sequence to control the output from the two side-by-side mounted VSC: s. The current and voltage regulators running on the DSP will generate an output, which is fed to the PWM controller, which subsequently controls the VSC: Regulators and functions are written in C and assembly.

The DSP model used in the laboratory setup is TMS320F2812. The main features are the 150 MHz processor clock, 32-Bit CPU. It contains an on-chip memory consisting of a flash device in 16 sectors, each 128K from which the program will be running. Additional storage is provided from the RAM and external memory on the DSP.

The analog-digital converter is a 12-bit 16-channel device allowing both sequential and simultaneous conversions with the conversion rate of 80ns. The DSP is fitted with a voltage buffer to decrease the charging time of the capacitors in the ADC, increasing the accuracy of the conversion.

#### The Voltage Supply

The voltage supply supplies the DSP and the four other cards in the DSP rack space with +15 V, +5 V and -15 V DC as well as a reference ground.

#### The Potentiometer Card

The potentiometer card is used to test regulators response to variable input voltages. It consists of two potentiometers, which can be continuously adjusted in 10 revolutions with each revolution indicated by 100 equally spaced points on the wiper. The output from the potentiometers is a voltage ranging from -10 to +10 V.

### The ADC signal adjustment card

The ADC signal adjustment card is designed for the various signals from the current and voltage transducers and the potentiometers. The signals are adjusted to range from 0-3 V from the transducer and potentiometer output voltage in the range of  $\pm 10$  V.

The reference ground is separated from the ground on the PWM card, as the digital signals will cause ground currents to flow destabilizing the reference point.

The design of the ADC signal adjustment card is done using MATLAB to find the lowest number of resistors to adjust the voltage and P-CAD 2000 to design the actual card.

#### The PWM card

The PWM card receives signals from the DSP I/O ports at 3.3 V, which are amplified in the PWM card to 0-15 V in order to control the drivers for the IGBT transistors at the VSC: s. This card has a separate path to ground, as the digital signals might interfere with the analogue ground. It is supplied with  $\pm$ 15 V from the power supply unit in the DSP rack.

#### The Voltage Buffer Card

The voltage buffer card will aid the charging of the capacitors in the AD converter to charge faster increasing the accuracy of the conversion.

#### The LEM Modules

LEM modules are transducers designed to measure voltage or current using the Hall effect. The principle of Hall effect is, that a conductive material with a current flowing through it enters a magnetic field, a magnetic force proportional to the current and the magnetic field will force charge carriers to move in the direction of the force. The buildup of charge carriers on one side of the conductor will result in a measurable potential difference between the two sides of the conductor.

The LEM module will also work as a galvanic isolation between the high voltage primary circuit and the secondary circuit consisting of the DSP input signals.

The Hall voltage is given by:

$$V_H = \frac{I \cdot B}{n \cdot e \cdot d}$$

Where B and I represent the magnetic field and current through the conductor. n represent the density of mobile charges, e the electron charge and d is the thickness of the conductor.

The LEM modules voltage transducers, LV 25-P uses the Hall effect as follows,  $\pm$  15 V DC is applied to the terminals to create the magnetic field using a coil and a resistor in series. Through the conductor in the magnetic field, the current to be measured will be flowing and the voltage over the conductor will be connected to the ground reference via a resistor.

The voltages to be measured are phase-to-phase voltages corresponding to 230 V with the manufacturers' criteria for best accuracy, that the primary nominal  $i_{rms}$  will be 10 mA. This is achieved by letting the current pass through 40 k $\Omega$ . The current conversion ratio is 2.5 in the LEM module, which is later to be fed out over a 120  $\Omega$  resistor. The voltage over the resistor will be  $\pm$  3  $V_{rms}$  before leaving the ADC signal adjustment card as 0-3  $V_{rms}$ .

The LEM modules for current measurements, LAH 25-NP are located in the VSC: s and they are designed to have a primary nominal  $i_{rms}$  of 25 At and a secondary nominal current at 25 mA with the conversion ratio of 1:1000. The voltage over the shunt resistor will be  $\pm$  5.75  $V_{rms}$  and out from the ADC signal adjustment card 0-3  $V_{rms}$ .

The LEM module measuring the DC-link voltage will measure up to 600 V. To achieve 10 mA rms current through the primary it's placed in series with 60 k $\Omega$ . The conversion ratio of 2.5 will give a 25 mA rms output current which is fed over a 120  $\Omega$  resistor with  $\pm$  3 V over it, giving a 0 – 3 V out from the ADC signal adjustment card.

## **5.2.2 The Voltage Source Converters (VSC)**

The voltage source converters are connected in series to create a common DC-link between them. The device used in the laboratory setup is manufactured by SEMIKRON with the model name: SKS 11F B6CI 07 V12.

The main features of the VSC are the 900  $\mu$ F capacitor bank able to charge to 800 V DC. The maximum rms current fed through the converter is 18 A and its working on a 97 % efficiency. It has a capacity of switching at 10 kHz, however in this application is will operate at 4.95 kHz.

In order to ensure that the reference signal won't exceed the manufacturers current and voltage limitations during operation, both VSC: s are fitted to limit the possible output according to the specifications.

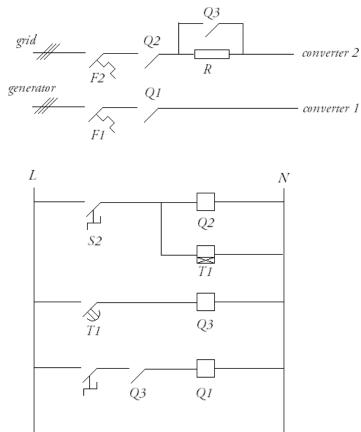

### 5.2.3 The relay setup

When the converter is connected to the grid, there is a charging current flowing to the capacitors. Due to the potential difference and the low resistive current path, the initial charging current will be relatively high, putting strain on the capacitors, diodes and fuses.

In order to limit the initial charging current, resistors are put in each phase conductor to the converter. However, as the resistive path would alter the future operation of the converters, the resistors should only be in use at the moment the converters are connected to the grid.

The solution to this is to set up a time relay, which initially limits the current with resistors but later on bypasses them when the converters are operational. The time needed to charge the capacitors is dependent on the time constant, which is approximately 1 second. The relay scheme is as follows:

Figure 27 The relay scheme protecting the converters at startup

As switch S2 is set to conduct, Q2 closes and current from the grid will flow to the converter capacitors via the resistor. Simultaneously, the timer relay (T1) will be activated setting the delayed switch to conduct after a set time. After the delayed switch starts to conduct, Q3 closes and the resistor is now bypassed.

To supply the converter connected to the generator with voltage switch S1 has to be conducting. The criterion is that the capacitors first need to be charged, which is set if Q3 is conducting.

F1 and F2 are fuses to protect the converters from currents over 16 A.

### 5.2.4 LC Filters

The current from the converters will contain high-order harmonics since the sine wave is constructed via PWM. To remove the harmonics, the converter output is filtrated using a LC filter. The switch frequency is 4.95 kHz and the grid frequency is 50 Hz. According to the stipulations concerning filter design, the cut off frequency is set to 500 Hz.

## 6. The Software Description

The converter control algorithm is written and tested in C-code and assembly in Code Composer Studio v3.1 (CCS); the development tool provided with the DSP. When the program set to run from the flash memory, it's programmed using SDFlash v1.63 [8].

CCS allows debugging; however the program does not allow variables to be viewed in real-time nor are the parameters to be adjusted while the program running. Any change in parameters needs to be reloaded into the memory and any variable graph needs manual refreshing. All graphs and variables can be simultaneously refreshed using software probe point triggering the variable update.

During the testing phase, the entire program is executed from the DSP RAM as the RAM memory is programmed considerably faster than the flash memory. The execution time is however longer from the RAM, limiting the complexity and size of algorithm calculations compared to if it was to be ran from the flash memory. Additionally, debugging in CCS when the program is executed from flash is more difficult, as graphs can't be refreshed using software probe points.

The principle for the embedded system is that each sample instance, there is an interrupt routine in which the ADC is calibrated, calculations are made on the values from the ADC, reference values from the current and voltage regulators are sent to The program is written from the shell of an example file included with the software, as the initiation sequences for every program to be executed from the DSP will be similar.

The functions that have been added:

- ADC calibration

- Clarke and Park transformation

- PI regulators

- Inverse Clarke and Park transformations

- Reference phase voltages for the PWM circuit

- Protect converters from over current and over voltage

This chapter does not aim to provide a tutorial on writing C code or assembly or using CCS apart from providing information for the basic understanding of how to run and debug the program which has been written [9][10][11].

The DSP is programmed using IQmath which enables the user to define the range and resolution of the 32-bit fixed point numbers. In this project IQmath is using the Q format 20 which range is -2048 to  $\sim$  2048 with the resolution of  $9.54 \cdot 10^{-7}$  to keep a high level of precision [12].

## 6.1 ADC calibration

ADC calibration is necessary since the ADC will be impacted by gain and offset errors contributing to errors in the control system. Calibration is executed using two reference values fed into two of the ADC channels. This will require that two of the 16 channels will be dedicated for the reference values to compensate for the errors [13][14][15][16].

The AD conversion is setup to lower the overall time for the sampling by simultaneous sampling 2 channels. The operation mode is defined in the ADCcalibrationDriver.h headerfile as well as what the reference values channels and what they correspond in ideal count value.

The calibration initiation is added to the initialization code for the DSP and in the beginning of the interrupt routine the ADC channels are read, calibrated and stored in the memory structure. From this point the values are also adjusted to correspond to values in A and V.

Using the source file gainoffset.c, the ADC-register values are altered. Initially the register values need to left-shifted 4 bits before they can be adjusted, as the ADC-register reserves the first 4 bits in the 16-bit register. The register value is subsequently altered to a two-bit complement representation, as the ADC-register stores the most negative value as the smallest value.

When the ADC-register samples values corresponding to the 12-bit resolution upper limit; 4095, there is an obvious risk for the values to exceed 4096 and be represented from 0 upwards. The equivalent scenario occurs when the ADC register contains values close to the lower bit limit being represented as 4096 and lower. Both problems can be mitigated setting a limit for the highest and lowest value to be represented. The representation can therefore only be made with values ranging from 5 bits to 4090, however this does not lower the bit resolution significantly (~0.27% lower).

44

#### 6.2 Clarke and Park transformation

Clarke and Park transformations are conducted according to the theory presented in chapter 3.3. Initially each phase passes through a symmetrization in order to remove any offset in the measurements for each phase-to-phase voltage measurement. The following process is to retrieve each phase voltage.

#### **6.2.1 Clarke transformation**

The Clarke transformation for the phase currents is identical except for the absence of the phase-to-phase to phase transformation.

The next process is to move the reference frame to a rotating two-phase orthogonal reference frame. The angular displacement of the q-axis from alfa-axis is represented by the angle THETA.

In order for the angle to be relatively stable, the voltage is firstly filtrated using a second order low pass filter before theta is calculated. The filter parameter values are calculated using MATLAB to correspond to a second order Butterworth filter with a cut off frequency of 10 Hz to remove most of the disturbance.

The filtration causes the angle between the alfa-axis and the q-axis to shift 90 degreed lagging the q-axis, prompting the Park transformation to be made between the d-axis and the alfa-axis.

### 6.2.2 Park transformation

```

void parkdq_calc(PARK *v){

_iq Cosine,Sine;

// Using look-up IQ sine table

Sine = _IQsin(v->Angle);

Cosine = _IQcos(v->Angle);

// with filtercompensation

v->d = _IQmpy(v->alfa,Cosine) + _IQmpy(v->beta,Sine);

v->q = _IQmpy(v->beta,Cosine) - _IQmpy(v->alfa,Sine);

}

```

The following step is to feed the Park transformed voltage and current values into the voltage and current regulators.

## 6.3 The PI regulators

The current and voltage regulators are designed to produce a reference value to correspond to the intended operation of each converter. The grid-side converter aims to:

- Keep the DC-link voltage stable at  $U_{DC}^{ref}$ Keep the grid voltage stable at  $U^{ref}$

The generator-side converter has only one purpose; that active power to be fed out on the grid.

#### 6.3.1 Keeping DC-link voltage stable

Keeping the DC-link voltage stable consists of feeding active current out on to the net when the wind turbine is generating power. The voltage regulator will produce a current reference value in the qaxis as only active power will be generated from the wind-turbine. The current reference is fed into a current regulator generating a qd-frame voltage value to be fed out from the grid-side converter using the PWM circuit on the DSP.

```

void VDCREGS_calc(VDCREGS *v)

{

v \rightarrow iq_ref_P = IQmpy((v \rightarrow Udc_ref - v \rightarrow Udc), v \rightarrow Kp);

v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Ts_Ki_Kp,(v \rightarrow Udc_ref - v \rightarrow Udc)) + v - v \rightarrow iq_ref_I = IQmpy(v \rightarrow Udc_ref - v \rightarrow Udc)

>iq_ref_I;

v \rightarrow coefficient = IQdiv(v \rightarrow Udc, v \rightarrow vg);

v- > iq_ref = (v- > iq_ref_P + v- > iq_ref_I);

if(v-)iq_ref > v-)iqmax

{

v->iq_ref = v->iqmax;

v \rightarrow iq_ref_I = v \rightarrow iq_ref_P;//,v \rightarrow coefficient);

else if(v->iq_ref < v->iqmin)

v \rightarrow iq_ref = v \rightarrow iqmin;

v->iq_ref_I = v->iqmin - v->iq_ref_P;//,v->coefficient);

v->iq_ref = _IQmpy(v->iq_ref, v->coefficient);

}

```

The q-axis current reference value is fed to a current regulator to obtain the phase voltages required.

```

void IregLC_calc(IREGLC *v)

{

v \rightarrow ud_ref_P = IQmpy((v \rightarrow id_ref - v \rightarrow id), v \rightarrow K);

v - ud_ref_I = IQmpy(v - Ts_Ki_K, (v - id_ref - v - id)) + v - ud_ref_I;

v-\ud_ref = (v-\ud_ref_P + v-\ud_ref_I) - _IQmpy(_IQmpy(v-\Kc, (v-\ud_ref_I) - _IQmpy(_IQmpy(v-\Ud_ref_I) - _IQmpy(_IQmpy(_IQmpy(v-\Ud_ref_I) - _IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_IQmpy(_

\geq iq_ref + v - \geq iq), IQ(0.5) + v - \geq vd;

v \rightarrow uq_ref_P = IQmpy((v \rightarrow iq_ref - v \rightarrow iq), v \rightarrow K);

v \rightarrow uq\_ref_I = IQmpy(v \rightarrow Ts\_Ki\_K, (v \rightarrow iq\_ref - v \rightarrow iq)) + v \rightarrow uq\_ref_I;

v \rightarrow uq_ref = (v \rightarrow uq_ref_P + v \rightarrow uq_ref_I) + _IQmpy(_IQmpy(v \rightarrow Kc, (v \rightarrow uq_ref_I) + _IQmpy(_IQmpy(v \rightarrow uq_ref_I) + _IQmpy(_IQmpy(u \rightarrow uq_ref_I) + _

>id_ref + v->id)),_IQ(0.5)) + v->vq;

if(v-)ud_ref > v-)umax

v \rightarrow ud_ref = v \rightarrow umax;

v-\ud_ref_I = v-\ud_ref_P -

_{IQmpy}(_{IQmpy}(v-)Kc, (v-)_{iq_ref} + v-)_{iq}),_{IQ}(0.5)) + v->_{vd});

else if(v->ud_ref < v->umin)

v \rightarrow ud_ref = v \rightarrow umin;

v->ud_ref_I = v->umin - (v->ud_ref_P - _IQmpy(_IQmpy(v-

Kc, (v-)iq_ref + v-)iq),_IQ(0.5) + v->vd);

if(v-)uq_ref > v-)umax

v \rightarrow uq_ref = v \rightarrow umax;

v-\geq uq_ref_I = v-\geq umax - (v-\geq uq_ref_P + u

_{IQmpy(\_IQmpy(v->Kc, (v->id\_ref + v->id)),\_IQ(0.5)) + v->vq)};

else if(v->uq_ref < v->umin)

v->uq ref = v->umin;

v-\geq uq\_ref_I = v-\geq umin - (v-\geq uq\_ref_P + _IQmpy(_IQmpy(v-

Kc, (v-)id_ref + v-)id),_IQ(0.5) + v->vq);

}

```

As the reference values call for both voltages in dq frame the regulator code is twice the size of the voltage regulator, which only outputs a current reference value on the q-axis.

The voltage reference values are transformed back to phase voltages using inverse Clarke and Park transformations:

#### Inverse Clarke transformation:

>beta);

```

void idq_calc(IDQ *v)

_iq Cosine,Sine;

// Using look-up IQ sine table

Sine = _{IQsin(v-)Angle)};

Cosine = _{IQcos(v-)Angle)};

//Theta angle between alfa-axel och d-axel

v-alfa = _IQmpy(v->d,Cosine) - _IQmpy(v->q,Sine);

v->beta = _IQmpy(v->q,Cosine) + _IQmpy(v->d,Sine);

}

Inverse Park transformation

void abc_calc(ABC *v)

{

v->a = IQmpy(IQ(0.816497), v->alfa);

//sqrt(2/3)

v-b = IQmpy(IQ(-0.408248), v-alfa) + IQmpy(IQ(0.707107), v-alfa)

>beta);

//sqrt(1/6) sqrt(1/2)

v \rightarrow c = IQmpy(IQ(-0.408248), v \rightarrow alfa) - IQmpy(IQ(0.707107), v \rightarrow alfa)

//sqrt(1/6) \ sqrt(1/2)

```

These values are fed to the source file called duty.c which symmetrizises the sinusoidal reference wave and feeds it to a PWM circuit on the DSP. The generated PWM signal will then control the output voltage from the grid-connected converter in order to keep the reference value.

### 6.3.2 Keeping the grid voltage stable

Keeping the grid voltage stable implies feeding reactive power out from or in to the grid-side converter depending on if the grid voltage is below or exceeds the reference value.

The reference value for reactive current is created using a voltage regulator and the output is fed into the same current regulator regulating the active current.

The current regulator parameters used are modifications of standard regulator parameter values as explained in chapter 4.4.2.

The generator side converter regulators work in parallel with the grid-side converters. The intended current reference value for the generator-side converter is based on the power-graph. However, as it involves lookup tables and speed measurements to complete, it has not been implemented. The active power requested from the generator-side converters is dependent on a manually controlled reference value, set with a potentiometer.

## 6.4 Protecting converters from over current and over voltage

In order to protect the converters from potential over current and over voltage, limitations for the measured voltage and current values are implemented.

The protection sends a stop signal to the PWM circuit halting the switching and effectively cutting the converter output current. High-order harmonics from the PWM process will trigger the high current protection without actually causing any stress on the converters. In order to handle such issues, the protection is set to respond to both a maximum limit, as well as a limit which can be triggered a number of times before halting the PWM.

```

void skydd_calc(SKYDD *v)

//limit 1

if(_IQabs(v->signal)>v->max1)

v \rightarrow tripp1 = 1;

}

//limit 2

if(_IQabs(v->signal) > v->max2)

{

v \rightarrow count + +;

}

else if(_IQabs(v->signal) < v->reset)

v->count--;

if(v->count<0)

{

v \rightarrow count = 0;

}

if(v->count > v->countmax)

v \rightarrow tripp2 = 1;

}

```

The complete code is presented in the appendix.

## 7. Experiment

The experiment will determine if the wind turbine model can generate active power out on to the power grid, while aiding in the stabilizing of grid voltage that differentiates from its nominal value.

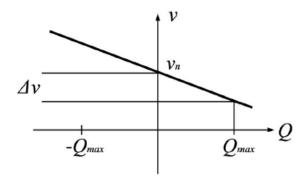

The voltage regulator running from the flash memory is set to produce reactive power to stabilize the network voltage back to its nominal value according to the following equation derived in chapter 3.4.3.

The expression shows that grid voltage is dependent on reactive power. As the grid droop characteristics for the voltage indicates, that grid voltage magnitude and reactive power are inversely proportional.

Figure 28 Grid voltage characteristics at reactive power flow, picture taken from [6]

Where  $v_n$  is the nominal voltage of the grid.

In order to simulate a voltage drop, a large inductive or resistive load can momentarily be connected to the power grid. However, as the grid in the laboratory is considered a strong power grid, i.e. low inductive and resistive components, this method would require a large inductive or resistive load.

The solution is to simulate a power grid, connecting the grid-side converter to the terminals of a 200 kVA synchronous generator. To adjust the generated voltage, the magnetization voltage will be adjusted to simulate both a lower and a higher grid voltage. Conducting the testing in this fashion will also allow for the voltage to increase from its nominal value.

## 8. Results

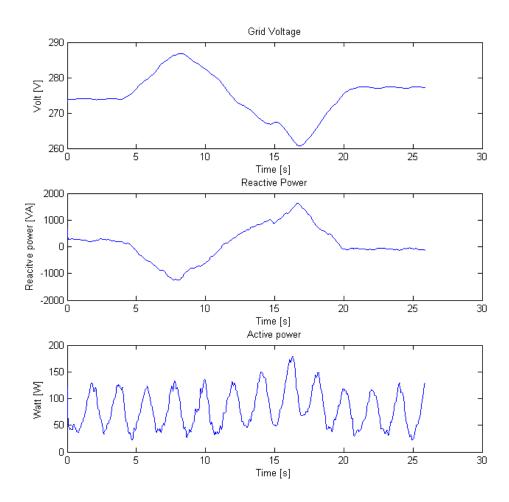

The following results are conducted where the grid voltage is not stabilized using the current regulator controlling reactive power flow.

# 8.1 Test without the grid voltage control

Figure 29 Test results without reactive power flow regulator

Varying the reactive power generated will cause voltage fluctuations corresponding to the inverse of the reactive power fed to or drawn from the grid. The active power is not dependent on the fluctuation, merely the grid frequency, which is constant. The active power displays fluctuations from the noise caused by the switching circuit and is therefore filtered to give it a smoother look.

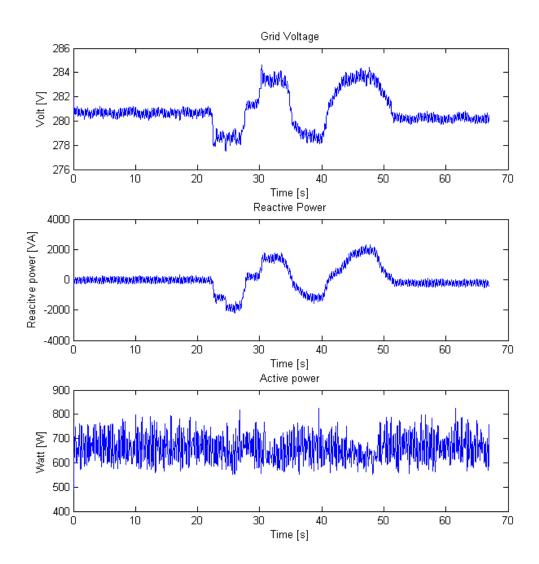

## 8.2 Test of grid voltage control

Figure 30 Test results with reactive power flow regulator

With the grid voltage regulation, the generated reactive power is proportional to the grid voltage variations as its actively attempting to suppress the variation. During this test, the active power is set to a higher value, to simulate voltage stabilization during active power generation.

The grid voltage is not entirely stable as its exhibiting a steady state error in the regulator indicating that the integral part is not correcting sufficiently.

The result is also heavily filtered to remove disturbances caused by the switching circuit.

### 9. Discussion

The back-to-back voltage source converters were successfully controlled using a control algorithm developed in the programming language C. The objective of the algorithm is to control the series connected converters to stabilize voltage fluctuations from the nominal grid voltage, while delivering active power to the grid. The voltage regulator controlling the reactive power responds correctly to the voltage reference deviation and feeds out reactive power on demand.

The control algorithm was also intended to be executed as an embedded system, independent of a secondary CPU, mainly the PC on which the algorithm is debugged from. This was successfully performed and the converters were controlled running the program from the flash memory. The process of executing the algorithm from the flash memory lowers the calculating time almost by half, as the memory sectors are read faster from the flash memory than as initially from its external memory.

The premise of controlling grid parameters such as lowering deviations from the grid nominal voltage on weaker grids allows for a wind turbine to have a greater role than simply supplying the grid with active power.

A reoccurring problem was the large disturbances, which could need further dampening using digital filters and the use of a Smith predictor.

### References

- [1] World Wind Energy Association (WWEA) "World Wind Energy Report 2009" 2009-03

- [2] J.F. Manwell, J.G. McFowan, A.L. Rogers "Wind Energy Explained Theory, Design and Application" 2:nd edition, 2009

- [3] O. Anaya-Lara, N. Jenkins, J. Ekanaye, P. Cartwright, M. Hughes "Wind Energy Generation Modelling and Control" 2009-01

- [4] Article concerning electrical design of crowbars http://axotron.se/index en.php?page=26

- [5] M. Alaküla, P. Karlsson "Power electronics Devices, Converters, Control and Applications" Department of Electrical Engineering and Automation, Lund Institute of Technology, Lund, Sweden

- [6] J. Björnstedt, M. Ström "Power Electronic Voltage and Frequency Control for Distributed Generation System" *Department of Electrical Engineering and Automation, Lund Institute of Technology*, Lund, Sweden 2005

- [7] O. Samuelsson "Kraftelektronik" *Department of Electrical Engineering and Automation, Lund Institute of Technology*, Lund, Sweden

- [8] Texas Instruments "SPRS174R Data Manual" 2001-04, revised 2010-05

- [9] Texas Instruments "SPRA958H Running an Application from Internal Flash Memory on the TMS320F28xx DSP" 2008-09

- [10] Texas Instruments "C281x C/C++ Header Files and Peripheral Examples Quick Start" Version 1.2 2009-06-27

- [11] Texas Instruments "SPRAAS1A Hardware Design Guidelines for TMS320F28xx and TMS320F28xx DSCs" 2008-09

- [12] Texas Instruments "C28x IQmath Library A Virtual Floating Point Engine v1.5" 2008-06

- [13] Texas Instruments "SPRU065D TMS320x281x DSP Event Manager (EV) Reference Guide" 2004-11, Revised 2006-08

- [14] Texas Instruments "SPRA989A F2810, F2811 and F2812 ADC Calibration" 2004-11

- [15] Texas Instruments "SPRU060D TMS320x281x DSP Analog-to-Digital Converter (ADC) Reference Guide" 2003-06, revised 2005-07

- [16] Texas Instruments "TMS320F2810, TMS320F2811 and TMS320F2812 SDFlash JTAG Programming Utilities" 2005-09

```

System Name: REG JB

File Name:

REG_JB.C

Global Q 20 (-2047 - 2047)

*/

// Include header files used in the main function

#include "target.h"

#include "DSP281x_Device.h"

//#include "DSP281x_Examples.h" // DSP281x Examples Include File

#include "IQmathLib.h"

#include "reg jb.h"

#include "parameter.h"

#include "build.h"

#include <ADCcalibrationDriver.h>

#include <math.h>

#pragma DATA_SECTION(out_buffer1, "DLOG");

//Logga data till externt minne

#pragma DATA_SECTION(out_buffer2, "DLOG");

#pragma DATA SECTION(out buffer3, "DLOG");

#pragma DATA SECTION(out buffer4, "DLOG");

#pragma DATA_SECTION(out_buffer5, "DLOG");

#pragma DATA_SECTION(out_buffer6, "DLOG");

*/

// Select the example to compile in. Only one example should be set as 1

// the rest should be set as 0.

#define EXAMPLE1 1 // Use DATA registers to toggle I/O's

#define EXAMPLE2 0 // Use SET/CLEAR registers to toggle I/O's

#define EXAMPLE3 0 // Use TOGGLE registers to toggle I/O's

*/

// Prototype statements for functions found within this file.

interrupt void MainISR(void);

interrupt void QepISR(void);

// Prototype statements for functions found within this file.

/*void delay_loop(void);