# Implementation of Fast Recursive Parameter Estimation Algorithms on the Signal Processor TMS 320

Bo Bernhardsson

Department of Automatic Control Lund Institute of Technology May 1986

| Department of Automatic Control                                                                                                          |                                                                                                                                                                               | Document name MASTER THESIS                                                                                                                                         |                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Lund Institute of<br>P.O. Box 118                                                                                                        |                                                                                                                                                                               | Date of issue May 1986                                                                                                                                              |                                                                                                                         |

| S-221 00 Lund Sweden                                                                                                                     |                                                                                                                                                                               | Document Number CODEN: LUTFD2/(TFR                                                                                                                                  | RT-5351)/1-148/(1986)                                                                                                   |

| Author(s) Bo Bernhardsson                                                                                                                |                                                                                                                                                                               | Supervisor Sten Bergman, Per Perss                                                                                                                                  | on                                                                                                                      |

|                                                                                                                                          |                                                                                                                                                                               | Sponsoring organisation Asea Relays                                                                                                                                 |                                                                                                                         |

| Title and subtitle Implementation of Fast 320                                                                                            | Recursive Parameter Esti                                                                                                                                                      | mation Algorithms on the                                                                                                                                            | Signal Processor TMS                                                                                                    |

| of a power system. Parameters that do not fault detection.  This thesis discusses the electrical power system. a signal processor, Texas | neter estimation related to<br>have a direct physical in<br>e use of fast recursive par<br>Both algorithmic and pra-<br>s TMS 320, is used. A cod<br>for parameter estimation | is usually related to measure Black-box models of e.g. atterpretation but nevertheld ameter estimation method ctical aspects are treated. It is an ARMAX-model. The | autoregressiv type gives ess can be valuable for s for fault detection in For the implementation en which automatically |

|                                                                                                                                          |                                                                                                                                                                               |                                                                                                                                                                     |                                                                                                                         |

| Key words                                                                                                                                |                                                                                                                                                                               |                                                                                                                                                                     |                                                                                                                         |

| Classification system and/or inde                                                                                                        | x terms (if any)                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                         |

| Supplementary bibliographical in                                                                                                         | formation                                                                                                                                                                     |                                                                                                                                                                     |                                                                                                                         |

| ISSN and key title                                                                                                                       |                                                                                                                                                                               |                                                                                                                                                                     | ISBN                                                                                                                    |

| Language<br>English                                                                                                                      | Number of pages 148                                                                                                                                                           | Recipient's notes                                                                                                                                                   | 1                                                                                                                       |

| Security classification                                                                                                                  |                                                                                                                                                                               | 1                                                                                                                                                                   |                                                                                                                         |

#### CONTENTS

- 1. Introduction.

- 2. Recursive Parameter Estimation.

- 3. The TMS 320 Processor with Development Boards

- 4. Signal Processor Arithmetics

- 5. Automatic Code Generation for the TMS 320.

- 6. Practical Experiments.

- 7. References.

- Appendix 1. Floating Point Procedures for TMS 320

- Appendix 2. Minimization of Quantization Effects

- Appendix 3. The Program CONVERT

- Appendix 4. The Program CODEGEN (Pascal)

- Appendix 5. The Program CODEGEN (Prolog)

## PREFACE

This thesis was written at the department of automatic control during the period of November 1984 to November 1985. I would like to thank all the people of the department for their support and enthusiasm. I am grateful to Per Persson, Karl Johan Aström and Rolf Johansson for suggestions on literature and practical hints concerning parameter estimation. I also thank Bengt Bengtsson at the department of tele transmission theory for hints concerning implementation on fast signal processors. Finally I am especially grateful to my advisorer at ASEA RELAYS, Sten Bergman, for an inspirational stay at ASEA in April 1985, and for his patience with this report.

Lund, November 1985

Bo Bernhardsson

"- So you claim that you can count, said the queen doubtfully. What is then one and on

- I dont know. I lost count, said Alice.

- Ha, she can't even do simple addition, said the queen laughing"

Lewis Caroll

#### 1. Introduction

The purpose for this MS dissertation has been to explore the possibilities of using fast recursive parameter estimation methods for fault detection in electrical power system. This included the following tasks:

- □ Learn recursive parameter estimation methods.

- m Study and select appropriate hardware.

- Develop software.

- □ Perform experiments with fault detection.

A power system is an electrical network. When short circuits or other faults occur the properties of the network changes. One possibility to detect a fault is thus to monitor the network parameters. The final goal was defined as follows: Determine the feasibility to estimate the R & L parameters from a given data record in less than a period i.e. 20 ms. This goal was successfully completed. Since rapid estimation is crucial a lot of effort was devoted to factors which influence convergence rates. This involves both algorithmic and hardware issues.

After several considerations it was decided to use a signal processor TMS 320. This was based partially on cost and availability. A drawback of the signal processor is that it has to be programmed in assembler. To make this in a convenient way a code generator was developed which generates TMS assembler based on a high level description of the estimation algorithm.

This report is organized as follows:

Parameter estimation with practical aspects on implementation is discussed in <u>Section 2</u>. The problem of detecting changes in the parameters ('faults') on-line is also discussed here. Different possibilities to implement the algorithms proposed in section 2 on-line have been investigated. The choice stood between using a floating point array processor to an IBM personal computer and a signal processor TMS 320 normally used for other applications.

The TMS 320 with development boards is described in <u>Section 3</u>. The new TMS 32020 processor with enhanced possibilities to floating point calculations is also discussed.

A drawback with today's signal processors is that they lack floating point numbers. Either all calculations must be done using fixed point numbers or floating point routines must be implemented in software. This is discussed in Section 4. A little unusual suggestion for the arithmetic format called the FOCUS number system with fractional exponent and no mantissa is also described here.

A procedure based system for automatically generating assembly code for the TMS 320 is described in <u>Section 5</u>. The code generator is written in Pascal, it is also shown how it could have been written in Prolog making an interactive programming environment possible.

The practical experiments performed are described in Section 6.

Section 7 contains a reference list and five appendices with programs etc..

# 2. Recursive Parameter Estimation

Models of physical, economical, social or biological systems can all be obtained in at least two different ways: by use of prior knowledge about the system or by experimentation and observation. Successful modelling is usually a combination of both. Often some parameters of the model have to be determined from experiments. Due to the development in computer technology and VLSI design the technics of parameter estimation can now be applied to new areas. If knowledge about the system is needed quickly the time for calculating good guesses of the parameters can be critical. One then has to settle with faster, less sofisticated algorithms. This is particularly the case for relay systems where decisions must be taken quickly. It is important that the algorithms be robust against disturbances. Reliability is especially important for relay systems that has to work, say once in ten years.

# 2.1 The ARMA Model

For a survey over the field of parameter estimation see [12]. We will here restrict us to one specific family of models often used for linear systems, the ARMAX-processes:

$$A(q)y(k) = B(q)u(k) + C(q)e(k) k = ..-1, 0, 1, ..$$

(2.1)

Here y is the output, u the input and e a disturbance often modelled to be white (often also Gaussian) noise. A, B, and C are polynomials in the forward-shift operator q, e.g. qy(k) = y(k+1).

The coefficients of the polynomials A,B and C might be time-varying. The impedance of a power net-work will e.g. change drastically when short-circuit occurs. This is the idea behind the ASEA RELAYS interest in these problems. 'Fault detection' means to discover when these parameter changes occurs. For the moment we will however assume that A,B and C are time-independent.

The signals y and u are assumed to be known and the problem is to fit the polynomial-coefficients to experimental data as well as possible. To measure how well the model corresponds to data some criterion must be introduced. The resulting 'optimal' parameter estimates will be highly dependent on how this criteria is chosen. The least squares criterion

$$J(A, B, C, N) = \sum_{1}^{N} \hat{e}^{2}(k)$$

(2.2)

is commonly used. Here e(k) is some kind of prediction error. The equation (2.1) can also be written more compactly as

$$y(k) = \Theta^{T} \varphi(k) + e(k)$$

(2.3)

where

$$\Theta = (a_1...a_m, b_1...b_n, c_1...c_1)^T$$

$$\varphi = (-y(k-1)...-y(k-m+1), u(k-1)...u(k-n+1), e(k-1)...e(k-j))^T$$

The signals e(k-1)...e(k-j) are not measurable. They are replaced by estimates calculated from prior measurements, see [1]. The parameter which minimizes the least square criterion is given by

$$\Theta = \left[\Phi^{T}\Phi\right]^{-1}\Phi^{T}Y \tag{2.4}$$

where

$$\Phi = \begin{bmatrix} \phi_1^T \\ \vdots \\ \dot{\phi}_N^T \end{bmatrix} \quad \text{and} \quad Y = \begin{bmatrix} y_1 \\ \vdots \\ \dot{y}_N \end{bmatrix}$$

It can be shown that if  $C(q) = q^n$  and e(k) is white noise with zero mean and finite variance then the parameters  $\Theta$  in (2.3) can be estimated unbiasedly by (2.4). With some restrictions on the input signal ("sufficient richness") the variance of the estimates will approach zero. This means that the parameters can be estimated arbitrary well if N is large enough. The 'convergence-rate' is determined through

$$\operatorname{var} \hat{\Theta} = \sigma^2 (\Phi^T \Phi)^{-1}$$

If  $C(q) \Leftrightarrow q^n$  the estimates (2.4) will be biased using the least squares criterion. Unbiased estimates can be obtained if other estimation methods are used, see [1]. Neither of these methods are suitable for on-line computation because a large matrix has to be inverted every time new data is obtained.

criterion. Unbiased estimates can be obtained if other estimation methods are used, see [1]. Neither of these methods are suitable for on-line computation because a large matrix has to be inverted every time new data is obtained. This will make on-line computation practically impossible which is a major drawback if the results are needed quickly. The time for detection of a short circuit in a power system should e.g. be less than one period i.e. 20 ms. For a discussion of fault detection in power systems see [2].

The least squares algorithm (2.4) can be written as a recursive formula. This means that new guesses of the model parameters are obtained in terms of old guesses. This speeds up the updating. It allows higher sampling rates and uses less memory.

#### 2.3 Recursive Computation

The recursive least squares algorithm can be written as

$$P(N+1) = [P(N)^{-1} + \varphi(N+1)\varphi(N+1)^{T}]^{-1}$$

(2.5)

$$\hat{\Theta}(N+1) = \hat{\Theta}(N) + P(N+1)\phi(N+1)[y(N+1) - \hat{\Theta}^{T}(N)\phi(N+1)]$$

, see [10]. This can be interpreted as a steepest descent method with decreasing gain given by the Hessian matrix P. Similar algorithms can be found in optimization literature. The equations (2.5) can also be viewed as a Kalman filter for a system having constant parameters as state variables and white measurement noise e:

$$\begin{cases} \Theta(k+1) = \Theta(k) \\ y(k) = \Theta^{T} \varphi(k) + \Theta(k) \end{cases}$$

The most time consuming part of (2.5) is the matrix inversion. By use of a matrix inversion lemma one can take advantage of the fact that  $\phi\phi^T$  is a rank one matrix to rewrite the updating of the P matrix in (2.5). The new formula will require a computation time proportional to  $n^2$  instead of  $n^3$  where n is the number of parameters, see [10]. Even after this improvement the recursive formula (2.5) may be too demanding computationally. Different simplifications

have therefore been developed.

In stochastic approximation the matrix P is replaced by the scalar

$$P(k) = \left[ \begin{array}{c} k \\ \gamma \end{array} \phi^{T} \phi \right]^{-1}$$

The convergence of the estimates with this algorithm will generally be slower but with proper conditions on the input the estimates will still be unbiased. The properties of the parameter estimation depend of course on the model and on the nature of the disturbances. If there is no disturbances the estimates from (2.5) will converge to the correct values after a finite number of steps. For stochastic approximation we have instead the following sufficient conditions on P(k) for consistent estimates:

$$P(k) \ge 0$$

$\sum P(k) = \infty$

$\sum P^{2}(k) < \infty$

If these three conditions are fulfilled the estimates will eventually converge to the correct values. Nothing is however said about the convergence rate which usually is slower than with the Hessian matrix P. Kestin and Lapidus has suggested that P(k) only should be decreased if  $\Delta\Theta_k$  changes sign. This, and similar tricks, can increase the convergence rate.

A third alternative is to have constant scalar gain P. This is called 'the MIT-rule' or just a 'constant gain algorithm'. The calculations can then be performed even faster, see [23]. A correct choice of P is important and may be troublesome. The choice is to be a trade-off between convergence rate and robustness against noise. A large P will give a fast but noise sensitive adaption. The choice of P is unfortunately also very sensitive to changes in the input signal. Too large a P will give an unstable algorithm as seen by the following calculation:

Introducing the prediction error  $\Theta = \Theta - \Theta$  equation (2.5) can be written as

$$\tilde{\Theta}_{t} = H_{t}\tilde{\Theta}_{t-1} + P \varphi_{t}e_{t}$$

where

$$H_{t} = I - P \varphi_{t} \varphi_{t}^{T}$$

(2.6)

The matrix  $H_t$  has the eigenvalues 1, with multiplicity n-1, and 1-P $\phi_t^T\phi_t$  . The recursive equation (2.6) is thus unstable if P is negative or larger than

$$P_{c} = \frac{2}{\varphi_{t}^{T} \varphi_{t}}$$

Ιf

$$P = \frac{1}{\varphi_t \varphi_t}$$

then H becomes a Householder projection-matrix. This will give the minimal prediction error. A proper choice of P therefore requires good knowledge about the magnitude of the input and output signals. This knowledge can be obtained e.g. through simulations of the system with 'typical' input signals.

With a constant P the variance of the estimates will not converge to zero. Still the method has the advantage of being very simple and can easily be implemented on a signal processor like the TMS 320. That the variance of the estimates not converges to zero should not worry to much. There is a general conflict between fast convergence and possibility to follow system variations. The constant gain algorithm has the advantage of being able to follow system variations fast.

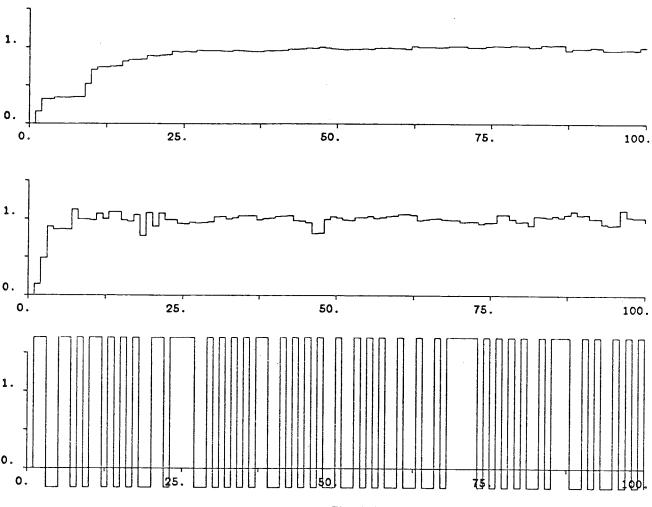

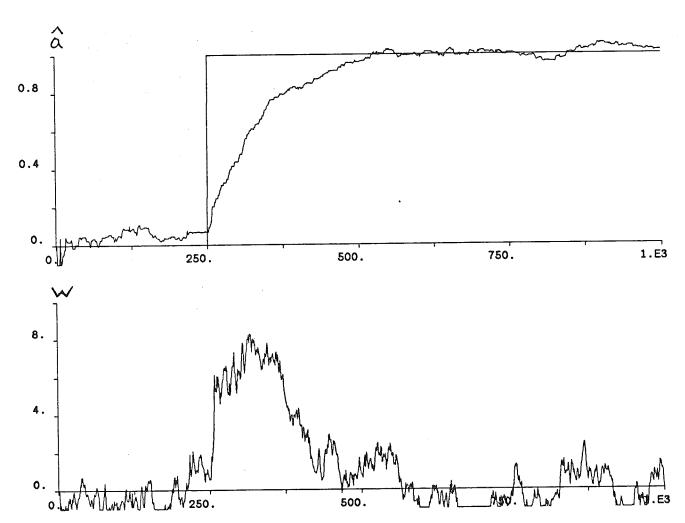

Ex 2.1 Figure 2.1 shows some simulations of the constant gain algorithm with  $y(k) = a\phi(k) + e(k)$ , a=1, e(k) is white noise with zero mean and variance V(e) = 0.1.  $\phi(k)$  is randomly generated with a Gaussian distribution and  $V(\phi) = 1$ . P is a constant equal to (a) 0.1, (b) 0.5 and (c) 5.

Fig 2.1

# A Comparison between methods

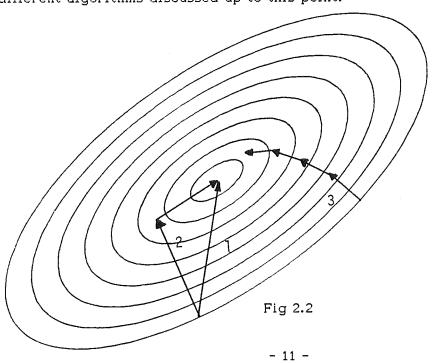

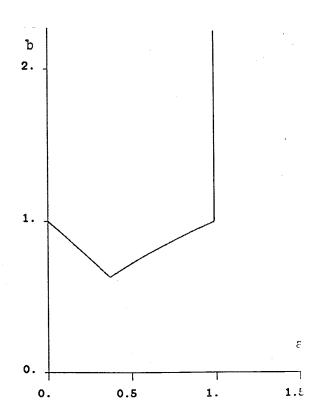

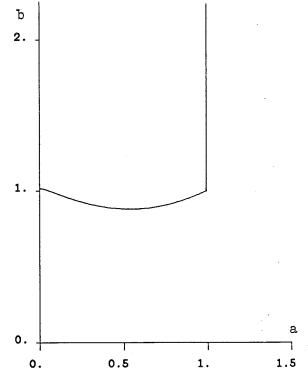

Figure 2.2 shows how the parameter estimates typically change when using the different algorithms discussed up to this point.

- 1) P = Hessian matrix, RLS algorithm.

- 2) P = Decreasing scalar gain, Stochastic approximation.

- 3) P = Constant scalar gain, MIT-rule.

Comparing the calculation time needed in 1,2 and 3 one sees that the following is needed

- 1) Inversion of n\*n matrix (n= number of estimates).

- 2) Inversion of scalar, otherwise like 3.

- 3) Scalar product of n-vectors.

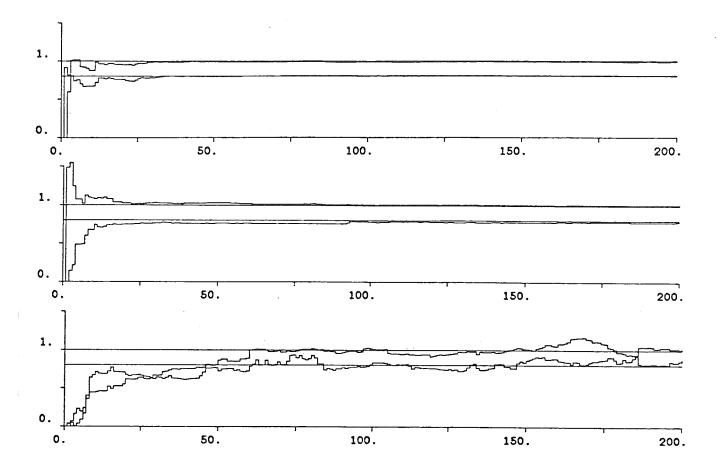

Comparing the convergence rate one sees that in the case of no noise the RLS method converges to the correct value in a finite number of steps and that algorithms with a scalar P converge exponentially instead (provided that the input u is 'sufficiently rich'). Generally the stochastic approximation algorithm gives slower convergence and using the MIT-rule the variance of the estimates will not converge to zero at all. This can be seen from the following example:

```

Ex 2.2 y(k+1) = ay(k) + bu(k) + e(k) V(e) = 0.1

a = 0.8

b = 1

u = Random binary sequence with amplitude 1

1) RLS with \Theta(0) = 0 and P(0) = 100 I

2) Stoch. approximation P(k) = 1/\Sigma \phi^T \phi

3) Constant gain P = 0.05

```

Fig 2.3

# Numerical Problems, the UDU T-Algorithm

The recursive least squares algorithm described above is poorly conditioned numerically because it requires inversion of the matrix  $\Phi^T\Phi$  in (2.4) whose elements are products of measured signals. Algorithms which avoids squaring the signals can be obtained by writing P as U D U<sup>T</sup> and derive recursive equations for U and D. These class of algorithms are called square root algorithms. They are discussed in debth in Biermann [3]. These algorithms are all rather computationally complicated.

To estimate the parameters unbiasedly and consistently from input - output data the input signal has to fulfil certain requirements. The more parameters we want to estimate the 'richer' the input signal has to be. The input signal should excitate all modes. Another way to say the same is that to find n unknowned one has to have n equations. There are a number of criterions on when it is possible to estimate n parameters consistently. The most useful is perhaps:

#### Theorem

Sufficient conditions for estimating n parameters consistently in an ARMAX-model is that

(1)

$$\bar{u} = \lim_{N \to \infty} \frac{1}{N} + \frac{N}{N} u(k)$$

exists.

(2)

$$R(i) = \lim_{N \to \infty} \frac{1}{N} = \sum_{k=0}^{N} \{u(k+i) - u\}\{u(k) - u\} \text{ exists for all i.}$$

(3) The Toeplitz matrix

$$A_n = \{a_{ij} = R(i-j)\}\ i=1,...,n$$

This implies consistent estimates for the least square algorithm, the maximum likelihood algorithm and the maximum likelihood method with white measurement noise, see [4]. Observe that since a matrix is positive definite if and only if its leading principal minors are positive, an input signal that do not satisfy the conditions for an order n do not satisfy them for any greater order.

For instance if the input is a pure sinusoidal we can see that the conditions are satisfied for order two (unless there is some aliasing effect) but not for order three or greater:

A pure sinusoidal is not persistently excitating of order three. The connection between the input and output is given by the transfer function at the frequency of the sinusoidal input. This transfer function is a complex number and therefore totally determined by two parameters. Yet another way to say this is that the sinusoidal output is determined by its amplitude and phase. In the same way if the input signal is a sum of n different sinusoidals at most 2n parameters can be estimated consistently.

A frequency domain variant of conditions for sufficient richness in the input signal can be found in [4].

#### 2.5 Time Varying Systems

Up to this point only time invariant models have been discussed. That is, the parameters to be determined are constant but unknown. A little different problem arises when it is known that the system parameters can change and the goal is to detect or adapt to such changes. These changes are often called 'faults', although these 'faults' does not necessarily correspond to malfunctions of the system. When having time-varying systems the least squares algorithm above is not satisfactory since the decreasing gain will make parameter-changes hard to detect. The influence of old data therefore has to be decreased. This can be done by introducing so called forgetting-factors. The loss function can e.g be changed to give exponentially decreasing weights to old data:

$$J(\Theta) = \sum_{i=1}^{N} \lambda^{N-k} \hat{e}^{2}(k)$$

The stochastic approximation algorithm will then be

$$P(N+1) = [\lambda P(N)^{-1} + \phi^{T}(N+1)\phi(N+1)]^{-1}$$

(2.8)

$$\hat{\Theta}(N+1) = \hat{\Theta}(N) + P(N+1)\phi(N+1)[y_{N+1} - \hat{\Theta}^{T}(N)\phi(N+1)]$$

The scalar P will now not approach zero. The forgetting factor,  $\lambda$ , will make it possible to adapt to system variations. The choice of  $\lambda$  will be a trade-off between fast adaption and robustness against noise, as can be seen from the following example.

The stochastic approximation algorithm will then be

$$P(N+1) = [\lambda P(N)^{-1} + \phi^{T}(N+1)\phi(N+1)]^{-1}$$

$$\hat{\Theta}(N+1) = \hat{\Theta}(N) + P(N+1)\phi(N+1)[y_{N+1} - \hat{\Theta}^{T}(N)\phi(N+1)]$$

(2.8)

The scalar P will now not approach zero. The forgetting factor,  $\lambda$ , will make it possible to adapt to system variations. The choice of  $\lambda$  will be a trade-off between fast adaption and robustness against noise, as can be seen from the following example.

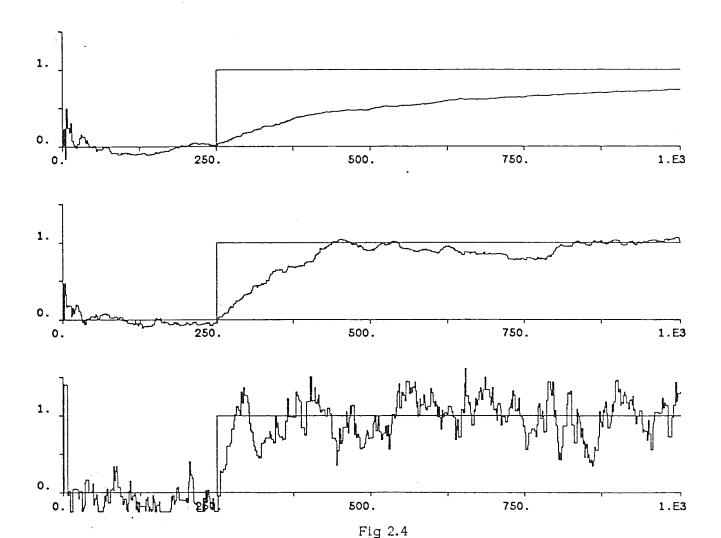

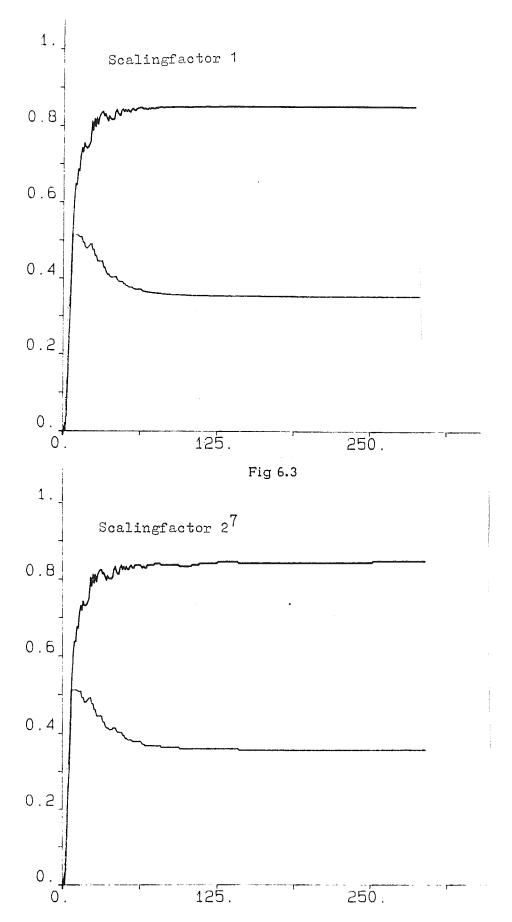

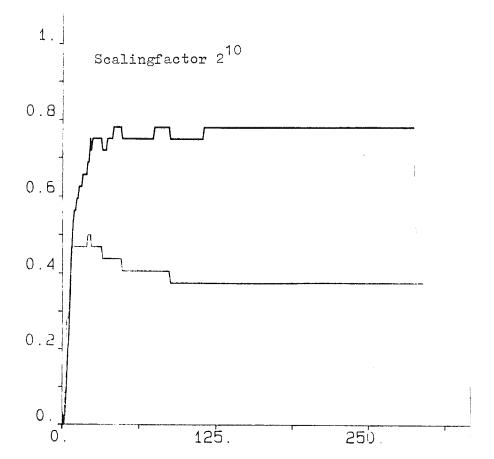

Ex 2.3

$$y(k) = au(k) + e(k)$$

$\lambda = 1, 0.99, 0.9$

$a = 0 (k<250) \text{ and } 1 (k \ge 250)$

$V(e) = 0.5$

- 16 -

#### Detecting Sudden Parameter Changes

Different methods have been suggested for finding large changes in the parameters. For a summary see [5]. Most methods require good knowledge about the disturbances which are often modelled having Gaussian distributions. This can partly be motivated by the central limit theorem, however if this fails to be true the properties of the algorithms might change drastically. It is probably not true that the disturbances occurring in power systems have Gaussian distribution.

The most obvious method for fault detection is perhaps to look at the magnitude of the estimation errors e(k). This has also been suggested in the literature. Large estimation errors suggest that a change in the parameters of the system has occured. Different schemes for implementing the above idea has been proposed, see e.g. [5].

Drawbacks of the above suggested methods are easily found. Only faults that have a large influence on the output signal can be detected. Better fault detection methods can be obtained by looking at the parameter estimates  $\hat{\Theta}$  directly and try to detect a change in these instead. One way of doing this is discussed in [5]. Introduce the difference between two consecutive estimates

$$\Delta \hat{\Theta}_{+} = \hat{\Theta}_{+} - \hat{\Theta}_{+-1}$$

If  $\Delta\hat{\Theta}$  is large this suggests a change in the parameters. A way of fault detection would therefore be to look at the norm of  $\Delta\hat{\Theta}_t$ . If the norm is larger than some threshold it is concluded that a fault has occurred. The threshold must be a compromise between low false alarm frequency and high sensitivity for faults. The test can be improved if one looks at more than one consecutive samples, e.g. by setting  $W_{t+1} = \lambda W_t + \Delta\hat{\Theta}_t$  where  $0 \le \lambda < 1$

Another possible fault detection method uses the direction of the parameter variations. In case of constant parameters the variation of the estimates has no trend and therefore

$$P (\Delta \hat{\Theta}_{t}^{T} W_{t} > 0) = P (\Delta \hat{\Theta}_{t}^{T} W_{t} < 0) = \frac{1}{2}$$

In case of a fault this will however no longer be true. The trend of the parameter estimates will then give.

$$P (\Delta \hat{\Theta}_{t}^{T} W_{t} > 0) > P (\Delta \hat{\Theta}_{t}^{T} W_{t} < 0)$$

This method has been suggested by Hägglund in [5]. It is a development of similar arguments used on the output estimates. For a discussion of this see [6].

Example 4 shows how the method of looking on the magnitude of the estimation error can be used to detect a change in the gain of a very simple system. For other examples, see [5].

Ex. 2.4

$$y(k) = au(k) + e(k)$$

$a = 0$  if  $k \le 250$  else 1

$u = random \text{ signal with } V(u)=1$

$V(e) = 0.1$

Fig 2.5

The success of all fault-detection algorithms described above will be rather dependent on the nature of the disturbances. In the theory these are often modelled to be Gaussian. If this fails to be true the fault detection might detoriate. The conclusion is that the applicability of the chosen method has to be carefully checked in practice on real input output data.

# The TMS 32010 Processor with Development Boards

#### 3.1 Introduction

The digital signal processor TMS 32010 is a member of Texas Instruments new digital signal processing family, designed especially for high-speed numeric-intensive applications. It is a 16/32-bit single-chip microcomputer with an on-chip array multiplier which offers an inexpensive alternative to multichip bit-slice processors.

The TMS320 is capable of performing 5 million instructions per second. This is due to the highly pipelined Harvard architecture and the reduction of the instruction set to incorporate only those operations normally needed for digital signal processing algorithms.

Table 3.1 lists some 'typical applications' of the TMS 320 as presented by TEXAS INSTRUMENT. It should be noted that those are <u>possible</u> applications, all have probably not been tried out in reality.

| SIGNAL PROCESSING                                                | TELECOMMUNICATIONS                                                              | IMAGE PROCESSING                               |

|------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------|

| Digital filtering                                                | Adaptive equalizers                                                             | <ul><li>Pattern recognition</li></ul>          |

| <ul><li>Correlation</li></ul>                                    | <ul><li>μ/A law conversion</li></ul>                                            | <ul><li>Image enhancement</li></ul>            |

| <ul> <li>Hilbert transforms</li> </ul>                           | <ul> <li>Time generators</li> </ul>                                             | <ul><li>Image compression</li></ul>            |

| Windowing                                                        | <ul> <li>High speed modems</li> </ul>                                           | <ul> <li>Homomorphic processing</li> </ul>     |

| Fast Fourier transforms                                          | <ul> <li>Multiple-bit-rate modems</li> </ul>                                    | <ul> <li>Radar and sonar processing</li> </ul> |

| <ul><li>Adaptive filtering</li><li>Waveform generation</li></ul> | <ul> <li>Amplitude, frequency, and phase<br/>modulation/demodulation</li> </ul> | HIGH-SPEED CONTROL                             |

| <ul> <li>Speech processing</li> </ul>                            | <ul> <li>Data encryption</li> </ul>                                             | <ul><li>Servo links</li></ul>                  |

| Radar and sonar processing                                       | <ul> <li>Data scrambling</li> </ul>                                             | <ul> <li>Position and rate control</li> </ul>  |

| Electronic counter measures                                      | <ul> <li>Digital filtering</li> </ul>                                           | <ul><li>Motor control</li></ul>                |

| Seismic processing                                               | <ul> <li>Data compression</li> </ul>                                            | <ul> <li>Missile guidance</li> </ul>           |

|                                                                  | <ul> <li>Spread-spectrum communications</li> </ul>                              | <ul> <li>Remote feedback control</li> </ul>    |

|                                                                  |                                                                                 | <ul><li>Robotics</li></ul>                     |

| INSTRUMENTATION                                                  | NUMERIC PROCESSING                                                              | SPEECH PROCESSING                              |

| Spectrum analysis                                                | Fast multiply/divide                                                            | <ul><li>Speech analysis</li></ul>              |

| Digital filtering                                                | <ul> <li>Double-precision operations</li> </ul>                                 | <ul><li>Speech synthesis</li></ul>             |

| Phase-locked loops                                               | <ul><li>Fast scaling</li></ul>                                                  | <ul><li>Speech recognition</li></ul>           |

| <ul><li>Averaging</li></ul>                                      | <ul> <li>Non-linear function</li> </ul>                                         | <ul><li>Voice store and forward</li></ul>      |

Table 3.1

computation

(i.e.,  $\sin x$ ,  $e^X$ )

Vocoders

Speaker authentification

Arbitrary waveform generation

Transient analysis

The key features of the TMS 320, as described by Texas Instrument, are collected in table 3.2.

- 200-ns instruction cycle

- 288-byte on-chip data RAM

- ROMless version TMS32010

- 3K-byte on-chip program ROM TMS320M10

- External program memory expansion to a total of 8K bytes at full speed

- 16-bit instruction/data word

- 32-bit ALU/accumulator

- 16 x 16-bit multiply in 200 ns

- 0 to 15-bit barrel shifter

- Eight input and eight output channels

- 16-bit bidirectional data bus with 40-megabits-per-second transfer rate

- Interrupt with full context save

- Signed two's complement fixed-point arithmetic

- 2.7-micron NMOS technology

- Single 5-V supply

- 40-pin DIP

#### Table 3.2

The processor costs 50 \$ and the delivery time is said to be about 8 weeks (Texas Instrument, Stockholm). This has been verified (for the processor and evaluation board) by the author. The analog interface however took about 4 months to get. The evaluation module costs 995 \$ and the analog interface board 850 \$ (spring 1985).

The easiest way to become familiar to the TMS is probably to read [11], [19], [20] and [21]. These manuals are available from TEXAS INSTRUMENT. Another good introduction is presented in the collected papers [29] which

also contains a summary of digital signal processing techniques. It is advisable to do small experimental programs in parallel to reading and use the simulator to test and verify these. The architecture is described in section 3.3. The system development tools including a simulator on VAX, an emulator board and a analog interface board is described in section 3.4.

#### 3.2 Why the TMS 320 Was Chosen, Some Alternatives

When this work was started the choice of implementation stood between using an array processor-floating point processor attached to an IBM personal computer and using a DSP-chip such as the TMS 320. The market for array processors was investigated by reading articles and advertisements. The best alternative found was a product available from SYSTOLIC SYSTEMS called the PC-100 and PC-1000 DESKTOP ARRAY PROCESSOR.

The PC-100 is a array processor that can increase the computational speed of the IBM PC over 100 times or a factor 3-10 if compared to a PC with 8087 coprocessor. The PC-100 features IEEE standard arithmetic, a 32-bit floating point processor, parallel I/O on the IBM PC bus, an extensive mathematical software library and a high-resolution graphics package.

The PC-100 is programmed in ANSI 77 FQRTRAN via subroutine calls to the PC-100's math library. The math library consists of commonly used matrix/vector routines, linear equation solvers, numeric integration methods, simulation tools, optimization algorithms and least square curve fitting. Fortran callable routines are provided to evaluate trigonometric and transcendental functions.

A signal processing library is also available with the PC-100. It contains Fortran callable routines for fast Fourier transforms, digital filtering, correlation, convolution and spectrum analysis. The PC-100 costs 2995 \$ (October 1984) plus about 2000 \$ for software library routines for signal processing, matrix operations and high-resolution graphics.

A short summary of the math library is given in below.

#### LINEAR MATRIX/VECTOR OPERATIONS

- Matrix/Vector Clear

- Matrix/Vector Addition

- Matrix/Vector Subtraction

- Matrix/Vector Multiplication

- Matrix Inversion (Vector Division)

- Solution of Linear Equations

- Solution of Triangular Equations

- · Least Square Curve Fitting

#### **NONLINEAR MATRIX/VECTOR OPERATIONS**

- Matrix/Vector Absolute Value

- Matrix/Vector Squared

- Matrix/Vector Square RootMatrix/Vector Logorithm

- Matrix/Vector Exponential

- Matrix/Vector Sine/Cosine

- Random Number Generator

#### SIGNAL PROCESSING LIBRARY

- Fast Fourier Transforms (FFTs)

- Digital Filtering

- Window Functions

- Auto/Cross Spectrum

- Convolution/Correlation Coherence Function

#### SIMULATION/INTEGRATION LIBRARY

- Trapezoidal Rule Integration

- Runge-Kutta Integration

- Predictor-Corrector Integration

#### **UNCONSTRAINED OPTIMIZATION**

- Steepest Descent Method

- Davidon-Fletcher-Powell (DFP) Method

- Broyden-Fletcher-Shanno (BFS) Method

#### PC-100 HARDWARE SPECIFICATIONS

| Wordlength (24-bit mantisa, 8-bit exponent) | <br>32 bits  |

|---------------------------------------------|--------------|

| Multiply Time (32-bit floating point)       | <br>500 nsec |

| Addition Time (32-bit floating point)       | <br>500 nsec |

| Computational Speed                         | <br>1 MFLOP  |

Table 3.3 contains some benchmarks of the PC-100 as presented by SYSTOLIC SYSTEMS.

| Calculation                   | IBM PC  | IBM PC + 8087 | IBM PC + PC 100 |

|-------------------------------|---------|---------------|-----------------|

| 100*100<br>Matrix<br>Multiply | 38 min  | 9 min         | 21 sec          |

| 100*100<br>Matrix<br>Addition | 12 sec  | 4 sec         | 0.31 sec        |

| 1024 point<br>Real FFT        | 4.1 sec | 0.9 sec       | 0.06 sec        |

Table 3.3

#### The PC-1000

This is how the PC-1000 is described by the manufacturer, Systolic Systems:

"The PC-1000 desktop array processor is the new industry standard for real-time data acquisition, estimation and control because now you can do it all for less than \$20,000. Applications like classical control, digital filtering and adaptive control can all be solved in real-time on the IBM PC and PC 1000. Control system designs based on frequency domain and multivariable control methods can all be implemented on the PC 1000 in a matter of minutes to improve engineering productivity. Decision analysis and graphics are performed on the IBM PC based on data received from the PC 1000. The PC 1000 can also be used in the laboratory for evaluating several engineering designs in the same day."

Application software to the PC-1000 can be written in high-level language such as FORTRAN or ADA on the IBM PC. The PC 1000 consists of a master processor, slave processor and data acquisition system. The is designed with a iAPX 8086 CPU, iAPX 8087 math coprocessor and 256K memory. The master processor performs numerical computations, coordinates each slave processor and communicates with the IBM PC. Two 32-bit slave processors can be installed in the PC 1000 to evaluate control functions at measurable throughput rates of up to 9.2 MFLOPs.

The data acquisition system provides 32 analog I/O channels with a maximum sampling frequency of (only) 2000 Hz.

The speedup of the PC-1000 system is 1000 times compared to the IBM PC (without coprocessor) when performing multiplication and addition.

The PC-1000 costs 20,000 \$ (Sept. 1984). It was therefore not consider any further in this project.

#### The TMS 32020 Processor

The TMS 32020 has been introduced during the spring of 1985. Its main features are collected in fig 3.4. There will also be development boards available for the TMS 32020. The system cost will however be so much greater so that the TMS 32020 can not be regarded as an alternative to the TMS 32010.

- \* 170 ns instruction cycle time

- \* 544 words of on-chip RAM (288 words are always data memory, 256 words are programmable as either data or program memory)

- \* 128K words of total program/data space

- \* 16-bit data word with internal 32-bit operations

- \* 16-bit instruction word

- \* Block moves for efficient data/code management

- \* 32-bit ALU and accumulator

- \* Single-cycle 16x16-bit multiply / 32-bit accumulate instruction

- : Floating point operation support through instruction set

- \* 0-16 bit input scaling shifter:

- \* Fractional/integer arithmetic support

- \* Variety of bit-manipulation and logical instructions

- \* 5 auxiliary registers (ARs) for indirect addressing and temporary storage

- \* A register arithmetic unit (RAU) dedicated to the AR file for arithmetic operations on AR and for auto-indexing by 16-bit numbers

- \* 16-bit parallel multiprocessor interface

- \* A hardware global memory interface

- \* Serial port for multiprocessing and interfacing to codecs and serial A/D converters

- \* On-chip timer for control operations

- \* 3 external maskable user interrupts

- \* l non-maskable interrupt for test and emulation On-chip clock generator

#### Fig 3.4

A very important factor when choosing the equipment to use is to check that the processor and development tools will be available with not too long delivery time. This can not be enough stressed.

#### Conclusions

The PC-100 (PC-1000) system needs an IBM PC. It is a suitable system for doing extensive simulations of different estimation algorithms off-line with simulated input data. As an component of a small intelligent relay system it is both too expensive with a system cost of 5-10,000 \$ and too slow for on-line calculations. Another disadvantage was that those systems were, when this project was started in November 1985, rather new and untested.

Instead it was decided to look into signal processors. Those have until recently only been used for a restricted type of applications like digital filters, FFT calculations or voice recognition. They are now being used in new areas where computational speed is of importance.

This inheritance of technique has had some drawbacks. The algorithms for which signal processors normally have been used can be characterized by very simple calculations being performed very fast. The signal processors are therefore programmed in assembler and use fixpoint arithmetics. This is the best trade off between complexity and speed in traditional applications. In control applications a slower sampling rate is used and often much can be gained by using a more advanced, and therefore more computationally complicated, algorithm.

It is therefore desirable to program in a higher, signal-processing oriented, language and to use floating point arithmetics.

The question arising was therefore: Is it possible to implement e.g. a parameter estimation algorithm on todays signal processors? And if not, what features are lacking? Which components should a signal processor contain if it is going to be used for e.g. adaptive control algorithms? How should it be programmed?

#### Future Trends for Signal Processors

(The comments inside paranthesis stands for the TMS 320)

☐ Faster clock cycle. (170 ns instead of 200 ns)

☐ More RAM on-chip. (544 \* 16 bit words)

- □ More address space for program, external data and I/O. (64 K + 64 K)

- □ Floating point support. (Instructions for normalize and computed shifts)

- multi address machines.

- □ More addressing modes. (Register ALU for e.g. auto-indexing)

- ☐ More functionality: timers, communication ports. (On chip timer and serial port).

- □ Loop and repeat hardware. (repeat counter)

- ☐ Better ALU.(logical operations on 32 bits etc)

- ☐ More interrupt support, context switch support. (3 external maskable)

- □ Lowering of external hardware speed requirements. (Wait states for slow memorys)

- m Multi processor interfaces.

- m Higher level programming languages.

- ☐ Higher degree of complexity. (More instructions)

In November 1985 the TMS 320 was believed to be the most promising signal processor. This opinion has just been strengthen during the project. There have appeared a lot of articles describing the use of TMS 320 in different applications, see [34], [35], [36], [37] and [38]. The TMS 320 has almost got a status of 'industrial standard' in the United States. Much of this is due to its simple architecture.

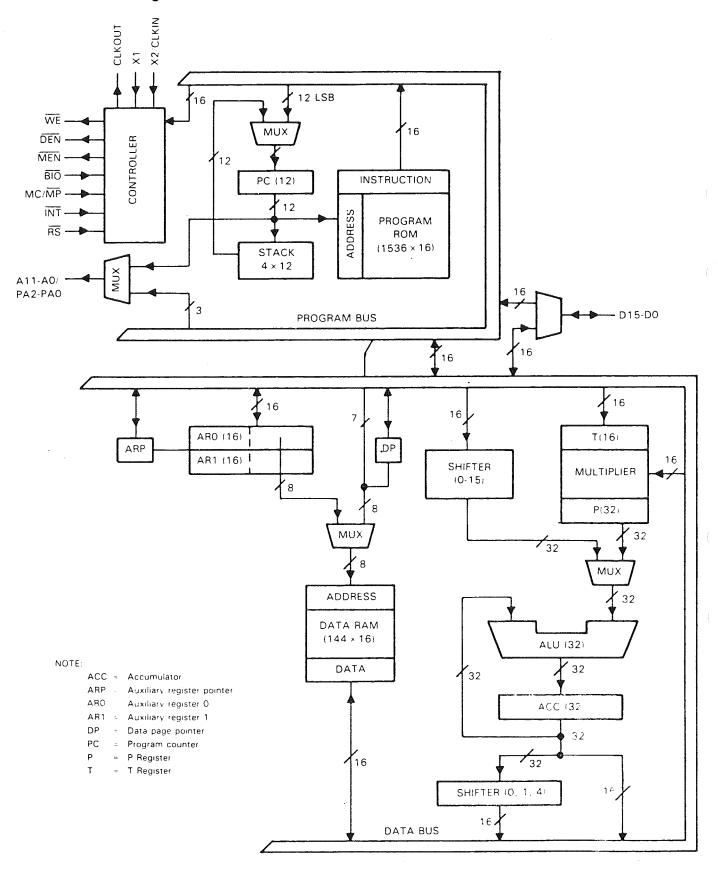

# The Harvard Architecture

A block diagram over the TMS 320M10 is shown in figure 3.5.

The TMS 320 has a modified Harvard architecture. In a Harvard Architecture the data (RAM) and program memory (RAM or ROM) are separated to make concurrency between instruction fetch and instruction execution possible. When the processor fetches an instruction from program memory, it can fetch the data that it needs from data memory at the same time since each bus operates independently. This of course increases the speed.

The TMS modification allows for transfering of data between program and data memory. An almost necessary modification since the data memory is only 144 double-bytes long. As an example data tables longer than 144 words can reside within program space so that the designer can make tradeoffs between the amount of table space and program space needed for a specific application. This can be used e.g. when storing the filter coefficients for a digital filter. It takes three instruction cycles to execute each of these transfers of 16 bit data. Future TMS chip will probably have a larger amount of on-chip data-RAM as finer (e.g. 1-micron) technology becomes available.

With some extra hardware, the IN and OUT instructions can be used to read and write from an external RAM storage addressed as a peripherel. The price will of course be larger execution times since 'in' and 'out' takes at least two cycles to execute, more if slower memory have to be used. Except for the transfer-instructions, TBLR and TBLW, all instructions operate on the data memory.

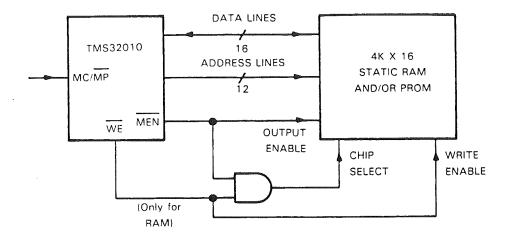

Program memory can lie both on-chip (in a 1536 \* 16-bit ROM) and off-chip. The TMS 32010 processor has no program ROM on chip. The ROM version, called TMS 32010M is used for large series (say more than 1000 ex) signal processors for the same application Since the program counter is 12 bits wide the maximum amount of program memory that can be addressed is 4096 \* 16-bit words. Fast memories with access times of under 100 ns are required if instructions in off-chip memories should be executed at full speed. Figure 3.6 shows how off-chip memory is addressed.

EXTERNAL PROGRAM MEMORY EXPANSION EXAMPLE

Fig 3.6

The data memory consists of 144 \* 16 bit RAM divided into two pages. Page 0 contains 128 double-bytes, page 1 contains 16 double-bytes. The reason for this unusual arrangement is probably that there was some space over on the chip after the preliminary layout. This is modified in the new TMS 32020 processor

## Multiplier, ALU, Accumulator and Shifters

All arithmetic operations are performed in fixed-point two's complement arithmetic. Different kinds of arithmetic formats are discussed in the next section.

The 16 \* 16-bit multiplier consists of: the T register (16 bit) which holds one of the factors, the P register (32 bit) that stores the product and the multiplier.

In order to use the multiplier the T-register must first be loaded with one of the operands. Then a MPY or a MPYK instruction is executed. The second factor is taken either from data memory (direct or indirect addressing) or defined by the instruction (immediate addressing). The product is in the third instruction cycle either added to or subtracted from the accumulator where from it can be loaded to data memory.

In this way a single multiplication takes 4 cycles = 800 ns. However when

several consecutive multiplication-add operations are to performed, e.g. when calculating scalar products, the operations can be pipelined in such a way that the overall multiplication-add time will be 400 ns. The architecture could be said to be optimized for calculations of scalar products which breaks down to the calculation of

$$ACC := ACC + X1 * X2$$

In TMS instructions this will become

LT X1 MPY X2 APAC

There is also a multiply immediate instruction which multiplies with 13-bit constants. For example:

LT X1 MPYK 5192 APAC

will accomplish the multiplication

The pipelining of multiplications in scalar products works as follows:

| ZAC<br>LT  | X1         | CLEAR ACCUMULATOR    |

|------------|------------|----------------------|

| MPY        | Y1         | FIRST MULTIPLICATION |

| LTA        | X2         | SECOND - " -         |

| MPY<br>LTA | Y2<br>X3   | SECOND - " -         |

| MPY        | <b>ү</b> З | THIRD - " -          |

|            |            |                      |

| •          |            |                      |

| APAC       |            | STORE THE RESULT     |

The LTA instruction will load the T register and add the product register to the accumulator. In this way a scalar product of two vectors of length N can be accomplished in 2(N+1) instructions, (each taking 200 ns).

The ALU is 32 bit arithmetic logical unit which can do the operations add, subtract, abs, and, or and xor. The first operand is always the accumulator the second operand is fetched from data memory (16 bits possibly left shifted 0-15 bit, the rest are zerofilled) or from the product register.

Note that the logical operations and or and xor only operates on the rightmost 16 bits of the accumulator. This is of course an annoying drawback when operations on the full 32 bits are wanted. The only possible solution is then to do these operations in several steps and store intermediate results in data memory. This will be rather time consuming. The TMS 32020 has a more flexible ALU

The ALU can be put in overflow mode under program control. If an overflow occurs when set in this mode, the most positive or negative representable value of the ALU will be loaded to the accumulator. This models the saturation processes inherent in analog systems and increases the chance of getting useful results even if an overflow have occured. Note though that the multiplication of -1 \* -1 will yield the answer -1 even in overflow mode! The overflow flag is not affected. This is a documented error which is corrected in the new TMS 32020 processor. Better would in this case be to load the accumulator with the largest representable positive number and set the overflow flag.

The accumulator has a 32 bit word length. Instructions exist for storing the high or low-order bits in data memory with shift (SACH and SACL). However only 0,1 or 4 bit left shift have been implemented and this only on the high order part. SACL has no shift facility at all. This is changed in the new processor to enhance the flexibility. The shifting facility is needed in the scaling operations.

There are two shifters available. Both are 16 bit and can only do left shifts. A right shift by n can however be implemented by loading the accumulator with the operand shifted 32-n bits and storing the high order part. This takes 2 clock cycles.

#### Registers

These consist of two 16 bit auxiliary registers (ARO, AR1) one auxiliary register pointer (ARP) and the data memory pointer (DP).

The auxiliary registers are used for indirect addressing in data memory and loop control. Indirect addressing uses the least significant bits of the auxiliary registers. There is only one operations that can be used for loop control, BANZ, branch on accumulator not zero.

#### Stack

The stack is four levels deep and 12 bits wide. It can be used to store return addresses when using nested subroutines.

#### <u>Status Register</u>

The status register consist of five status bits containing information of the processor state.

OV - overflow has occurred

OVM - overflow mode is on

INTM - interrupt is enabled

ARP - current auxiliary pointer is AR1

DP - current data page is 1

The status register can be saved and reloaded by the SST and LST instructions.

#### Input/output

There are 8 parallel input ports and 8 parallel output ports on the TMS 32010 all 16 bits wide. Data is transferred to and from the data memory by the strobes DEN (data enable) and WE (write enable).

#### Technology

The TMS 32010 is made in a VLSI 2.7-micron NMOS technology. The next generation will probably be made in even finer technology making a larger number of on-chip registers and data memory possible.

# 3.4 The system development tools

To help the engineer in the design of the hardware and software TI have some development facilities:

- □ An assembler

- □ A linker

- A simulator.

- $\square$  An evaluation module (EVM) with emulation support.

- $\square$  An analog interface board (AIB) that is used with the EVM.

The assembler, linker and simulator reside on a host computer, VAX 11/780 or IBM PC. There is also an assembler on the EVM-board.

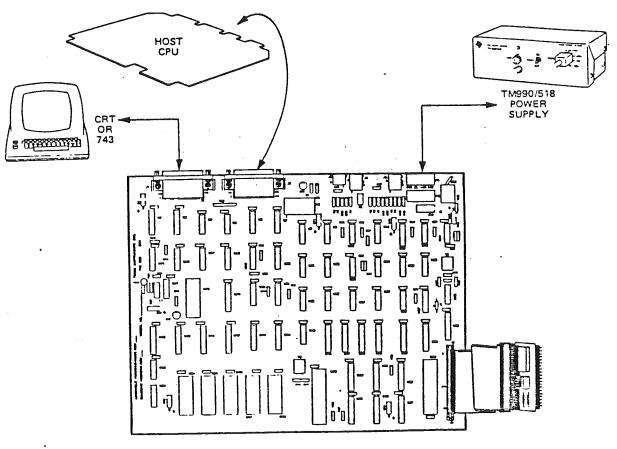

See also figure 3.7.

......

TMS program code transfer EVM- hit & VAX soft appeal : 7115 520;

& Roylsson

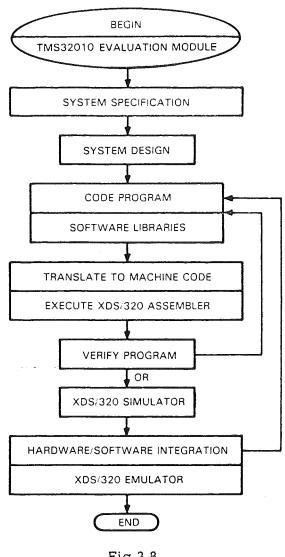

The design of a complete system could go as follows, see figure 3.8

Fig 3.8

#### System specification/design. 1)

The function of the system must be exactly defined and generally how the system will be implemented. It is probably advisable to do extensive simulations of the system with different solutions if the problem is complicated. In this stage a preliminary algorithm flow chart and hardware block scheme should be drawn. Based on the requirements and functionality an implementation approach is chosen. This will include the selection of processor and other hardware together with how software will be developed (e.g. programming language). In the design of signal processing systems the designer is unfortunately forced to

write in assembly language since there is no alternative available today. The use of an code generator, described in section 5, can however fasten up the process.

#### 2) Hardware/software design.

Here the design engineer choose an implementation of the parts left out under point 1. A detailed schematics over the hardware together with a high level pseudo language description of the software is made.

## 3) Software coding/Hardware fabrication.

Due to the lack of suitable languages with compilers for signal processing one is often forced to produce the assembly code for the processor by one self. The code can be generated either 'by hand' which is the most used way, or by a code generator. (If a high-level language compiler is available the code generator will be part of the compiler.) The advantages of this and an example of a simple code generator is described in section 5. The output in this stage will be assembly language which is then inputted to an assembler which produces machine code. This has been done with the problem of fast recursive parameter estimation as an example. This is also found in section 5.

### 4) Software/Hardware test.

Before the final implementation of the system it is necessary to test the software in the real environment. The design up to this point has only been based on a, more or less accurate, model of the real world and it must be checked that not too much information has been lost in this process. This can be a time consuming part of the design process. A normally good tip is that the software and hardware first should be tested out separately if possible. For the TMS 320 there is a simulator available which make it possible to test the assembly program extensively before going to point 5.

#### 5) Final implementation.

In the last step the hardware and software that now has been tested and verified are integrated into the application environment.

The following is a demonstration of how the software programs is run on a VAX 11/780 at the Department of Automatic Control, Lunds Institute of Technology.

#### The Assembler

For an extensive description see [20]. The files concerning the assemblation are collected in

[BOB. IMPORT. ASM3]

#### They are

README. DAT - Installation and verification guide

XASM.COM - Executes the assembler

LINKASM.COM- Re-links the assembler

PARSE.C25 - Parses pathnames for VAX 2.5 O.S.

PARSE.COM - Used by the above procedures to parse

pathnames for 3.0 0.5.

ASM320.EXE - Executable code for the assembler.

ASM.OBJ - Assembler objet code, used in re-linking

RUNTIME - Source/ object library

TEST. ASM - Source for the assembler test program

TEST.LIS - Correct listing for the test program

TEST. MPO - Correct object for the test program

The \*.com files contains information that has to be changed if the files are copied to another directory. E.g. the command

#### \$ @[BOB.IMPORT.XASM]PARSE

in XASM.COM should be changed to the new directory-name. If one puts

xasm == "@[BOB.IMPORT.ASM]XASM"

in the login-file the assembler can be started with the command

XASM FILENAME

FILENAME.ASM should then contain the assembler program in VMS-format. The

file should start with the line:

IDT 'FILENAME'

and end with

END

It is important that capital letters is used in FILENAME.ASM.

The assembler will produce two output files:

FILENAME.LIS - information about errors during assemblatic

FILENAME. MPO - relocatable module. Is used by the linker.

A four pages long assembly program takes only a few seconds to assemble.

#### The Linker

For an extensive description of the linker see [20].

The files concerning the linking are collected in

[BOB. IMPORT, LINKER]

They are

README.DAT - Installation and verification guide

LINKER.COM - Executes the linker

LINKLINK.COM - Re-links the assembler

PARSE.C25 - Parses patnames for VAX 2.5 O.S.

PARSE.COM - Used by the above procedures to parse

pathnames for 3.0 0.5.

LINKER.EXE - Executable code for the assembler.

LINKER.OBJ - Assembler objet code, used in re-linking

LINKRTS.OLB- Source/ object library

TEST1.ASM - Source for the assembler test program

TEST2. ASM - Source for the second test program

TEST1.LIS - Correct listing for the test program

TEST2.LIS - Correct listing for the test program

TEST.CON - Control file for the test

TEST. MAP - Correct map file

TEST.LOD - Correct load module

The \*.com files contains information that has to be changed if the files are copied to another directory. E.g. the command

\$ @[BOB.IMPORT.LINKER]PARSE

in LINKER.COM should be changed to the new directory-name. If one puts

xlink == "@[BOB.IMPORT.LINKER]XLINK"

in the login-file the assembler can be started with the command

XLINK FILENAME

The linker takes relocatable units and links them together to an object file. To execute the linker one has to write a command file, see [19]. It could look like (capital letters):

[BOB. EXJOBB. TMS]FILENAME. CON:

TASK KOD

PROGRAM >0000

DATA >0000

INCLUDE [BOB.EXJOBB.TMS]FILENAME

END

The linker produces two output files:

FILENAME. MAP - contains the errors during linking FILENAME. LOD - object code

The object code can then be used as input to the simulator.

The linking takes less than ten seconds.

The Simulator.

The simulator is a software program that is available for VAX and IBM-PC. It can, off-line, simulate the behaviour of a real TMS 320 and is a very useful tool when testing out the software. A thorough description of the simulator can be found in [19].

To start the simulator write

RUN [BOB.IMPORT.SIM]SIM.EXE

(Or, better, you can define this as XSIM in your login-file).

On the prompt 0/1 ? answer 0 (return) and then strike return again. You will get a list of all the commands available. The list is slightly hierarchical, for example you can get all the I/O commands by writing IOH.

The TMS assembly program to be tested should now have been written with the host computer editor. It is loaded into the (artificial) TMS memory by the command:

L [DIRECTORY\_NAME] FILENAME.MAP

Note that capital letters <u>must</u> be used everywhere (slightly irritating). Now suitable breakpoints can be set. Investigate this by writing:

вн

This will list all the commands for setting and resetting different kinds of breakpoints. For a thorough description see [19]. To start the simulation write

R

A simulation can be halted with Ctrl-c at any time. It is also possible to single step by writing

SS

To display the current status of the processor write

This will display all registers, the current instruction and the number of clock pulses since the last reset.

To look at the data or program memory write

MH

which will display all the commands available for doing this. Input and output files can be 'connected' to the simulator. Write IOH to learn more about this. The input data should be in TMS arithmetic format, e.g. 7FFF is the largest representable positive number. More about the arithmetic format can be found in section 4.

To save your commands in a journal file write

JF

[DIRECTORY\_NAME]JOURNAL\_FILE

To execute the commands in such a file write

ΕX

[DIRECTORY\_NAME]JOURNAL\_FILE .

Finally to stop the simulation write

Q

#### The Evaluation Module

The Evaluation Module (EVM) enables a user to test if the TMS 320 meets the speed requirements of the application. A firmware package contains a debug monitor, editor, assembler, reverse assembler, EPROM programmer, communication software to talk to two EIA ports and an audio cassette interface. Either source code or object code can be downloaded into the EVM via the EIA ports provided on the board. These supports baud rates of 110-19200 baud. There was however some problems when using baud rates of over 600 baud when dumping an assembly program from the mass storage. The

board contains a Debug Monitor including over 60 commands with 8 breakpoints, single step and software trace.

The board can be configured either as a stand alone unit with just a cassette recorder or with a host CPU as mass storage, see figure 3.9.

Fig 3.9

If a host computer is used there is of course no reason for using the on board editor or assembler.

For more information about the Evaluation Module, see [21].

### The Analog Interface Board

The analog interface board has A/D and D/A converter (12 bit) together with an anti-aliasing lowpass filter. It is compatible with the evaluation module. The maximum sampling rate is limited by the A/D converter to 20,000 Hz.

The TMS 320 has like most other signal processors fixed point arithmetics. No true floating point signal processor is yet available, although for example the Hitachi's HD 61810 has floating point support for a number representation with a 16 bit mantissa and 4 bit exponent. Floating point support normally only means that instructions are available for implementing floating point operations. The new TMS 32020 processor have e.g. floating point support in the form of instructions for normalization of the mantissa and calculation of computed shifts. (Shift the accumulator x bits where x is stored in a register or data memory.)

## 4.1 Floating Point Software Routines

An example of how floating point operations can be implemented on the TMS 32010 is given in appendix 1 in the form of some floating point macros. The lack of proper instructions for shift of the accumulator and normalizing of the mantissa makes this approach slow. Floating point multiplication will be about 100 times slower than fixed point multiplication. This is probably not acceptable. Another drawback with those routines is that IEEE standard for floating point representation on microprocessors is not used.

Software floating point procedures for the TMS 320 are further discussed in [7], where it is suggested that additional hardware should be cludged to the processor to speed up the normalization of the mantissa. The 7.8 microsec. multiply and 18.4 microsec. addition time mentioned there could be compared to the 24 and 25 microsec. of the 8086/8087 co-processor arrangement. IEEE standard is used. This is not a very attractive alternative either.

The lack of floating point operations is a major problem with signal processors. This problem can sometimes be avoided by choosing the algorithm in such a way that all data can be represented in the same way internally. The TMS 320 makes implicit use of the left point two's complement format which means that all 16 bit numbers represent real numbers in the interval [-1,1). The 16 bit of the TMS is used as one sign bit and a 15 bit mantissa. Therefore all numbers between -1 and 1 should be multiplied by a factor 2<sup>15</sup> and rounded

to the nearest integer before conversion to internal binary form.

A program for conversion between 16 bit left point two's complement format and real numbers is shown in appendix 3.

#### 4.2 Scaling Factors

Due to the fixed point number format it is up to the programmer to interpret the 16/32 bit data correctly. The binary pattern 0100.0000.0000.0000 might stand for the real number 0.5 as well as  $0.5*2^8$  if a scaling factor of  $2^8$  is assumed for that number. The most practical would be to use the same scaling factor for all data. If a larger dynamical range is needed one must however use different scaling factors for different data. Another way to interpret fixed point format with scaling factors is that only mantissas are stored and the exponents are fixed for each data. Since they are not stored they must be remembered by the programmer. A way to handle this automatically is to use the automatic code generator proposed in section 5. The scaling factors for each data can then be supplied by the user and the correct code can be generated automatically using correct scaling factors for each data.

The problem of choosing appropriate scaling factors is often 'solved' by guessing or in the best case by performing simulations of the algorithm in 'typical situations' on a floating point processor. Procedures for simulating calculations in fixed point format can easily be written in Pascal e.g. by representing fixed point numbers by records:

Another possibility is to use the 'chop(x)' instruction in the program package CNTLC, see [9].

The scaling factors are most often chosen as exponents of 2 since conversion

between different scaling factors then corresponds to simple binary shifting of data.

The performance of the algorithm can be very dependent on the scaling factors. If a to small factor is used i.e. the data x is represented internally by  $x*2^n$  where n is smaller than required there will be loss of accuracy since the data are shifted out to the right. This loss of accuracy will build up during the computations and can eventually result in erroneous results.

On the other hand if the scaling factor is chosen to large there is an increased risk of overflow occurring i.e. the data are shifted out to the left. This is even worse since it is in this case the most significant bits that are lost. If one uses the TMS 320 the errors can be made smaller setting the processor in the saturation mode described in section 3.

Choosing appropriate scaling factors is a problem with fixed point arithmetics and this is why changeable scaling factors, i.e. floating point numbers, where invented.

When finally the suitable scaling factors have been chosen there must be ways of operating on pairs of data with different scaling factors. E.g. there should be instructions for addition, subtraction, multiplication and division of data represented in different forms. For instance when two numbers with different scaling factors should be added one of them must be shifted before performing the addition. Such instructions is not directly available in the TMS 320 but can be implemented in the automatic code generator as macro's. Such macros ADDSC (add scaled numbers) and MULSC (multiply scaled numbers) are shown below.

Here again the advantages with automatic code generation are appreciated. The scaling procedure when writing assembly code 'by hand' is a great burden on the programmer. Taking care of a number of different ways to represent data and an even greater way of combining different data with different representations is quite troublesome. This is easily taken care of by the automatic code generator.

Remember though that the problem only arises when different scaling factors must be used for different data. In e.g. applications with digital filters, (which is the normal use for this processor), this can usually be avoided by

scaling the filter coefficients by the same factor. (E.g. the largest coefficient or the sum of the absolute values of the coefficients, the later is called worst case scaling).

#### Macros for different scaling factors

#### ADDSC (A,B,C,EA,EB,EC)

$$C := 2^{-EC}(A*2^{EA} + B*2^{EB})$$

Adds two 16-bit numbers A and B stored in data ram with, possibly different, scaling factors EA and EB. The sum, C, is stored in data ram with a third scaling factor. WARNING: The overflow flag is not set if an overflow occurs.

Ex. ADDSC(A,B,C,-15,-14,-15) where A=4000H and B=1000H (hexa decimal numbers) yield the answer C=6000H. This corresponds to the fact that  $4000H*2^{-15} + 1000H*2^{-14} = 6000H*2^{-15}$ . That is 0.5 + 0.25 = 0.75

Since overflow and underflow has to be avoided in the intermediate steps the procedure has been divided into three cases. Case 2 requires that a macro for shifting a double word left and storing the upper 16 bits in data RAM has been written. (The SACH instructions normally only works with shifts of 0,1 and 4.)

1) EA ≤ EB ≤ EC

LAC (A,EA-EC+16) ADD (B,EB-EC+16) SACH (C)

2) EA ≤ EC ≤ EB

LAC (A,EA-EB+16)

ADDH (B)

SACHE(C,EB-EC)

#### 3) EC ≤ EA ≤ EB

LAC (A,EA-EC)

ADD (B,EB-EC)

SACL (C)

#### MULSC (A,B,C,EA,EB,EC)

$$C := 2^{-EC}(A*2^{EA} * B*2^{EB})$$

Multiplies two numbers A,B in data RAM with possibly different scaling factors and stores the product in data memory C. The procedure is divided into two cases. Case 1 requires the extended SACH macro. Case 2 requires that a macro for shifting the accumulator left and storing the lower 16 bits has been written.

1)

$$-16 \le EA + EB - EC \le 0$$

LT (A)

MPY (B)

PAC

SACHE (C,EA+EB-EC+16)

2)

$$0 \le EA + EB - EC < 16$$

LT (A)

MPY (B)

PAC

SACLE(C, EA+EB-EC)

#### Summary of 4.2

It is not advisable to try to implement floating point routines on the TMS 32010. Better is to store only the mantissa and attach each data a constant exponent called scaling factor. The choice of scaling factor is important.

#### Remark

Another possible solution is to only store an exponent and have no mantissa. The exponent can be fractional not to give to large quantization steps. This is described in the next section, and is there called the FOCUS number system.

#### 4.3 FOCUS Number System

FOCUS is a number system especially useful for computer control and signal processing applications on processors which lack a hardware multiplier / divider. It is based on a representation of numbers without any mantissa and with fractional exponent. In this number system multiplication and division becomes very fast. Addition and subtraction can be performed using a one-dimensional lookup table, see [15], [16] and [18].

The name FOCUS was chosen to emphasize that this representation concentrate available states near zero as an analogy to how the human eye concentrates near 'a center of focus'. This is however true also for a normal floating point system.

The choice of number representation in computer systems have been extensively debated, see [27]. The rich variety of different systems existing today proves the nonexistense of a universally superior solution. When implementing floating point numbers on a fixed point processor one can choose the number representation oneself. The IEEE standard format for 32 bit floating point numbers is

Where S is a sign bit, the E:s eight exponent bits and the M:s 23 mantissa bits.

When choosing number representation for a digital control system or a signal processing system one must remember that many systems should have the possibility to represent both large and small numbers with high accuracy. The choice of number representation one makes will be a trade-off between a large number range and high accuracy i.e. possibility to represent numbers separated with small steps. The instruction set of the processor might also

influence the choice. The TMS 320 has possibilities to handle 16 bit quantities only and it is advisable to store the exponent and mantissa separately:

The roundoff error introduced through the finite number length can be modelled by random noise. The FOCUS system has a constant quotient between two neighbouring representable numbers. This gives a logarithmically uniform distribution of representable numbers. The quantization noise introduced thereby is in some cases smaller than with a 'normal' number representation. This is true under some conditions of the probability distribution on the data to be quantizised, as we shall see in a later section.

#### The FOCUS representation

FOCUS is a logarithmic coding system in which no mantissa is given. This separates it from usual floating point systems. The numbers are represented with one sign bit and an offset binary for the integer part of the exponent.

$\underline{\text{Ex.}}$  A system with 8 bits is used and one decides upon using 3 fractional bits.

[S]

$$\begin{bmatrix} E & E & E \end{bmatrix}$$

.  $\begin{bmatrix} F & F & F \end{bmatrix}$  sign exponent fraction

If an offset of 1000 for the integer part of the exponent is used one will have:

1000 = 0

1001 = 1

1010 = 2

1011 = 3

1100 = 4

1101 = 5

1110 = 6

1111 = 7

0111 = -1

0110 = -2

0101 = -3

0100 = -4

0011 = -5

0010 = -6

0001 = -7

The smallest representable number is thus