# IMPLEMENTATION OF A SELF-TUNING REGULATOR ON A MICROCOMPUTER

GEORGE KIZIROGLU

RE-182 June 1976

Department of Automatic Control

Lund Institute of Technology

## IMPLEMENTATION OF A SELF-TUNING REGULATOR ON A MICROCOMPUTER

ВΥ

GEORGE KIZIROGLU

Master Thesis in Automatic Control.

Department of Automatic Control,

Lund Institute of Technology,

Lund, Sweden

Supervisors: L Andersson

B Wittenmark

#### ABSTRACT

The main purpose with this master thesis is to show how a microcomputer, Intel 8080, is used to implement a special kind of adaptive regulators, called self-tuning regulators. The report presents some theory, software solution and some experiments.

The programmemory requirement is about 1.4KKBytes, and the datamemory needed is 0.5K Bytes.

The self-tuning regulator have been implemented on different processes simulated by a analog computer.

#### SAMMANFATTNING

Ändamålet med detta examensarbete, är att visa hur en mikrodator, Intel 8080, används för att implementera vissa typer av adaptiva regulatorer, s.k. självinställande regulatorer.

I rapporten framförs en del teori, mjukvarulösningen, och en del gjorda experiment.

Programminnesuttrymmet är ungefär 1.4K Bytes och dataminnesbehovet är 0.5K Bytes.

Självinställande regulatorn har implementerats på olika processer som har simulerats på en analogimaskin.

#### CONTENTS

| 1. | INTRODUCTION                                 | Ŀ   |

|----|----------------------------------------------|-----|

| 2. | SELF-TUNING REGULATORS                       | Ę   |

|    | 2.1 The Basic Algorithm                      | 5   |

|    | 2.2 Selection of Parameters in the Algorithm | 8   |

| 3. | SHORT DESCRIPTION OF INTEL 8080 ASSEMBLER    | 11  |

| 4. | SOFTWARE SOLUTION                            | 15  |

|    | 4.1 System Solution                          | 15  |

|    | 4.2 Programstructure                         | 17  |

|    | 4.2.1 Sture in Algol                         | 18  |

|    | 4.2.2 The low-level subroutines              | 2.5 |

|    | 4.3 Datastructure                            | 31  |

| 5. | A HARDWARE SUMMARY                           | 36  |

| 6. | MANUAL FOR STURE                             | 40  |

| 7. | EXPERIMENTS                                  | 42  |

| 8. | REFERENCES                                   | 5 5 |

|    | APPENDIX A                                   | 56  |

|    | APPENDTY B                                   | 57  |

#### 1. INTRODUCTION

computer.

Τά καλά τοῖς κό¶οις κτῶντε Greek Proverb

The department of Automatic Control at Lund Institute of Technology have for many years done researches on Adaptive controllers. Extensive research have been done on the theory and application of self-tuning regulators {4}. Self-tuning regulators have been applied on different kind of industrial processes, paper-machines, ore crushers, autopilot for tankers using minicomputers.

The microcomputers have now been developed so much, that it would be interesting to implement a self-tuning regulator on a microcomputer.

In Chapter 2 is given a theoretical background for the further discussions in this report. Chapter 3 describes the assembly language of Intel 8080. A description of the programand datastructure is given in Chapter 4.

In this master thesis also some hardware was developed. A cooperation was done with P-O Sjöberg for the construction of the microcomputer system, in which the self-tuning regulator was implemented. A short description is given in chapter 5. Chapter 6 describes, the way the user have to do for test the regulator on different processes. Chapter 7 describes some results of the implementation of the regulator on some processes, simulated on the analog

Appendix A containes the Instruction Set for Intel 8080, and in Appendix B the whole program is given, which takes about 1.4 K Bytes and is programmed in PROM-memories.

#### 2. SELF-TUNING REGULATORS

I think, therefore I am.

RENE DESCARTES

#### 2.1 The Basic Algorithm

The self-tuning regulators are controllers which are used on processes with constant but unknown parameters.

The basic algorithm described in (4) is derived to control minimum phase single-input single-output systems. The algorithm can be divided into two parts. Firstly, the parameters in a prediction model of the process are estimated using the method of least squares. Secondly, the minimum variance regulator is computed, as if the values of the estimated parameters were the true ones. Thus it is not taken into consideration that the values of the estimated parameters are uncertain.

Consider the system

$$A(q^{-1})y(t) = B(q^{-1})u(t-k-1) + C(q^{-1})e(t)$$

(2.1) where e(t) is a sequence of independent N(0,0) random

variables and

$$A(q^{-1}) = 1 + a_1 q^{-1} + a_2 q^{-2} + \dots + a_n q^{-n}$$

$$B(q^{-1}) = b_1 + b_2 q^{-2} + \dots + b_n q^{-(n-1)}$$

$$C(q^{-1}) = 1 + c_1 q^{-1} + c_2 q^{-2} + \dots + c_n q^{-n}$$

The purpose of the control is to minimize the loss function

$$E\Sigma (y_r(t) - y(t))^2$$

(2.2)

where  $y_r(t)$  is a known time-varying reference value.

Introduce the reference input,  $u_r(t)$ , defined as

$$u_r(t) = \frac{A(q^{-1})}{B(q^{-1})} y_r(t+k)$$

Equation (2.1) can now be written as

$$A(q^{-1})(y(t)-y_r(t)) = B(q^{-1})(u(t-k-1)-u_r(t-k-1))+C(q^{-1})e(t)$$

The loss function (2.2) is minimized by the control strategy

$$u(t) - u_r(t) = -\frac{G(q^{-1})}{B(q^{-1})F(q^{-1})} (y(t) - y_r(t))$$

(2.3)

where F and G are polynamials given by the identity

$$C(q^{-1}) = A(q^{-1})F(q^{-1}) + q^{-k-1}G(q^{-1})$$

The control law (2.3) can now be written as

$$u(t) = -\frac{G(q^{-1})}{B(q^{-1})F(q^{-1})} y(t) + \frac{C(q^{-1})}{B(q^{-1})F(q^{-1})} y_r(t+k+1)$$

To compute the optimal control law it is thus necessary to know the reference value in at least k+l steps ahead.

Now introduce the prediction model of the process

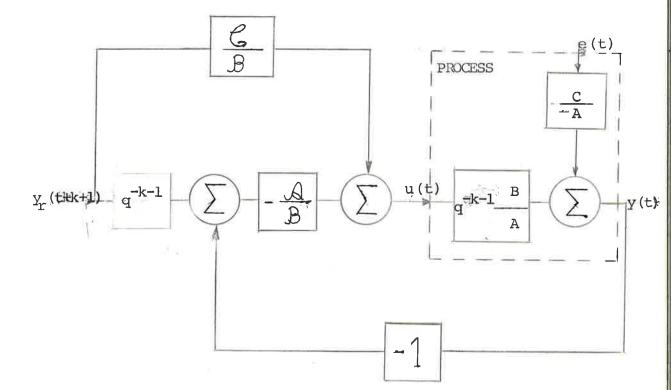

Figure 2.1  $y(t+k+1)-y_{r}(t+k+1)+\lambda(y(t)-y_{r}(t)) = \beta_{o} \times \beta u(t)+\beta y_{r}(t+k+1)+ +\epsilon(t+k+1)(2.4)$

The minimum variance control law, for considering this model will be

$$u(t) = (\mathcal{A}(y(t) - y_r(t))/\beta_0 - \mathcal{C}y_r(t+k+1)/\beta_0)/\mathcal{B}$$

(2.5)

The structure of the process and the controller is shown in Figure 2.1. Notice that the block represents a feedforward regulator and the block a feedback regulator.

#### Introduce

$$VS(t+k+1) = y_{r}(t+k+1)/\beta_{0}$$

$$YS(t) = (y(t)-y_{r}(t))/\beta_{0} = y(t)/\beta_{0} - VS(t)$$

We can rewrite (2.4) and (2.5) as follows:

$$YS(t) + AYS(t-k-1) = Bu(t-k-1) + CVS(t) + \epsilon(t+k+1)$$

$u(t) = (AYS(t) - CVS(t+k+1))/B$

#### 2.2 Selection of Parameters in the Algorithm

The basic self-tuning regulator is specified by the following parameters:

- a) Sampling time, T

- b) Scale factor in the regulator,  $\beta$

- c) Exponential forgetting factor,  $\lambda$

- d) Number of pure time-delays in the model, k

- e) Allowed maximum value of the control signal, ULIM

- f) Number of regulator parameters, NA, NB, NC

- g) Initial values for the least squares estimator

A: thorough discussion is given in { 4 }.

- a) Some aspects that must be considered when determining the sample intervall are follows:

- . The dynamics of the process

- . The dead time in the process

- . The complexity of the regulator

- . The computation times

- b) If the sign of the scale factor is assumed known its value is not crucial for the convergence if the control signal is limited. The transient behaviour seems to be best if  $\beta_0$  and  $b_1$  are of the same magnitude. The number of times the control signal hits the limit can be used to determine if a good value of  $\beta_0$  has been used. If  $\beta_0$  is too small, then the control signal use to reach the limit more often, than if too large a  $\beta_0$  is used. Too large a  $\beta_0$  will on the other hand give very small input signals in the beginning. Further the  $\alpha_1$  parameters use to be large if  $\beta_0$  is too large.

- c) The forgetting factor is used to determine how many old values should be remembered. About 200 old values are remembered for  $\lambda = 0.99$ , while only 40 are remembered for  $\lambda = 0.95$ . A rule of thumb to determine how many values that are remembered, n, is given by  $n = 2/(1-\lambda)$ .

The parameter  $\lambda$  is best chosen by inspecting the variations in the parameter estimates. Too much fluctuations implies either that too many parameters are used in the regulator

or that a too small a value of  $\lambda$  is used.

If the parameter estimates are almost constant it is advisable to make a small decrease in the value of  $\lambda$  occasionally. This should be done in order to make sure that the estimates really have converged and not only are slowly changing.

- d) The number of pure time-delays in the model, k, is the most crucial parameter to choose. Too large a value of, k, can give an output variance which is larger than necessary. Sometimes it is also difficult to get the estimates to converge. Too small k can make very difficult to get good control and even make it impossible to stabilize the system.

- e) A limitation of the control signal has in many cases good influence on the transient behaviour of the selftuning regulators. This is the case if the initial estimates of the parameters are poor. The regulator might then send large signals into the process which can cause large errors initially. The control signal can thus be limited to get a smooth start-up. The limit can be small in the beginning and later increased when better parameter estimates are obtained. Another way is to have a fixed limit which should not be reached under normal control of the process. If the maximum value is feached often it is not possible for the regulator to converge to the minimum variance regulator.

- f) If NA or NB or NC is too large then it can be shown that the resulting controller is equivalent to the minimum variance regulator, but there might be a common factor in the regulator. No indication is given of how much the output variance is increased if the number of regulator parameters is decreased.

- g) Initial values of the parameters  $\alpha_{\tt i}$  and  $\beta_{\tt i}$  and the covariance matrix, P(t), must be given when starting up the least squares estimator.

If the parameters are unknown a standard choise can be

to put them equal to zero. In this case the covariance matrix shall be given a rather large value, say  $(10-100)\times I$ , where I is a unit matrix. A too small value on P(0) can, however, give rise to slow rate of convergence. In order to avoid this the exponential forgetting factor can be given a value somewhat less than one.

### 3. SHORT DESCRIPTION OF INTEL 8080 ASSEMBLER

Se non é vero, é bon trovato

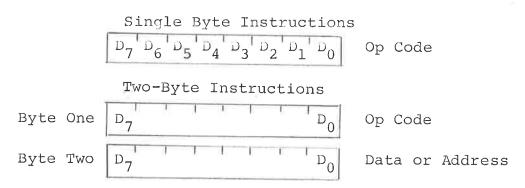

#### Instruction and Data Formats:

Memory for the Intel 8080 is organized into 8-bit quantities, called Bytes. Each Byte has a unique 16-bit binary address corresponding to its sequential position in memory. Data in the 8080 is stored in the form of 8-bit binary integers:

MSB= Most significant Bit

LSB= Least significant Bit

The 8080 program instructions may be one, two or three bytes in length. Multiple byte instructions must be stored in succesive memory locations; the address of the first byte is always used as the address of the instructions. The exact instruction format will depend on the particular operation to be executed.

Three-Byte Instructions

Byte One  $D_7$   $D_6$   $D_5$   $D_4$   $D_3$   $D_2$   $D_1$   $D_0$  Op Code

Byte Two  $D_7$   $D_0$  Data or Address

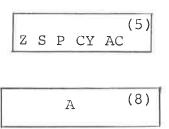

#### Registers:

The program-addressable registers in 8080 are:

Six general purpose registers addressed singly or in pairs

B,C, D,E, H,L

The 8-bit accumalator, also known as register, A.

The 16-bit stack point register, SP.

The 16-bit program counter register, PC.

One of the registers that are employed internally in the 8080 chip, but cannot be addressed from a computer program include

a 5-bit flag register (Z, S, P, CY, AC)

They are Zero, Sign, Parity, Carry and Auxiliary Carry.

| В | (8) | С       | (8)  |

|---|-----|---------|------|

| D | (8) | E       | (8)  |

| Н | (8) | L       | (8)  |

|   |     | POINTER | (16) |

|   |     | COUNTER | (16) |

A flag is "set" by forcing the bit to 1; "reset" by forcing the bit to 0. When an instruction affects a flag, it affects it in the following manner:

Zero: If the result of an instruction has the value 0, this flag is set; otherwise it is reset.

Sign: If the most significant bit of the result of the operation has the value 1, this flag is set; otherwise it is reset.

Parity: If the result has even parity, this flag is set; otherwise it is reset.

Carry: If the instruction resulted in a carry (from addition) or a borrow (from subtraction or comparison) out of the highorder bit this flag is set; otherwise it is reset.

#### Auxiliary

Carry: Used in connection with computing decimal numbers (is seldom used)

#### Instruction set:

The 8080 instruction set includes five different types of instructions:

<u>Data transfer group:</u> The 8080 has four different modes for addressing data stored in memory or in registers:

Direct- Bytes 2 and 3 of the instruction contain the exact memory address of the data item, e.g.

LDA addr (Load Accumulator direct)

Register- The instruction specifies the register or register-pair in which the data is located, e.g. MOV A,B  $\qquad$  (Move B to A)

#### Register

indirect- The register pair H,L contains the memory address where the data is located, e.g.

MOV A,M (The content of the memory location whose address is in registers H and L is moved to A)

Condition flags are not affected by any instruction in this group.

Immediate- The instruction contains the data itself.

Arithmetic group: All instructions in this group affect at least one of the five flags according to the standard

ADD B  $((A) \leftarrow (A) + (B))$

rules, e.g.

Logical Group: This group of instructions performs logical (Boolean) operations, AND, OR, EXCLUSIVE-OR, COMPARE, ROTATE or COMPLEMENT on data in registers or in memory. Besides the instructions CMC and STC, A register is involved in all instructions. At least one of the five flags are affected by all instructions, e.g.

ANA B  $((A) \leftarrow (A) \text{ AND } (B)$

Branch Group: The program counter register is involved in all instructions. Consider flags are not affected by any instruction.

Stack, I/O, and Machine Control Group: Except the instruction POP PSW, no other instruction affects the condition flags.

The execution time of all the instructions is varying from 4 (e.g. ADD B ) up to 18 states (XTHL). For a detailed description of the instruction set of the Intel 8080, see Appendix.

#### 4. SOFTWARE SOLUTION

Slow and steady wins the race. DAVID LLOYD, FABLES

#### 4.1 System Solution

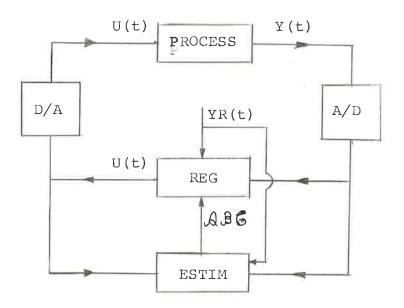

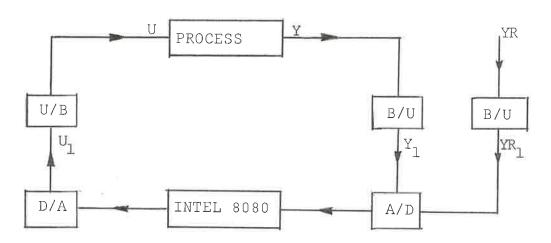

The structure of the system is given in the following figure.

At each sample the microcomputer reads following values from the  $\mbox{A/D}$  - converter:

The output signal of the process, Y

The reference signal of Y, YR

and outputs the control signal to the process via an D/A - converter.Normally the self-tuning regulator, STURE, is divided into two parts.

In the first part the parameters of the process are estimated by the estimator subroutine, ESTIM. The algorithm is based on the model

$Y(t+k+1)-YR(t+k+1)+AE(1)\times(Y(t)-YR(t))+...+AE(NA)\times(Y(t-NA+1))$ - $YR(t-NA+1))=B0\times(U(t)+BE(1)\times U(t-1)+...+BE(NB)\times U(t-NB)+$ + $CE(1)\times YR(t+k+1)+...+CE(NC)\times YR(t+k-NC+2)+E(t+k+1)$  In the second part the regulator subroutine, REG, computes the control signal to be applied at time, t, to the process from

$$\begin{split} & \text{U(t)} = (\text{AE(1)} \times (\text{Y(t)} - \text{YR(t)}) + \ldots + \text{AE(NA)} \times (\text{Y(t-NA+1)} - \text{YR(t-NA+1)})) / \text{BØ} \\ & - \text{BE(1)} \times \text{U(t-1)} - \ldots - \text{BE(NB)} \times \text{U(t-NB)} - (\text{CE(1)} \times \text{YR(t+k+1)} + \ldots \\ & \ldots + \text{CE(NC)} \times \text{YR(t-NC+k+2)}) / \text{BO} \end{split}$$

AE(I), BE(I), CE(I) are the least squares estimates from the subroutine, ESTIM.

Assuming that the parameters changes slowly between the samples, this kind of scheduling is uneffective, because it takes long time until U(t) can be computed. Instead, we can divide the subroutine REG into REG1 and REG2. In REG1 is U(t) computed by the formula:

$U(t) = AE(1) \times (Y(t) - YR(t)) / B0 - CE(1) \times YR(t+k+1) / B0 + Fscal(t-1)$

where AE(1) and CE(1) are the estimated parameters from the sampleinterval, t-1, and Y(t), YR(t), YR(t+k+1) are the input values at time t.

At the rest of the sampleinterval ,t, the new parameters are estimated and on the base of these Fscal(t) is computed by

Fscal(t)=AE(2)(×(Y(t)-YR(t))+..+AE(NA)×(Y(t-NA+2) - YR(t-NA+2))/B0 - BE(1) $\pi$ U(t) - ...-BE(NB)×U(t-NB) - (CE(2)×YR(t+k+1)+...+CE(NC)×YR(t-NC+k+3)/B0

#### 4.2 Programstructure

The mainprogram, STURE, is divided into the following subroutines:

The high-level subroutines: INIT, ADIN, DAOUT, FMOVE,

FLIM, SCAPR, REG1, ESTIM,

REG2

The low-level subroutines: FMUL, FADD, FDIV, LOAD,

STORE, BINF, FBIN, FMAGN

NEGDE, OUFLW, OFLW, UFLW, UFLWE

The low-level subroutines are explained in 4.2.2. Using the mainprogram and the high-level subroutines the whole program can be written in Algol.

#### 4.2.1 STURE in Algol

Begin Integer k;

Real YR, Y, B0;

Array VS(1:14), YS(1:14);

Procedure ADIN, REG1, ESTIM, REG2;

Comment

The vectors YS,U,VS,T and the variables NA,NB,

NC,k appears in the procedures REG1,ESTIM, and

REG2 and they have following meaning:

YS- vector of scaled process outputs of dimension NA+k+2. YS is organized as follows.

YS(1) = (Y(t) - YR(t))/B0 = Y(t)/B0 - VS(t)

YS(2) = (Y(t-1) - YR(t-1))/B0 = Y(t-1)/B0 - VS(t-1)

\* \*

. . .

U- vector of process inputs of dimension NB+k+2. U is organized as follows.

U(1) = U(t-1)

U(2) = U(t-2)

VS-scaled vector of reference signal of dimension NC+k+2. VS is organized as follows.

VS(1) = YR(t+k+1)/B0

VS(2) = YR(t+k)/B0

VS(k+2) = YR(t)/B0

....

. .

T--vector of estimated parameters of dimension NA+NB+NC and organized as follows.

T(1) = AE(1)

T(2) = AE(2)

• •

```

T(NA) = AE(NA)

T(NA+1) = BE(1)

T(NA+NB) = BE(NB)

T(NA+NB+1)=CE(1)

T(NA+NB+NC)=CE(NC)

NA- number of A- parameters in (4.1)

NB- number of B- parameters in (4.1)

NC- number of C-parameters in (4.1)

k- number of pure time delays in the process.

Dimension restrictions

MAX(NA+NB+NC)=9

MAX(NA+k+2)=14

MAX(NB+k+2)=14

MAX(NC+k+2)=14

End of comments;

INIT;

STURE: YR:=ADIN(0);

Y := ADIN(1);

VS(1):=YR/B0;

YS(1) := Y/B0 - VS(k+2);

REG1;

ESTIM;

REG2;

GO TO STURE

```

END

#### Procedure INIT; Begin comment This procedure initialize STURE; Real FSCAL, 1/B0, 1/RL, ULIM, A; Integer NA, NB, NC, k, I, J; Read (1/B0); Read (1/RL); Read (ULIM); Read (NA); Read (NB); Read (NC); Read (k); Read (A); Fscal:= 0; I:=1 step 1 until For 14 do YS(I) := U(I) := VS(I) := 0; For I:=1 step 1 until I'(I) := S(I) := FI(I) := 0; Begin For J:=1 step 1 until 9 do P(I,J):=0; P(I,I) := A;

End

End;

Real Procedure ADIN (I);

Integer I;

Begin comment

Entry: I=channel number

This procedure converts an input value from channel I to a normalised floating-point number with the exponent in Excess-64 form and the mantissa in two-complement representation;

Real Procedure BINF;

Begin ADIN:=BINF

End

End;

```

Real Procedure DAOUT (I,U);

Integer I;

Real U;

Begin

comment

Entry:

I = channel number

U = the control signal

This procedure converts the limited controlsignal

from a normalised floating-point number to a

fix number and outputs it in channel number I;

Integer procedure FBIN (A); Real A;

DAOUT: = FBIN(U)

End;

Procedure FMOVE(A,L);

Integer L;

Array A(1:L);

Begin

comment

Entry:

A = the vector

L = the vectorlength

This procedure moves the vector A one step

upwards in the memory;

Integer

I;

I := 1

step l until L do A(L+2-I):=A(L+1-I);

A(1) := 0;

End;

Real Procedure FLIM(U,UL);

Real U, UL;

Begin

comment

Entry: U = signal to be limited

UL = limit of signal

This procedure limits the magnitude of signal U

to UL volts;

If ABS (U) < UL

then FLIM:=U else

if U> UL

then FLIM:=UL else FLIM:= -UL

End;

```

```

Real Procedure SCAPR(A,B,N);

Integer N;

Array A,B(1:N);

Begin

comment

Scalar product of the vectors A and B

of length N;

Integer

I; Real

R:=0;

If N = 0 then go to out;

For I = 1 step 1 until N do R:=R+A(I)×B(I);

out: SCAPR := R;

End;

Procedure

REG1;

Begin

comment

This procedure outputs the control signal

to the process. Fscal is computed from the

sampleintervall t-1.

U-vector is moved one step upwards in the memory;

Array YS, U, VS(1:14);

Integer NA, NB, NC, k, NS;

Real Fscal, U, A, Ul;

Real Procedure FLIM, DAOUT, BINF;

NS:=NB+k+1;

FMOVE (U, NS);

Ul := T(1) \times YS(1) + Fscal;

If NC=/=0 then U1:=U1-T(NA+NB+1)\times VS(1);

U:= FLIM(U1,ULIM);

A := DAOUT(0,U);

U(1) := BINF(A);

End;

```

```

Procedure

ESTIM;

Begin

comment

Performs the tuning in the self-tuning regulator.

The tuning is done with a repeated least squares

estimation of the model parameters.

YS-U- and VS- vectors are not changed in ESTIM.

P- covariance matrix of the parameter estimates

of order (NA+NB+NC) \times (NA+NB+NC)

RL- the base of the exponential forgetting function;

Array YS,U,VS(1:14), T,FI,S,PI,RK(1:9),P(1:9,1:9);

Integer NA,NB,NC,k,I,J,N1,NS;

Real

RL, Denom, Res;

N1 := NA + NB + NC ;

FI(1) := -YS(k+2);

If NB=/=0 then FI(NA+1) := U(k+2);

If NC=/=0 then FI(NA+NB+1) := VS(k+2);

For I:=1 step 1 until N1 do

Begin

for J:=1 step 1 until N1 do

PI(J) := P(I,J);

S(I) := SCAPR(PI,FI,NL)

End;

Denom: = SCAPR(FI,S,N1);

Denom: = 1.0 + Denom;

Res:= SCAPR(FI,T,N1) ;

Res:= YS(1)-U(k+1)-Res;

NS := N1-1;

FMOVE (FI, NS) ;

For I:= 1 step 1 until N1 do

RK(I) := S(I)/Denom;

Begin

T(I) := T(I) + RK(I) \times Res;

For J:=l step l until I do

Begin P(I,J) := (P(I,J) - RK(I) \times S(J)) / RL;

```

P(J,I) := P(I,J) ;

End;

End;

End;

#### Procedure REG2

#### Begin comment

```

This procedure moves YS- and VS-vectors one

step upwards in the memory and computes Fscal

in the sampleintervall t.

Array YS,U,VS(1:14) , T,A(1:9);

Integer NA,NB,NC,NS,I,k;

Fscal,Fl,F2,F3;

Real

NS:= NA+k+1;

FMOVE (YS, NS) ;

NS:=NC+k+1;

FMOVE (VS, NS) ;

Fl := SCAPR(YS, T, NA);

For I:=1 step 1 until NB do A(I):=T(NA+I);

F2:=SCAPR(U,A,NB);

For I:=1 step 1 until NC do A(I):=T(NA+NB+I);

F3:=SCAPR(VS,A,NC);

Fscal:= F1-F3-F2 ;

```

End;

#### 4.2.2 The low-level subroutines

The floating-point arithmetic routines FMUL, FADD, FDIV use a floating-point number representation. This representation uses two 8-bit words holding the magnitude of the number in 2's-complement form, normalised within the range  $\pm (0.5 \text{ to } 1.0-2^{-15})$ , together with one 8-bit word holding the 7-bit exponent in Excess-64 form. Excess-64 form is chosen, since when used in conjuction with the 8 th bit (MSB) of the exponent word, it is easy to detect and distinguish between overflow and underflow of the exponent. The exponent range is -64 to +63 decimal.

The range of numbers represented by these three words is  $0.5\times2^{-64}$  to  $(1-2^{-15})\times2^{63}$ , which is  $2.7105\times10^{-19}$  to  $0.9223\times10^{19}$  and accuracy is 1 part in  $2^{15}$  (approx. 0.003%) giving 4.5 decimal digits.

Overflow results are set to  $0.9223 \times 10^{19}$  with the appropriate sign; underflows are set to zero, which is represented here by three words all containing zero, which is  $0 \times 2^{-64}$ , in order to make zero less significant than the smallest non-zero number.

The choise of register allocation convention is influenced by the special functions associated with certain registers. H and L are used together to address memory, so should not be used to hold the first operand or the result. H and L can be transferred directly to and from consecutive memory locations, storing the contents of L before H; the accumalator, A, can also be transferred directly to and from memory. D and E can be exchanged with H and L by a single instruction.

The arithemetic routines are pressed for register space and therefore they first calculate the result exponent and move it out of the way. An operand exponent can therefore be loaded initially into the accumalator, ready for the exponent calculation. To chain aruthemetic routines

it is best if the result of one operation is left in the correct registers to be the first operand of the next operation. Taking into account all these considerations, registers (B DE) are used for the first operand exponent, more significant half, and less significant half respectively, and registers (A HL) are similarly allocated for the second operand (if any). The remaining register, C, is used for storing a count of the negations performed, and a copy of the carry bit for determining over or underflow. All routines leave the result in registers (B DE):

Floating-point numbers in memory are allocated three consecutive words containing the exponent, less significant half, and more significant half respectively. This order allows use of the INTEL 8080's direct double load and store instructions (LHLD and SHLD). The stack is used for temporary storage of numbers.

All arithmetic routines operate on normalised numbers and expect the operands to be correctly normalised and in the correct registers. The routines give invalid results if used with unnormalised operands.

Basic routines used by the arithmetic routines Negation routine, NEGDE

NEGDE negates the contents of registers D and E, trated as a 2's complement number. There are two entry points, one of which increments register C containing the negation count; the order does not.

In two's complement the largest negative number, NEGMAX, has no positive equivalent, and if used as an operand of NEGDE the result still equals NEGMAX. NEGMAX is not counted as a correctly normalised number, and can only occur as the result of an addition of two negative numbers. The floating-point addition routine detects the result of NEGMAX by finding that the number is still negative after NEGDE has been used to try and make it positive.

Overflow and Underflow Handler, OUFLW

OUFLW consists of several routines and entry points, which detect which of exponent overflow or underflow has occured and set the result accordingly.

OUFLW: uses the carry produced during exponent calculation, and stored in the MSB of register C, to determine the condition prevailing. It then uses OFLW or UFLW to set the correct result.

$\underline{\text{OFLW}}\colon$  sets the result to the largest floating-point number, 0.9223×10  $^{19}$  and sets the sign according to the negation count in C.

UFLW: sets the result to zero.

<u>UFLWE</u>: sets the result exponent to zero.Used to correct the exponent if the result of a calculation is truly zero.It is not reported as an overflow.

Floating-Point arithmetic routines FMUL, FADD, FDIV

For a detailed description of these routines, see {2}.

A modification has been done of the routine FADD and it is listed in Appendix B.

Execution times are listed in Table 1 for typical and maximum time cases for the floating-point routines. If a fast return is made because of a zero operand or an over or under flow then the time taken is much less than the times given.

| FADD | typical 0.25 | ms maximum | 0.53 mS  |

|------|--------------|------------|----------|

| FMUL | 0.75         | i mS       | 0.861 mS |

| FDIV | 0.75         | 5 mS       | 0.845 mS |

Table 1 Execution times

LOAD, STORE, BINF, FMAGN: See Appendix

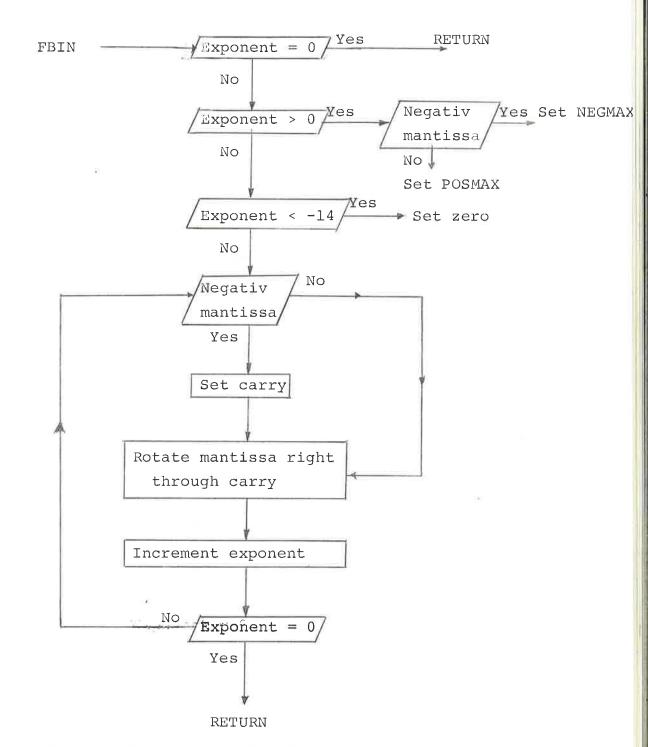

FBIN: For the assembler program with the comments, see Appendix. Here follows the flow diagram:

Fig 4.5 Flow diagram for the conversion from a floating-point number to a fix number.

The amount of memory needed for the subroutines used in the Self-Tuning regulator are as follows:

| ¥     | Bytes |

|-------|-------|

| UTIL  | 60    |

| FADD  | 93    |

| FMUL  | 79    |

| FDIV  | 74    |

| FBIN  | 48    |

| FLIM  | 23    |

| SCAPR | 74    |

| ADIN  | 23    |

| DAOUT | 8     |

| FMOVE | 36    |

| INIT  | 76    |

| STURE | 91,   |

| REGl  | 97    |

| ESTIM | 432   |

| REG2  | 107   |

The routines above begin at address 000:071.

The following instructions are stored in the memory locations 000:000-000:070

000: LXI SP, $10 \times 400 + 400$

003: CALL INIT

006: JMP STURE

011: NOP

• •

067: NOP

070: RET

Including this the total amount of memory requirement is 1378 Bytes, meaning that 6 PROM are needed.

The execution time of the program depends on the number of parameters. The experiments have resulted in following execution times. (Instruction cycle-time of  $1 \mu s$  were used)

| Number of pa | rameters | Time    | (ms) |

|--------------|----------|---------|------|

| NA+NB+NC     |          |         |      |

|              |          |         |      |

| 1            |          | typical | 20   |

| 2            |          |         | 50   |

| 3            |          | 1       | 00   |

| 5            |          | 2       | 10   |

| 7            |          | 4       | 00   |

| 9            |          | 5       | 50   |

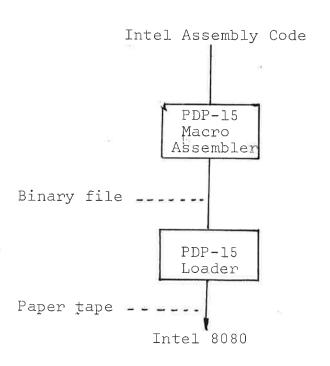

For the compilation of the program for the microcomputer, the host computer PDP-15 was used.

Using the macrodefinition file ASS80, the assembler of PDP can generate code for Intel 8080. The program LOAD8 take then care of the of the work of the assembler. The programs ASS80 and LOAD8 are described in {1}. Load8 relocates and link together the subroutines and it produces absolute code on a paper tape, which, via a teletype, directly can be read into the RAM- and PROM memories.

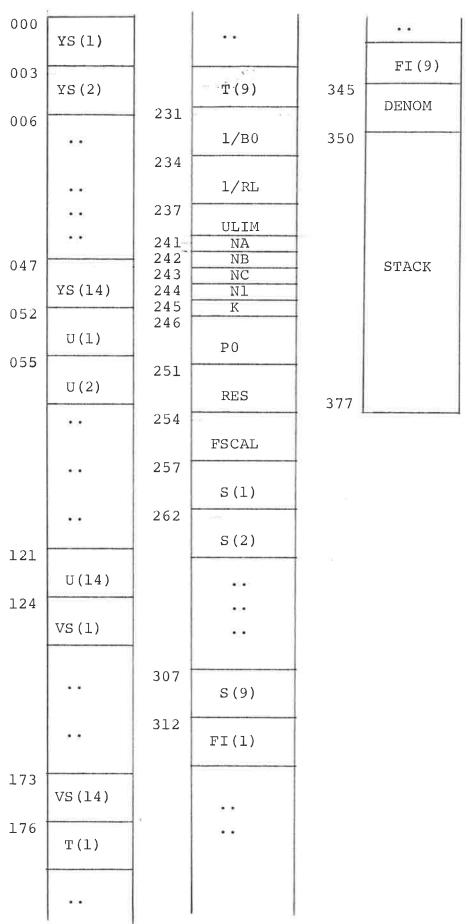

#### 4.3 Datastructure

All the data needed to STURE, are stored in RAM-memory beginning at bank 010 (A bank has 0400=256 bytes.

1 Byte = 1 word = 8 bits). See fig. 4.6 and fig. 4.7

Every data is represented as a floating-point number, except for the integers NA,NB,NC,k,Nl,Slask3,Slask4,N and for the fractional number ULIM.

A floating-point number has the 8-bits exponent in Excess-64 form and the 16 bits mantissa in two's complement form. Each number has its exponent stored in the first byte, the low-order mantissa in the second byte and the high-order mantissa in the third byte.

The meaning of the vectors YS,U,VS,T are explained in the comments to STURE. The adress of the first element of the vectors U,VS,T,S,FI are fixed by the following dimension restrictions:

MAX(NA+NB+NC) = 9

MAX(NA+k+2) = 14

MAX(NB+k+2) = 14

MAX(NC+k+2) = 14

Dynamical allocation has not been used for these vectors since we can save more programmemory than datamemory. It is also naturally to use a temporary storage for the computed values of S(I) since these are used several times in the subroutine ESTIM, and it is impossible to save all the values in the stack.

On the contrary the need of a seperate FI-vector stored in the memory can be discussed. The FI-vector is organized as follows:

FI(1) = -YS(k+2)

FI(NA) = -YS(k+NA+1)

FI(NA+1) = U(k+2)

FI(NA+NB) = U(k+NB+1)

FI(NA+NB+NC) = VS(k+NC+1)

The advantages of having a separate FI-vector are

- a) The subroutine SCAPR needs to be called only once instead of three times for computing each element of the S-vector, also for computing the variables Denom and Res.

- b) The execution time is shorter.

The drawbacks of having a separate FI-vector are

- a) More data memory space.

- b) One extra call of the routine FMOVE is needed.

As the memory requirement is only 033 Bytes of a FI-vector, we see that the advantages are superior the drawbacks.

1/B0, 1/RL - See the comments to the Algol program.

NA, NB, NC, k - These variables are explained in the comments to STURE:

N1 - The subroutine INIT computes N1=NA+NB+NC.

P0 - At the beginning of the simulations the subroutine INIT updates the P-matrix according to  $P(0) = P0 \times I$ , where I is a unit matrix.

Denom, Res, RKI- These variables are used in ESTIM. It is not necessary to store the RK-vector. In this case thetstack is used.

Fscal - Is used in REG1 and REG2.

ULIM - The limit of control signal is stored with the less significant half on the first byte and the most significant half on the second byte.Considering that |U| < ULIM, Ulim is varying from 00000 to 077777 (2-complement form) corresponding to 0 V respectively 9.984 V.

The rest of the bank 010, 030 Bytes, is used as temporary storage space by the stackregister, which gets the value 0400 at the beginning of the program. SP is then decremented by the first CALL-instruction.

Fig. 4.6 Dataorganization for Bank 010

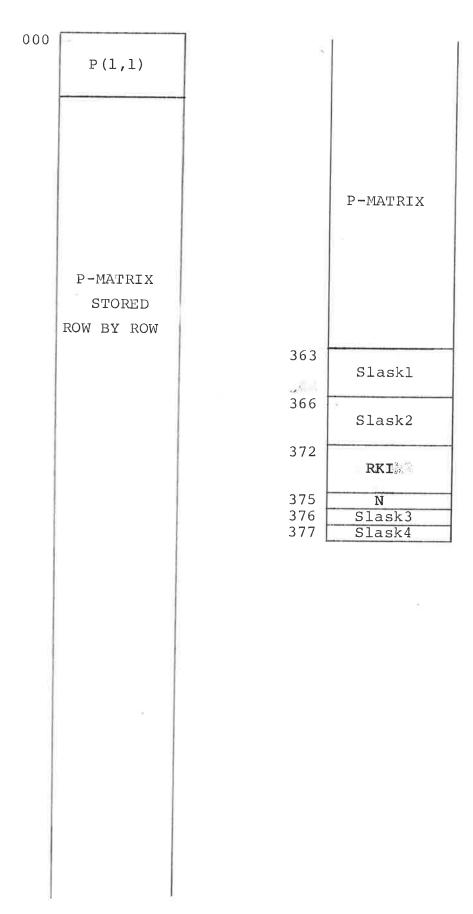

Fig. 4.7 Dataorganization for Bank 011

In Bank 011 the P-matrix and some temporary cells are stored.

P-matrix- The P-covariance matrix of the parameter estimates of order (NA+NB+NC) × (NA+NB+NC) is symmetric.

Advantages with symmetric matrixes are:

- a) Memory space can be saved. A n×n matrix needs only to store n×(n+1)/2 elements.

In our case, assuming that n=9, using the symmetric property only 0107 bytes has to be stored as maximum, otherwise 0363 bytes are stored as maximum.

- b) The computation P(I,J)=P(J,I) is done automatically.

If the array is stored lexicographically as follows:  $P(1,1),P(2,1),P(2,2),P(3,1),\ldots,P(n,1),\ldots P(n,n)$  we get a big problem when computing the S-vector, for calling the subroutine SCAPR, (see ESTIM). We will need more space for programmemory for each test of the indixes of elements. Consider, the execution time and the programmemory space, the P-matrix is ordered by rows and would be stored with dynamically allocation in the order:  $P(1,1),P(1,2),\ldots P(1,n),P(2,1),\ldots P(2,n),\ldots P(n,1),\ldots P(n,n)$ .

Slask1- Three temporary cells, used in ESTIM.

Slask2- Three temporary cells, used in SCAPR.

N- One temporary cell, used in SCAPR.

Slask3- One temporary cell, used in ESTIM.

Slask4- One temporary cell, used in ESTIM.

### 5. A HARDWARE SUMMARY

Houses are built to live in and not to look on.

FRANCIS BACON

In this chapter follows a summary of the hardware. For a detailed description see  $\{\ \ \ \ \ \ \ \}$ .

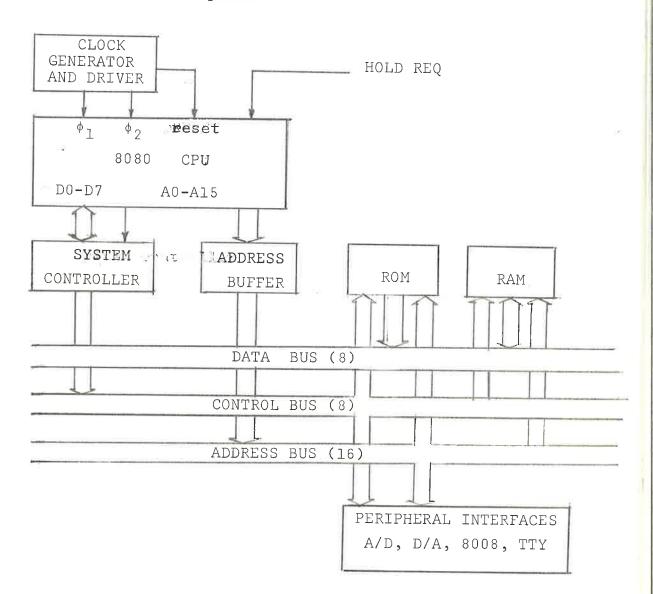

In the figure below is shown the microcomputer system, where STURE, is implemented.

For this implementation we need six modules; CPU, ROM, RAM, A/D, D/A, Interface to 8008.

CPU module - Contains the Clock generator, the **Sy**stem controller, the **C**entral Processing Unit, and some extra logic for interrupt, display, etc.

Clock generator contains a crystal-controlled oscillator, a"divide by nine" counter, two high-level drivers and several auxilliary logic functions.

It generates two non-overlapping clock pulses ( $\phi_1$  and  $\phi_2$ ) who drive the 8080.

Each clock period marks a state; three to five states constitute a machine cycle, and one to five machine cycles comprise an instruction cycle. A full instruction cycle requires anywhere from 4 to 18 states for its completion, depending on the kind of instruction involved. With a crystal frequency of 9 MHz, we get an instruction cycle time of 1  $\mu s$ . The System controller generates all control signals required to directly interface. MCS-80 family RAM, ROM, and I/O- components.

The Central Processing Unit consists of the following functional units:

- . Registers array and address logic

- . Arithmetic and logic unit (ALU)

- . Instruction register and control section

- . Bi-directional, 3-state data bus buffer.

When power is applied initially to the 8080, the processor begin operaing immediately. The contents of its program counter, stack pointer, and the other working registers are naturally subject to random factors and cannot be specified. For this reason, it will be necessary to begin the power-up sequence with RESET, where the program execution begins with memory location zero.

Systems which require the processor to wait for an explicit start-up signal will store a halt instruction (EI,HLT). A manual or an automatic INTERRUPT will be used for starting.

One-byte call instruction RESTART (RST) facilitates the processing of interrupts.RST enables the interrupting device to direct a call to memory location 070. Since the RST-instruction is a CALL-instruction, a RETURN (RET) instruction has to be put in cell 070.

The 8080 CPU contains provisions for Direct Memory Access (DMA) operations. By applying a HOLD to the appropriate Control pin on the processor, an external device such as the Intel 8008, can cause the CPU to suspend its normal operations and relunguish control of the address and data busses. The processor responds to a request of this kind by floating its address to other devices sharing the busses.

ROM module - A ROM is a device that stores data in the form of program and it is non-volatible.

This module contains 2K Bytes of PROM, with addresses 000:000 - 007:377.

The Self-Tuning regulator needs less than 1,55K.

RAM module - RAMs do not hold their data when power is removed.

The RAM module also contains 2K with addresses 010:000 - 017:377.

Interface :

The problem of operator's communication in this first experimental setup is solved by using another microcomputer based on an Intel 8008, which has some communication programs.

A part of the 8008 memory is shared between the 8008 and 8080, thus enabling the operator to enter parameters to the 8008 and then switch the shared memory to the 8080.

A/D - converter-It is an eight channel, eight-bit converter with a conversion time of appr. 75  $\mu s$ . The input value to the CPU is in offset binary form. The conversion to 2-complement is done by software.

D/A-converter- It has four eight-channels.

The input value to the converter is in offset

binary form.

Both the A/D - and D/A - converters work between 0-9.98  $\rm V$  with a resolution of 39 mV.

| Analog       | signal | Binary representation        |

|--------------|--------|------------------------------|

| (∀)          |        | D/A - and $A/D$ - converters |

|              |        |                              |

| 9.984        |        | 11111111                     |

| 9.945        |        | 11111110                     |

| •            | ¥      |                              |

|              |        |                              |

| 7 <b>=</b> % | 4      |                              |

| 4.992        |        | 1000000                      |

| •            |        | ¥ 19                         |

| 42           |        | ¥                            |

| 0.039        |        | 0000001                      |

| 0            |        | 0000000                      |

### 6. MANUAL FOR STURE

Science is organized knowledge.

HERBERT SPENCER, EDUCATION

- 1. Connect the interface module to the memory slot.

- 2. Switch on the power supplies to both Intel 8080, and to the TRANSINTRO.

- 3. Set the switch EXT/INT on the interface module to EXT, and push the switch RUN/STOP/SINGLE STEP to the SINGLE STEP once.

Now, TRANSINTRO has the command over the datamemory belonging to 8080.

4. Set the switchregister in TRANSINTRO to

0 0 0 0 0 0 0 0 0 0 1 1 1 0 1

and push on RUN:

Now, to change your data, you can use the operator consol and the program which has been developed at the department.

5. A memory address may be selected using a thumbwheel switch. The content of the selected location, which is shown on the display, may be changed using another thumbwheel switch. There are possibilities to choose if the input value will be an integer or real, decimal or octal. When the IN-button is pushed the computer reads the new value. The floating-point numbers 1/RL, 1/BO, PO have the mantissa in 2-complement and the exponent in Excess-64 form, a\*2<sup>b</sup>, where b=(x-100)<sub>8</sub> and x is the value on the display in octal form.

All the vectors are initialized by the subroutine INIT.

The input parameters have following organization in the memory:

| memory | location | content |                                    |

|--------|----------|---------|------------------------------------|

| 010:   | 231      | 1/B0    | Exponent                           |

|        | 232      | 1/B0    | Less significant half of mantissa  |

|        | 233      | 1/B0    | Most significant half of mantissa  |

|        | 234      | 1/RL    | Exponent                           |

|        | 235      | 1/RL    | Less significant half of mantissa  |

|        | 236      | 1/RL    | Most significant half of mantissa  |

|        | 237      | ULIM    | Less significant half of ULIM (=0, |

|        |          |         | using an 8-bit D/A -converter      |

|        | 240      | ULIM    | Most significant half of ULIM      |

|        | 241      | NA      | Integer                            |

|        | 242      | NB      | Integer ·                          |

|        | 243      | NC      | Integer                            |

|        | 244      | Nl      | INIT computes N1=NA+NB+NC          |

|        | 245      | k       | Integer                            |

|        | 246      | ΡO      | Exponent                           |

|        | 247      | PO      | Less significant half of mantissa  |

|        | 250      | P0      | Most significant half of mantissa  |

- 6. Push STOP on the TRANSINTRO.

- 7. Switch the button EXT/INT to INIT.

- 8. Connect the reference signal to channel 0 on the A/D -converter.

- 9. Connect the output signal from the process to channel 1 on the D/A -converter.

- 10. Connect the output from channel 0 on the  ${\rm D/A}$  -converter to the process.

- 11.Connect the interrupt signal to INT on the CPU-module,

and choose a sampling-interval.

- 12.Push RESET

- 13. Push RUN (voilà)

If you want to stop, for example change any parameter push STOP, and GO TO 3.

#### 7. EXPERIMENTS

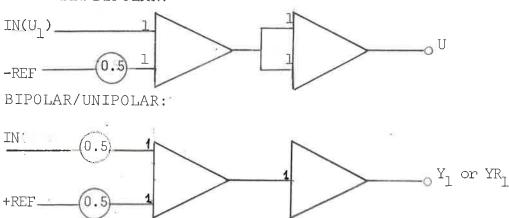

Different processes have been simulated on the analog computer. The output value from the process as well as the input value to the process can vary between -10 V to +10 V. Since the A/D - and D/A - converters works only for 0-10 V we have to use an Bipolar-Unipolar converter and an Unipolar-Bipolar converter respectively.

The schemes for the blocks U/B and B/U on the analog computer are as follows:

# UNIPOLAR/BIPOLAR:

In all the following experiments, the number of pure timedelays, k ,have been chosen equal to zero.

1. A simple test of the algorithm.

A registration of the output signal from the process (A single integrator) and the control signal to the process has been done when applicating a referencesignal change of 5 V.

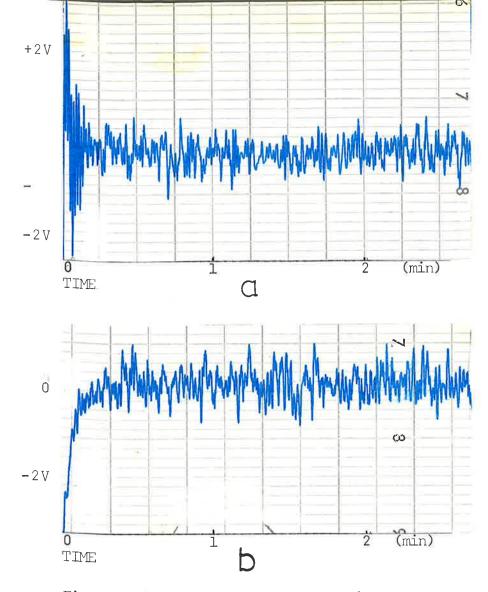

A change of 5 V is for the computer a change of 0.5. Figure 7.1 a shows the simulation of the process on the PDP-15. The reference signal change was entered after 15 samples. The second plot (Fig. 7.1 b ) is from the analog computer and the microcomputer.

After the change of reference signal the output signals behave appropriate in the same manner in both figures.

## 2. Single-Integrator

Consider the system

$$(1-q^{-1})y(t) = T \times u(t-1) + e(t)$$

(7.1)

The scheme of the process on the analog computer is as follows:

The optimal minimum-variance regulator is defined by the polynamials

$$Q = 1$$

$B = 1$   $G = 1 - q^{-1}$

Let T=1 ( the samplinginterval is one second ).

a) Let the reference value be a square wave with amplitude 1 V and a period of 20 steps. Further we assume that e(t)=0. The system is controlled by a self-tuning regulator with NA=1, NB=0, NC=0. The initial covariance matrix was  $P(0)=5\times I$ , the exponential forgetting factor was  $\lambda=0.98$ , and the scale factor  $\beta_0$  was 1.

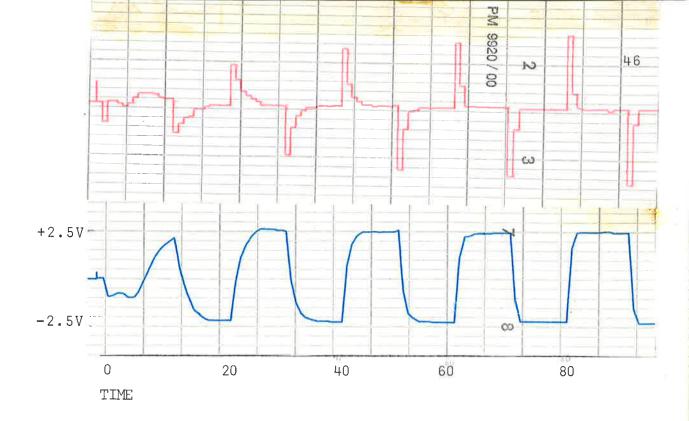

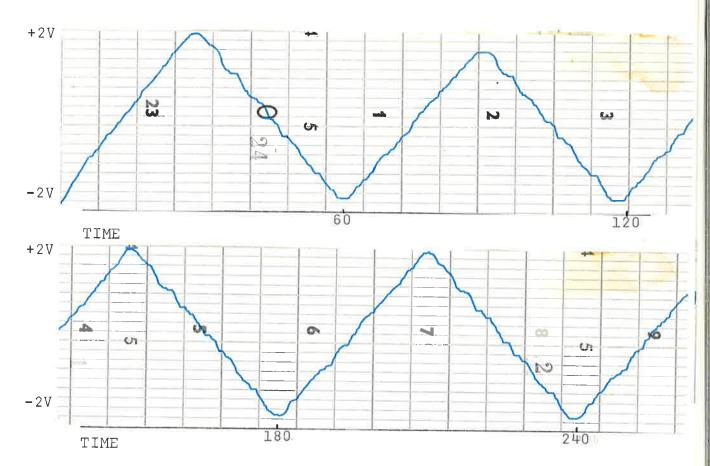

Fig. 7.1 - The output and the control signal when the process is a single integrator.

The simulations were done on a. A Minicomputer, PDP-15

b. A Microcomputer and an Analogcomputer

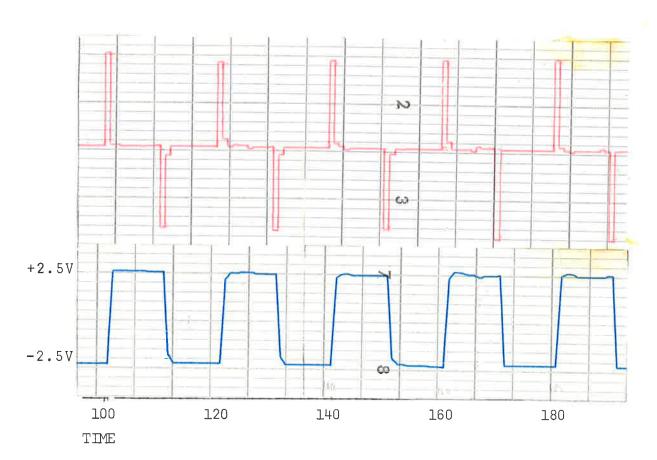

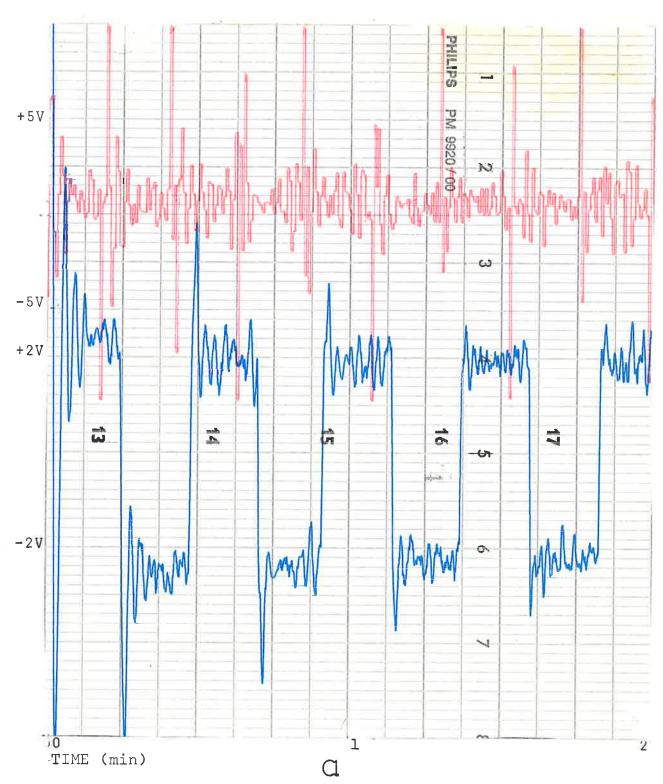

The output from the system and the input to the system at different periods of time is shown in figure 7.2. From the figure it is seen, ignoring for some disturbances on the converters, that the self-tuning regulator, after 10-12 changes in the reference values, converges to a regulator with the property that the error is zero after one step after a change in the reference value has occured. When using the forgetting factor  $\lambda$ =1 the same result was obtained after 30 changes in the set-point.

The regulator obtained after 300 steps (30 changes in the reference signal) was

$$u(t) = -0.87(y(t)-y_n(t))$$

The parameter  $\alpha_1$  converge to the value -1.

The optimal control law is  $u(t) = -l(y(t)-y_r(t))$

The closed loop system will then be

$$y(t) = y_n(t - 1) + e(t)$$

(7.2)

For the system (7.1) the self-tuning algorithm converges to the same controller indepedent of the amplitude and period of the square wave signal as long as the system has time to settle between the changes.

b) Let the initial parameters be the same as in a) except for NC. Using feedforward control with NC=2, the simulation gave the result that the delay of the response was one sampling interval shorter than without feedforward control. In this case the regulator obtained after 300 steps was

$$u(t) = -0.93(y(t) - y_r(t)) - (0.98y_r(t+1) - 0.99y_r(t))$$

The optimal control law is

$$u(t)=-1(y(t)-y_r(t))-(y_r(t+1)-y_r(t))$$

The closed loop system will then be

$$y(t)=y_{r}(t)+e(t)$$

Compare with (7.2)

With the same initial parameters as above, a test of the regulator was done by changing the process during the control.

Fig. 7.2 The output and the input of system (7.1). The reference signal is a square wave.

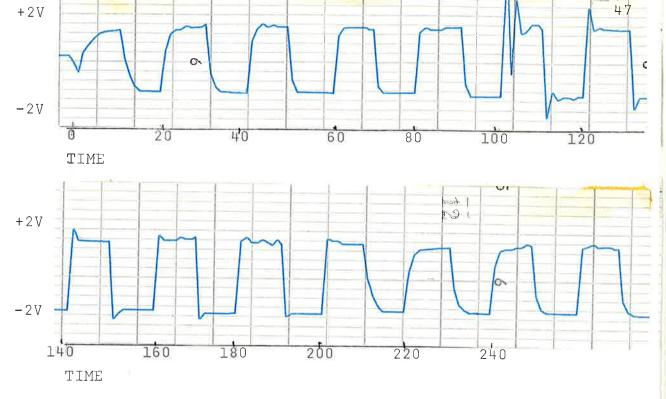

Fig. 7.3 The output of the system 7.1, when a change of the process occures.

Figure 7.3 shows the step responses at different times. After 11 changes of the reference value, the gain of the process was doubled. The overshot became of the same magnitude as the disturbances already at time 160. At time 220 the gain was set to its initial value.

c) Let the reference value be a triangular wave with amplitude 1.8 V and a period of 60 steps. The forgetting factor,  $\lambda$ , was chosen to 0.98. The system has been controlled by the self-tuning regulator with NA=2, NB=1, NC=0. The output from the system is shown in figure 7.4.

The regulator obtained after 488 steps was

$$u(t)=-0.31(y(t)-y_n(t))-0.225(y(t-1)-y_n(t-1))-0.875u(t-1)$$

The closed loop system in this case will be  $y(t)=(2-q^{-1})y_n(t-1)$

Fig. 7.4 The output of system 7.1, without any feedforward control. The reference signal is a triangular wave.

Fig. 7.5 The output of system 7.1, with feedforward control. The reference signal is a triangular wave.

d) Let NA=1, NB=0, NC=2. Using the optimal feedforward controller the closed loop system will be

$$y(t) = y_n(t) + e(t)$$

The result when using the self-tuning regulator is shown in figure 7.5. The regulator obtained, in this case, after 360 steps was

$$u(t)=-1.64(y(t)-y_r(t))-(-1.4y_r(t+1)+1.25y_r(t))$$

The optimal control law is  $u(t)=-1(y(t)-y_r(t))-(-1y_r(t+1)+1y_r(t))$

e) All the experiments above have been done with the noise equal to zero.

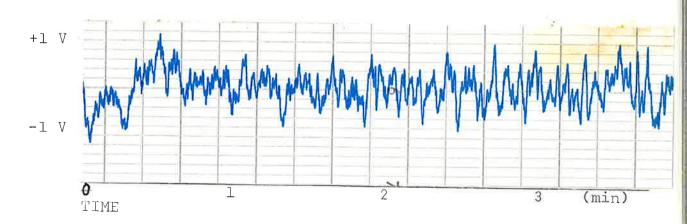

Figure 7.6 shows the output of the system when adding noise. In this case a constant reference signal is used, and NA=1,NB=0,NC=0 has been chosen.

The output is varying within  $\pm$  1V. The regulator converged to

$$u(t) = -0.97(y(t) - y_n(t)$$

Normally the regulator converge faster with a noise.

Fig. 7.6 The output of system 7.1, with noise and constant reference signal.

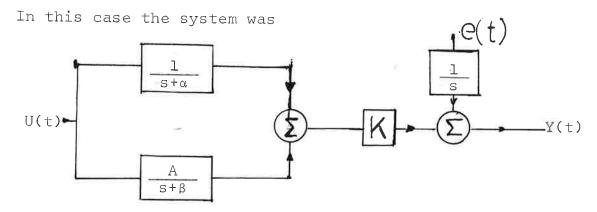

## 3. Third order system.

where  $\alpha$ =0.211,  $\beta$ =0.713, A=0.877 and K=4.744 The sampled system will then be

$$A(q^{-1})y(t)=B(q^{-1})u(t-1)+C(q^{-1})e(t)$$

where

$$A(q^{-1})=1-2.6q^{-1}+2.23q^{-2}-0.63q^{-3}$$

$$B(q^{-1})=0.5(1-q^{-1})$$

$$C(q^{-1})=1-1.6q^{-1}+0.63q^{-2}$$

The optimal minimum variance regulator is determined by

$$\mathcal{A} = -1 + 1.6q^{-1} - 0.63q^{-2}$$

$$\mathcal{B} = 1 - q^{-1} \qquad \beta_0 = 0.5$$

$$\mathcal{E} = 1 - 2.6q^{-1} + 2.23q^{-2} - 0.63q^{-3} \qquad (7.3)$$

The sample interval for this system has been chosen to 0.5s. The scale factor  $\beta_0$ =0.5.

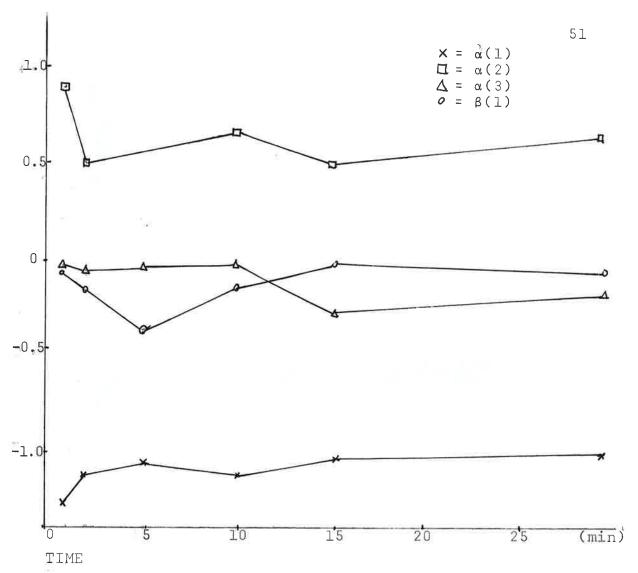

# a) Parameter convergence.

Let the reference signal be constant and intoduce noise on the system.Let the forgetting factor be  $\lambda=1$ . The convergence matrix has been chosen to P(0)=10×I.

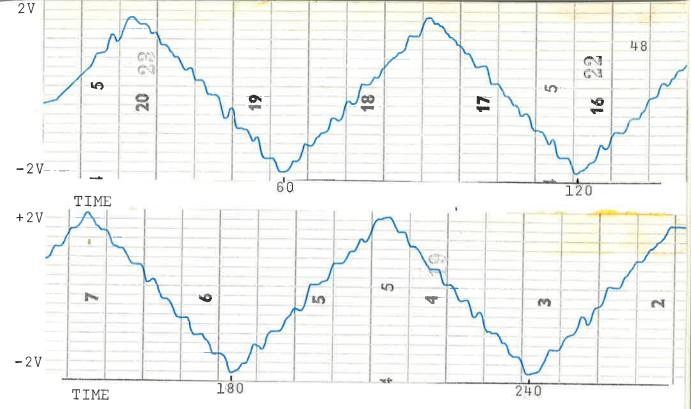

In figure 7.7 the parameter estimates are shown.

Fig. 7.7 Parameter estimates of system 7.2.

Even if the parameters have not converged to the optimal values after 30 min., the control of the system was very good which will be shown in the next section.

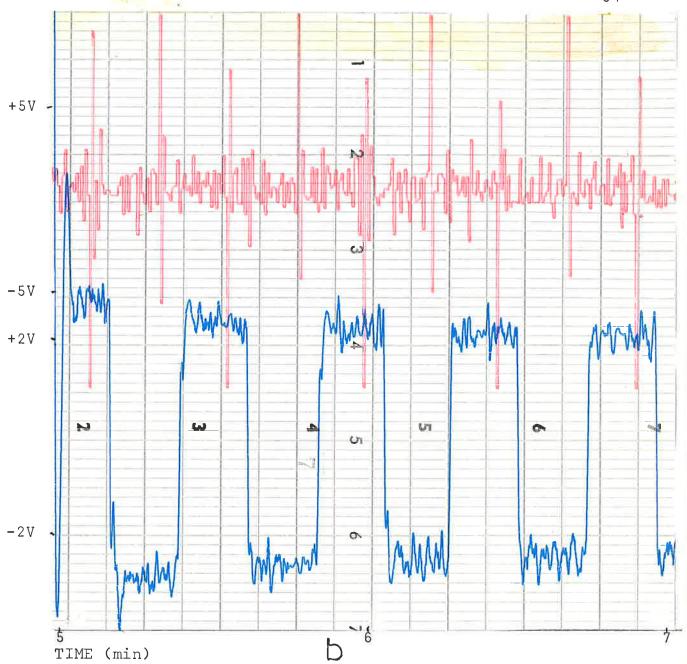

## b) Comparison between

Controlling the system with STURE. (Fig. 7.8 a)

Controlling the system with the theoretical minimum variance regulator. (Fig. 7.8 b)

The reference signal is constant and noise is introduced on the system. The initial parameters are:  $\lambda=1$ ,  $P(0)=5\times I$ , NA=3, NB=1, NC=0.

Although the parameters in the selftuning regulator had not converged to the theoretical values (7.3) the behavior of the closed loop system was very good. By just looking at the recording of output when using the two regulators it can be seen that the selftuning regulator is at least as good as the theoretical regulator.

Fig. 7.8 The output of system 7.2 with

a) the self-tuning regulator

b) the minimum variance regulator

c) Let the reference signal be a square wave with amplitude 2V and period about 50 steps.

Noise is also added to the process. A better perfomance can be obtained if the controller also gets direct information about changes in the reference signal. This can be taken care of by a feedforward signal from the reference value. Let therefore NA=3, NB=1, NC=4. The covariance matrix  $P(0)=5\times I$ .

The forgetting factor was at the beginning chosen to  $\lambda=0.98$  and when the overshoot become less, the forgetting factor was changed to  $\lambda=1$ . (Fig. 7.9 a,b.)

The change of  $\lambda$  occurred after 5 minutes.

Fig. 7.9 The output and the control signal of system 7.2 with  $\lambda\!=\!0.98$

Fig. 7.9 The output and the control signal of system 7.2 with  $\lambda \not\cong 1$ .

The regulator obtained after  $1150\ \text{steps}$  (48 changes in the reference signal ) was

$$U(t) = (-1.68 + 1.25q^{-1} - 0.38q^{-2})(y(t) - y_r(t))/0.5 - (-0.6u(t-1) - (-1.2q + 2.5 - 1.75q^{-1} + 0.4q^{-2})y_r(t)/0.5$$

#### 8. REFERENCES.

I recommend you to take care of the minutes for the hours will take care of themselves.

LORD CHESTERFIELD

- {1} Andersson, L: Cross Assembly and relocation of programs for the Intel microprocessors using a PDP-15 as host computer, Report 7602, Division of Automatic Control, Lund Institute of Technology.

- {2} Clarke, F,D: Floating-point arithmetic routines and Macros for an Intel 8080 microprocessor, Department of Engineering Science, University of Oxford.

- {3} Sjöberg, P-0: Hardware to Intel 8080, Department of Automatic Control, Lund Institute of Technology.

- {4} Wittenmark,B : A self-tuning regulator, Report 7311, April 1973,Division of Automatic Control, Lund Institute of Technology.

# INSTRUCTION SET

# Summary of Processor Instructions

| Mnemonic                 | Description                                         | D,    | D <sub>6</sub> |    | tructi<br>D <sub>4</sub> |     |      |     | D <sub>O</sub> | Clock 121<br>Cycles | Mnemonic       | Description                           | D,   | n <sub>G</sub> | Inst<br>Oh | ructi<br>D <sub>4</sub> | on C | ode!<br>D <sub>2</sub> | 0  | 00 | Clack!<br>Cycles |

|--------------------------|-----------------------------------------------------|-------|----------------|----|--------------------------|-----|------|-----|----------------|---------------------|----------------|---------------------------------------|------|----------------|------------|-------------------------|------|------------------------|----|----|------------------|

| .01/                     | Move register to register                           | 0     | 1              | D  | D                        | D   | S    | S   | s              | 5                   | RZ             | Return on zero                        | :10  | 191            | 0          | 0                       | ,    | 0                      | _  | _  |                  |

| /0 V d . i2<br>/0 V M, r | Move register to memory                             | 0     | 1              | 1  | 1                        | 0   | S    | S   | S              | 1                   | RNZ            | Return on na zero                     | 1    | 1              | 0          | 0                       | 0    | 0                      | 0  | 0  | 5/11             |

| M. VON                   | Move memory to register                             | 0     | 1              | D  | D                        | 0   | 1    | 1   | 0              | 7                   | RP             | Return on positive                    | 1    | 1              | 1          | 1                       | 0    | 0                      | ů. | 0  | 5/11             |

|                          | Han                                                 | t)    | 1              | 1  | 1                        | 0   | 10   | 1   | 0              | 1                   | RM             | Return on minus                       | 1    | 1              | i          | 1                       | 1    | 0                      | 0  | () | 5/11             |

| ILT<br>NVI 1             | Move immediate register                             | 0     | 0              | D  | n                        | D   | 1    | 1   | 0              | 1                   | RPE            | Return on parity even                 | 1    | 1              | i          | 0                       | 1    | 0                      | 0  | 0  | 5/11             |

| IVI M                    | Move immediate memory                               | 0     | 0              | 1  | 1                        | 0   | 1    | 1   | O              | 10                  | RPO            | Return on parity odd                  | 1    | 1              | i          | 0                       | 0    | 0                      | 0  | 0  | 5/11             |

| yR r                     | Increment register                                  | 0     | 0              | n. | 11                       | n   | 1    | (1) | 0              | 5                   | RST            | Restart                               | 1    | 1              | À          | Α                       | Ä    | 1                      | 1  | 1  | 5/11             |

| CRr                      | Decrement register                                  | 0     | 0              | D  | D                        | 1)  | 1    | D   | 1              | 5                   | IN             | Input                                 | 1    | 1              | 0          | 1                       | 1    | 0                      | i  | i  | 11               |

| NR M                     | Increment memory                                    | 0     | 0              | 1  | 1                        | U   | 1    | 0   | 0              | 10                  | 0.01           | Output                                | 1    | 1              | 0          | 1                       | Ú    | 0                      | i  | 1  | 10               |

| CRM                      | Decrement inemory                                   | 0     | 0              | 1  | 1                        | O.  | 1    | ()  | 1              | 10                  | LXLB           | Load immediate register               | 0    | 0              | 0          | 0                       | 0    | 0                      | Ó  | 1  | 10<br>10         |

| 100                      | Add register to A                                   | 1     | 0              | 0  | 0                        | (F  | S    | S   | S              | 4                   |                | Pair B & C                            |      | (40)           | _          | 100                     | u    | u                      | U  | '  | 10               |

| DC r                     | Add register to A with carry                        | 1     | 0              | Ü  | 0                        | 1   | S    | S   | S              | 4.1                 | LXLD           | Load immediate register               | 0    | 0              | 0          | 1                       | 0    | 0                      | 0  | 1  | 10               |

| UB r                     | Subtract register from A                            | 1     | 0              | 0  | 1                        | 0   | S    | 5   | S              | 4                   |                | Pair D & E                            |      | 02.0           |            | 032                     |      |                        | 34 | 76 | 10               |

| 188                      | Subtract register from A with borrow                | 4     | n              | 0  | 1                        | 1   | S    | S   | S              | 1                   | TXIH           | Load immediate register<br>Pair H & L | U    | 0              | ì          | D)                      | 0    | 0                      | 0  | 1  | 10               |

| ı An,                    | And register with A                                 | 1     | 0              | 1  | 0                        | 0   | S    | S   | S              | 4                   | LXLSP          | Load immediate stack pointer          | 0    | 0              | 1          | 1                       | 0    | 0                      | 0  | 1  | 10               |

| (RA)                     | Exclusive Or register with A                        | 1     | 0              | 1  | 0                        | 1   | S    | S   | S              | 4                   | PUS11 B        | Push register Pair B & C un           |      | ï              | o          | 0                       | 0    | i                      | 0  | i  | 11               |

| ) GA r                   | Or register with A                                  | 1     | 0              | 1  | 1                        | 0   | S    | S   | S              | 4                   |                | stack                                 | (10) | 3.5            | 20         | 177                     | 92   | 50                     | 1  |    | 6.67             |

| MP r                     | Compare register with A                             | -11   | 0              | 1  | 1                        | 1   | S    | S   | S              | 4                   | PUSH D         | Push register Pair D & E on           | 1    | 1              | 0          | 1                       | 0    | 1                      | 0  | 1  | 11               |

| DO M                     | Add memory to A                                     | 1     | 0              | Ü  | 0                        | 0   | 1    | 1   | 0              | i                   | 0311.0         | stack                                 | (8)  | •              | O.         |                         | ()   | '                      | "  | 1  |                  |

|                          | Add memory to A with carry                          | 1     | 0              | 0  | 0                        | 1   | 1    | ī   | Ü              | î                   | PUSH H         | Push register Pair H & L on           | 1    | 1              | 1          | 0                       | 0    | 1                      | 0  | 1  | 1.1              |

| DC M                     | Subtract memory from A                              | 1     | 0              | 0  | 1                        | 0   | 1    | î   | 0              | Ž                   | 1 0311 11      | stack                                 | 9    | '              | 1          | U                       | ()   | '                      | u  |    | Ð                |

| 3B M<br>JB M             | Subtract memory from A with horrow                  | 1     | 0              | o  |                          | 1   | ī    | į   | 0              | ì                   | PUSTI PSW      | Push A and Flays<br>on stack          | 1    | 1              | 1          | ı                       | 0    | 1                      | υ  | 1  | 11               |

| NA M                     | And memory with A                                   | 1     | 0              | 1  | 0                        | 0   | 1    | 1   | n<br>n         | 7                   | POP B          | Pop register pair B & C off           | 1    | 1              | ()         | 0                       | 0    | 0                      | n  | 1  | 10               |

| RA M                     | Exclusive Or memory with A                          | 1     | 0              | 1  | 0                        |     | 1    |     | (2)            |                     | 7799-2019-2017 | stin k                                | 173  |                |            |                         |      |                        |    |    | 17.23210         |

| RAM                      | Or memory with A                                    | 1     | 0              | 1  |                          | 0   | - 5  | 2   | 0              | 7                   | POP O          | Pop register pair D & E off           | 1    | 1              | 0          | 1                       | 0    | 0                      | 0  | 1  | 10               |

| MP M                     | Compare memory with A                               | 1     | n              | 1  | 1                        | 1   | 1    | 1   | 0              | 7                   | D. C. Whi hile | stack                                 | 24.1 | S              |            |                         |      | ō                      |    |    | 2440             |

| 01<br>C1                 | Add immediate to A<br>Add immediate to A with       | 1     | 1              | 0  | 0                        | 1   | 1    | 1   | 0              | ,                   | POPH           | Pop register pair H & L off<br>stack  | 1    | 9              | 1          | 0                       | 0    | 0                      |    | 1  | 10               |

|                          | carry                                               | 11407 | 140            |    |                          | 0   |      |     | D.             |                     | POP PSW        | Pop A and Flags                       | 1    | 3              | 1          | I                       | 0    | 0                      | 0  | 1  | 10               |

| UI                       | Subtract immediate from A                           | - 3   | 1              | 0  | - 2                      | 0   | 1    | 1   | 0              | 7                   | 4              | off stack                             |      |                |            |                         |      | 1.744.7                |    |    | 17.000007        |

| 31                       | Subtract immediate from A                           | 1     | 15             | 0  | 1                        | - 1 |      | 1   | ū              | 1                   | STA            | Store A direct                        | 0    | 0              |            | 1                       | 0    | 0                      | 1  | 0  | 13               |

|                          | with horrisw                                        |       |                |    |                          |     |      |     |                |                     | LUA            | Load A direct                         | 0    | 0              | 1          | 1                       | 1    | 0                      | 1  | 0  | 13               |

| N I<br>fil               | And immediate with A<br>Exclusive Or immediate with | 1     | 1              | 1  | 0                        | 1   | i.   | 1   | 0              | 7                   | XCHG           | Exchange D & E, H & L<br>Registers    | 3    | ì              | 1          | 0                       | F    | 0                      | 1  | ), | 4                |

|                          | Α                                                   |       |                | -0 |                          |     | - 23 |     |                |                     | XTHL           | Exchange top of stack, H & L          | 1    | 1              | 1          | 0                       | a    | 0                      | 1  | 1  | 18               |

| M                        | Or immediate with A                                 | -1    | 1.             | 1  | 1                        | 0   | 1    | 1   | 0              | 7                   | SPHI           | H.& L to stack pointer                | 1    | 1              | 1          | 1                       | 1    | 0                      | 0  | 1  | 5                |

| PI                       | Compare immediate with A                            | 1     | 1              | 1  | 311                      | 1   | 1    | 1   | 0              | ,                   | PCHL           | H & E to program counter              | 1    | 1              | 1          | (1                      | 1    | 0                      | 0  | 1  | 5                |

| L C                      | Rotate A left                                       | 0     | 0              | 0  | 0                        | 0   | 1    | 3   | 1              | 4                   | DADB           | Add 8 8 C to H & L                    | 0    | 0              | 0          | u                       | 10   | ()                     | 0  | 1  | 10               |

| LAC                      | Rotate A right                                      | 0     | 0              | 0  | 0                        | 1   | 1    | 1   | 1              | 1                   | DADD           | Add D & F to H & L                    | n    | 0              | 0          | 1                       | 1    | 0                      | Ü  | 1  | 10               |

| ΑL                       | Rotate A left through carry                         | 0     | 0              | 0  | 1                        | 0   | 1    | 1   | 1              | 4                   | DAU H          | Add H & L to H & L                    | 0    | 0              | 1          | 11                      | 1    | O.                     | 0  | 1  | 10               |

| AR                       | Rotale A right through                              | 0     | 0              | 0  | -11                      | 11  | 1    | 1   | 1              | 4                   | DAD SP         | Add stack pointer to H & L            | 0    | U              | 1          | 1                       | 1    | 0                      | 0  | 1  | 10               |

|                          | carry                                               |       |                |    |                          |     |      |     |                |                     | STAXB          | Store A indirect                      | U    | 0              | 0          | 0                       | D    | 0                      | 1  | 0  | 1                |

| MP                       | Jump unconditional                                  | 1     | 1.             | 0  | Ü                        | ()  | 0    | 1   | 1              | 10                  | STAXD          | Store A indirect                      | 0    | ()             | 0          | 1                       | 0    | 0                      | 1  | 0  | 1                |

| C                        | Jump on carry                                       | 1     | 1              | 0  | 1                        | 1   | ()   | 1   | 0              | 10                  | LOAXB          | Load A indueci                        | 0    | 0              | 0          | 0                       | 1    | 0                      | 1  | 0  | 1                |

| VC.                      | Jump on no carry                                    | 1     | 1              | 0  | 1                        | ()  | ()   | 1   | 0              | 10                  | LOAXO          | Luad A indirect                       | 0    | 0              | 0          | 1                       | 1    | 0                      | 1  | 0  | 7                |

| 2                        | Jump on zero                                        | 1     | 1              | 0  | 0                        | 1   | 0    | 1   | 0              | 10                  | INXB           | Increment B & C registers             | 0    | 0              | 0          | O                       | 0    | 0                      | 1  | 1  | 5                |

| ٧Z                       | Jump on no zero                                     | 1     | 1              | 0  | 0                        | 0   | 0    | 1   | 0              | 10                  | INX D          | Increment D & E registers             | 0    | 0              | 0          | 1                       | 0    | U                      | 1  | 1  | 5                |

| )                        | Jump on positive                                    | 1     | 1              | 1  | 1                        | 0   | 0    | 1   | 0              | 10                  | INXH           | Increment H & L registers             | 0    | 0              | 1          | 0                       | 0    | 0                      | Ť  | i  | 5                |

| Л                        | Jump on minus                                       | 1     | 1              | 1  | 1                        | 1   | U    | 1   | 0              | 10                  | INXSP          | Increment stack puinter               | 0    | 0              | i          | ï                       | 0    | 0                      | i  | i  | 5                |

| E                        | Jump on parity even                                 | 1     | 1              | 1  | O.                       | 1   | 0    | 1   | 0              | 10                  | DCXB           | Decrement B & C                       | 0    | 0              | Ü          | 0                       | 1    | 0                      | 1  | i  | 5                |

| ,0                       | Jump on parity odd                                  | -1    | 1              | i  | 0                        | 0   | 0    | 1   | 0              | 10                  | DCXD           | Decrement D & E                       | 0    | 0              | 0          | i                       | 10   | 0                      | 1  | ì  | 5                |

| ALL                      | Call unconditional                                  | 3.0   | 1              | 0  | 0                        | 1   | 1    | 0   | 1              | 17                  | DCX H          | Decrement H & L                       | 0    | 0              | ñ          | n                       | 1    | 0                      | î  | 1  | 5                |

| C                        | Call on carry                                       | 1     | 1              | 0  | ĭ                        | 1   | i    | 0   | 0              | 11/17               | DCX SP         | Decrement stack pointer               | 0    | 0              | Š.         | 1                       | 1    | 0                      | 1  | i  | 5                |

| NC -                     | Call on no carry                                    | 1     | 1              | 0  | 1                        | 0   | i    | 0   | 0              | 11/17               | CMA            | Complement A                          | 0    | 0              | 1          | 0                       | 1    | 1                      | 1  | ,  | 4                |

| Z                        | Call on zero                                        | 1     | 1              | 0  | n                        | 1   | 1    | 0   | 0              | 11/17               |                |                                       |      | 0              | î          | 0                       | 0    |                        |    | 1  | 4                |

|                          |                                                     | 4     | 4              | 0  | 0                        | 'n  | 1    | ö   | 0              | 11/17               | STC            | Set carry                             | 0    |                | 1          |                         | ,    |                        |    | 1  | 4                |

| ١Z                       | Call on no zero                                     |       |                | 1  | 1                        | U.  | 1    |     | 0              |                     | CMC            | Complement carry                      | 0    | 0              | 4          |                         | n    |                        |    | 15 |                  |

|                          | Call on positive                                    | - 5   |                | 1  | 1                        | 0   | 1    | 0   |                | 11/17               | DAA            | Decimal adjust A                      | 0    | 0              | 1          | 0                       | 0    |                        | 1  | 1  | 4                |

| M<br>nr:                 | Call on minus                                       | - 3   |                | 1  | - 1                      | 1   | 1    | 0   | 0              | 11/17               | SHLD           | Store H & L direct                    | 0    | 0              | 1          | 0                       | 0    | 0                      | 1  | 8  | 16               |

| PE                       | Call on parity even                                 |       |                | 1  | 0                        | 1   | 1    | 0   | 0              | 11/17               | LHLD           | Load H & L direct                     | 0    | 0              | 3          | 0                       | 1    | 0                      | 1  | 0  | 16               |

| PO                       | Call on parity odd                                  | 1     | 1              | 1  | 0                        | 0   | 1    | 0   | 0              | 11/17               | EI             | Enable Interrupts                     | 1    | 1              | 1          |                         | 1    | 0                      | 1  | 1  | 4                |

| ET                       | Return                                              | 1     | 1              | 0  | 0                        | 1   | 0    | 0   | 1              | 10                  | D1             | Disable interrupt                     | 1    | 1              | 1          | 1                       | 0    | 0                      | 1  | 1  | 4                |

| C                        | Return on carry                                     | 1     | 1              | 0  | 1                        | 1   | 0    | 0   | 0              | 5/11                | NOP            | No-operation                          | 0    | 0              | 0          | 0                       | 0    | 0                      | 0  | 0  | 4                |

| NC                       | Return on no carry                                  | 1     | 1              | 0  | 1                        | 0   | ()   | 0   | 0              | 5/11                |                |                                       |      |                |            |                         |      |                        |    |    |                  |

NOTES: 1. DDD or SSS = 000 B = 001 C = 010 D = 011 E = 100 H = 101 L = 110 Memory = 111 A<sub>v</sub>

<sup>2.</sup> Two possible cycle times, (5/11) indicate instruction cycles dependent on condition flags.

```

FILE NAMES

INIT

STURE

REG1

REG2

ESTIM

SCAMU

FBIN

FLIM

FMOVE

FDIV

```

LIBRARY: NONE

MEMORY REQUIRED: 000:100 - 005:216

| LOAD MAP |         |

|----------|---------|

| INIT     | 000:100 |

| STURE    | 000:220 |

| REG1     | 000:353 |

| REG2     | 001:136 |

| ESTIM    | 001:312 |

| SCAMU    | 003:210 |

| FBIN     | 004:273 |

| FLIM     | 004:353 |

| FMOVE    | 005:001 |

| FDIV     | 005:045 |

| ADDA     | 005:160 |