Master's Thesis

### Hardware Architectures for the **Inverse Square Root and the Inverse Functions**

**Niclas Thuning** Leo Bärring

Department of Electrical and Information Technology, Faculty of Engineering, LTH, Lund University, 2016.

SIG

AIN

\*

1666

011000.51

Department of Electrical and Information Technology, Faculty of Engineering, LTH

MASTER OF SCIENCE THESIS

### Hardware Architectures for the Inverse Square Root and the Inverse Functions

using Harmonized Parabolic Synthesis

Authors: Niclas Thuning Leo Bärring Supervisors: Peter Nilsson Erik Hertz Rakesh Gangarajaiah

> **Examiner:** Fredrik Rusek

Lund, 17 Mar, 2016

The Department of Electrical and Information Technology Lund University Box 118, S-221 00 LUND SWEDEN This thesis is set in Computer Modern 11pt, with the IATEX Documentation System

© Niclas Thuning and Leo Bärring, 2016

#### Abstract

This thesis presents a comparison between implementations of the inverse square root function, using two approximation algorithms; Harmonized Parabolic Synthesis (HPS) and the Newton-Raphson Method (NR). The input is a 15 bit fixed-point number, the range of which is selected so that the implementation is suitable for use as a block implementing the inverse square root for floating-point numbers, and the designs are constrained by the error, which must be  $< 2^{-15}$ . Multiple implementations of both algorithms have been investigated and simulated as Application-Specific Integrated Circuits (ASIC) using ST Microelectronics 65.0nm Complementary Metal-Oxide Seminconductor (CMOS) technology libraries for Low Power (LP) and General Purpose (GP),  $V_{DD}$  levels of 1.00V and 1.10V, and for various clock speeds. Error distribution, area, speed, power, and energy consumption are analyzed for variants of the implementations of the two algorithms. Depending on how the properties rank in desirability, when choosing an implementation, the recommended choice will vary. The thesis finds that if mean error, and error distribution are important, the implementations of Harmonized Parabolic Synthesis show superiority regarding implementable clock speed, area requirements, power and energy consumption. If power and energy consumption is the most prioritised property, an implementation of the Newton-Raphson algorithm is promising, although at the cost of a worse error distribution.

### Acknowledgements

This thesis was possible thanks to our supervisors, Professor Peter Nilsson and Lic. Eng. Erik Hertz. We would like to express our deepest gratitude and respect to Peter and Erik for the guidance and help they have given us throughout the completion of this master thesis. We are glad to have had them as our supervisors and could not have asked for any better. Furthermore, we like to thank Rakesh Gangarajaiah for his help in getting us started with the synthesis tools, whose interfaces are anything but intuitive. The authors would also like to thank the Departement of Electrical and Information Technology, Lund University, for providing access to the software tools necessary for conducting the research presented in this thesis.

We like to thank Lars Bärring and Alana York for their contribution of proof reading the thesis and giving valuable inputs and corrections.

Niclas Thuning wants as well to thank his family and friends for their love and support while working on this thesis. He wants to express a very special appreciation to his beloved girlfriend Alana York, who loved and supported him throughout this work.

Leo Bärring thanks his family for all the love and support, both during times of doubt, as well as when everything mysteriously worked. C. Arabica deserves mention for being a good friend and a constant source of much needed energy.

#### Peter Nilsson

#### in memoriam

For being our supervisor through the ups and downs during this project, and teaching in courses we attended before that, we feel deep sorrow that he is not here to share our joy and pride of seeing this thesis finally being brought to completion.

# Contents

| Li            | st of | Figures                                            | xiii                   |

|---------------|-------|----------------------------------------------------|------------------------|

| $\mathbf{Li}$ | st of | Tables                                             | $\mathbf{x}\mathbf{v}$ |

| $\mathbf{Li}$ | st of | Acronyms                                           | xvi                    |

| 1             | Intr  | roduction                                          | 1                      |

| <b>2</b>      | Sco   | ре                                                 | 3                      |

| 3             | Har   | monized Parabolic Synthesis                        | <b>5</b>               |

|               | 3.1   | General Description                                | 5                      |

|               |       | 3.1.1 The First Sub-Function                       | 5                      |

|               |       | 3.1.2 The Second Sub-Function                      | 6                      |

|               |       | 3.1.3 Pre-Processing and Post-Processing Functions | 7                      |

| 4             | The   | e Newton-Raphson Method                            | 9                      |

|               | 4.1   | General Description                                | 9                      |

|               | 4.2   | Calculation of Look-Up Table                       | 10                     |

| <b>5</b>      | Err   | or Analysis Theory                                 | 13                     |

|               | 5.1   | Error Behavior Metrics                             | 13                     |

|               |       | 5.1.1 Maximum Error                                | 13                     |

|               |       | 5.1.2 Mean Error $\ldots$                          | 13                     |

|               |       | 5.1.3 Median Error $\ldots$                        | 13                     |

|               |       | 5.1.4 Standard Deviation                           | 14                     |

|               |       | 5.1.5 Root Mean Square Error                       | 14                     |

|               |       | 5.1.6 Skewness                                     | 15                     |

|               | 5.2   | Error Probability Distribution                     | 15                     |

|    | 5.3   | Bit Precision                                                                                                                                                 |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | Nur   | mber Representation 1                                                                                                                                         |

|    | 6.1   | Fixed-Point Numbers                                                                                                                                           |

|    | 6.2   | Floating-Point Numbers                                                                                                                                        |

|    |       | 6.2.1 Representation and the Inverse Square Root                                                                                                              |

| 7  | Cal   | culating the Inverse Square Root                                                                                                                              |

| •  | 7.1   | Harmonized Parabolic Synthesis                                                                                                                                |

|    | 7.2   | The Newton-Raphson Method                                                                                                                                     |

|    |       |                                                                                                                                                               |

| 8  |       | rdware Architecture 2                                                                                                                                         |

|    | 8.1   | Harmonized Parabolic Synthesis                                                                                                                                |

|    |       | 8.1.1 Pre-Processing                                                                                                                                          |

|    |       | 8.1.2 Processing (HPS) $\ldots \ldots \ldots$ |

|    |       | 8.1.3 Post-Processing                                                                                                                                         |

|    | 8.2   | The Newton-Raphson Method                                                                                                                                     |

| 9  | Imp   | blementation: Data Flow Design and Simulation                                                                                                                 |

|    | 9.1   | Harmonized Parabolic Synthesis                                                                                                                                |

|    |       | 9.1.1 Choosing $c_1$ and Interval Count $I$                                                                                                                   |

|    | 9.2   | The Newton-Raphson Method                                                                                                                                     |

|    |       | 9.2.1 Design Constraints                                                                                                                                      |

|    |       | 9.2.2 Data-Path Width                                                                                                                                         |

|    |       | 9.2.3 Optimization                                                                                                                                            |

| 10 | ) Imr | blementation: Hardware Design and Simulation 4                                                                                                                |

|    |       | VHDL                                                                                                                                                          |

|    |       | 10.1.1 Semi-Generic Multiplier                                                                                                                                |

|    |       | 10.1.2 Algorithm for Squaring Component - Jingou Lai                                                                                                          |

|    |       | 10.1.3 Pre-Processing                                                                                                                                         |

|    |       | 10.1.4 Post-Processing                                                                                                                                        |

|    |       | 10.1.5 Subtraction and Shift in the Newton-Raphson Method                                                                                                     |

|    |       | Implementation                                                                                                                                                |

|    | 10.2  | Synthesis                                                                                                                                                     |

|    |       | Placement and Routing                                                                                                                                         |

|    |       | Power Analysis                                                                                                                                                |

|    |       | Main Process Control Script                                                                                                                                   |

| 11 | Res   | ults                                                                                                                                                          |

| 11 |       | Data Flow Behavior                                                                                                                                            |

|    | 11.1  | 11.1.1 Harmonized Parabolic Synthesis                                                                                                                         |

|    |       | 11.1.1       Harmonized Farabolic Synthesis                                                                                                                   |

|    |       | 11.1.2 The new on naphson Method                                                                                                                              |

|    |      | 11.1.3 Comparision of Statistics                                              | 68  |

|----|------|-------------------------------------------------------------------------------|-----|

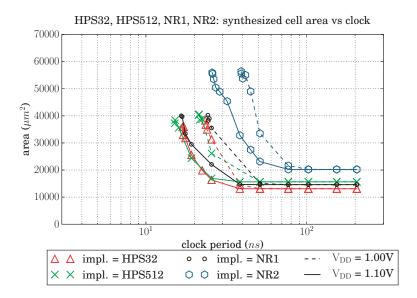

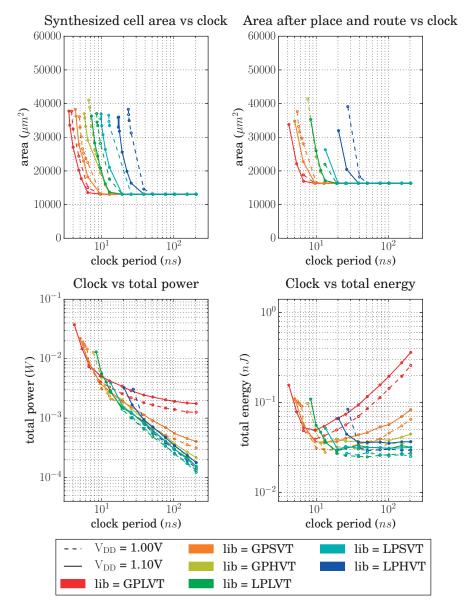

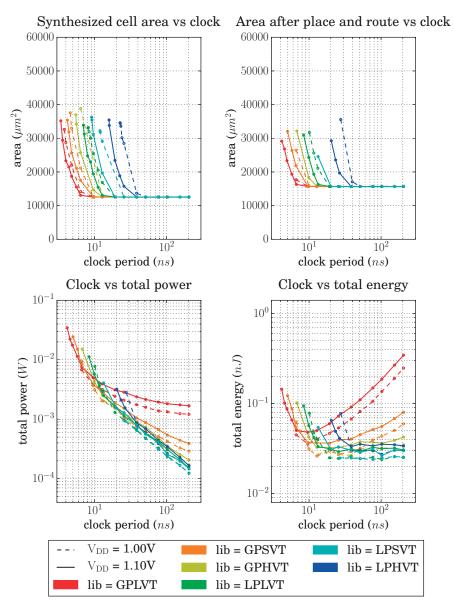

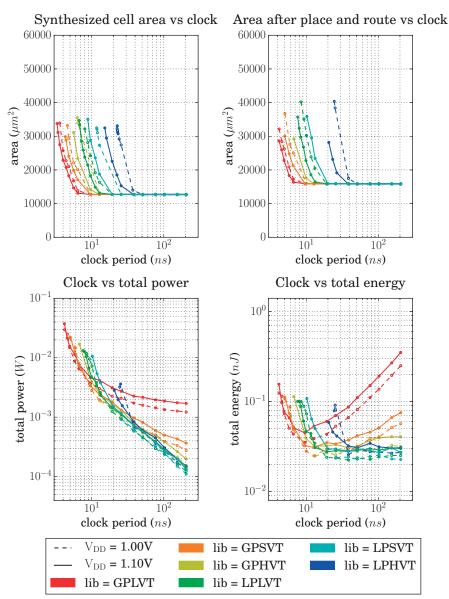

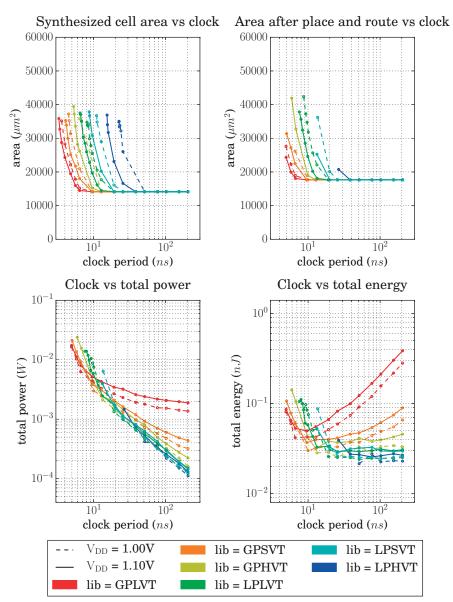

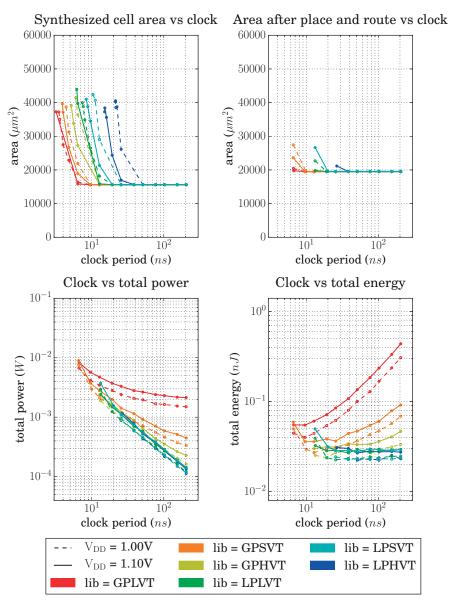

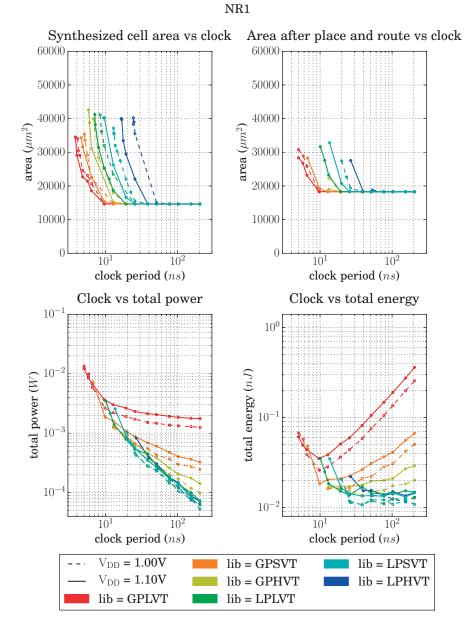

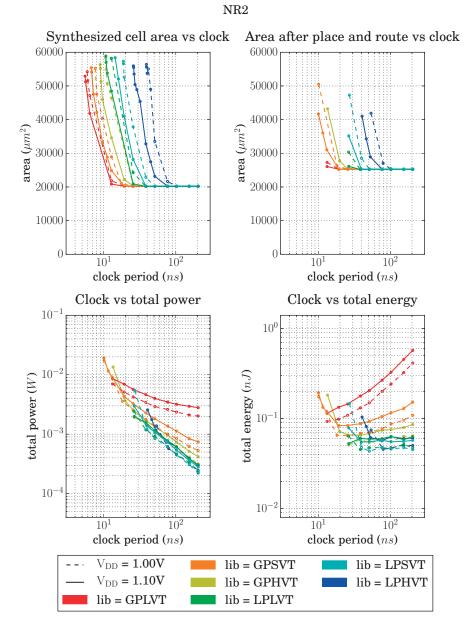

|    | 11.2 | Hardware Behavior                                                             | 70  |

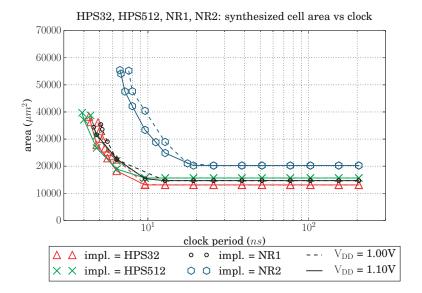

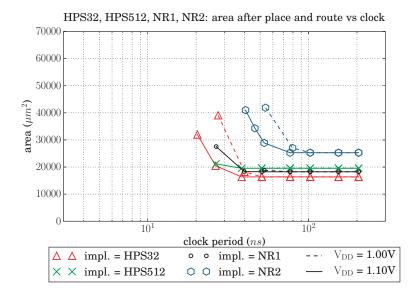

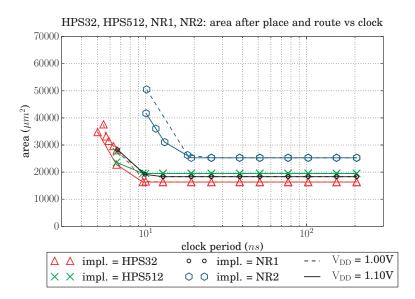

|    |      | 11.2.1 Clock Speed and Area                                                   | 71  |

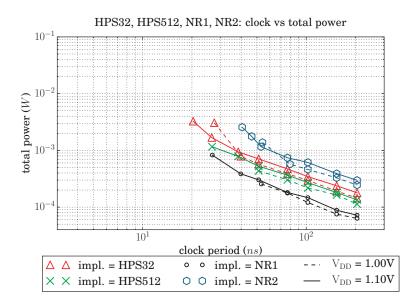

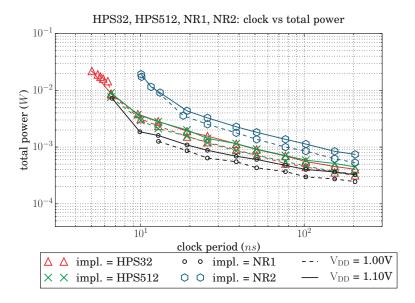

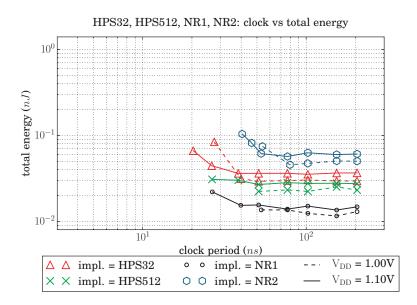

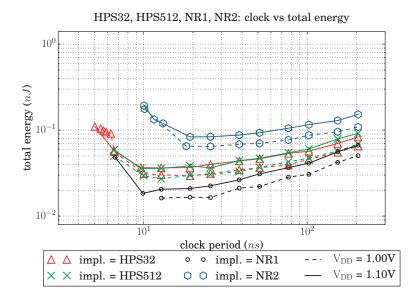

|    |      | 11.2.2 Power and Energy                                                       | 75  |

| 12 | Con  | clusions                                                                      | 83  |

|    | 12.1 | Future Work                                                                   | 84  |

| A  | App  | endix                                                                         | 91  |

|    | A.1  | Look-up Tables for the NR Method                                              | 91  |

|    | A.2  | HPS Dataflow Simulation                                                       | 96  |

|    |      | A.2.1 Elaboration of Software Development                                     | 96  |

|    |      | A.2.2 Error Behaviour of Additional HPS Implementa-                           |     |

|    |      | tions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 98  |

|    | A.3  | Extra Hardware Behaviour Plots                                                | 100 |

|    | A.4  | Extra Hardware Behaviour Tables                                               | 107 |

|    |      | A.4.1 Clock and Area                                                          | 107 |

|    |      | A.4.2 Power and Energy                                                        | 110 |

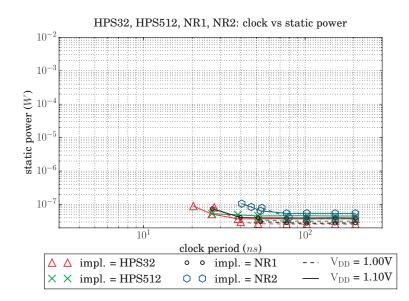

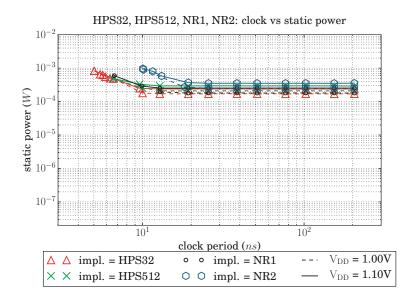

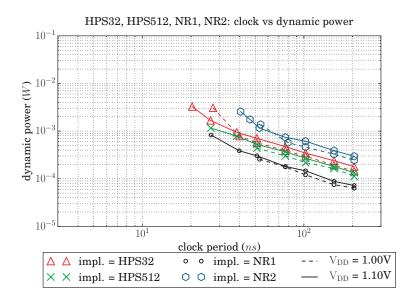

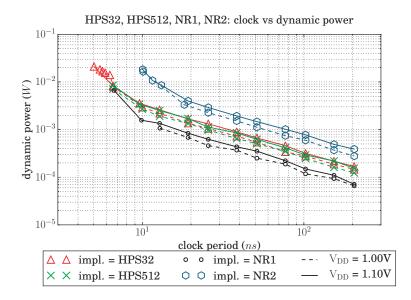

|    | A.5  | Static and Dynamic Power Plots                                                | 112 |

|    | A.6  | Tool Control Scripts                                                          | 114 |

|    |      | A.6.1 Synthesis Script                                                        | 114 |

|    |      | A.6.2 Static Timing Analysis Script                                           | 115 |

|    |      | A.6.3 Placement and Routing Script                                            | 115 |

|    |      | A.6.4 Power Analysis Script                                                   | 118 |

### Preface

This thesis is written by Niclas Thuning and Leo Bärring for the Department of Electrical and Information Technology, Faculty of Engineering, Lund University. Niclas and Leo are both students in the Master of Science in Electrical Engineering Program with the specialization Design of Processors and Embedded Systems. This thesis is an admission for the degree of Master of Science.

For this thesis paper, most of the work has been divided between the two authors. The individual contributions and collaborations between the authors are as follows.

Niclas Thuning has written the chapter on the Newton-Raphson Method and all sections concerning the Newton-Raphson Method. Furthermore, Niclas Thuning has written the Introduction, Error Analysis Theory (apart from Skewness and Bit Precision) and Implementation: Hardware Design and Simulation (apart from Semi-Generic Multiplier and Main Process Control Script).

Leo Bärring has written the chapters on Harmonized Parabolic Synthesis and all sections concerning Harmonized Parabolic Synthesis. Leo has also written the Skewness part of Error Analysis Theory, Number Representation, Calculating the Inverse Square Root, and Main Process Control Script. Furthermore, Leo has done the final versions of the graphics and the generated plots for this thesis.

The two authors have through collaboration written the chapters/sections, Abstract, Preface, Acknowledgments, Scope, Bit Precision, Results, Semi-Generic Multiplier, Conclusions and Appendix, as well as discussed and collaborated on improving sentence structure, phrasing, and word choice, as needed throughout the thesis, regardless of the original author of the part.

# List of Figures

| 2.1   | Overview of the architectures                                      | 4  |

|-------|--------------------------------------------------------------------|----|

| 4.1   | Example of a 9 entry LUT                                           | 11 |

| 4.2   | Example of an improved 9 entry LUT                                 | 12 |

| 5.1   | Example histogram                                                  | 15 |

| 8.1   | A bird's eye of HPS                                                | 27 |

| 8.2   | The pre-processing Function                                        | 28 |

| 8.3   | The processing/HPS function                                        | 28 |

| 8.4   | The post-processing Function                                       | 29 |

| 8.5   | Unrolled Newton-Raphson architecture                               | 30 |

| 9.1   | Plot of $c_1$ and interval count effect on maximum error $\cdot$ . | 33 |

| 9.2   | The implementation architecture of HPS                             | 34 |

| 9.3   | The architecture for 1 iteration NR                                | 39 |

| 9.4   | The architecture for 2 iterations NR                               | 40 |

| 9.5   | Bit precision for 1 iteration with horizontal line                 | 41 |

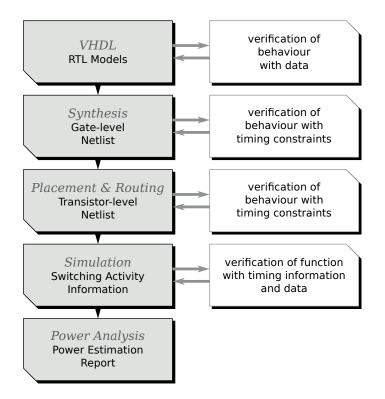

| 10.1  | Hardware design workflow                                           | 44 |

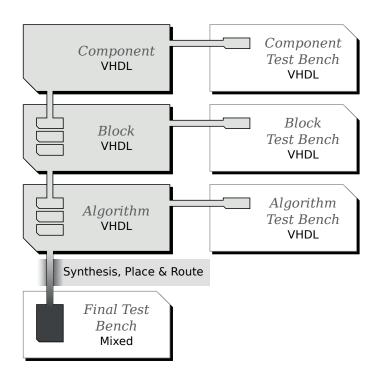

|       | VHDL development workflow                                          | 45 |

|       | The real RTL design with flip-flop.                                | 45 |

| 10.4  | 3x3 multiplier for one negative and one positive number            | 48 |

|       | Final design of the pre-processing subtraction                     | 49 |

| 10.6  | Post-processing addition of one                                    | 51 |

| 10.7  | Final design of post-processing.                                   | 52 |

| 10.8  | Basic design of subtraction and shift                              | 52 |

| 10.9  | Subtraction and shift with HA where possible                       | 53 |

|       | OSubtraction and shift further simplified                          | 53 |

| 10.11 | 1Synthesis flow.                                                   | 55 |

| 10.12STA flow                                                   | 57  |

|-----------------------------------------------------------------|-----|

| 10.13Placement and routing flow                                 | 58  |

| 10.14Power analysis flow.                                       | 60  |

| v                                                               |     |

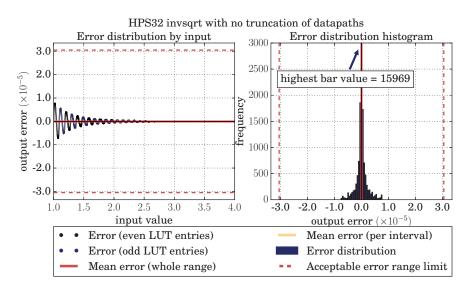

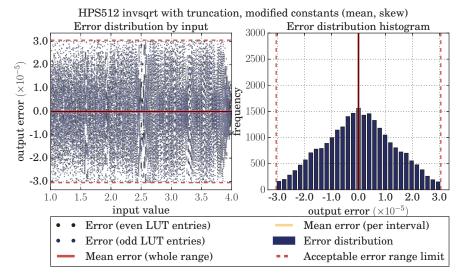

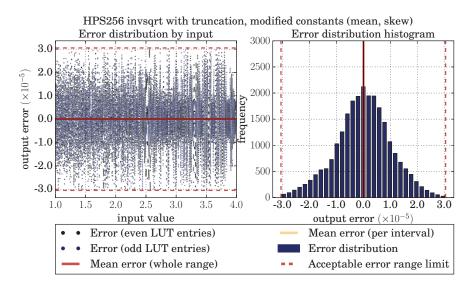

| 11.1 Error behaviour for 32 interval unconstrained HPS $\ldots$ | 64  |

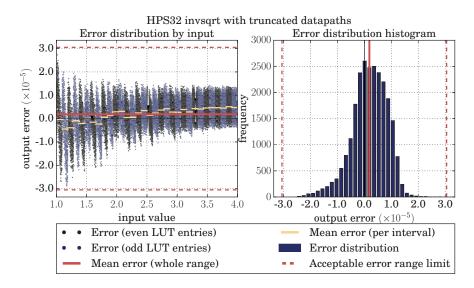

| 11.2 Error behaviour for 32 interval truncated HPS              | 65  |

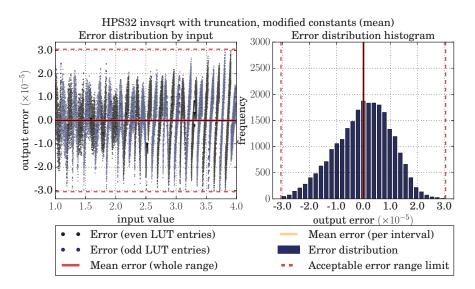

| 11.3 Error behaviour for 32 interval modified HPS               | 65  |

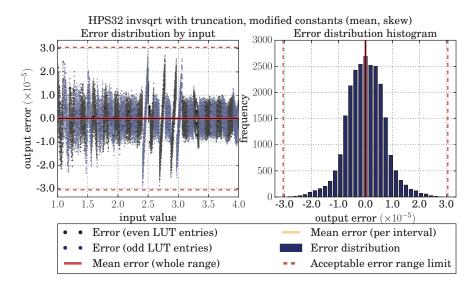

| 11.4 Error behaviour for 32 interval further modified HPS       | 66  |

| 11.5 Error behaviour for 512 interval further modified HPS .    | 66  |

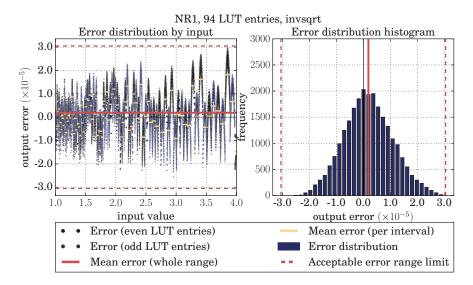

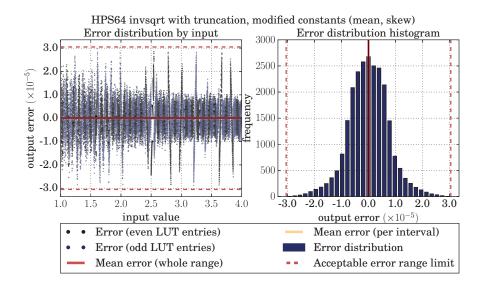

| 11.6 Error behaviour for 1 iteration, 94 interval NR            | 67  |

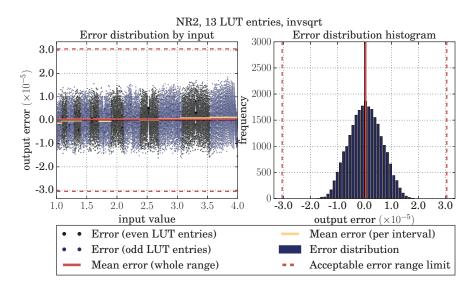

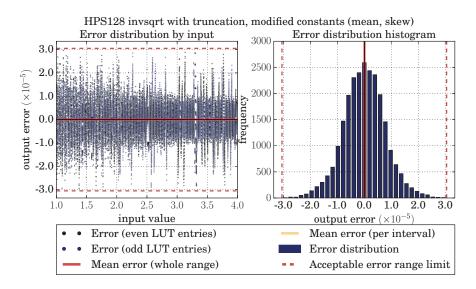

| 11.7 Error behaviour for 2 iteration, 14 interval NR            | 68  |

| 11.8 Synthesized clock and area results for LPHVT implemen-     | 00  |

| tations                                                         | 72  |

| 11.9 Synthesized clock and area results for GPSVT implemen-     | 12  |

|                                                                 | 72  |

| tations                                                         |     |

| 11.10PNR clock and area results for LPHVT implementations       | 73  |

| 11.11PNR clock and area results for GPSVT implementations       | 73  |

| 11.12Power consumption results for LPHVT implementations        | 78  |

| 11.13Power consumption results for GPSVT implementations        | 78  |

| 11.14Energy consumption results for LPHVT implementations       | 80  |

| 11.15Energy consumption results for GPSVT implementations       | 80  |

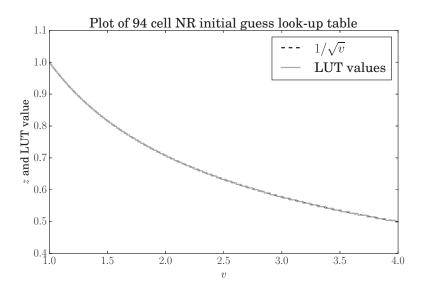

| A.1 Plot of 1 iteration, 94 interval NR look-up table           | 94  |

|                                                                 |     |

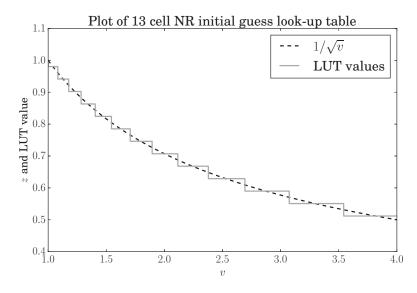

| A.2 Plot of 2 iteration, 14 interval NR look-up table           | 95  |

| A.3 Error behaviour for 64 interval further modified HPS        | 98  |

| A.4 Error behaviour for 128 interval further modified HPS .     | 99  |

| A.5 Error behaviour for 256 interval further modified HPS .     | 99  |

|                                                                 | 100 |

|                                                                 | 101 |

| A.8 Hardware results for all 128 interval HPS implementations   |     |

| A.9 Hardware results for all 256 interval HPS implementations   | 103 |

| A.10 Hardware results for all 512 interval HPS implementations  | 104 |

| A.11 Hardware results for all 1 iteration NR implementations    | 105 |

| A.12 Hardware results for all 2 iteration NR implementations    | 106 |

| A.13 Static power consumption for implementations using the     |     |

|                                                                 | 112 |

| A.14 Static power consumption for implementations using the     |     |

|                                                                 | 112 |

| A.15 Dynamic power consumption for implementations using        |     |

|                                                                 | 113 |

| A.16 Dynamic power consumption for implementations using        | 0   |

|                                                                 | 113 |

| the GLOVI technology notary.                                    | ттЭ |

## List of Tables

| 9.1  | HPS data-path widths                                       | 35  |

|------|------------------------------------------------------------|-----|

| 9.2  | Comparision of bit precision of floating-point NR variants | 36  |

| 9.3  | Comparision of bit precision of fixed-point NR variants .  | 37  |

| 9.4  | Bit precision of selected NR variants                      | 39  |

| 9.5  | NR data-path widths                                        | 40  |

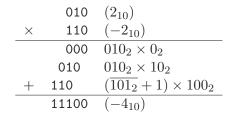

| 10.1 | Simple binary multiplication                               | 46  |

| 10.2 | Binary multiplication modified for one negative input      | 47  |

| 10.3 | Truth table for pre-processing subtraction                 | 49  |

| 10.4 | Truth table for post-processing                            | 50  |

| 11.1 | Error metrics from simulations                             | 69  |

|      | Error metrics from simulations in bits                     | 69  |

|      | Fastest synthesized clock for various implementations.     | 74  |

|      | Fastest PNR clock for various implementations.             | 75  |

|      | Lowest PNR area for various implementations.               | 75  |

|      | Lowest power consumption for various implementations       | 81  |

| 11.7 | Lowest energy consumption for various implementations      | 81  |

| A.1  | LUT values for 1-iteration NR                              | 94  |

| A.2  | LUT values for 2-iteration NR                              | 95  |

| A.3  | Fastest synthesized clocks of all implementations          | 107 |

| A.4  | Fastest PNR clocks of all implementations.                 | 108 |

| A.5  | Lowest PNR areas of all implementations.                   | 109 |

| A.6  | Lowest power consumption of all implementations            | 110 |

| A.7  | Lowest energy consumption of all implementations           | 111 |

|      |                                                            |     |

# List of Acronyms

| ASIC                 | Application-Specific Integrated Circuit           |

|----------------------|---------------------------------------------------|

| CMOS                 | Complementary Metal-Oxide Seminconductor          |

| dB                   | Decibel                                           |

| DRC                  | Design Rule Check                                 |

| DSP                  | Digital Signal Processing                         |

| FA                   | Full Adder                                        |

| GPHVI                | C General Purpose High Threshold Voltage          |

| GPLVT                | General Purpose Low Threshold Voltage             |

| GPSVT                | General Purpose Standard Threshold Voltage        |

| $\operatorname{GPU}$ | Graphic Processing Unit                           |

| HA                   | Half Adder                                        |

| HPS                  | Harmonized Parabolic Synthesis                    |

| IC                   | Integrated Circuit                                |

| IEEE                 | Institute of Electrical and Electronics Engineers |

| LPHVT                | Low Power High Threshold Voltage                  |

| LPLVT                | Low Power Low Threshold Voltage                   |

| LPSVT                | Low Power Standard Threshold Voltage              |

| LSB                  | Least Significant Bit                             |

|                      |                                                   |

- LUT Look-up Table

- **MSB** Most Significant Bit

- **NR** the Newton-Raphson Method

- **PNR** Placement and Routing

- **RMS** Root Mean Square

- **RTL** Resistor Transistor Logic

- **SD** Standard Deviation

- **SDC** Synopsys Design Constraints

- **SDF** Standard Delay Format

- **SNR** Signal-to-Noise Ratio

- SPEF Standard Parasitic Exchange Format

- **STA** Static Timing Analysis

- VCD Value Change Dump

- **VHDL** Very High Speed Integrated Circuit Hardware Description Language

Chapter

### Introduction

Unary functions, like logarithm, exponential, trigonometric functions, and the square root, are examples of widely used building blocks in more complex algorithms. These unary functions can, for example, be found in applications in the fields of wireless communication, Digital Signal Processing (DSP), Graphic Processing Units (GPU), etc [1].

Performance improvement for algorithms using software solutions is not always sufficient. Although software can compute with extreme accuracy, implementing algorithms in terms of sequences of simpler processor instructions is sometimes not fast enough for high speed and/or numerically intensive applications. In order to improve the performance, the algorithms can be implemented directly into hardware [1].

This thesis will investigate an algorithm called Harmonized Parabolic Synthesis to compute the inverse square root, proposed by Erik Hertz and Peter Nilsson [2]. As comparison, the Newton-Raphson Method algorithm is used.

Inverse square root is essential for normalizing a vector in linear algebra. A normalized vector, or unit vector  $\hat{v}$ , is calculated as shown in (1.1) [3, pp. 131–192].

$$\hat{\boldsymbol{v}} = \frac{1}{|\boldsymbol{v}|} \boldsymbol{v} \tag{1.1}$$

where  $|\boldsymbol{v}|$  is the norm calculated as  $\sqrt{v_1^2 + v_2^2 + \ldots + v_n^2}$  (with  $v_i$  being vector component in each dimension).

Unit vectors are crucial e.g. when calculating reflections, used e.g. in 3D graphics rendering code used by the gaming industry and when constructing graphic design tools. An increased speed of computation can mean either faster rendering, or rendering with higher precision [4].

### Scope

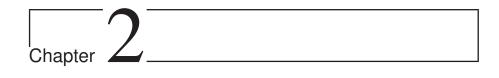

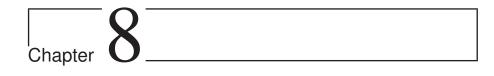

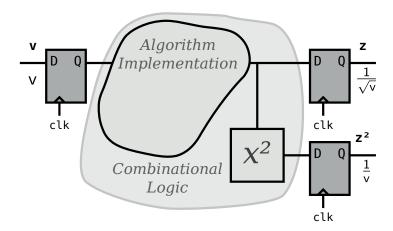

The objective of this project is to design and implement an inverse square root function and an inverse function using Harmonized Parabolic Synthesis and compare it with the Newton-Raphson Method with iterations unrolled in hardware. The implementations are required to be able to process input inputs  $v \in [1, 4)$  represented with 15 bits precision in fixed-point format. The output  $z = 1/\sqrt{v}$  is required to have 15 bits precision or better, as well as the output being *exactly* 1 when the input equals 1. The second output, the inverse function  $z^2 = 1/v$  is not subject to any precision constraints. There is also a goal to have a balanced error probability distribution. Figure 2.1 shows the basic implementation architecture for the two designs.

The designs are simulated and compared for accuracy, error behavior, power consumption, and performance. For power consumption, both static and dynamic power consumption are estimated. The core area of the implementations are estimated as well. Physical layouts of the designs are synthesized.

The hardware implementation is written in Very High Speed Integrated Circuit Hardware Description Language (VHDL) and synthesized with different clock frequencies, library technologies, supply voltage and threshold voltage. The library technologies used are ST Microelectronics 65.0nm CMOS and the following variants are examined.

- Low Power Low  $V_t$  (LPLVT)

- Low Power Standard  $V_t$  (LPSVT)

- Low Power High  $V_t$  (LPHVT)

- General Purpose Low  $V_t$  (GPLVT)

- General Purpose Standard  $V_t$  (GPSVT)

- General Purpose High  $V_t$  (GPHVT)

The results of this report will focus on General Purpose Standard  $V_t$  and General Purpose High  $V_t$ , with additional results in the appendix section. For each library, two different supply voltages are used: 1.00V and 1.10V.

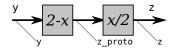

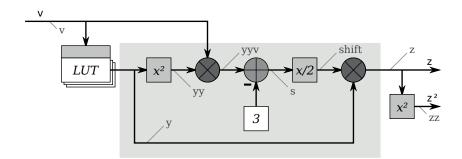

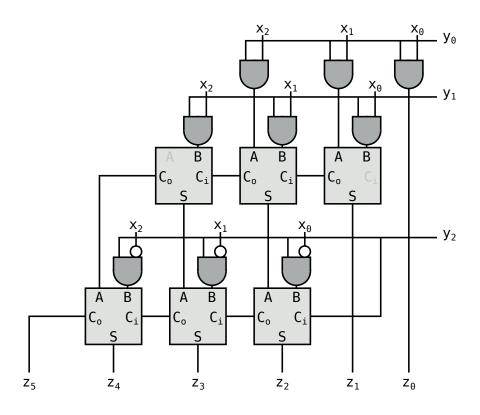

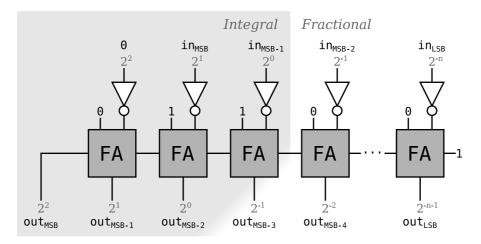

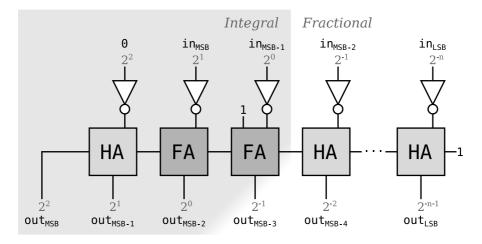

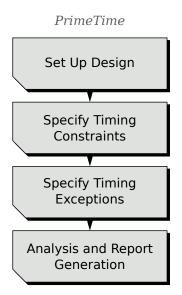

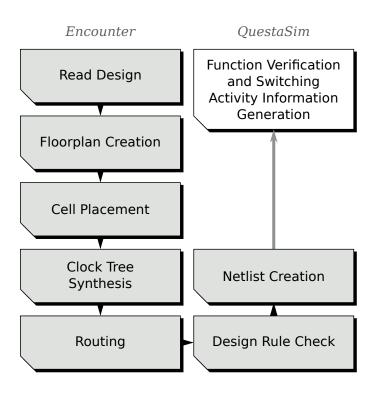

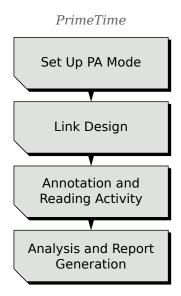

(a) Harmonized Parabolic Synthesis (b)

(b) The Newton-Raphson Method

Figure 2.1: Overview of the architecture implementing the inverse square root and inverse function with Harmonized Parabolic Synthesis (a) and the Newton-Raphson Method (b). Chapter 3\_

### Harmonized Parabolic Synthesis

#### 3.1 General Description

The Harmonized Parabolic Synthesis (HPS)[5] algorithm approximates a function  $y = f_{org}(x)$ . To facilitate development, the range of x, as well as the allowed range of y is constrained to [0, 1]. If there is a need to approximate a different range, the input and/or output will need conditioning, with corresponding changes to the  $f_{org}(x)$  function.

The approximation of  $f_{org}(x)$  is calculated as the product of two sub-functions  $s_1(x)$  and  $s_2(x)$ , (see (3.1)) where the first sub-function,  $s_1(x)$ , is a second order polynomial and the second sub-function,  $s_2(x)$ , is a second order interpolation.

$$f_{org}(x) \approx s_1(x)s_2(x) \tag{3.1}$$

#### 3.1.1 The First Sub-Function

The first sub-function  $s_1(x)$ , shown in (3.2) and coefficients are chosen to roughly approximate  $f_{org}(x)$ .

$$s_1(x) = l_1 + k_1 x + c_1(x - x^2)$$

(3.2)

If possible,  $s_1(x)$  is constructed so that it intersects (0;0) and (1;1), or (0;1) and (1;0), which allows the expression to be simplified to one out of the ones shown in (3.3), by way of setting  $l_1 = 0$  and  $k_1 = 1$ , or  $l_1 = 1$  and  $k_1 = -1$ .

$$s_1(x) = x + c_1(x - x^2)$$

(3.3a)

$$s_1(x) = 1 - x + c_1(x - x^2)$$

(3.3b)

Which particular variant of  $s_1$  to use depends on the shape of the function to be approximated. The constant  $c_1$  remains unassigned so far and a suitable value has to be determined experimentally.

#### 3.1.2 The Second Sub-Function

The second sub-function,  $s_2(x)$  which improves on the approximation in  $s_1(x)$ , is a second order interpolation of  $f_{help}(x)$ , which is defined in (3.4).

$$f_{help}(x) = \frac{f_{org}(x)}{s_1(x)} \tag{3.4}$$

Splitting  $f_{help}(x)$  into I intervals yields a set of equations shown in (3.5), where i is the interval index  $0 \le i < I$ , and  $x_w$  linearly increases from 0 to 1 over each interval.

$$s_{2,i}(x) = l_{2,i} + k_{2,i}x_w + c_{2,i}(x_w - x_w^2)$$

(3.5)

Assuming that the intervals are chosen to be of equal size, the interval index i can be calculated by extracting the integral part of Ix, i.e. by truncating Ix towards zero. Conversely  $x_w$  can be calculated by taking the fractional part of Ix.

Calculation of the coefficients of the  $s_2(x)$  polynomials in each interval is shown in (3.6), and is based on the fact that the polynomial is chosen to intersect  $f_{help}(x)$  in the beginning, middle, and end of each interval, where  $x_w$  takes on the values 0, 0.5, and 1 respectively.

$$x_{start,i} = i/I$$

$$x_{mid,i} = (i+0.5)/I$$

$$x_{end,i} = (i+1)/I$$

$$l_{2,i} = f_{help}(x_{start,i})$$

$$k_{2,i} = f_{help}(x_{end,i}) - l_{2,i}$$

$$c_{2,i} = -4f_{help}(x_{mid,i}) - 4l_{2,i} - 2k_{2,i}$$

(3.6)

Due to its role as a divisor in  $f_{help}(x)$ , it is necessary to make sure that for any x in the interval where  $s_1(x) = 0$  there exists a limit value in  $f_{help}(x)$ . If choosing (3.3a), the zero occurrs at x = 0, and directly affects how the constant  $l_{2,0}$  is calculated. In case of (3.3b) being the chosen form of  $s_1(x)$ , the zero occurrs at x = 1, and special care has to be taken when calculating the value of the constant  $k_{2,I-1}$ . The limits that have to be calculated in either case, and their associated constants, are shown in (3.7). It is imperative that the limit exists for the implementation to be feasible.

$$l_{2,0} = \lim_{x \to 0} f_{help}(x)$$

(3.7a)

$$k_{2,I-1} = \lim_{x \to 1} f_{help}(x) - l_{2,I-1}$$

(3.7b)

Furthermore, there will be a second zero in either  $x = 1 + 1/c_1$  (using  $s_1$  from 3.3a), or  $x = -1/c_1$  (using 3.3b), for which  $f_{help}(x)$  may have no limit, in which case care has to be taken when choosing a value for  $c_1$ , so that the zero does not appear in the range  $x \in [0, 1]$ .

At this point, the method to calculate all constants in the second sub-function has been shown. The number of intervals I remains as an implementation detail.

#### 3.1.3 Pre-Processing and Post-Processing Functions

As mentioned in the introduction to this chapter, when implementing an approximation of a function with an arbitrary input and output range, such as the one shown in (3.8), additional functions may be needed in order to bring input to the working domain of the algorithm, as well as bringing the algorithm output from the algorithm domain, to the output range of the approximated function [6].

$$z = f(v) \tag{3.8}$$

The pre-processing and post-processing, as declared in (3.9), are used to translate between whatever ranges are desired, and the [0, 1] range required by the implementation of  $f_{org}(x)$  that is to be approximated.

$$x = f_{pre}(v)$$

$$z = f_{post}(y)$$

(3.9)

The overall expression then becomes as in (3.10), with the second variant written with  $\circ$  denoting function composition (meaning that  $(g \circ f)(x) = g(f(x))$ ).

$$z = f_{post}(f_{org}(f_{pre}(v)))$$

$$z = (f_{post} \circ f_{org} \circ f_{pre})(x)$$

(3.10)

This arrangement makes it necessary to choose  $f_{org}(x)$  so that it compensates the effect that the pre- and post-processing functions have on the overall expression, i.e. so that the (ideal) approximation matches the function in (3.8). This can be done by including the inverses of the pre- and post-processing functions in the definition of  $f_{org}(x)$ , as shown in (3.11), where z = f(v) is the unconstrained function in (3.8).

$$f_{org}(x) = (f_{post}^{-1} \circ f \circ f_{pre}^{-1})(x)$$

(3.11)

Doing this, the overall expression will compose the pre- and postprocessing functions with their corresponding inverses, which makes them equal to the identity function  $(f_{id}(x) = x)$ , and makes it possible to eliminate them from the expression. This is shown in (3.12).

$$f(v) = (f_{post} \circ f_{org} \circ f_{pre})(v)$$

=  $(f_{post} \circ f_{post}^{-1} \circ f \circ f_{pre}^{-1} \circ f_{pre})(v)$

=  $(f_{id} \circ f \circ f_{id})(v)$

=  $f(v)$  (3.12)

At this stage, the definition of  $f_{org}(x)$  in terms of the function to be approximated (f(v)), and the pre- and post-processing functions, is clear and the search for suitable sub-functions can begin.

Two unknowns remain: the constant  $c_1$  from the first sub-function, and the number of intervals, I, to use in the second sub-function. Both affect the complexity of a hardware implementation directly, as well as indirectly, by influencing error behaviour, and thus influencing what further constraints can be placed on the data paths. Suitable values have to be determined by e.g. simulation on a case-by-case basis.

### The Newton-Raphson Method

#### 4.1 General Description

One method to find a root of an arbitrary function f(x) = 0 numerically is the Newton-Raphson method (NR) [7], named after Isaac Newton and Joseph Raphson. The objective of this method is to successively find a more accurate approximation by iteration. It starts from a presupplied approximate answer (initial guess) and then iterates until a sufficiently close approximation is reached. The general form of an iteration of NR is given in the formula shown in (4.1) [8, pp. 393].

$$x_{i} = x_{i-1} - \frac{f(x_{i-1})}{f'(x_{i-1})}$$

for  $i = 1, 2...$

where  $x_{0}$  is the initial guess. (4.1)

For each iteration,  $x_i$  closes in on the sought value x. For the derivative in (4.1) the condition of  $f'(x) \neq 0$  must be met.

In order to use NR to calculate an arbitrary function y = g(v), the expression for which a root has to be calculated can be written as  $f(y) = g^{-1}(y) - v$ . A concrete example for the function  $g(v) = \frac{1}{v}$  is given in (4.2) and (4.3).

$$y = g(v) = \frac{1}{v} \quad \Rightarrow \quad v = g^{-1}(y) = \frac{1}{y}$$

$$f(y) = \frac{1}{y} - v$$

$$f'(y) = -\frac{1}{y^2}$$

(4.2)

$$y_{i} = y_{i-1} - \frac{\frac{1}{y_{i-1}} - v}{-\frac{1}{y_{i-1}^{2}}}$$

$$y_{i} = 2y_{i-1} - vz_{i-1}^{2}$$

(4.3)

The final expression in (4.3) uses no division and can be implemented effectively in hardware to use as an approximation for the division function together with a suitable initial guess  $z_0$ . The number of iterations required would depend on the error of the initial guess and the required precision of the answer. There are functions and cases where NR may not converge as well, although they are outside the scope of this report.

#### 4.2 Calculation of Look-Up Table

In order to increase the speed of the NR convergence, the initial guess should be as close as possible to the actual result. If the guess is too far away from the result, either more iterations or more initial guesses will be needed. For many initial guesses, a Look-Up Table (LUT) is preferable.

To keep the area of the LUT at a minimum, the number of stored values and the width of the data paths of said values should be kept as low as possible. A good trade-off between the number of iterations and the number of stored values is important.

Fewer iterations will require a bigger LUT with more initial guesses, in order to keep the error small and the answer within a given bit precision, Inversely, a smaller LUT will require more iterations in order to keep the precision.

More iterations in an unrolled architecture require more hardware and will increase area and latency, however, the size of the LUT will also increase area and latency. It is not known beforehand if a smaller LUT will compensate for higher amount of iterations and vice versa.

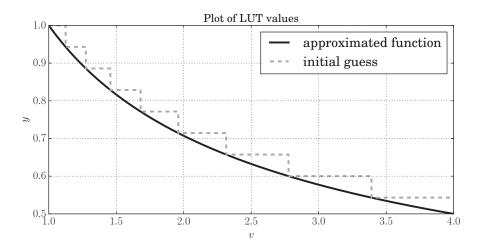

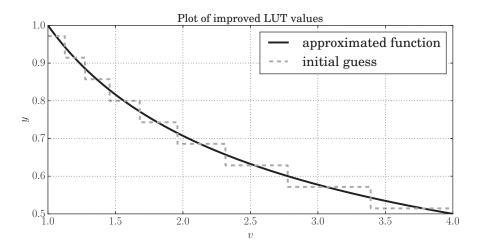

For the inverse square root function, an algorithm for finding an adequate initial guess has been made. More initial guesses will be needed closer to the y-axis due to the greater down slope. By using an algorithm which calculates the same maximal distance from the actual result for each initial guess throughout the function, a more even approximation will be computed for NR. Figure 4.1 is an example of how the LUT will be represented over the input v. The LUT is the plot which resembles a staircase. Each step is an initial guess over a certain range in v.

The algorithm works by setting the number of values wanted in the LUT, afterwards the algorithm will calculate the placement for each

Figure 4.1: Example of a look-up table with 9 entries for the Newton-Raphson Method.

initial value so the maximum distance to the function is the same for all values. By doing this, the height between each initial value will be the same. The beginning of the input value range (x-axis) for the LUT is at the intersection of the guess and the approximated function, and the range ends at the beginning of the next LUT entry range, see (4.4).

LUT length

$$\Delta x = x_1 - x_2 = \frac{1}{y_1^2} - \frac{1}{y_2^2}$$

(4.4)

Where  $y_1$  is the start of the LUT in y-axes and  $y_2$  is the start of the next LUT in y-axes minus one bit resolution.

Another method to decrease the errors originating from the initial values is to halve the maximum distance between the values in the LUT and the function. If the values of the LUT is lowering half its height in the *y*-axis, the interception of the inverse square function will be in the middle of the LUT and not in the beginning as in in Fig. 4.1. By doing this, the initial guess will be closer to the actual result as represented in Fig. 4.2.

By comparing Fig. 4.1 and Fig. 4.2, it can be seen that the gap between the initial guess and the actual value is smaller in Fig. 4.2. The longest distance between the initial guess and the actual value is cut in half in Fig. 4.2. Therefore, the method for choosing the initial values will be the one shown in Fig. 4.2.

There is another method when choosing the initial values in the LUT. Instead of first choosing initial values and then truncating the data-

Figure 4.2: Representation of an improved 9 entry Look-Up Table for the Newton-Raphson Method

path widths, a reverse method should be possible, where the truncations are done first, and then the initial values are calculated. The idea is to choose a starting point below the function that is just inside the acceptable error range. As the function decreases, the absolute error goes toward zero, and then increases again. When the error goes outside the acceptable limit, a new interval with a new constant is created.

This method was found to be difficult to use. Input signals next (or near) to each other can give different bit precision, were the one closer to the real value can show a bit precision outside the maximum bit precision and the other one inside.

### Error Analysis Theory

To evaluate the error behavior, a number of five methods is used to analyze the two approximation models (the Newton-Raphson Method and Harmonized Parabolic Synthesis), maximum error, mean error, median error, Standard Deviation (SD) and Root Mean Square (RMS) [9].

#### 5.1 Error Behavior Metrics

#### 5.1.1 Maximum Error

The maximum error  $e_{\text{max}}$  is the absolute value of the biggest error between the approximation result  $\hat{x}_i$  and the ideal result  $x_i$ .

$$e_{\max} = \max |e_i| = \max |\hat{x}_i - x_i|$$

(5.1)

#### 5.1.2 Mean Error

The mean error  $\bar{e}$  is the average error between the approximation value  $\hat{x}_i$  and the real value  $x_i$ .

$$\bar{e} = \frac{1}{n} \sum_{i=1}^{n} e_i = \frac{1}{n} \sum_{i=1}^{n} (\hat{x}_i - x_i)$$

(5.2)

where n is the number of samples.

#### 5.1.3 Median Error

When calculating the median error, a sorted list of all errors have to be created, which can be costly. The median error is the sample found in the center of the sorted list. To calculate the median error there are two cases depending on if the numbers of samples is odd or even, see (5.3). If there is a large difference between the median and the mean error, then it is likely that there is a large number of errors placed closely to the mean on one side, and a large outlier on the other side of the mean, skewing the distribution.

$$e_{\text{median}} = \begin{cases} e_{(n+1)/2} & \text{if } n \text{ is odd} \\ \frac{1}{2}(e_{(n+1)/2} + e_{n/2}) & \text{if } n \text{ is even} \\ & \text{where } e \text{ is a sorted list of errors,} \\ & \text{and assuming 1-based indexing.} \end{cases}$$

(5.3)

#### 5.1.4 Standard Deviation

Standard Deviation  $\sigma$  is used to see the dispersion around the mean. A small standard deviation indicates that the samples tend to lie close to the mean. If the standard deviation is high, this indicates that the samples are spread over a wide range. Equation (5.4) shows how to calculate the standard deviation.

$$\sigma = \sqrt{\frac{1}{n} \sum_{i=1}^{n} (e_i - \bar{e})^2}$$

(5.4)

#### 5.1.5 Root Mean Square Error

The root mean square error, shown in (5.5), gives a measure on how far the error is from 0 on average. The root mean square error differs from the mean error in that two values, of equal magnitude but different sign would have a zero mean, but nonzero root mean square. The main difference between the standard deviation of the error, and the root mean square error is that the size of the mean error has no effect on the standard deviation, but may show up on the root mean square error. If the mean error is small, the difference between the standard deviation and the root mean square error will be small as well.

$$e_{\rm rms} = \sqrt{\frac{1}{n} \sum_{i=1}^{n} e^2} = \sqrt{\frac{1}{n} \sum_{i=1}^{n} (\hat{x}_i - x_i)^2}$$

(5.5)

#### 5.1.6 Skewness

Another way to assess whether or not a distribution is symmetrical, and to compare different distributions, is *skewness*. The definition of the term is somewhat vague and more than one way to measure it has been defined, the one used in this report is shown in (5.6) [10, pp. 183–184].

$$\gamma_1 = \frac{\mu_3}{\sigma^3} = \frac{\frac{1}{n} \sum_{i=1}^n (e_i - \bar{e})^3}{\left(\sqrt{\frac{1}{n} \sum_{i=1}^n |e_i - \bar{e}|^2}\right)^3}$$

(5.6)

#### 5.2 Error Probability Distribution

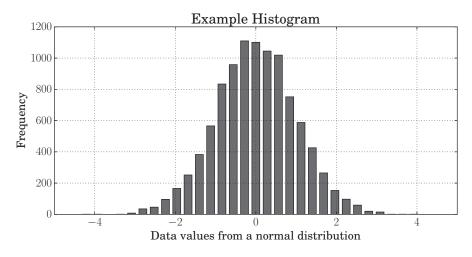

To visualize the error probability distribution, a graph in form of a histogram is a good tool to use. A histogram can show a hint of both the mean error, as well as the standard deviation as described in the previous sections.

An error distribution histogram splits the error range into a number of smaller ranges, and plots a bar for each range, corresponding to how many errors occur in that range. Figure 5.1 shows an example of a histogram. The goal for the error distribution is to be centered around zero. The reason to have the error distribution around zero is that for a large number of calculations, the average error should converge towards zero. For this to happen, the error distributions needs to be centered around zero.

Figure 5.1: Example of a histogram.

#### 5.3 Bit Precision

When looking at the error, it is common to do so on the logarithmic scale, a common approach is to use the decibel unit(dB), shown in (5.7), where x is the error [11].

$$x_{dB} = 20\log_{10}(x) \tag{5.7}$$

When using decibel as a measurement, the correlation between bits, and the decibel unit has to be established. This is done by using Signalto-Noise Ratio(SNR), where noise will represent the error. First the bit resolution must be determent for one bit in fixed-point representation. Shifting the error by one bit to the left or right corresponds to a factor 2 multiplication or division.

1 bit error for fixed-point representation in the fractional part is equivalent to 0.5 (0.1<sub>2</sub>). Equation (5.8) shows the corresponding decibel for one bit resolution.

$$x_{dB} = 20\log_{10}(0.5) \approx -6dB \tag{5.8}$$

From (5.8) it is given that one bit resolution in the fractional part is approximately -6 dB. This measurement is not precise but gives a relatively accurate approximation for one bit. For a more accurate equation for bit precision the formula for calculating one bit should be included instead of using the approximation 6 dB. The equation for bit precision using decibel will be as shown in (5.9).

$$bit precision = \frac{20 \log_{10}(x)}{20 \log_{10}(2^{-1})}$$

(5.9)

Instead of using division, logarithm law of change of the base can be use to simplify the expression. The logarithm law of change of the base is as followed [12, pp. 78-79].

$$\frac{\log_k(x)}{\log_k(b)} = \log_b(x), \qquad \log_k(x^t) = t \log_k(x) \tag{5.10}$$

From (5.10) a direct equation for bit errors in fractional part will be given without division of the resolution, see (5.11) [13, pp. 40].

$$bit \ error = -\log_2(x) \tag{5.11}$$

The assignment is to calculate the bit precision for the fractional part, were 1 bit is equivalent to 0.5. Using (5.11) this will give -1 bit  $(\log_2 (2^{-1}) = -1)$ .

Note that an error of  $0.5 (0.1_2)$  will actually be 0 bit precision in the fractional part due for bit precision in fractional part to be one or higher the error have to be less then  $0.1_2$ .

For the bit precision to be 1, the binary representation of the error has to be  $0.1 > x \ge 0.01$ , which is  $0.5 > x \ge 0.25$  in decimal and  $1 > x \ge 2$  from (5.11). This example gives the general condition for bit precision shown in (5.12), where x is the error and bit precision is e.

$$-\log_2(x) = e \implies bit \ precision = \begin{cases} (e-1) & \text{if } e = \text{integer} \\ \lfloor e \rfloor & \text{if } e \neq \text{integer} \end{cases} (5.12)$$

For this project, one of the goals is that the output values should have 15 bits of precision to the right of the radix point. Having m significant bits to right of the radix point translates to that the largest absolute error  $e_{\text{max}}$  can have no bit set signifying a larger value than  $2^{-m-1}$ . For infinite precision, this means that the largest absolute error allowable can be constructed by the infinite series  $\sum_{i=m+1}^{\infty} 2^{-i}$ , which converges towards the value  $2^{-m}$ . Given that the representation in simulations and hardware will have limited precision, infinite series and convergence does not have to be considered, and the inequality to consider becomes  $e_{\text{max}} < 2^{-m}$ . As this project requires 15 bits of precision to the right of the radix point, every implementation will have to pass a trial to make sure that  $e_{\text{max}} < 2^{-15}$  for all valid inputs.

Alternatively, one could express the goal as that the project requires a signal to noise ratio (SNR) of slightly above 90.3dB, given that the peak output value of the function is 1 and the error limit is  $2^{-15}$ , see (5.13). This can be related to the fact that each extra significant bit represents a power of two increase in dynamic range, corresponding to about 6.02dB, as shown in (5.14)

$$SNR_{dB} = 20\log_{10}\left(\frac{signal}{noise}\right) = 20\log_{10}\left(\frac{1}{2^{-15}}\right) \approx 90.3 \qquad (5.13)$$

$$x_{dB} = 20\log_{10}(2) \approx 6.02dB \tag{5.14}$$

# Chapter 6

# Number Representation

# 6.1 Fixed-Point Numbers

Fixed-point notation is a simple way to extend regular integral representation of a number into that of the rationals. For integers, a number expressed in base b with n digits,  $d_{n-1}$  down to  $d_0$ , has the value  $\sum_{i=0}^{i-1} d_i b^i$ . In the case of fixed-point numbers, the difference can be visualized by introducing an additional constant, the number of fractional digits k, and the value of the number becomes  $\sum_{i=0}^{i-1} d_i b^{i-k}$ .

When writing out the digits, a radix point<sup>1</sup> is usually used to help differentiate fixed-point numbers from integers, as well as showing which digits are integral, and which are fractional. With integers, the smallest representable number is  $b^0 = 1$ , whereas for fixed-point numbers it is  $b^{-k}$ . Arithmetic operations on fixed-point numbers are similar to integer arithmetic. Negative numbers can be represented through two's complement notation in the same manner as for integers.

## 6.2 Floating-Point Numbers

A common method to represent (or at least approximate) real numbers in computers and digital electronics, is binary floating-point representation, (e.g. as standardized by the Institute of Electrical and Electronics Engineers (IEEE) 754[14]), where a real number x is stored as a significand a paired with an exponent b so that  $x = a2^b$ .

$<sup>^{1}</sup>$ The radix point is more commonly known the decimal point when the base is ten, and in a more general sense demarcates the integral and fractional parts of the number

The representation is also normalized, meaning that the significand is made to be greater than one and smaller than the base, and the exponent scaled accordingly.<sup>2</sup> In the case of base two representation, this means that a significant of length n will have the Most Significant Bit (MSB) and Least Significant Bit (LSB) representing 2<sup>0</sup> and 2<sup>n-1</sup> respectively.

#### 6.2.1 Representation and the Inverse Square Root

The inverse square root operation on a floating-point number  $v = a2^b$  can be simplified as shown in (6.1).

$$\frac{1}{\sqrt{a2^b}} = (a2^b)^{-0.5} = a^{-0.5}2^{-0.5b} = \frac{1}{\sqrt{a}}2^{-0.5b}$$

(6.1)

If b is odd, the exponent in the final expression -0.5b will not be an integer (which is required due to the datatype representation), which has to be dealt with, e.g. by subtracting 0.5 from the exponent and multiplying the whole expression with the square root of the base, encumbering the equation with an extra multiplication that can not be converted to shifts or other simple operations. If instead base four is used for the representation of the input data, further simplifications can be made, shown in (6.2).

$$\frac{1}{\sqrt{c4^d}} = (c4^d)^{-0.5} = c^{-0.5}4^{-0.5d} = \frac{1}{\sqrt{c}}2^{-d}$$

(6.2)

Fortunately, converting integers from base two to base four is simple, since sequential pairings of base two digits (so that the most significant digit in the pair corresponds to an odd power of two) can be transparently interpreted as base four digits. In the case of floating-point represented numbers however, some additional work is necessary, given that the base of the exponential is changed. This conversion (6.3) is however lighter on computing resources than the extra multiplication needed if two was kept as the base.

$$a2^{b} = a4^{\frac{b}{2}} = \left\{ \begin{array}{l} a4^{\frac{b}{2}} & \text{if } b \text{ is even} \quad (d = \frac{b}{2}, c = a) \\ 2a4^{\frac{b-1}{2}} & \text{if } b \text{ is odd} \quad (d = \frac{b-1}{2}, c = 2a) \end{array} \right\} = c4^{d}$$

(6.3)

The normalization of the significand is kept through the conversion to base four, in the case of b being even, the significand c will be in the range

<sup>&</sup>lt;sup>2</sup>This is not always possible in a finite precision implementation, but subnormal numbers are considered outside the scope of this project

[1,2), and if b is odd, the range will be [2,4). From this, together with the final expression in (6.2), it can be concluded that by implementing the inverse square root function  $\frac{1}{\sqrt{v}}$  for fixed-point numbers in the range  $v \in [1,4)$ , the function can be implemented for the whole range of the floating-point data type with little extra cost.

| Chapter

# Calculating the Inverse Square Root

## 7.1 Harmonized Parabolic Synthesis

Section 6.2.1 showed the relative ease with which it is possible to extend a fixed-point implementation of the inverse square root, to a fully working floating-point implementation. The requirement is that the fixed-point implementation can operate on an input range  $v \in [1, 4)$ . However, the input working range for the HPS algorithm is  $x \in [0, 1]$ , as discussed in Chapter 3, and for this reason a pre-processing function is necessary. Such an equation and its inverse is shown in (7.1).

$$f_{pre}(v) = \frac{v-1}{3} f_{mre}^{-1}(x) = 3x+1$$

(7.1)

A post-processing function is required as well, since the inverse square root function output varies between 1 and 0.5 for the desired input range, and the output working range of the HPS algorithm is  $y \in [0, 1]$ . The post-processing function and its inverse is shown in (7.2).

$$f_{post}(y) = \frac{y+1}{2} f_{post}^{-1}(z) = 2z - 1$$

(7.2)

Other pre-processing and post-processing functions exist, e.g.  $f_{pre2}(v) = (4 - v)/3$ , however the subtraction of a variable is a more expensive

operation than the subtraction of a constant, and even more so if the addition of the constant only affects the integral part of a number in which most bits signify fractional values.

With both pre-processing and post-processing functions defined, the  $f_{org}(x)$  function can be defined, as shown in (7.3).

$$f_{org} = f_{post}^{-1} \circ f \circ f_{pre}^{-1}$$

$$f_{org}(x) = \frac{2}{\sqrt{3x+1}} - 1$$

(7.3)

From the shape of  $f_{org}(x)$ , i.e. it intersects (0; 1) and (1; 0), the implementation of  $s_1(x)$  is chosen to be that of (3.3b):  $s_1(x) = 1 - x + c_1(x - x^2)$ .

In order to check if  $f_{org}(x)$  is viable for approximation with HPS, the limit of  $f_{help}(x)$  as x approaches 1 needs to be checked for existence and calculated. The definition of  $f_{help}(x)$  is shown in (7.4) and the limit value is shown in (7.5). It can be concluded that approximating the inverse square root with HPS should be possible as long as  $c_1 \ge -1$ , and as long as  $-1/c_1 \notin [0, 1]$  (From the second zero discussed in Section 3.1.2, for which  $f_{org}(x)$  has no defined limit.).

$$f_{help}(x) = \frac{f_{org}(x)}{s_1(x)} = \frac{\frac{2}{\sqrt{3x+1}} - 1}{1 - x + c_1(x - x^2)}$$

(7.4)

$$k_{2,I-1} = \lim_{x \to 1} f_{help}(x) = \frac{3}{8c_1 + 8}$$

(7.5)

## 7.2 The Newton-Raphson Method

In Chapter 4 it was shown with an example of how to use NR for calculating g(v) = 1/v. With the same principle,  $g(v) = 1/\sqrt{v}$  will be calculated, shown in (7.6) and (7.7).

$$y = g(v) = \frac{1}{\sqrt{v}} \quad \Rightarrow \quad v = g^{-1}(y) = \frac{1}{\sqrt{y}}$$

$$f(y) = \frac{1}{y^2} - v \qquad (7.6)$$

$$f'(y) = -\frac{2}{y^3}$$

$$y_{i} = y_{i-1} - \frac{\frac{1}{y_{i-1}^{2}} - v}{-\frac{2}{y_{i-1}^{3}}}$$

$$y_{i} = y_{i-1} \times \frac{1}{2} (3 - v \times y_{i-1}^{2})$$

(7.7)

As in (4.3) the algorithm for calculating the inverse square root can be done without any division (division by 2 can be done by shift). A good approximate algorithm is given for the inverse square root for a given amount of iteration. The bit precision will depend on the number of iterations and the proximity of the initial guess to the actual result.

# Hardware Architecture

## 8.1 Harmonized Parabolic Synthesis

The hardware architecture of the HPS algorithm follows the equations described earlier, as shown in Fig. 8.1 pre-processing and post-processing blocks that transform the input and output of the HPS algorithm block to and from the necessary range, and the HPS block itself, where the two subfunctions  $s_1(x)$  and  $s_2(x)$  reside.

Figure 8.1: A bird's eye view of the HPS hardware architecture

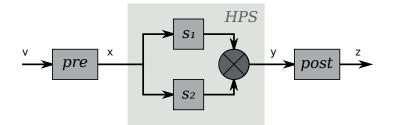

#### 8.1.1 Pre-Processing

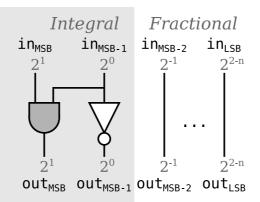

The pre-processing block, shown in Fig. 8.2 is quite simple, one subtraction, and multiplication by a constant. The subtraction can be made very simple due to the fact that the input v is defined to be in the range [1, 4), and the subtrahend is integral, consequently, the subtraction will have no effect on the fractional bits of v, and only two integral bits will ever need to be modified.

Figure 8.2: The pre-processing Function

#### 8.1.2 Processing (HPS)

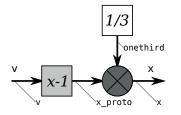

Figure 8.3: The processing/HPS function

The processing block contains the two subfunctions,  $s_1(x)$  and  $s_2(x)$ . Choosing to restrict the potential interval counts I to integral powers of two simplifies the generation of  $x_i$  and  $x_w$ . The value  $x_i$ , used to index the look-up table, is calculated as  $x_i = \lfloor I x \rfloor$ , and  $x_w$ , is calculated as  $x_w = I x - \lfloor I x \rfloor$ . In both cases the multiplication I x becomes a shift, and the equations can be simplified as extracting the correct bits from xand reinterpreting their value. The expression of  $s_2(x)$  in Fig. 8.3 is also a bit different than in (3.5), introducing the constant  $j_{2,i} = k_{2,i} + c_{2,i}$ , which allows expressing  $s_2(x)$  with fewer operations, shown in (8.1). It should also be noted that in the actual hardware implementation, the subtraction of  $c_{2,i}x_w^2$  is made into an addition, by changing the sign of the  $c_{2,i}$  values stored in the look-up table. The motivation is that the hardware becomes simpler.

$$s_{2} = l_{2,i} + k_{2,i} x_{w} + c_{2,i} (x_{w} - x_{w}^{2}) = l_{2,i} + (k_{2,i} + c_{2,i}) x_{w} - c_{2,i} x_{w}^{2} = l_{2,i} + j_{2,i} x_{w} - c_{2,i} x_{w}^{2}$$

$$(8.1)$$

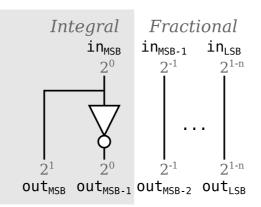

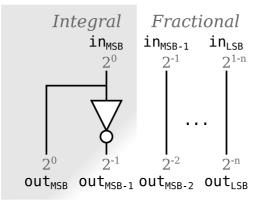

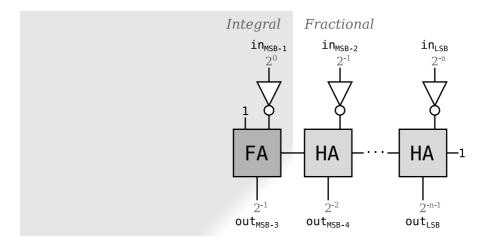

#### 8.1.3 Post-Processing

Figure 8.4: The post-processing Function

The post-processing block in Fig. 8.4 can be optimized as well, y is defined to be on the range (0, 1] and, like in the pre-processing case, it interacts with an integer, so the actual change of the data when added together with a constant 1 does only affect the integral bits. The last block, dividing the result of the addition by 2 can be implemented as a simple bit shift, or in the case of a hardware implementation, as a reinterpretation of the significance of the bits in the data path.

### 8.2 The Newton-Raphson Method

From (7.7) the hardware architecture for the inverse square root can be designed. The simplified algorithm will be as follows:

$$y_i = y_{i-1} \times \frac{1}{2} (3 - v \times y_{i-1}^2) \tag{8.2}$$

The components needed for this algorithm are a subtractor, two multipliers and a shift. The initial value  $(y_0)$  based on the input v, will be placed in a look-up-table (LUT). Figure 8.5 shows an unrolled NR architecture. The iteration count is preferable to keep low, in order to keep a narrow data path (enabling shorter clock periods) and area requirements.

The actual number of iterations and the values placed in the LUT will be determined by the results from the simulations in Matlab. These simulations do also decide the necessary data-path widths of the data paths, so a schematic can be made.

A number of different combination of iterations, LUT and data-path widths will be tested during the simulation process.

Figure 8.5: Unrolled Newton-Raphson architecture

Chapter 9

# Implementation: Data Flow Design and Simulation

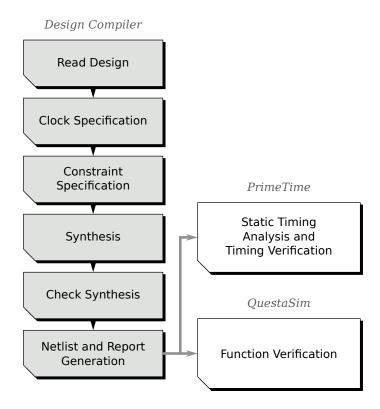

From the theory in Chapter 3 and Chapter 4, the algorithms for Harmonic Parabolic Synthesis and the Newton-Raphson Method are given. To be able to implement these algorithms in hardware, each algorithm needs to have their corresponding constants calculated and the data paths constrained. The effects of combining different constant values and constraints are tested and verified in software based simulations, written in Matlab and C.

For Harmonic Parabolic Synthesis, the value of the constant  $c_1$  needs to be chosen, as well as the number of intervals to use in the subfunction  $s_2(x)$ . The values for the constants  $(c_2, l_2, j_2)$  in each interval is calculated as well.

In the Newton-Raphson Method, the LUT for the initial guesses needs to be calculated and the number of iterations chosen.

For both algorithms, the dataflow of a complete circuit with constrained widths for each data path will be simulated. The final result, z, is going to have at bit precision of at least 15 bits in fractional part, except for v = 1 for which the requirement is that z = 1 exactly, as described in Chapter 2 Scope. These are the primary design objectives.

This chapter will show how these constants are calculated or chosen with the help of the error metrics, probability distribution, and bit precision found in the error analysis theory of Chapter 5.

## 9.1 Harmonized Parabolic Synthesis

In the theory in Chapter 3, methods for calculating values for all the values are presented, except for the value of  $c_1$ , the remaining yet to be defined constant in the first sub-function  $s_1(x)$ , and the number of intervals I in which to split the second sub-function,  $s_2(x)$ . Additionally, the required precision of the various data paths in the implementation need to be determined.

There exists no known simple mathematical rule of thumb for choosing  $c_1$  and I and they, as well as suitable constraints on the data path have to be determined by simulation.

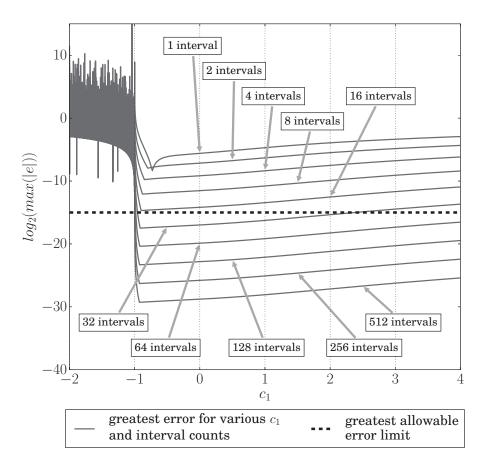

#### 9.1.1 Choosing $c_1$ and Interval Count I

In order to choose suitable values for the constant  $c_1$  and the number of intervals in which to split  $s_2(x)$ , the maximum error for the approximation, over the entire input interval [1, 4) was gathered and plotted for a number of intervals (integral powers of two), and values of  $c_1$  (a high number of points selected from a continuous range). The results are shown in Fig. 9.1

Given the fact that  $c_1$  is going to be fed into a multiplier, choosing a value that is an integral power of two is desirable. This since fixedpoint multiplications and divisions by powers of two can be realized as shifts, which when it comes to hardware, is just a reinterpretation of what the bits present in the data path signify. From an implementation standpoint setting  $c_1$  to zero should be even more beneficial, since multiplication by zero always equals zero, enabling removal of hardware that does not contribute to the final result.

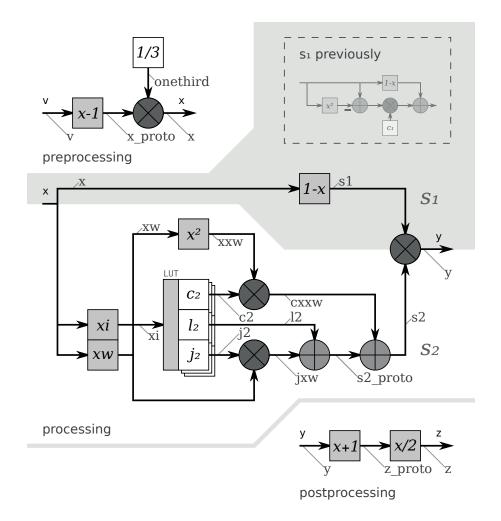

From Fig. 9.1 it can be concluded that at least 32 intervals are required in order to get a small enough error, and that increasing the interval count decreases the error. For all interval counts for which there exists a point below the maximum error limit, choosing the constant  $c_1 =$ 0 is viable, and is selected as the value to be used in all implementations. Now the design can be simplified to the flow shown in Fig. 9.2.

Comparing the processing part in Fig. 8.3 with the corresponding part of Fig. 9.2 the immediate benefit of selecting  $c_1 = 0$  becomes apparent, one multiplier and two adders can be removed.

Following the selection of zero as the value for  $c_1$ , software tools to simulate the data flow behaviour and to report and/or visualize it in various ways were developed. This in order to try multiple combinations of interval counts together with testing how much the data paths can be constrained without the maximum error becoming too big. Both of

Figure 9.1: Plot of the largest approximation errors for the whole input range  $(v \in [1, 4))$ , when choosing various numbers of intervals and values for the constant  $c_1$

these parameters give hard constraints for how the hardware can be implemented. The properties of the simulation software and development work is expanded on in Appendix A.2.1 HPS Data Flow Simulation.

Figure 9.2: The architecture of the implementation of the HPS algorithm; the data paths are annotated with the names they have been given in the simulation output. The implementation of  $s_1$  has been simplified following the selection of  $c_1 = 0$

Apart from removing leading and trailing zeroes from the data paths, some of the paths are only ever representing negative values, making the most significant bit set at all times, making it possible to hard-wire it as a constant. In Table. 9.1 these paths are marked.

| data path  | data-path width |               |  |

|------------|-----------------|---------------|--|

| data patri | 32 intervals    | 512 intervals |  |

| V          | 15              | 15            |  |

| x_proto    | 15              | 15            |  |

| onethird   | 14              | 14            |  |

| х          | 16              | 16            |  |

| XW         | 11              | 7             |  |

| s1         | 17              | 17            |  |

| XXW        | 12              | 5             |  |

| 12         | 18              | 17            |  |

| j2         | $13 (14)^*$     | 10            |  |

| c2         | 9               | 9             |  |

| jxw        | 14              | 9             |  |

| CXXW       | 11              | 6             |  |

| $s2_proto$ | 18              | 17            |  |

| s2         | 18              | 18            |  |

| У          | 16              | 16            |  |

| Z          | 17              | 17            |  |

| ZZ         | 18              | 18            |  |

\* Always negative, meaning that the MSB is always 1 and does not have to be stored

Table 9.1: Width of each data path in two different HPS implementations.

# 9.2 The Newton-Raphson Method

#### 9.2.1 Design Constraints

For the Newton-Raphson Method there are not many design constraints that will affect the approximation of the results. The two main constraints are the number of iterations and the count and values of the initial guesses, and the third is the width of the data paths in the design. By evaluating combinations of these three constraints, a design can be decided on.

The first of these constraints to be determined is the number of iterations versus the number of initial guesses in the Look-Up Table (LUT). In this early step of the design analysis from one iteration to four iterations is done in Matlab by using floating-point representation of the numbers. The method for calculating the initial guesses is explained in Chapter 4.2. When using Matlab to calculate it's crucial to use the

| 1 i | iteration | 2 it | terations   | 3 it | terations   | 4 i | terations   |

|-----|-----------|------|-------------|------|-------------|-----|-------------|

| LUT | Max error | LUT  | Max error   | LUT  | Max error   | LUT | Max error   |

| 81  | 15.0915   | 9    | 16.0772     | 4    | 20.9267     | 2   | 19.6506     |

| 79  | 15.0403   | 8    | $15,\!3849$ | 3    | 17,0273     | 1   | $17,\!2487$ |

| 78  | 14.9747   | 7    | 14.5989     | 2    | $10,\!4489$ |     |             |

Table 9.2: Bit precision for iteration count vs LUT size for floating-point numbers

From Table 9.2 the number of LUT entries each iteration needs in order to have a bit precision of 15 bits or more. Table 9.2 gives that one and two iterations are enough for a precision of 15 bits. A good trade-off is done here, and three and four iteration are no longer candidates for further analysis. The decision is based on that more iterations results in a slower implementable minimum clock period and will also increase the area of the design.

#### 9.2.2 Data-Path Width

The first analysis with floating-point representation is not optimized according to data-path width and an analysis with fixed-point representation for one and two iterations will be done. In fixed-point representation the design should have as small path width as possible to minimize the clock period and also decrease the area, since wider data requires bigger, slower components to implement operations on them. For this purpose Matlab will be used by using "Fixed-point numeric object" toolbox. The rounding method will be set to floor and overflow action to wrap to simulate truncation and overflow in a real Resistor Transistor Logic (RTL) design.

There are no good analytical methods to find the optimal data-path widths since a wider path can give a worse precision than a more narrow one. The method for this approach is simply trial and error, this project does it by decreasing paths in the beginning of the design. Besides a precision of 15 bits, a good error distribution is to be achieved and needs to be accounted for.

Because of truncation, the LUT found in Table 9.2 will not be enough. The algorithm used in Table 9.2 uses the default rounding method in Matlab and no truncation for each operation will be done. In reality a truncation will be done after each operation of the algorithm. The main problem is not how many LUT entries the design will require but to find a good relation between bit precision and the error distribution which is to be centred around zero. Seen in Table 9.3 for one and two iterations, a number of LUT entries have been added to maintain a bit precision of at least 15 bits. For 1 iteration all paths have a width of 18 bits and for 2 iterations the width is 17 bits for all paths.

| 1 i | teration  | 2 iterations |           |  |

|-----|-----------|--------------|-----------|--|

| LUT | Max error | LUT          | Max error |  |

| 94  | 15.4241   | 13           | 15.7297   |  |

| 92  | 15.2967   | 12           | 15.7708   |  |

| 88  | 15.2235   | 11           | 15.7897   |  |

Table 9.3: Bit precision for iteration count vs LUT size for fixed-point numbers

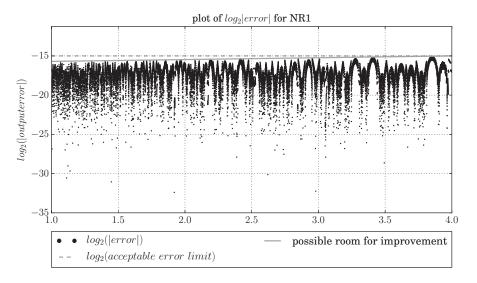

For these designs there is still room for improvement for the data paths, but the next step will be to improve the error distribution. It is beneficial to have some leeway, when modifying the design so that the error distribution comes closer to what is described in Chapter 5.2. The goal is to have SD and RMS as identical as possible. Changes in data-path widths can now make the bit precision go under the required 15 bits and/or make the error distribution worse.

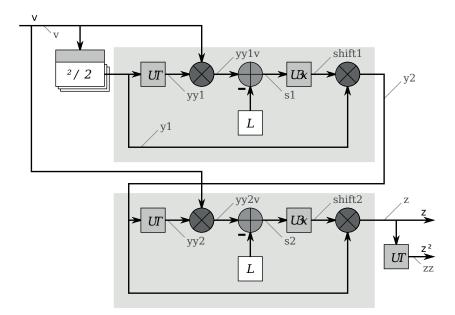

After many simulations, LUT sizes were chosen to be 13 entries for 2 iterations and 94 entries for 1 iteration, due to the good error distribution with the given widths of the paths. The final schematics for 1 iteration and 2 iterations and can be seen in Fig. 9.3 and Fig. 9.4. The bit precision for the final schematic can be seen in Table 9.4.

When all the values in the LUT for 1 iteration and 2 iterations are chosen there is one more constraint that needs to be taken into account. When v = 1 the result needs to be  $1/\sqrt{1} = 1$ . If the first initial guess for when v = 1 is chosen to be 1, simulation of the final schematics of Fig. 9.3 and Fig. 9.4 gives the result 1, the constraint is satisfied. This means that one more initial value will be put into the LUT; for the input value v = 1 the initial guess will be 1, ensuring a correct answer. This extra value will increase the amount of LUT entries to 95 for 1 iteration and 14 for 2 iterations.

| 1 i           | teration | 2 it | terations |

|---------------|----------|------|-----------|

| LUT Max error |          | LUT  | Max error |

| 95            | 15.0376  | 14   | 15.7297   |

Table 9.4: Final bit precision for fixed-point numbers, iteration vs. LUT.

It is time consuming work to find the best error distribution by changing path widths for different LUT sizes. To not get stuck trying to find the best solution, the design is considered to have met its goal when a good enough error distribution is found with a bit precision of at least 15 bits.

Fig. 9.3 and Fig. 9.4 show the final schematics which are to be implemented in VHDL code and analyzed. The data-path widths for the architectures are shown in Table (9.5).

The 14 and 95 LUTs' values and the ranges of v the entries are responsible for can be seen in Appendix A.1.

Figure 9.3: The architecture for 1 iteration of the Newton Raphson method

Figure 9.4: The architecture for 2 iterations of the Newton Raphson method

| 1 iteration  |    | 2 iterations<br>First Second |    |                        |    |

|--------------|----|------------------------------|----|------------------------|----|

|              |    | 1 115                        | 0  | beeor                  | lu |

| v            | 15 | V                            | 15 | V                      | 15 |

| У            | 15 | y1                           | 16 | y2                     | 16 |

| уу           | 16 | yy1                          | 16 | yy2                    | 17 |

| yyv          | 19 | yy1v                         | 16 | yy2v                   | 17 |

| $\mathbf{S}$ | 19 | s1                           | 16 | s2                     | 18 |

| shift        | 19 | shift1                       | 16 | shift2                 | 18 |

| $\mathbf{Z}$ | 18 |                              |    | Z                      | 17 |

| ZZ           | 19 |                              |    | $\mathbf{Z}\mathbf{Z}$ | 19 |

$\label{eq:table 9.5: Width of each data-path in two different NR implementations.$

Figure 9.5: Bit precision for 1 iteration with horizontal line.