## MASTER'S THESIS | LUND UNIVERSITY 2016

## Investigating Different Register Allocation Techniques for a GPU Compiler

Max Andersson

ISSN 1650-2884 LU-CS-EX 2016-23

## Investigating Different Register Allocation Techniques for a GPU Compiler

Max Andersson

June 22, 2016

Master's thesis work carried out at ARM Sweden.

Supervisors: Jonas Skeppstedt, jonas.skeppstedt@cs.lth.se Dmitri Ivanov, Dmitri.Ivanov@arm.com

Examiner: Flavius Gruian, flavius.gruian@cs.lth.se

#### **Abstract**

Register allocation is one of the most critical parts of an optimizing compiler. Although a great effort has been put into researching how to allocate registers, not much of it has been focused on vector registers. This report seeks to find out what fundamentally new problems arise when allocating vector registers rather than scalar registers, how the previously known problems change in vector registers and what methods can be used to tackle these issues. Furthermore, an attempt to use a combined scheme of register allocation and instruction scheduling is made, to see how it performs with vector registers. This thesis presents the results of an investigation of how two commonly used register allocation techniques, Linear scan and Graph coloring, perform relatively. Furthermore, it presents generalizations to a commonly used algorithm used in graph coloring, Chaitin's algorithm.

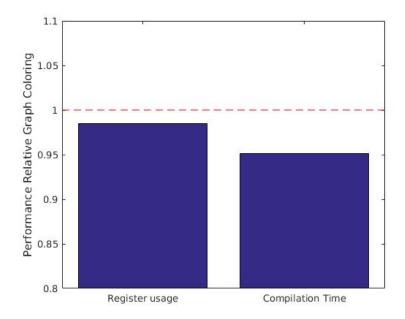

Using the internal performance suites of ARM Midgard compiler, our investigation revealed that linear scan can in fact speed up code generation quite significantly, up to 12.5% compared to graph coloring. However, this comes at the cost of reduced code quality. The generalized spill criterion resulted in an significant reduction in spill code inserted, where 10% less spill code was inserted using the derived criterion. This however did not equate to 10% reduction in execution time, although execution time of the generated code was overall decreased by 0.5%. The combined scheme reached comparable efficiency compared to graph coloring, however, since it was only used for single basic block shaders, it is difficult to say how efficient the register allocation would be for larger shaders.

**Keywords**: Register allocation, vector registers, graph coloring, compiler optimization.

## Acknowledgements

First of all, I would like to thank ARM Sweden for offering me the possibility to do this thesis work. I would especially like to thank my supervisor at ARM, Dmitri Ivanov, for invaluable discussions, comments and help throughout the entire thesis work. I would also like to thank my supervisor at LTH, Jonas Skeppstedt, for his enthusiasm, proofreading and support through this thesis.

I would like to thank my family for their support throughout my time at LTH. Lastly, I want to thank Ellen Rieloff for her love and help throughout our time in Lund.

## **Contents**

| 1 | Intr | oductio | on Control of the Con | 7  |

|---|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Resear  | rch Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

|   | 1.2  | Contri  | ibutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9  |

| 2 | Back | kgroun  | d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

|   | 2.1  | Comp    | iler infrastructure in general                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11 |

|   | 2.2  | Comp    | iler Back-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 |

|   |      | 2.2.1   | Instruction Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 |

|   |      | 2.2.2   | Liveness Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14 |

|   | 2.3  | Regist  | er Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14 |

|   |      | 2.3.1   | Graph Coloring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14 |

|   |      | 2.3.2   | Chaitin's Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15 |

|   |      | 2.3.3   | Chaitin-Briggs algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

|   |      | 2.3.4   | Linear Scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

|   | 2.4  | Vector  | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18 |

| 3 | Нур  | otheses | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 |

|   | 3.1  | Requir  | red Adjustments To Chaitin-Briggs Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 |

|   |      | 3.1.1   | Criterion for Trivial Colorability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

|   |      | 3.1.2   | True Criterion For Trivial Colorability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

|   |      | 3.1.3   | Criterion for Potential Spill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28 |

|   | 3.2  | Subgra  | aph Coloring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |

|   | 3.3  |         | Scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36 |

|   | 3.4  |         | ining Register Allocation with Instruction Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37 |

|   |      | 3.4.1   | Top-down or Bottom-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37 |

|   |      | 3.4.2   | Avoiding Fragmentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38 |

|   |      | 3.4.3   | Placement Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

|   |      | 3.4.4   | Fragmentation and Live Range Splitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39 |

|   |      |         | Tragmentation and Live Range Spitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

| 5  | Resu   | ılts and | l Discussion                            | 43   |

|----|--------|----------|-----------------------------------------|------|

|    | 5.1    | Linear   | r Scan                                  | . 43 |

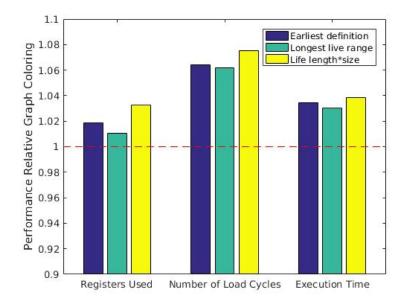

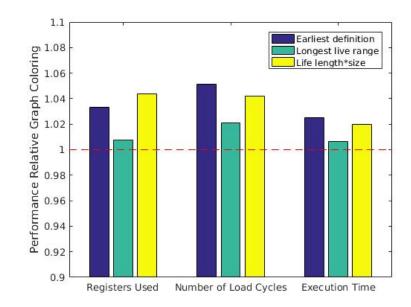

|    | 5.2    | Graph    | Coloring                                | . 45 |

|    |        | 5.2.1    | True Criterion For Trivial Colorability | . 45 |

|    |        | 5.2.2    | Criterion For Potential Spill           | . 46 |

|    |        | 5.2.3    | Subgraph Coloring                       | . 47 |

|    | 5.3    | Combi    | ined Scheduling and Register Allocation |      |

|    |        | 5.3.1    | Top-down or Bottom-up                   | . 49 |

|    |        | 5.3.2    | Efficiency of a combined scheme         |      |

| 6  | Con    | clusions | s                                       | 51   |

|    | 6.1    | Summ     | nary                                    | . 51 |

|    | 6.2    |          | e Work                                  |      |

| Bi | bliogi | raphy    |                                         | 53   |

## Chapter 1

## Introduction

A graphics processing unit, or *GPU* abbreviated, is a processor which handles displaying graphics. The reason why this is done on a separate processor, and not the CPU, is because the task of displaying graphics is fairly different from normal computation. First of all, much of graphics can be computed in parallel. Another difference is the extensive use of *vectors*, which motivates the use of *SIMD*-instructions. SIMD is an abbreviation of *single instruction, multiple data*, and simply means that instead of using the two separate instructions *add r0.x, r1.x, r2.x* and *add r0.y r1.y, r2.y*, have a single instruction *add r0.xy r1.xy, r2.xy* [11]. For a GPU, this is practically invaluable, since computer graphics heavily uses vectors for many reasons, e.g. to model the light sources, characters, texture positions, pixel positions etc. Being able to do these operations in a single clock cycle results in a vast improvement of performance.

This have been done with SIMD on e.g. ARM NEON [2] or SSE [11], but a vital difference between those and GPU-vector registers is the use of *swizzling*. Swizzling is the act of modifying which components is read/written in a register, so that we may for instance have instructions such as add r0.x~zr1.y~w, r2.x~x, where the tilde on a component signals that that components is not read or written. In this instruction, we would add the y-value of r1 and the x-value of r2 and store it as the x-value in r0, while simultaneously add the w-value of r1 to the x-value of r2 and store it as the z-value in r0. It is possible to do this in SSE and NEON, however in order to do so, we need an vector permute, which is often an instruction. Swizzling is common in computer graphics, and for this reason, using an instruction to reorganize the registers would be quite expensive. While swizzling may not seem to be a big difference, it allows for much flexibility in how the components can be allocated. Furthermore, it allows for increased optimization properties, as discussed in detail later. Using a SIMD architecture does not only offer improvements. Some issues with using a SIMD architecture are that it typically uses more power and instructions have a higher latency.

Programs that run on a GPU are called *shaders*. Shaders are of course not written in machine code, and thus need to be compiled into machine code by a compiler. A compiler

is typically divided into three stages, called front-end, middle-end and back-end. The front-end parses source code and creates an *intermediate representation*, (IR), which is sent to the middle-end. The middle-end then performs several high-level optimizations on the code, for instance to reduce redundancy. Finally, the representation enters the back-end, which converts the IR into machine code. The back-end is dependent on the target machine and its characteristics while the front-end is dependent on the program language. One of the most crucial parts of the back-end is *Register allocation*, which is the main focus of this thesis.

The range between the first definition of a variable and the last use of it is called its live range. Register allocation attempts to assign each variable a register for the entirety of its live range. There are many ways of allocating registers to variables. One of the most commonly used methods is to construct a graph, called the Register Interference Graph, or RIG abbreviated, which one then attempts to color using at most as many colors as there are registers available. Since graph coloring is a NP-complete [8] problem, it is not feasible to use an optimal algorithm. Another way of performing register allocation is by linear scan, which simply attempts to order the live ranges in some order allocate them in that order. The clear advantage of this is faster compilation time, but it may result in worse register allocation. There is also a possibility to allocate registers during the Instruction scheduling pass. Such a scheme would perhaps prove useful, since it eliminates the need to perform liveness analysis and register allocation after the scheduling. It is also worth mentioning that efforts have been made to use constraint programming to achieve optimal register allocation. However, due to the amount of computational time it would take to find such a solution, it is not feasible on a GPU compiler [9]. There is a strong incentive to design architectures with as few registers as possible, since register memory is very expensive. Being able to reduce the amount of registers while not significantly reducing performance is thus very beneficial for hardware design.

Finally, there are different types of compilers, two of which are *ahead-of-time*, abbreviated AOT, and *just-in-time*, abbreviated JIT, compilers. The difference lies in that AOT-compilers compile source code prior to execution whereas JIT-compilers compile during runtime. There are advantages and disadvantages of both types, but the main difference is speed of compilation. Since JIT-compilers compile during runtime, it is vital that they are quick, whereas AOT-compilers are allowed to take longer time to compile in order to better improve code efficiency.

## 1.1 Research Questions

This thesis aims to investigate how the vector registers in a GPU affect register allocation, and how the current techniques can be improved. Furthermore, other techniques will be investigated to see how they perform. This has motivated the following research questions, which the thesis revolves around:

- How does Linear Scan perform relative to Graph Coloring in a GPU compiler?

- Can the current implementation of Graph Coloring be improved?

- How do vector registers affect the possibility to perform register allocation during instruction scheduling?

• How can fragmentation be avoided when performing register allocation during instruction scheduling? Fragmentation will be formally defined in Section 2.4.

## 1.2 Contributions

The contributions in this thesis comes in three fields, namely *linear scan*, *graph coloring* and *combining register allocation with instruction scheduling*.

I have compared how the, for GPUs, commonly used technique linear scan performs relative to graph coloring. I have also investigated how different orderings of linear scan perform with vector registers.

Register allocation by graph coloring has been in an ad-hoc manner with vector registers. I present a mathematical generalization of the ad-hoc method for finding trivially colorable nodes. I then prove the generalization to be non-optimal, and formulate a true generalization of trivial colorability. I then present a new criterion for spill node selection. Lastly, I present an improved version of Chaitin-Briggs algorithm, called Subgraph coloring, which is meant to decrease the amount of potential spill nodes which are spilled.

Lastly, I have implemented a combined scheme of register allocation and instruction scheduling. The effectiveness of such a scheme in a GPU compiler has been investigated. I have also found some problems which arise when combining the two methods. Many of these problems occur in register allocation in general, since they are related to register fragmentation.

## Chapter 2

## **Background**

In this chapter a detailed description of the register allocation pass, as well as the necessary information of compiler infrastructure will be presented. Lastly, the characteristics of a SIMD-vector register are presented and formulated.

Throughout this thesis, the terms *variable*, *live range*, *register* and *output of instruction* will be used interchangeably. A variable is the output of an instruction which is stored in a register during its live range. This background presumes scheduling is done before register allocation.

## 2.1 Compiler infrastructure in general

As mentioned in the introduction, a compiler consists of three parts: front-end, middle-end and back-end. We will be focusing on the back-end, since that is where instruction scheduling and register allocation are performed. For the purpose of this thesis, we simply assume that we will be given a *Control Flow Graph*, (CFG), which we will do these passes on. A more formal definition of a graph is found in Section 2.3.1. The CFG is a directed graph, whose nodes are *basic blocks*, and there exists an edge between two nodes in the CFG if there exists a branch instruction from the origin basic block to the target basic block. A basic block is a set of instructions which contains an entry point and only a single branch instruction at the end of the basic block. There are two special basic blocks in the CFG; the entry and the exit blocks. The entry block is the source of all flow in the CFG, and the exit block is the sink of all flow in the CFG [13].

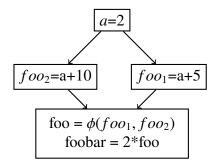

In order to make better optimizations, the variables are transformed into *Single Static Assignment* form, or SSA for short. In SSA, each variable is only defined once. Once a variable is updated, the output of such an instruction results in a new variable rather than an updated variable. This is done in the middle-end, and its purpose is to make it easier to handle definitions and uses of a variable. An issue which arises due to this, is that we sometimes define a variable once, but there are two different definitions. Take the

following C-code for example:

```

1: function Example C-code

2:

int a = 2;

int foo;

3:

if bar then

4:

foo = a + 5;

5:

6:

else

7:

foo = a + 10;

end if

8:

foobar = 2 * foo;

10: end function

```

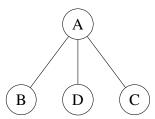

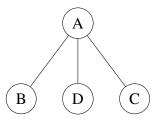

In this case, there exist two definitions of the variable *foo*. We have previously claimed that a redefinition creates a new variable. The issue is that there are two definitions and we do not know which of these reaches the use in *foobar*. To solve this issue, the concept of *phi-nodes* is introduced. A phi-node is a pseudo-instruction which takes all the possible values of the defined variable, and assigns the correct value to the variable according to the actual control transfer CFG edge. From the example code, we can construct a CFG, which would look like this:

## 2.2 Compiler Back-end

In this section, the parts of a compiler back-end which are vital for this report will be presented.

## 2.2.1 Instruction Scheduling

Instruction scheduling is done in order to use the hardware efficiently. This needs to be done in the back-end, since it is highly dependent on the characteristics of the target machine. Processors heavily use *pipelining* to achieve better performance. Pipelining is an act of splitting computations into sequential stages. In a traditional 5-stages pipeline, there are the following stages [11]:

#### 1. Instruction Fetch

- 2. Instruction Decode

- 3. Execute

- 4. Memory Access

- 5. Write Back

During stage 1, the next instruction is fetched. During stage 2, the fetched instruction is decoded, so that the processor knows what to do. Stage 3 is where the actual computation is done. During stage 4, memory is accessed, which is not always necessary. Finally, during stage 5, the output of the instruction is written to a register. There are *dependencies* [11, 13], which determine how instructions may be issued. For instance, there are *data dependencies*, such that an instruction i defines a value, which is then read by instruction j. We can clearly not issue instruction j before the instruction j has written its output to registers.

Typically, instruction scheduling is done on a basic block level, so that each basic block in the CFG is scheduled individually. It is possible to construct a *dependency graph* [13] from the instructions in a basic block. All instructions in the basic block then forms nodes, and there is a directed edge from a node to another if there exists a dependency from the origin instruction to the target instruction, e.g. if the origin instruction produces a result which is used by the target instruction. There can be no cycle in such a graph, which makes it a *directed acyclic graph* (DAG), and the dependency graph is henceforth referred to as the DAG. Although it is possible to traverse the DAG in many ways, we will focus on two, which are *Top-down* and *Bottom-up*.

Essentially, every time we select an instruction to schedule, we select an instruction from a set of instructions which are available for scheduling. What instructions are available for scheduling is dependent on whether the scheduling is top-bottom or bottom-up. Which instruction to choose is not important for the purpose of this thesis, but it not a trivial problem (in fact, it is also NP-complete [13]).

Top-down is perhaps the most intuitive way to schedule, since it follows the flow of the program. Essentially, instructions which have all operands they use defined, are available for scheduling, and may be scheduled. In terms of the DAG, this is equivalent to a node having no incoming edges. After an instruction has been scheduled, all outgoing edges are removed from the DAG. This is then done until the DAG is empty, at which point the entire basic block has been scheduled.

In bottom-up scheduling however, an instruction is available for scheduling if it has no outgoing edges, i.e. there is no instruction dependent on it which has not yet been scheduled. When an instruction has been scheduled, all incoming edges from its corresponding DAG-node will be removed. Much like in top-down, whenever the DAG is empty, the entire basic block has been scheduled.

Finally, the scheduler needs to take *register pressure* into account. Register pressure is an estimate of how many physical registers are currently live. If the register pressure is high, then it is likely that we need to spill variables. Every instruction may use a number of variables and may write to a register. An instruction which writes its value to a register clearly requires register space. If there is currently a shortage of registers, then the scheduler should focus on freeing register space, whereas if the is a large amount of register space, the scheduler should focus on consuming register space.

In a VLIW, an abbreviation of *very long instruction word*, or a superscalar architecture, several instructions are issued the same clock cycle [11]. There are a number of functional units which the instructions can utilize, and if there for instance only exists a single adder, then two instructions which utilize an adder may not be scheduled at the same clock cycle. Using a superscalar or VLIW architecture means that the scheduler needs to take all the instructions in the instruction word into account when calculating how register pressure is affected by this instruction word, while at the same time optimizing functional unit usage, for instance using the adders as efficiently as possible.

## 2.2.2 Liveness Analysis

Liveness analysis is determining when a variable is *live*. Formally, a variable is live between its definition and its last use. This duration is called its *live range* [13], and that is what we will use henceforth. It is not necessarily easy to determine a variables live range. A variable may for instance have different last uses depending on paths taken in the CFG. If two variables at some point in time can not share register, then they are said to *interfere*.

We may split the live ranges into *local* and *global* live ranges. A local live range is a live range which is only live during a single basic block, whereas a global live range is live during several basic blocks. This division will be used later when describing the combined scheme of register allocation and instruction scheduling.

## 2.3 Register Allocation

Register allocation is the act of assigning all the variables in the CFG a register to be stored in through their live ranges. Typically, live ranges are ordered and then they are allocated according to that ordering. There are two main ways in which the ordering is done, which is *Graph Coloring* and *Linear Scan*.

## 2.3.1 Graph Coloring

A graph G is said to consist of *vertices*, sometimes referred to as *nodes*, and *edges*, sometimes referred to as *arcs*. The two entities are denoted V and E respectively, and the graph itself is denoted G(V, E). Two nodes are said to be adjacent if there exists an edge which connects the two nodes. Additionally, the set of all nodes adjacent to a node is called its *neighborhood* [8].

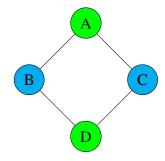

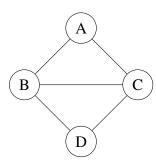

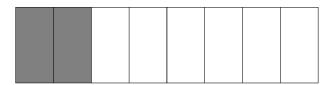

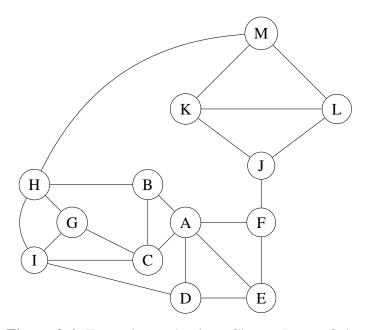

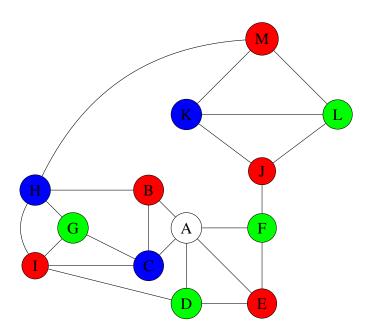

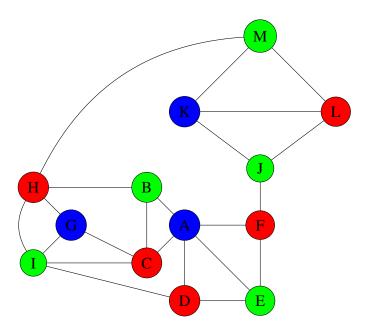

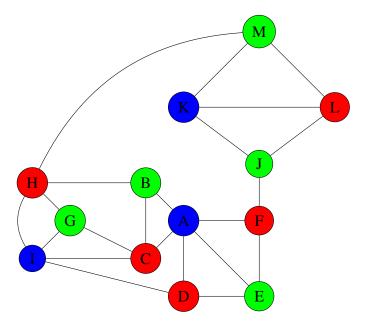

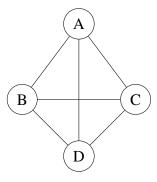

During graph coloring, the nodes of a graph are colored, such that no adjacent nodes share the same color. Generally, we attempt to find a coloring using k colors, which is referred to as a k-coloring. The lowest number of colors needed to color a graph is said to be its *chromatic number* and is denoted  $\chi(G)$ . An example graph, called the *Diamond Graph*, is displayed in Figure 2.1. We see in Figure 2.1 that the chromatic number for the diamond graph is 2.

How does graph coloring correlate to register allocation? To answer that question, we first look into how variables can be stored in registers. Assume that we have a value in register R0. Then it must be safe to overwrite that value with another value if the original value did not have any more uses. Analogously, if we overwrite the value but still need to

Figure 2.1: Diamond graph.

use it at some point in the future, we need to write that value to a register again. This of course means that we either need to have the value stored in memory, so that we can load it from memory, or have the possibility to compute the value again. Regardless of which way we restore the value to a register, it comes at a cost. Ideally, we would not want to need to restore any values in such a manner. We thus come to the conclusion that if two values are ever live simultaneously, then we do not want them to share the same register. This is equivalent to allowing two variables to share a register if they do not interfere. In graph coloring, we want to find a coloring such that no node shares color with an adjacent node. Assume we let a node represent a variable, and let there be an edge between two nodes if their corresponding variables interfere. Finally, if we let the number of colors equal the number of registers present, then we see that we can rephrase register allocation as "We attempt to assign registers to all variables, such that no interfering variables share the same register". We thus conclude that if we can find a coloring of the constructed graph, called the *Register Interference Graph* (RIG), then we can successfully allocate the variables registers [5].