# Device development for doping evaluation in nanowires using capacitance-voltage measurements

Emil Nylander emil.nylander@hotmail.com

Supervisor: Magnus Borgström Co-Supervisor: Ali Nowzari

August 30, 2016

#### 1 Abstract

This thesis aims to show the prospect of capacitance measurements over nanowire arrays as an evaluation method of the p-doping level in weakly p-doped p-n nanowires. The premise of the method is that there will be a high yield of statistical data regarding the doping level of the nanowires. The majority of the work carried out and presented in this thesis is however aimed at the manufacturing of a device suitable for said evaluation, and thus a range of different properties for materials were investigated. Due to early signs of parallel resistance in the device, allowing for an undesirably high back current, the disassociating isolator material as well as radial overgrowth of n-type InP was questioned. The isolating resist Cyclotene 3044-46 was thoroughly investigated before it was discarded due to its lacking electrical properties. The optional combination of SiO<sub>2</sub> and photoresist \$1818 was instead favored, albeit the resulting prolonged processing times. A device was created through various epitaxial, lithographic and etching techniques, creating a device inspired by the design used in nanowire-based solar cells. The design still needs further improvement, in order to eliminate flaws influencing the current through the device. Since the usage of Cyclotene would simplify the design and decrease the manufacturing time, further investigation into the origins of the poor electrical properties is of great interest.

## Contents

| 1 | Abstract                                     | i    |

|---|----------------------------------------------|------|

| 2 | Introduction                                 | 1    |

| 3 | Background                                   | 5    |

|   | 3.1 Epitaxy                                  | 5    |

|   | 3.2 Band structure                           | 8    |

|   | 3.3 The p-n Junction                         | 11   |

|   | 3.4 Doping Evaluation                        | 14   |

|   | 3.5 Impedance                                | 15   |

|   | 3.6 Model Diodes                             | 17   |

| 4 | Methodology                                  | 19   |

|   | 4.1 Material Investigation                   | 19   |

|   | 4.2 Design II                                | 22   |

|   | 4.3 BCB Investigation                        | 28   |

|   | 4.4 S1818                                    | 31   |

| 5 | Results                                      | 35   |

|   | 5.1 Material Investigation                   | 35   |

|   | 5.2 IV Characteristics of a BCB-based Device | 39   |

|   | 5.3 BCB's Isolating Properties               | 42   |

|   | 5.4 CV Characteristics of Design IV          | 45   |

| 6 | Outlook                                      | 50   |

| 7 | Summary                                      | 51   |

| A | Appendix A                                   | v    |

| В | Appendix B                                   | vii  |

| C | Appendix C                                   | viii |

| D | Appendix D                                   | ix   |

| E | Appendix E                                   | x    |

| F | Appendix F                                   | xi   |

| G | Appendix G | xii  |

|---|------------|------|

| Н | Appendix H | xiii |

| I | Appendix I | xiv  |

#### 2 Introduction

As technology advanced throughout the 20th century, and into the 21st the importance of semiconductor science became abundantly clear. The ability to scale down transistors allowed for the computer industry to increase the computational power of a chip, and this is what often comes to mind first when talking about semiconductors and their influence on technology. In accordance with Moore's Law, the number of transistors has steadily been increasing, pushing to unlock the potential of semiconductors. In addition it also unlocked the potential of several other fields, e.g. solar cells, light emitting diodes (LED), and a diverse range of sensors. These are devices that are integrated and essential for the growth of modern technology. As research is carried out to improve or develop new technology, the demand for innovation grows. However, that is not to imply that there is a stagnation of semiconductor science, as new findings are being brought to light regulary. As recently as 2014 the Nobel Price in Physics was bestowed upon Isamu Akasaki, Hiroshi Amano and Shuji Nakamura for inventing the blue LED.

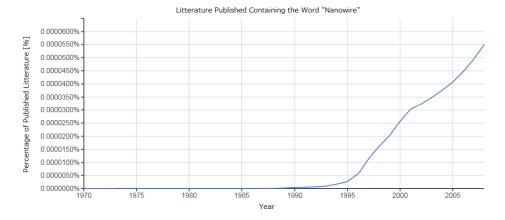

Figure 1: 'ngram' depicting the increase in occurance of the word "nanowire" in literature[9]

A promising field of study is that concerning nanowires. Showing many unique properties, the prospect of nanowires has attracted much attention in recent years. This can be inferred through observing the increase of the word "Nanowire" in literature. As displayed in figure 1 it is evident to the observer that the interest for nanowires is increasing. This attention

is not without cause, and electrical devices such as resonant tunneling diodes (RTDs)[1], single electron transistors (SETs)[2], and LEDs[3] have been demonstrated in NWs. The ability to engineer well-ordered arrays of nanowires[4], as well as to control the axial and radial growth[5] allows for highly optimized designs. If optimized, an InP nanowire array with a wire length of 2  $\mu$ m is predicted to absorb more than 90% of the light above the InP bandgap[6]. Investigations concerning properties of nanowires have thus proven promising.

In order to achieve desired electrical properties impurities are often introduced into the semiconductor, i.e. doping. While doping is generally done in order to alter the conductivity of the semiconductor[8], it has also been demonstrated to affect growth of nanowires[7]. LEDs can be realized with nanowires by changing doping species during growth, resulting in an n-type doping area, and a p-type doping area[3]. In the presence of a forward bias, this allows for radiative recombination, i.e. injection electroluminescence, at the junction region[8]. As the electrical properties of the semiconductor heavily rely on the introduced dopant, there is a value in monitoring the growth process, thus allowing for the growth parameters corresponding to the desired properties of a nanowire to be determined.

The knowledge concering doping of nanowires is closely related to the strength of the evaluation techniques used. During the development of nanowire fabrication various evaluation techniques have been shown capable of evaluating the doping[7]. However, due to the limitations of the system (the nanowire), and/or the evaluation techniques, all methods are faced with complications, which have to be taken into account during processing. When considering what evaluation technique to use, aspects such as simplicity of the technique and time constraints of the process are often the deciding factor. Optical methods are thus attractive, as they usually require no further processing, and are generally faster than electrical measurements. One such optical technique is to observe the so-called Burstein-Moss shift during photoluminescence (PL). The PL spectra will be blue-shifted as dopant concentration increases. The method has been demonstrated to give accurate results on doping in bulk[10], as well as for nanowires[11]. Although the method carries over from bulk to nanowires, it is limited to evaluation of high doping concentrations and incapable to deliver a qualitative profile of the nanowires. In addition, as the blue-shifting is observed a broadening of the peak is also observed, thus rendering measurements harder to interpret.

Raman spectroscopy is another commonly employed optical method used for doping evaluation of semiconductors, and has also been used to characterize nanowires[12]. The method is well suited for qualitative measurements, but in order to extract quantitative information a continuous measurement of the nanowire is needed. As this is both time consuming and only provide information on a single nanowire, other methods are preferred for quantitative analysis.

In contrast to the optical methods, electrical techniques and methods utilizing spatial measurements are also available for characterization. Spatial measurement techniques are seldom desired outside of academic environments due to being extremely time consuming. Electrical techniques are however widely used, as they often can deliver information regarding the device under working conditions. The most commonly used method for quantitative characterization of doping in a nanowires is to create a socalled nanowire field-effect transistor (NW-FET) device[13]. The FET can be made by using a substrate with an oxide grown on top of it (e.g. Si and SiO<sub>2</sub>) as the gate and isolating oxide layer, the nanowire is then placed on top of the oxide and contacted on each side, where by the contacts will act as source and drain and the nanowire as the transport channel [38]. By sweeping the source-drain voltage it is possible to determine the conductivity of the nanowire, and therefor the carrier concentration (directly related to the doping) can be determined[7]. This technique is generally only limited by extensive need of processing, resulting in a very time consuming process.

Evaluation of doping using the well-known Hall-effect, while having been proven possible[14], is not commonly used due to it sharing a similar necessity for processing as the NW-FET, and is further constrained by the physical size of the system. It is clear that an evaluation method unlimited by processing time or the physical size of the system would be beneficial to the semiconductor industry. One promising technique is that of CV-measurements on an array of vertically grown nanowires. The promising prospect of the technique was displayed in 1991[3], but has since been generally left uninvestigated. In 2014 attempts to develop a device capable of doping evaluation using said method was carried out[15], producing promising results. This method would demand less processing, and would be capable of delivering high statistical, quantitative characterization of nanowires.

Following previous research[15], attempts at processing a functional device, capable of doping evaluation in nanowires through CV measurements was carried out. The work will be explained during the length of this report.

The report consists of an initial part (3) describing the underlying theory used in order to attempt the doping evaluation of the nanowires. Although the processing and measurements were carried out in parallel these processes will be split up in a second part presenting the methodology throughout this project (4), followed up by the results (5) obtained through measurements on the devices described in section 4. Lastly ideas for further research on the subject (6), as well as a summary (7) of the project is presented.

## 3 Background

To support the idea of CV-measurements as a possible evaluation method for doping in nanowires, a brief explanation of a p-n junction in a nanowire and its features will first be given. As the properties of the p-n junction are made clear an attempt will be made to evaluate the doping with a parallel plate capacitor approximation, allowing for an uncomplicated method.

#### 3.1 Epitaxy of Nanowires

To understand how a p-n junction in a nanowire is realized it is necessary to explain the growth process of a nanowire. When talking about nanowire manufacturing, there are two different approaches that are conducted in order to achieve the desired structure. The first method is the so-called top-down approach, where the structure is etched out from bulk[16]. The other is known as the bottom-up approach, where nanowires are grown using epitaxial methods. Using these methods it has been shown possible to grow nanowires on a substrate[3] as well as in an aerosol[17] enviroment. Throughout this project, nanowires were grown on substrate using the the second approach, and this section will thus be dedicated to summarizing the process flow.

In a bottom-up approach, the nanowires are generally grown from seed particles that are deposited on the substrate before the growth process. Au as a seed particle is one of the most studied form of catalyst for nanowire growth, and the conditions of the seed particles can affect the growth considerably. The growth process exhibits highly similar behaviour between different deposition methods (e.g. electrospray method, Electron Beam Lithography-defined or aerosol gold particles generated by evaporation), but the particles are rather sensitive to nanowire incubation time and annealing[18], greatly effecting nanowire growth.

As the position of the particle will determine the position of the finalized nanowire, both the actual properties of the particle, as well as the deposition location of the particle will have to be taken into consideration. Several techniques to generate and deposit seed particles are available, including aerosol carried particles generated through spark discharge, as well as colloid particles spun on to the target substrate[18]. As metal precursor particles are guided towards the substrate by a gas, and spun colloid particles are deposited in a random fashion on top of the substrate, a control mechanism is vital in order to achieve organized structures. For their ability to guide the deposition with high precision, *Electron Beam Lithog-*

raphy (EBL)[20] and Nano Imprint Lithography (NIL)[4, 6] are favoured for nanowire growth. NIL comes with the advantage of higher throughput, but with a lower precision than that of EBL. As NIL was the method used in this project it will be described in further detail.

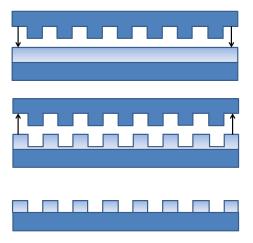

The promising results for the technique known as NIL were demonstrated in 1996[21], as a resolution of 25 nm for imprint lithography was achieved. In imprint lithography a mould with thickness contrast features are pressed into a resist, and a mirrored structure is formed in the resist. During the moulding step the resist is generally heated, as low viscosity promotes the conforming of the resist. Finally, unwanted resist between the finally sought features are removed, this through anisotropic etching (fig. 2). The mould is generally made with slower methods such as EBL defined areas etched by Reactive Ion Etch (RIE), which is known to be a time consuming process. Since the mould used to imprint the structures into the resist can be rendered unusable for further processing by resist sticking to it after the moulding, a master is often created, mimicking the finally desired structure. A second mold used for the imprint is then patterned by the master, increasing the life-time of e.g. the EBL defined mould (the master). An anti-sticking coating is also often applied to the mask to further diminish the possibility of resist being torn of the sample as the mould is removed[36]. The method can imprint a large area[21] with high resolution, and is thus as previously stated favoured for high throughput.

When defining the position of the nanowires with NIL, the pattern transferred by the mould will create holes in the resist residing on the substrate. The patterning is then followed by e.g. metal evaporation[4], that will result in the sought after seed particles as the resist is lifted off.

Although the crucial role of each seed particles' position has been stated, the process promoted by the particle is yet to be discussed, and this process is to validate the part the position plays during growth. After seed particle deposition, the method of interest used to grow the nanowires is *Metal Organic Vapor Phase Epitaxy* (MOVPE). This epitaxial method utilizes a carrier gas to transport the constituent elements (in gas phase) to the vapour-solid interface. The gaseous species then dissociate/pyrolyse at the heated growth area, thereby releasing the elements intended for growth. The metalorganic sources are generally stored in bubblers, and at a set pressure the liquid creates an equilibrium vapour pressure, allowing the carrier gas to be saturated with precursor molecules, which are then carried away to the growth chamber, also known as the reactor. The growth process is then governed by three major factors; adsorption, growth and desorption. The elements are adsorbed onto the growth area, were they induce growth.

Figure 2: Flow chart of a general NIL process. The mould is first pressed into the thermoplastic. The mould is then removed, and anisotropic etching is used to expose the underlying substrate.

Excess reaction products are then desorbed from the growth area[22].

In the case of a nanowire, the growth is as previously stated locally catalysed by the metal seed particle[23]. As the seed particle saturates it will cause nucleation at the base, forming a crystal layer. The nanowires are as noticed fabricated through a VLS mechanism, and the process needs to be carried out at a high temperature so the seed particle can form a liquid alloy. It has been shown that the continiuous growth at the collector-crystal interface is favourable in comparison to new growth at other interfaces of the collector/seed particle[24], as well as the side facets of the wire. Although not favoured, side growth is a factor that needs to be taken in to consideration when growing nanowires, as it can result in radial overgrowth, rendering the nanowire unusable for the intended purpose. In order to avoid side growth *in situ* etching is performed[5], for InP nanowires (used in this project) HCl is usually used as the etching agent. In the case of InP nanowires the reaction, if simplified, is as follows[15, 35]:

$$In(CH_3)_3 + PH_3 \rightarrow InP + 3CH_4 \tag{1}$$

The small dimensions of the nanowires also allows for different materials to be grown on top of each other to a larger extent then for a bulk system. For example, for a planar structure attempts at growing different materials

on top of each other would cause defects at the junction due to different lattice constants. However, as the junction interface in a nanowire is small the lattice mismatch will not be enough to cause strain or defects[26]. The ability to grow different materials with very well defined interfaces opens up for interesting structures for e.g. photonics, and instinctively we can see that if it holds for different materials the growth process should allow us to grow differently doped regions on top of each other[7], thus enabling structures such as the p-n junction to be created.

#### 3.2 Band Structure

As semiconductors in general are poor conductors impurities are often introduced to promote electrical current in the material[8]. The source of the poor conductance is that there is a clearly defined bandgap between the valance band and the conductance band. In order for electrons to contribute to a current it is necessary that they are excited to the conduction band. In metals the valence band and the conductance band overlap, allowing for conductance. In semiconductors there is a separation that electrons, given enough excitation energy, can be excited over. Although the bandgap is smaller than that of an insulator, the thermal energy at room temperature is generally not enough to maintain a sufficient electron concentration in the conduction band. During excitation the electron overcomes the energy barrier, moving into the conductance band, leaving a vacancy in the valance band, e.g. a hole. Said holes behave as positively charged particles, and contribute to conductivity.

As previously stated, impurities are usually introduced to promote conductivity. There are two different doping types: the introduction of an energy state close to the conduction band called n-type doping, and an energy state close to the valance band called p-type doping. In order to create an n-type doping profile in the semiconductor impurities with an excess valence electron are introduced. This creates a filled energy state close to the semiconductor's conduction band, and electrons can with conciderably less energy (than the energy needed to be exited from the valance band) be exited to the conduction band, increasing conductivity in the semiconductor. The opposite type of doping is p-type. A p-type doping profile is created by introducing dopants with a shortage of a valence electron, and this will create an energy state close to the edge of the semiconductor's valance band. As the introduced energy states are close in energy to the edge of the valance band (thermal energy allows for excitation), this allows for electrons to be excited from the valance band to the vacant energy states.

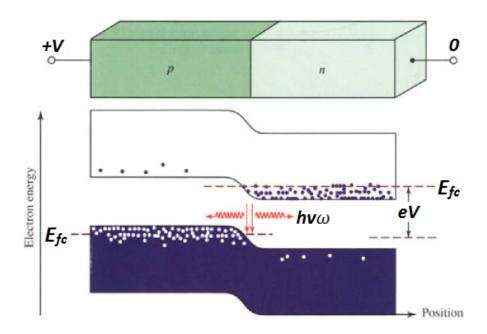

As the electrons are excited they become bound, unable to contribute to any current. However, simultaneously they create holes, which as previously mentioned can contribute to conductance. The effect of doping on a material is illustrated in figure 3.

Figure 3: Energy-band diagram of a p-n junction with a forwarded bias, as a result of applied voltage. The blue dots in the conduction band signify electrons, while the white dots signify holes. The figure was adapted from [8].

As can be seen in figure 3, the Fermi level's offset is determined by the doping profile. As the Fermi level guarantees charge neutrality/marks half occupation, n-doping forces the Fermi level up against the conduction band, while p-doping forces the Fermi level down towards the valance band. As two materials are connected the band structure at the interface bends as to maintain a constant Fermi level in the material [28], thus maintaining charge neutrality through the sample. The bending of the bands can be seen in figure 3 (under a bias V), where a so called p-n junction has been formed between a p-type and an n-type doped semiconductor.

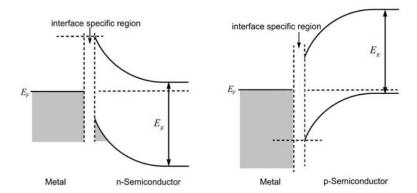

As the Fermi level of a metal is located in the conduction band, merging a semiconductor interface with a metal may cause the band structure of

Figure 4: Illustration of the bending of the conduction and valence band as a semiconductor is merged with a metal. The image is an altered version of an image available at [40].

the semiconductor to bend towards higher energy (Fig. 4)[29]. This is especially prominent in semiconductors with a p-type doping profile. This bending will render electrons occupying the lower levels of the conduction band unable to move past the junction. This barrier is called a Schottky barrier and can cause trouble when attempting to make a contact to a semiconductor[25, 30]. The thickness of the barrier d is given by equation 2, were e is the electron charge,  $N_D$  is the number of introduced dopants,  $V_b$  is the applied bias (in eV), and the permittivity is denoted by  $\epsilon_0$  and  $\epsilon_b$ :

$$V_b = \frac{e^2 N_D d^2}{2\epsilon_0 \epsilon_b} \tag{2}$$

For small d electrons can tunnel through the barrier with a probability T (Eq. 3), where m is the carrier mass, and  $\hbar$  is Planck's constant:

$$T \approx exp\left[-\left(\frac{2mV_b}{\hbar^2}\right)^{1/2}d\right] \tag{3}$$

This allows for a current to pass through the junction. Thus heavily doped semiconductors can form ohmic contacts with metals. For the purpose of this project InP nanowires were used, a material which has shown difficulties in forming an ohmic contact between metals and p-type InP[25].

#### 3.3 The p-n Junction

As a p-type and an n-type material are brought together, carriers (electrons and holes) will start to diffuse to areas with lower concentration; i.e. electrons will diffuse into the p-region, and holes into the n-region. As the electrons diffuse they leave positively charged ions behind, and holes will leave negatively charged ions. Electrons will recombine with holes in the p-region, and holes with electrons in the n-region, as they are abundant. The build-up of charge in the junction area, due to the presence of ions, will eventually block further diffusion over the junction, resulting in an area around the junction nearly depleted of mobile charge carriers[32] known as the *depletion layer*.

The space charge distribution and electrostatic potential  $\psi$  of the p-n junction can be described by the Poisson's equation[33]:

$$\frac{\mathrm{d}^2 \psi}{\mathrm{d}x^2} \equiv -\frac{\mathrm{d}E}{\mathrm{d}x} = -\frac{q}{\varepsilon_s} (N_D - N_A + p - n) \tag{4}$$

As can be seen the electric field E is determined by the acceptor-  $N_A$  and donor-impurity density  $N_D$ , and the density of free holes p and electrons n, with q and  $\varepsilon_s$  being the electron charge and the semiconductor's permittivity constant. Local charge neutrality is maintained when:

$$\frac{\mathrm{d}^2\psi}{\mathrm{d}x^2} = 0\tag{5}$$

as such

$$N_D - N_A + p - n = 0 (6)$$

As the junction becomes depleted of mobile charge carriers, p = n = 0, and equation 4 becomes reduced to:

$$\frac{\mathrm{d}^2 \psi}{\mathrm{d}x^2} = \frac{q}{\varepsilon_s} (N_A - N_D) \tag{7}$$

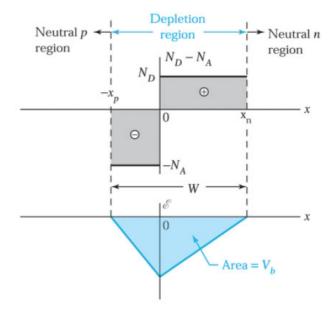

If the depletion layer is divided into two parts, the space charge distribution (Eq. 7) can also be divided in two parts (Fig. 5): one for the p-side, and one for the n-side.

$$\frac{\mathrm{d}^2 \psi}{\mathrm{d}x^2} = \frac{qN_A}{\varepsilon_s}, -x_p \le x < 0 \tag{8}$$

Figure 5: Space charge distribution and electric-field distribution in the depletion region at thermal equilibrium[33].

$$\frac{\mathrm{d}^2 \psi}{\mathrm{d}x^2} = -\frac{qN_D}{\varepsilon_s}, 0 < x \le x_n \tag{9}$$

The overall space charge neutrality of the semiconductor requires that the total negative space charge per unit area in the p-side equals the total positive charge per unit area in the n-side. Assuming a 1D uniform structure along the e.g. x-axis results in:

$$N_A x_p = N_D x_n \tag{10}$$

The total depletion layer width W (Fig. 5) is given by:

$$W = x_p + x_n \tag{11}$$

The electric field over the depletion layer is obtained by integrating over the electrostatic potential (Eq. 4), and utilizing equations 8 and 9 give:

$$E(x) = -\frac{qN_A}{\varepsilon_S}(x + x_p), -x_p \le x < 0$$

(12)

$$E(x) = \frac{qN_D}{\varepsilon_c} (x - x_n), 0 < x \le x_n$$

(13)

The total electrostatic potential difference between the p-side and the n-side neutral regions at thermal equilibrium is called the *built-in potential*  $V_b$ , and can be obtained by integrating over the electric field (Eqs. 12 and 13) in the depletion area:

$$V_b = \int E(x) dx = \frac{1}{2} E(0) W$$

(14)

By combining equation 10 through 14, the depletion layer width as a function of built-in potential is obtained:

$$W = \sqrt{\frac{2\varepsilon_s}{q} \left(\frac{N_A + N_D}{N_A N_D}\right) V_b} \tag{15}$$

If a bias  $V_a$  is applied over the junction (in the fashion of a positive voltage at the p-side in respect to the n-side), the junction becomes forward-biased, and the electrostatic potential decreases by  $V_a$ . A change in electrostatic potential naturally effects the width of the depletion region, and as the total electrostatic potential  $V_b$  is replaced by  $V_b - V_a$ , the width of the depletion area becomes:

$$W = \sqrt{\frac{2\varepsilon_s}{q} \left(\frac{N_A + N_D}{N_A N_D}\right) (V_b - V_a)}$$

(16)

As the depletion layer separates the neutral p- and n-side, ions at the interfaces causes charge separation, and the p-n junction effectively acts as a capacitor, where the junction depletion layer capacitance per unit area  $C_j$  can be defined as[33]:

$$C_j = \frac{\mathrm{d}Q}{\mathrm{d}V} \tag{17}$$

Here dQ is the incremental change in depletion layer charge per unit area for an incremental change in the applied voltage dV. The amount of change in charge distribution due to an applied voltage can be approximated to be  $dV = WdQ/\varepsilon_s$ , and equation 17 can be rewritten as:

$$C_j = \frac{\varepsilon_s}{W} \tag{18}$$

The attentive reader can now see the connection to the parallel plate capacitor  $C = \epsilon A/d$ , where A is the area of the parallel capacitor, d is the distance between the plates, and  $\epsilon$  is the dielectric constant. The model of a parallel plate capacitor is only true as long as edge effects can be neglected  $(R \gg d)$ , where R is the radius of the plates). In the case of a small R more complex numerical models have to be used to solve for the capacitance[34]. Assuming the model of a parallel plate capacitor d = W, and  $C_i = C/A$ .

By combining equations 16 and 18, the capacitance per unit area as a function of applied voltage can be expressed as:

$$\frac{1}{C_i^2} = \frac{2(V_b - V_a)}{q\varepsilon_s} \frac{N_A + N_D}{N_A N_D} \tag{19}$$

Naturally this only holds when the doping levels are constant in the two doped materials.

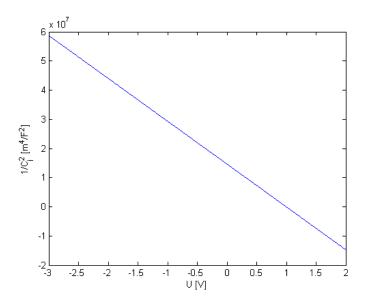

#### 3.4 Doping Evaluation

As the goal of this project is to develop a method to determine the doping level of weakly p-doped material, further explanation regarding the correlation between capacitance (3.2) and doping levels is necessary. If equation 19 is analysed, a linear relation between  $1/C_j^2$  and  $V_a$  can be observed. However, it is also evident that the depletion layer capacitance per unit area also has a strong relation to the doping levels in the materials  $(N_A + N_D/N_A N_D)$ . Under the assumption of  $N_A \ll N_D$ , equation 19 can be rewritten as:

$$\frac{1}{C_i^2} \approx \frac{2(V_b - V_a)}{q\varepsilon_s N_A} \tag{20}$$

From 20 it is evident that only the doping level in the low-doped side can be evaluated. In order to evaluate the doping level, a capacitance-voltage measurement would need to be conducted, where the built in voltage would be determined as an axis cut off ( $V_a = 0$ ), and the doping level could be extracted from the slope of the curve (Eq. 21).

$$\frac{\mathrm{d}}{\mathrm{d}V_a} \left(\frac{1}{C_i^2}\right) = -\frac{2}{q\varepsilon_s N_A} \tag{21}$$

It was previously mentioned that equation 19 only holds for constant doping levels. However, the doping profile of the low-doped side of the junction as a function of position x (Fig. 5) can also be determined[15]. This

Figure 6: Example figure of  $1/C_j^2$  in InP plotted agains  $V_a$  using equation 20, with  $N_A = 10^{16} \ [1/cm^3]$ ,  $N_D = 10^{19} \ [1/cm^3]$  and  $V_b = 1$  V. This graph does not take diffusion capacitance into account.

is done by combining equations 18 and 21, which allows for the construction of a doping profile along x.

The theory presented in the sections 3.3 and 3.4 for the capacitance of a p-n junction only holds for the reverse biased case. For the forward case diffusion capacitance becomes much larger than the transition capacitance previously presented. When a forward bias is applied over the p-n junction charge carriers will start to move into the oppositely charged region in order to recombine with the abundance of the opposite charge carrier in that region. As a result the depletion region decreases. The build-up of charge carriers trying to move into another region as well as a decreasing depletion region width results in an increase in capacitance.

For the purpose of this project the reverse bias case will be utilized.

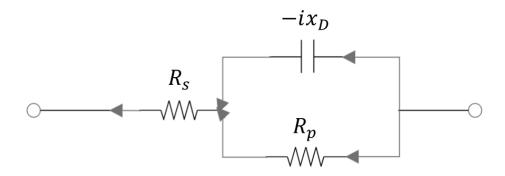

#### 3.5 Impedance Translation

The generally used method for capcitance measurements is an impedance measurement. As impedance P consists of a real part R and an imaginary part -iZ, models are needed in order to extract the capacitance from the

measurements. The impedance of a capcitor  $-ix_D$  can be written as:

$$-ix_D = -\frac{i}{\omega C} \tag{22}$$

Where C is the capacitance of the capacitor and  $\omega$  is the angular frequency of the applied bias. The model adopted in order to describe the pn-junction was that of a capacitor in paralell with a resistor, in series with yet another resistor (Fig. 7).

Figure 7: Model used to interpret impendance measurements for the pnjunction. The diode is modeled as a capacitor with a paralell resistor, in series with another resistor.

With the model depicted in figure 7 the total impedance of the component becomes:

$$P = R_s - \frac{ix_D R_p}{R_p - ix_D} = -i\frac{x_D R_p^2}{R_p^2 + x_D^2} + \frac{R_s R_p^2 + x_D^2 R_s + x_D^2 R_p}{R_p^2 + x_D^2}$$

(23)

By using the imaginary part  $Z = x_D R_p^2 / R_p^2 x_D^2$ , where  $R_p$ ,  $R_s$  and  $x_D$  are resistances/impedances as depicted in figure 7, the resistance of the paralell resistor  $R_p$  can be described as:

$$R_p = x_D \sqrt{\frac{-Z}{x_D + Z}} \tag{24}$$

In a similar fashion the real part R can be used to describe  $x_D$ :

$$x_D = \frac{(R - R_s)^2 + Z^2}{-Z} \tag{25}$$

By estimating the current through the diode at backwards bias, rather than passing through any paralell component, the total resistance  $R_{TOT}$  can be estimated as:

$$R_{TOT} = \frac{U_{TOT}}{I_{TOT}} = R_s + R_p \tag{26}$$

This allows  $R_p$  to be written as:

$$R_p = \frac{R^2 + R_{TOT}^2 + Z^2 + 2RR_{TOT}}{R_{TOT} - R} \tag{27}$$

By combining equation 24 and 27,  $w_D = 1/\omega C$  yields the capacitance C as:

$$C = \frac{-Z}{\omega ((R - R_{TOT} + R_p)^2 + Z^2)}$$

(28)

As such the capacitance required to solve equation 21 can be extracted from the impedance measurements.

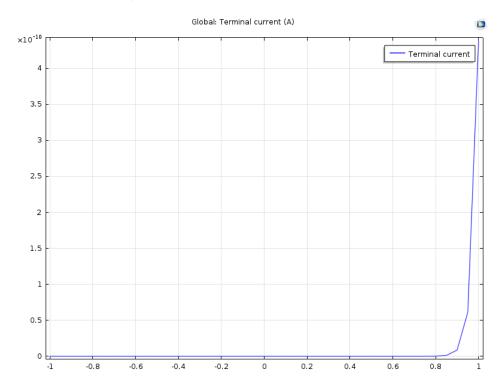

#### 3.6 The Ideal Diode Equation

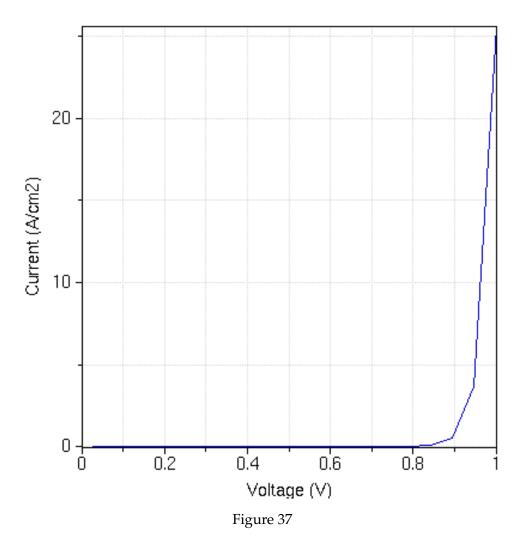

As p-n junctions behave as diodes the measured current over a p-n junction can be used in order to determine if the p-n junction is well defined. In a model diode the current should follow the behaviour as specified in equation 29[39]:

$$i_D = I_s \left( exp \left( \frac{v_D}{nV_T} \right) - 1 \right) \tag{29}$$

Where  $i_D$  is the current through the diode,  $v_D$  is the bias applied over the diode, n is the ideality factor, and  $V_T$  is the thermal bias ( $V_T = kT/q$ ). For a model diode the ideality factor is in the range [1 2]. The equation (Eq. 29) describes the diode well in forward direction, and in the reverse direction it predicts that  $i_D \rightarrow -I_S$  for large negative bias. However, usually the measured current is larger than the predicted one. As a low reverse current is desired the rectification ratio r is used in order to give an indication of the quality of the diode. The rectification ratio is defined as:

$$r = \frac{i_D(x)}{|i_D(-x)|}$$

(30)

As can be seen in equation 30 the rectification ration determine order of magnitude which the forward current towers the reverse current at a given bias x in forward respectively reverse direction.

As a model diode predicts low currents in the range close to  $v_D = 0$ , it can be used to determine any parallel resistance included in a diode system. As the total resistance at any given voltage V gives:

$$\frac{1}{R_{TOT}} = \frac{1}{R_D} + \frac{1}{R_P} \tag{31}$$

Where  $R_D$  is the resistance of the diode,  $R_P$  is the parallel resistance, and  $R_{TOT}$  the total resistance. If there is any significant current through the diode system for small biases, and as  $R_D$  becomes really large for small biases, the current can be used to approximate any parallel resistance as:

$$R_P \approx \frac{V}{I_{TOT}} \tag{32}$$

## 4 Methodology

#### 4.1 Investigation of the Device Material

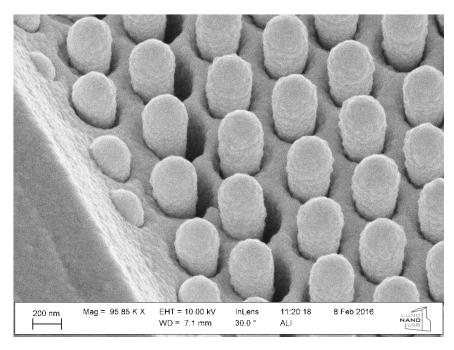

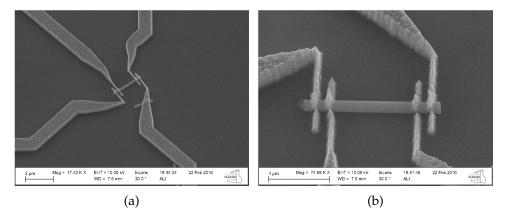

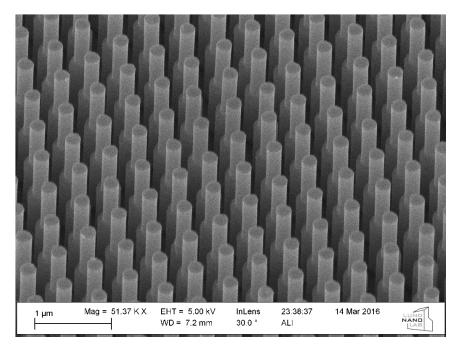

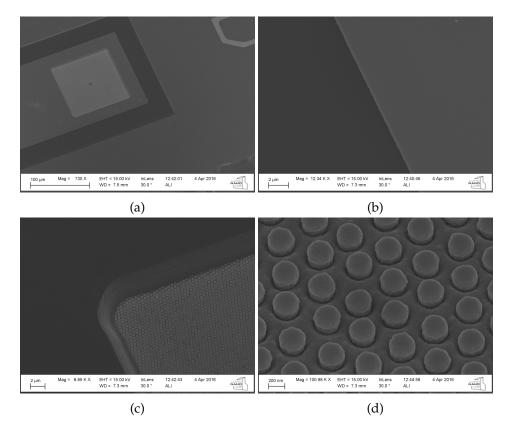

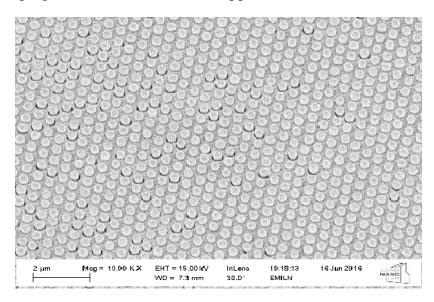

To be able to continue previous research[15] on the possibility to use a vertical array device of nanowires as a tool for doping evaluatation, processing and measurements were carried out to investigate the poor electrical properties of the previous devices. During measurements on previous devices poorly rectifying devices were found [15], suggesting leakage currents. Previous designs were investigated using a *Scanning Electron Microscope* (SEM), and semi-cracks were found along a small portion (< 10%) of the device edges (Fig. 8). These cracks' effect on the device's performance as a whole was deemed insignificant due to the small number of appearances.

The devices generally displayed a uniform benzocyclobutene (BCB) surface with evenly spaced nanowires protruding from the surface by approximately 200 nm. The nanowires are 2 µm long, with a 1 µm long segment of heavily doped ( $\sim 10^{19}~\rm cm^{-3}$ ) n-type InP on top of a weakly p-doped ( $\sim 10^{16}~\rm cm^{-3}$ ) segment. As the nanowires are protruting the surface by approximately 200 nm it is thought that the metal contact is not circumventing the p-n junction. This due to the fact that the metal contact would need to be in contact with the depletion region centered around the p-n junction (3.3) for the current to be able to circumvent the p-n junction. As the depletion region does not expand as far as 800 nm from the p-n junction (the rough location of the metal contact) it can be assumed that the current is not circumventing the p-n junction as a result of contacting.

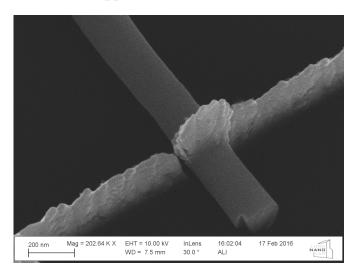

In order to localize the error in the design of the device used in order to perform electrical measurements on the nanowires a logical starting point was thought to be the nanowires, as they constitute the most vital part of the device. The nanowires were processed in order to, via single wire contacting, determine their electrical properties. The nanowires in question were broken off from a sample consisting of an array of grown InP nanowires with dimensions as presented previously. In order to be able to measure on the nanowires they had to be moved to a bonding substrate. The substrate was prepared by washing it in acetone during ultrasonic treatment for 2 min, followed by a similar treatment in IPA. This method was used to break the nanowires off from the substrate, and a piece of paper was later used to transfer them to the bonding substrate. Two samples were prepared in parallel in order to yield a larger amount of reliable data in the end.

The preparations for the contacts that were to be defined using EBL, consisted of localizing the nanowire intended for bonding and then con-

Figure 8: SEM image of formed semi-cracks in BCB along the device edge. The Nanowires protrude from the surface by roughly 200 nm.

structing a contact pattern using software EBL-Builder in unison with images taken with a SEM. As it is reasonable to expect the possibility of so-called Schottky-like contacts when contacting to the p-doped part of the wires, a bonding pattern for 4-probe measurements was constructed for one of the samples. The ability to determine if ohmic contacts are possible with the 4-probe setup. Despite the trade-off of a lower yield (4-probe measurements results in half the amount of bondable nanowires) this was thought to be preferable, and thus two different patterns were prepared (one for 2-probe bonding and one for 4-probe bonding). An example of a 4-probe setup can be seen in figure 9a. The resist that was to be patterned Polymethyl Methacrylate 950K (PMMA 950K) was spun on to the samples at 5000 rpm for 1 min, followed by baking on a hot plate at 180°C for 5 min. The resist was then treated in an EBL system Raith 150 to define the desired pattern for the contacts. The pattern was then developed for 1 min in 1:3 Methyl Isobutylketone:Isopropanol (MIBK:IPA), followed by 1 min in IPA. As there was a possibility for natural oxide to form on the substrate between development and evaporation of the metal contacts, the samples were treated

Figure 9: (a): SEM image of a contacted nanowire. The outer contacts are spaced 100 nm from each other. (b): The rougher end determines its doping as p-type. In contrast, the smoother end determines it as previously contacted to the seed particle, thus being n-doped.

in *Buffered Oxide Etch (BOE) 10:1 JT Baker* for 1 min, followed by 1 min in *deionized water* (DIW) before being placed in the evaporator *AVAC*. A layer of Pd/Zn/Pd/Au[25] was evaporated on top of the samples with thicknesses 2.5/20/2.5/225 nm. The samples were then left in acetone over the night in order to lift off the resist and unwanted metal on the surface. The lift off was completed the next day, as the resist was rinsed off in Acetone, followed by IPA.

I-V measurements were carried out on a probestation *Cascade 11000B* to determine the properties of the p-n junctions. The results are presented in 5.1 (Fig. 21 and 23). The contacts were then investigated with a SEM as to determine the polarity, and thus whether any diodic behaviour originated from the nanowire p-n junction or from other sources, e.g. Schottky contacts. The polarity of the wires was determined by comparing the ends of each individual wire, distinguishing the doping type by the general roughness of the ends (Fig. 9b), as the nanowires were broken off from the substrate at the p-doped side. In order to determine to what degree the nanowires influence the full device, measurements were also taken for previously manufactured devices, with an isolating BCB layer[15].

As signs of parallel resistance (3.6) were found in the full devices during measurements (see 5.1, Fig. 22a) an attempt to cure the BCB was carried out. It was reasoned that successful curing could reveal if there were pinholes in the resist. The sample was thus cured for 10 min at 250°C, using a rapid

thermal processing system RTP 1200.

It was realized after the first series of measurements that InP had a turnon voltage at around 1.4 V, although slightly higher than the bandgap it is consistent with other research [27], and in order to get a better estimate of the ideality factor, as well as the rectification, a second series I-V measurements were carried out on the nanowires between -2.5 to 2.5 V.

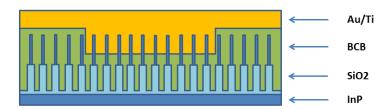

### 4.2 First Revision of Device Design

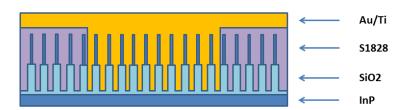

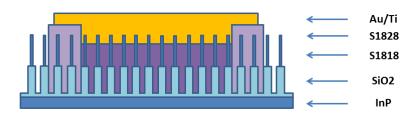

As described in 5.1 there were apprehensions concerning parallel resistance in the device. Electrical measurements showed diodic behaviour in the nanowires. Hence radial overgrowth had been ruled out during the single nanowire contacting (5.1. Fig. 23), the properties of the insulating BCB was instead thought to be the cause, and a design for a new device was made (Fig. 10) in order to investigate said BCB. The new design incorporated a thin layer of  $SiO_2$  around the nanowires, thus protecting the p-segment and the substrate from current leaking through the resist.

Figure 10: Schematics depicting the design used in order to investigate the properties of the BCB.

Since the exact etch rate of BCB inside the RIE system *Etcher RIE - Trion T2* was unknown, and it was of interest to investigate if a current could be drawn through the BCB, a set of dummy samples were created. This was done by cleaning eight Si substrates in Acetone inside an ultrasonic bath for 1 min, followed by 1 min in IPA. A layer of BCB was then spun onto the substrates. Four substrates were spun at 3000 rpm, resulting in a resist thickness of  $\sim$ 3  $\mu$ m. The remaining four substrates were spun at 5000 rpm, resulting in a resist thickness of  $\sim$ 2.3  $\mu$ m. The spin-coating was followed by soft baking for 90 s at 120°C, before which the backside of the samples were cleaned of resist using EBR PG. In order to harden the resist the samples were placed in a rapid thermal processing system to bake for

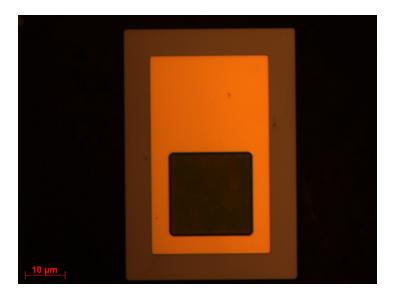

1 h at 250°C, for full recipe see Appendix C. To create dummy samples similar in design to that shown in figure 10, a photolithography step was carried out on the four samples that had been spin-coated at 3000 rpm. The samples were first cleaned in Acetone for 30 s, followed by 30 s in IPA. In order to coat the samples with photoresist S1828, they were spin-coated at 3000 rpm, followed by baking for 90 s at 115°C. After 2 bursts of UV-light exposure in UV-lithography system Mask aligner MJB4 (soft UV) the resist was developed for 2 min in MF319, followed by 1 min in DIW. The exposed BCB was then etched in a RIE system, using 10 sscm of  $CF_4$ , 70 sscm of  $O_2$ , at a pressure of 250 mTorr, with 150 W of power feeding the plasma. The four samples were etched for different amounts of time, at 30, 60, 90, and 120 s respectively. This allowed for determination of the etch rate. Through the usage of a surface profiler system the etch rate was determined to be ~2 μm/min. The remaing S1828 was removed in Acetone for 1 min, followed by 1 min in IPA. To create the metal contact on top of the samples, two samples, determined to have a BCB layer not fully etched through during RIE, were placed in sputtering system *Sputterer - AJA Orion 5*, where a thin layer (206 Å) of Ti was first sputtered onto the samples, followed by 200 nm of Au.

Figure 11: Optical image of the device created through the process described in 4.2. The orange area is the Au contact, the light brown is the isolating BCB layer, and the dark surrounding area consists of exposed nanowires.

The final devices were defined with yet another UV-lithography step, where the samples were first cleaned with Acetone for 1 min, followed by 1 min in IPA, a layer of S1828 was then spin-coated at 3500 rpm, and baked for 90 s at 115°C. The samples were then exposed in a UV-lithography system for 2 intervals of 10 s, followed by development in MF319 for 2 min, and 1 min in DIW. The exposed Au was then etched in KI/I<sub>2</sub> for 2 min, followed by 1 min in DIW. As it is likely that there are remains of the Ti layer after the Au etch a second etching was done to remove the Ti where the samples were etched for 10 s in BOE 1:10 JT Baker, followed by 1 min in DIW. The remaining photoresist was removed by 1 min in Acetone and 1 min in IPA. The finished device resembled the real device displayed in figure 11, aside from the nanowires not being present.

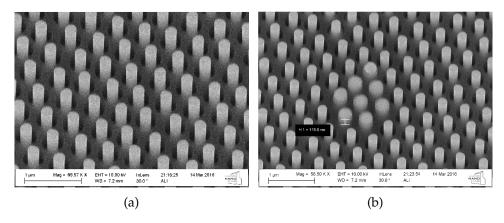

As the final objective was not to create dummy samples, but rather a device as depicted in figure 10, processing was carried out on InP substrates with nanowire arrays grown on top. The samples were provided, and had a p-doped substrate with a segment of p-doped nanowire on top, the p-doped segment was then followed by an n-doped segment. The nanowires had a width of ~200 nm, and length of ~2.2  $\mu$ m, with a ~1.1 nm long p-doped segment and an ~1.1 nm long n-doped segment.

Figure 12: (a): Exposed nanowires, protruding the S1818 surfaces. (b): Unetched nanowires, SiO<sub>2</sub> still covers the top segment of 8 nanowires after 227 s of etching in BOE 1:10 JT Baker.

Two samples with InP nanowires were processed. A table summerizing the processing method for the two samples can be found in Appendix I. The samples were prepared for the deposition of a thin layer of SiO<sub>2</sub> by first being cleaned for 1 min in Acetone, followed by 1 min in IPA. A 40-50 nm

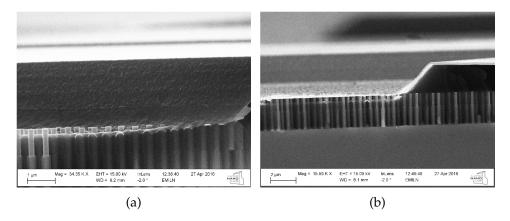

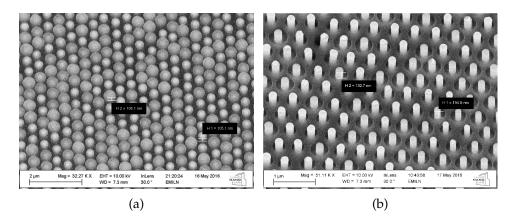

SiO<sub>2</sub> layer was deposited followed by a 5 nm layer of  $Al_2O_3$  (in order to promote adhesion of BCB to the sample) in an ALD system *ALD system - Savannah-100*. With the intent to etch away  $SiO_2$  from the top of the covered wires a layer of S1818 was spun on top of the samples. Before spin-coating the samples were cleaned in Acetone for 1 min, followed by 1 min in IPA. The samples were then spun at 3000 rpm, and baked at 115°C for 90 s. To allow the ends of the nanowires to be etched the S1818 needed to be etched back, exposing the tops of the nanowires. This was done using a RIE system, for a total of 2600 s, with a gas flow of 15 sscm  $O_2$ , and 50 W of power feeding the plasma. The result can be observed in figure 12a (unfortunately one of the samples broke, and was from there only used as a dummy sample). The  $SiO_2$  was then etched using BOE 1:10 JT Baker for 227 s, as the etch rate was understood to be 2.7 nm/s from in house experience, it would result in ~600 nm of etching. The sample was then rinsed in DIW for 1 min.

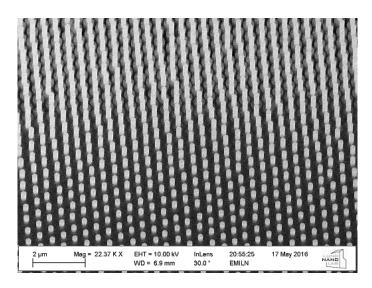

As the thickness of the  $SiO_2$  was ~50 nm it was undoubtedly thought to be enough. However, during SEM investigation unetched wires were found (Fig. 12b). In order to remove these a second series of RIE etching was performed, etching an extra 750 s with 15 sscm of  $O_2$ , and 50 W of power feeding the plasma. The  $SiO_2$  was then etched once more with BOE 1:10 JT Baker, this time for 45 s, followed by 1 min in DIW. The S1818 was then stripped with Acetone for 1 min and 1 min of IPA. The resulting structure is displayed in figure 13.

Figure 13: Nanowires after the  $SiO_2$  has been etched, and the S1818 has been stripped. ~800 nm of the nanowires are exposed.

In order to define the outline of the devices a layer of BCB was spun onto the sample. The sample was spun at 5000 rpm, resulting in a resist thickness of  $\sim$ 2.35 µm. The spin-coating was followed by soft baking for 90 s at 120°C, before which the backside of the sample was cleaned of resist using EBR PG. To harden the resist the sample was placed in a rapid thermal processing system to bake for 1 h at 250°C—for full recipe see Appendix C. To create the design shown in figure 10, a photolithography step was carried out on the sample. The sample was first cleaned in Acetone for 30 s, followed by 30 s in IPA. In order to coat the sample with photoresist \$1828, it was spin-coated at 3000 rpm, followed by baking for 90 s at 115°C. After 2 bursts of UV-light exposure in UV-lithography system *Mask aligner MJB4* (soft UV) the resist was developed for 2 min in MF319, followed by 1 min in DIW. The exposed BCB was then etched in a RIE system for a total of 85 s, using 10 sscm of CF<sub>4</sub>, 70 sscm of O<sub>2</sub>, at a pressure of 250 mTorr, with 150 W of power feeding the plasma. The remaing S1828 was removed in Acetone during 1 min, followed by 1 min in IPA. To create the metal contact on top of the sample it was first etched for 1 min in H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O 1:10, followed by

1 min of DIW in order to remove natural oxide. It was then placed in a sputtering system where a thin layer (206 Å) of Ti was first sputtered on to the sample, followed by 2000 Å of Au. The final devices were defined with yet another UV-lithography step, where the sample was first cleaned with Acetone for 1 min, followed by 1 min in IPA. A layer of S1828 was then spin-coated at 3500 rpm, and baked for 90 s at 115°C. The sample was then exposed in a UV-lithography system for 2 intervals of 10 s, followed by development in MF319 for 2 min, and 1 min in DIW. The exposed Au was then etched in KI/I<sub>2</sub> for 2 min, followed by 1 min in DIW. As it is unlikely the Ti layer is etched in the process, a second etching was done to remove the Ti. The sample was therefor etched for 10 s in BOE 1:10 JT Baker, followed by 1 min in DIW. The remaining photoresist was removed by 1 min in Acetone and 1 min in IPA. The finished device can be seen in figure 11.

Electrical measurements were then carried out on a probestation *Cascade* 11000B. I-V characteristics were collected for biases between -1.7 V and 1.7 V. The data is presented in 5.2 (Fig. 24). After receiving data that supported the idea of leakage between the devices the sample (Fig. 26) was cleaved to enable for a cross-section inspection through SEM, see figure 14. This was mainly done in order to see if there was a thin metal layer on top of the sample that created a contact between devices (the sample being the fully processed substrate, and the device being a device as depicted in figure 11).

Figure 14: (a): SEM images of the exposed nanowires outside of a device. The edge of metal layer of the device can be seen in the background (poorly focused). (b): The nanowires inside the device, covered with the contacting metal layer.

#### 4.3 Investigating the Isolating Properties of BCB

From the results in 5.2 it can be seen that there was a similar fault (poorly rectifying devices) in the devices as the one observed for the devices presented in 4.1, and the fact that no metal seemed to be present between different devices on the samples (a clear edge of metal is visible in figure 14) the BCB layer was now questioned. As such one of the two previously prepared planar Si substrates which had had a layer of BCB spun on them at 5000 rpm was treated with UV-light in UV-lithography system for two bursts of 10 s. The reason only one of the two samples was flooded was to determine if the UV-treatment could alter the properties of the BCB. The samples were then placed in a sputtering system, depositing 200 Å Ti and 2000 Å Au on top of them. Isolated measuring pads were then defined using the same UV-lithography treatment and metal etch as for the InP nanowire sample presented later in this section. Measurements were then carried out on a probestation in order to see if the BCB was conductive. The results can be found in 5.3.

Measurements on the design presented in 4.2 (Fig. 10) showed a strong reverse current (Fig. 24). Hence in order to see whether the problem with the heavy back-current (3.6) during reverse bias was due to BCB's involvement in the device, a device similar to that in 4.2 but void of BCB inside the metalnanowire bonding area was manufactured: see figure 15. A new batch of InP nanowires with the same growth parameters as previous samples were provided. See Appedix F for parameters.

Figure 15: Schematics depicting the design used in order to investigate the properties of the BCB.

The samples were first cleaned in Acetone for 1 min, followed by 1 min in IPA. As the catalyst Au particle was still attached to the grown nanowires, and thought to pose a problem during contacting, the particle was etched off by treating the sample with 10s of H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O 1:10 followed by 10s of KI/I<sub>2</sub>. This treatment was repeated three times. During SEM inspection

of the samples (Fig. 16a) doubts regarding whether the Au particle had fully been removed arose. The substrate was thus etched for three more cycles before the samples were placed in an ALD system. A 40-50 nm layer of  $SiO_2$  was deposited, with a 5 nm  $Al_2O_3$  on top of it in order to promote adhesion. After the ALD treatment the samples were once more investigated with SEM (Fig. 16b), and it was found that the samples had been stripped of nanowires during the second etching treatment, this to our surprise, as similar etching times had been used previously[15]. After receiving input from other researchers, whom have had the same experience with  $KI/I_2$  etching InP, it was decided to maintain more conservative etching times for future processing. The reason for the break off could be due to the intermediate DIW, that is supposed to be a rinsing agent, becoming contaminated and thus resulting in added etching times.

Figure 16: (a): The nanowires after attempts to remove the catalyst Au particle had been carried out. (b): After second etch the nanowires had been shaved off from the substrate.

During the next attempt to create the device sought after (void of BCB), the InP nanowire sample was prepared in the same way as previously, except the sample was only exposed to the etching process three times, with the etching process being: 10s of H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O 1:10 followed by 10s of KI/I<sub>2</sub>. As the processing method is similar to the one presented in 4.2 it will be summerized in the table below.

| Design III                                                                                           |

|------------------------------------------------------------------------------------------------------|

| Nanowire Au seed particle removed:                                                                   |

| $3x(20 \text{ s } H_2SO_4 \text{ 1:}10 + 10 \text{ s DIW} + 20 \text{ s KI}/I_2 + 10 \text{ s DIW})$ |

| Cleaned backside with IPA + rinse in Acetone for 1 min + 1 min IPA                                   |

| ALD: $40-50 \text{ nm } SiO_2 + 5 \text{ nm } Al_2O_3$                                               |

| Rinsed in Acetone for 1 min + 1 min IPA                                                              |

| Spin-coat S1818 @ 3000 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| RIE, 15 sscm O <sub>2</sub> , 50 W, 2000 s                                                           |

| Etch SiO <sub>2</sub> : 111 s BOE 1:10 JT Baker + 1 min DIW                                          |

| Strip S1818: 1 min Acetone + 1 min IPA                                                               |

| Spin-coat S1828 @ 3500 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| UV-lithography: 2x 10 s exposure                                                                     |

| Develop: 2 min MF319 + 1 min DIW                                                                     |

| Hard-baking S1828: 200°C for 40 min + 10 min cooling down                                            |

| Ecth natural oxide: 1 min $H_2SO_4$ : $H_2O$ 1:10 + 1 min DIW                                        |

| Sputter 200 Å Ti + 2000 Å Au                                                                         |

| Rinse in DIW for 1 min                                                                               |

| Spin-coat S1828 @ 3500 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| UV-lithography: 2x 10 s exposure                                                                     |

| Develop: 2 min MF319 + 1 min DIW                                                                     |

| Au-etch: 2 min KI/ $I_2$ + 1 min DIW                                                                 |

| Residue-etch: 10 s BOE 1:10 JT Baker + 1 min DIW                                                     |

| Strip S1828: 1 min Acetone + 1 min IPA                                                               |

The sample was contacted with a brass coin using conductive silver glue before measurements were carried out on a probe station. Measurements can be found in 5.3.

As surfaced during measurements (5.2 and 5.3) of the device presented in 4.2 and previous planar Si samples, there were doubts regarding the isolating properties of BCB. BCB is marketed as a good isolator [31], and thus the measurements obtained (5.2 and 5.3) were surprising. As the BCB previously used had been provided by a second party, the quality of the resist was unknown, and thus a new batch of BCB *Cyclotene 3022-46* was used for the processing presented in this section. During processing it was observed that the viscosity of the solution was questionably less. If true, this would suggest that the previous batch had higher viscocity, as a result of manufacturing or due to the solvent evaporating over time (this is also strengthen by the vendor specifications, see Appendix E, as thicker resists results in a thicker layer after spin-coating). The higher viscosity also answer the question regarding longer etching times than expected during

RIE during processing (4.2), as higher viscosity would mean a thicker layer after spin-coating. In order to investigate the isolating properties of BCB two devices were produced.

The new samples were created by first cleaning the Si substrates in Acetone for 2 min during ultrasonic treatment, followed by 1 min in IPA. A layer of BCB was then spun onto the samples at 5000 rpm, creating a layer thickness of roughly 2.3 µm. The backsides of the substrates were then cleaned with EBR PG before the samples were left to soft bake at 120°C for 90 s. As the BCB was going to be the final layer under the top metal contact, with no other treatment to it as it is unaffected by UV-lithography (Sec. 5.3), it needed to be hard baked, and this was done in a RTP system at 250°C for 1 h. Before placing the samples in a sputtering system they were cleaned in Acetone for 1 min, followed by 1 min in IPA. A 200 A layer of Ti, followed by 2000 A of Au were then deposited on top of the sample. In order to define measuring pads on top of the sample a layer of S1828 was spun onto the samples at 3500 rpm. The resist was soft baked at 115°C for 90 s before being treated to two bursts of UV-light for 10 s each in a UV-lithography system. The pattern was then developed in MF319 for 2 min followed by rinsing in DIW for 1 min. The unwanted metal was then etched away in KI/I<sub>2</sub> for 2 min, rinsing the samples in DIW for 1 min before following up with 10 s in BOE 1:10 JT Baker and another rinsing step in DIW for 1min. Lastly the unwanted S1828 was removed with Acetone for 1 min, followed by 1 min in IPA.

#### 4.4 Investigating the adoption of S1818

As the properties of BCB were being questioned, a design void of BCB was instead favoured. As shown during earlier attempts to manufacture the desired device [15] S1818 could be used as an isolating inter-wire medium. A design utilizing S1818 was previously discarded due to the increased manufacturing times, as well as an abundance of cracks showing up in the S1818 film during processing. The cracks were thought to be able to enable the deposited metal contact to create leakage paths, and were thus heavily opposed. In order to avoid cracking a new design was created. Instead of having a uniform S1818 film covering the whole sample, a lithography step would be carried out, creating localized platelets of S1818 in the device areas. A decrease in the are covered by S1818 was thought to decrease the strain introduced to the S1818, thus lowering the probability of cracking. A layer of SiO<sub>2</sub> was also used in parallel with the S1818 to ensure separation between wires, as well as no capacitance occurring from side-contacted

wires. Simple schematics of the intended device can be seen in figure 17.

Figure 17: Schematic depicting the design used for the intended device, utilizing S1818 as the isolating medium.

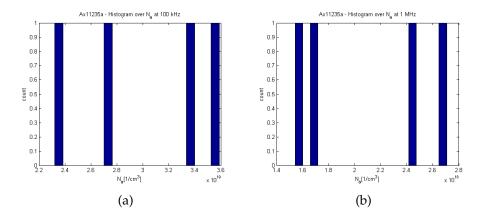

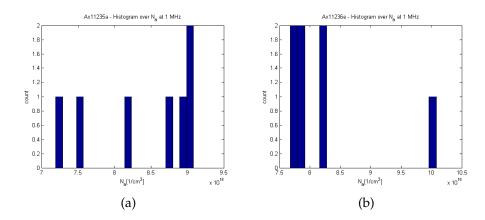

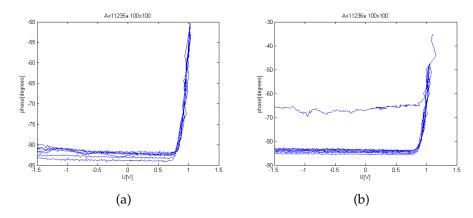

In order to manufacture the device described, 3 samples were prepared. Among the three samples, one (Ax11235a) had nanowires that had had psegments grown under conditions with a molar fraction of  $6.3 \cdot 10^{-7}$  DEZn, and the other two (Ax11236d and Ax11236e) had been grown under conditions with a molar fraction of  $2.1 \cdot 10^{-7}$ . See Appendix F for more details. As the processing method is similar to the one presented in 4.2 it will be summerized in the table below.

| Design IV                                                                                            |

|------------------------------------------------------------------------------------------------------|

| Nanowire Au seed particle removed:                                                                   |

| $3x(20 \text{ s } H_2SO_4 \text{ 1:}10 + 10 \text{ s DIW} + 20 \text{ s KI}/I_2 + 10 \text{ s DIW})$ |

| Cleaned backside with IPA + rinse in Acetone for 1 min + 1 min IPA                                   |

| ALD: $50-100 \text{ nm } SiO_2 + 5 \text{ nm } Al_2O_3$                                              |

| Spin-coat S1818 @ 3000 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| RIE, 15 sscm O <sub>2</sub> , 50 W, 2900-3000 s                                                      |

| Etch SiO <sub>2</sub> : 186 s BOE 1:10 JT Baker + 1 min DIW                                          |

| Strip S1818: 2 min Acetone + 1 min IPA                                                               |

| Spin-coat S1818 @ 3000 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| UV-lithography: 2x 7.5 s exposure (1 min between exposures)                                          |

| Develop: 2 min MF319 + 1 min DIW                                                                     |

| Hard-baking S1818: 200°C for 40 min + 10 min cooling down                                            |

| RIE, 15 sscm O <sub>2</sub> , 50 W, 2300-2450 s                                                      |

| Spin-coat S1828 @ 3500 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| UV-lithography: 2x 10 s exposure (1 min between exposures)                                           |

| Develop: 2 min MF319 + 1 min DIW                                                                     |

| Hard-baking S1828: 200°C for 40 min + 10 min cooling down                                            |

| RIE, 15 sscm O <sub>2</sub> , 50 W, 100 s                                                            |

| Ecth natural oxide: 1 min $H_2SO_4$ : $H_2O$ 1:10 + 1 min DIW                                        |

| Sputter 200 Å Ti + 2000 Å Au                                                                         |

| Spin-coat S1828 @ 3500 rpm for 60 s, soft baked for 90 s @ 115°C                                     |

| UV-lithography: 2x 10 s exposure                                                                     |

| Develop: 2 min MF319 + 1 min DIW                                                                     |

| Au-etch: 2 min KI/ $I_2$ + 1 min DIW                                                                 |

| Residue-etch: 10 s BOE 1:10 JT Baker + 1 min DIW                                                     |

| Strip S1828: 1 min Acetone + 1 min IPA                                                               |

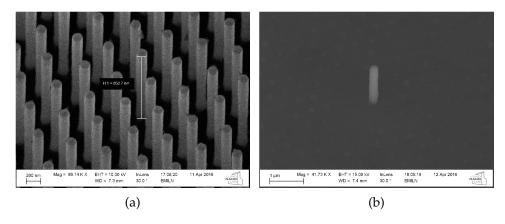

It was found that the deposited  ${\rm SiO_2}$  layer was 50-100 nm thick. The variation in thickness can be seen in figure 18a, where the S1818 has been etched back using an RIE system for 2900 s.

As shown in figure 17 platlets of S1818 needed to be created before applying the S1828 layer (this differs from previous designs). The difference between an S1818 covered area and a non-covered area (outside of platlet) is shown in figure 19.

Figure 18: (a):Ax11236d after 2900 s of RIE, before  $SiO_2$  etch. The  $SiO_2$  caps covering the nanowires can be seen protruding the S1818 with ~200 nm. (b): After  $SiO_2$  etching using BOE 1:10 JT Baker the caps have been removed.

Figure 19: The edge of one of the S1818 platelets on Ax11235a. Outside the S1818 area (top of the image) the covering  $SiO_2$  can be seen, but inside the area (bottom of image) only the protruding top segment ( $\sim$  300 nm) of the nanowires is visible.

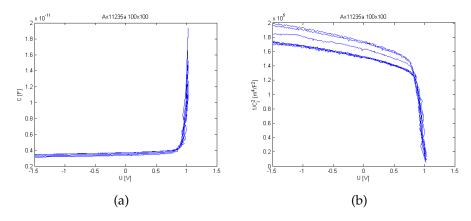

Electrical measurements on the finished devices; IV- as well as CV-measurements were carried out on a probestation. See 5.4 for measurements.

#### 5 Results

In this section the data from the previously described experiments (4) will be revealed and analyzed in an attempt to further increase the understanding for the intention of this project.

#### 5.1 Previous Device Design

As the purpose of doing single nanowire contacting was to determine if the earlier results[15] were due to e.g. radial overgrowth on the nanowires, I-V measurements were carried out. The sample with two contacts applied to each individual nanowire (intended for 2-probe measurements) had a very bad ratio of measurable nanowires. This was revealed to be due to bad contacts, as the contacts had collapsed (Fig. 20) while they were grown. The reason behind this is thought to have been a too generous amount of metal being deposited to make the contacts. Thus only two measurements could be carried out on the first sample. The breaking of the contacts was thought to be avoidable if the nanowires were partially emerged in resist before the contacts were applied.

Figure 20: A collapsed contact, a fracture in the contact can be seen at the edge of the nanowire/contact interface. Failure is thought to be due to weight of the contacts, as a result of too generously chosen thickness (~250 nm). The metal contact appears brighter than the underlying nanowire in the image.

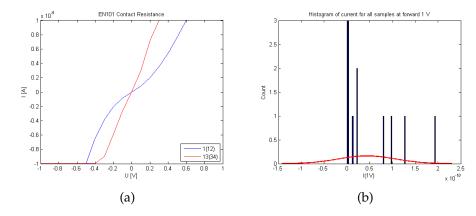

As the second sample contained more contacts per each individually contacted nanowire (intended for 4-probe measurements) a higher yield of measurable nanowires were obtained. The measurements (Fig. 23) showed clear diodic behaviour, and concerns regarding the possibility that the nanowires would have been subjected to radial overgrowth during the growth of the n-doped segment could be discarded for the moment. As the contacts were subject to the same type of collapse as the sample with two contacts per nanowire, the existence of a nanowire with four intact contacts were not observed. For two of the nanowires two intact contacts existed on the same doped segment, the I-V measurements are displayed in figure 21a. The resistance was calculated to be 75 k $\Omega$ , 31 k $\Omega$  respectively. These values strengthen our belief that contacts that satisfy our needs have been formed. Unfortunately, after analysing the polarity of the nanowires it was determined that both of these measurements had been performed on the n-doped segment, generally thought to form good contact. At the time no conclusions about the properties of the more troublesome p-doped segment could be made.

Figure 21: (a): The measured current over contacts located on the n-doped segment of the nanowires. (b): The current for all 2-probe nanowires at 1 V. The data has been altered to take polarity in to account. The red curve symbolizes the distribution, with an average around  $0.5 \cdot 10^{-10}$  A.

The measured current levels over the p-n junctions, displayed in figure 21b, were compared with results obtained through simulations in *COMSOL: Multiphysics* 5.0, as well as an evaluation tool available at *nanoHUB*[19]. The measured values of the current at 1 V were found to be in the range of 1/10 of the simulated values (Appendix A). As the real system can

contain e.g. series resistance, not included during simulations, the obtained measurement reassures us that the nanowires' properties are close to what is intended. Thus concerns regarding radial overgrowth were once again discarded. The nanowires showed a rectification ratio of, at best, 388, and a mean ideality factor (3.6) of ~4.49 (for more data see Appendix B).

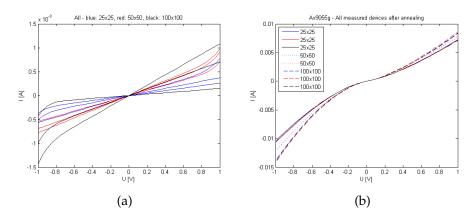

Figure 22: (a): The I-V characteristics for working devices of various sizes, blue are for the smallest ( $25x25 \ \mu m^2$ ) device size, red is the  $50x50 \ \mu m^2$  devices, and black is the  $100x100 \ \mu m^2$  devices. (b): The current through device Ax9055g after attempted curing of the BCB.

The measured values for the bonded single nanowires were then compared to the current of the full device. In order to compare the two systems the single nanowire measurements had to be scaled up with a factor representing the number of nanowires a window of the devices contained. The density of wires can be calculated using equation 33, where  $\rho$  is the density, and l is the pitch between wires.

$$\rho = \frac{2}{3} \frac{\sqrt{3}}{l^2} \tag{33}$$

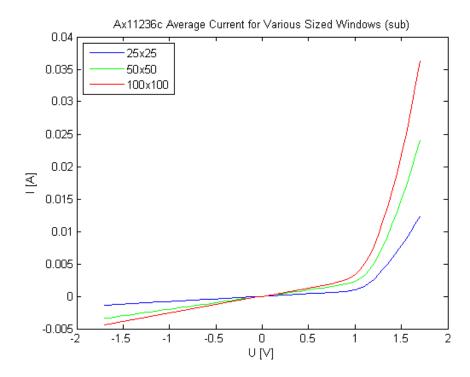

The density was calculated using a pitch of 500 nm, resulting in  $2.85 \cdot 10^3$ ,  $1.15 \cdot 10^4$  and  $4.6 \cdot 10^4$  nanowires for windows of sizes  $25x25 \, \mu m^2$ ,  $50x50 \, \mu m^2$  and  $100x100 \, \mu m^2$  respectively. As the average current (fig. 21b) at 1 V for a single nanowire were scaled up and compared to the current observed in the finished devices (fig. 22a), it was discovered that the device current is a factor of  $10^3$  higher than the scaled up current. This causes us to believe that there is a leak current present in the device. As the devices display linear behaviour between -0.6 V and 0.6 V (fig. 22a), a parallel resistance

behaviour in conjuncture with the diodic behaviour of the p-n junction was assumed. Hence, measurements of the resistance of two devices, as well as the resistance between them were conducted. The two devices displayed an internal resistance of  ${\sim}1~k\Omega$  each, and an inter-device resistance of  ${\sim}400~\Omega$ . As it is expected that the inter-device resistance should be in the range of  $P\Omega$  if passing through the BCB (Appendix E) or atleast 2  $k\Omega$  if passing through the nanowires (series of two  ${\sim}1~k\Omega$  devices), the measurements act to further strengthen the idea that there is unwanted parallel resistance in the devices.

Figure 23: The logarithm of the current through a single nanowire as a voltage is applied.

During the measurements performed under the new parameters described in 4.1 (current measured for biases between -1 V and 1 V) it was found that the attempted curing of the BCB had caused the devices to further behave as a resistor (fig. 22b). As the resist was cured after metal contacts had been applied there is the possibility of a tear between resist and contact. A tear could cause the nanowires to become disconnected

from the metal contact. If there are shunt paths/leakage paths the measured current will behave more like that for a resistor (as the nanowires becomes disconnected the diodic behavior contribute less to the measured signal). However, this would also mean less of a current, and as there is still an observable current the problem is likely that of an alternative origin.

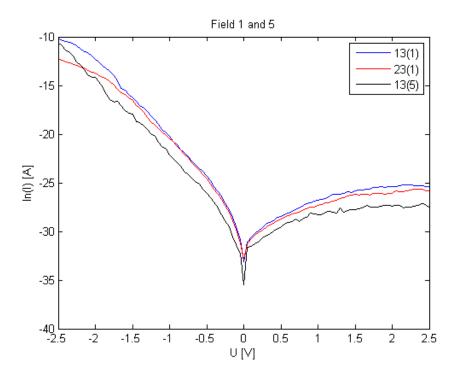

From the measurements carried out on single nanowires for an applied bias ranging between -2.5 to 2.5 V, a reduction of measurable nanowires were observed, and the data collected from the still measurable nanowires is displayed in figure 23. From the data it was deduced that the ideality factor was  $\sim$ 4.92, and the mean rectification (calculated for -2 V and 2 V) was calculated to be  $\sim$  4.16·10<sup>5</sup> (for more data see Appendix B). The ideality factor lies between 1 and 2 for an model diode, and the fact that the ideality factor is larger than 2 suggests that there are imperfections in the device, e.g. high series resistances from nonohmic contacts. It could also come from recombination at the p-n junction, which is also highly likely as InP is (as previously stated) suited for solar cells. It is worth noting that for the type of devices presented throughout this report the typical ideality factor lies above 2 for reasons just stated.

#### 5.2 IV Characteristics of a BCB-based Device

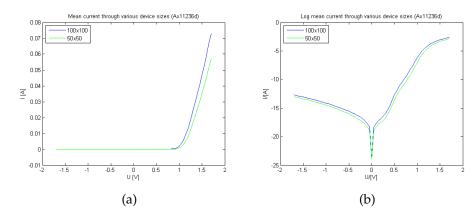

As was discovered during early measurements on old devices[15] a large leakage at low voltage was observed (5.1, Fig. 22a). As the current at low voltages was significantly larger than the model predicted (Appendix A) it was concluded to be signs of parallel resistance in the devices. The source of the parallel resistance was thought to be either deficiency in the nanowires, or the inter-nanowire isolating layer of BCB. The properties of the nanowires were investigated (5.1), and from the data collected (Fig. 23) it was found that the nanowires could not be the source of the parallel resistance.

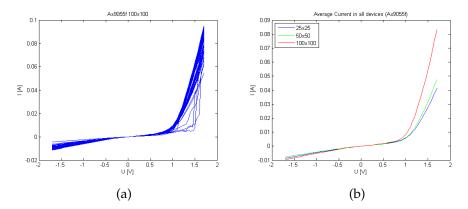

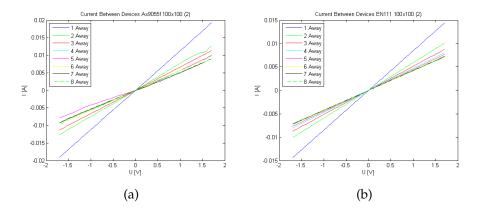

In order to investigate the properties of the isolating BCB layer a second device design was used (4.2) . Electrical measurements were first carried out on the manufactured device. From the measurements it was deduced that the processing had been successful, due to consistently measured currents and clear diodic behaviour in various devices (Fig. 24a). This also deters the idea of a poorly defined junction, as during processing areas with different degrees of etched back  $SiO_2$  were observed, but the measured data is consistent for various devices over the full sample. In accordance to  $Ohm's\ Law$  we expect to see the current increase with a factor of 4 as device size increases. However, when the data shown in figure 24b is observed a

Figure 24: (a): The current measured through devices of the size  $100x100 \mu m^2$ . The graph depicts data collected from 80 devices. (b): The average currents measured through different device sizes.

different behaviour is apparent (e.g. the current only scales with a factor of 2 between the  $50x50~\mu m^2$  and the  $100x100~\mu m^2$  devices). This behaviour indicates that the current does not only scale with the increasing number of nanowires connected to a larger device area, but also with some other factor, thus furthering the idea of leakage current.

Figure 25: (a): The current measured through Si planar substrate with a layer of BCB spun on it. The BCB had been etched in a RIE system for 30 s ( $R = 262 \Omega$ ). (b): Si planar substrate, etched for 60 s ( $R = 219 \Omega$ ).

As the SiO<sub>2</sub> layer is preventing current from directly moving through the BCB from the top contact to the bottom contact, potential leakage current

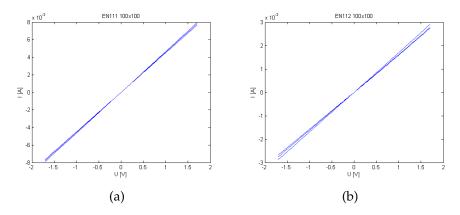

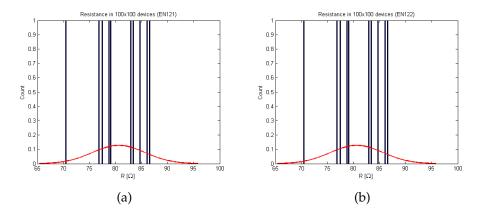

through the BCB layer can not be measured in the sample. In parallel to the sample two planar samples with BCB spun on top of a Si substrate had been prepared (4.2). This was used to measure possible currents through the BCB layer. Measurements (Fig. 25) acted to strengthen the idea of a current through the BCB layer. The resistance for a  $100 \times 100 \ \mu m^2$  device calculated from the obtained data was ~270  $\Omega$ , ~320  $\Omega$  for a  $50 \times 50 \ \mu m^2$  device, ~310  $\Omega$  for a  $25 \times 25 \ \mu m^2$  device, 262  $\Omega$  for EN111 and 219  $\Omega$  for EN112 (Appendix D), undermining the isolating properties of BCB (Appendix E).

Since the front contact is connected to the back contact through nanowires for the InP sample it is hard to distinguish any parallel current originating from the BCB layer from that originating from the InP nanowires. As such, measurements were also taken between neighbouring devices to see if the current scales with distance. Results can be observed in figure 26, and it is indicated that there is leakage between devices that can not be correlated with the nanowires' properties as the interdevice resistance is significantly lower than the advertised PQ[31]. In order to rule out the possibility of the devices being physically in contact, through e.g. a thin metal layer, SEM investigation was carried out, revealing well defined devices, with the sought architecture, as can be seen in figure 5.2.

Figure 26: (a): The current measured between devices on InP sample Ax9055f. (b): The current measured between devices on Si planar sample EN111 (without nanowires).

Suspicions regarding the devices being in contact with one another through the metal contact were thwarted by the well-defined metallic contacts observed (Fig. 27b). From the well-defined contacts, and the consistent interdevice resistance that was observed (Fig. 24a & 25), it was concluded

that further investigation of the isolating material had to be carried out, and it was concluded that a design void of BCB (4.3) could be used in order to determine if BCB was behind the poor electrical properties, or if the issue lied somewhere else.

Figure 27: (a): SEM image of a finished device on sample Ax9055f. (b): The interface of the metallic Au contact and the underlying BCB layer, deposited on top of the device. (c): The edge of the contact area of the device. (d): The ends of the nanowires inside the contact area of the device, covered with a metallic Au contact.

#### 5.3 Further BCB Investigation