### Development of III-V RF Nanowire MOSFETs

JOSEFINE ROST

ANNA WAGNSTRÖM

MASTER'S THESIS

DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY

FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

### Development of III-V RF Nanowire MOSFETs

Josefine Rost

tna13jro@student.lu.se

Anna Wagnström

tna13awa@student.lu.se

Department of Electrical and Information Technology Lund University

> Supervisor: Erik Lind Co-supervisor: Fredrik Lindelöw

Examiner: Mats Gustafsson

June 14, 2018

### Abstract

The silicon MOSFET is one of the most important components used in modern electronics. The pursuit to continue fulfilling Moore's law by scaling transistors to even smaller sizes have driven the development forward for CMOS technologies and new approaches have been necessary. These include changing the geometry of the devices for even higher performance, like creating 3D structures (finFETs or tri-gates) for better electrostatic control. With the aggressive scaling, power dissipation has become an increasing problem in CMOS applications. One way to combat this is by introducing a material in the channel with superior transport properties, like InGaAs.

As the development of MOSFET technology for CMOS applications continue, devices with excellent high frequency performance have been demonstrated. Thus, the MOSFET has also emerged as a possible alternative to the HEMT in high frequency applications. The desirable properties of an RF transistor differs somewhat from CMOS transistors, as stability and high gain are more important than size and power dissipation.

In this thesis, lateral InGaAs nanowire MOSFETs for RF applications with different geometries have been fabricated and characterised. The transistors exhibit a highest  $f_t$  and  $f_{max}$  of 150 GHz and 280 GHz respectively. The devices were fabricated in a cleanroom environment and measured in both DC and RF. Small signal modelling was performed using Matlab. A model of the devices was also made in COMSOL multiphysics and simulations were performed to investigate the effect of different geometries on the gate-source and gate-drain capacitance. The results form the simulation showed similar values to the fabricated devices. This indicates that the model was accurate.

The fabrication yielded very few working devices compared to what was fabricated. Some of the working devices showed performance compared to similar devices that have been demonstrated. Though a few devices show promising RF characteristics, the fabrication process needs to be refined.

## Populärvetenskaplig sammanfattning

Om du skulle gissa på hur många komponenter det finns i din mobiltelefon, vad hade du gissat på då? 10? 100? 1 000 000? Skulle du tro mig om jag säger att svaret är runt 200 miljarder? För det är faktiskt så.

I din telefon och i all elektronisk utrustning runt omkring dig finns miljontals små elektroniska byggdelar som gör vårt tekniska samhälle möjligt. Snabba, smarta och kraftfulla datorer och mobiltelefoner är vi vana vid att ha med oss varje dag och det finns en konstant strävan till förbättring. Komponenten som har gjort denna tekniska utveckling möjlig är transistorn, som är en väldigt mångsidig byggsten. Trots dess minimala storlek på endast några nanometer i gatelängd (nu pratar vi om storlek tjockleken av ett hårstrå delat i 100 000 delar!) är transistormarknaden en miljardindustri. Gatelängd är ett mått som används för att jämföra storleken på olika transistorer, och motsvarar sträckan strömmen måste färdas i transistorn. Om det ska få plats 200 miljarder komponenter i en mobiltelefon behöver de vara rätt så små om du ska orka bära med dig den, inte sant?

Transistorn kan både användas som av/på-knapp i logiska kretsar och som förstärkare, beroende på hur den byggs. För hur konstigt det än låter att så små saker kan byggas så är det faktiskt sant! I väldigt rena miljöer, med stora och dyra maskiner, tillverkas transistorer med en rad komplicerade men väl beprövade metoder. Beroende på hur man designar geometrin och vilka material man använder i byggandet får transistorn olika egenskaper. Den vanligaste typen av transistor kallas MOSFET och är vanligtvis baserad på grundämnet kisel, vilket är superbra för logiska användningsområden. Men om man ändrar materialet till en sammansättning av andra grundämnen, och ändrar geometrin lite, kan man få en MOSFET som passar bra även till andra applikationer, så som förstärkare vid höga frekvenser.

I detta examensarbete har vi tillverkat transistorer för högfrekvensapplikationer med en gatelängd mellan 40 och 70 nanometer som uppvisar goda egenskaper vid höga frekvenser. För en transistor med 40 nanometer gatelängd uppmättes en högsta användningsfrekvens till 153 GHz för strömförstärkning och motsvarande 278 GHz för effektförstärkning. Transistorerna som tillverkades är MOSFETs baserade på en förening mellan indium, gallium och arsenik (InGaAs) och använder nanotrådar för att leda ström. Att använda nanotrådar och InGaAs är båda att föredra för att uppnå höga hastigheter, då elektroner rör sig mindre hindrat i denna kombinationen.

Målet var att jämföra hur olika geometrier skulle påverka prestandan, och även skapa en bild av hur transistorn kan förbättras för att nå högre frekvenser. Tre olika geometrier designades men bara två av dem gav resultat. Alla transistorer tillverkades i Lund Nano Lab och mättes sedan i både direktström (DC)- och radiofrekvens (RF)-miljö. Resultaten var mycket varierande eftersom många av transistorerna inte fungerade. Trots det har vi visat att transistorerna med de valda materialen och designen fungerar och visar lovande förutsättningar för att bli bättre!

## Acknowledgements

We would like to thank our supervisors Erik Lind and Fredrik Lindelöw. Fredrik, thank you for the extreme patience, countless lab hours and unlimited positivity. Also, for the Kexchoklad. Thank you Erik for your guidance and support. We would also like to thank the remaining members of the Nanoelectronics group, as well as the LNL staff.

Dedicated to Sophie Wagnström.

## Abbreviations & Symbols

### Abbreviations

$Al_3O_2$  Aluminium Oxide

**ALD** Atomic Layer Deposition

Au Gold

**BOE** Buffered Oxide Etch

CMOS Complementary Metal Oxide Semiconductor

**DC** Direct Current

DIBL Drain Induced Barrier Lowering

EBL Electron Beam Lithography

FinFET Fin Field-effect Transistor

$\begin{array}{ll} \mathbf{H_3PO_4} & \quad \text{Phosphoric Acid} \\ \mathbf{H_2O_2} & \quad \text{Hydrogen Peroxide} \\ \mathbf{HCl} & \quad \text{Hydrochloric Acid} \end{array}$

**HEMT** High Electron Mobility Transistor

**HfO**<sub>2</sub> Hafnium Dioxide

HSQHydrogen SilsesquioxaneInGaAsIndium Gallium ArsenideInPIndium PhosphideIPAIsopropanol Alcohol

LRRM Load-Reflect-Reflect-Match

MOCVD Metalorganic Chemical Vapor DepositionMOSFET Metal-oxide-semiconductor field-effect transistor

$(NH_4)_2S$  Ammonium Sulfide

Pd Palladium

**PMMA** Poly(methyl methacrylate)

RF Radio Frequency

SEM Scanning Electron Microscopy

Ti Titanium

TMAH Trimethylammonium hydroxide

### Symbols

$egin{array}{ll} C_{gd} & \operatorname{Gate-drain Capacitance} \ C_{gg} & \operatorname{Total Gate Capacitance} \ C_{gs} & \operatorname{Gate-source Capacitance} \ C_{sd} & \operatorname{Source-drain Capacitance} \ C_{ox} & \operatorname{Oxide Capacitance} \ f_T & \operatorname{Cutoff Frequency} \ \end{array}$

$f_{max}$  Maximum Oscillation Frequency

$\begin{array}{ll} g_m & \text{Transconductance} \\ g_d & \text{Output conductance} \\ h_{21} & \text{Current Gain} \\ L_g & \text{Gate Length} \\ MSG & \text{Maximum Stable} \end{array}$

${\cal M}{\cal A}{\cal G}$  Maximum Available Gain

$egin{array}{ll} R_G & {

m Gate \ Resistance} \ R_D & {

m Drain \ Resistance} \ R_S & {

m Source \ Resistance} \ U & {

m Unilateral \ Gain} \ V_{gs} & {

m Gate \ Voltage} \ V_{ds} & {

m Drain \ Voltage} \ V_T & {

m Threshold \ Voltage} \ \end{array}$

$\boldsymbol{W_m}$  Mesa width

## Table of Contents

| 1  | Introduction             |                             |  |  |  |

|----|--------------------------|-----------------------------|--|--|--|

| 2  | MOSFET                   |                             |  |  |  |

|    | 2.1                      | Background                  |  |  |  |

|    | 2.2                      | MOSFET Operation            |  |  |  |

|    | 2.3                      | III-V Nanowire MOSFET       |  |  |  |

|    | 2.4                      | III-V Materials             |  |  |  |

|    | 2.5                      | RF Applications             |  |  |  |

| 3  | Fabi                     | ication                     |  |  |  |

|    | 3.1                      | Device Design               |  |  |  |

|    | 3.2                      | Experiment setup            |  |  |  |

|    | 3.3                      | Processing                  |  |  |  |

| ļ  | Simulations              |                             |  |  |  |

|    | 4.1                      | Pad capacitance             |  |  |  |

|    | 4.2                      | Nanowire capacitance        |  |  |  |

|    | 4.3                      | Device capacitance          |  |  |  |

|    | Measurements & Modelling |                             |  |  |  |

|    | 5.1                      | DC measurements             |  |  |  |

|    | 5.2                      | RF measurements & modelling |  |  |  |

|    | 5.3                      | Limitations                 |  |  |  |

| •  | Resi                     | ılts & Analysis             |  |  |  |

|    | 6.1                      | Processing                  |  |  |  |

|    | 6.2                      | DC measurement & analysis   |  |  |  |

|    | 6.3                      | RF analysis of sample V     |  |  |  |

| ,  | Con                      | clusions                    |  |  |  |

| ₹e | feren                    | ces                         |  |  |  |

| Λ  | Fabrication methods      |                             |  |  |  |

| A.1 | Spin coating              | 55 |

|-----|---------------------------|----|

| A.2 | Electron Beam Lithography | 55 |

| A.3 | Plasma ashing             | 56 |

| A.4 | Atomic Layer Deposition   | 56 |

| A.5 | Evaporation               | 56 |

# List of Figures

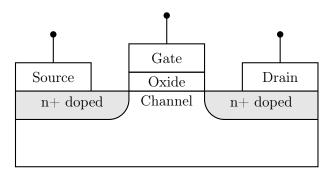

| 2.1  | Schematic of a planar n-type MOSFET structure                                                                                              | 4  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | MOSFET band structure in the off-state                                                                                                     | 4  |

| 2.3  | MOSFET band structure in the on-state                                                                                                      | 4  |

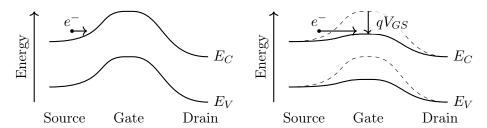

| 2.4  | Nanowire MOSFET structure                                                                                                                  | 5  |

| 2.5  | Side view of the nanowire MOSFET structure                                                                                                 | 5  |

| 3.1  | Device schematic                                                                                                                           | 7  |

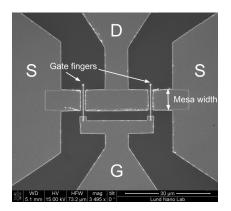

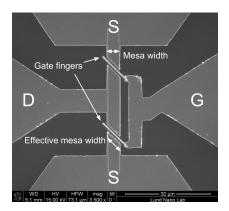

| 3.2  | SEM overview image of a finished A-device with source (S), drain (D), gate (G) and mesa width marked                                       | 8  |

| 3.3  | Device type A                                                                                                                              | 8  |

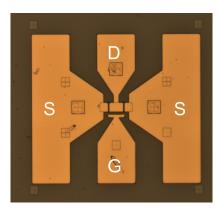

| 3.4  | Device type B                                                                                                                              | 8  |

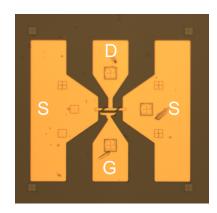

| 3.5  | Device type C                                                                                                                              | 8  |

| 3.6  | SEM overview image of a finished $B$ -device with source (S), drain (D), gate (G), mesa width and effective mesa width marked. This layout |    |

|      | also applies to the <i>C</i> -devices                                                                                                      | 9  |

| 3.7  | Pad layout of device type A                                                                                                                | 10 |

| 3.8  | Pad layout of device type $B$ and $C$                                                                                                      | 10 |

| 3.9  | Contact growth schematic with HSQ dummy gate                                                                                               | 12 |

| 3.10 | A B-type device a) before and b) after contact regrowth                                                                                    | 13 |

| 3.11 | Contact ledge growth schematic with second HSQ dummy gate                                                                                  | 13 |

| 3.12 | A $52^{\circ}$ tilted SEM image of a T-gate                                                                                                | 15 |

| 4.1  | Model geometry for the pad capacitance simulation                                                                                          | 18 |

| 4.2  | Gate to drain pad capacitance                                                                                                              | 18 |

| 4.3  | Finished gate contact layout with extended gate pad sections                                                                               | 19 |

| 4.4  | Side view of nanowire model geometry                                                                                                       | 19 |

| 4.5  | Gate view of nanowire model geometry                                                                                                       | 19 |

| 4.6  | Parasitic capacitance per nanowire                                                                                                         | 20 |

| 4.7  | Model side view                                                                                                                            | 21 |

| 4.8  | Model gate stack view                                                                                                                      | 21 |

| 4.9  | Gate to source capacitance for different ledge heights and widths $\ \ .$ .                                                                | 22 |

| 4.10 | Electric potential cross-section plot for different ledge widths a) 0 nm,                                                                  |    |

|      | b) 5 nm and c) 10 nm                                                                                                                       | 23 |

| 5.1  | Transfer characteristics                                                        | 25 |

|------|---------------------------------------------------------------------------------|----|

| 5.2  | Output characteristics                                                          | 26 |

| 5.3  | Schematic describing the intrinsic and parasitic capacitances in MOS-           |    |

|      | FET structure.                                                                  | 28 |

| 5.4  | A hybrid- $\pi$ model of a MOSFET                                               | 31 |

| 6.1  | A overview of a finished A device with mesa 7 $\mu$ m                           | 33 |

| 6.2  | A overview of a finished $B$ device with mesa 3.5 $\mu$ m                       | 33 |

| 6.3  | A SEM image of the nanowire channel of a A-device                               | 34 |

| 6.4  | A SEM image of the nanowire channel of a <i>B</i> -device                       | 34 |

| 6.5  | SEM image of under etch on a <i>B</i> -type device                              | 35 |

| 6.6  | SEM image of a misaligned <i>B</i> -device                                      | 36 |

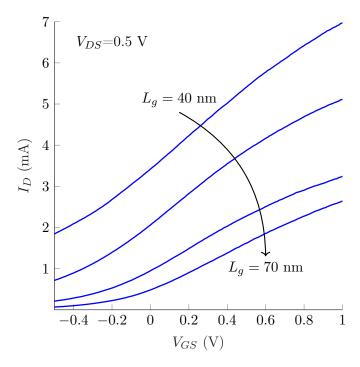

| 6.7  | $I_D	ext{-}V_{GS}$ curve for devices with gate lengths of 40, 50, 60 and 70 nm  | 39 |

| 6.8  | Output characteristics                                                          | 40 |

| 6.9  | Transfer characteristics                                                        | 40 |

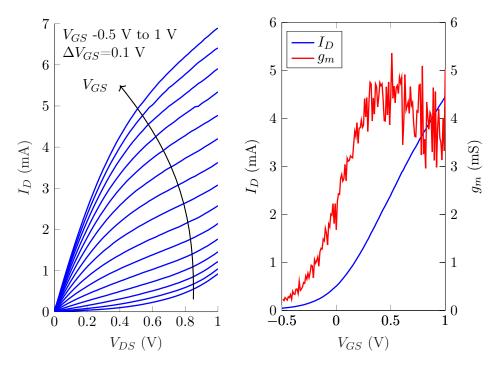

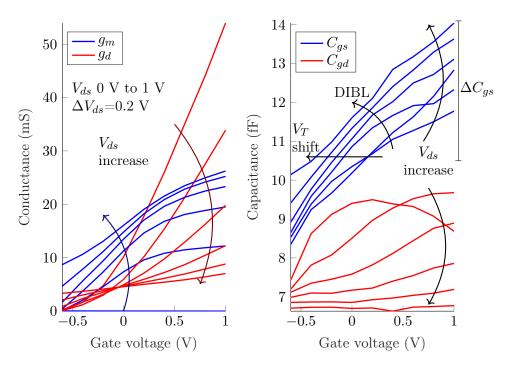

| 6.10 | Extracted transconductance and output conductance for each bias                 | 41 |

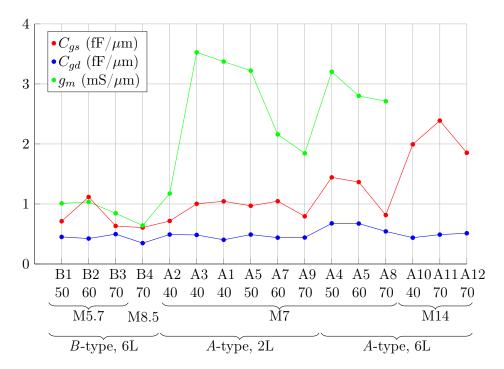

| 6.11 | Extracted gate-source and gate-drain capacitance for each bias                  | 41 |

| 6.12 | Transconductance and capacitances for the devices measured on sam-              |    |

|      | ple V. Device name and gate and mesa dimensions are showed under-               |    |

|      | neath the plot                                                                  | 43 |

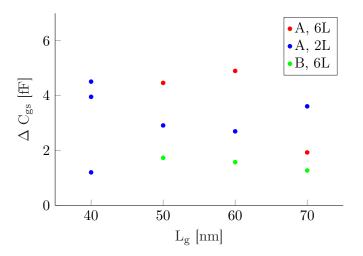

| 6.13 | $\Delta C_{gs}$ against gate length $\ldots \ldots \ldots \ldots \ldots \ldots$ | 44 |

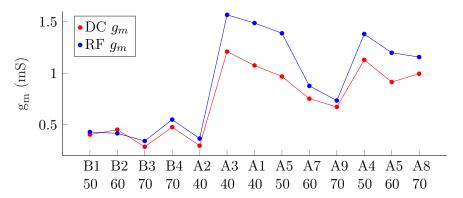

| 6.14 | Transconductance from both DC and RF measurements                               | 44 |

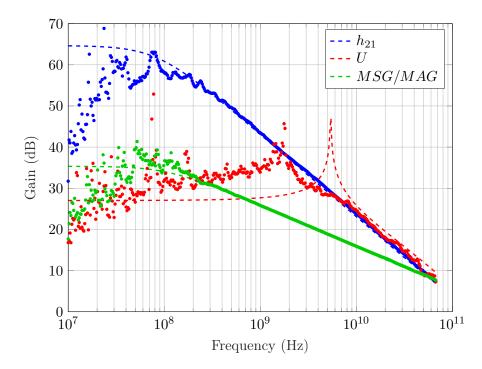

| 6.15 | Current and power gain                                                          | 45 |

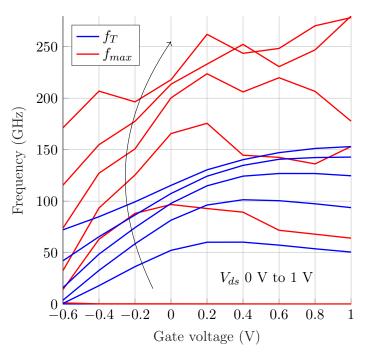

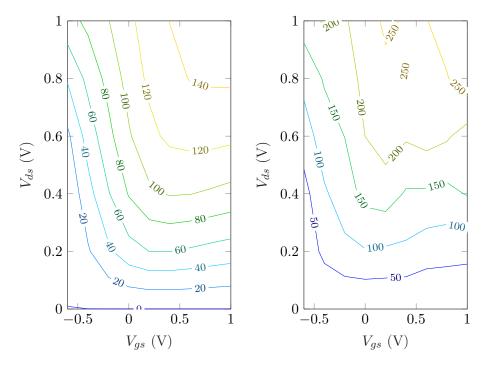

| 6.16 | Extracted cutoff and maximum oscillation frequency for each bias                | 46 |

| 6.17 | Contour plot of $f_T$                                                           | 48 |

| 6.18 | Contour plot of $f_{max}$                                                       | 48 |

## List of Tables

| 3.1 | Mesa widths                                                                                                            | 10 |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Material parameters used in simulations                                                                                | 17 |

| 6.1 | Summary of gate length, mesa width, nanowire design and gate design for measured devices                               | 37 |

| 6.2 | DC results of some devices from sample V                                                                               | 38 |

| 6.3 | RF results of same devices from sample V as presented in previous                                                      |    |

|     | section                                                                                                                | 42 |

| 6.4 | Frequency results of the same devices from sample V as presented in previous section. Gain is given as $MSG$ at 20 GHz | 47 |

### Introduction

Since World War 2, the evolution of electronics has been sky rocketing. The war introduced the need for logical circuits that was used to break enemy codes, as well as good communication systems [1]. This led to a rapid development of electronic devices and with that a higher demand for computing power. The first electrical computer used vacuum tubes as logical components [2]. The problem was that these were both fragile and had a short life span, so something better was needed for the development to continue. This is where the transistors and the third generation of computers came in [1]. The transistors were smaller, more reliable and produced less heat. The computing power increased rapidly and has ever since [3].

The MOSFET (metal-oxide-semiconductor field-effect transistor) has been one of the most important building blocks of modern electronics since it was first invented in 1959 at Bell Labs [4]. MOSFETs today are used for a wide number of applications, ranging from digital CMOS logic to wireless communication [5]. The request for higher performance and more complex circuits challenges the boundaries of the conventional Si MOSFET [6]. To meet these requirements, new approaches need to be taken. One way of increasing the performance of the FET-devices is to change the geometry and material composition of the device, to improve performance without changing the fundamental physics [5]. By changing the material from silicon to another semiconductor, and tweaking the geometry to a non planar device, the performance and speed of the devices can be greatly increased.

As the development of the MOSFET for CMOS applications pushes on, another possible application for the MOSFET has emerged in the RF market. With its scaling potential, good high frequency performance and excellent transport properties, a RF MOSFET that can compete with the HEMT has become a reality [5].

In this diploma work, a take on the III-V nanowire MOSFET is studied and further developed in the quest of reaching even higher performing RF components.

2 Introduction

### 2.1 Background

The first patent for a field-effect-transistor was filed by Julius Edgar Lilienfeld as early as 1926 [7]. After this, researchers at Bell Labs began investigating the properties of semiconductor devices. In 1947 the first transistor was presented by John Bardeen, Walter Brattain and Walter Shockley, a three point contact device with amplification [8]. Shortly after, in 1947, Shockley published a paper describing the p-n junction and the bipolar junction transistor [9]. Bardeen, Brattain and Shockley were in 1956 awarded the Nobel prize in physics "for their researches on semiconductors and their discovery of the transistor effect" [10]. The bipolar transistor is yet today one of the most important semiconductor devices. This discovery was followed by the creation of the metal-oxide-semiconductor field-effect transistor (MOSFET) by Kahng and Atalla which was reported in 1960. This development was possible only after Atalla had discovered a technique for thermal growth of Silicon oxide [4].

The MOSFET and integrated circuits based on the MOSFET make up about 95 % of the semiconductor device market [11]. This popularity was mainly possible due to the rise of the digital computer around the same time. Integrated circuits based on MOSFETs had superior performance compared to other technologies in terms of fabrication cost and scaling. MOSFETs could be scaled down without losing performance, allowing for better performance with lower voltages, lower power dissipation and higher speed. It was this scaling ability that allowed for the rapid growth in computing power as the number of devices per area could be increased for a lower device cost [4].

This transistor downscaling is often referred to as Moore's law from the predictions made by Gordon Moore in his 1965 paper [12]. The publication predicts an exponential increase in the number of transistors per unit area and this trend was followed for many decades. However, as the transistors became smaller, physical limitations challenged the progress. Structures cannot be downsized indefinitely, as eventually they would reach the atomic levels. Simple downscaling is no longer viable, and thus other methods must be used to ensure the continued improvements in transistor performance.

### 2.2 MOSFET Operation

The MOSFET is a three-terminal device. There are two different types, n-type and p-type MOS [11]. Here, only the nMOS will be described as it is the one fabricated in this work. It consists of three metal contacts, gate, source and drain, a p-type semiconductor substrate and two n<sup>+</sup>-doped regions. The pMOS has the same structure, but with an n-type substrate and two p<sup>+</sup>-doped regions [11]. The abbreviation MOS stands for metal-oxide-semiconductor and describes the geometry of the device, shown in figure 2.1. The metal gate contact is separated from the semiconductor channel by an insulating oxide layer. The device is controlled by the field-effect, an electric field that is formed over the oxide as a voltage is applied on the gate. This allows the conductivity of the channel to be controlled by the voltage applied to the gate contact. This is the basic principle of MOSFET operation [11].

Figure 2.1: Schematic of a planar n-type MOSFET structure.

Without a voltage applied to the gate there is an energy barrier preventing charge carriers from moving from source to drain formed by the two p-n junctions between  $n^+$ -doped source and drain and p-type channel. This is illustrated in figure 2.2. When a bias is applied to the gate it creates an inversion layer between the two  $n^+$  regions. This allows for a current to flow from drain to source, if a bias is applied between the source and drain  $(V_{DS})$ . This is shown in figure 2.3.

**Figure 2.2:** MOSFET band structure in the off-state

**Figure 2.3:** MOSFET band structure in the on-state

The bias applied between the gate and source is referred to as  $V_{GS}$ . The threshold where current starts flowing is called  $V_T$ . The transistor is said to be

in the off-state when  $V_{GS}$  is below  $V_T$ , and similarly in the on-state when  $V_{GS}$  is above  $V_T$ .

As stated in section 2.1, improving performance by only scaling down MOS-FETs is no longer feasible. Not only is the scaling limited by the atomic scale, but transistors with short gate length also show so called short-channel effects [11]. This means that the device performance is degraded by e.g. drain induced barrier lowering (DIBL), when the barrier in figure 2.2 is affected by the increase in drain voltage and thus the conductance of the channel is affected [11]. With a high drain voltage, it will no longer be possible to turn off the channel.

This can be counteracted in different ways, e.g. by changing the geometry or changing the material. This is described below.

#### 2.3 III-V Nanowire MOSFET

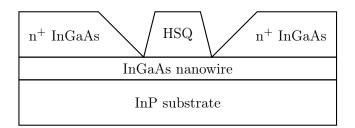

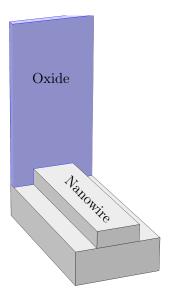

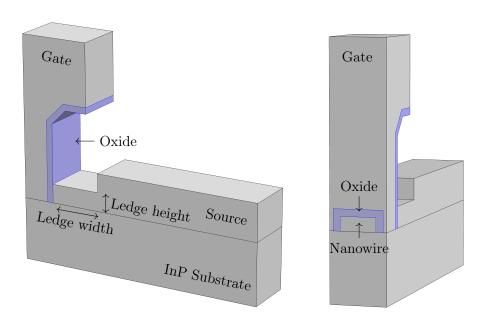

The electrostatic control can be improved by changing the geometry of the gate structure. Instead of only having the gate control the channel from one direction, a multi-gate device can be used, also known as FinFETs or tri-gate devices [5]. Then, the channel is no longer part of the bulk as in the planar MOSFET but a raised "fin". The gate is placed around the channel, providing much better electrostatic control as the contact area is increased without increasing the gate length. Such a device with a nanowire channel is shown in figure 2.4, where the gate stack is shown and in figure 2.5 where the source, gate and drain layout is shown.

Figure 2.4: Nanowire MOSFET structure

**Figure 2.5:** Side view of the nanowire MOS-FET structure

#### 2.4 III-V Materials

Electronics today are mainly silicon based and the combination of silicon and its native oxide remains one of the key material combinations in transistor development [11]. Silicon is abundant, and therefore cheap, and  $SiO_2$  is a stable oxide. These characteristics has made it the foundation for all CMOS technology, and its characteristics and performance is well researched.

However, silicon transistors have some drawbacks. With the aggressive scaling of transistors, power dissipation has become one of the key issues with CMOS performance. To increase performance by scaling, operating voltage needs to be

decreased resulting in a decrease in speed. One solution to this is introducing a material in the channel with a higher carrier mobility than silicon [13]. This is where the III-V compound semiconductors come in.

III-V materials are compounds of elements from group III and V of the periodic table, such as InAs, GaAs, InP and AlAs. They also include the ternary alloys, like InGaAs. These compounds show a wide variety of characteristics and some have unique applications in both optics and electronics [13]. The ternary III-V alloys have another advantage, as properties like mobility, band gap and lattice parameter can be fine-tuned by changing the composition [14]. A few III-Vs show especially high electron mobility, namely InAs and InGaAs, which have demonstrated mobilities up to 10 times that of silicon [13].

A restriction to the development of InGaAs or GaAs MOSFETs has been the poor nature of their respective native oxides. The interface formed when for instance GaAs is exposed to oxygen is highly unstable and has a high interface state density [13], thus impeding the effective modulation of the channel. A major breakthrough was made in 2003, when the first GaAs MOSFET with an ALD deposited  $Al_2O_3$  layer was demonstrated [15].

### 2.5 RF Applications

III-V materials are already successfully used in high frequency applications, for instance in high electron mobility transistors (HEMTs) [11]. The HEMT is a heterojunction device that differs from the MOSFET by using a high band gap semiconductor instead of an oxide barrier [11]. HEMTs also use modulation doping, where that barrier layer is doped except for a narrow region closest to the channel and the channel is undoped. Carriers from the barrier layer will move to the channel, increasing the carrier concentration. This will result in an increased carrier mobility compared to if dopant atoms would sit in the channel, thanks to the increased carrier concentration without any impurity scattering in the channel [11]. III-V HEMTs with cutoff frequencies above 600 GHz and maximum oscillation frequencies above 1 THz have been demonstrated.

However, to further increase the high frequency performance of HEMTs, gate capacitance would need to be increased since the transconductance depends on the gate capacitance. Due to the small band gap of the barrier layer (compared to an insulator), scaling is difficult without significantly increasing the gate leakage current. MOSFETs, which use an oxide barrier that allows for much more aggressive scaling, could therefore be a viable option for high frequency applications [5].

Manufacturing a transistor from scratch takes time and involves many processing steps. This chapter describes the geometry and fabrication of the InGaAs nanowire MOSFETs processed in this diploma work. Three different device geometries were fabricated, two of which have never been fabricated by the Nanoelectronics group before, on a total of six samples. Five of the samples were measured in DC, but only the best performing sample was studied at high frequencies and analysed in chapter 6. The different geometries are called A, B and C and are introduced in the section below.

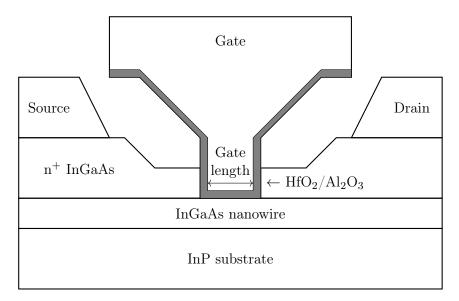

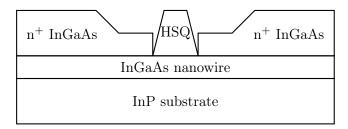

Figure 3.1: Device schematic

### 3.1 Device Design

This diploma work builds on previously processed devices by the Nanoelectronics group, here referred to as type A. Several papers have been published on lateral In-GaAs nanowire MOSFETs by the group with very promising results [5]. Nanowires

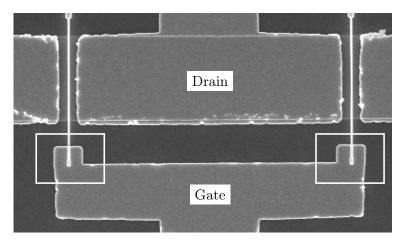

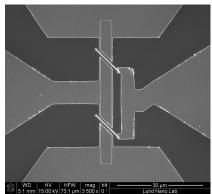

exhibit a low crystal defect density, which allows for low surface scattering and thus higher electron mobility. By placing the channel on top of the substrate, the electrostatic control is increased significantly compared to a conventional buried channel, which also is a perk of using nanowires. This makes nanowire channels an interesting challenger to the planar MOSFET and other fin structures. A schematic side view of the devices is shown in figure 3.1. A top view of a fabricated A-device can be seen in figure 3.2. Here, source drain and gate is marked, as well as the structure called mesa, which is described later in this chapter.

**Figure 3.2:** SEM overview image of a finished *A*-device with source (S), drain (D), gate (G) and mesa width marked

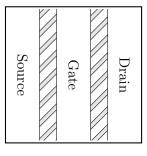

For these devices, the nanowires are grown parallel in an array with a density of 14.3 nanowires per  $\mu m$  gate width. The direction of the nanowires in relation to the InP substrate creates {110} crystal facets on the nanowire sides. The source and drain contacts are grown on each sides of the arrays, resulting in {111}-facets of the InGaAs contact layers. The gate is placed over the arrays with a 45° angle with respect to the nanowires. How the nanowires are orientated under one of the gate fingers are visualized in figure 3.3, together with source and drain contacts. The nanowires are show in grey.

To explore new grounds and hopefully achieve higher performance, the geometry of these previously fabricated devices were altered.

**Figure 3.3:** Device type A.

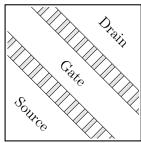

**Figure 3.4:** Device type B.

**Figure 3.5:** Device type C.

The first alteration was to rotate the gate  $45^{\circ}$  with respect to the A-gate. This makes the gate orthogonal to the nanowires. This is visualized in figure 3.4. The rotation of the gate, and thus source and drain contacts, results in new crystal facets of the contact layer. This device design is expected to create  $\{110\}$  crystal facets on the contact layer as well. The nanowires stay exactly the same as in type A. The rotation of the gate results in a higher density of nanowires in the channel per gate width, which is clearly visible in figure 3.4. The new nanowire density becomes  $14.3 \cdot \sqrt{2} = 20.2$  per  $\mu m$  gate width. A higher nanowire density should result in higher currents and thus higher transconductance, which is a desired RF metric. This could result in lower electron scattering and thus higher transconductance. These devices are called type B. In figure 3.6 a top view of a finished B-device can be seen. Here, the contacts are marked, as well as the mesa and effective mesa widths.

**Figure 3.6:** SEM overview image of a finished *B*-device with source (S), drain (D), gate (G), mesa width and effective mesa width marked. This layout also applies to the *C*-devices.

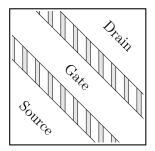

The second alteration and third geometry that was examined used the gate rotation from B, but with the nanowires rotated  $45^{\circ}$  as well. This layout can be seen in figure 3.5. The contacts are the same as in B. However, this new nanowire orientation should result in  $\{111\}$ -facets with a  $56^{\circ}$  angle, the same facet as for the contact layer in A. The nanowire density is the same as for A, but with new crystal facets. The current from drain to source has a straight path through the nanowires, without any bends that are very distinct in A and B. The interesting analysis for this device type would be if there is any difference in performance for the different crystal facets. One could argue that steeper walls would result in a larger cross sectional area and thus lower resistance in the channel. Another difference is that there is probably a different interface trap density,  $D_{it}$ , of the  $\{111\}$  facets compared to the  $\{110\}$ . These devices are called type C.

To be able to measure the DC and RF performance, pads connected to the contacts are needed. The finished pad layout can be seen in the optical microscopy images in figure 3.7 and 3.8. All three transistor types were designed with two gate fingers connected to one common gate contact, two source contacts and one drain contact. The layout of the gate pad was the result of a COMSOL simulation

presented in chapter 4.

**Figure 3.7:** Pad layout of device type *A*

**Figure 3.8:** Pad layout of device type *B* and *C*

### 3.2 Experiment setup

To be able to compare a maximum number of parameters of the three different device types introduced above, the diversity of the components were planned before starting the processing. All three type of devices were designed with gate lengths ranging from 20 nm to 70 nm. The gate length is defined in figure 3.1. Beyond the gate length variations, a structure called mesa was also varied. The mesa is marked in figure 3.2 and 3.6. The width of the mesa sets the gate width and hence number of nanowires. By changing the mesa width, the performance can be compared when the number of nanowires are increased. The relation between mesa width and amount of nanowires in the channel for the three different types of devices is presented in table 3.1 below. For the B and C devices, it is more clear to compare the effective mesa width. Since the gate is rotated 45° related to the mesa, instead of being orthogonal, the effective gate width becomes longer with a factor of  $\sqrt{2}$ .

Table 3.1: Mesa widths

| Device type | Mesa width         | Effective mesa width | # Nanowires |

|-------------|--------------------|----------------------|-------------|

|             | $(\mu \mathrm{m})$ | $(\mu \mathrm{m})$   |             |

| Device A    | 7                  | 7                    | 100         |

| Device A    | 14                 | 14                   | 200         |

|             | 3.5                | 5                    | 100         |

| Device $B$  | 5                  | 7                    | 140         |

|             | 7                  | 10                   | 200         |

| Device C    | 5                  | 7                    | 100         |

| Device C    | 7                  | 10                   | 140         |

Beyond gate and mesa geometry variations, different EBL-patterns were also compared. The first is the pattern of the nanowires, where two different exposure geometries were tested. One used rectangles (R) to define the nanowire array, and the other used six parallel single pixel lines (S). The other variation was the gate exposure. The first gate type used two single pixel lines (2L) to define the gate. The other used six single pixel lines (6L) to achieve a wider gate. This is further discussed in the corresponding sections below, and the results are presented in chapter 6.

### 3.3 Processing

The different process methods that were used to build the devices are briefly described in Appendix A. Some process steps are recurrent and are therefore described in less detail after the first mention. The processing described below is the general process. The real processing deviates from the general as described in section 3.3.9 in the end of this chapter.

#### 3.3.1 Sample preparation

From a 4" InP (100) wafer, 12x10 mm samples were cut using a scriber. The substrates were cleaned in acetone for 15 seconds followed by a longer soak in acetone for 5 min and finally a 60 s soak in Isopropyl Alcohol (IPA).

#### 3.3.2 Nanowire channel

The lateral nanowires, which makes up the channel of the MOSFET, were the first structures to be processed. The samples were pre-baked on a 200°C hotplate for 2 min to remove any water or other liquids that had been formed on the sample, to increase the adhesion of the photoresist. After cooling for one minute, the samples were placed on a spinner. Hydrogen silsesquioxane (HSQ) was used as photoresist and was diluted with Tetramethylammonium hydroxide (TMAH) 1:3 to achieve a thinner resist layer and optimize resolution. The samples were spun on a spin coater at 3000 rpm for 60 s, with a ramping of 1500 rpm/s. To increase adhesion of the HSQ to the InP substrate, the sample was baked on a 200°C hotplate for 2 min. The patterning was made using EBL. The aperture was set to 30  $\mu$ m, the voltage to 50 kV and the step-size 2 nm. On two of the samples, two different exposure geometries were tested to see if there were any difference in edge roughness. The first geometry used rectangles to define where the nanowires should grow. The second exposure geometry used six single pixel lines with a higher dose than for the rectangle. This dose was also varied, increasing from left to right on the sample to see which dose gave the best result. After exposure, the resist was developed using TMAH for 90 s heated to 37°C to reduce edge roughness. When HSQ is exposed, it transforms to SiO<sub>2</sub>, and can sustain high growth temperatures.

The In<sub>0.85</sub>Ga<sub>0.15</sub>As nanowires were grown using metalorganic chemical vapour deposition (MOCVD) at 500°C. This step is critical for the device performance since it limits the channel mobility, which is important for RF applications. Therefore all growth was outsourced to Lasse Södergren, PhD student in the Nanoelec-

tronics group. The InGaAs only grows in the *trenches* between the HSQ strips created by the EBL pattern, not on the HSQ itself. When the HSQ is removed, it leaves lateral InGaAs nanowires. HSQ removal was done using 1:10 diluted Buffered Oxide Etch (BOE) for 2.5 min, followed by 60 s  $\rm H_2O$  and 60 s IPA. To decrease the size and edge roughness of the nanowires, five cycles of digital etch followed. This was done by placing the samples in 1:5 Hydrochloric acid (HCl): $\rm H_2O$  for 12 s and ozone cleaning for 8 minutes.

#### 3.3.3 Contact regrowth

After the nanowire channel was processed, the heavily doped drain and source contacts were added according to the images in section 3.1. To prevent the contact layer from growing over the nanowires, a 70 nm strip of HSQ was added covering the nanowire array. This strip is called a dummy-gate. Resist was deposited in the same way as in section above 3.3.2, with the only difference that undiluted HSQ was used to achieve a thicker resist layer. The patterning was made using EBL, this time with an aperture of 40  $\mu$ m, a step size of 8 nm and an area dose of 1500  $\mu$ C/cm<sup>2</sup>.

After exposure, the resist was developed for 2 min in TMAH. 30 nm thick, heavily n-doped, InGaAs contacts were then grown on the samples using MOCVD.

A schematic of this step can be seen in figure 3.9. The HSQ shows where the gate will be placed in a later process step.

Figure 3.9: Contact growth schematic with HSQ dummy gate

The exposed HSQ was removed using BOE 10:1 for 2.5 min. In figure 3.10 the nanowire array of a B device before and after the contact regrowth can be seen.

Figure 3.10: A B-type device a) before and b) after contact regrowth

### 3.3.4 Ledge & sacrificial InP layer

Following the contact regrowth was the ledge and InP sacrificial layer. The InGaAs ledge creates a lower contact resistance to the the channel. The sacrificial InP layer creates an air spacer between the gate and drain/source contacts, decreasing the capacitance between contacts. Air is the most desirable spacer material, since it has a low relative permittivity of 1. The resist was spun in the same way as for the contact regrowth. EBL was used once again for making the pattern, with the same settings as the previous step. Development was done for 2 min in TMAH. After development, a 8 nm heavily doped InGaAs ledge was grown, which is shown in figure 3.11.

Figure 3.11: Contact ledge growth schematic with second HSQ dummy gate

After the ledge growth, the sacrificial InP layer was grown. The exposed HSQ was removed using BOE (10:1) for 2.5 min.

#### 3.3.5 Mesa Etch

The mesa sets the gate width and thus how many nanowires that will be present in the channel. This step also makes sure that the drain and source pads are not short-circuited by the contact layer. The EBL preparations was the same as

can be seen in section 3.3.3 and 3.3.4. The exposure was done using the same settings as above. This time a wide rectangle covering both gate fingers was exposed. Development was done using TMAH soak for 2 min. The sacrificial InP outside the mesa was then etched by using 5 s 1:1 HCl:H<sub>2</sub>O. Then the InGaAs was etched by using 1:1:25 dilution of  $\rm H_3PO_4:H_2O_2:H:_2O$  for 25 s. The sacrificial InP, InGaAs ledge, InGaAs contact layer and nanowires that were not covered by the mesa structure was thus removed. Finally, the exposed HSQ was removed in BOE (10:1) for 3 min.

#### 3.3.6 Oxide deposition

The gate oxide is one of the most important parts of a transistor. It separates the gate from the channel and prevents leakage. To get a better device performance, high- $\kappa$  materials are often used as gate oxide. This oxide is deposited with Atomic Layer Deposition (ALD), which uses precursor gases at elevated temperatures. Before depositing the oxide, the native oxide needs to be removed and the samples need to be passivated. The native oxide is the natural oxide that forms on the surface of the sample when it is exposed to air. Passivation is a chemical process that makes the surface unable to react with air. Removal of the native oxide was done with 10 min of ozone cleaning. The samples were passivated by 20 min soak in  $(NH_4)_2S:H_2O$  1:1. The oxide,  $Al_2O_3/HfO_2$ , was deposited using ALD. First, the sample was self cleaned with Al pulses in the ALD chamber. The  $Al_2O_3$  was deposited using TMAl and  $H_2O$  as precursors for five cycles. This oxide is used to improve the channel-oxide interface. The actual oxide,  $HfO_2$ , was deposited using TDAHf and  $H_2O$  as precursors for 35 cycles.  $HfO_2$  has a significantly higher dielectric constant  $(\kappa)$  of 25 compared to  $Al_2O_3$  with  $\kappa=9$  [16].

#### 3.3.7 Gate

On top of the gate oxide is the gate contact. To lower the gate resistance, a T-gate was used. The large bulk metal of the gate increases the cross sectional area and thus reduces the resistance. To achieve the T-shape a double layer resist was used. The upper resist is exposed by the (primary) electron beam from the EBL, while the lower resist is exposed by both primary and secondary electrons. Thus, the upper resist needs to be more sensitive to electrons than the lower one since the number of exposing electrons is fewer.

PMMA 950 A2, which is a positive photo resist, was spun on the samples at 6000 rpm for 45 s. The samples were baked on a 180°C hotplate for 90 s. Another layer of positive resist, MMA EL6, was spun on top of the PMMA 950 A2 layer at 2000 rpm for 45 s. The gate contacts were patterned with EBL, using a 40  $\mu$ m aperture, an area dosage of 790  $\mu$ C/cm² and a 2 nm step size. The resists were developed in MIBK:IPA 1:3 for 90 s. The gate exposure was done in two different sizes, one using two single pixel lines (2L) and one using six single pixel lines (6L). The larger configuration was mainly to avoid alignment errors, since the gate was hard to align to where the dummy gate had been. To remove resist residues, the samples were placed in a plasma asher for 7 s at 5 mbar oxygen pressure. Gate metal was deposited using evaporation under sample rotation. The rotation

ensures an even metal layer. First 10 Å Titanium (Ti) was deposited, followed by 50 Å Palladium (Pd) and 800 Å Gold (Au). The unwanted metal was removed using an acetone soak for 20 min, with assisted lift-off using pipettes. The gate structure is shown in figure 3.12 below. The T-shape of the gate can clearly be seen, as well as the nanowires in the channel.

Figure 3.12: A 52° tilted SEM image of a T-gate

### 3.3.8 Source, gate & drain pads

To be able to measure the performance of the device in probe stations, pads for the contacts are needed. The sample was pre-baked on a 200°C hotplate for 2 min. PMMA 950 A8 was spun on the samples at 4500 rpm for 45 s with a ramping of 1500 rpm/s. The resist was baked on a 180°C hotplate for 2 min. The pad pattern was made using EBL with a 60  $\mu$ m aperture, an area dose of 790  $\mu$ C/cm² and a step size of 8 nm. The resist was developed in TMAH for 90 s and the resist residues were removed using 30 s plasma ashing at 5 mbar oxygen. The pad metal was deposited using evaporation. 100 Å Ti was followed by 100 Å Pd and 2000 Å Au. The lift-of was done with acetone using pipettes. Some final sample cleaning was done with plasma ashing for 35 s at 5 mbar oxygen pressure, and a final IPA soak for 60 s.

#### 3.3.9 Samples

Six different samples were processed during this thesis. Below is a description of each sample deviations from the general process method.

Sample I follows the general processing with the exception that only 2L gates were processed. However, the HSQ strip that is supposed to protect the nanowires before sacrificial InP and contact regrowth was hard to align. This EBL-step, which involved resist spinning, exposure and development, was remade five times.

Sample II follows the general processing except some small deviations. This sample also lacks the 6L gate, and only has 2L. Just like sample I the

alignment of the third EBL step was remade several times to make the alignment acceptable. The evaporation of Ti in the source and drain pads was not successful for this sample. This is due to that there were two-Ti boats in the evaporator, which would have required double evaporation current during deposition.

- Sample III and the following samples do not have any C-type devices since the quality of the "C-nanowires" in sample I and II was very poor after the nanowire growth. To avoid remaking the same EBL-step several times (as in the samples described above), the HSQ from the second EBL-step was etched back instead of removed. This applies to the following samples as well. To achieve different gate lengths, the HSQ-strip that was deposited before the contact regrowth (section 3.3.3) was altered in length between 20 and 70 nm.

- Sample IV has several deviations from the general process. The sample lacks InGaAs ledge. The etching of sacrificial InP and InGaAs contact layer was not successful and required repeating etching steps. Because of this extra etching, the gate contact metal was not thick enough to make a contact with the gate finger. To fix this, an extra EBL and evaporation step was added to deposit a thick layer of metal at the finger-contact interface.

- Sample V has the same deviations as sample III, plus that the digital etch of the nanowires was skipped to minimize the risk of etching down all the InGaAs. This step was skipped for the last device as well. To avoid any risk of separation between the gate contact and the gate finger, the thickness of the metal contact layer was increased. The Ti layer was increased from 10 to 100 Å, the Pd layer from 50 to 100 Å and the Au layer from 900 Å to 2000 Å.

- Sample VI did not have the ledge or InP sacrificial layer, and is a DC reference sample for sample V. On this sample, the source and drain contacts were added before the gate-oxide and gate. To avoid an extra EBL-step the gate fingers and contacts were added together.

As was mentioned in the beginning of this chapter, the road from substrate to finished devices is complicated and takes time. The human factor as well as limitations of the processing methods will lower the yield and performance of at least some devices. Therefore one can not expect that the results always will correspond to the expected values.

### Simulations

The software COMSOL Multiphysics was used to model different parts of the device and simulate capacitance performance. All simulations were performed using the AC/DC module, doing a stationary analysis of electrostatics to calculate capacitance.

The AC/DC module uses FEM (finite element method) and BEM (boundary element method) to solve Maxwell's equations [17]. FEM is a numerical method of solving large mathematical problems and is often used in engineering. The idea is to divide the problem into smaller sections (finite elements) and solving the equations for each part. These sub-solutions then constitute an approximative solution for the entire problem when put together.

The relative permittivity of the materials used in the simulations is shown in table 4.1.

Table 4.1: Material parameters used in simulations

| Material | Relative permittivity |

|----------|-----------------------|

| InP      | 12.5                  |

| InGaAs   | 14                    |

| Oxide    | 20                    |

| Air      | 1                     |

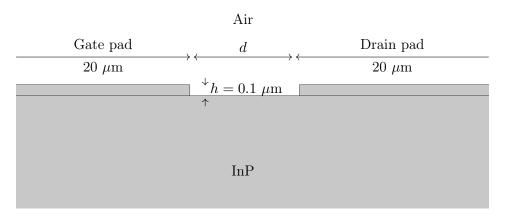

### 4.1 Pad capacitance

Simulations were made to investigate the capacitance between the gate and the drain pad. A simple model was created where both gate and drain contacts were modelled as 20 by 20  $\mu$ m blocks with height 0.1  $\mu$ m. The 2D model geometry is shown in figure 4.1.

18 Simulations

Figure 4.1: Model geometry for the pad capacitance simulation

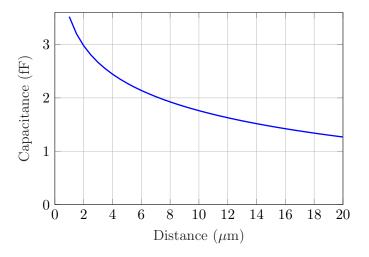

This 2D model was simulated with an out-of-plane thickness of 20  $\mu$ m so that the pads were 20x20  $\mu$ m. The distance d between the pads was swept between 1 and 20  $\mu$ m and the results of this simulation is shown in figure 4.2.

Figure 4.2: Gate to drain pad capacitance.

As can be seen by this simulation, the capacitance is quite significant. At 1  $\mu$ m distance, the capacitance is more than 3.5 fF. To decrease this contribution, the gate contact was redesigned. The distance between gate and drain was increased, and smaller sections of the gate contact drawn out to ensure that gate resistance would not be affected by the change. The finished gate contact structure can be seen in figure 4.3 below where the added extensions are marked.

Simulations 19

**Figure 4.3:** Finished gate contact layout with extended gate pad sections

### 4.2 Nanowire capacitance

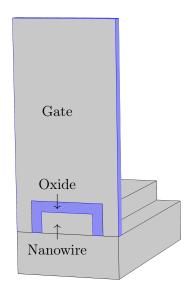

A simple transistor model was created consisting only of a single nanowire and the gate terminal. The purpose of this model was to determine a minimum capacitance between the gate and the nanowire, without the contacts, ledges or other elements present. The model geometry is shown in figure 4.4 and 4.5 where the oxide is shown in blue.

**Figure 4.4:** Side view of nanowire model geometry

**Figure 4.5:** Gate view of nanowire model geometry

The nanowire shape was approximated as rectangular, though not entirely true this shape variation was not estimated to have a great impact on the result. The nanowire had the dimensions 25x10 nm and the oxide thickness was set to 5 nm.

To simulate the capacitance between the gate and the nanowire using only electrostatics, some approximations must be made. Here, the nanowire and the gate are both modelled as metallic, with one terminal on the gate surface shown in figure 4.5 and the other terminal on the surface of the entire nanowire.

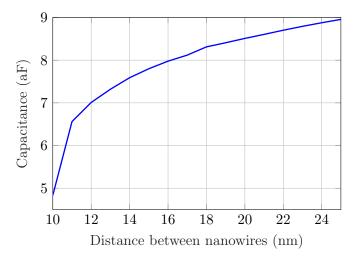

The width of the model, and thus the distance between the nanowires, was swept to investigate how much it affects the capacitance per nanowire. A model width of 35 nm corresponds to a distance between the nanowires of 10 nm. A periodic boundary condition was put on the side edges of the model, since the actual devices consist of multiple nanowires. All other dimensions were kept constant. The result is shown in figure 4.6. Note that the capacitance is given in aF and is not normalized with gate width, which means the capacitance is shown per nanowire.

Figure 4.6: Parasitic capacitance per nanowire

As would be expected, the capacitance per nanowire is lowest when the distance between the nanowires is small. Since transconductance should scale with the number of wires, the best performance in terms of maximizing  $g_m$  and minimizing the parasitic capacitance would be achieved with wires as close together as possible.

The much lower value at 10 nm distance could be because the oxide is as thick as the distance between the wires, so there is no gate in contact with the substrate. This means that some of the parasitic capacitance to the sides of the nanowire is eliminated. This is however not a desirable design of the channel, since it would result in a channel without the tri-gate structure.

At 15 nm nanowire spacing, the capacitance is 7.8 aF corresponding to a normalized value of 0.2 fF/ $\mu$ m. By normalising per  $\mu$ m, a value is obtained that can be compared to the other simulations as well as the measured values. This

normalisation corresponds to a normalisation of a devices gate-source or gate-drain capacitance by total gate width.

# 4.3 Device capacitance

The model was extended to be as similar to the processed devices as possible. Since only an electrostatic simulation was performed, the whole contact area with n<sup>+</sup> contact and ledge are grounded while the gate domain is biased. This means that the highly doped InGaAs is modelled as metallic, which is an approximation. This results in slightly higher capacitance.

Only half the transistor device is modelled, as it is symmetric on both source and drain sides. Also, a single nanowire is modelled with periodic boundary condition to simulate a device with multiple wires. The capacitance is then normalized, corresponding to the measured capacitance normalized by the mesa width.

Dimensions were approximated from SEM images taken during processing. The nanowire has dimensions 25x10 nm and the oxide thickness is 5 nm. The width of the model is 40 nm, corresponding to a nanowire spacing of 15 nm. The gate length is 40 nm (20 nm in model) and the height of the gate is 130 nm. The thickness of the source contact is 30 nm. The geometry of the model is shown in figure 4.7 and 4.8 where the oxide is marked in blue. The nanowire is hidden by the ledge so it is only visible in the gate stack view.

Figure 4.7: Model side view

**Figure 4.8:** Model gate stack view

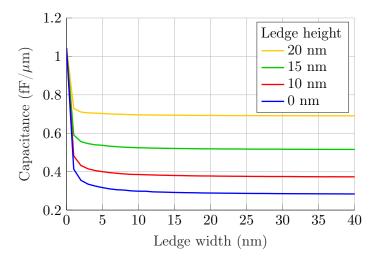

Four different ledge models were simulated. The device was first modelled without the ledge, varying the distance between the source contact region and

the gate between 0 and 40 nm. The nanowire was modelled as metallic, like in the simpler model in the previous section. Then, a ledge the same height as the nanowire (10 nm) was added. Following was two other variations, with ledge 15 and 20 nm (5 and 10 nm above the nanowire). The fact that the fabricated ledge is shaped around the nanowires is not taken into account. Instead the ledge is modelled at completely flat. In the case with 10 nm ledge height, this corresponds to filling the trenches between the wires with  $\rm n^+$  material. In the fabricated devices, a 8 nm ledge was grown. Thus, the model with a 15 nm straight ledge is estimated to be the closest to the fabricated devices.

The ledge distance was varied from 0 to 40 nm for the different configurations to see the significance of the parasitic capacitance between the gate contact and the  $n^+$  source region. The result is shown in figure 4.9. The normalisation is per  $\mu m$ , corresponding to a normalisation per total gate width.

**Figure 4.9:** Gate to source capacitance for different ledge heights and widths

As can be seen in this figure, a small spacing between the gate and the contact region has a great impact on the capacitance. For the 15 nm ledge, increasing the ledge width from 0 to 5 nm corresponds to a decreased capacitance from 1 fF/ $\mu$ m to 0.54 fF/ $\mu$ m. The capacitance is thus almost halved.

Besides the first few nanometers, the ledge width does not have great impact on device parasitic capacitance. These results indicate that having a wide ledge does not improve performance significantly. Instead, the capacitance between the ledge and the gate contact is the dominating factor. This conclusion is also supported by the large increase in capacitance when the ledge height is increased.

At ledge width 0 nm, the source  $n^+$  region is in direct contact with the gate oxide. This is why the different ledge heights give the same capacitance at this distance, which is dominated by the capacitance directly between the source and the gate with the oxide in between. This would also be equivalent to a ledge height of 30 nm. The value of this is found to be just above 1 fF/ $\mu$ m.

At 0 nm ledge height, the results can be compared to the simple nanowire capacitance model in the previous section where the normalized capacitance was 0.2 fF/ $\mu$ m. This value is close to the  $\sim$ 0.3 fF/ $\mu$ m obtained in the device simulation for a wide ledge. The higher value can be attributed to the presence of the source contact as well as the T-gate geometry.

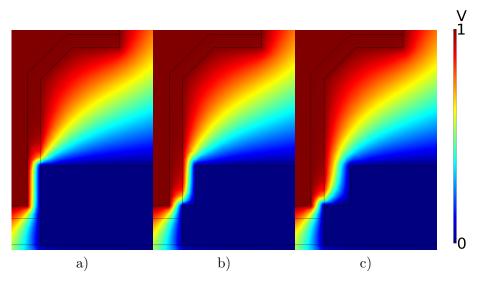

The electric potential for ledge height 15 nm and ledge width 0, 5 and 10 nm are shown in figure 4.10.

Figure 4.10: Electric potential cross-section plot for different ledge widths a) 0 nm, b) 5 nm and c) 10 nm

Without the spacer, the electric field is strongest inside the oxide, as can be seen in figure 4.10 a). When the ledge width is increased to 5 nm, that electric field is instead moved to the air spacer between the oxide and the contact. Because the permittivity of air is much lower than that for the oxide, this decreases the capacitance. However, the capacitance between the gate and the ledge through the oxide is still large and does not change by increasing the ledge width. This can be seen in figure 4.10 b) and c).

# Measurements & Modelling

To be able to form a perception of the device performance, benchmarking is necessary. This is done by evaluating DC- and RF-performance. This chapter introduces the different benchmarking metrics and how they are obtained.

### 5.1 DC measurements

### 5.1.1 DC performance

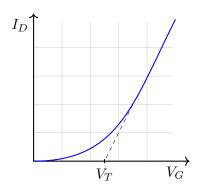

DC-evaluation is done by measuring the output and transfer characteristics at DC voltage. The *transfer characteristics* is measured by sweeping the gate voltage at a set drain bias. The drain current is then plotted against gate voltage. From the results, threshold voltage and transconductance can be found.

Figure 5.1: Transfer characteristics.

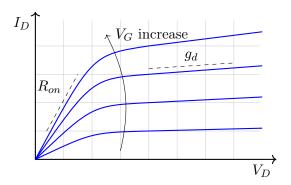

The *output characteristics* is measured by sweeping drain voltage for different set gate biases. This results in several plots with a similar shape. From these plots, output conductance and on-resistance can be extracted.

Figure 5.2: Output characteristics.

### 5.1.2 Transconductance

Transconductance is a very important metric for benchmarking the MOSFET and can be extracted from the transfer characteristics (figure 5.1) as the slope of the drain current. It is defined as the derivative of the drain current when the gate voltage is changed.

$$g_m = \left. \frac{\partial I_D}{\partial V_{GS}} \right|_{V_{DS} \text{ constant}} \tag{5.1}$$

The transconductance is affected by the conduction properties of the channel and the gate control. It can be increased by improving the transport properties of the channel, e.g. by using a material with high carrier mobility  $\mu$  and long mean free path  $\lambda$ . Transconductance can also be improved by decreasing gate length and thus the channel resistance, and by increasing the oxide capacitance  $C_{ox}$  and thus the gate control.

### 5.1.3 Output conductance

The output conductance is defined as the derivative of the drain current but instead when the drain voltage is changed.

$$g_d = \left. \frac{\partial I_D}{\partial V_{DS}} \right|_{V_{GS \text{ constant}}} \tag{5.2}$$

The output conductance can be extracted from the output characteristics as the slope of the current in the saturated region. Ideally, the output conductance should be zero as the drain voltage should not affect the current in the saturated region. However, the channel length modulation of the drain current has an effect on the resistance of the channel and thus the current. Output conductance is also affected by short-channel effects.

### 5.1.4 On-resistance

The on-resistance of the MOSFET can be obtained from the slope of the output characteristics in the linear region, seen in figure 5.2. The on-resistance describes

how large the total resistance is between the source and drain contact. To achieve a high current and low current loss, a low  $R_{on}$  is desirable.

$$R_{on} = \left. \left( \frac{dI}{dV_{DS}} \right)^{-1} \right|_{V_{DS} \to 0} \tag{5.3}$$

The on-resistance can be reduced by having a short and wide channel with few crystal defects, to minimize scattering.

### 5.1.5 Threshold voltage

The threshold voltage,  $V_T$  is the gate voltage at which the device switches from off-state to on-state. It can be extracted from the transfer characteristics (figure 5.1) by extrapolating the slope of the  $I_D$  curve at the maximum transconductance down to zero drain current. It is generally defined as the voltage required to create an inversion layer in the MOSFET channel but the extraction of this parameter is quite arbitrary and can be done in different ways.

### 5.1.6 Measuring DC

In this diploma work, a Cascade 11000B Probe station was used to measure the transfer and output characteristics of the devices. Three probes were connected to gate, drain and one of the source contacts respectively. This means that one of the source-pads was not biased and one of the gate fingers was unmeasured. For the transfer characteristics, the gate voltage was swept from -0.5 V to 1 V for a constant drain bias of 0.5 V. For the devices with promising transfer characteristics  $(g_m > 0)$ , the output was measured as well. For the output characteristics, the drain voltage was swept from 0 V to 1 V for gate voltages between -0.5 V to 1 V with a step size of 0.1 V. From the DC data, an evaluation of which devices to measure RF performance on can be made.

# 5.2 RF measurements & modelling

### 5.2.1 RF performance

For good RF performance, the important metrics are somewhat different from that of DC performance. One big difference is the importance of capacitances. In a DC environment the capacitances can be seen as open circuit element, but when the frequency increases the impedance of the capacitances decreases as  $\frac{1}{\omega}$ . At gigahertz frequencies, small parasitic capacitances can be limiting the to RF performance. The capacitances along with the transconductance sets the upper limit of frequency where there is gain. Gain and maximum frequency are very important metrics for high-frequency applications.

### 5.2.2 Capacitance

There are both wanted and unwanted capacitances in a transistor. The MOSFET design relies on a capacitance that opens the channel from the gate over the oxide,

using the field effect. Here, it is beneficial with a large oxide capacitance  $(C_{ox})$  to increase the electrostatic control of the channel.

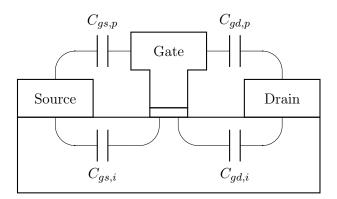

However, there are also some parasitic coupling between the transistor contacts that limits the performance. These can be divided into *intrinsic* and *parasitic* capacitances.

The intrinsic capacitances are located *inside* the MOS-region of the transistor, between the channel and the source and drain contacts. This is visualized in figure 5.3, where the intrinsic capacitance between gate and source are denoted  $C_{gs}$  and the capacitance between gate and drain are denoted  $C_{gd}$ . The intrinsic capacitances are determined by the internal properties of the transistor, eg. geometry and material properties. The intrinsic gate-source capacitance is approximated (in saturation) with [18]

$$C_{gs,i} \approx \frac{2}{3} W L_g C_{ox} || C_q \tag{5.4}$$

$C_q$  is the quantum capacitance and stems from the is a limited density of states. Large intrinsic capacitances result in a slow response when the drain and gate voltages are changed. This causes a low switching speed and high power losses [19].

**Figure 5.3:** Schematic describing the intrinsic and parasitic capacitances in MOSFET structure.

Between source and gate pads there is a parasitic capacitance denoted  $C_{gs,p}$  and between gate and drain there is a parasitic capacitance denoted  $C_{gd,p}$ . Both of these capacitances can be seen in figure 5.3. The parasitic capacitances are a limiting factor of the transistor speed, which is critical for RF applications. This is discussed further in the sections about maximum frequencies later in this chapter. To achieve low parasitic capacitances there are some parameters that can be tweaked. A larger distance between the contacts and a low permittivity material between them results in a low parasitic capacitance [20].

The parasitic and intrinsic capacitances constitute the total gate-source  $(C_{gs,t})$  and gate-drain  $(C_{gs,t})$  capacitances, as can be seen in the equations listed below.  $C_{gg,t}$ , the total gate capacitance, is the sum of the gate-source and gate-grain

capacitances.

$$C_{gs,t} = C_{gs,i} + C_{gs,p} (5.5)$$

$$C_{gd,t} = C_{gd,i} + C_{gd,p} (5.6)$$

$$C_{qq,t} = C_{qs,t} + C_{qd,t} (5.7)$$

To achieve good RF properties, the device layout should be optimized for a large oxide capacitance and for minimum parasitic capacitances between the contacts.

### 5.2.3 Gain

The gain of a device describes its ability to enhance a signal from the input to the output. The gain is defined as the ratio between the amplitude of the output signal and the input signal and is often displayed in dB. There are different gain definitions used for different applications. Current gain  $(h_{21})$ , are used to define the cutoff frequency,  $f_T$ . At  $f_T$ ,  $h_{21}$  is equal to unity. Maximum available gain (MAG), maximum stable gain (MSG) and unilateral gain (U) are examples of power gain. These are used to define the maximum oscillation frequency,  $f_{max}$ . At  $f_{max}$ , U and MAG/MSG are both equal to unity. The MAG/MSG also shows where the circuit goes from unconditional to conditional stability.

### 5.2.4 Cutoff frequency

The cutoff frequency, denoted  $f_T$  is defined as the frequency where there is unity current gain, that is when  $h_{21}$  is equal to one (0 dB) [5].

$$\frac{1}{2\pi f_T} = \frac{C_{gg,t}}{g_m} + \frac{C_{gg,t}}{g_m} (R_S + R_D)g_d + (R_S + R_D)C_{gd,t}$$

(5.8)

For small  $R_S$  and  $R_D$ ,  $f_t$  can be approximated to be only dependent on transconductance  $g_m$  and the total gate capacitance  $C_{gg,t}$ .

$$f_T \approx \frac{g_m}{2\pi C_{qq,t}} \tag{5.9}$$

This approximation shows which parameters are most important for maximizing cutoff frequency,  $g_m$  and  $C_{qq,t}$ .

#### 5.2.5 Maximum oscillation frequency

The maximum oscillation frequency, denoted  $f_{max}$ , is defined as the frequency where the power gain U is equal to unity (0 dB) [5].

$$f_{max} = \sqrt{\frac{f_T}{8\pi R_G C_{gd,t} \left(1 + \frac{2\pi f_T}{C_{gd,t}} \Psi\right)}}$$

(5.10)

where

$$\Psi = (R_D + R_S) \frac{C_{gg,t}^2 g_d^2}{g_m^2} + (R_D + R_S) \frac{C_{gg,t} C_{gd,t} g_d}{g_m} + \frac{C_{gg,t}^2 g_d}{g_m^2}$$

This shows that  $f_{max}$  is affected by the gate resistance  $R_G$  and the output conductance  $g_d$ .

### 5.2.6 RF measurements

In this diploma work, a Karl Suss PSM6 probe station and a network analyzer was used to extract the frequency dependence of the devices. First calibration of the setup was performed with the LRRM (Line-Reflect-Reflect-Match) method. The calibration was repeated until an acceptable noise-level was achieved. Open and short de-embedding structures, fabricated on the same sample as the transistors, were measured to extract and remove the pad impedance later. Here both gate and drain voltage was set to 0 V. To be able to de-embed the contact resistances, the off-state was measured. To measure off-state, the drain voltage was set to 0 V and the gate voltage to -0.8 V. The S-parameters were measured in the operating frequency span 10 MHz to 67 GHz at a port power of -27 dBm. The drain voltage was swept from 0 V to 1 V, and the gate voltage from -0.6 V to 1 V.

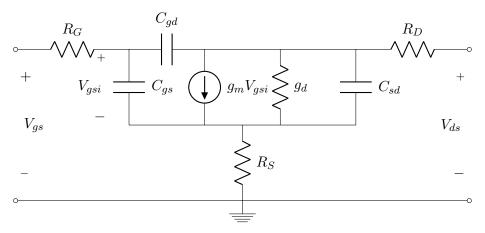

### 5.2.7 RF modelling

To further analyse the behaviour of a fabricated device, a hybrid- $\pi$  model can be extracted. The collected S-parameters from the RF-measurements are converted into y-parameters. From these, small signal parameters can be extracted. The expressions used was similar to the ones presented in an article by Sofia Johansson [21].

$$g_m = \text{Re}(y_{11})\big|_{\omega^2 = 0}$$

(5.11)

$$g_d = \text{Re}(y_{22})\big|_{\omega^2 = 0}$$

(5.12)

$$R_g = \frac{\text{Re}(y_{21})}{(\text{Im}(y_{11}))^2} \tag{5.13}$$

$$C_{gd} = \frac{-\operatorname{Im}(y_{12})}{\omega} \tag{5.14}$$

$$C_{dg} = \frac{-\operatorname{Im}(y_{21})}{\omega} - g_m R_g (C_{gs} + C_{gd})$$

(5.15)

$$C_{gs} = \frac{\text{Im}(y_{11}) + \text{Im}(y_{12})}{\omega}$$

(5.16)

$$C_{sd} = \frac{\text{Im}(y_{22})}{\omega} - C_{gd} - g_m R_g C_{gd} + \omega^2 C_{gd} C_{dg} (C_{gd} + C_{gs}) R_g^2$$

(5.17)

The modelling was done using a Matlab-script that makes an automatic fitting of the real and imaginary part of the y-parameters. It then extracts the values of the parameters listed above. This script was written by associate professor Erik Lind, and thus not a part of this diploma work.

A schematic of a hybrid- $\pi$  model can be seen in figure 5.4 below.

**Figure 5.4:** A hybrid- $\pi$  model of a MOSFET

## 5.3 Limitations

There are some limitations of this small signal modelling. First of all, the hybrid- $\pi$  model is only an approximation of a real device. To achieve a model that is closer to a real device, more circuit elements would be needed for the small signal model. The automatic fitting of the model to the real y-parameters is written for an A type device with a mesa width of 7  $\mu$ m. This could be a problem for the B devices and for the devices with mesa 14, resulting in worse fitting and less accurate parameter extraction.

# Results & Analysis

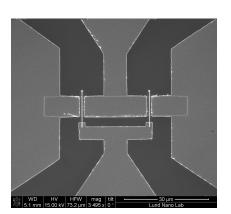

During this diploma work, six samples were fabricated with a total number of 464 devices. However, sample I was not finished and lack pad metal, and thus was not analysed in a DC or RF environment. This means that 380 devices, on four samples, were analysed in a DC environment. Out of the 380 devices, only 124 showed transistor behaviour (transconductance>0 mS). This corresponds to a yield of 33%. The DC measurements showed that sample V had a superior performance compared to the other samples, and it was therefore the only sample measured in RF. The best performing devices on sample V were analysed further in Matlab.

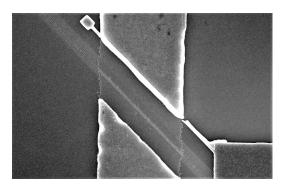

In figure 6.1 and 6.2, SEM images of one finished A-device and one finished B-device are shown.

Figure 6.1: A overview of a finished A device with mesa 7  $\mu$ m

**Figure 6.2:** A overview of a finished B device with mesa 3.5  $\mu$ m

# 6.1 Processing

Before any electrical measurements are performed, the samples can be analysed in terms of how well the resulting devices correspond to the intended fabrication. Some of the samples encountered more problems during the processing than others.

This results in large variations of the quality between the samples, and also between devices on the same sample. In this section, all six processed samples are presented with some problems that were encountered during processing.

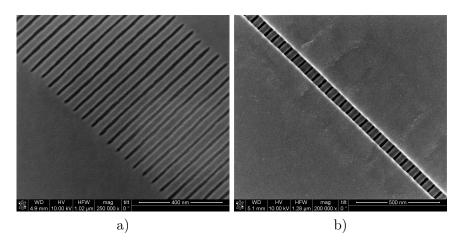

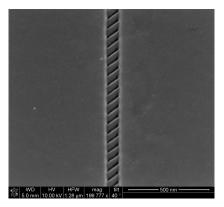

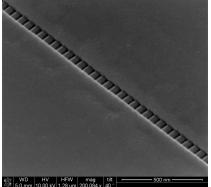

**Sample I & II:** Tilted SEM images of the nanowire channel of one A- and one B-device is shown in figure 6.3 and 6.4 below.

**Figure 6.3:** A SEM image of the nanowire channel of a *A*-device

**Figure 6.4:** A SEM image of the nanowire channel of a *B*-device

The nanowires of the C-type devices were discovered to be very rough in the edges after growth compared to A and B-devices. This may result in poor performance of device, such as higher resistances due to crystal defects and lower carrier mobility, resulting in a lower  $g_m$ . Since there is no interest of fabricating devices with a probable poor performance, the C-type devices were not fabricated on the subsequent samples. There was also a problem with aligning the dummy gate since the EBL exposure deviated 30 nm from the designed placement. This was corrected by adding a 30 nm offset in the EBL design file. This resulted in well-aligned A-devices, but the offset of B- and C-devices was still 30 nm. To correct this, these device design files were moved an additional 30 nm. The third exposure and development resulted in wavy HSQ dummy gates, and the resist was removed and the exposure was made again. This resulted in even worse alignment. Using the first corrected files, a new exposure was made, and the alignment was somewhat better. One reason the B- and C-type devices seemed to be more sensitive to poor alignment is that they need to be aligned both in the vertical and horizontal direction of the layout. Since they are rotated 45° to the A-gate, a misalignment in the vertical direction can look like a horizontal misalignment. A vertical misalignment of a A-device would only result in a shift of the gate, making it a bit shorter on one side but not affecting performance.

Other than redesigning the EBL-files, the devices with gate length 50 nm was replaced with 20, 30 and 40 nm devices. The 70 nm gate length devices

Results & Analysis 35

were also reduced in number. For longer gate lengths, there is a smaller margin of error, making them harder to align. This could result in a very low yield of working long gate devices. In total, the sample was exposed four more times than intended in the dummy gate EBL step, and thus the resist was removed four additional times. Every time the HSQ is removed using BOE, it also works as a digital etch on the nanowires. This means that part of the InGaAs wires were etched away and the BOE etched down in the InP substrate. This results in nanowires that are InGaAs in the top, and InP at the bottom.

Sample III & IV: The biggest problem encountered in the fabrication of these devices was the InP and InGaAs mesa etch. Etch pits were visible after InP etching and did not seem to vanish when the etching time was increased. When the concentration of HCl was increased the etching was somewhat successful. Some remaining etch pits and surface roughness was present. The gate lift off was difficult and resulted in low yield, as several devices were shorted due to residual metal.

Sample V & VI: The nanowire growth was not completely successful and resulted in poor edges and lower mobility than expected. From Hall measurements on an InGaAs layer grown in the same way as the nanowire layer, the mobility was found to be approximately 700 cm<sup>2</sup>/Vs. This had been previously measured to around 3000 cm<sup>2</sup>/Vs for similar structures [22].

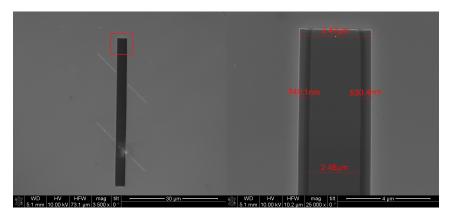

The 20 and 30 nm wide gates had a yield close to zero due to collapsing of the thin dummy gate structure. Therefore, no 20 and 30 nm gate lengths are included in the results. The InP etch is anisotropic and has a higher etch rate in the (111)B plane than in the (111)A [23], which resulted in a large under etch of the mesa in the (111)B-plane. The under etch of a B-device mesa is shown in figure 6.5.

**Figure 6.5:** SEM image of under etch on a B-type device

The under etch mainly affects the mesa of the *B*-devices, since they are placed so the width of the mesa is etched. The under etch was measured to around 530-540 nm on each side, resulting in a 1  $\mu$ m shorter mesa width.

Therefore the effective mesa widths are recalculated and presented as the actual effective mesa width in the following sections.