# Detection and location of HVDC commutation faults from PMU data

Alejandro Belinchón Calderón

Division of Industrial Electrical Engineering and Automation Faculty of Engineering, Lund University

Supervised by LTH: Olof Samuelsson ABB: Stefan Thorburn

#### **Master thesis**

# Detection and location of HVDC commutation faults from PMU data

Alejandro Belinchón Calderón

#### Abstract:

Commutation Failures in LCC HVDC converters is a topic that is normally addressed from the component perspective, looking at converters' internal signals. How these commutation failures affect the outer AC network is not deeply understood yet. This thesis will provide proof of how commutation failures causes abnormal behavior in the AC network, and how PMU data can be used in order to distinguish commutation failure from AC faults. In order to do so, simulations have been carried out in PSCAD and MATLAB-Simulink. The spreading of commutation failures in a bigger network, in this case NORDIC32, has also been studied using DigSilent-PowerFactory.

#### **Keywords:**

HVDC-links, HVDC converters, Commutation failures, Phasor measurement units (PMUs), Electric power systems, Wide Area Measurement systems (WAMS), Standard IEEEC 37.118, Single-line to ground faults, Three-Phase faults, Fault detection and location, Nordic 32, DigSilent-PowerFactory, PSCAD, MATLAB-Simulink, Symmetrical components.

If I have seen further it is by standing on the shoulders of giants.

Sir Isaac Newton, 1676

#### Acknowledgements

First, I would like to express my thankfulness to the main supervisor of the thesis, Professor Olof Samuelsson at the Division of Industrial Electrical Engineering and Automation in LTH. Thank you for guidance, advice and support during all the process of the thesis and for awaken my interest in topics such as power system stability and control. I would also like to thank Morten Hemmingsson for his advice regarding PMU's.

I would also like to show my admiration to Stefan Thorburn and Robert Saers, from ABB corporate research center in Västerås, who helped me enormously during my time working there, making my stay enriching and comfortable. I am pleased to thank as well some of their colleagues as Lidong Zhang and Jianping Wang for sharing their knowledge regarding HVDC-links. I would also like to thank Monika Koerfer for helping me with the paperwork.

Lastly, I would like to show my gratitude to friends, both in Sweden and in Spain, for listen to me when talking about my thesis and give me strength to carry on. As well as to my beloved family that has done everything for make this moment possible.

#### **Preface**

After an event in the Nordic system, it was recently realised that HVDC converter commutation failures are not visible to TSO control room. Therefore, it is highly interesting to understand how these failures spread along the AC network.

The main aim of the thesis was, firstly, to develop an algorithm for detecting and locating commutation failures using PMU data, but after the first simulations in MATLAB-Simulink, an unrecognizable behaviour in the AC current was found, which no one could explain at the first glance. To understand that behaviour became the main focus of the thesis. Simulations were carried out in PSCAD in order to address the validity of the previous simulations, finding the same unknown behaviour. For that reason, the aim of the thesis changed, being the algorithm less interesting and prioritizing the understanding about the reasons why the system reacts in that way when commutation failures happen and how can PMU data be used for characterizing that behaviour.

After some time and discussions, it was found that the reason of that behaviour is the configuration of the transformers in the HVDC-link. Therefore, new simulations were carried out in order to prove what was a hypothesis so far. Once the interaction between the HVDC and the AC system while commutation failures was understood, an HVDC was simulated in a complex network in order to understand how these faults spread, but without focusing on the development of an algorithm but only qualitatively, due to time limitations.

#### List of abbreviations

AC – Alternating current

CCA – Current control amplifier

CFC – Converter firing control

CMU – Current measurement unit

CMU-Current measurement unit

DC - Direct current

EC - European commission

EU- European Union

FACTS controllers – Flexible AC Transmission System controllers

GPS – Global Positioning System

HVDC – High voltage direct current

PC – Power control unit

PDC – Phasor Data Concentrator

PLL - Phase-locked loop

PMU – Phasor measurement Unit

PV - Photovoltaics

RES – Renewable energy sources

ROCOF – Rate of Change of Frequency

SCADA – Supervisory Control and Data Acquisition

SLG fault-Single line to ground fault

SVC – Static VAR compensator

VDCOL – Voltage dependent current order limiter

WAMS – Wide area monitoring system

## List of figures

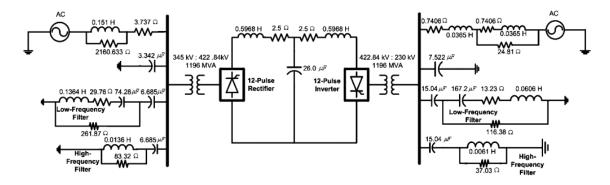

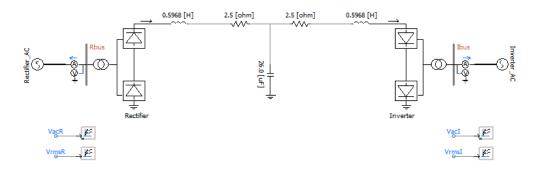

| Figure 1. Single-line diagram of the CIGRÉ benchmark HVDC system [15][15]                              | 7                   |

|--------------------------------------------------------------------------------------------------------|---------------------|

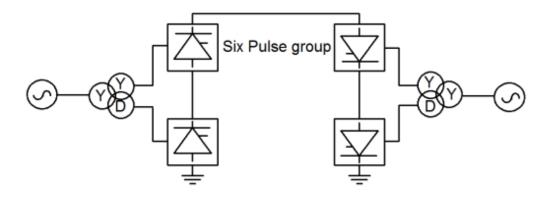

| Figure 2. 12-Pulse Monopolar HVDC [7]                                                                  | 8                   |

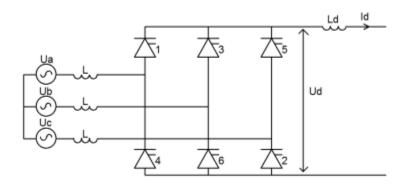

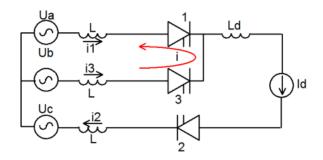

| Figure 3. Basic 6-pulse converter [7]                                                                  | 8                   |

| Figure 4. Equivalent circuit for commutation process [7]                                               | 9                   |

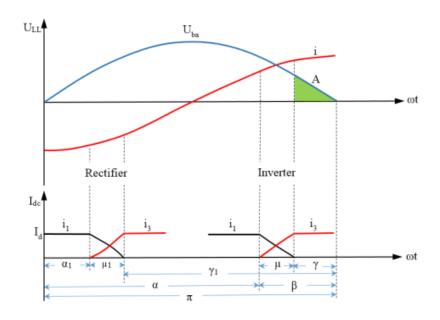

| Figure 5. Commutation and angle relationships [7]                                                      | 9                   |

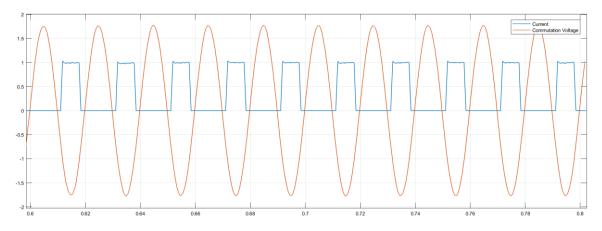

| Figure 6. Normal commutation. Commutation voltage (Orange) and current through valve 1 (E              | 3lue)               |

| in Simulink model                                                                                      | 10                  |

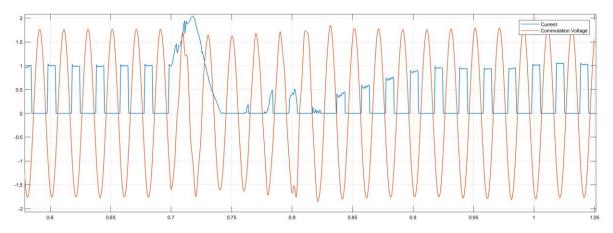

| Figure 7. Commutation failure. Commutation voltage (Orange) and current through valve 1 (B             | lue)                |

| in Simulink model                                                                                      | 11                  |

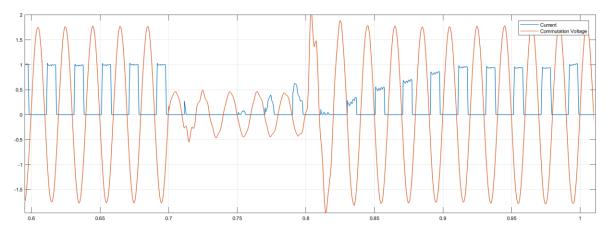

| Figure 8. Interrupted commutation. Commutation voltage (Orange) and current through valve              | 1                   |

| (Blue) in Simulink model                                                                               | 11                  |

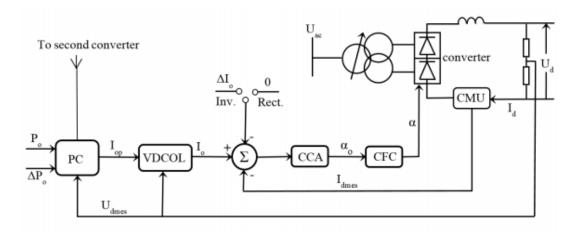

| Figure 9. Basic converter control system. Source [7]                                                   | 12                  |

| Figure 10. 12-Pulse configuration for HVDC converters [11]                                             | 13                  |

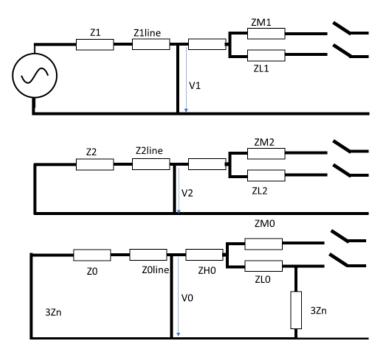

| Figure 11. Sequence models for a Three-winding transformer with grounded wye, delta and w              | ye                  |

| configuration. On the left, the transformer configuration. In the center positive and negative         |                     |

| sequence with the neutral above. On the right, zero sequence network with the neutral above            | e [18]              |

|                                                                                                        | 13                  |

| Figure 12. ABB RES670 Phasor measurement unit                                                          | 14                  |

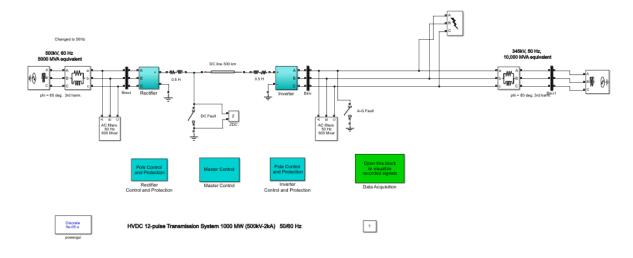

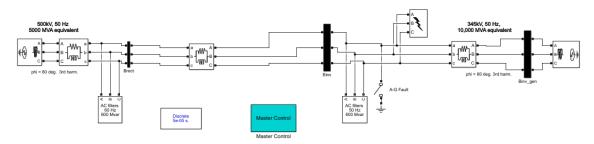

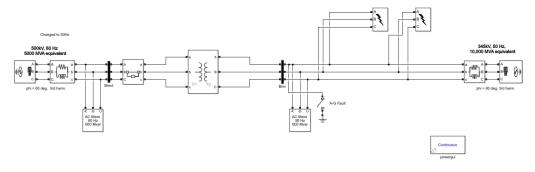

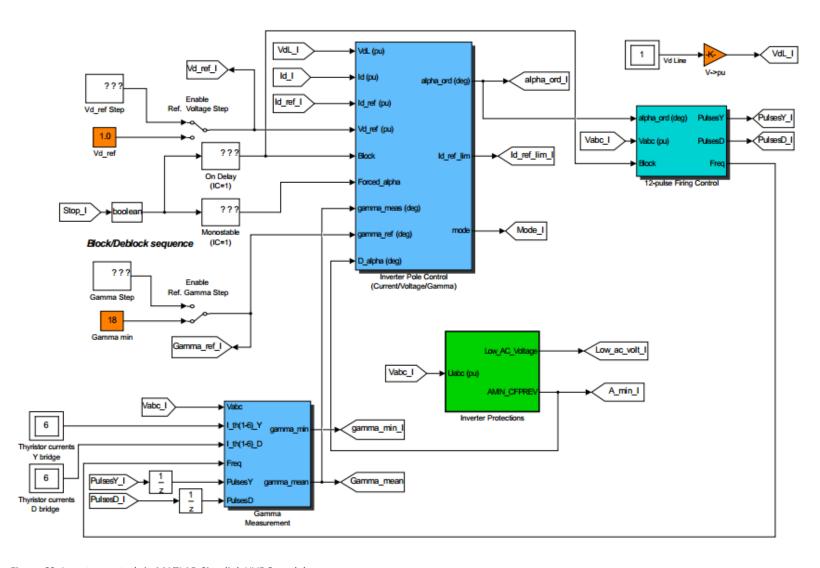

| Figure 13. HVDC model in MATLAB-Simulink [29]                                                          | 17                  |

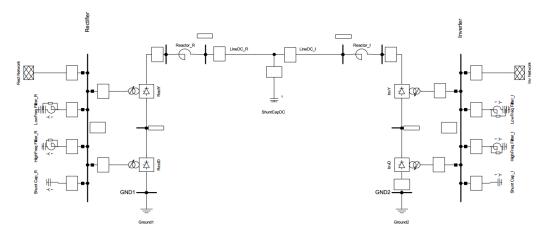

| Figure 14. HVDC model in PSCAD [30]                                                                    | 18                  |

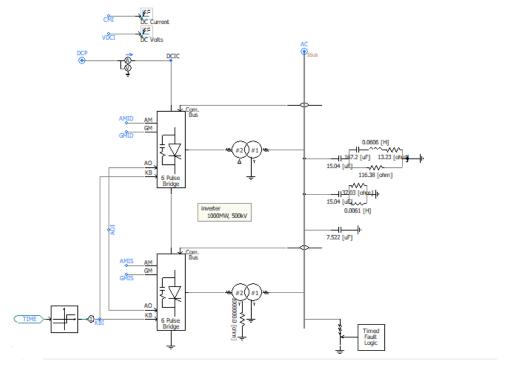

| Figure 15. HVDC model in PSCAD. Inverter details [30]                                                  | 18                  |

| Figure 16. HVDC model in Digsilent-PowerFactory. [35]:                                                 | 19                  |

| Figure 17. HVDC model in Digsilent-PowerFactory. HVDC controls (Composite frame) [35]                  | 19                  |

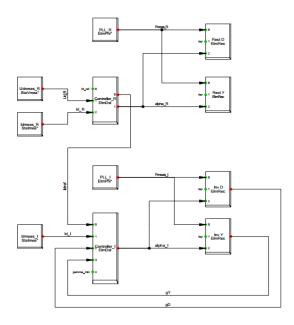

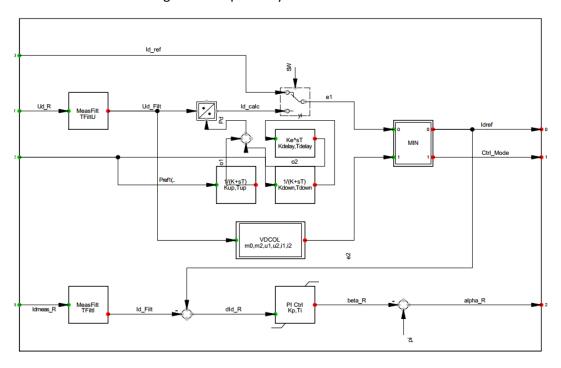

| Figure 18. HVDC model in Digsilent-PowerFactory. Rectifier controls (Composite model) [35].            | 20                  |

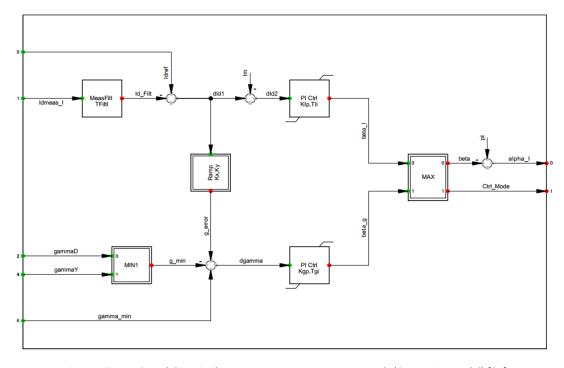

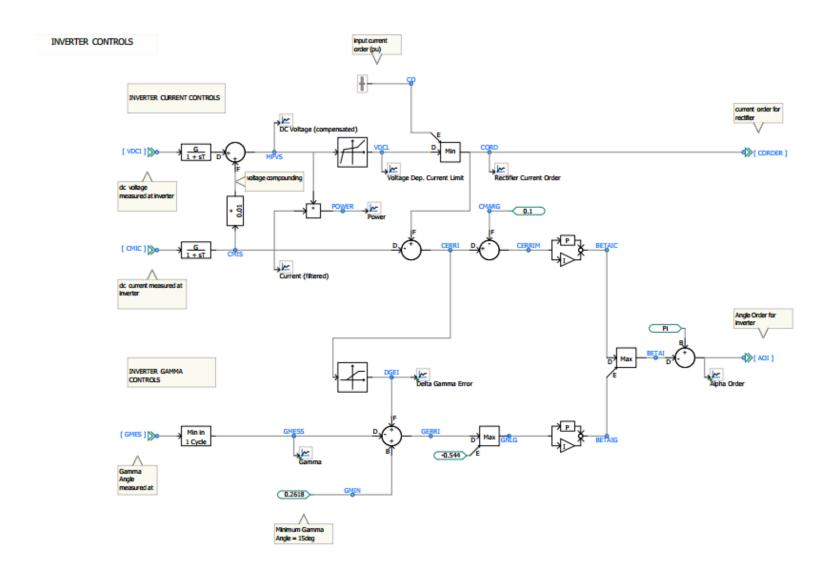

| Figure 19. HVDC model in Digsilent-PowerFactory. Inverter controls (Composite model) [35]              | 20                  |

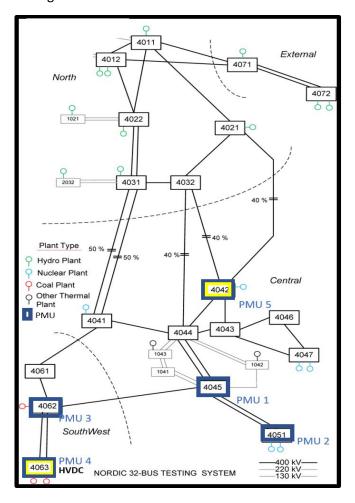

| Figure 20. Modified Nordic32 network                                                                   |                     |

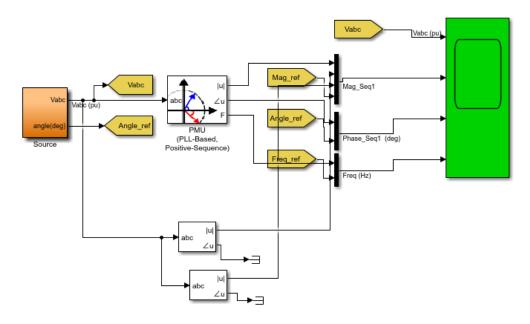

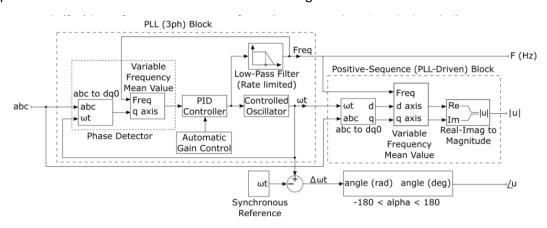

| Figure 21. Model for testing the PMU block, based on [29]                                              | 22                  |

| Figure 22. PMU model in detail [29]                                                                    |                     |

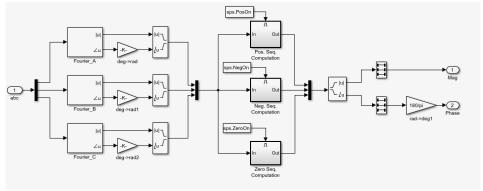

| Figure 23. Sequence analyzer model in Simulink [30].                                                   | 23                  |

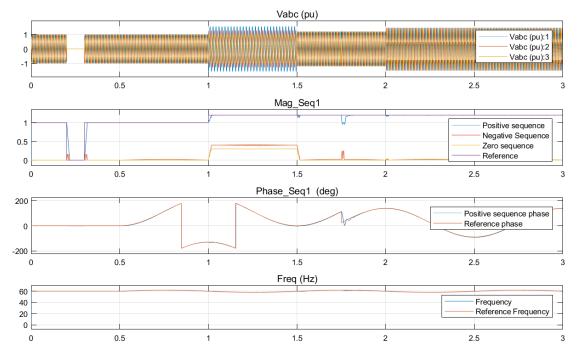

| Figure 24. PMU benchmark model simulation with test signal. At t=0 has Positive-sequence vo            | ltage               |

| = 1 pu and phase 0 deg. Between 0.2 s $<$ t $<$ 0.4 s the Positive-sequence voltage falls to 0 p.u. In | ı t >               |

| $0.5$ a sinusoidal frequency modulation (58/62 Hz Freq = 1 Hz) is applied. During the interval 1 $\pm$ | s <t<< td=""></t<<> |

| 1.5 s unbalance (20% 3rd + 30% 4th) are added. First graph shows the AC voltage, the second            | one                 |

| the PMU output and then phase of the positive sequence phasor and frequency respectively.              |                     |

| Figure 25. Transmission system model                                                                   | 26                  |

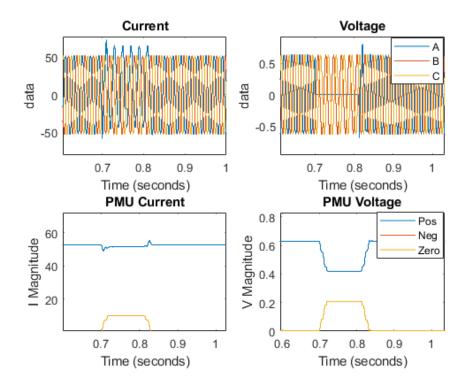

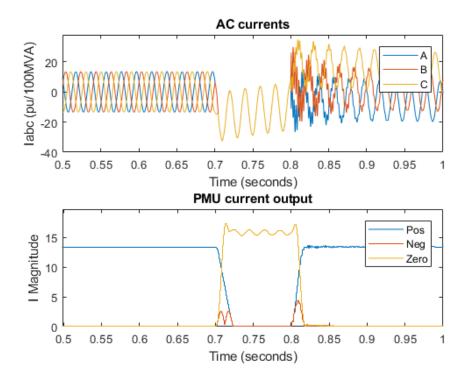

| Figure 26. SLG fault in transmission model. Fault applied at t=0.7 and self-cleared at t=0.8 in b      | us2.                |

|                                                                                                        | 26                  |

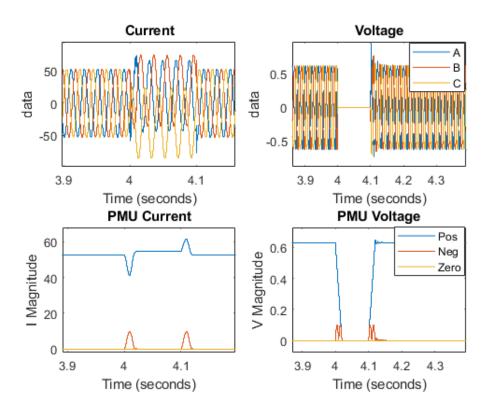

| Figure 27. Three-phase fault in transmission model. Fault applied at t=0.7 and self-cleared at t       | =0.8                |

| in bus2                                                                                                |                     |

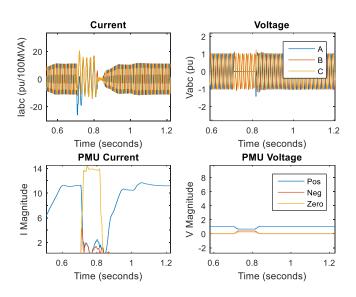

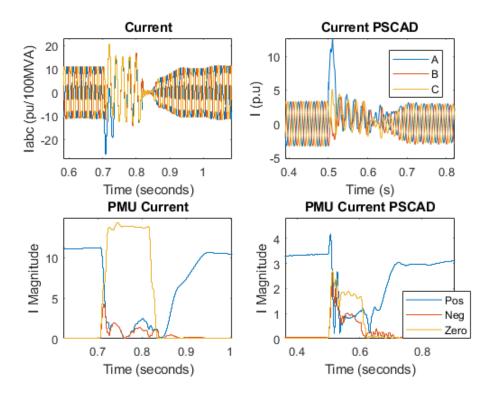

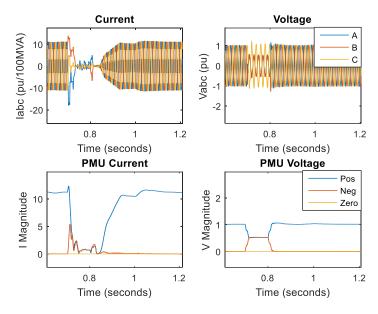

| Figure 28. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared a        | ıt                  |

| t=0.8 s in MATLAB-Simulink. Fault resistance R=0.01 Ohms. AC current and voltage and PMU               |                     |

| outputs                                                                                                | 28                  |

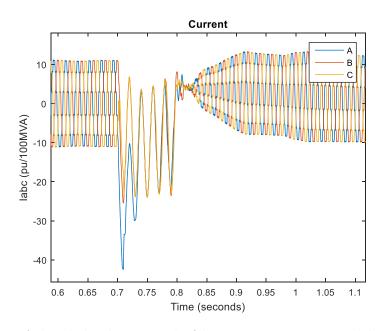

| Figure 29. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

|-----------------------------------------------------------------------------------------------------|

| t=0.8 s. Fault resistance R=0.01 Ohms. AC current detail                                            |

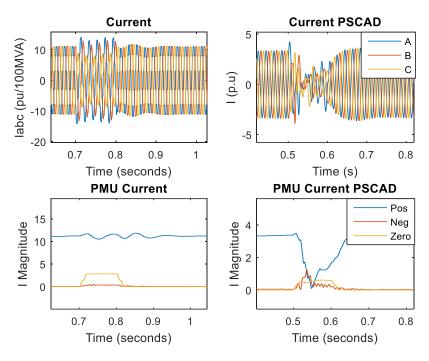

| Figure 30. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

| t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Fault resistance |

| R=0.01 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD (Right) 2                |

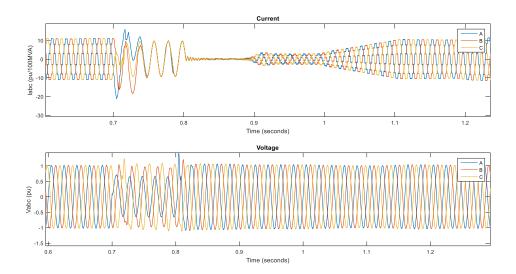

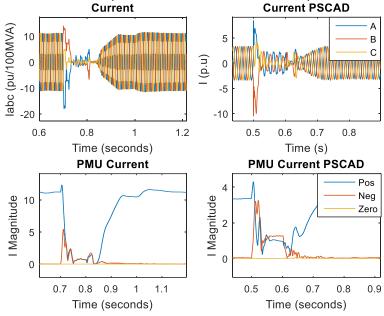

| Figure 31. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

| t=0.8 s in MATLAB-Simulink. Fault resistance R=10 Ohms. AC current (above) and voltage (Below).     |

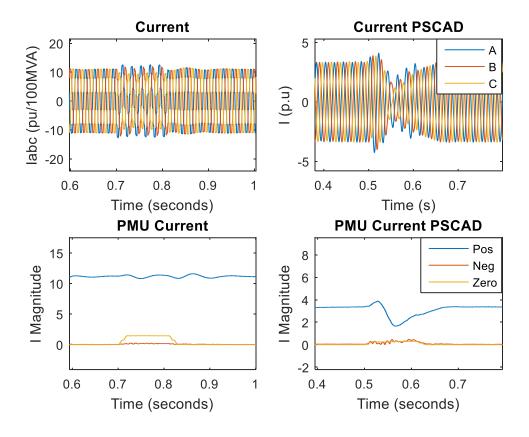

| Figure 32. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

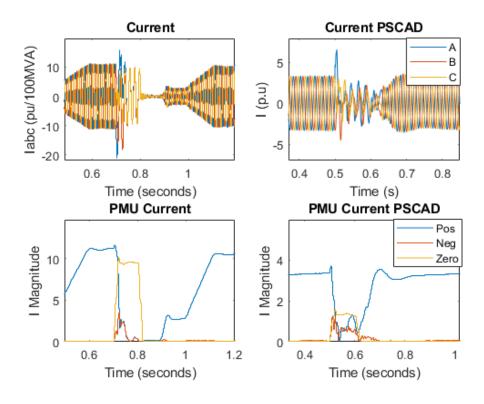

| t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Fault resistance |

| R=10 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD (Right)3                   |

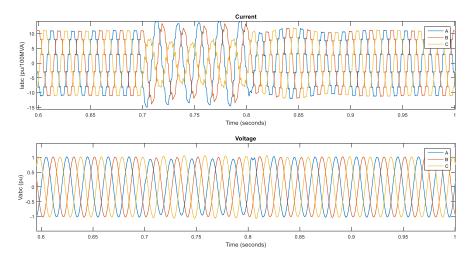

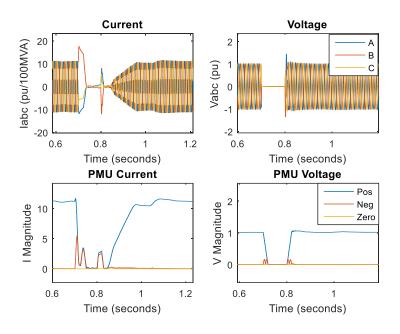

| Figure 33. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

| t=0.8 s. Fault resistance R=50 Ohms. AC current and voltage 3                                       |

| Figure 34. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

| t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Fault resistance |

| R=50 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD (Right)3                   |

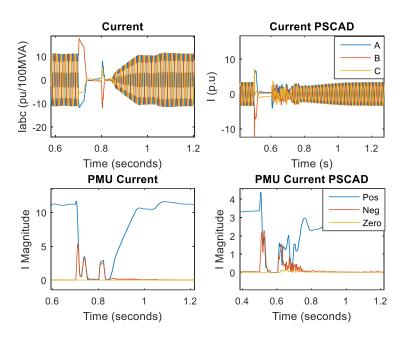

| Figure 35. SLG fault applied on the inverter side of the HVDC converter at t=0.7s and cleared at    |

| t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Fault resistance |

| R=100 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD (Right) 3                 |

| Figure 36. Two-Phase to ground fault applied on the inverter side of the HVDC converter at $t=0.7s$ |

| and cleared at t=0.8 s. Fault resistance R=0.01 Ohms. AC current and voltage and PMU outputs 3      |

| Figure 37. Figure 27SLG fault applied on the inverter side of the HVDC converter at t=0.7s and      |

| cleared at t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Fault |

| resistance R=100 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD (Right)        |

| Figure 38. Two-Phase fault applied on the inverter side of the HVDC converter at t=0.7s and         |

| cleared at t=0.8 s. Fault resistance R=0.01 Ohms. AC current and voltage and PMU outputs 3          |

| Figure 39. Two-phase fault applied on the inverter side of the HVDC converter at t=0.7s and         |

| cleared at t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Faul  |

| resistance R=100 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD (Right)        |

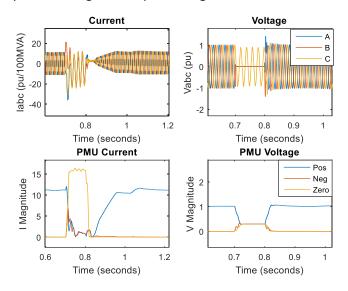

| Figure 40. Three-Phase fault applied on the inverter side of the HVDC converter at t=0.7s and       |

| cleared at t=0.8 s. Fault resistance R=0.01 Ohms. AC current and voltage and PMU outputs 3          |

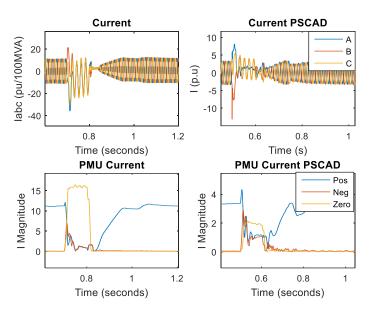

| Figure 41. Three-Phase fault applied on the inverter side of the HVDC converter at t=0.7s and       |

| cleared at t=0.8 s in MATLAB-Simulink and applied at t=0.5 s and cleared at t=0.6 s in PSCAD. Fault |

| resistance R=0.01 Ohms. AC current and PMU output in MATLAB-Simulink (Left) and PSCAD               |

| (Right)                                                                                             |

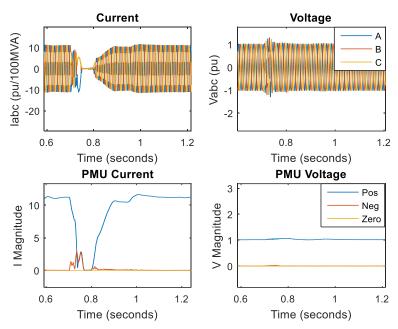

| Figure 42. HVDC converter failure simulation at t=0.7s and cleared at t=0.8 s. AC current and       |

| voltage and PMU outputs                                                                             |

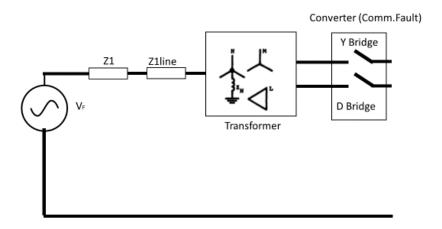

| Figure 43. Schematic model of the inverter side when commutation failures happen                    |

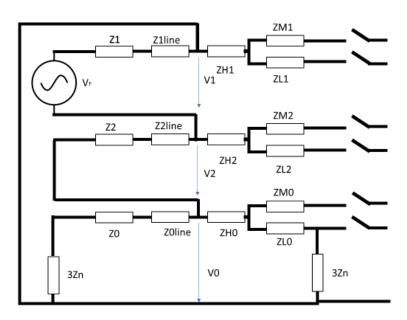

| Figure 44. SLG fault at the inverter side during commutation failure. Sequence network with zero    |

| fault resistance3                                                                                   |

| Figure 45. Two-phase fault at the inverter side during commutation failure. Sequence network        |

| with zero fault resistance                                                                          |

| Figure 46. Two-phase to ground fault at the inverter side during commutation failure. Sequence network with zero fault resistance                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 47. Three-Phase fault at the inverter side during commutation failure. Sequence network                                                                                                          |

| with zero fault resistance39                                                                                                                                                                            |

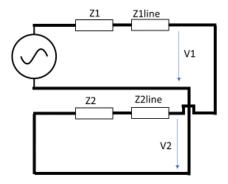

| Figure 48. System equivalent during commutation failure modelled in MATLAB-Simulink 39                                                                                                                  |

| Figure 49. SLG fault simulated in the delta transformer model. Fault applied on the inverter side at                                                                                                    |

| t=0.7 s and self-cleared at t=0.8 in MATLAB-Simulink                                                                                                                                                    |

| Figure 50. AC currents in the HVDC benchmark model simulation in DigSilent-PowerFactory. SLG fault applied on the inverter side of the transformer at t=0s and cleared (Self-extinguish) at t=0.1s.  42 |

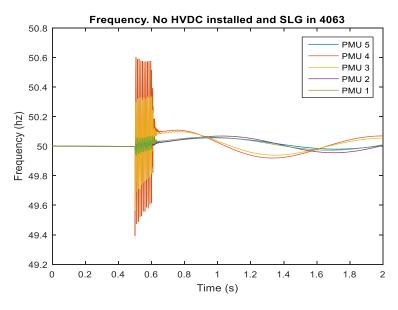

| Figure 51. SLG fault on Bus4063 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed. Frequency signal                                                                                             |

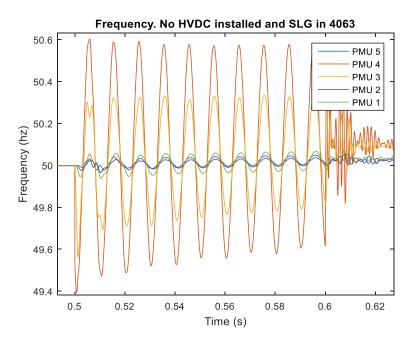

| Figure 52.SLG fault on Bus4063 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed. Frequency signal detail (100 Hz component)44                                                                  |

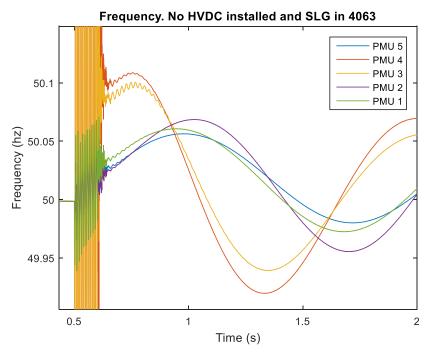

| Figure 53. SLG fault on Bus4063 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed. Frequence signal detail (delay)                                                                              |

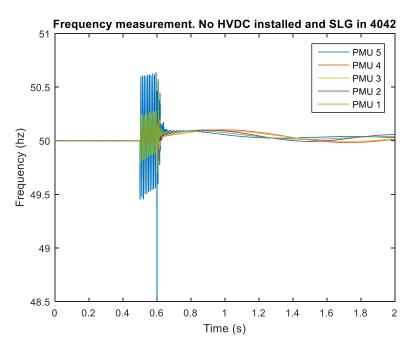

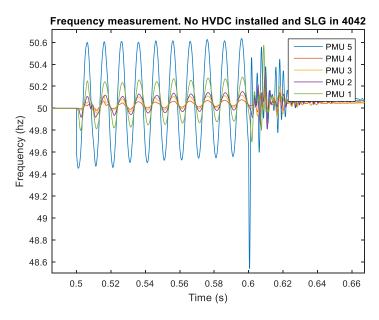

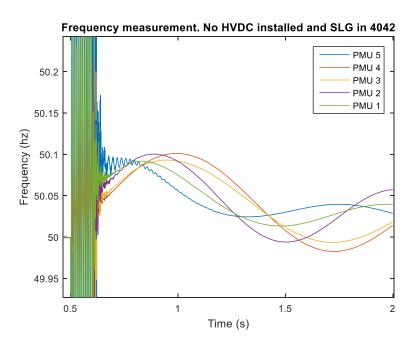

| Figure 54. SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Frequency signal45                                                                                               |

| Figure 55. SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Frequency signal detail (100 Hz component)45                                                                     |

| Figure 56. SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Frequency signal detail (Delay)                                                                                  |

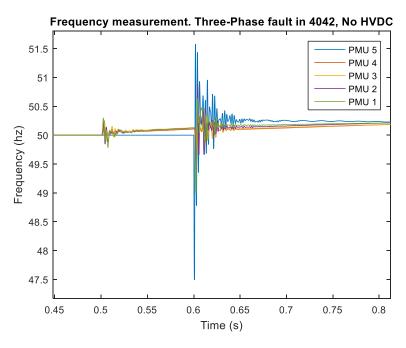

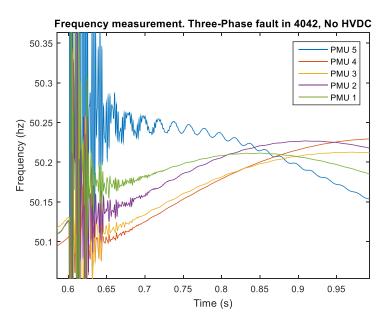

| Figure 57. Three.Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed.  Frequency signals                                                                                  |

| Figure 58. Three.Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed.  Frequency signal detail                                                                            |

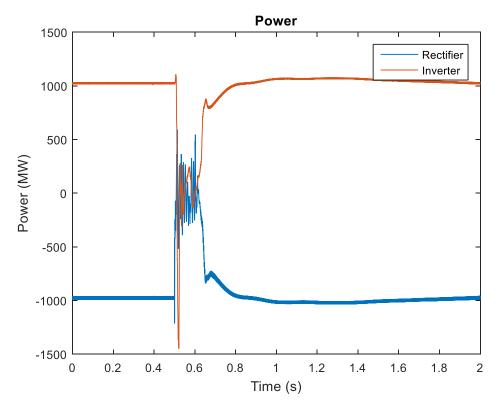

| Figure 59. Power profile through the converter when commutation failure. SLG fault applied on the inverter side att=0.5 s and self-cleared at t=0.6 s                                                   |

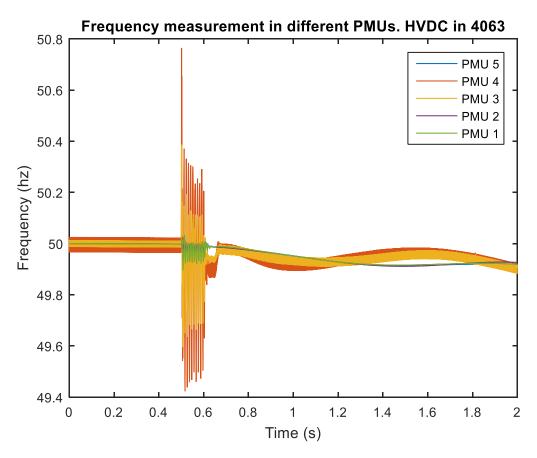

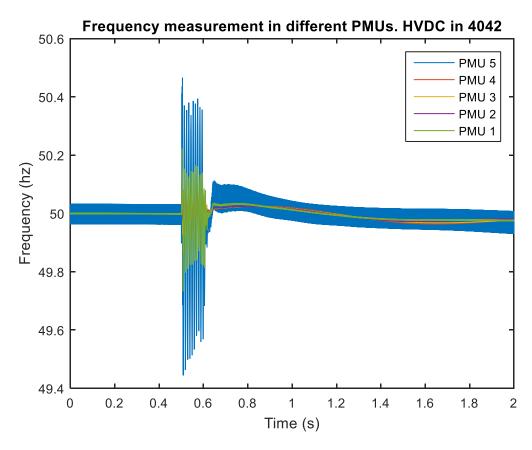

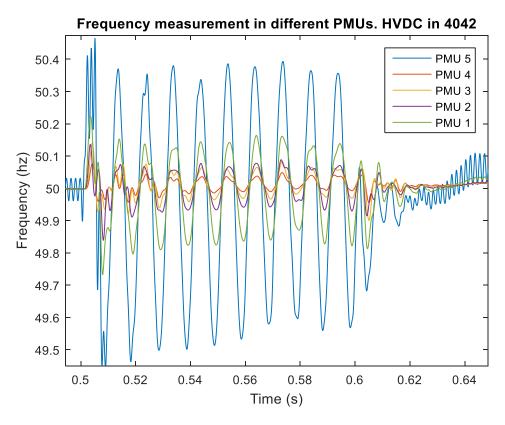

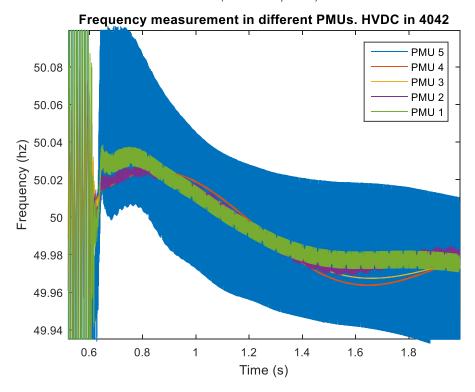

| Figure 60. SLG fault on Bus 4063 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 4063.  Frequency signals                                                                                 |

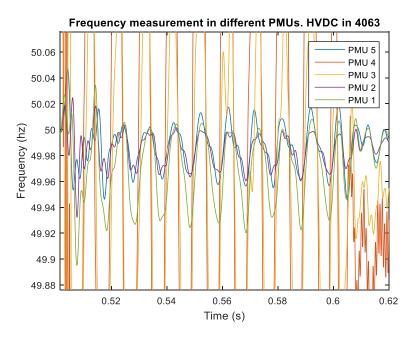

| Figure 61. SLG fault on Bus 4063 at t=0.5 s and cleared at t=0.6 s. HVDC installed on Bus 4063.  Frequency signals detail                                                                               |

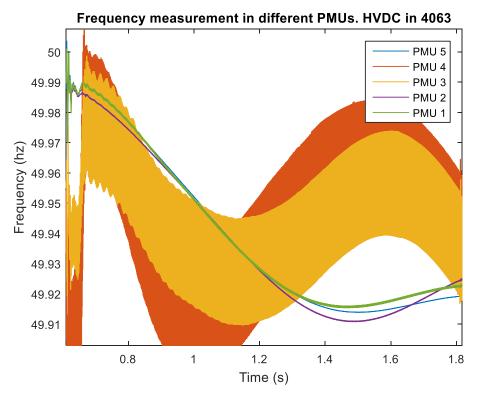

| Figure 62. SLG fault on Bus 4063 at t=0.5 s and cleared at t=0.6 s. HVDC installed on Bus 4063.  Frequency signals detail                                                                               |

| Figure 63. SLG fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 4063.                                                                                                    |

| Frequency signals                                                                                                                                                                                       |

| Figure 64. SLG fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 4063.                                                                                                    |

| Frequency signals detail (100 Hz component)52                                                                                                                                                           |

| Figure 65. SLG fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 4063.                                                                                                    |

| Frequency signals detail (Delays)52                                                                                                                                                                     |

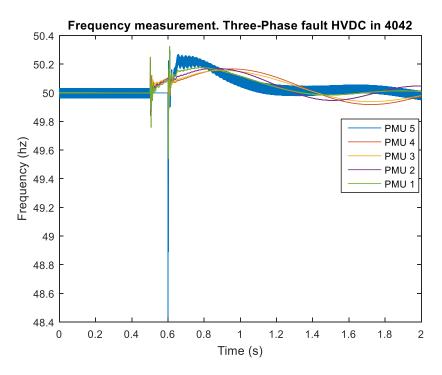

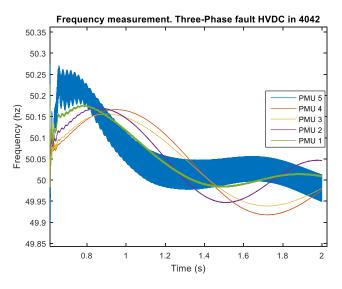

| Figure 66. Three-Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on                                                                                                      |

| Bus 4063. Frequency signal53                                                                                                                                                                            |

| Figure 67. Three-Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on                                                                                                      |

| Bus 4063. Frequency signals detail (Delays)53                                                                                                                                                           |

| Figure 68. Inverter controls in PSCAD HVDC model                                                                                                                      | . 62 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 69. Inverter controls in MATLAB-Simulink HVDC model                                                                                                            | . 63 |

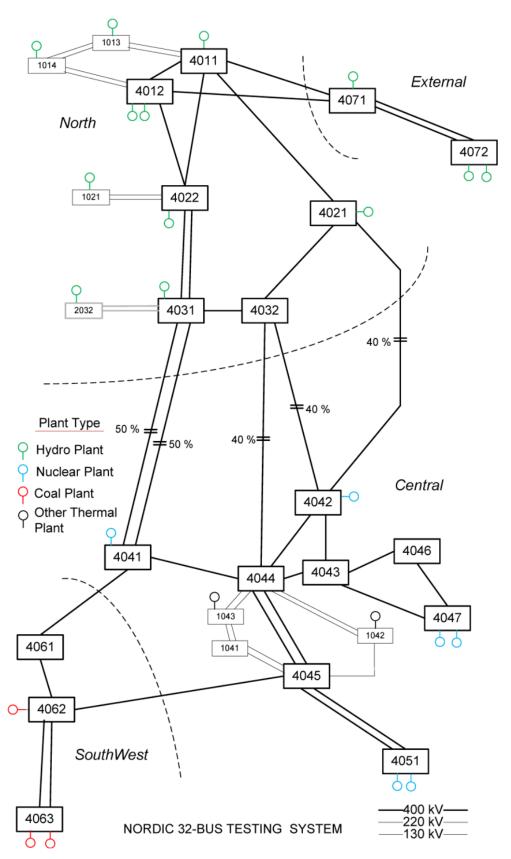

| Figure 70. Original Nordic32 model [32]                                                                                                                               | . 64 |

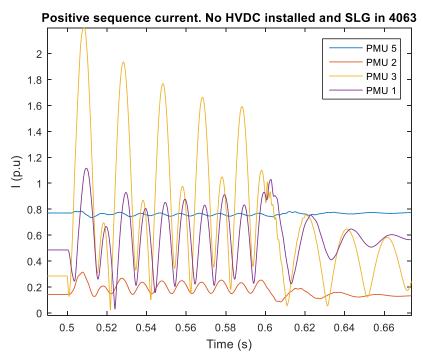

| Figure 71. SLG fault on Bus4063 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed. Positive                                                                   | e    |

| sequence current.                                                                                                                                                     | . 65 |

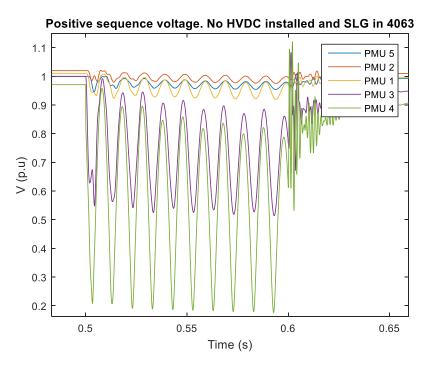

| Figure 72. SLG fault on Bus4063 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Positive                                                                        |      |

| sequence voltage.                                                                                                                                                     |      |

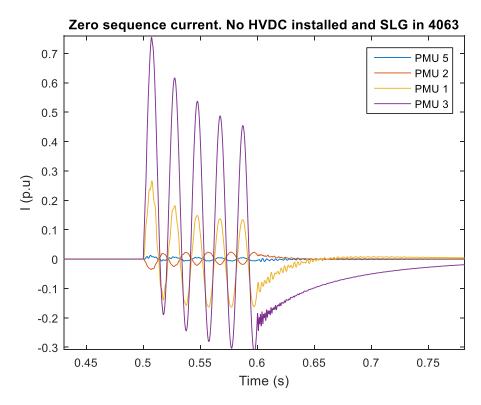

| Figure 73. SLG fault on Bus4063 at $t$ =0.5 s and cleared at $t$ =0.6 s. No HVDC installed. Zero sequence $t$ =0.5 s and cleared at $t$ =0.6 s.                       | nce  |

| current                                                                                                                                                               | . 66 |

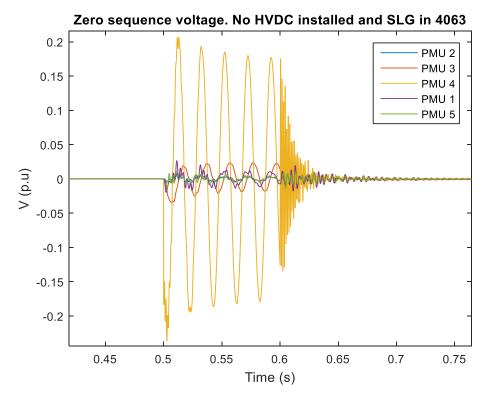

| Figure 74. SLG fault on Bus4063 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed. Zero                                                                       |      |

| sequence voltage                                                                                                                                                      | . 66 |

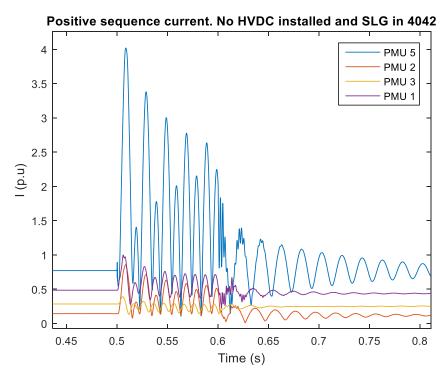

| Figure 75. SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Positive                                                                       |      |

| sequence current                                                                                                                                                      | . 67 |

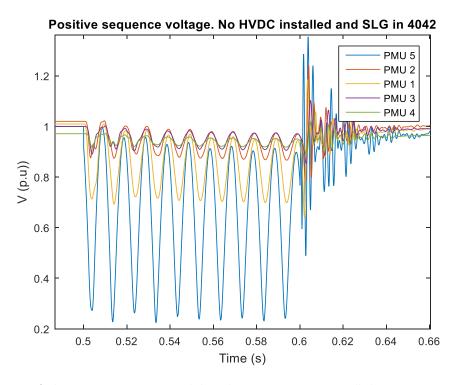

| Figure 76. SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Positive                                                                       |      |

| sequence voltage                                                                                                                                                      | . 67 |

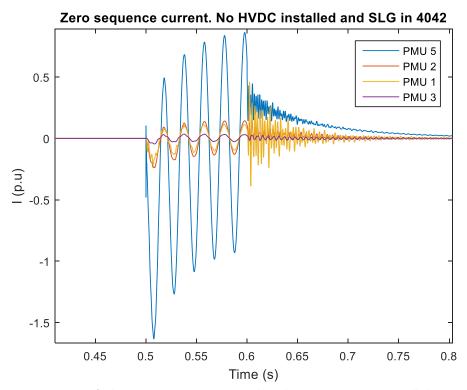

| Figure 77. SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Zero-                                                                          |      |

| sequence current                                                                                                                                                      |      |

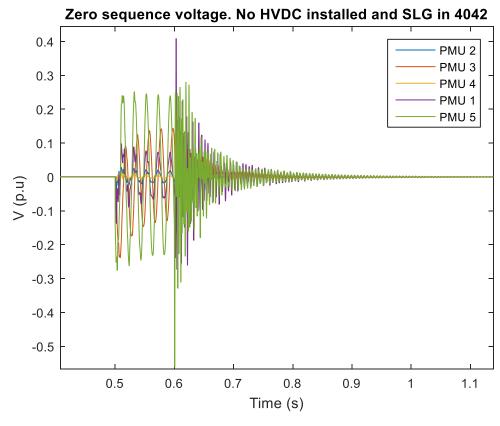

| Figure 78 SLG fault on Bus 4042 at t=0.5 s and cleared at t=0.6 s. No HVDC installed. Zero-seque                                                                      | nce  |

| voltage                                                                                                                                                               |      |

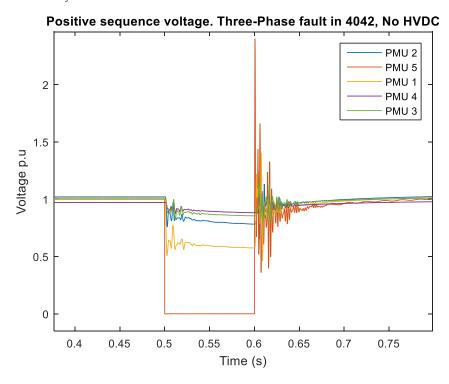

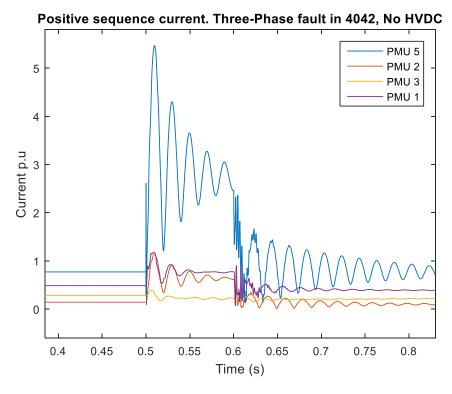

| Figure 79. Three.Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. No HVDC installed                                                                    |      |

| Positive-sequence voltage signals                                                                                                                                     |      |

| Figure 80. Three.Phase fault on Bus 4042 at $t=0.5  s$ and self-cleared at $t=0.6  s$ . No HVDC installed                                                             |      |

| Positive-sequence current signals                                                                                                                                     |      |

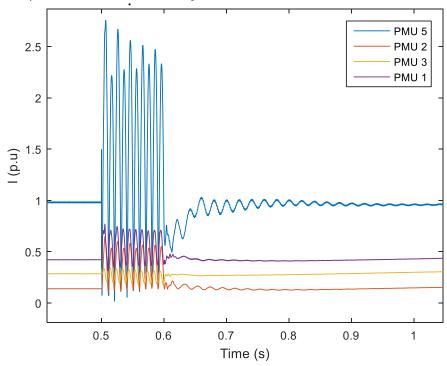

| Figure 81. SLG fault on Bus 4063 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 406                                                                    |      |

| Positive sequence current                                                                                                                                             |      |

| Figure 82. SLG fault on Bus 4063 at $t=0.5 \text{ s}$ and self-cleared at $t=0.6 \text{ s}$ . HVDC installed on Bus 4063 at $t=0.5 \text{ s}$ and $t=0.6 \text{ s}$ . |      |

| Positive sequence voltage                                                                                                                                             |      |

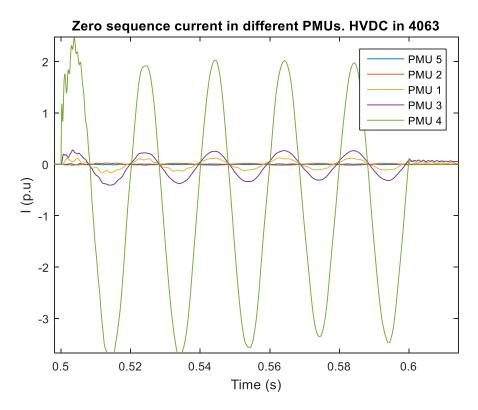

| Figure 83. SLG fault on Bus 4063 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 406                                                                    |      |

| Zero sequence current                                                                                                                                                 |      |

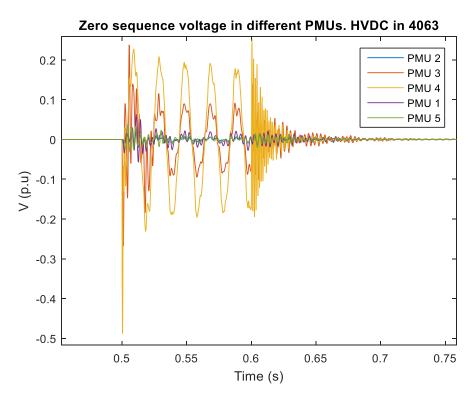

| Figure 84. SLG fault on Bus 4063 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 406                                                                    |      |

| Zero sequence voltage                                                                                                                                                 | . 71 |

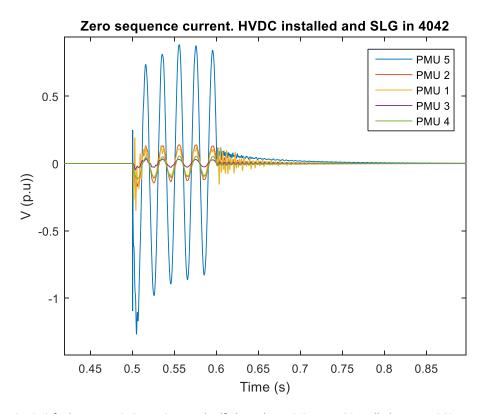

| Figure 85. SLG fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 406                                                                    |      |

| Positive sequence current                                                                                                                                             |      |

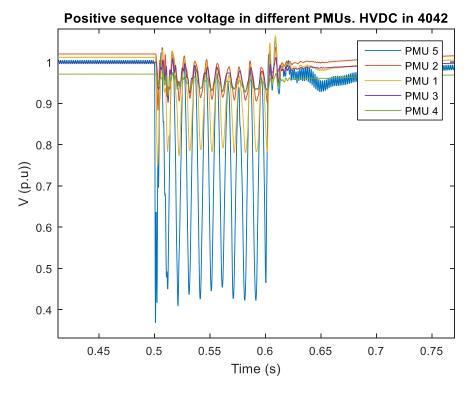

| Figure 86. SLG fault on Bus 4042 at $t=0.5 \text{ s}$ and self-cleared at $t=0.6 \text{ s}$ . HVDC installed on Bus 4060 at $t=0.6 \text{ s}$ .                       |      |

| Positive sequence voltage                                                                                                                                             |      |

| Figure 87. SLG fault on Bus 4042 at $t=0.5 \text{ s}$ and self-cleared at $t=0.6 \text{ s}$ . HVDC installed on Bus 4060 at $t=0.6 \text{ s}$ .                       |      |

| Zero- sequence current                                                                                                                                                |      |

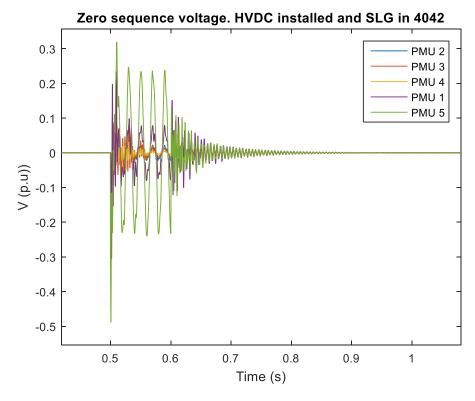

| Figure 88. SLG fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed on Bus 406                                                                    |      |

| Zero-sequence voltage                                                                                                                                                 |      |

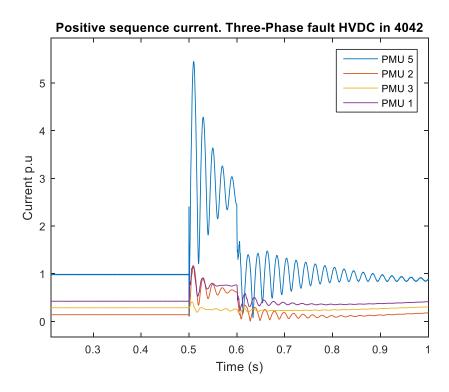

| Figure 89. Three-Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed or                                                                    |      |

| Bus 4063. Positive-sequence voltage signals.                                                                                                                          |      |

| Figure 90. Three-Phase fault on Bus 4042 at t=0.5 s and self-cleared at t=0.6 s. HVDC installed or                                                                    |      |

| Bus 4063. Positive-sequence current signals.                                                                                                                          | . 74 |

### Contents

| A  | cknowledgements                                                           | ii  |

|----|---------------------------------------------------------------------------|-----|

| P  | reface                                                                    | iii |

| Li | ist of abbreviations                                                      | iv  |

| Li | ist of figures                                                            | v   |

| 1. | Introduction                                                              | 1   |

|    | 1.1 Background                                                            | 1   |

|    | 1.2 Objectives                                                            | 3   |

|    | 1.3 Methodology                                                           | 4   |

|    | 1.4 Limitations                                                           | 5   |

|    | 1.5 Thesis structure                                                      | 6   |

| 2. | . Theoretical background                                                  | 7   |

|    | 2.1 HVDC converters and commutation faults                                | 7   |

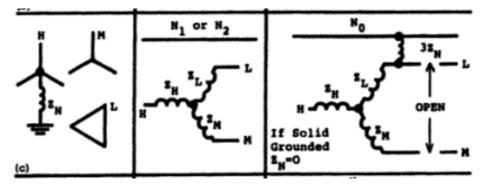

|    | 2.2 Sequence connections for transformer banks used in HVDC links         | 13  |

|    | 2.3 Phasor Measurement Units                                              | 14  |

|    | 2.4 Fault detection and location methods based on sparse PMU measurements | 15  |

| 3. | . Modelling tools and simulation models                                   | 16  |

|    | 3.1 Simulation tools                                                      | 16  |

|    | 3.1.1 PSCAD/EMTDC and PSB/Simulink                                        | 16  |

|    | 3.1.2 Digsilent-Power Factory                                             | 16  |

|    | 3.2 Network models                                                        | 17  |

|    | 3.2.1 CIGRÉ HVDC benchmark                                                | 17  |

|    | 3.2.2 Nordic 32                                                           | 21  |

|    | 3.3 PMU model                                                             | 22  |

| 4. | . Commutation faults in CIGRÉ HVDC benchmark model                        | 25  |

|    | 4.1 Faults in a transmission line with a PMU installed                    | 26  |

|    | 4.2 Faults in a HVDC link with PMUs installed                             | 28  |

|    | 4.2.1. SLG Fault applied at the inverter bus                              | 28  |

| 4.2.3 Two-phase fault applied at the inverter bus 4.2.4 Three-phase fault applied at the inverter bus 4.2.5 Converter failure 4.3 System equivalent during commutation failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.2.2 Two-phase to ground fault applied at the inverter bus         | 33 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----|

| 4.2.5 Converter failure  4.3 System equivalent during commutation failure  4.4 Summary HVDC-link simulations  5. Commutation failure detection and location in Nordic32 network  5.1 HVDC simulation in Digsilent-PowerFactory  5.2 Simulation of faults in the Nordic32 network using PowerFactory  5.2.1 SLG fault on bus 4063- No converter installed  5.2.2 SLG fault on bus 4042- No converter installed  5.2.3 Three-Phase fault on bus 4042- No converter installed  5.3 Simulation of commutation failures caused by SLG and Three-phase faults in externally connected HVDC converters along the Nordic32 network using Digsilent-PowerFactory  5.3.1 HVDC externally installed at bus 4063- SLG fault inverter  5.3.2 HVDC externally installed at bus 4042- SLG fault inverter  5.3.3 HVDC externally installed at bus 4042- 3-Phase fault inverter  5.4 Nordic 32 simulations' summary  6. Discussion and implications  6.1 Commutation failure in PMU data  6.2 Commutation failure detection and location  7. Conclusions and future work | 4.2.3 Two-phase fault applied at the inverter bus                   | 32 |

| 4.3 System equivalent during commutation failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.2.4 Three-phase fault applied at the inverter bus                 | 35 |

| 4.4 Summary HVDC-link simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.2.5 Converter failure                                             | 36 |

| 5. Commutation failure detection and location in Nordic32 network  5.1 HVDC simulation in Digsilent-PowerFactory  5.2 Simulation of faults in the Nordic32 network using PowerFactory  5.2.1 SLG fault on bus 4063- No converter installed.  5.2.2 SLG fault on bus 4042- No converter installed.  5.2.3 Three-Phase fault on bus 4042- No converter installed.  5.3 Simulation of commutation failures caused by SLG and Three-phase faults in externally connected HVDC converters along the Nordic32 network using Digsilent-PowerFactory.  5.3.1 HVDC externally installed at bus 4063- SLG fault inverter.  5.3.2 HVDC externally installed at bus 4042- SLG fault inverter.  5.3.3 HVDC externally installed at bus 4042- 3-Phase fault inverter.  5.4 Nordic 32 simulations' summary.  6. Discussion and implications.  6.1 Commutation failure in PMU data.  6.2 Commutation failure detection and location.  7. Conclusions and future work.                                                                                                   | 4.3 System equivalent during commutation failure                    | 37 |

| 5.1 HVDC simulation in Digsilent-PowerFactory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.4 Summary HVDC-link simulations                                   | 41 |

| 5.2 Simulation of faults in the Nordic32 network using PowerFactory  5.2.1 SLG fault on bus 4063- No converter installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5. Commutation failure detection and location in Nordic32 network   | 42 |

| 5.2.1 SLG fault on bus 4063- No converter installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.1 HVDC simulation in Digsilent-PowerFactory                       | 42 |

| 5.2.2 SLG fault on bus 4042- No converter installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.2 Simulation of faults in the Nordic32 network using PowerFactory | 43 |

| 5.2.3 Three-Phase fault on bus 4042- No converter installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2.1 SLG fault on bus 4063- No converter installed                 | 43 |

| 5.3 Simulation of commutation failures caused by SLG and Three-phase faults in externally connected HVDC converters along the Nordic32 network using Digsilent-PowerFactory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2.2 SLG fault on bus 4042- No converter installed                 | 45 |

| connected HVDC converters along the Nordic32 network using Digsilent-PowerFactory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.2.3 Three-Phase fault on bus 4042- No converter installed         | 47 |

| 5.3.2 HVDC externally installed at bus 4042- SLG fault inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · · · · · · · · · · · · · · · · · · ·                               | •  |

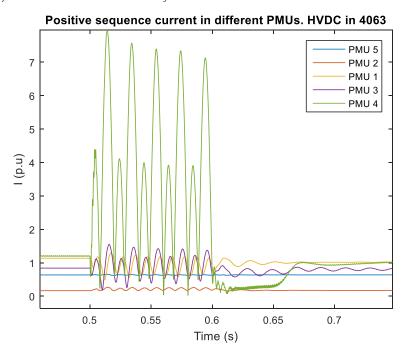

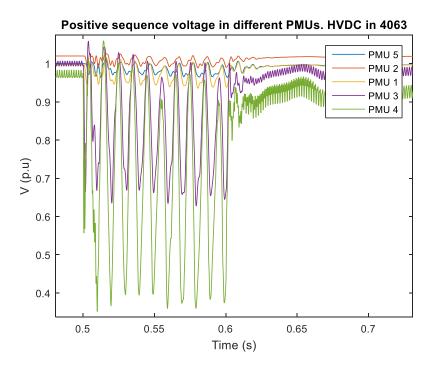

| 5.3.3 HVDC externally installed at bus 4042- 3-Phase fault inverter  5.4 Nordic 32 simulations' summary  6. Discussion and implications  6.1 Commutation failure in PMU data  6.2 Commutation failure detection and location  7. Conclusions and future work  8 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.3.1 HVDC externally installed at bus 4063- SLG fault inverter     | 49 |

| 5.4 Nordic 32 simulations' summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.3.2 HVDC externally installed at bus 4042- SLG fault inverter     | 51 |

| 6. Discussion and implications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.3.3 HVDC externally installed at bus 4042- 3-Phase fault inverter | 53 |

| 6.1 Commutation failure in PMU data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.4 Nordic 32 simulations' summary                                  | 54 |

| 6.2 Commutation failure detection and location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6. Discussion and implications                                      | 55 |

| 7. Conclusions and future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.1 Commutation failure in PMU data                                 | 55 |

| 8 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6.2 Commutation failure detection and location                      | 56 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7. Conclusions and future work                                      | 57 |

| 9 Annexes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8 References                                                        | 58 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9 Annexes                                                           | 61 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ANNEY B. Simulation results                                         | 4  |

#### 1. Introduction

The purpose of this introductory chapter is to define the topic of the research and what it seeks to achieve. Apart from that, a short background and an explanation of the methodology and limitations found during the process are included.

#### 1.1 Background

Due to human action, climate change and its consequences arise [1][2]. Population and energy consumption increases globally as well as pollution does. Therefore, humankind must find new ways of generate, manage and transform energy. Most authors and institutions state that electricity will have a dominant role in the future's energy system, so the electric power system must be upgraded in order to meet the future needs [1][2][3][4]

Among other objectives regarding social or economic issues, the European Commission (EC) has developed the "20/20/20" energy targets for mitigating climate change [3]. Recently, these targets have been updated for 2030 [4], which basically consist in achieve the following objectives:

- At least 40% cuts in greenhouse gas emissions (from 1990 levels)

- At least 27% share for renewable energy

- At least 27% improvement in energy efficiency

The framework seeks to achieve a low-carbon economy that ensures affordable energy for all consumers, reduces the dependence on energy imports and consequently provide environmental and health benefits

In order to achieve these goals, the use of renewable energies emerge as one of the cleaner, and currently cost-effective, measures that would lead to shift towards a sustainable future. Thus, the developing of Smart Grids, given that helps to increase renewables' penetration and increases energy efficiency, are a key point in the EC agenda [4].

Apart from environmental reasons, the high share of renewables and an increase on energy efficiency would lead Europe to become more energy independent. In this case, the energy supply will not depend on imports but will be generated in-situ.

Studies as [5] concluded that a 100% renewable system based on wind, solar and hydropower is feasible at a reasonable price, being electricity and hydrogen the unique energy carriers used. This research has been revised and criticized in [6], that states that the previous work has been based on invalid modelling tools, modeling errors and inadequately supported assumptions. More recent studies as [6] agrees that 80% penetration of renewables can be achieves at a reasonable cost, but the last 20% remaining is difficult and expensive to achieve. Based on [6] conclusions, a broader portfolio of energy sources, including nuclear, bioenergy and Carbon Capture and Storage technologies (CCS) can truly help to decarbonize the energy system in a realistic way. In any case, the integration of renewables will reduce the dependency on other countries, even though to become 100 % independent is not realistic at all at a cheap price.

Due to the variability inherent in renewable energy sources, as solar and wind energy, transmission grids will suffer bigger challenges as the share of RES increases. Highly controllable networks are needed in order to sustain stability. To upgrade the current network integrating power electronics and communications is crucial for being able to tackle future problems caused by generation-load unbalance in an energy system with high penetration of renewables.

The evolution of power electronics as HVDC connections, FACTS controllers, Phasor measurement units (PMU) and the decrease in Renewable energy sources (RES) prices are creating the perfect landscape for countries in order to renew their power networks. Wide-area measurement systems (WAMS) based on PMU's, whose reporting time is much faster than the usual SCADA system, allows the grid operators to see detailed dynamics of the system in real-time. Also, as the measurements are synchronized, grid operators can analyze the stability problem much better thanks to more accurate angle difference measurements. [20]

High-Voltage Direct-Current transmission can be more advantageous than traditional AC transmission in many situations. These systems are a suitable and more efficient option for subsea connections, connection of asynchronous systems and long-distance bulk power transmission, apart from specific projects [11]. That is another reason why HVDC-links are an important technology for integrating renewables, such as off-shore wind farms and solar-PV units. The main advantages are its lower energy loss, the capacity to interconnect asynchronous systems and high control capability that enhances network stability [7]. HVDC technology has, when suited, technical, economic and environmental advantages.

Therefore, both PMUs and HVDC will play a role in the managing of integrate renewable energy sources. The interaction of both systems with the rest of the transmission system under unbalanced situations still not deeply explored in some fields.

In the Nordic countries, many spread PMUs are already installed along their networks. The aim so far is to deeply understand electromechanical oscillations between countries. As can be read in [8], the subsequent action is that the damping control of SVC and HVDC devices will be based on PMU data.

After an event in the Nordic system, it was recently realised that HVDC converter commutation failures are not visible to TSO control room. This is unfortunate as the faults may excite power system dynamics. While the SCADA system is generally too slow for detecting commutation faults, using phasor measurement units (PMUs), due to its faster reporting rate, dynamics events of the system can be detected.

That's why a deeper understanding about how PMU's and HVDC-links interact, specifically how HVDC commutation failures are monitored by Phasor Measurement Units (PMUs), is needed. Therefore, this project aims to broaden the knowledge on this topic.

In the present days, algorithms to detect and locate faults based on PMU measurements have been developed already [9], [10] and [38]. On the contrary, location of HVDC commutation failures using PMU measurements has not been treated in literature. Commutation failures is an issue that is almost always analyzed from a "device perspective". AC events that can lead to a commutation failure in a HVDC converter have been studied [11]. On the contrary, how commutation faults affect the exterior network is not deeply understood yet.

#### 1.2 Objectives

The main objective of this Master Thesis is to understand if commutation failures in HVDC converters can be characterized from PMU data.

Commutation faults are normally studied using waveform-simulation in software like PSCAD/EMTDC or MATLAB-Simulink [12], where electromagnetic transients (EMT) are simulated. On the contrary, dynamic phenomena in large systems are normally studied using phasor-simulation in software like PSS/E or DigSilent-PowerFactory.

A first step to combine these two perspectives and include commutation faults in phasor-simulation has been taken in [13]. The cited work focuses on the voltage dip that an AC disturbance creates along a big network. These voltages are compared with the critical voltage dip that lead to a commutation fault in a supposedly installed HVDC converter. How these commutation faults affect the AC system is not studied.

In the first part of the thesis, a model which include a single HVDC link and a PMU has been simulated with the aim to understand how PMUs behaves when a commutation faults happen. The simulation of commutation faults in the CIGRÉ standard benchmark HVDC converter have been carried out both in MATLAB-Simulink, PSCAD and PowerFactory (EMT). The simulations include different types of faults and fault impedances and provide AC signals and PMU signals.

The results are interpreted in order to identify characteristics in PMU data that make it possible to distinguish commutation faults from other disturbances. It is also important to highlight the differences between the simulation programs when simulating the behavior of the system. Physical reasons are given for explaining the behavior found in the AC side of the converter when commutation faults happen.

After understanding the implications of commutation faults in the outer AC network, analyze how these faults spread along a bigger network is highly interesting. In the CIGRÉ HVDC benchmark angle dynamics are excluded as the two AC systems are represented by voltage sources with fixed phase angles. Therefore, a simulation that includes the whole electromechanical dynamics of the system is needed.

The last aim is to point out the main differences in behavior when the HVDC converter is installed and when it's not in order to define characteristics that could be used in detection and location algorithms based on PMU data in future work.

#### 1.3 Methodology

With the aim of achieving these objectives, the following methodology has been followed:

After going through the theoretical documentation, several simulations have been carried out in MATLAB-Simulink, PSCAD. At first, the models used are based on the Benchmark models [27], [28], based on [15] and include a HVDC-link in a simplified network with AC sources at both ends and without focus on angle dynamics but the electromagnetic behavior of the system.

To start with, the PMU Model available in the MATLAB-Simulink library [29] has been upgraded, including the possibility of computing also negative and zero sequence, and simulated. Its performance is checked with the standard IEEEC 37.118 [21]. Then, a Single-line to Ground (SLG) fault and a Three-Phase fault along a transmission line model are simulated, the output is sent to the PMU model and the results are analyzed. That has been done in order to be able to highlight the main differences in behavior when the HVDC converter is installed.

After that, the CIGRÉ standard benchmark HVDC model has been simulated using MATLAB-Simulink and PSCAD, focusing on commutation faults. In the first step, the model is simulated under normal operating conditions. After the analysis of the results and the model, several AC faults, with associated commutation failures, are simulated in a modified model which includes more measurement points. The model's outputs are sent to the PMU model and both group of signals are analyzed and compared with the ones obtained from the transmission model. The result of the analysis aims to characterize commutation faults in the AC side of the HVDC model seen from a PMU perspective.

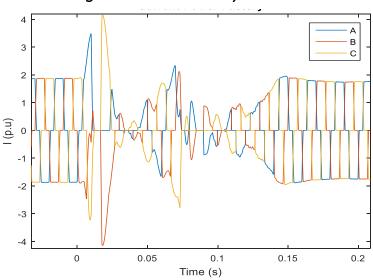

The next step is to simulate the inverter side of the converter, focusing on the delta configuration of the transformer, when a SLG fault happens and leads to a commutation fault. This has been done in order to corroborate the hypothesis that the delta configuration is the reason why the current behaves in a strange way in the AC side of the converter after commutation faults.

The results in the different simulators are analyzed and the main differences highlighted. The reasons of these discrepancies are also provided.

For the second part of the Thesis, a larger model (based on Nordic 32) is simulated in Digsilent-PowerFactory. In this case, the generators' angles are not fixed, as in the previous simulations, and the system is therefore more complex. Before simulating the HVDC converter in a bigger network, a simplified HVDC model is simulated in Digsilent-PowerFactory in order to understand the main differences in the behavior when compared to the MATLAB-Simulink and PSCAD simulations.

Then, the HVDC benchmark model available in Digsilent-PowerFactory is connected to external nodes within the Nordic 32 Network. The new model is tested under normal operation and when SLG faults are applied in the inverter bus where the converter is installed. Five PMUs are installed spread along the network. The PMUs computes frequency and positive and zero sequence of both current and voltage measurements. The computation of the frequency has been done based on PLLs. Three-phase simulations have been done as well, regarding the same principle.

Later on, the information is organized and presented in this report.

#### 1.4 Limitations

Due to time horizon and regarding the scope of the Thesis, the following limitation have arisen.

The HVDC model used is based on the MATLAB-Simulink library example, which is sufficient regarding the scope of the project but could be more detailed, in any case, the model is built based on the CIGRÉ benchmark model [27]. The same happens with the PSCAD model [28], that is based on the library example provided in the software, and the model in DigSilent-PowerFactory [35]. This can be considered a limitation, as the model can be built with more detailed, but also strengthen the truthfulness of the simulation results, as the models are trusted.

In a similar way, the PMU block used for simulations is based on the MATLAB-Simulink library as well. The PMU model computes the positive sequence magnitude, angle and frequency variation of the phasors but also negative and zero sequence, which is not included in the default model. This has been done using sequence analyzers models, which are less accurate than the PMU model itself, as for the sequence analyzer the frequency is given as an input but it's not directly calculated.

Besides, must be said that no physical experiment has been done and all the results come from simulations.

Regarding the second part of the thesis, it would have been interesting to perform more simulations, varying the location of the PMUs and the converter connection point. But due to time restriction it hasn't been possible.

A further analysis on this topic would be highly interesting. A deeper understanding regarding how commutation faults spread along a network and the reasons behind that behavior can be considered as the natural next step. The conclusions of this study can be used for developing a detection and location algorithm for commutations faults but it hasn't been implemented.

Lastly, it must be pointed out that no comparison with real data has been done. Definitely, this is something that must be done in future studies.

#### 1.5 Thesis structure

In this subsection, the outline of the rest of the thesis is exposed. First, after the introduction, an extended background chapter regarding HVDC and commutation faults, sequence components for transformer banks, PMUs and methods that use PMU data for location of events come next.

The next chapter describe the simulators and models used during the whole process of the thesis. Focusing on the differences between the HVDC benchmark model of the three different simulators.

The rest of the thesis can be divided in two parts. The first part focuses on the interaction between HVDC converters and PMU's, using a simple network for that purpose. Several simulations are carried out in PSCAD and MATLAB-Simulink in order to explain how commutation faults are managed by PMUs. First, simulations of a transmission line where PMU are installed is also included in order to understand the differences in behavior when the HVDC link is simulated.

After simulating the transmission line, the HVDC Benchmark model is simulated in MATLAB-Simulink and PSCAD. The simulations include SLG fault, Two-Phase fault, Two-Phase to ground, Three-Phase fault and converter failure.

In order to explain the reasons why the AC current behaves as it does when ground is involved in the fault, a system equivalent during commutation fault is simulated. The model focuses on the configuration of the transformer included in the HVDC model.

The second part focuses on how commutation fault spread along a big network and analyzes how PMU data can be used for detect and locate these faults. Therefore, the next chapter analyzes simulation results from Digsilent-PowerFactory. First, the simulation results of the HVDC benchmark model is included.

In order to summarize and point out important conclusions, a final discussion and conclusion chapters close the research. The discussion aims to conclude the findings from the first part of the thesis, while opening a new discussion regarding the results from the Digsilent-PowerFactory simulations.

The last part of the thesis includes the reference list and annexes.

#### 2. Theoretical background

In this section, the basis of HVDC converters and PMU are defined, including a deep theoretical explanation of commutation faults. The focus is on Line Commuted Converters (LCC), or current based transmission, which is the technology that has been installed mainly in the past years. This technology dominates the existing HVDC installations and commutation failures are intrinsic to it. Other systems, as the newer Voltage Source Converters (VSC), are not considered in this study. These are highly interesting and have several advantages as the ability of exchange active and reactive power independently [17] but have very different behaviour during faults.

Apart from that, due to abnormal operation of the system when commutation faults happen, a theoretical explanation regarding symmetrical components in transformers is also included. This is needed as transformers have a decisive importance in the behaviour of the AC current that will be shown later on.

In this section, the theoretical basis of the electromechanical-wave propagation phenomena and fault detection and location methods based on it are also explained. These methods use PMU data, mostly angle differences and frequency variation in order to determine the location of a fault based on time-of-arrival of the electromechanical waves. Already developed methods are able to detect different kind of faults, but so far, none of them focus on commutation faults.

#### 2.1 HVDC converters and commutation faults

A High Voltage Direct Current connection (HVDC-link) consists basically of a rectifier station, a DC-line, and an inverter station. Each station includes transformers and filter banks.

There exist a CIGRÉ HVDC benchmark model since 1991, proposed in [14], [15]. The model represents a 500-kV,1000-MW HVDC link. The converters are based on thyristors (12-pulse configuration with two six-pulse valves in series), transformers, harmonic filters, shunt capacitors and DC smoothing reactors. The model is connected to weak AC systems (Short circuit ratio 2.5 at 50hz). The simplified model can be seen in the Figure 1. The simulation of the system in MATLAB-Simulink has been done before in [12]

Figure 1. Single-line diagram of the CIGRÉ benchmark HVDC system [15].

LCC converters consume reactive power during normal operation, and that reactive power is supplied by shunt capacitors and other sources. The DC current is smoother thanks to the DC reactor [7]

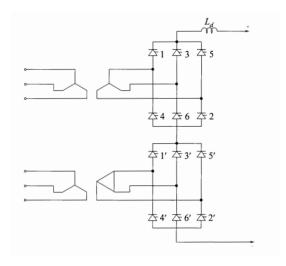

HVDC transmission systems can be implemented using different configurations. This study will focus on 12-Pulse monopolar systems as in [15]. This configuration is widely used for undersea power transmissions [7]. A schema of the configuration cited can be seen in Figure 2.

Figure 2. 12-Pulse Monopolar HVDC [7].

The working principle of the LCC converters is based on the Graetz bridge, which configuration can be seen in Figure 3. In the schema, the voltage sources of the AC network, thyristor valves, L, representing the commutation inductance, and  $L_d$ , that represents the smoothing reactor, are included.

Figure 3. Basic 6-pulse converter [7].