# High-Level Synthesis for Efficient Design and Verification

Alfred Johansson elt13aj2@student.lu.se John Johansson elt13jjo@student.lu.se

Department of Electrical and Information Technology Lund University EITM01/EITM02

> Supervisor: Liang Liu Examiner: Erik Larsson February 19, 2020

© 2020 Printed in Sweden Tryckeriet i E-huset, Lund

### Abstract

Designing hardware using *High Level Synthesis* automates parts of the digital hardware design process. By automating the process control is passed from the designer to the tool, thus it is highly important that the tool generates high performance hardware in terms of area and speed. This thesis explores the tool performance of Vivado HLS using two designs implemented anew with *High Level Synthesis* and *Hardware Description Language*. The evaluations are done based on hardware performance and functional verification times and how these scale to larger designs.

When using *High Level Synthesis* one should have a good idea of what hardware that is ideal for the given design in order to design high performance hardware. The synthesis process of generating *Register Transfer Level*-code from C or C++ is highly dependent on syntax, especially as designs grow larger. This could be satisfied by having a good balance of pre-defined libraries and design specific code and keeping native C data types for high functional verification speed.

There are different ways of designing using *High Level Synthesis* this thesis aims to explore these and highlight their pros and cons. Thus providing guidelines and ideas for how to work with *High Level Synthesis* in different situations.

Keywords: HLS, HDL, VHDL, C, C++, Vivado, FPGA, Xilinx

### Popular Science Summary

Newer digital circuit technologies are rapidly arising which allow for higher clock frequency, better energy efficiency and a higher number of transistors in a given area. All these enhancements opens up for more complex designs. This will in turn increase the development, simulation and verification time taken by the designers. The marketing window for a product is usually short and products needs to be ready for marketing within that window. Otherwise it might lead to huge economical set backs for the developers of the product.

Initially, digital circuit design took place at transistor level, which meant that designers had to place every single transistor which is a time consuming process. As the designs became more complex the development time increased a lot. A hardware description language called VHDL, at first used for document the behaviour of ASIC's (Application Specific Integrated Circuit) became very popular for also describing hardware. This reduced the development time a lot since every line of VHDL corresponds to several transistors. Today HDL coding languages like VHDL and SystemVerilog are the contentious industry standard and the preferred way of designing hardware. But as the designs have gotten even more complex and demanding large bases of VHDL code, techniques to design hardware at a higher abstraction levels have emerged. This way of designing hardware has been around for some years and has been met with some scepticism. So we might be facing a another shift in industry standard if it turns out to give the same benefits as VHDL did back then.

HLS (High Level Synthesis) is a way which lets the development take place at a high level language instead of a low level one. This will speed up development time since functions does not have to be implemented from scratch and also because it requires little knowledge of the hardware compared to HDL coding.

HLS has been around since 1994 but was not seen as matured enough for producing effective hardware in terms of resources and speed. Today there exists a "smörgåsbord" of different vendors which offers HLS, to mention some Cadence's Stratus, Xilinx's Vivado HLS, Mathworks HLS and Mentor's Catapult with more. This thesis will focus on Xilinx's Vivado HLS and evaluate if it can bee seen as mature enough for competing with traditional HDL coding and if there will be any time gain during verification.

### Acknowledgements

Looking back at the last six months it has been an interesting learning experience in many different ways. We want to dedicate this section to the people who helped and supported us throughout it. First of all we wish to express our sincere appreciation of our supervisor Liang Liu from the department of Electrical and Information Technology who has supported and guided us throughout the entire process. The technical guidance and support from our company supervisor Kevin Cushon has been crucial for the thesis to succeed and for ensuring the use of forensic methods, and for that we express our deepest gratitude. We also want to thank Sacki Agelis for the administrative- and general support that has been crucial for the process and completion of this thesis. We also want to express our thanks to Ericsson and the department of Electrical and Information Technology at LTH for the opportunity to execute on this thesis. At last we want to express our sincere appreciation to our families and friends who has supported us.

## Acronyms

| ASIC<br>BRAM<br>CCY<br>CFG<br>CLK<br>CROM<br>CPU<br>DSP<br>FF<br>FFT<br>FFT<br>FPGA<br>FT<br>HDL<br>Hz<br>HLS<br>I/O<br>$X_i$<br>IP<br>LUT<br>MSB<br>MUX<br>N/A<br>NCO<br>PWM<br>$X_r$<br>RAM<br>RMS<br>ROM<br>RTL | Application Specific Integrated Circuit<br>Block Random Access Memory<br>Clock Cycle<br>Control Flow Graph<br>Clock<br>Cosine ROM<br>Central Processing Unit<br>Digital Signal Processing<br>Flip-Flop<br>Fast Fourier Transform<br>Field Programmable Gate Array<br>Frequency Translator<br>Hardware Description Language<br>Hertz<br>High Level Synthesis<br>Inputs and Outputs<br>$X_{imaginary}$<br>Intellectual Property<br>Look-Up Table<br>Most Significant Bit<br>Multiplexer<br>Not Applicable/Available, No Answer<br>Numerically Controlled Oscillator<br>Power Meter<br>$X_{real}$<br>Random Access Memory<br>Root Mean Square<br>Read Only Memory<br>Register Transfer Level |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTL<br>SROM<br>UVM<br>VHDL (VHSIC-HDL)<br>VIO                                                                                                                                                                      | Register Transfer Level<br>Sine ROM<br>Universal Verification Methodology<br>Very High Speed Integrated Circuit HDL<br>Virtual Input Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| XOR                                                                                                                                                                                                                | eXclusive OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## Table of Contents

| 1 | Intro | oduction                                  | . 1  |

|---|-------|-------------------------------------------|------|

|   | 1.1   | Thesis Structure                          | 3    |

| 2 | Bac   | kground                                   | 5    |

|   | 2.1   | Motivation                                | 5    |

|   | 2.2   | FPGA Fabric                               | 7    |

|   | 2.3   | Abstraction Levels and Design Hierarchies | 8    |

|   | 2.4   | Hardware Optimization and Structure       | 9    |

| 3 | Wor   | kflow and Xilinx Vivado HLS               | 13   |

|   | 3.1   | Xilinx Vivado HLS                         | 13   |

|   | 3.2   | Design and Verification Workflow          | 15   |

| 4 | Case  | e studies                                 | 21   |

|   | 4.1   | Modules                                   | 21   |

|   | 4.2   | General Design Specifications             | 26   |

| 5 | Res   | ults                                      | 29   |

|   | 5.1   | HLS- versus HDL-Synthesis                 | 30   |

|   | 5.2   | Synthesis- and Simulation Times           | 30   |

|   | 5.3   | Timing Results                            | 33   |

|   | 5.4   | Hardware Mapping and Area Consumption     | 34   |

| 6 | Ana   | lysis                                     | 47   |

|   | 6.1   | Simulation- and Synthesis Times           | 47   |

|   | 6.2   | Area Consumption and Hardware Mapping     | 50   |

|   | 6.3   | Aspects of Designing Which Affect Timing  | 54   |

|   | 6.4   | Changes in Workflow from HDL to HLS       | 57   |

| 7 | Con   | clusions                                  | . 59 |

|   | 7.1   | Synthesis- and Simulation Times           | 59   |

|   | 7.2   | Hardware Utilization                      | 60   |

|   | 7.3   | Timing                                    | 61   |

|   | 7.4   | Workflow                                  | 62   |

|    |       | Future work                           |    |

|----|-------|---------------------------------------|----|

| Re | feren | ces                                   | 65 |

| Α  | Sche  | ematic of Power Meter Implementations | 67 |

| в  | Exar  | nple of Abstraction Levels            | 71 |

## List of Figures

| 2.1 | Design hierarchy levels used in this thesis component (left) and system        |    |

|-----|--------------------------------------------------------------------------------|----|

|     | (right)                                                                        | 8  |

| 2.2 | Dataflow graph example with no pipelineing.                                    | 10 |

| 2.3 | Dataflow graph example with pipelineing                                        | 10 |

| 2.4 | Example of software loop that could be unrolled                                | 11 |

| 2.5 | Hardware implementation of loop before unrolling                               | 11 |

| 2.6 | Hardware implementation of loop after unrolling                                | 11 |

| 3.1 | Description of the HDL workflow used in this thesis                            | 16 |

| 3.2 | Description of the HLS workflow used in this thesis.                           | 17 |

| 3.3 | Verification levels                                                            | 19 |

| 4.1 | Block-Diagram for an overview of the frequency translator.                     | 21 |

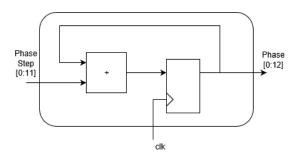

| 4.2 | Schematic picture of the accumulators function.                                | 22 |

| 4.3 | Description of the accumulator circuit used for calculating the next           |    |

|     | phase value                                                                    | 23 |

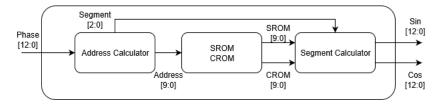

| 4.4 | Block-Diagram overview of the cos-/sin Generator                               | 23 |

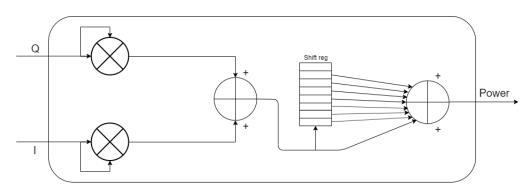

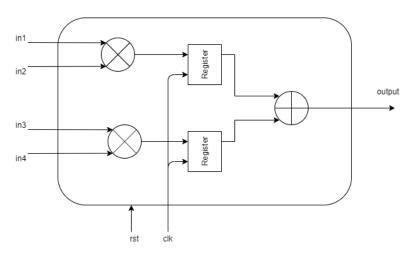

| 4.5 | Block-Diagram overview of the power meter                                      | 25 |

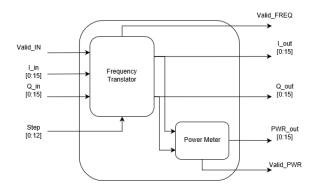

| 4.6 | Block-Diagram overview of the top module                                       | 25 |

| 4.7 | The large system design used to test long simulations                          | 26 |

| 5.1 | Plot of how the HLS-Synthesis time changes with the number of com-             |    |

|     | ponents                                                                        | 33 |

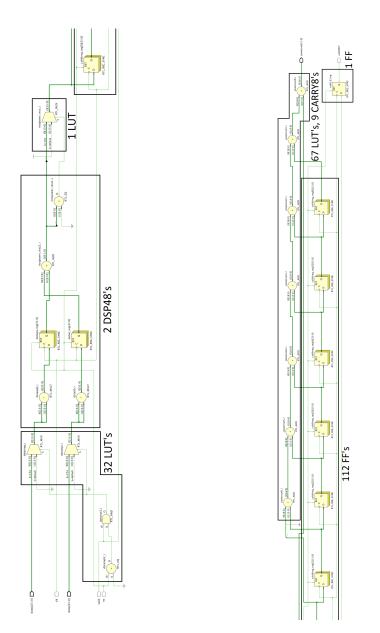

| 5.2 | RTL Analysis of the VHDL Accumulator implementation.                           | 35 |

| 5.3 | Functional RTL Analysis of the VHDL model for Cosine & Sine Cal-<br>culations. | 36 |

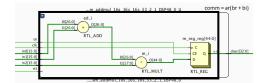

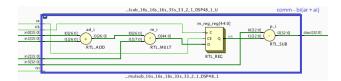

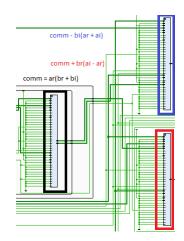

| 5.4 | Functional RTL-Analysis of the common factor calculation.                      | 36 |

| 5.5 | Functional RTL-Analysis of the complex multiplication for the imagi-           |    |

|     | nary output.                                                                   | 36 |

| 5.6 | Functional RTL-Analysis of the complex multiplication for the real output.     | 36 |

| 5.7 | Three DSP48-Slice implementation representing the architecture used            |    |

|     | for all implementations.                                                       | 37 |

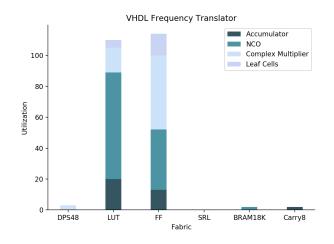

| 5.8  | Bar chart showing the number of components for the VHDL imple-<br>mentation of the frequency translator.      | 38 |

|------|---------------------------------------------------------------------------------------------------------------|----|

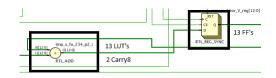

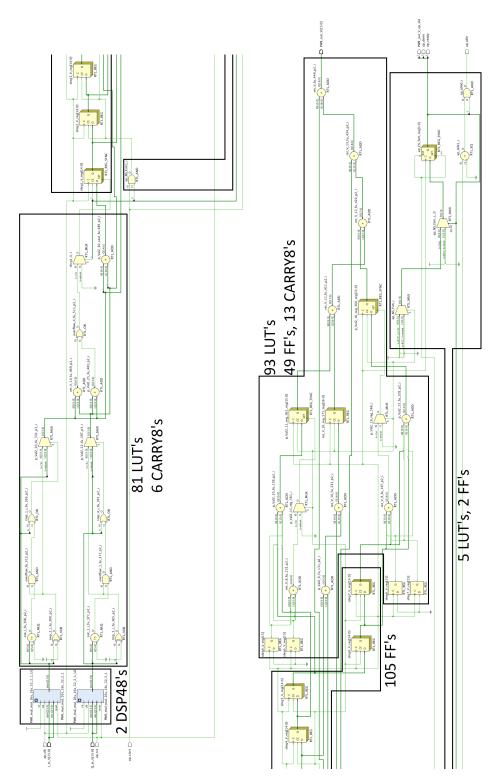

| 5.9  | RTL Analysis of the BE Accumulator implementation.                                                            | 38 |

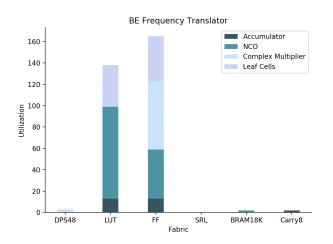

| 5.10 | Bar chart showing the number of components for the bit-exact imple-<br>mentation of the frequency translator. | 39 |

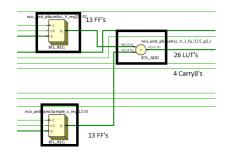

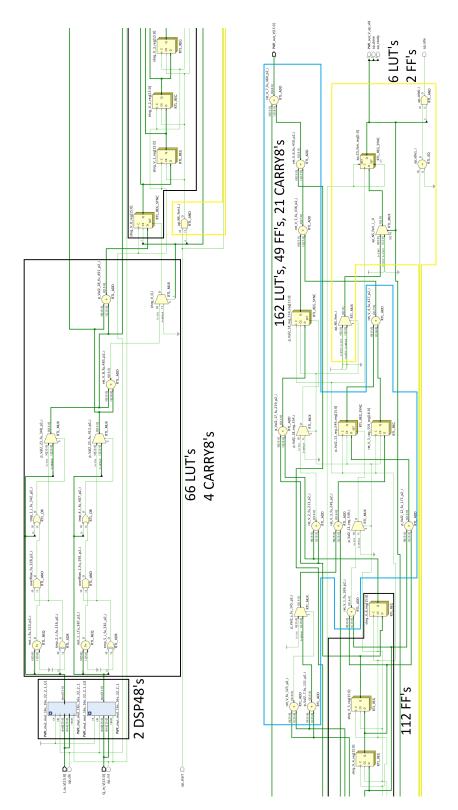

| 5.11 | RTL Analysis of the Ultra High Level Accumulator implementation.                                              | 40 |

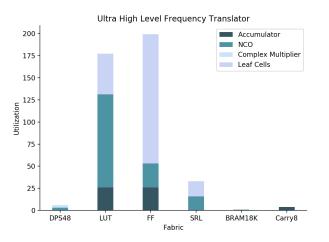

| 5.12 | Bar chart showing the number of components for the ultra high level                                           |    |

|      | implementation of the frequency translator                                                                    | 41 |

| 5.13 | The common multiplier block used in both HLS designs                                                          | 42 |

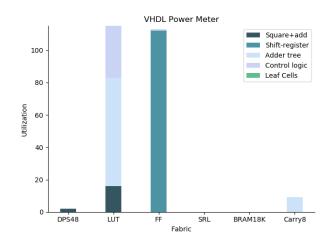

| 5.14 | Bar chart showing the number of components for the VHDL imple-                                                |    |

|      | mentation of the Power meter                                                                                  | 42 |

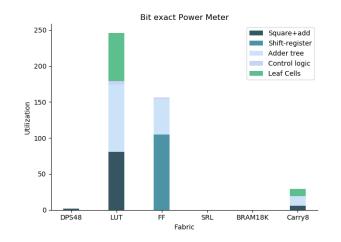

| 5.15 | Bar chart showing the number of components for the Bit-exact HLS implementation of the Power meter.           | 44 |

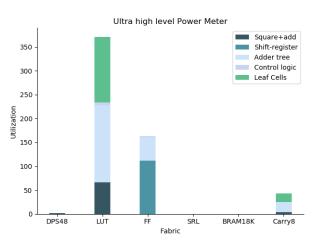

| 5.16 | Bar chart showing the number of components for the ultra high level HLS implementation of the Power meter.    | 45 |

| 6.1  | Cast to unsigned                                                                                              | 54 |

| 6.2  | Syntax for writing an adder-tree                                                                              | 56 |

| 6.3  | Example code showing how static variables could be shared                                                     | 56 |

| 6.4  | Example code showing how to avoid static variables sharing                                                    | 56 |

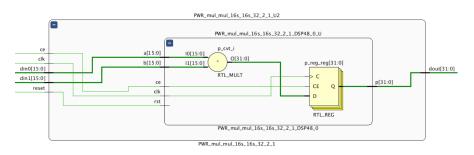

| A.1  | Block diagram for VHDL design of the power meter                                                              | 68 |

| A.2  | Block diagram for bit-exact HLS design of the power meter                                                     | 69 |

| A.3  | Block diagram for TLM HLS design of the power meter                                                           | 70 |

| B.1  | Example component for abstraction level example                                                               | 71 |

| B.2  | Example component implemented using VHDL                                                                      | 72 |

| B.3  | Example component implemented using HLS                                                                       | 72 |

### List of Tables

| 4.1  | Truth table for address and value representation depending on the segment address.                                              | 23 |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | Design specification                                                                                                            | 26 |

| 5.1  | Result-matrix of the comparison between the HLS-synthesis and the HDL-synthesis.                                                | 30 |

| 5.2  | Result-matrix of the comparison between CPU time of the simulation and build times of the frequency translator, format hh:mm:ss | 31 |

| 5.3  | Result-matrix of the comparison between CPU time of the simulation and build times of the power meter                           | 31 |

| 5.4  | Result-matrix of the comparison between CPU time of the simulation and build times of the big design                            | 32 |

| 5.5  | Result-matrix of the timing results for the frequency translator                                                                | 33 |

| 5.6  | Result-matrix of the timing results for the power meter.                                                                        | 34 |

| 5.7  | Result-matrix of the timing results for the large system                                                                        | 34 |

| 5.8  | Result-matrix of the Number of components used for the different                                                                |    |

|      | abstraction levels of the frequency translator                                                                                  | 35 |

| 5.9  | Detailed result-matrix for the VHDL Frequency translator showing the number of components.                                      | 37 |

| 5.10 | Detailed result-matrix for the bit-exact Frequency translator showing                                                           | 01 |

| 0.20 | the number of components.                                                                                                       | 39 |

| 5.11 | Detailed Result-matrix for the ultra high level frequency translator                                                            |    |

| - 10 | showing the number of components.                                                                                               | 40 |

| 5.12 | Result-matrix of the area consumption of the power meter for all three abstraction levels.                                      | 41 |

| 5 13 | Detailed result-matrix for the VHDL power meter showing the number                                                              | 71 |

| 5.15 | of components.                                                                                                                  | 42 |

| 5.14 | Detailed result-matrix for the Bit-exact HLS power meter showing the                                                            | 12 |

|      | number of components.                                                                                                           | 43 |

| 5.15 | Detailed result-matrix for the ultra high level HLS power meter show-                                                           |    |

|      | ing the number of components.                                                                                                   | 44 |

| 5.16 | ••••                                                                                                                            |    |

|      | components.                                                                                                                     | 46 |

### \_\_\_\_ <sub>Chapter</sub> L Introduction

Automation of industries could be argued, together with IT, as one of the biggest drivers of the modern economy. Automation could simply be put as the aim to complete a given task with as little human interaction as possible. Achieving this has several benefits' perhaps the most sought after would be to free up human attention and effort from more mundane tasks to work on innovation and progress. The word automation could refer to many different areas and implementations. It could refer to anything as simple as software program performing a set sequence of tasks on a computers file system to advanced mechatronic implementations in modern manufacturing processes.

The potential gains of automation are large but while there are many gains of automation it too has its downsides. The lack of contextual understanding that machines or tools, posses could affect the result of the task it is to perform in a negative way. Where the lacking of contextual awareness yield a sub-optimal result the automation process require more sophistication. Generally where understanding why something is performed would increase the quality of the result by adapting to the specific circumstances of the specific task at hand. In such a case the progress of automation could be staggered. To surpass this problem most commonly the context of the problem at hand needs to be integrated into the automation process. Regarding simple and isolated tasks this is possible. As for more complex tasks integrating all possible outcomes and context becomes almost impossible which would yield in worse performance for some situations.

The gain in execution speed and versus the loss of contextual awareness is perhaps the most common dilemma one would face when when deciding if automation is the right course of action. The maturity of the automation process do often weigh heavy in these cases. Introducing a new way of working should yield in a more efficient way of working then what it previously was. Automation affects almost all industries including digital hardware design. The most common way to design digital hardware would be with *Register Trans-fer Level*- (RTL) coding, that is describing digital hardware through code on a cycle- and bit accurate level. This was introduced with HDL-Synthesis in the mid 1980s [5]. HDL-Synthesis [5] tools aimed to take an RTL design and transfer it to a gate-level ASIC netlist consisting of logical gates. In doing so it automated the process of digital hardware design from the placement of logical gates and transistors to designing it in RTL-code.

The next step of abstraction for digital hardware design could be *High Level Synthesis*, or *HLS*. Which is a way of designing hardware by using the same coding syntax that is normally used for software design. HLS is an attempt to automate parts of the hardware design process by increasing the abstraction level from the traditional ways of designing hardware using RTL to designing hardware by describing its functionality in classical software syntax.

This thesis is aimed to be an analysis of HLS. The analysis will be done using Vivado HLS 2018.3. A development environment from Xilinx which uses C-, C++or System C syntax to design hardware. The hardware results presented in this thesis is not guaranteed to be repeatable using any other tool or target hardware. But the methodologies used when working with Vivado HLS could be applicable when working with other HLS vendor tools. This should be achieved by giving an insight into working with HLS, what the benefits and drawbacks there are and how they can be leveraged to fit into different situations.

HLS has the potential to bridge the knowledge gap to hardware design, pushing design up on a system level requiring only software, or less hardware, knowledge. To do this the tool needs to prove sufficient performance that it can, in a trusted manner, produce hardware as good, or better, than with RTL. If this is not the case the tool needs to provide additional benefits, not existing with RTL, that can make up for the loss of performance. By analysing the state of Vivado HLS this thesis hopes to show the state of the tool but also HLS in general.

The analysis will be conducted by creating a digital hardware design in RTL and then the design should then be recreated using HLS. The HLS designs will be divided into two designs. One design should mimic the RTL-codes functionality and behaviour by coding as close to bit and cycle accurate as possible using C++. This design aims to recreate the RTL design but using the HLS tool. The other HLS design aims to maximize abstraction by using provided libraries with a more software approach to designing.

Designing with HLS can produce hardware with results much resembling those generated using RTL-coding. If the goal is to design high performance hardware in terms of area and timing, the logic functionality and hardware should be determined before the design is done in HLS. The C/C++ syntax should then be written so that the functionality resembles the goal design. This pushes the tool to generate hardware using the same logic and timing as to goal design. HLS could

also generate hardware using normal software syntax with the right settings. Designing using normal software syntax in general produces digital hardware that consumes more logic with worse timing results. HLS is sensitive to syntax and using pre-defined libraries makes it easier for the tool to synthesize the hardware but it can also decrease the performance when simulating in C.

It should be noted that qualities of designs is heavily dependent on the designer and the experience they posses. Before this thesis neither of the authors has done any previous work using HLS and their experience with RTL is restricted to academics only.

### 1.1 Thesis Structure

This thesis aims to compare the results produced as well as the workflow of Vivado to that of RTL when designing digital hardware aimed for FPGAs. It should also provide guidelines for people designing in HLS with an analysis of how the tool performs in different scenarios. Even if the design and practical work is done using Vivado HLS methodologies and workflow practices used throughout this thesis should be applicable, to some extent, if one should choose to design in HLS using different tools.

This thesis will be structured into six different parts, excluding the introduction.

- 1. Background This chapter aims to explain why and what that was conducted throughout this thesis. It will also cover some basic digital hardware concepts the reader should be familiar with to understand the results and analysis. It will also give a brief introduction to RTL design concepts and how it was conducted throughout this thesis.

- 2. Xilinx Vivado HLS This chapter should serve as an general introduction to HLS, more specifically to Vivado HLS. The aim is to get the reader familiarized with HLS design concepts and also how the differ as well as connects to digital design using RTL.

- 3. Case Study Is about the hardware components, or designs, used throughout this thesis. Their specifications and an overview of their functionality will be presented as well as how they are intended to be used to analyse and test the Vivado HLS tool.

- 4. Results In this chapter the quantifiable results are presented. It presents graphs and tables of the different designs implementations as well as the results of the design process it self. It aims to only present quantifiable and measurable results for the reader to extract.

- 5. Analysis Aims to present the reader with a more in depth analysis of the results. Why the designs ended up the way they did and how they differ from each other. It will also bring up problems and hurdles one could face when designing hardware using HLS and how these could be prevented or solved.

6. Conclusions - Should conclude the thesis results and analysis with a concise description of HLS and its current state. In this chapter the authors opinions and experiences will be presented. These are not to be taken as facts but the opinions of two master students using HLS for digital hardware design for the first time.

The thesis is aimed at Vivado HLS and how it can be used for hardware design with measurable results as the main resource of analysis. Throughout the thesis the impact HLS might have on workflow methodologies in different parts of digital hardware design will be covered. Even so it is important as a reader to keep in mind that this is not an evaluation of methodologies used when designing hardware but the hardware produced as a result. The methodologies are brought up because they present one of the differences, and potential gains, when designing digital hardware in HLS compared to RTL.

## \_\_\_\_ <sub>Chapter</sub> 2 Background

To follow along in this thesis a basic knowledge of hardware design, how it is done and what's the reason behind it, is recommended. Even so the following chapter will briefly cover the methods, concepts and theory used throughout this thesis. The content of this chapter should be kept in mind when reading the rest of this thesis, which will hopefully explain the reasoning and decisions made throughout this work.

### 2.1 Motivation

Hardware development is in many aspects costly and resource demanding. Due to modern tools requiring a lot of detail to create functionality the design aspects can take a lot of time, get large and slow down development. Developing using HLS has the potential to allow the focus to be shifted from a bit-wise design to a more modular design approach. Which has the potential to reduce the development time and speed up the time to market for hardware and IP:s if it can reach sufficient performance compared to the tools used today. Other than design speed, HLS has the potential to speed up verification by moving it from an RTL environment to system-C/C. This could speed up the verification process significantly since the entire RTL model does not have to be simulated in order to do a functional verification.

High Level Synthesis tools have several potential benefits that could speed up the design of hardware. They include:

- Higher abstraction level for easier design

- Faster design verification from higher level simulation

While High Level Synthesis has several potential benefits for both hardware design and verification, it also presents potential drawbacks. By increasing the abstraction level the designer gives up control of design aspects that modern HDL tools provide. This could potentially lead to different types of implementation problems where design architectures are not as efficiently, in terms of area and timing of the circuit, implemented as they could be had the designer been given more control. To evaluate the performance of Vivado HLS this thesis aims to use three different approaches.

- Basic RTL design using VHDL

- C++ design using an bit exact coding approach

- C++ design using a "Ultra High Level" -style of coding

These design ways do represent three abstraction levels of coding, ranking from lowest to highest in the list. A higher level of abstraction would generally be seen as better from a design speed perspective, but with a lower level of customization and performance.

Exploring different abstraction levels when designing could provide important insight to how well the tool performs in different scenarios. Even though a higher abstraction level would make hardware design more accessible. An approach to hardware design using C/C++ while having a goal implementation in mind, in terms of hardware as well as functionality, could have potential benefits of efficient hardware- and DSP design together with the design speed potential of software.

Through out this thesis the quality and efficiency of the hardware produced by different design methods, using high level synthesis and VHDL, will be analysed to determine how well they work. For each level of abstraction the design will be evaluated on the following parameters.

- Area

- Speed

- Time for Synthesis

- Simulation Time

This should provide a better view of the current state of the tool and what tradeoffs that is being made when used in comparison to traditional RTL design using Verilog or VHDL.

### 2.2 FPGA Fabric

To understand the measurement of area efficiency, which is a very important indicator of the quality of the generated hardware, it is important to understand the basics of how hardware is mapped onto the FPGA. The target FPGA circuit for this thesis is the Xilinx Zync Ultrascale ZU27DR [9]. The FPGA holds a set of standard building blocks and programmable interconnections to design different logic implementations. The three basic building blocks discussed throughout this thesis are:

- DSP48 The DPS48 slice in the Ultrascale architecture is the main slice for multiplication. The DSP contains a multiplier, adders, a multi-purpose ALU, and pipeline registers. By default multiplications are mapped to the DPS-slice, if possible the multiplication can be combined with other basic arithmetic operations [1].

- Block RAM RAM's with programmable width and depth. Block RAM usually used for storing large amount of data such as comprehensive look up tables and large registers, data which would only need to be partly updated or accessed. This ultrascale+ arcitecture feature 38 Mb of block RAM [3].

- CLB Is the main resource to implement general-purpose sequential- and combinational circuits on and FPGA [2]. It holds several blocks of hardware functionalities such as *Look-up Tables*(LUT), *Shift Register Logic*(SRL), *Flip Flops*(FF) and *High Speed Carry Logic*(Carry8) to implement logic and arithmetic operations. All this logic is contained within one CLB '*slice*', which then has several interconnects to other CLB-slices as well as other parts of the fabric to create the FPGA-architecture.

These are the standard FPGA fabric components used to build up different hardware logic and will be used in order to measure the area efficiency of Vivado HLS. The number of logic blocks used in a design matters also for timing reasons. If the logic needs more LUT's or FF's it could effect the timings of the circuit. The reason why it could affect timing is that if the design does not fit in CLB some of it might have to be spread over several CLB's were communication delay for the signal to travel to the next CLB can affect timing in a negative manner. The routing of the FPGA fabric allows for easier communication within a block than between several of them because there can not always be an available CLB close and a longer communication route may therefore have to be taken. Inefficient usage of the block RAM- or DSP- fabric could be even worse than CLB mapping, since the placement of these are less frequent on the FPGA-board and there are a limited number of them. If something does not map to a RAM or DSP, it might have to be built from CLB's leading to a increase in utilization for RAM case. In the DSP case it will mainly be the timing that will be affected, since DSP are rather complex and developed to be efficient at their capabilities it will require a high number of CLB's to perform this, see [1] and [16].

Different FPGA manufacturers has different fabric architectures and building blocks. Thus the same design might have different utilization depending on the FPGA provider. During this thesis Xilinx Vivado HLS is used to program a Xilinx FPGA. This could cause a biased view and different result might be obtained if using FPGA-boards from different vendors, due to inefficient mapping and other mismatches.

It is important to understand these basic FPGA architecture blocks to understand the analysis of the area efficiency. Because of the structure of filed programmable gate arrays the number of blocks, or slices, used to implement the hardware functionality will determine how area efficient the final design is. The number of slices used is also affected on how the hardware algorithm is optimized and implemented but these are kept constant as much as possible through out this thesis.

### 2.3 Abstraction Levels and Design Hierarchies

This section should briefly clarify some terms used throughout this thesis. It is mainly to those how are not as familiar with digital hardware design and the different terms one usually uses to describe components of a design. The section also covers briefly what *abstraction levels* are referring to which is used frequently throughout this thesis to describe the design methods.

### 2.3.1 Design Hierarchies

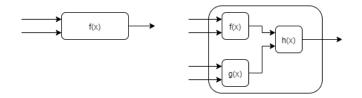

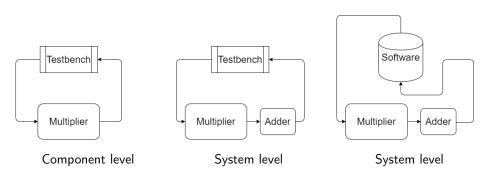

The digital designs used in this project can be divided into two parts, top-module or system level and sub-module or component. An example of these can be seen in figure 2.1 where the left is a component usually performing a function or arithmetic operation with a set of I/Os. The right part of figure 2.1 is the system level or the top-module used to describe how different components are connected as well as the top level inputs and outputs.

**Figure 2.1:** Design hierarchy levels used in this thesis component (left) and system (right).

It should be noted that functionality can be divided into several sub-modules, or components. How this division is done is decided by the designer.

### 2.3.2 Abstraction Levels

Abstraction levels are used to describe the different ways of designing hardware that was used throughout this thesis. Where the lower abstraction levels are designs where the functionality and logical hardware are more meticulously expressed. Higher abstraction levels indicates a reduction of the level of detail required, leaving the left out details to be performed by the tool. An example of the abstraction levels can be seen in appendix B.

To compare the HLS implementations with the RTL implementations three abstraction levels will be used. *VHDL* is the abstraction level closest to hardware. *VHDL* is design on a logic level and after HDL-synthesis it is converted to a netlist. The netlist is mapped onto physical hardware units which will be used to measure the utilization efficiency of HLS. The *VHDL* model will be used as the baseline performance measurement as it is a form of RTL design which is one of the most common ways to design hardware today.

The HLS implementations will be divided into two abstraction levels, *Bit-Exact* and *Ultra High Level*. The goal of the *bit-exact* model is recreate the hardware described in this chapter and to recreate or surpass, if possible, the VHDL design using HLS. Using syntax that both in timing and functionality is intended to force the HLS-synthesis to create RTL that function and maps to hardware as the VHDL design does. This should be achieved by coding as close to clock- and bit accurate as possible.

The Ultra High Level model goal is to demonstrate the performance of a design using higher abstraction level style of coding. In this case higher abstraction level is achieved by using libraries, syntax and arithmetic operations as one would in classic software design. It should be noted that the syntax is altered in a way so that it generates functional hardware and uses directives to improve HLS-synthesis result so that the design meets the initial requirements, see section 4.2.

### 2.4 Hardware Optimization and Structure

In digital hardware design there are several different optimization methods that could be utilized in order to increase the performance of a circuit. Throughout this thesis some of this optimizations will be implemented to meet specific hardware requirements. Therefore this section of the report aims to present some of these optimization methods, why they are used and how they affect the circuit they are applied to. A brief introduction to hardware hierarchy is also presented in this section. Even though the hierarchy is not a optimization method by itself it is important to understand the basic concept to fully grasp the results presented later in the report.

### 2.4.1 Pipelineing

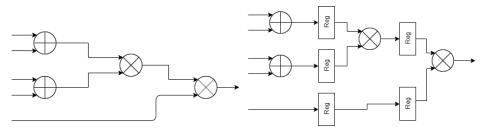

Pipelineing is the insertion of registers at strategic places in a circuit to divide its functionality over as many clock cycles as the number of inserted registers [12]. As an example of this see figure 2.2 showing a made up datapath and figure 2.3 showing the same datapath with inserted registers. If in this dataflow graph representation of a fictitious circuit uses addition that requires two nanoseconds to complete and multiplication that requires four nanoseconds the circuit in figure 2.2 would take ten nanoseconds in total to complete. Which would require the datapath to have a clock cycle with at least a ten nanosecond period, if register setup and hold times are discarded. One way of pipelineing the datapath can be seen in figure 2.3 where, if once again register setup and hold times are discarded, a clock period of four nanoseconds would be possible. With the use of pipelineing the clock period were decreased which is one of the main advantages of this optimization method. Introducing pipeline stages in the datapath has one other advantage. It exploits hardware parallelism, meaning that the next operation in the datapath show in figure 2.3 can start after one clock cycle. Effectively allowing the hardware to have three active calculations in parallel which allows the circuit to produce one result every fourth nanosecond instead of every tenth. One should also note that in this case the total execution time increases from ten nanoseconds to twelve because the additions execute during one clock cycle even if it is finished before increasing the time compared to the non-pipeliened version of the datapath. This example summarises the main pros, clock speed and parallelism, and cons, increased hardware and possible longer execution time, of pipelineing a circuit.

Figure 2.2: Dataflow graph example with no pipelineing.

Figure 2.3: Dataflow graph example with pipelineing.

### 2.4.2 Loop Unrolling

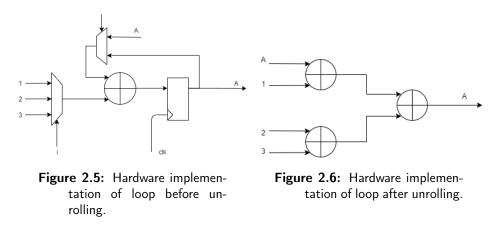

Unrolling is an optimization method to reduce the number of clock cycles required to implement a iterative algorithm. Unrolling is done by performing several iterations each cycle, or if the loop is completely unrolled all iterations are performed in parallel [12]. An example of a loop that could be unrolled can be seen in figure 2.4. This loop could be implemented using a single adder which looks like figure 2.5 calculating one addition per cycle. By unrolling this loop the resulting hardware could look like that of figure 2.6

Figure 2.4: Example of software loop that could be unrolled.

The normal benefits of unrolling is a lower latency circuit that has to utilize more hardware to perform its calculations.

## \_\_\_\_ Chapter 3

### Workflow and Xilinx Vivado HLS

This chapter will introduce Vivado HLS to the reader and give basic knowledge of the tool. Presenting briefly how the tool works and the process of generating RTL from C/C++. It also aims to present the workflow used in this thesis, both for the RTL- and HLS design and verification. Understanding the workflow and how it changes when designing in HLS compared to RTL is an important aspect to consider when evaluating the tools because the workflow can affect the designand verification process and their speed.

### 3.1 Xilinx Vivado HLS

The tool used to design HLS throughout this thesis was Xilinx Vivado HLS and the tool used to do RTL design was Xilinx Vivado. The most significant difference between the two, that Vivado HLS is using C - or C++ code and Vivado using HDL code. It is assumed that the reader has some experience or previous knowledge of designing hardware using HDL and this thesis will not cover that in any detail.

### 3.1.1 HLS-Synthesis

High Level Synthesis is used to generate functional RTL from C/C++ source code. The synthesis itself is when the source code is interpreted and used to generate functional RTL. This process of generating RTL-code will throughout this thesis be referred to as *HLS-Synthesis* to differentiate it from HDL-Synthesis which is used to generate a netlist from RTL-code [5].

The synthesis process is the critical factor that enables HLS to be used for hardware design. The synthesis process could be described briefly in three parts. First the tool identifies key parts of the code. There are usually six attributes of the code that the tool has to identify, *Functions*, *Top Level I/O*, *Types*, *Loops*, *Arrays* and *Operators* [8]. These part all needs to be handled to correctly to synthesize the C/C++ code. Second the tool has to identify the control parts of the C-code. This is usually the start and end of a function call or internal loops. Using these sequences the tool creates a CFG to determine the order of operations. The tool then identifies the different operators used in the code and they are then placed within the different parts of the *Control Flow Graph* (CFG) [8] so that they are performed in the correct order. Using this CFG with the different operators integrated the tool can then structure RTL to replicate the C functionality in hardware. Third the tool has to schedule which operations that should be performed on which clock cycle.

The structure of the CFG and its internal operators can be changed using directives, or C-pragmas [8]. This could tell the tool to implement different hardware optimization options, such as unrolling a loop (see section 2.4.2) for lower latency or pipelineing (see section 2.4.1) a function to increase the throughput of the hardware.

### 3.1.2 Customisation, Optimization and Constraints

Vivado HLS has several features and options to optimize and customize the hardware design implementation [8]. Note that all of them wont be covered in this thesis but this section aims to present the ones that one needs to know to understand the thesis results and analysis.

#### Arbitrary Precision

Arbitrary precision data types are provided from a Vivado HLS library. They are used in Vivado HLS for doing bit exact models and calculations. Assigning a variable to be of arbitrary precision type allows for more exact design beyond the standard C/C++ data types [14]. The arbitrary data types can be of  $ab_fixed < WL$ , N > or  $ab_ufixed < WL$ , N > where the data type can be set with word length, WL, and integer length, N, to create a fixed-point or unsigned fixed-point implementation. The arbitrary precision data types  $ab_int < N >$  and  $ab_uint < N >$  which will create a N-bit integer number [8].

#### Directives or Pragmas

By default the key attributes from the HLS-Synthesis are synthesised in standard ways. An array is for example by default synthesised as a BRAM [8]. How the tool should synthesise the source code could be modified with pragmas or directives. This allows the designer to perform different optimization methods by telling the tool specifically how a part of the code should be synthesised, or mapped to hardware. The directives mostly commonly used throughout this project are *Pipeline*, *Unroll*, *Array Mapping*. Pipeline has been explained in section 2.4.1 and are applied to functions to tell the tool that all the operations in that function should be pipelined. Unroll has been explained in 2.4.2 and is applied to loops to reduce the loop-iterations. Array mapping is used to change how an array is synthesised in HLS. This was often used to force the tool to synthesise arrays into registers instead of BRAM. For a full explanation of which directives there are and how they should applied we refer to the Vivado HLS user guide [8].

#### Constraints

A constraint when writing HLS is that memories has to be defined on compile time, i.e. you can't use memories with dynamic range, since it is not possible to synthesise a memory of unknown size. Therefore one cannot use pointers with offsets to access values. Normal C/C++ code would most likely contain a pointer to an array index then with the use of offset different values can be accessed. This is not the case in HLS where pointers are allowed but arrays has to be statically defined at compile time in some part of the code in order for the code to pass synthesis.

### 3.2 Design and Verification Workflow

To evaluate the HLS effect on design and verification it's important to have a good overview of the work flow when designing in HLS and in VHDL. In this chapter the design methodology used for this thesis is presented first and why it was chosen. Then a version of a VHDL workflow is presented, as a starting point, to be compared with the recommended HLS workflow. In the end of this chapter the differences will be compared and the possible impact these might have will be discussed.

### 3.2.1 Design

Hardware design-flow is usually done in one of two ways, using a top-down- or bottom-up design methodology. The bottom-up methodology is used because it was regarded as a preferable methodology when working with HLS design. In a bottom-up methodology the system functionality is divided up in smaller blocks which are designed separately first and then connected afterwards using a predefined interface.

There are especially two advantages of this design methodology. First the bottomup methodology will allow the designer to evaluate the performance of each individual block by itself, thus knowing its limitation before it's implemented inside the entire system, or top model. This will make it easier for the designer to know what performance limitations that are existing before the top model implementation is done.

Secondly the saturation of *Moore's Law* [10] causes higher frequencies to cost more to achieve, which in turn is pushing the development towards more parallel, or multi-core, computing. This would be better utilized by running the synthesis of several design blocks in parallel instead of in one single core.

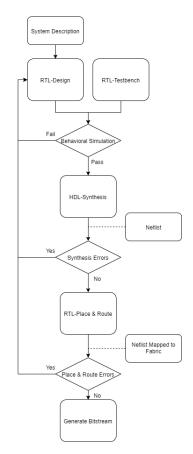

### VHDL

The RTL workflow used in this thesis starts with a system description, overall and for each individual part. Using the system description a RTL-design and a RTLtestbench are designed using VHDL. The two designs are then used for behavioral simulation to verify that the design is logically correct. If the design does not perform as expected the design has to be modified and the behavioral simulation re-run until the design works correctly. If the design functions as expected in the behavioral synthesis it goes through HDL-synthesis to generate a netlist. During synthesis the design is tested for timing errors and latches [15]. Should these test fail one has to redo the RTL-design once again. If the HDL-synthesis passes it generates a functional netlist that can be used in Place and Route where the design is mapped to a FPGA circuit. Should this fail one has to go back to the RTLdesign step, if it passes a bit-stream to program the hardware onto the FPGA can be generated. An overview of the HDL workflow can be seen in figure 3.1.

Figure 3.1: Description of the HDL workflow used in this thesis.

#### Vivado HLS

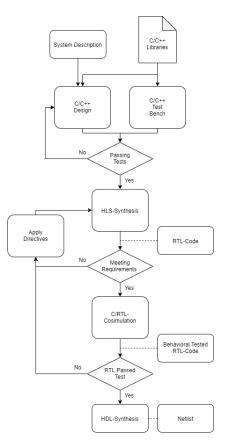

Designing in HLS starts with the system description of the design which describes the goal functionality. The system description is then used, together with existing software libraries, to create a system design and testbench in C or C++. Running the testbench as a main function the functionality of design is verified. Should it not pass changes have to be made to the design, if it passes it can go through HLS-synthesis. HLS-synthesis generates RTL-code and provides an estimate of the hardware performance, timing and utilization. If the performance estimate are not good enough, directives [8] can be applied to improve them and change the hardware. In the worst case the C design has to be changed to improve the estimates. Once the estimates are good enough C/RTL-Cosimulation is performed, which verifies the RTL with the same testbench. Should the C/RTL-Cosimulation fail the directives or C design has to be altered to solve it. Once C/RTL-Cosimulation passes the design RTL can be exported to go through the flow of figure 3.1. The difference here is that the functional verification of the RTL is automated and done with a testbench written in C/C++. An overview of the HLS-workflow can be seen in figure 3.2.

Figure 3.2: Description of the HLS workflow used in this thesis.

### 3.2.2 Verification

In this section of the report the verification process used throughout this thesis is presented. Verification could differ between different industries and even between different projects therefore the verification method, specification and process used are presented in this section. This should give some understanding of how verification could be performed and aims to improve the understanding of the verification results and analysis.

Verification is an integral part of hardware design. Before hardware can be sent into production or to be put in commercial use comprehensive testing has to be done in order to ensure design functionality and rated performance. The verification process is designed to emulate, even if limited, the process used in modern industry. It has to be noted that due to the time limiting factor of this thesis more advanced verification methods, which is a industry standard, for testing integrated circuits such as UVM [13] could not be used to test verification with HLS.

The metric used for evaluating verification is the simulation time for designs. These times will give a quantitative measurement on the time reduction when simulating functionality on a higher abstraction level in C/C++ versus RTL-simulation. This will be done by simulating for both smaller design on an IP-level as well as on a larger system level. The goal is to describe the verification processes and measure time differences to show how verification could change, for better or worse, with HLS.

To analyse the verification performance of HLS the main focus is the verification time i.e. how fast can the circuit be simulated and the logic functionality verified compared to traditional hardware design verification in HDL. This is of high relevance to industrial companies since larger hardware designs often contains large quantities of logic thus use up large areas on FPGA fabric and takes longer time to simulate.

#### Verification Flow

Verification for the traditional hardware design languages, VHDL or Verilog, are usually done on three levels which are listed below and shown in figure 3.3.

- 1. Component Level where each component or block is tested individually.

- 2. Verify System Level functionality with a mathematical model emulating the desired functionality of the implemented RTL design.

- 3. Advanced software from Xilinx, or similar vendors, which is used to toggle all switches and explore all branches in the given design.

Figure 3.3: Verification levels

The verification in HLS is conducted with the same methodology as described in figure 3.3. The difference is that the testbench and design are written in C/C++. The top of figure 3.1 and 3.2 shows the behavioral verification, on each verification level, it is done in C/C++ for HLS and VHDL for the HDL design.

#### Verification Specification

The low level component verification is done using small test benches in VHDL for each component. These test benches uses static inputs to verify the basic functionality that is correct outputs for given inputs, latency of the circuit matches expectation and that enable-, reset- and valid signals behave as expected with correct timings.

Design in HLS will not use this verification step in the same way. In HLS design the code will be verified on a module level where each sub component input and output could be compared but this will not include any timing- or control signal verification since it's expected that the tool handles that when the code is synthesised. The timing- and control signal are mostly automated, or abstracted away, giving only limited customization options, mainly through directives.

The top design verification is done using both functional verification, for design specific cases, as well as constrained input testing, for regions more commonly used for frequency translators. The functionality tested for are:

- Fixed Operation Testing where the component is feed with static inputs, either fixed or zero, to verify its behaviour for the edge cases.

- Functional Testing Verifying the function of the component by feeding it a set of known inputs, and comparing it with a set of known outputs. This should be done for different variations of inputs to cover as many cases as possible.

- Hardware Functionality Verify behavior at edge cases which causes overflow. As well as verification of hardware rounding due to the limited number of bits in the data-path.

• Random Vector Testing - Generate random inputs and run through a working software model. Use the same inputs and the generated outputs to verify the functionality of the hardware.

### Verification Method

To do verification a model of the system has been implemented in python together with code for generating system inputs- and outputs then saving them to a file. The python model also contains a main part that is used to define various test cases which are used to verify the functionality of different parts of the system.

The RTL verification for the VHDL-design will be done using a VHDL test-bench reading an input file then computing the output using the RTL-logic then writing the logic-output to an output file. The output file will be compared with the one that was generated using the python script, see appendix ??], for all the implemented designs, including HLS. Doing the HLS verification the same inputand output files, from the script, will be used to verify but the test-bench used is designed in C++. Because Xilinx HLS RTL co-simulation verifies the generated RTL-logic with the same stimuli that is used for the C-verification earlier in the HLS work flow, figure 3.2, the input- and output files can be used to verify both C functionality as well as HLS generated RTL.

# \_\_\_\_ <sub>Chapter</sub> 4 Case studies

In order for Vivado HLS to be evaluated it has to be used for designing hardware. This section describes the hardware design used throughout this thesis and explains why they were chosen. This chapter is also presenting the specification of the hardware that is to be used to have common design goals for each of the abstraction levels that are tested.

# 4.1 Modules

In this section the different modules and hierarchies used throughout this thesis are presented. The design is divided according to section 2.3.1 to divide the functionality into separate modules in order to ease the design process. The modules where chosen because they contains complex arithmetic operations in order to test the tool. They also uses all the main resources of an FPGA, DSP's, BRAM's which allows analysis of utilization choices. The two models can also be chained together in order to create a large design.

# 4.1.1 Frequency Translator Module

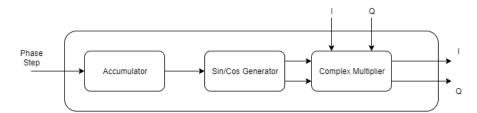

The frequency shift module is used to modify an input frequency by shifting it up or down. Frequency translators are commonly used in communication applications to shift signals to other frequency bands. Its basic functionality can be described with a block-diagram, see figure 4.1.

Figure 4.1: Block-Diagram for an overview of the frequency translator.

The sine and cosine generator uses one LUT for cos angles and one for sin angles respectively. To clarify the LUTs and their outputs will be referenced to as *SROM*, for the sine values, and *CROM*, for the cosine values, in the upcoming sections.

#### Accumulator

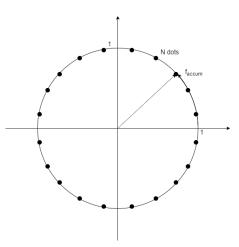

The accumulator and the cosine and sine generator together works as a digital oscillator. It will rotate its phase with a static step size (see figure 4.2) depending on the phase resolution in the sine- and cosine generator ROMs address-space. Throughout this thesis they have been separated to ease the analysis of each hardware implementation.

Figure 4.2: Schematic picture of the accumulators function.

The phase step size can not be smaller than the highest possible phase resolution, which will be the same as an accumulation of one, and has to be a multiple of the resolution in the SROM and CROM. The frequency generated by the accumulator can be described with equation 4.1

$$f_{accum} = \frac{f_{clk} \cdot N}{(2^{pwl} \cdot 2^{awl - pwl})} \tag{4.1}$$

where  $f_{accum}$  is generated frequency,  $f_{clk}$  is the on chip clock frequency, pwl is the number of bits used for the address space in the *SROM* and *CROM* respectively and awl is the accumulator word-length. N is the integer step size with which the accumulator is increasing. The *SROM* and *CROM* size has to be multiplied with  $2^{awl-pwl}$  in equation 4.1 because the memory represents one of eight segments for an entire  $2\pi$  rotation and the bits which are not used to address the memories are used in the truth table 4.1. The circuit itself is a simple accumulator circuit which can be seen in figure 4.3.

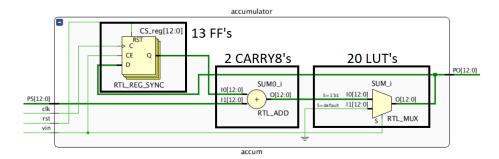

**Figure 4.3:** Description of the accumulator circuit used for calculating the next phase value.

#### Sine and Cosine Generation

The sine and cosine values are generated using a ROM, where function values of cosine and sine between zero and forty-five degrees are stored then modified according to table 4.1 to represent a full rotation. The whole sine and cosine generator can be seen in figure 4.4. The 13-bit input phase will be split up so that the three MSB's will be used to determine what segment the angle is in, see table 4.1, and the lower 10-bits will be addressing the space according to table 4.1. The outputs from the *SROM* and *CROM* is then used to determine the sine and cosine value from the input phase, see table 4.1.

Figure 4.4: Block-Diagram overview of the cos-/sin Generator

| Segment Address | ROM Address | COS   | SIN   |

|-----------------|-------------|-------|-------|

| 0               | k           | CROM  | SROM  |

| 1               | $k_0 - k$   | SROM  | CROM  |

| 2               | k           | -SROM | CROM  |

| 3               | $k_0 - k$   | -CROM | SROM  |

| 4               | k           | CROM  | -SROM |

| 5               | $k_0 - k$   | -SROM | -CROM |

| 6               | k           | SROM  | -CROM |

| 7               | $k_0 - k$   | CROM  | -SROM |

**Table 4.1:** Truth table for address and value representation depending on the segment address.

The cosine and sine generator together with the accumulator is often refereed to as an *Numerically-Controlled oscillator* or *NCO*. In this report the accumulator and trigonometric calculations are separated into different components to make it easier to analyse the different parts of the frequency translator.

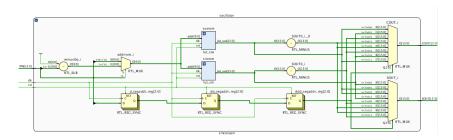

#### **Complex Multiplication**

The complex multiplication is used to mix the I and Q values from the sine and cosine generator with a fixed complex number  $z_i = Q_i + jI_i$ . The complex multiplication uses the three multiplication algorithm [11], thus it needs three DSP-blocks on the FPGA-fabric to be represented. The complex multiplier is designed using the Xilinx template in order to optimize the mapping to the FPGA-fabric, thus giving the best possible benchmark to be compared with the HLS. The real and imaginary calculations can be seen in equations 4.2 and 4.3.

$$I = a_r(b_r + b_i) - b_i(a_r + a_i)$$

(4.2)

$$Q = a_r(b_r + b_i) + b_r(a_i - a_r)$$

(4.3)

There are other ways of doing complex multiplication in hardware but it requires more multiplications and thus more DSP-units to keep the throughput to one.

#### 4.1.2 Power Meter

The other module that were implemented is a power meter. A power meter calculates the power of the I and Q signals.

The power is calculated by squaring I and Q and adding them up according to the formula 4.4, this gives the instantaneous power. The average power is then calculated by shifting in the instantaneous power values into a shift register which holds the eight previously calculated instantaneous power values. A rolling average is then calculated by summing up all of the eight entries and dividing them by eight to get the average, the division is in this case a three step right bit-shift since eight is a power of two.

A schematic picture of the module can be seen in figure 4.5.

$$P_{Peak} = I^2 + Q^2 \tag{4.4}$$

Figure 4.5: Block-Diagram overview of the power meter

#### 4.1.3 Top-Module

The top-module which ties the power meter together with the frequency translator is show in figure 4.6. The "Valid\_FREQ" indicates when valid data from the frequency translator can be obtained at "I\_out" and "Q\_out", whereas the "Valid\_PWR" indicates when valid data from the power meter can be obtained at "PWR\_out".

Figure 4.6: Block-Diagram overview of the top module

Note the top-model is used to describe an implementation that is connecting the frequency translator and power meter together. The purpose of the top-model design is to be used in the large system simulation experiment conducted to test simulation- and synthesis times of HLS when using large systems.

#### 4.1.4 Large System

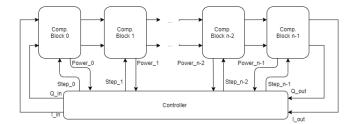

The large system is implemented by connecting n modules from figure 4.6 in series where  $I\_out$  and  $Q\_out$  from each model are connected to the next  $I\_in$  and  $Q\_in$ . The first  $I\_in$  and  $Q\_in$  as well as n inputs of *step* are used in the large system as inputs. The  $I\_out$  and  $Q\_out$  from the last component as well as n outputs of  $PWR\_out$  are used as the large system outputs. This allows for

separate reading of the signal power after each component. Figure 4.7 shows the design that is to be used for testing larger simulations using Vivado HLS. The *Comp. Block* are the module show in figure 4.6. The controller is supposed to set all step sizes as well as the first real- and imaginary input and to read all power calculations done in the design.

Figure 4.7: The large system design used to test long simulations.

The actual design done in HLS is the *Comp. Block* show in figure 4.7 connected in series with n step inputs, n power outputs as well as the real- and imaginary inputs and outputs. The *controller*-unit is a behavioral test bench designed in C++.

# 4.2 General Design Specifications

All the design should keep consistent goals so that each of the designs can be compared in a fair manner. This should make it so that the hardware keep approximately the same performance, if it is possible, and the difference will be mainly hardware utilization and design aspects. The design have the following hardware specification, see 4.2.

| Clock Frequency               | 400 MHz                                             |  |

|-------------------------------|-----------------------------------------------------|--|

| Throughput                    | 1 cycles/output                                     |  |

| Goal Latency Freq. Translator | 6 cycles                                            |  |

| Goal Latency Power Meter      | 1 cycle                                             |  |

| Data-                         | path Specification                                  |  |

| 16-bit                        | fixed point signed with 6 integer-, 10 decimal-bits |  |

| Overflow                      | saturate                                            |  |

| Rounding                      | truncate                                            |  |

| Addres                        | s-path Specification                                |  |

| 13-bit                        | unsigned integer                                    |  |

| Overflow                      | wrap around                                         |  |

| Rounding                      | s not needed                                        |  |

Table 4.2: Design specification

The address width for the frequency translator is 13-bits to represent the phase which was chosen so that the cosine and sine memories would have a 10-bit address space which would match the memory modules on the Xilinx FPGA-fabric [3]. The full 13-bits of the phase will not be used for memory addressing, it can be read more about in this section 4.1.1.

| Chapter | 5   |

|---------|-----|

| Resu    | lts |

Throughout this chapter the results of the case studies are presented using graphs and tables with brief descriptions of their content. The results will be divided into four main parts first comparing HLS- and HDL-synthesis then the simulation and synthesis times. The third section will cover the timing results from the case studies and the forth section will cover the hardware utilization and how the implementations mapped onto hardware. This chapter only aims to present the result of the different measurements that were done in this thesis. The discussion and analysis of the tool are presented in chapter 6. All designs were done targeting the FPGA circuit ZU27DR FPGA [7]. The results were generated by a RTL simulator from Xilinx using the Vivado design environment and the libraries for the ZU27DR FPGA.

The simulation-, synthesis- and place and route times are all measured in CPU time. This was deemed to be a good way of comparing the different design moments against each other since elapsed time is not as repeatable and would depend on what system the design is done on.

All the functional verification have been done using the same input and output samples generated from a Python reference model. The input stimuli has been randomly generated from normal distributions. The input frequency used was generated from a normal distribution using normal value  $\mu = 5MHz$  and standard deviation  $\sigma = 100KHz$ . Where as the input step, generating the internal frequency, for the frequency translator used a normal value  $\mu = 50$  and standard deviation  $\sigma = 10$  where, from equation 4.1, each step corresponds to an internal frequency step of approximately 49KHz.

When presenting the results there are differences between the VHDL design and the HLS designs. The choice was made to not design RTL testbenches for the HLS generated design but to use the C/RTL-Cosimulation provided by Xilinx Vivado HLS to verify the behaviour of the generated RTL.

## 5.1 HLS- versus HDL-Synthesis

It is important to emphasize on the difference between HLS- and HDL synthesis. Where HLS-Synthesis is used to transform C or C++ to RTL-code and HDL-Synthesis is used to transform RTL-code into a netlist which can be mapped onto hardware. Vivado HLS provides estimates of hardware performance after HLS-Synthesis. These estimates usually contains information if the design is going to meet timing and the logic consumption of the circuit. In table 5.1 the estimates of frequency translator and power meter implementations can be seen.

|                 | Bit-e         | exact         | Ultra High Level |               |  |  |  |

|-----------------|---------------|---------------|------------------|---------------|--|--|--|

|                 | HLS-synthesis | HDL-synthesis | HLS-synthesis    | HDL-synthesis |  |  |  |

|                 |               | Frequency     | translator       |               |  |  |  |

| Clock Period    | 2.5 ns        | 2.5 ns        | 2.5 ns           | 2.5 ns        |  |  |  |

| Slack           | 0.311 ns      | 0.576  ns     | 0.311 ns         | 0.615 ns      |  |  |  |

| LUT's           | 661           | 128           | 746              | 188           |  |  |  |

| FF's            | 399           | 165           | 915              | 199           |  |  |  |

|                 | Power meter   |               |                  |               |  |  |  |

| Clock Period    | 2.5 ns        | 2.5 ns        | 2.5 ns           | 2.5 ns        |  |  |  |

| Slack           | 0.211 ns      | 0.445 ns      | 0.148 ns         | 0.657 ns      |  |  |  |

| LUT's           | 420           | 179           | 437              | 234           |  |  |  |

| $\mathbf{FF's}$ | 156           | 156           | 163              | 163           |  |  |  |

**Table 5.1:** Result-matrix of the comparison between the HLS-synthesis and the HDL-synthesis.

The estimation are, and was throughout, underestimating the performance of the hardware that the generated RTL was going to implement. In table 5.1 the hardware estimates shows an overhead of 200% for some cases. This is mainly due to HLS-Synthesis not making any hardware optimizations such as removing signals bound to zero or, implementing division or multiplication with a power of two with shifts.

HLS-Synthesis did also provide timing information which for the single component implementations ensured that timing was going to be met after HDL-Synthesis as well. This was not the case for the large system which passed HLS-Synthesis timings but not HDL-Synthesis which contained to long physical paths and limited the large system design.

# 5.2 Synthesis- and Simulation Times

In this section the synthesis- and simulation times will be presented for each of the case studies. The section will cover the performance for each case study and the abstraction levels related to it. Each of the simulations are done with one million input samples for each respective abstraction level and component.

The C/RTL-Cosimulation times, presented in tables 5.2 and 5.3, shows the CPU time measured from the C-testbench. The CPU time to run the actual C/RTL-Cosimulation after it has synthesised is down to ms.

#### 5.2.1 Frequency Translator - Synthesis- and Simulation Times

The C-simulation times for the frequency translator is approximately eleven times faster for the bit-exact implementation, see table 5.2. This is mainly due to the use of arbitrary precision datatype library used so that datatypes are synthesised into fixed-point. The bit-exact C simulation is also faster than the behavioral simulation.

|                           | VHDL RTL | HLS Bit-Exact | HLS Ultra High Level |

|---------------------------|----------|---------------|----------------------|

| C simulation              | N/A      | 00:00:03      | 00:00:33             |

| <b>RTL CO-Simulation</b>  | N/A      | 00:01:16      | 00:01:11             |

| Behavioral RTL-simulation | 00:00:25 | N/A           | N/A                  |

| HLS-synthesis             | N/A      | 00:00:30      | 00:01:19             |

| HDL-Synthesis             | 00:00:52 | 00:00:47      | 00:00:46             |

| Place and route           | 00:01:27 | 00:02:30      | 00:02:43             |

Table 5.2: Result-matrix of the comparison between CPU time of the simulation and build times of the frequency translator, format hh:mm:ss.

#### Power Meter - Synthesis- and Simulation Times 5.2.2

The times presented in table 5.3 shows no noticeable differences in any of the synthesis- and simulation times for the power meter. The power meter implementation shows a reduction between functional simulation using C compared to behavioral simulation.

|                           | VHDL RTL | HLS Bit-Exact | HLS Ultra High Level |

|---------------------------|----------|---------------|----------------------|

| C simulation              | N/A      | 00:00:10      | 00:00:12             |

| RTL CO-simulation         | N/A      | 00:00:26      | 00:00:26             |

| Behavioral RTL-simulation | 00:00:23 | N/A           | N/A                  |

| HLS-synthesis             | N/A      | 00:01:12      | 00:01:10             |

| HDL-Synthesis             | 00:01:05 | 00:01:02      | 00:00:59             |

| Place and route           | 00:01:12 | 00:01:49      | 00:01:40             |

TT O TH TT: 1 T ----

Table 5.3: Result-matrix of the comparison between CPU time of the simulation and build times of the power meter

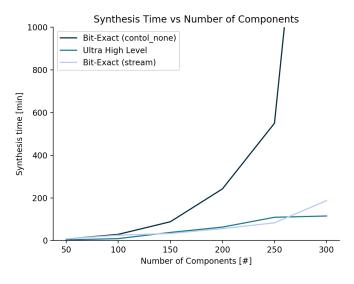

#### 5.2.3 Large System - Synthesis- and Simulation Times

In table 5.4 the functional verification- and synthesis times of a large system is presented. The goal of these measurements are to represent the verification- and synthesis times that one could expect when designing a larger and more complex system that utilizes more hardware where Number of devices indicates the number of frequency translator and power meter pairs used.

The results for the HLS bit-exact C simulation (see table 5.4) time is taken from simulations which were using C data types. That is *double* for floating point calculations and *int* for the integer calculations. Should the same C-simulation be done with the Vivado HLS libraries for fixed point and integer it would increase the simulation time for the bit-exact model as for the ultra high level implementation. The ultra high level is forced to use the arbitrary precision libraries because the Vivado HLS libraries for complex multiplication and cosine and sine generator are using them. Thus the C-simulation times are higher for the ultra high level design than the bit-exact. The difference between behavioral simulation for RTL and C simulation (using native C data types) is grows larger as the design size increases. This can be seen in table 5.4 which has seven minutes and seventeen seconds compared to thirteen second difference in table 5.3.

|                              | VHDL RTL  | HLS Bit-Exact | HLS Ultra High Level |

|------------------------------|-----------|---------------|----------------------|

| Number of devices            | 100       | 100           | 100                  |

| Number of inputs             | 1 000 000 | 1 000 000     | 1 000 000            |

| C-Simulation                 | N/A       | 00:00:20      | 00:20:01             |

| HLS-synthesis                | N/A       | 00:09:24      | 00:13:30             |