# Gate Recurrent Unit Neural Networks for Hearing Instruments

Harshit Sharma

ha2442sh-s@student.lu.se

Pallavi Rajanna

pa6354ra-s@student.lu.se

Department of Electrical and Information Technology Lund University

Supervisor: Oskar Andersson and Adrian Mardari

Academic Supervisor: Joachim Rodrigues

Examiner: Pietro Andreani

June 25, 2020

# Abstract

Gated Recurrent Unit (GRU) neural networks have gained popularity for applications such as keyword spotting, speech recognition and other artificial intelligence applications. Typically for most applications training and inference is performed on cloud servers, and the result are transferred to the power constrained device, e.g., an hearing instrument (HI). This approach has disadvantages such as latency and connectivity, privacy concern, and high energy cost per bit for real-time data transfer. Therefore, there is a strong demand to move inference from cloud to power constraint devices. However, executing inference on HI introduces many challenges in terms of throughput, power budget, and memory footprint. This research investigate how efficient it is to execute inference on a dedicated hardware accelerator, rather than using an existing audio digital signal processor (xDSP in Oticon's HI).

The two approaches are compared in terms of area, power, energy dissipation and total clock cycles required to perform an inference. Straightforward implementation of nonlinear activation function is expensive in hardware, therefore, different methods of approximation are evaluated. Out of different approximation algorithms, fast sigmoid and fast tanh approaches were chosen. A pretrained keyword spotting (KWS) model was used. However, it exceeds the memory space available on xDSP. Instead, three small GRU networks were trained and executed on xDSP to approximate energy dissipation and clock cycle count if a bigger network was run on the xDSP.

Precision needed to store and compute data was reduced to minimize storage needed keeping detection accuracy in mind. By reducing wordlength from 32-bit to 8-bit for network parameters, memory space required was reduced by 4 times while accuracy decreased from 91% to 88%. The GRU inference runs on per layer basis, data flow was optimized to achieve significant reduction in area and power.

The xDSP needs around  $2\times$  more clock cycles to complete a full network inference for a benchmark keyword spotting neural network compared to dedicated hardware accelerator. The energy dissipation increased by around  $10\times$  while using Oticon's xDSP processor instead of a dedicated accelerator. The xDSP is capable of executing GRU network with upto 40 neurons per layer, but for bigger networks hardware accelerator is a better solution. All in all, the dedicated accelerator solution has the best performance from the explored solution and can be integrated in HI to compute neural networks.

# Popular Science Summary

Artificial intelligence is becoming a huge part of our life, from being used in mobile phones, smart watchs, home entertainment systems etc. However, due to a large amount of computations need to be performed to execute a simple task, most of this processing is done in cloud servers. Although, there is a breakthrough in artificial intelligence, there has been serious limitation in terms of power and energy efficiency that needs to be addressed.

In 2019, artificial intelligence (AI) computer program known as AlphaStar built by Google's AI firm DeepMind played the science-fiction video game *StarCraft II* on European servers. The AI competed against 90,000 player and was placed within the top 0.15%. DeepMind, previously built world-leading AIs that play chess and Go. However, estimated power consumption of these AI is in order of megawatts, whereas human brain only consumes 20 watt. This means that AI needs to be more efficient before it can be completely integrated in daily our life.

AI has gained popularity in speech recognition technology, where AI can recognize spoken words, which can then be converted to text or used to perform tasks. A subset of speech recognition is keyword spotting, where a task is performed after identifying a keyword in the input voice signal. Companies such as Facebook, Amazon, Microsoft, Google and Apple have already integrated this feature on various devices through services like Google Home, Amazon Echo and Siri.

With this in mind, the goal of this thesis has been to select a pretrained keyword spotting model and propose a efficient dedicated hardware accelerator to perform this task. The spotting of spoken keyword has been performed using a GRU algorithm which is an advanced recurrent neural network. In order to compare the scalable and efficient hardware accelerator design, it was compared with an existing audio digital signal processor used in Oticon's hearing instruments. This research addresses the problem of high power consumption and large memory reference that restricts the use of large scale neural networks on power constrained devices. Research also addresses the issue of privacy, i.e., sharing of data with cloud servers.

The proposed dedicated hardware accelerator can be integrated in HI to compute neural networks.

# Table of Contents

| 1 | Intro                                | oduction                        | . 1 |  |  |  |

|---|--------------------------------------|---------------------------------|-----|--|--|--|

|   | 1.1                                  | Artificial Neural Networks      | 1   |  |  |  |

|   | 1.2                                  | Artificial NN at the edge       | 5   |  |  |  |

|   | 1.3                                  | Recurrent Neural Networks       | 6   |  |  |  |

|   | 1.4                                  | Keyword Spotting System         | 8   |  |  |  |

|   | 1.5                                  | Thesis Goal                     | 10  |  |  |  |

| 2 | Gated Recurrent Unit - GRU1          |                                 |     |  |  |  |

|   | 2.1                                  | A GRU cell                      | 11  |  |  |  |

|   | 2.2                                  | Arithmetic Operations           | 14  |  |  |  |

|   | 2.3                                  | Data dependencies               | 15  |  |  |  |

| 3 | Wordlength and Hardware Optimization |                                 |     |  |  |  |

|   | 3.1                                  | Data representation             | 17  |  |  |  |

|   | 3.2                                  | Role of the Activation Function | 19  |  |  |  |

|   | 3.3                                  | Activation Function exploration | 20  |  |  |  |

|   | 3.4                                  | Quantization Experiments        | 28  |  |  |  |

| 4 | xDSP Implementation                  |                                 |     |  |  |  |

|   | 4.1                                  | Register Files                  | 35  |  |  |  |

|   | 4.2                                  | Datapath                        | 35  |  |  |  |

|   | 4.3                                  | Memory interfaces               | 36  |  |  |  |

|   | 4.4                                  | Design considerations           | 36  |  |  |  |

|   | 4.5                                  | Implementation                  | 37  |  |  |  |

|   | 4.6                                  | Result                          | 39  |  |  |  |

|   | 4.7                                  | Discussion                      | 41  |  |  |  |

| 5 | Dedicated Neural Network Engine      |                                 |     |  |  |  |

|   | 5.1                                  | Design Considerations           | 43  |  |  |  |

|   | 5.2                                  | Overview                        | 44  |  |  |  |

|   | 5.3                                  | Top module                      | 44  |  |  |  |

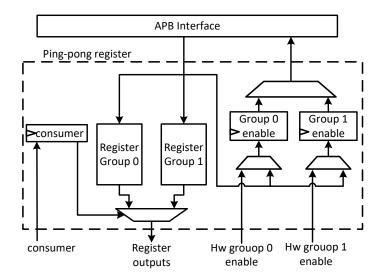

|   | 5.4                                  | Input ping-pong registers       | 49  |  |  |  |

|   | 5.5                                  | Arithmetic Functional Units     | 50  |  |  |  |

|   | 5.6                                  | Configuration Module            | 53  |  |  |  |

|                | 5.7  | Memory                               | 54 |  |  |  |  |  |

|----------------|------|--------------------------------------|----|--|--|--|--|--|

|                | 5.8  | FSMs                                 | 56 |  |  |  |  |  |

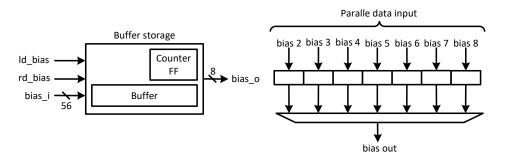

|                | 5.9  | Buffer for bias                      | 59 |  |  |  |  |  |

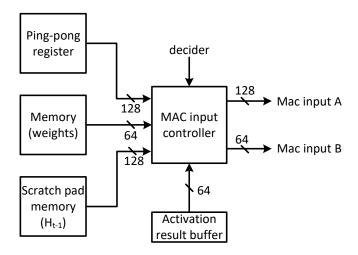

|                | 5.10 | MAC input selector module            | 60 |  |  |  |  |  |

|                | 5.11 | Activation result buffer module      | 61 |  |  |  |  |  |

|                | 5.12 | Scratch pad memory controller module | 62 |  |  |  |  |  |

|                |      | Functionality verification           | 62 |  |  |  |  |  |

| 6              | Synt | hesis Results                        | 65 |  |  |  |  |  |

|                | 6.1  | xDSP                                 | 65 |  |  |  |  |  |

|                | 6.2  | Dedicated GRUE                       | 66 |  |  |  |  |  |

|                | 6.3  | Discussion                           | 71 |  |  |  |  |  |

| 7              | Conc | clusion                              | 73 |  |  |  |  |  |

|                | 7.1  | Future works                         | 73 |  |  |  |  |  |

| Ribliography 7 |      |                                      |    |  |  |  |  |  |

# List of Figures

| 1.1  | Neural network vs deep neural network. Edges represent weights and     |    |

|------|------------------------------------------------------------------------|----|

|      | vertices/nodes represent activations [2]                               | 2  |

| 1.2  | Operations at one neuron of a neural network                           | 2  |

| 1.3  | Sigmoid non-linearity squashes real numbers to range between $[0,1]$ . | 3  |

| 1.4  | The tanh non-linearity squashes real numbers to range between [-1,1].  | 3  |

| 1.5  | Rectified Linear Unit (ReLU) activation function, which is zero when x |    |

|      | $<$ 0 and then linear with slope 1 when $\times >$ 0                   | 3  |

| 1.6  | Recurrent Neural Network                                               | 4  |

| 1.7  | Feedforward Neural Network                                             | 5  |

| 1.8  | RNN cell                                                               | 7  |

| 1.9  | Back propagation in RNNs                                               | 8  |

| 1.10 | KWS system [14]                                                        | 9  |

| 2.1  | Gated Recurrent Unit (GRU)                                             | 11 |

| 2.2  | Reset and update gate in a GRU unit                                    | 12 |

| 2.3  | Candidate hidden state computation in a GRU unit                       | 13 |

| 2.4  | Structure of an GRU unit followed by a output layer and a softmax      |    |

|      | activation function                                                    | 14 |

| 2.5  | Data dependency graph of the GRU algorithm                             | 16 |

| 3.1  | Example layout of 32-bit floating point                                | 18 |

| 3.2  | Format of a Fixed-Point Number                                         | 18 |

| 3.3  | Feature selection Linear vs Non linear [27]                            | 20 |

| 3.4  | Sigmoid function                                                       | 21 |

| 3.5  | The hyperbolic tangent function (tanh)                                 | 21 |

| 3.6  | PLAN approximation of sigmoid function                                 | 23 |

| 3.7  | PLAN approximation of hyperbolic tangent function (tanh)               | 23 |

| 3.8  | Second Order approximation of sigmoid function                         | 24 |

| 3.9  | Second Order approximation of hyperbolic tangent function (tanh)       | 25 |

| 3.10 | Fast sigmoid function approximation                                    | 26 |

| 3.11 | The Fast hyperbolic tangent function approximation                     | 27 |

| 3.12 | Network accuracy for GRU network with different precision bits to      |    |

|      | represent the network                                                  | 30 |

| 3.13<br>3.14<br>3.15 | Network accuracy for different network parameter precision for fixed-point implementation of 154x154x154x12 topology     | 32<br>32 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|----------|

| 3.16                 | Raw prediction of the fixed-point implementation (red line) against the 32-bit floating-point implementation (blue line) | 34       |

| 4.1                  | MAC unit.                                                                                                                | 3        |

| 4.2                  | Illustration of steps executed to load the bias value into accumulator.                                                  | 38       |

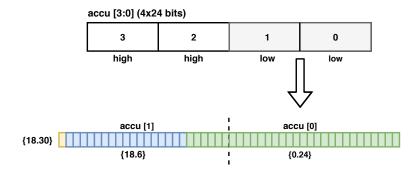

| 4.3<br>4.4           | 96-bit accumulator divided into low and high part                                                                        | 39<br>41 |

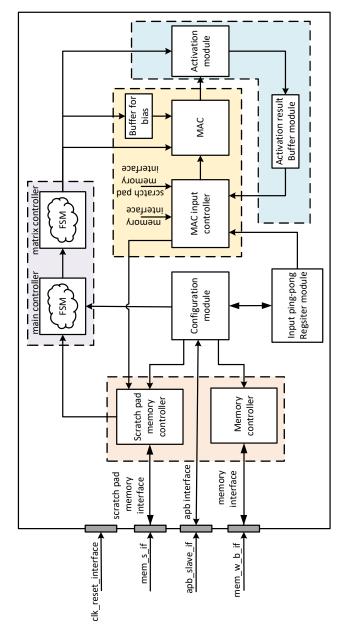

| 5.1                  | Top level architecture of the design                                                                                     | 45       |

| 5.2                  | Data Flow of GRUE without optimizations                                                                                  | 46       |

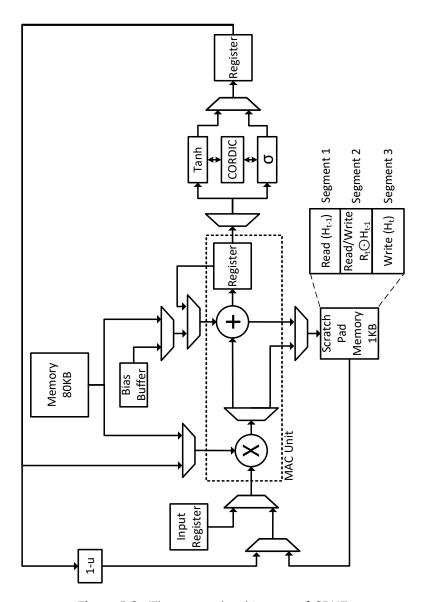

| 5.3                  | The proposed architecture of GRUE                                                                                        | 48       |

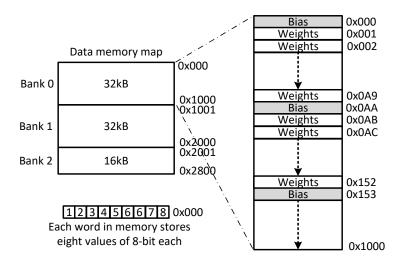

| 5.4                  | Structure of data memory representing the way biases and weights are                                                     | 40       |

| 5.5                  | arranged                                                                                                                 | 49<br>50 |

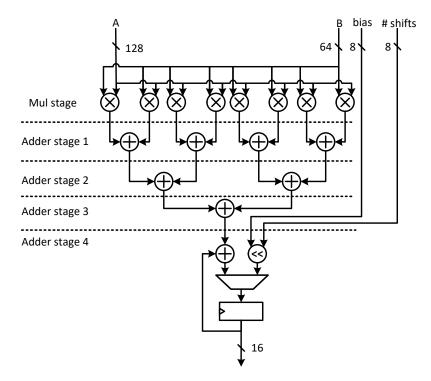

| 5.6                  | Architecture of MAC unit.                                                                                                | 52       |

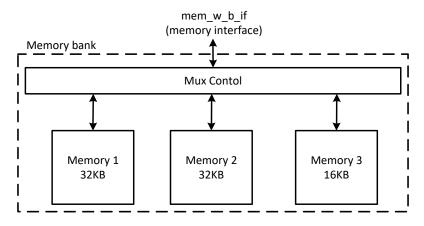

| 5.7                  | Structure of RAM bank                                                                                                    | 54       |

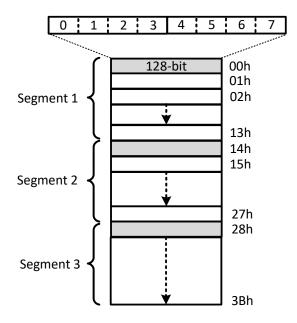

| 5.8                  | Structure of scratch pad memory constructed using standard cells                                                         | 55       |

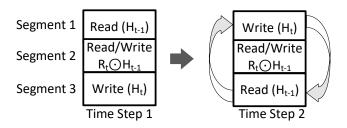

| 5.9                  | Figure showing the flipping of scratch memory segments after each                                                        |          |

|                      | time step                                                                                                                | 55       |

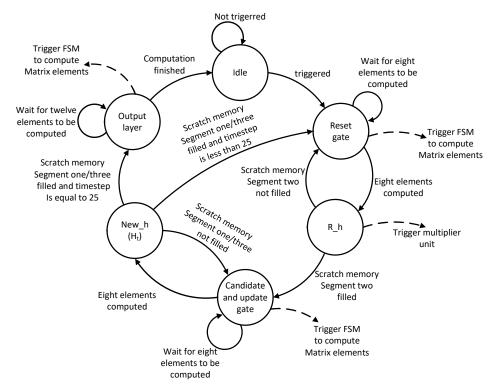

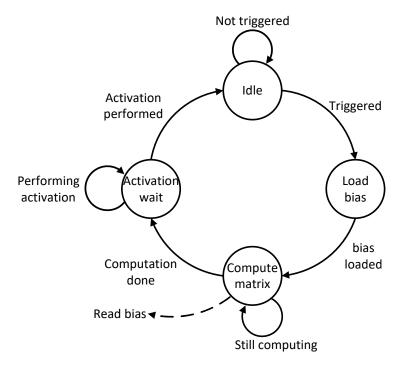

| 5.10                 | Main controller FSM                                                                                                      | 5        |

| 5.11                 | Matrix controller FSM                                                                                                    | 58       |

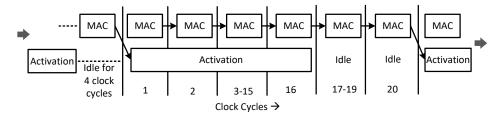

| 5.12                 | Activation computation in parallel with the MAC operation                                                                | 59       |

| 5.13                 | Block diagram of bias buffer                                                                                             | 60       |

| 5.14<br>5.15         | Data flow of MAC input controller                                                                                        | 6.       |

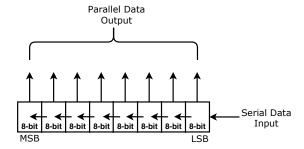

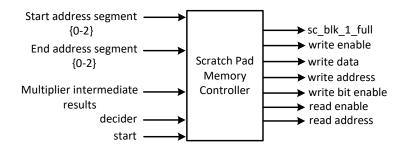

| 5.15                 | A shift register with parallel output to buffer activation results Block diagram of scratch pad memory controller        | 62       |

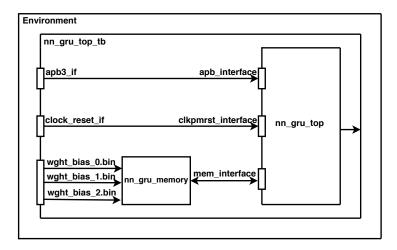

| 5.17                 | Overview of the testbench setup                                                                                          | 63       |

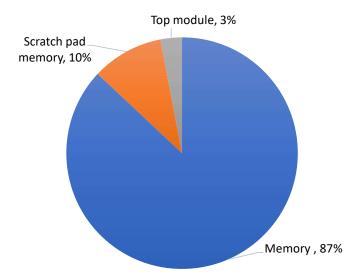

| 6.1                  | Area percentage occupied by modules.                                                                                     | 67       |

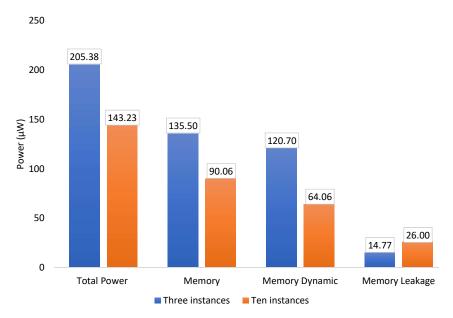

| 6.2                  | Power cost comparison of GRUE with three and ten memory instances.                                                       | 68       |

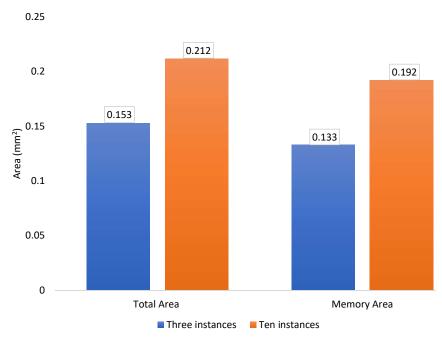

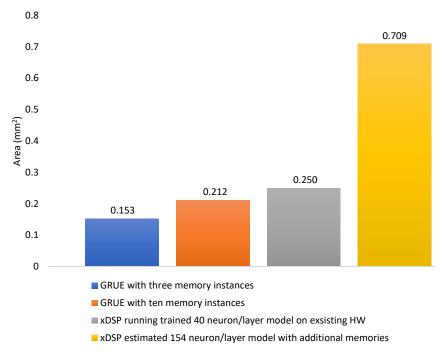

| 6.3                  | Area comparison of GRUE with three and ten memory instances                                                              | 69       |

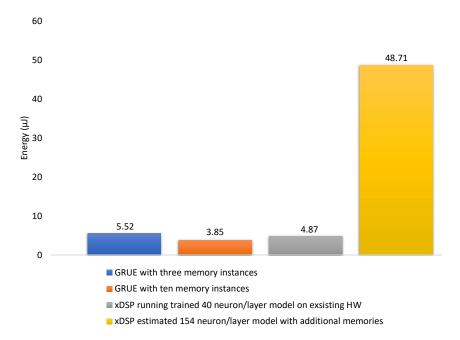

| 6.4                  | Energy cost comparison of GRUE with xDSP                                                                                 | 70       |

| n h                  | Area comparison of CDITE with VISD                                                                                       | - /      |

# List of Tables

| Energy and area comparison [34]                                           | 29                                               |

|---------------------------------------------------------------------------|--------------------------------------------------|

| Accuracy of GRU network with different precision                          | 29                                               |

| Accuracy of 16-bit GRU network with different precision bits for pa-      |                                                  |

| rameters.                                                                 | 30                                               |

| Classification accuracy for different input data precision                | 31                                               |

| Classification accuracy for different input precision based KWS Tensor-   |                                                  |

| flow dataset                                                              | 32                                               |

| Register files.                                                           | 35                                               |

| <del>-</del>                                                              | 36                                               |

| ·                                                                         |                                                  |

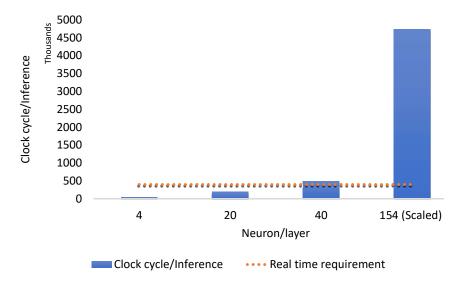

| neurons per layer                                                         | 40                                               |

| Power in $\mu W$ for the small and estimated GRU network implemen-        |                                                  |

| tation on xDSP. It includes power numbers with and without power          |                                                  |

| management (PM)                                                           | 65                                               |

| Energy dissipation in $\mu J$ for the GRU network implementation on xDSP. | 66                                               |

| Power in $\mu W$ for the dedicated GRUE with three and ten memory         |                                                  |

| instances                                                                 | 67                                               |

| Energy cost for the dedicated GRUE                                        | 68                                               |

|                                                                           | Accuracy of GRU network with different precision |

# List of Abbreviations

$\mathbf{GRU} \quad \mathbf{Gated} \ \mathbf{Recurrent} \ \mathbf{Unit}$

$\mathbf{GNNE}\ \mathbf{GRU}\ \mathbf{N}\mathrm{eural}\ \mathbf{N}\mathrm{etwork}\ \mathbf{E}\mathrm{ngine}$

ANN Artificial Neural Network

RNNs Recurrent Neural Networks

NN Neural Network

NNs Neural Networks

$\mathbf{RTL} \qquad \mathbf{Register} \ \mathbf{Transfer} \ \mathbf{Level}$

RAM Random-access Memory

$\mathbf{MAC} \quad \mathbf{M} \text{ulitiply } \mathbf{A} \text{nd } \mathbf{A} \text{ccumulate}$

$\mathbf{LUT} \quad \mathbf{Look} \; \mathbf{Up} \; \mathbf{Tables}$

$\mathbf{KWS} \quad \mathbf{Keyword} \ \mathbf{Spoting}$

FSM Finite State Machine

FSMs Finite State Machines

HI Hearing Instruments

Deep learning is an umbrella term for a set of machine learning algorithms that attempt to model high-level abstractions in data. Included in this machine learning branch are neural networks, which try to mimic the highly intricate way of the human brain in which it processes information. In large, due to increasingly powerful computing capabilities, these types of networks have, in the past years, produced remarkable advances in several fields.

### 1.1 Artificial Neural Networks

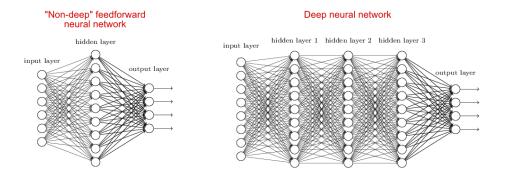

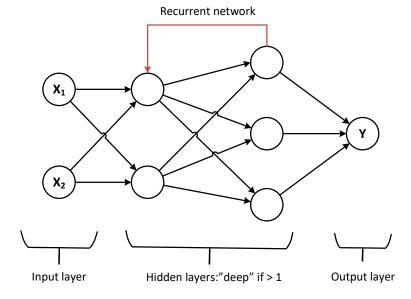

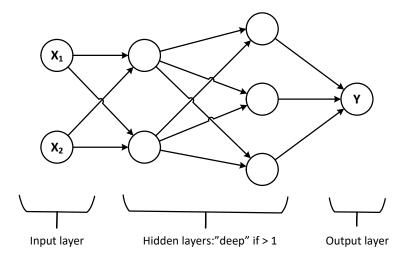

Neural Networks (NNs) were first proposed by Warren McCullough and Walter Pitts in 1944. Neural networks are multi-layer networks of neurons that are used to classify things, make predictions, etc. Artificial Neural Networks (ANNs) attempt to emulate the human brain, which is a collection of connected networks of neurons. An ANN is based on a network of connected units or nodes called artificial neurons where each connection can transmit a signal to other neurons. Different sections of the human brain are responsible for processing different pieces of information, and these parts of the brain are arranged hierarchically in layers. Therefore, as information enters the brain, it is processed in each layer of neurons and passed to the next one. It is this layered approach to processing information and making decisions that ANNs are trying to replicate. In the simplest form, an ANN has only three layers of neurons: the input layer (where the data enters the system), the hidden layer (where the information is processed), and the output layer (where the system decides what to do based on the data). However, ANNs can get much more complex than that, and include multiple hidden layers. When a Neural Network (NN) has more than one hidden layer it is referred to as a deep neural network. This distinction is illustrated in Figure 1.1. Whether it is three layers or more, information flows from one layer to another, just like in the human brain [1].

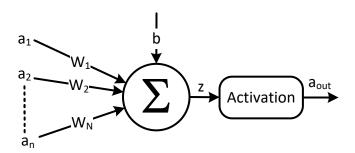

The basic structure of a NN consists of neurons whose underlining operation is multiply-accumulate (MAC). A neuron computes the weighted average of the input data and passes the information through a non-linear function, i.e., activation function, such as sigmoid function. Figure 1.2 illustrates operations at one neuron of a NN. For a given artificial neuron, let there be a n + 1 inputs with signals  $a_1$  through  $a_N$  and weights  $w_1$  through  $w_N$ . The inputs  $(a_1 \text{ to } a_N)$  are multiplied with their respective weights  $(w_1 \text{ to } w_N)$ , and the results are summed together. A

bias value (b) is added to this value, resulting in the final sum (z). The activation function is used to bring non-linearity in the output of the neuron.

**Figure 1.1:** Neural network vs deep neural network. Edges represent weights and vertices/nodes represent activations [2].

**Figure 1.2:** Operations at one neuron of a neural network.

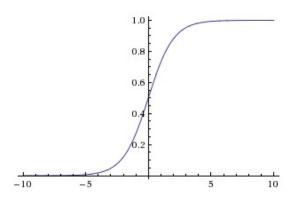

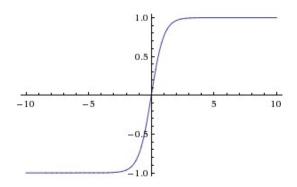

Every activation function (or non-linearity) takes a number as input and performs a certain fixed mathematical operation on it. Figure 1.3, Figure 1.4 and Figure 1.5 illustrates three commonly used activation functions namely sigmoid, tanh, and rectified linear unit (ReLu).

**Figure 1.3:** Sigmoid non-linearity squashes real numbers to range between [0,1].

**Figure 1.4:** The tanh non-linearity squashes real numbers to range between [-1,1].

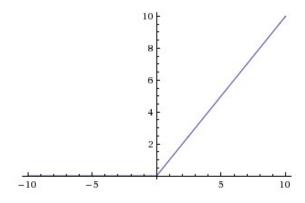

**Figure 1.5:** Rectified Linear Unit (ReLU) activation function, which is zero when  $\times < 0$  and then linear with slope 1 when  $\times > 0$ .

Activation functions and the algorithms explored to approximate the sigmoid and tanh activation functions are explained later in Chapter 3.

The three most commonly used types of neural network architectures in artificial intelligence:

- Feedforward NNs also referred to as multi-layer perceptrons, dense/fully connected networks, or ANNs. The flow of information through the network is unidirectional without any internal feedback connections, and are the essential deep learning models [3].

- Recurrent NNs (RNNs) [4]–[6] these networks have an internal state (memory) to process sequences of inputs. Unlike feedforward NNs, RNNs have feedback loops which makes their output depended on the previous computations. However, conventional RNNs have a few limitations. They are difficult to train and have a very short-term memory, which limits their functionality. More advanced variants of RNNs models were developed, e.g., Gated Recurrent Unit (GRU) and Long Short Term Memory (LSTM), to overcome this problem.

- Convolutional neural network has the ability to capture the spatial and temporal dependencies in an input through the application of relevant filters. It performs better on the image data set due to the reduction in the number of parameters involved and reusability of weights [7].

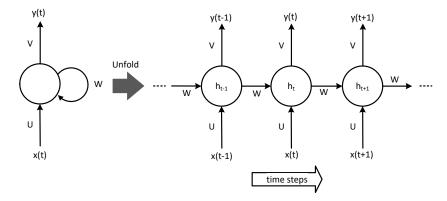

One of the neural network architecture paradigms that have driven breakthroughs in deep learning is RNNs. Recurrent neural networks, as their name states, use recurrent paths (loops) to insert previous outputs as inputs for the current iteration as shown in Figure 1.6.

Figure 1.6: Recurrent Neural Network.

RNNs are a type of neural network that takes sequential input and produces sequential output by sharing parameters between time steps. Two identical data structures will not produce the same output if the previous inputs were not identical as well. Compared to the feed-forward neural networks which do not process previous results or states to make decisions. Feed forward computations require no feedback of previous outputs or any kind of short or long range context as shown in Figure 1.7. A feed-forward neural network is trained to match two identical inputs to the same output. This is very efficient in many cases where past events must not alter the networks perception of the current situation. A typical example is image recognition where two identical images must produce the same output.

Figure 1.7: Feedforward Neural Network.

RNNs have led to breakthrough results in natural language processing [8], image captioning [9], and speech recognition [10]. Their limitation is that this mechanism provides access to the most recent events only. As stated in [10], traditional RNNs are incapable of dealing with long term dependencies.

## 1.2 Artificial NN at the edge

There are two main phases in the deep learning process: training and inference. Training refers to the preparation of a machine learning model to do a specific task. During training, each layer of data in the model assigned with random weights. After running forward pass through the data, the model predicts the scores and classify labels using the random weights assigned. After comparing classified labels against the actual labels, a loss function is used to compute the error. This error is then backpropagated through the network, and weights are updated accordingly via weight update algorithm such as Gradient Descent.

The inference is the actual execution of the task using the statistical model obtained during the training session. It comprises of a similar forward pass as

training to predict the values. Unlike training, it does not include a backward pass to compute the error and update weights. Therefore, the inference cannot happen without training.

Training and inference have different computational needs. Since deep learning algorithms are very costly in terms of energy dissipation, both the training of a NN and its inference is typically executed on Central Processing Unit (CPU) servers or Graphics Processing unit (GPU) in the cloud. Afterward, the results are transmitted to lower-complexity power-constrained (edge) devices such as hearing instruments. However, this setup has several disadvantages [11]

- Latency and connectivity issues, as it requires a wearable device always to be connected to the cloud, and low latency is critical for specific tasks.

- Privacy issues related to sharing raw data such as images, speech, video, locations with a remote system, which is not desirable for users.

- Wireless connections have a high energy cost per transferred bit for real-time data transfer on energy-constrained platforms.

Due to these reasons, there is a strong demand to move especially the inference from the cloud to the edge instead. This setup would mitigate latency and privacy issues as well as improve the battery life of the device [12] [3]. Designing efficient hardware architectures at the edge is therefore crucial; especially for low-power devices such as hearing instruments where area, memory footprint, power budget, and throughput, are limiting factors. These limiting factors of hearing instruments have the disadvantage that large NNs cannot fit on the edge device. Therefore, there should be a balance between which NNs that are deployed on the edge devices and which NNs that still are run in the cloud. Another motivation to design dedicated hardware accelerators for NNs is that conventional processors are not optimized for running NNs.

### 1.3 Recurrent Neural Networks

The feed forward neural networks make assumption that all inputs are independent on each other. This assumption is wrong in the case of sequential data, where data exhibits a dependency on past data.

RNN model include dependency on past data through a hidden state, or memory, that holds information of what has been processed so far. At any point in time, (1.1) shows that the value of the hidden state is a function of the value of the hidden state at the previous time step and the value of the input at the current time step.

$$h_t = \phi(h_{t-1}, x_t) \tag{1.1}$$

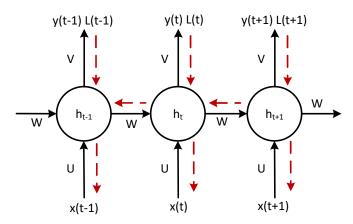

The term  $h_t$  and  $h_{t-1}$  are the values of hidden state at the time steps t and t-1, respectively, and  $x_t$  is the input value at time t. RNNs are network of nodes (neurons) organized into successive layers. Each node in a given layer is connected with a one-way connection to every other node in the next layer. Figure 1.8 illustrates the graphical representation of RNN cell on the left and unrolled RNN on the right. The RNNs, parameters are defined by three weight matrices U, V,

and W, corresponding to the input, output and hidden state respectively. At time t, the cell has an input  $x_t$  and an output  $y_t$ . A portion of output  $y_t$  (the hidden state  $h_t$ ) is fed back into the cell as an input to next time step t+1.

Since, the same operation is applied on different inputs at each time step, weights matrices U, V, and W are shared across the time steps. Due to the sharing of weight vectors across all the time steps, the number of parameters that needs to learn reduces. The value of hidden vector is

$$h_t = \tanh(Wh_{t-1} + Ux_t),\tag{1.2}$$

where W is the hidden state weigh matrix,  $h_{t-1}$  is the previous hidden state, U is the input weight matrix and  $x_t$  the input at time t.

Figure 1.8: RNN cell.

Using (1.3), the output vector is computed where V is the weight matrix,  $h_t$  the hidden state at time t and softmax is the function that converts the raw predictions to the probability distributions of a list of potential outcomes the input sequence belongs.

$$y_t = softmax(Vh_t) \tag{1.3}$$

Tanh is chosen over other nonlinearities, to keep the gradients in the linear region of the activation function and prevent the vanishing gradient problem.

### 1.3.1 Vanishing and exploding gradient problem

Training of RNN involves back propagation. Since the parameters are shared by all the time steps, the gradient at each output not only depends on the current time step, but also on the previous time steps. This is known as backpropagation through time (BPTT).

Figure 1.9: Back propagation in RNNs.

Figure 1.9 represents the state of an RNN at different instances of time t. During the forward propagation (denoted by solid black lines), the network produces predictions that are compared with the labels (ground truth values) to compute the loss  $L_t$  at each time step. During backpropagation (shown by solid red lines), the gradients of the loss with respect to the weight matrices U, V, and W are computed at each time step and the parameters are updated by adding the gradients. At any point of time, the gradient is the product of all the gradients up to that point.

When the gradients of the hidden state is less than one, brackpropagation across multiple time steps leads to smaller and smaller product of the gradients, leading to vanishing gradient problem. Similarly, if the gradients are larger than one, the product gets larger and larger, leading to the exploding gradient problem.

The side effect of vanishing gradients is that the gradients of distant time steps do not contribute to the learning process, so the RNN do not get trained for long term dependencies. Exploding gradients are easy to identify, as the gradients becomes very large, the training process will crash.

As stated in [10], traditional RNNs are incapable of dealing with long term dependencies. Over the years more advanced alternatives such as the Gated Recurrent Unit (GRU) and Long Short Term Memory (LSTM) have evolved. Both the architectures have been designed to deal with vanishing gradient problem and learn long term dependencies. The GRU is a simpler form of LSTM, using fewer gates that modulate the flow of information inside the unit and has no separate memory cell. The GRU architecture is the focus of this thesis and is explained in the chapter 2 in detail.

# 1.4 Keyword Spotting System

The goal of keyword spotting is to detect the presence of specific spoken words in unconstrained speech. The majority of keyword spotting systems are based on generative hidden Markov models and lack discriminative capabilities. However, discriminative keyword spotting systems are currently based on frame-level posterior probabilities of sub-word units [13]. This project presents a discriminative keyword

spotting system based on GRU NN, that uses information from long time spans to estimate word-level posterior probabilities. KWS application has highly constrained power budget and typically runs on tiny microcontrollers with limited memory and compute capability [14].

An open-source KWS project developed by ARM [14] is used in our experiments. The project provide pretrained models for various neural network architectures such as DNN, CNN, LSTM, GRU, etc.

The parameters are extracted from the pretrained GRU model using python and are used for inference in both high-level (Python and Matlab) and low level (xDSP and hardware) implementation. The pretrained GRU model has three layer (input, hidden and output), having 154 neurons in input and hidden layer and 12 neurons in output layer. The input to the GRU NN is the flattened featured matrix, Mel-frequency cepstral coefficients (MFCC) is one of the commonly used for feature extraction. Feature extraction using MFCC involves translating the time-domain speech signal into a set of frequency-domain spectral coefficients, which enables dimensionality compression of the input signal.

The input data represents features from a one-second long audio recordings which are obtained from the Google speech commands dataset [14] created by TensorFlow and AIY teams. The dataset has more than 65,000 one-second long utterances of 30 short words, by thousands of different people. The files are in 16-bit little-endian PCM-encoded WAVE format. They are divided into three sets, namely training, validation, and test set in 80:10:10 ratio that undergo further selection. Raw data was extracted from the recordings using Python in a test set, which was used as an input for the GRU NN.

Figure 1.10 illustrates a feature extractor and a NN based classifier. The input signal of length L is framed into overlapping frames with window size of l and window stride s. The total frames are given as

$$T = \frac{L - l}{s} + 1.$$

From each frame F MFCC features are extracted, producing total of TF features for the input audio signal of length L. For GRU NN, 10 MFCC features (F) are extracted from a window size of 40ms (l), with a stride of 40ms (s), which gives 250 features for 1 second of audio input. A GRU NN processes 250 features sequentially, ten per frame.

Figure 1.10: KWS system [14].

The output layer has 12 neurons, each representing on keyword/category. The first neuron correspond to "silence" (no speech is present in the recording) and

"unknown" (meaning that GRU NN is not able to classify the word into one of the twelve keywords). The remaining ten neurons represents the following keywords respectively: "yes", "no", "up", "down", "left", "right", "on", "off", "stop", "go".

To meet the requirement of implemented feature extractor, there is a real time requirement of 40ms to classify the features using GRU NN.

### 1.5 Thesis Goal

The objective of this master thesis is to examine the GRU algorithm and propose an efficient ASIC architecture capable of functioning as an GRU NN and can be implemented at the edge device. To achieve the mentioned goals, the thesis project is split into five tasks:

- 1. Behavioral model of GRU Network using Python and Matlab The first task is to implement a behavioral model of GRU network using numpy scientific library, and parameters from pretrained KWS model in Python and then construct a fixed-point model without using any predefined functions. Both the numpy and fixed-point models are functionally the same and are used as reference models.

- 2. Basic implementation of neural network on the xDSP Implement GRU NN inference on Oticon's audio DSP processor referred to as the xDSP. This implementation is carried out to obtain important metrics such as cycle count and energy dissipation, which are further used to compare performance of dedicated GRU engine (GRUE).

- 3. Wordlength exploration and hardware optimization Neural network accelerators with low latency and low energy dissipation are desirable for edge computing. Due to resource constraints, specifically the memory requirements, model size plays an important role. Model size refers to the network parameters (inputs, weights and biases). A common approach to reduce the model size is by reducing the precision of the parameters. However, reducing precision leads to trade-off between network accuracy and computation efficiency. Different ways of realising activation functions such as sigmoid and tanh are also explored to have efficient hardware resource use. Therefore, the purpose of this task is to investigate efficient algorithms to implement the activation functions and identify the appropriate wordlength for representing the NN parameters.

- 4. **Data reuse exploration** For RNNs, the fundamental operation unit is MAC which requires multiple memory access operations. This has an impact on both throughput and energy efficiency. Hence, we will exploit different data reuse techniques, to enhance the parallel execution of the algorithm, and minimize the data movement.

- A dedicated neural network engine Implementation of a dedicated accelerator and investigate the improvements in latency and energy dissipation.

# Gated Recurrent Unit - GRU

GRU is a variant of RNN that is capable of learning long term dependencies. GRUs have an internal mechanism called gates that regulate the flow of information and avoid the vanishing gradient problem. Two such mechanisms are update gate  $z_t$  and reset gate  $r_t$ . During training GRU learns the parameters for these gates. This chapter will explain how the GRU mechanism work and discuss how the output of a GRU cell can be used to classify the given input sequence.

## 2.1 A GRU cell

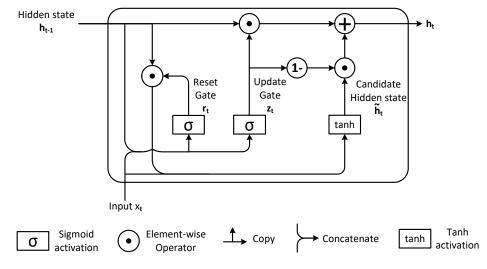

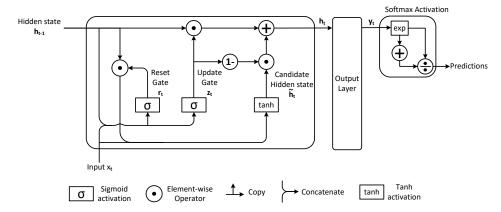

Figure 2.1: Gated Recurrent Unit (GRU).

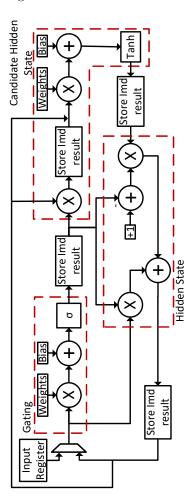

The architecture of a GRU cell used is depicted in Figure 2.1 and encapsulated in the following equations:

$$r_t = \sigma(x_t U_r + h_{t-1} W_r + b_r) \tag{2.1}$$

$$z_t = \sigma(x_t U_z + h_{t-1} W_z + b_z) \tag{2.2}$$

$$\tilde{h}_t = \tanh(x_t U_h + (r_t \odot h_{t-1}) W_h + b_h)$$

(2.3)

$$h_t = z_t \odot h_{t-1} + (1 - z_t) \odot \tilde{h_t}.$$

(2.4)

Each element of (2.1), (2.2), (2.3), (2.4) is summarized as follows:

- $r_t$  is the reset gate.

- $z_t$  is the update gate.

- $\tilde{h_t}$  is the candidate hidden state.

- U and W are weight matrix, and subscripts r, z, and h indicate that weight matrix belongs to reset gate, update gate and candidate hidden state, respectively.

- b denotes the bias vector and subscripts r, z, and h indicate that bias vector belongs to reset gate, update gate and candidate hidden state, respectively.

- $\bullet$   $\sigma$  denotes the sigmoid activation and tanh signify tangent hyperbolic activation

- ullet stands for element-wise vector multiplication also known as Hadamard product, and subscripts t denote the time step associated with the gate or unit.

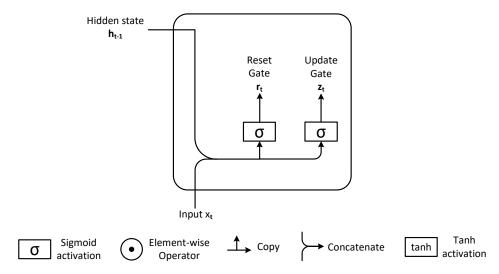

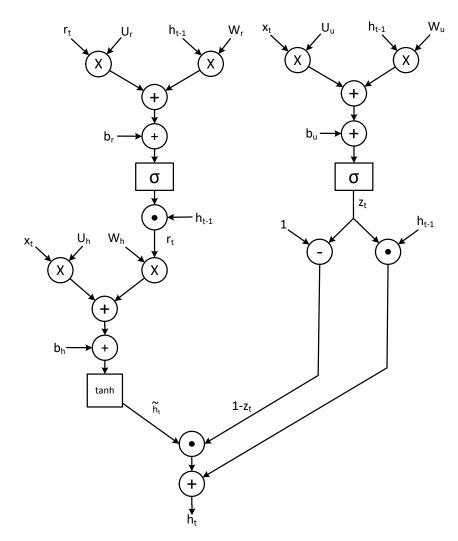

#### 2.1.1 Reset gate and Update gate

Through the use of reset  $r_t$  and update  $z_t$  gates, a GRU network can learn when the incoming information is important and when it should be integrated into the internal state of the cell (hidden state).

Figure 2.2: Reset and update gate in a GRU unit.

The reset gate  $r_t$  defines how to combine the new input  $x_t$  with the previous memory  $h_{t-1}$ , i.e., how much past information to forget. The update gate  $z_t$  allow

us to control how much hidden state  $h_t$  is a copy of the old state. The sigmoid function modulates the outputs of the reset and update gate to the interval [0,1].

Figure 2.2 illustrates the inputs for both the reset and update gate in a GRU unit, for current time step input  $x_t$  and the hidden state of previous time step  $h_{t-1}$ . The reset gate  $r_t$  and update gate  $z_t$  are computed as (2.1) and (2.2), respectively.

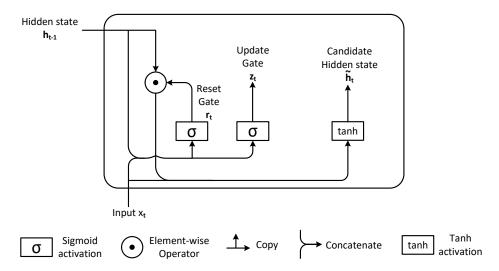

#### 2.1.2 Candidate hidden state

The candidate hidden state  $(h_{t-1})$  is computed as (2.3). The value of the reset gate  $r_t$  decides how much information from previous hidden state  $h_{t-1}$  to forget, denoted by  $r_t \odot h_{t-1}$ . Setting the value of  $r_t$  closer to one makes the influence of the previous hidden state  $h_{t-1}$  influence less and vice versa. Figure 2.3 illustrates the computational flow after including the candidate hidden state. The symbol  $\odot$  indicates the pointwise multiplication between the tensors.

Figure 2.3: Candidate hidden state computation in a GRU unit.

### 2.1.3 Hidden state

The hidden state,  $h_t$ , is computed as (2.4). The hidden state stores the information of the current GRU cell and passes this information down the network. The update gate  $z_t$  is used to decide how much information to gather from previous hidden state  $h_{t-1}$ , given by  $z_t \odot h_{t-1}$  and current memory content  $\tilde{h_t}$ , given by  $(1-z_t) \odot \tilde{h_t}$ . When  $z_t$  is set close to one,  $1-z_t$  will be close to zero, the model retains the previous information  $h_{t-1}$ , ignoring the information from  $x_t$  and skipping the timestep t in the dependency chain. On other hand, when  $z_t$  is close to zero, the new hidden state  $h_t$  approaches the candidate hidden state  $\tilde{h_t}$ . This helps to cope with the vanishing gradient problem and capture long-term dependencies better.

### 2.1.4 Output layer

A fully connected layer that takes the hidden state output  $h_t$  as input and delivers the number of classes in the network as output  $y_t$ . The output layer is computed by

$$y_t = h_t W_y + b_y. (2.5)$$

After the output layer, softmax activation is performed that converts the logits into probabilities that sum to one. Softmax activation given by (2.6), outputs a vector that represents the probability distributions of a list of potential outcomes the input sequence belongs. Logits are the raw prediction output by the output layer of GRU NN, before softmax activation takes place.

$$softmax(y_i) = \frac{e^{y_i}}{\sum_{j=1}^{n} e^{y_j}}$$

(2.6)

Figure 2.4 shows the complete structure of an GRU cell connected with a fully connected layer and a softmax function to deliver the expected probability results.

**Figure 2.4:** Structure of an GRU unit followed by a output layer and a softmax activation function.

## 2.2 Arithmetic Operations

In order to design an architecture that can efficiently function as an GRU neural network it is important to understand the sequence of arithmetic operations, their number and dependencies. This section goes through the arithmetic operations that formulate the entire algorithm.

Matrix to vector multiplications dominate the number of computations and parameters. For each matrix to vector multiplication, the input vector  $x_t$  of size m and the hidden state output vector  $h_{t-1}$  of size n are multiplied with weight matrices of size  $(m + n) \times n$ . That requires (m + n) times n MAC operations, which is equivalent to (m + n) times n multiplications and additions. Since this computation is repeated three times within the GRU computation for reset, update

and hidden state, these numbers are multiplied by three to obtain the total number of MAC operations for an GRU. However this calculation can be broken into smaller operations which can prove valuable when it comes to designing the control of the arithmetic units and exploring design space parallelism.

Every matrix to vector multiplication operation in the algorithm is followed by addition of bias. This requires n more additions. The result of bias addition is saturated by the sigmoid function for reset and update gates. However, for the candidate hidden state tanh function is used.

$$\sigma(x) = \frac{1}{1 + e^{-x}} \tag{2.7}$$

$$\tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}} \tag{2.8}$$

Using (2.7) and (2.8), the sigmoid and tanh function implementation requires division and an exponential function which would cost a lot in terms of area, energy and efficiency. In order to avoid this and also reduce execution time, these function can be approximated.

The hidden state  $h_t$  computes as (2.4), requires element-wise matrix multiplication. This operation requires additional n adders. Finally, the output layer also requires a matrix to vector multiplication operation increasing the number of such operations to four in the entire computation. More details on this will be discussed in the following chapters.

# 2.3 Data dependencies

It is crucial to determine data dependencies throughout the entire algorithm. Identifying data dependencies allows parallelization of operations in an ASIC implementation. Figure 2.5 shows data dependencies throughout arithmetic operations in the GRU algorithm. It can be observed that the gate operations  $r_t$ ,  $z_t$  operations can be computed in parallel, independent of each other. However the  $c_t$ ,  $h_t$  computations require the output of gate operations.

Figure 2.5: Data dependency graph of the GRU algorithm

# Wordlength and Hardware Optimization

GRUs have been successfully developed in broad range of applications including speech recognition [6], [15]. However, storage and computational complexity of these models have forced the majority of computations to be performed on high-end computation platforms or in the cloud. Storing of data such as weights and biases becomes an issue with growing size of the network. Our initial representation of GRU uses 32 bits for representing weights, biases and inputs. Such precision costs in terms of computation and storage complexity, model size and memory access operations such as load and stores.

Therefore, to cope with the computational and storage complexity, solutions such as weight and bias quantization are evaluated in this section along with the impact of reduced wordlength on performance, energy and accuracy. This step includes both high-level simulation, e.g., Python/Matlab, of GRU NN's and evaluation of their accuracy, as well as evaluating different algorithms to implement activation functions (sigmoid and tanh).

### 3.1 Data representation

An important consideration for implementing an NN is the arithmetic representation format. The difficulty is to achieve a balance between the need for numeric precision, which is important for network accuracy and speed, and the cost of hardware logic associated with increasing precision. While standard floating point representation (i.e 32 and 64 IEEE floating point formats) offer adequate precision, they require more resources than other area efficient arithmetic representations, such as less precise floating and fixed point formats.

Recent studies have empirically shown that 16-bit precision is sufficient to train DNNs without effecting model accuracy [16], [17], and [18]. Therefore, state-of-the-art hardware platform for training are now moving towards 16-bit floating point precision from traditional 32-bit floating point. This is due to reduced storage requirements associated with the reduced precision and high energy efficiency [19], [20]. Furthermore, research on using floating point 8-bit for training are also carried out, demonstrating two to four times speedup without compromising in accuracy [21].

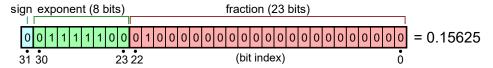

### 3.1.1 Floating-Point format

A floating point number is represented as  $\pm d_0.d_1d_2...d_{p-1}*\beta^e$ . Where  $\beta$  is called the base and e is called the exponent and p is the precision. For example, if  $\beta = 10$  and p = 4 then the number 0.2 is represented as  $2.000x10^{-1}$ . The exponent is said to have *biased* representation when the value of the exponent is

$$e = k - (\beta^{m-1} - 1), \tag{3.1}$$

where k is the value of the exponent bits interpreted as an unsigned integer and m is the number of bits in the exponent. The Floating-Point number is said to be normalized number when  $d_0$  is '1'.

One of the most common floating point formats is the IEEE floating point format (IEEE 754-1985 format [22]). In this format, for 32-bit precision numbers,  $\beta=2$ , p = 24, m = 8, and e = k - 127. The value of floating point number can be obtained as

$$\pm (d_0 + d_1 \beta^{-1} + \dots + d_{p-1} \beta^{-(p-1)}) \beta^e, (0 \le d_i \le \beta).$$

(3.2)

The bit representation of this format is illustrated in Figure 3.1.

Figure 3.1: Example layout of 32-bit floating point

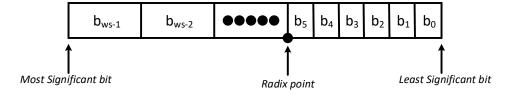

#### 3.1.2 Fixed-Point format

Figure 3.2 illustrates a Fixed-point representation. It contains two parts, one is the integer part which is  $b_{ws-1}$  to  $b_w$  and the other part is fractional part which is  $b_3$  to  $b_0$ . If the base of the Fixed-Point number is  $\beta$  and it is a positive number, the decimal equivalent value can be calculated by

$$b_{ws_1}\beta^{ws-5} + \dots + b_4 + b_3\beta^{-1} + b_2\beta^{-2} + b_3\beta^{-3} + b_4\beta^{-4}.$$

(3.3)

Figure 3.2: Format of a Fixed-Point Number

If the base of Fixed-Point number is 2, the value is determined by which number representation that is used.

- Sign bit representation ranges from  $-(2^{(k-1)}-1)$  to  $(2^{(k-1)}-1)$ , for K bits.

- Signed representation ranges from  $-(2^{(k-1)})$  to  $(2^{(k-1)}-1)$ , for K bits.

Generally 2's complement representation is preferred because of unambiguous property and more convenient arithmetic operations.

Wordlength and number representation of GRU model parameters such as weights, biases, inputs, has a big impact on the overall performance of the GRU inference. A larger wordlength increases the model size, and effects the efficient use of HW resources. By reducing the parameters, word length, more parameters can be read through the same memory interface in a single cycle, thus, decreasing the memory wordlength requirements. Another motivation is that reduced wordlength of the parameters can enable a higher number of operations for almost same hardware costs, since lower precision multipliers require less silicon area and power. The drawback of using a smaller wordlength is potential accuracy decrease of the implementation, explained in following sections.

A reduced floating-point representation could provide lower wordlength parameters with close to no impact on accuracy, since it has a greater dynamic range and precision than fixed-point. However, the drawback of using an equivalent floating-point is that the energy cost increases up to 10 times [23]. Floating-point can provide a higher range for the same wordlength. There is significant amount of research that suggests that for majority of applications, 8-bit fixed-point or lower precision is sufficient, specifically for inference purposes [23].

Another advantage of using fixed-point representation is that the adders and multipliers occupy less area and are more power-efficient since the same adders and multipliers as for integer operations can be reused. Quantizing the fixed-point by powers of two is also considerably cheaper to do than the other touched upon representations, since it only requires arithmetic shift operations.

Our experiments are focused on 16 bit fixed point implementation, described in detail in the following section in terms of higher-level simulations using Matlab and Python.

### 3.2 Role of the Activation Function

Neural network activation functions are a crucial component of deep learning. Activation functions determine the output of a deep learning model, its accuracy, and also the computational efficiency of training a model. Activation functions are mathematical equations that determine the output of a neural network. The function is attached to each neuron in the network, and determines whether it should be activated ("fired") or not, based on whether each neuron's input is relevant for the model's prediction[24]. Besides restricting outputs to a certain range, activation functions break the linearity of a neural network, allowing it to learn more complex functions than linear regression. The weight multiplication at each layer is a linear transformation. Adding the bias vector makes it an affine transformation. Thus, a many layer neural network would reduce to a single layer network in the absence of non-linear activation functions [25], [26].

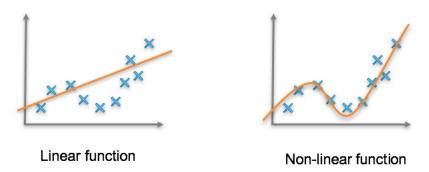

Figure 3.3: Feature selection Linear vs Non linear [27].

A linear equation is simple to resolve, but it is restricted in its complexity and has less power to learn complex functional mappings from data. Thus with an non linear activation function, neural network will be able to learn and model other complicated kinds of data such as images, videos, audio, speech, etc. Also, another important feature of an activation function is that it should be differentiable to perform backpropagation optimization strategy during training [19].

### 3.3 Activation Function exploration

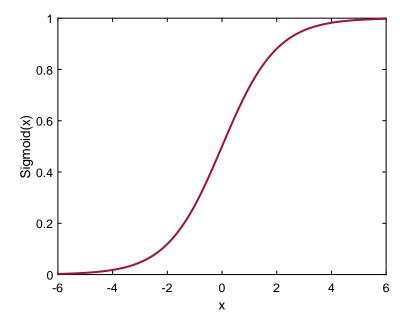

GRU network uses two activation functions, sigmoid function and tanh function . Sigmoid outputs range from 0 to 1, and are often interpreted as probabilities, as shown in Figure 3.4 and is given by (3.4).

$$\sigma(x) = \frac{1}{1 + e^{-x}} \tag{3.4}$$

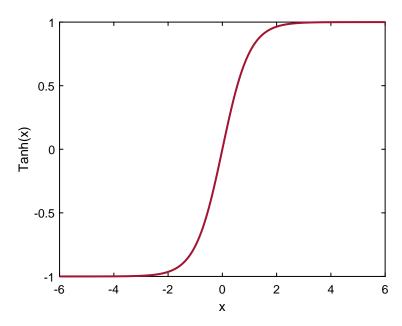

The tanh function is simply a scaled and shifted version of the sigmoid function, such that its outputs range from -1 to 1, as shown in Figure 3.5. The relationship between sigmoid and tanh is given by (3.5).

$$\tanh(x) = 2 \cdot \sigma(2 \cdot x) - 1 = \frac{e^x - e^{-x}}{e^x + e^{-x}}$$

(3.5)

Due to its symmetric property it's enough to calculate the activation function only for positive arguments x. For negative values of x it can be calculated using

$$F(-x) = 1 - F(x). (3.6)$$

Gated Neural network algorithm uses nonlinear activation functions sigmoid and the hyperbolic tangent (tanh) function to flatten the vectors within range [0,1] and range [-1,1]. Since the reset and update in GRU neural network outputs a value between 0 and 1, it can either let no flow or complete flow of information. The sigmoid function is used as a gating function for the two gates (reset and update gate).

Figure 3.4: Sigmoid function.

Figure 3.5: The hyperbolic tangent function (tanh).

To overcome the vanishing gradient problem, a function whose second derivative can sustain for a long-range before going to zero is required. Since tanh has the above property, it is used to calculate the candidate hidden state value [28].

Straightforward implementation of the nonlinear activation functions in hardware is very expensive in terms of hardware, as these equations require division and exponent function [29]. Different methods of approximation are used for the hardware implementation of nonlinear activation functions: look up table (LUT), Taylor transformation, piecewise linear approximation, fast sigmoid and tanh approximation.

When decomposing a taylor series, many multiplications and additions need to be performed, therefore, this method is not well suitable for implementation in hardware [30]. LUT is the most commonly used approach to implement the sigmoid and tanh functions. In this approach, the function curve is divided into different segments and the corresponding output values for each input segment are stored in a table. Only one memory access time is required to get the function outputs, thus, LUT is the fastest implementation as compared to other techniques. However, in order to get better accuracy, large storage space are required for LUT implementation [29].

# 3.3.1 Piecewise linear approximation of the sigmoid function (PLAN approximation)

In this method, the approximation is performed using

$$f(x) = \begin{cases} 1 & x \ge 5\\ 0.03125 * x + 0.84375 & 2.375 \le x < 5\\ 0.125 * x + 0.625 & 1 \le x < 2.375\\ 0.25 * x + 0.5 & 0 \le x < 1. \end{cases}$$

(3.7)

Calculations need to performed only for positive input data x. For negative input data x, the sigmoid function is calculated using (3.6). For implementation in hardware the real numbers are converted to integers using multiplication by  $2^{10}$  as

$$f(x) = \begin{cases} 1024 & |x| \ge 5120\\ 2^{-5} \cdot |x| + 864 & 2432 \le |x| < 5120\\ 2^{-3} \cdot |x| + 640 & 1024 \le |x| < 2432\\ 2^{-2} \cdot |x| + 512 & 0 \le |x| < 1024. \end{cases}$$

(3.8)

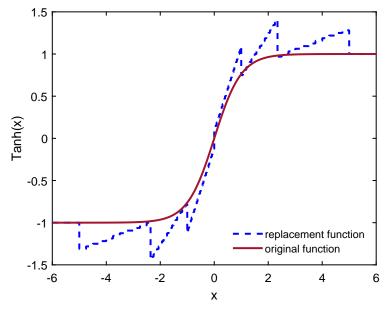

This expression can be implemented in hardware with only shifters and adders, with no multipliers needed. Figure 3.6 and Figure 3.7 illustrates the comparison of sigmoid and tanh approximation, respectively.

The functions are tested by passing inputs ranging from -6 to 6 in steps of 0.001. The sigmoid PLAN approximation has relative error of 0.032 and tanh has relative error of 0.151. Since PLAN approximation algorithm used is optimised for sigmoid approximation, approximating of tanh using (3.5) introduces error (spikes) as shown in Figure 3.7.

Figure 3.6: PLAN approximation of sigmoid function.

**Figure 3.7:** PLAN approximation of hyperbolic tangent function (tanh).

#### 3.3.2 Taylor Series Implementation

The Taylor series expansion of the sigmoid and hyperbolic tangent function are computed as

$$\sigma(x) = \frac{1}{2} + \frac{x}{4} - \frac{x^3}{48} + \frac{x^5}{480} - \dots$$

(3.9)

$$\tanh(x) = x - \frac{x^3}{3} + \frac{2x^5}{15} - \frac{17x^7}{315} + \dots$$

(3.10)

Implementing these polynomials is not feasible for hardware as it is complex and costly in terms of area. Therefore, this approach was not evaluated.

## 3.3.3 Second order curve approximation

In this method, the approximation is performed using

$$f(x) = \begin{cases} 1024, & x \ge 4096 \\ -2^{-15} \cdot x^2 + 2^{-2} \cdot x + 512 & 0 \le x < 4096. \end{cases}$$

(3.11)

Calculations must be performed only for positive input data x. For negative input data x, the sigmoid function is calculated using (3.6). For implementation in hardware the real numbers are converted to integers using multiplication by  $2^{10}$ .

$$f(x) = \begin{cases} 1, & x \ge 4 \\ -0.03125 \cdot x^2 + 0.25 \cdot x + 0.5 & 0 \le x < 4. \end{cases}$$

(3.12)

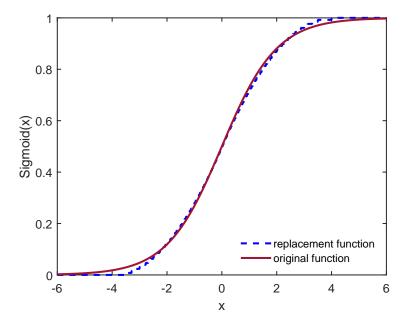

Figure 3.8: Second Order approximation of sigmoid function

Inputs in the range (-6, 6) are divided in steps of 0.01. In this range the maximum and average relative error of approximation of sigmoid function were 0.029 and 0.020, respectively. The hyperbolic tangent function is a scaled and shifted version of sigmoid function, its implemented using (3.5).

**Figure 3.9:** Second Order approximation of hyperbolic tangent function (tanh).

The maximum error and average relative error of approximation of tanh function were 0.357 and 0.121, respectively. Implementation of second-order polynomial on HW requires one multiplier, shift registers, and adders.

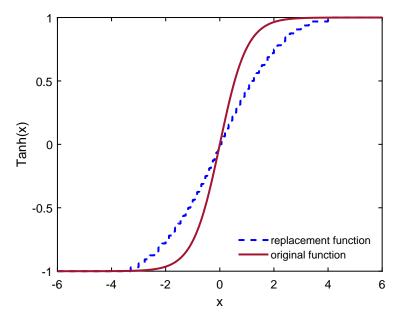

#### 3.3.4 Fast Sigmoid and Hyperbolic Tangent function

Sigmoid function can be approximated as

$$f(x) = \begin{cases} 1 & x \ge 4\\ (0.5 * x)/(1 + x) + 0.5 & 0 \le x < 4\\ 1 - ((0.5 * x)/(1 + x) + 0.5) & -4 \le x < 0\\ 0 & x < -4. \end{cases}$$

(3.13)

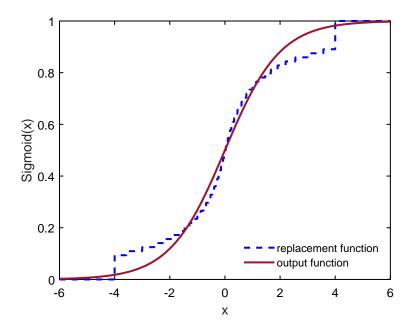

From (3.5), hyperbolic tangent function can be written as

$$f(x) = \begin{cases} 1 & x \ge 4 \\ 2 * ((0.5 * x)/(1 + x) + 0.5) - 1 & 0 \le x < 4 \\ 2 * (1 - ((0.5 * x)/(1 + x) + 0.5)) - 1 & -4 \le x < 0 \\ 0 & x \le -4. \end{cases}$$

(3.14)

$$f(x) = \begin{cases} 1 & x \ge 4\\ 2*((0.5*x)/(1+x) + 0.5) - 1 & 0 \le x < 4\\ 2*(1 - ((0.5*x)/(1+x) + 0.5)) - 1 & -4 \le x < 0\\ 0 & x < -4. \end{cases}$$

(3.15)

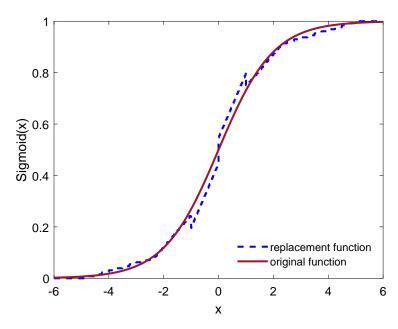

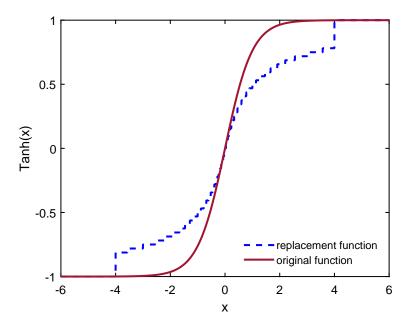

Figure 3.10 and Figure 3.11 illustrates the comparison of original and replacement functions for sigmoid and tanh activation, respectively. The average relative error of sigmoid and tanh function were 0.07 and 0.17, respectively.

Figure 3.10: Fast sigmoid function approximation

The fast sigmoid, and fast tanh function were implemented using adders, shifters, and division operation can be performed using CORDIC division algorithm . A CORDIC division algorithm is based on re-writing the equation z = x/y into the form x - yz = 0 [31]. The expanded series representation of z is expressed as (3.16), which can be simplified to (3.17).

$$x - y * \sum_{i=1}^{B} a(i)2^{-i} = 0$$

(3.16)

$$x - \sum_{i=1}^{B} a(i)(y2^{-i}) = 0 (3.17)$$

Figure 3.11: The Fast hyperbolic tangent function approximation

Using (3.17), the quotient z is estimated one bit at a time by driving x to zero using right shifted versions of y. If the current residual is positive, the  $i^{th}$  bit in z is set. Likewise if the residual is negative, the  $i^{th}$  bit in z is cleared.

```

divide(x,y){

for (i=1; i=<B; i++){</pre>

2

3

if (x > 0)

x = x - y*2^(-i);

4

= z + 2^{(-i)};

5

6

x + y*2^{(-i)};

z - 2^{(-i)};

8

9

return(z)

10

11 }

```

Listing 3.1: Cordic algorithm 1 [31].

While x may be either positive or negative, y is always assumed to be positive. As a result, the division algorithm is only valid in two quadrants. Also, if the initial value for y is less than the initial value for x it will be impossible to drive the residual to zero. This means that initial y value must always be greater than x, resulting in domain of 0 < z < 1. The algorithm may be modified as follows for four quadrant division with -1 < z < 1.

```

divide_4q(x,y){

for (i=1; i=<B; i++){

if (x > 0)

if (y > 0)

```

```

y*2^(-i);

5

6

2<sup>(-i)</sup>;

else

+ y*2^{(-i)};

2^(-i);

9

z

else

(y > 0)

if

11

x = x + y*2^(-i);

12

= z - 2^{(-i)};

13

14

= x - y*2^(-i);

= z + 2^{(-i)};

}

17

return(z)

19

}

```

Listing 3.2: Cordic algorithm 2 [31].

Since multiplications are all powers of 2, they are realized using shift operations; no actual multiplier is needed. Hence, it is well suited to hardware implementation, simplifying overall hardware complexity.

Due to the nature of fast sigmoid given by (3.14), the value of y is never less than the initial value of x. Therefore, CORDIC algorithm mentioned in Listing 3.1 was used. The fast sigmoid and fast tanh approximation technique has been chosen for implementation for this thesis.

# 3.4 Quantization Experiments

The motivation behind quantization and wordlength optimization is that NNs are typically trained with floating-point weights and activations. In various cases, quantizing a model trained with a 32-bit floating-point into eight-bit fixed-point, without any re-training, can result in a moderately low accuracy loss, which can be improved by further fine-tuning [32].

Quantizing a model without re-training is referred to as post-training quantization. However, publications have shown that there are cases where post-training quantization to eight-bit fixed-point effect accuracy [33]. Smaller models such as MobileNet does not respond well to post-training quantization, likely due to their smaller representational capacity. As discussed above, fixed-point weights are sufficient to run NNs without any significant accuracy loss. Edge devices have memory constraints that motivate the need for quantization of 32-bit floating-point weights and biases to eight-bit fixed-point weights and biases. Also, using an eight-bit fixed-point consumes four times less overall bandwidth and the model size compared to 32-bit floating-point. Furthermore, fixed-point integer operations are more energy efficient than floating-point operations as shown in Table 3.1.

**Table 3.1:** Energy and area comparison [34].

| INT8 Operation | Energy Saving vs FP32 | Area Saving vs FP32 |

|----------------|-----------------------|---------------------|

| Add            | 30x                   | 116x                |

| Multiply       | 18.5x                 | 27x                 |

A basic quantization of fixed-point numbers is shifting the values until the MSBs fit within the specified word length. The range of fixed-point is determined by  $-2^{i-1}$  to  $2^{i-1} - 2^{-f}$ . For instance, if the wordlength is 16 bits and the number of both integer i and the fractional f bits is eight, its range is -128 to 127. If the number lies out side this range, it is truncated by a specific number of positions. If the number is very small, e.g., 0.00034 and cannot be represented by the available fractional bits in fixed-point representation, number get eradicated to zero. Therefore, the chosen number of integer and fractional bits significantly influences the outcome, and it should be adjusted to fit the specified dataset. For values of weights  $w \in [0, 1]$ , reserving most of the fractional bits during quantization gives the highest precision.

#### 3.4.1 High-level model (Accuracy evaluation)

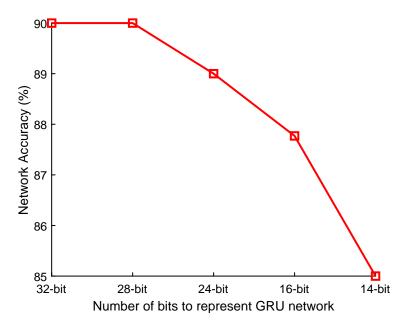

Implementing pretrained KWS GRU NN with 32-bit parameters is not efficient approach. To compress the neural network model, the number of bits required per parameter (weights and biases) was reduced by truncating the fraction bits. The MATLAB model of GRU fixed point implementation was used to perform experiments. The accuracy of the fixed-point model remained constant untill 28-bit representation, dropped by one percentage unit at 24-bit representation, and two percentage unit at 16-bit representation as illustrated in Figure 3.12. This section will focus on 16-bit representation and below. The accuracy of the fixed-point model is compared with accuracy of 32-bit full-precision floating-point implementation having a accuracy of 91%. Within 16-bit fixed point representation, the most accurate results were achieved with the Q10.6 format. Since, input ranges from -247 to +90, minimum nine integer bits are required.

**Table 3.2:** Accuracy of GRU network with different precision.

| GRU network precision | Accuracy |

|-----------------------|----------|

| 32-bit floating point | 91.1%    |

| 32-bit fixed-point    | 90%      |

| 28-bit fixed-point    | 90%      |

| 24-bit fixed-point    | 89%      |

| 16-bit fixed-point    | 87.7%    |

| 14-bit fixed-point    | 80%      |

**Figure 3.12:** Network accuracy for GRU network with different precision bits to represent the network.

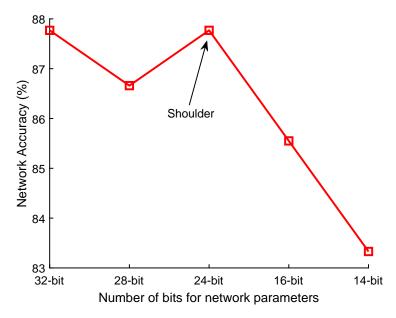

After selecting a 16-bit fixed-point representation for GRU network, a second experiment was conducted where network parameter (weights and biases) bits were truncated from 16-bit to 6-bit representation. The accuracy of the network remained constant until 10-bit representation, a shoulder was noticed at 8-bit representation as illustrated in Figure 3.13. Also, fluctuation in the network accuracy was observed just before the shoulder. To reduce the precision of the network, fractional bits are truncated. Table 3.3 shows the accuracy of GRU NN with varying network parameter precision.

**Table 3.3:** Accuracy of 16-bit GRU network with different precision bits for parameters.

| Network parameter precision | Accuracy |

|-----------------------------|----------|

| 10-bit fixed-point          | 87.7%    |

| 9-bit fixed-point           | 86.6%    |

| 8-bit fixed-point           | 87.7%    |

| 7-bit fixed-point           | 85.5%    |

| 6-bit fixed-point           | 83.3%    |

Since the accuracy was identical with eight bits as network parameter precision, further experiments were conducted using 16-bit GRU network with 8-bit parameter precision.

**Figure 3.13:** Network accuracy for different network parameter precision for fixed-point implementation of 154x154x154x12 topology.

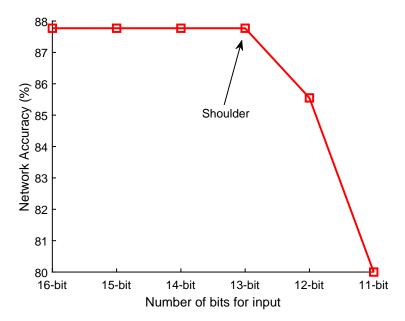

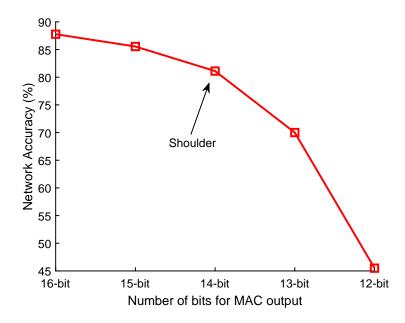

Figure 3.14 depicts the accuracy plot for different input precision. Figure 3.15 illustrates the accuracy plot when the MAC output precision is kept same as input precision, shoulder was noticed at 13-bit representation. MAC output precision here refers to the wordlength used for truncating the output of the MAC unit. Table 3.4 and Table 3.5 show the accuracy of various combinations of input and MAC output precision used.

The shoulder in the graph refers to a point, after which there is a sudden drop in the accuracy.

Table 3.4: Classification accuracy for different input data precision.

| Input precision    | Accuracy |

|--------------------|----------|

| 16-bit fixed-point | 87.7%    |

| 15-bit fixed-point | 87.7%    |

| 14-bit fixed-point | 87.7%    |

| 13-bit fixed-point | 87.7%    |

| 12-bit fixed-point | 85.5%    |

| 11-bit fixed-point | 80%      |

**Figure 3.14:** The figure shows the accuracy for different input data precision.

When the MAC output precision was truncated with the same precision as input, shoulder was observed at 14-bit representation. From the above experiments, it can be concluded that reducing the MAC output precision leads to accuracy loss, and using 16-bit fixed point network with 8-bit weights and biases produced the best accuracy at slightly higher hardware cost.

**Table 3.5:** Classification accuracy for different input precision based KWS Tensorflow dataset.

| Network precision  | Accuracy |

|--------------------|----------|

| 16-bit fixed-point | 87.7%    |

| 15-bit fixed-point | 85.5%    |

| 14-bit fixed-point | 81.1%    |

| 13-bit fixed-point | 70.0%    |

| 12-bit fixed-point | 45.5%    |

**Figure 3.15:** The figure shows the accuracy for different input data precision and MAC output precision at Q10.6 format.

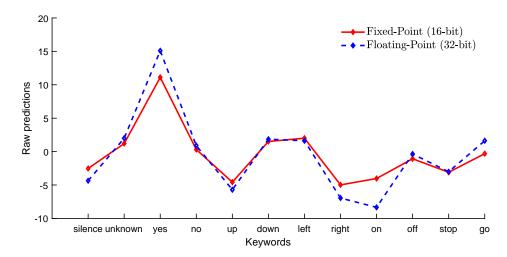

Figure 3.16 illustrates the raw predictions with the chosen wordlength, i.e., 16-bit for representing GRU fixed-point model and eight-bit for representing weights and biases. All the experiments are carried out without retraining the network after performing the truncation. Findings might be different if the network is re-trained after performing the truncation of network parameters, which might recover some of the accuracy loss introduced due to truncation.

**Figure 3.16:** Raw prediction of the fixed-point implementation (red line) against the 32-bit floating-point implementation (blue line).

# **xDSP** Implementation

The xDSP is a 3-stage pipeline processor optimized for DSP applications with multiple data-paths, register files, parallel instructions and custom functional units. The sections below provide a high-level overview of the architecture of the xDSP processor.

## 4.1 Register Files

The XDSP contains three register files: one for the integer datapath (R), one for the scalar datapath (S), and one for the vector datapath (V). To allow a greater flexibility, the scalar datapath also has access to the R register file, and the vector datapath has access to the R and S register files.

Table 4.1: Register files.

| Register file  | Data type | Integer size               | Fixed point format |

|----------------|-----------|----------------------------|--------------------|

| $\overline{R}$ | Integer   | 16 bits                    | N/A                |

| S              | Scalar    | 24 bits                    | $\{5.19\}$ bits    |

| V              | Vector    | $4 \times 24 \text{ bits}$ | 4 x {5.19} bits    |

# 4.2 Datapath

The XDSP contains the following datapaths:

- 1. Integer datapath supports arithmetic, logic, shift, and compare instructions. Also handles the program control flow. This datapath can only access the 16-bits R register file.

- Scalar datapath is for data processing in both fixed point and integer format. This datapath also supports more complex operations specifically targeted to DSP applications and allows access to both R and S register files.

- 3. Vector datapath can process four scalars in parallel. This datapath can access all the register files.

4. Multicycle datapath - for operations that cannot be completed in a single clock cycle.

The main bottleneck for processing NN is the memory access. Each MAC operation requires three memory reads (input, weight and bias). Hence to reduce the memory access operations and increase the speed of computation the vector datapath is used.

## 4.3 Memory interfaces

The xDSP utilizes a 24-bit data bus for scalar/integer datatypes and 96 bit data bus for vector data. The memory can be accessed with a 16-bit address, which are stored as sign extended 24 bit variables. All of the vector data memory accesses are performed as single cycle operations, while the scalar memory accesses depend on the Network-on-Chip (NoC) arbitration delay.

The program memory consists of variable length instructions (8/16/24/32 bit) and is packed in 8-bit blocks. The processor uses a 16-bit address format. Hence it can address a maximum 64 kB of program memory. The program memory interface is a 64-bit data bus and uses a 128-bit program memory cache for instruction fetching.

## 4.4 Design considerations

The XDSP uses 24 bits to represent fixed point data. To implement KWS GRU model, 230KB of memory storage is required to store the network parameters, inputs, weights and biases.

The data memory size available on XDSP is limited, which constraints the size of NNs that can be run on the XDSP. Thus, three small GRU NN with 4, 20, and 40 neurons in each layer were chosen for implementation on XDSP. These network were trained using the Python script provided with the KWS model. The trained smaller models occupy 1.5kB, 7KB, and 21KB of the data storage available on XDSP, respectively. Table 4.2 shows the number of entries required by GRU NN parameters (inputs, weights and biases).

Table 4.2: Number of entries for different parameters in GRU NN.

| Network parameter | Entries   |            |            |             |

|-------------------|-----------|------------|------------|-------------|

|                   | 4 neurons | 20 neurons | 40 neurons | 154 neurons |

| Weights           | 180       | 2040       | 6480       | 77616       |

| Biases            | 15        | 72         | 132        | 474         |

| Inputs            | 10        | 10         | 10         | 10          |

| Total             | 205       | 2122       | 6622       | 78100       |

The xDSP has a separate datapath for vectorized data, see section 4.2. To use this feature, weights and initial inputs are loaded into the memory as matrices in the vectorized format such that four multiplications are executed in parallel.

### 4.5 Implementation

This section introduces basic concepts that are needed in order to understand design decisions, wordlength used, and bias alignment in registers.

#### 4.5.1 Multiply-accumulate operation

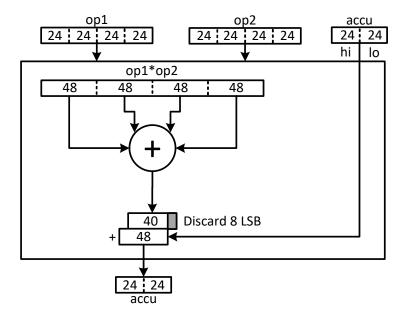

The Vector double precision MAC functional unit available on XDSP is used for implementing matrix multiplication operation performed in different layers of GRU network. This function executes in two clock cycles.

The MAC operation multiplies two input vectors, adds the results together and then stores the sum in an accumulator. The accumulator uses a vector type and is interpreted as two custom fixed-point values, *high* and *low*, stored in either the high (accu[3:2]) or low (accu[1:0]) part of the vector. Each part holds the accumulated values in extended precision of 48 bits (Q18.30). The accumulated value has 8 guard bits, which also means that the lowest 8 bits are discarded after multiplication.

The hi and lo in Figure 4.1, return data in Q18.6 format, and Q0.24 bit format, respectively. Together, they represent a number in Q18.30 format. The result of the MAC operation in extended precision (Q18.30) is then scaled back to the Q5.19 format.

Figure 4.1: MAC unit.

With this MAC unit, only one neuron output can be computed at a time as the four multiplication results (and the subsequent ones) are added together.

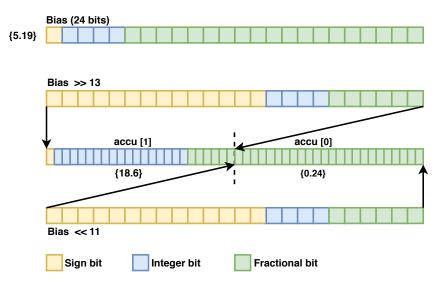

### 4.5.2 Bias alignment

As mentioned in the above section since computations are executed for one neuron at a time, bias values are loaded from the memory as regular scalar values in Q5.19 format unlike weights and initial inputs. Hence, loading the bias cannot exploit the advantages of the vectorized data format.