# Study of Monitoring Circuitry for Ageing in FPGAs

Pengxiang Cheng pe8244ch-s@student.lu.se

Department of Electrical and Information Technology Lund University

> Supervisor: Erik Larsson, LTH erik.larsson@eit.lth.se

Supervisor: Farrokh Ghani Zadegan, Ericsson

Examiner: Pietro Andreani, LTH pietro.andreani@eit.lth.se

December 2, 2021

© 2021 Printed in Sweden Tryckeriet i E-huset, Lund

# Abstract

Along with the down-scaling of CMOS technology, ageing has become one of the most important reliability challenges in CMOS devices. Ageing is defined as degradation in certain device characteristics such as delay, which can result in failure. Field Programmable Gate Arrays (FPGAs) are typically the first among the CMOS devices to adopt the latest technology. It is, therefore, crucial to tackle ageing in FPGAs. As design-time-only techniques might prove insufficient in providing enough margins for future CMOS technology nodes, it becomes important to also monitor for the ageing degree to ensure the correct functionality.

This thesis aims to review previous work to understand ageing and find effective ageing monitoring methods for FPGAs, in terms of the ability to detect degradation of the fabric resources with high accuracy and high precision. A comprehensive survey of previous methods is conducted, reporting a comparison of monitors in detail and comparing their pros and cons. Based on the survey, we perceived the process/performance variation mapping method by use of ring-oscillators (the so-called PV mapping) to have great potential and enhanced the existing PV mapping method by (1) introducing sensors based on new ring-oscillator types that cover significantly more hardware resources, and thus enhance the monitoring coverage, (2) pushing the number of uniform sensors (each sensor being comprised of a ring oscillator and a frequency counter) by the use of carefully developed placement constraints to almost 80% of the maximum theoretically possible number of sensors of the suggested type, and (3) designing extra ring-oscillator types and circuitry for gaining more insights into the precision and coverage of the proposed performance variation (PV) mapping method. The PV mapping method was applied to 20 Digilent Nexys4 boards, featuring a 28nm XILINX ARTIX 7 XC7A100T FPGAs to validate that the proposed method is capable of detecting delay differences among uniformly shaped sensors on the same device, and for each sensor among multiple boards. In addition, the precision and accuracy of the proposed method are reported.

# Acknowledgments

Firstly, I would like to appreciate my supervisors Farrokh Ghani Zadegan at Ericsson Lund and Erik Larsson at Lund University, for their patient and tireless help. Especially, Farrokh Ghani Zadegan has guided me to solve techniques problems and given me continuous help during our thesis work. Erik Larsson, I would like to thank him for providing constructive advice. Moreover, thank you for proofreading all my drafts.

Secondly, I also want to thank my line manager, Mikael Lostedt at Ericsson Lund for providing me this opportunity and for his supports.

Thirdly, I am grateful to my friends, Zilin Zhang and Yu Zhu for their practical advice in my debugging time and their cheering through the tough times. Additionally, a great thanks to my friend, Marcus Sandberg for his contribution to our IC project when I am busy doing the thesis.

Finally, I would like to express my gratitude to my family for their understanding and support.

# Popular Science Summary

We use electronic systems everyday as they are present in computers, phones, home appliances, cars, etc. Electronic systems are made of small components called chips, and the chips are made of up to billions of nano-scale components called transistors, which are connected with nano-scale wires. The transistors and wires inside a chip are subject to a phenomenon called ageing, which results in the degradation of their functionality. For example, an aged chip cannot perform as fast as when it was new, resulting in malfunctioning. Up until now, to avoid such degradation due to ageing, the systems designers added a lot of performance margin so that even if the chip is affected by ageing, it could still continue working with the intended performance for the intended life-cycle. However, since in the future, due to the need for more performance and lower power consumption, more and smaller transistors should be used. Designing with such extra margins for future technology is going to be too costly. One solution, would be to monitor the chips for ageing and take action, such as replacement, before the chip malfunctions. For monitoring, typically, designers need to integrate monitoring sensors with the circuits inside the chips, which takes some design effort and also requires resources in terms of transistors and wires.

This thesis work looks into a class of chips called FPGAs. FPGAs are programmable, meaning that after they are manufactured, one can program their internal circuitry many times to carry out different functions. In this thesis work, we take advantage of this programmability to perform monitoring for ageing. The advantage with this method is that the designers can save both design efforts and programmable resources by avoiding integrating the monitoring sensors directly into their designs, and instead design one program just for monitoring.

We place a certain number of sensors on the FPGA board, and the frequency reported by the sensor is used as the indicator for ageing. If the sensor frequency is lower than the minimum acceptable value, the chip is judged to have aged too much. We will periodically measure and collect the results of the sensors to monitor aging by observing whether they are close to the minimum acceptable value. We have performed extensive experiments with our monitoring method, and have shown that with our method it is possible to detect subtle frequency differences both between sensors inside the same FPGA, as well as between the same sensor location on different FPGAs. Based on this, we expect that this method will also be capable of detecting ageing (indicated by gradual changes in the frequencies reported by the sensors) and predicting malfunctions when sensor data is collected periodically throughout the lifetime of an FPGA.

# Table of Contents

| 1           | Introdu  | ction                                | 1  |

|-------------|----------|--------------------------------------|----|

| 1.1         | Motiva   | ation                                | 1  |

| 1.2         | Goal a   | nd Objectives                        | 2  |

| 1.3         |          | Organization                         |    |

|             |          |                                      |    |

| •           | <b>.</b> |                                      | 2  |

|             | •        | ound                                 |    |

| 2.1         |          | Overview                             |    |

|             | 2.1.1    | CLBs                                 |    |

|             | 2.1.2    | Switch Matrix                        |    |

|             | 2.1.3    | Other Components                     |    |

| 2.2         | Degrae   | dation Mechanisms                    |    |

|             | 2.2.1    | Transistor Degradation Mechanisms    | 7  |

|             | 2.2.2    | Interconnects Degradation Mechanisms | 8  |

|             |          |                                      |    |

| 3           | Litorati | ure Survey                           | 11 |

| <b>3</b> .1 |          | nsor                                 |    |

| 5.1         | 3.1.1    | Performance Variation Analysis       |    |

|             | 3.1.2    | Ageing Effect Analysis               |    |

|             |          |                                      |    |

|             | 3.1.3    | Temperature Monitoring               |    |

|             | 3.1.4    | Counter                              |    |

| 3.2         |          | nsor                                 |    |

|             | 3.2.1    | Performance Variation Analysis       |    |

|             | 3.2.2    | Ageing Monitoring.                   | 16 |

| 3.3         |          | nsor                                 |    |

| 3.4         | Compa    | arison of the Three Types of Sensors | 18 |

|             |          |                                      |    |

| 4           | The Pr   | oposed PV Mapping Method             | 23 |

| 4.1  |         | cture of the Proposed Method.        |    |

|------|---------|--------------------------------------|----|

| 4.2  | RO Ser  | sor Design and Deployment            | 25 |

|      | 4.2.1   | Ring Oscillator                      | 25 |

|      | 4.2.2   | Frequency Counter                    | 27 |

|      | 4.2.3   | Sensor Deployment                    |    |

| 4.3  | Design  | and Operation of the Proposed Method |    |

| 4.4  | Maxim   | um Measurement Error                 | 32 |

| 4.5  | Data R  | etrieval and Analysis                | 34 |

| 4.6  | Conclu  | sion                                 | 34 |

| 5    | Experim | ental Setup and Results              | 35 |

| 5.1  |         | pping Using the Two Large Sensors    |    |

|      | 5.1.1   | Simulation Results                   |    |

|      | 5.1.2   | Measurement Results                  |    |

|      | 5.1.3   | Discussion                           |    |

| 5.2  |         | gh vs RO low                         |    |

| 5.3  |         | cation                               |    |

| 0.0  | 5.3.1   | Simulation and Measurement           |    |

|      | 5.3.2   | Discussion                           |    |

| 5.4  | Multipl | e Consecutive Measurements           |    |

|      | 5.4.1   | Architectural Changes                |    |

|      | 5.4.2   | Measurement Results                  |    |

|      | 5.4.3   | Discussion                           |    |

| 6    | Conclus | ions and Future Work                 | 53 |

| 6.1  |         | sions                                |    |

| 6.2  |         | Work                                 |    |

| Refe | erences |                                      | 55 |

| Арр  | endix A | FPGA Board Information               | 59 |

| Арр  | endix B | PV Maps                              | 61 |

# List of Figures

| 2.1  | An abstracted FPGA architecture (island-style) [1], Copyright © 2013, IEEE                     |

|------|------------------------------------------------------------------------------------------------|

| 2.2  | Arrangement of Slices within the CLBs [2]                                                      |

| 2.3  | The BLE structure                                                                              |

| 2.4  | The CLB structure                                                                              |

| 2.5  | N-inputs LUT                                                                                   |

| 2.6  | Two-input LUT                                                                                  |

| 2.7  | Schematic of the Carry Chain [2]                                                               |

| 2.8  | Degradation Mechanisms [3]                                                                     |

| 3.1  | Traditional Ring Oscillator Structure                                                          |

| 3.2  | Basic principle of delay characterization circuits with shadow register [4] 15                 |

| 3.3  | Schematic diagram of the aging sensor $[5]$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.16$ |

| 3.4  | Basic principle of the TP sensor [6]                                                           |

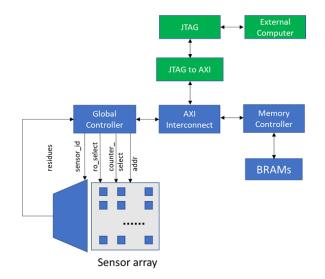

| 4.1  | Overview of proposed technique                                                                 |

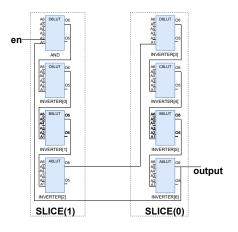

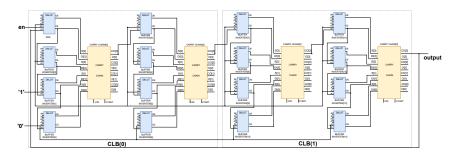

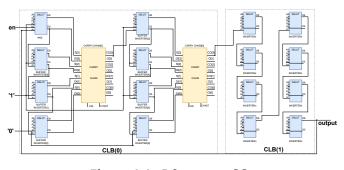

| 4.2  | RO_8                                                                                           |

| 4.3  | RO_8_CC2_8_CC2                                                                                 |

| 4.4  | RO_16_8_CC2                                                                                    |

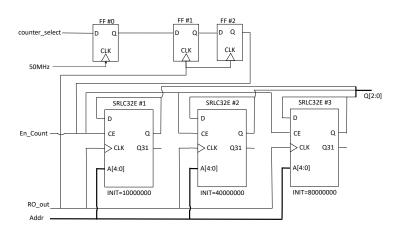

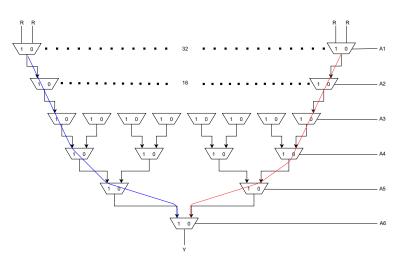

| 4.5  | Schematic of RNS ring counter                                                                  |

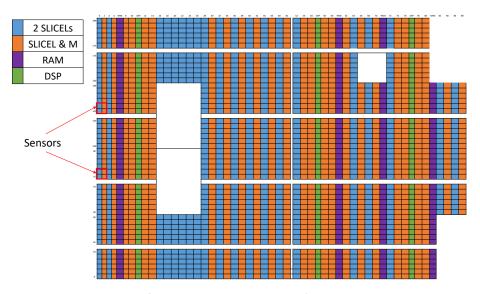

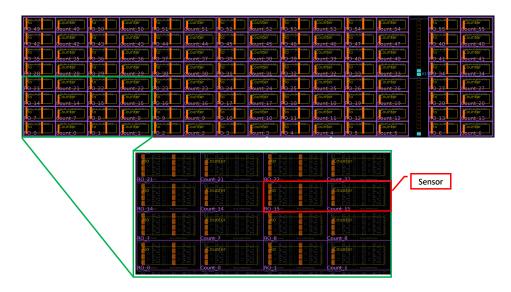

| 4.6  | The deployment of 1400 sensors                                                                 |

| 4.7  | The Principal Design of our method                                                             |

| 4.8  | The operation flow of our method                                                               |

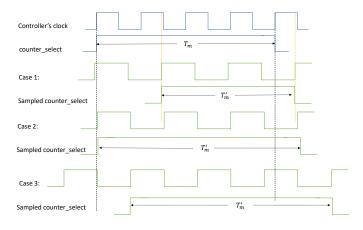

| 4.9  | The schematic of introducing extra Flip-Flops                                                  |

| 4.10 | Cases of the phase of the RO's output affecting $T'_m$                                         |

| 4.11 | Algorithm to calculate the counter ticks from the residue values $\ldots$ 34                   |

| 5.1  | FPGA resources layout                                                                          |

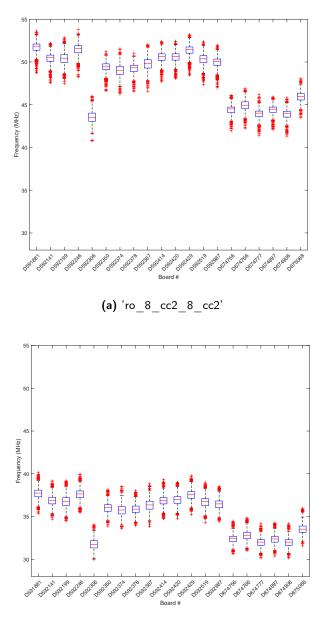

| 5.2  | Summary statistics with box plot for 'ro_8_cc2_8_cc2'                                          |

|      | and 'ro_16_8_cc2' on 20 Boards                                                                 |

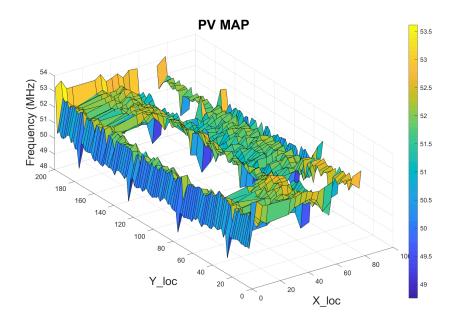

| 5.3  | PV map for 'ro_8_cc2_8_cc2' of Board D591881                                                   |

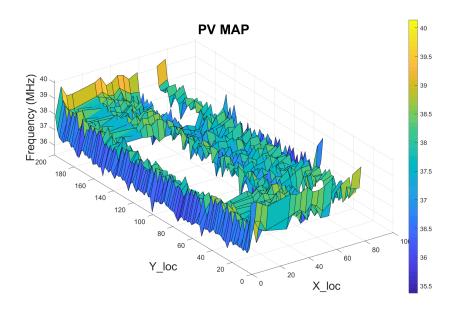

| 5.4  | PV map for 'ro_16_8_cc2' of Board D591881                                                      |

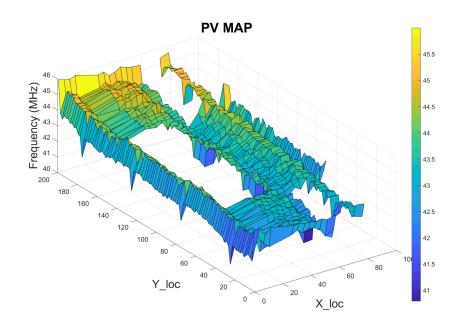

| 5.5  | PV map for 'ro_8_cc2_8_cc2' of Board D592306 $\ldots \ldots \ldots 40$                         |

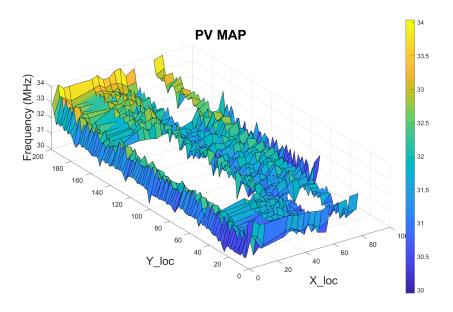

| 5.6  | PV map for 'ro_16_8_cc2' of Board D592306                                                      |

| 5.7  | LUT6's inner structure                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------|

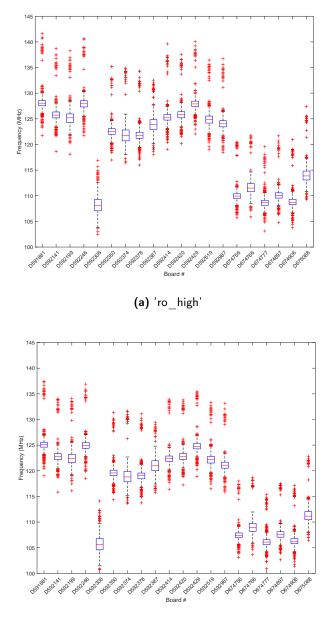

| 5.8  | Summary statistics with box plot for 'ro_high' and                                                                        |

|      | 'ro_low' on 20 Boards                                                                                                     |

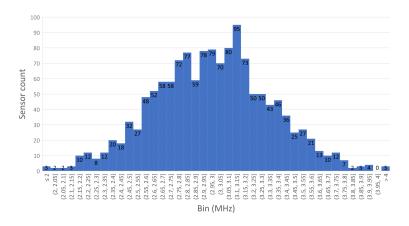

| 5.9  | Histogram of differences between 'ro_high' and 'ro_low' on 'D591881' 44                                                   |

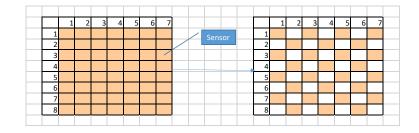

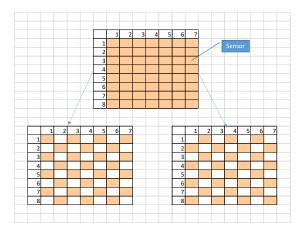

| 5.10 | An $8\times7$ dense patch $\hfill \ldots 45$ |

| 5.11 | The image to the right shows a patch covering only                                                                        |

|      | half of the resources                                                                                                     |

| 5.12 | Two patches covering half resources                                                                                       |

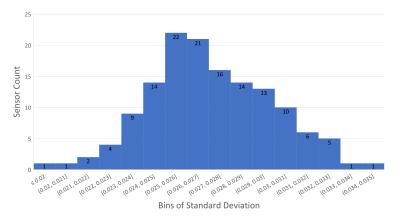

| 5.13 | The histogram of standard deviation among 140 sensors                                                                     |

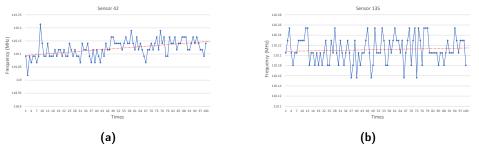

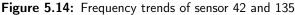

| 5.14 | Frequency trends of sensor 42 and 135                                                                                     |

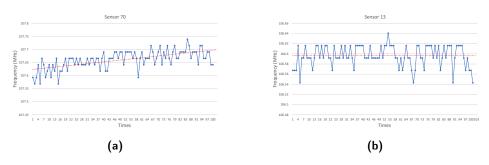

| 5.15 | Frequency trends of sensor 70 and 13                                                                                      |

| 5.16 | Frequency trends of sensor 100 and 0 $\ldots \ldots 50$    |

|      |                                                                                                                           |

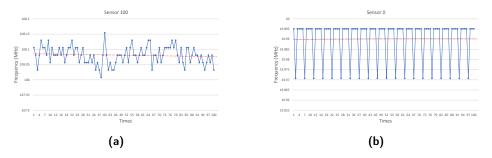

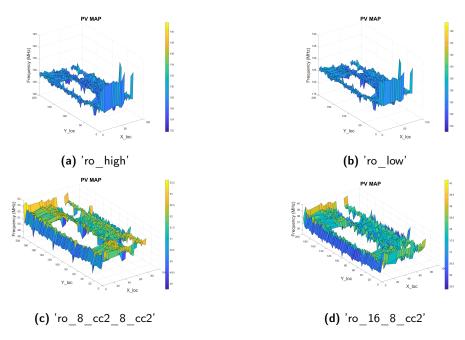

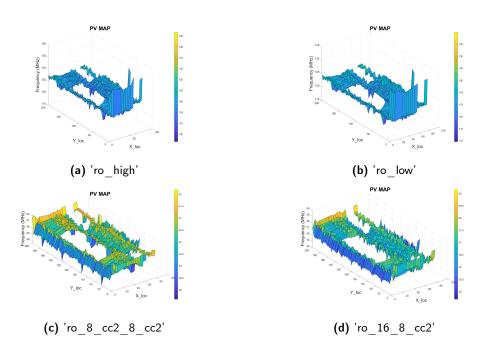

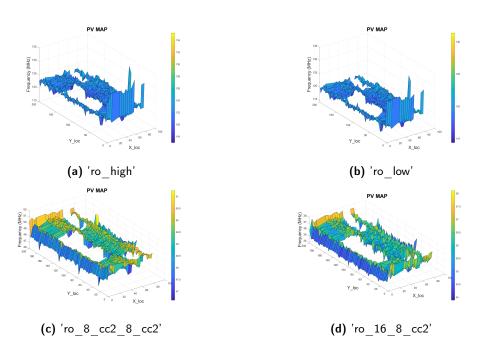

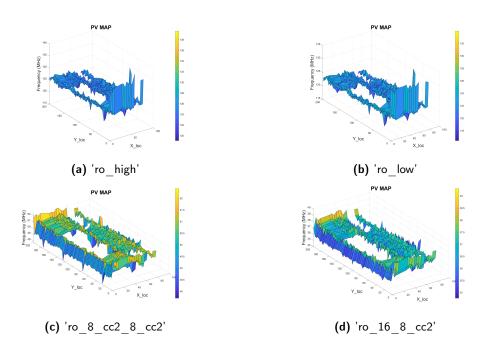

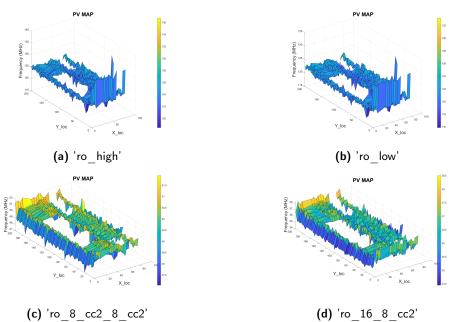

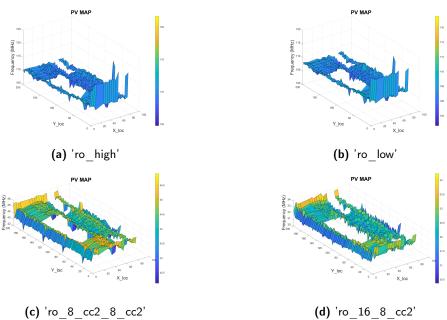

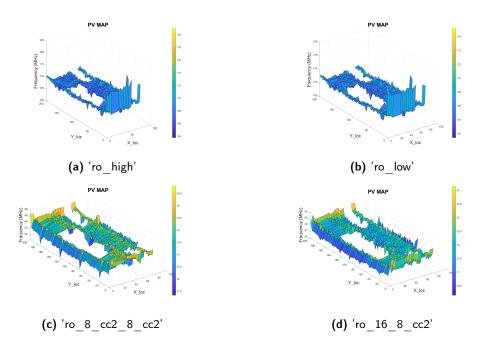

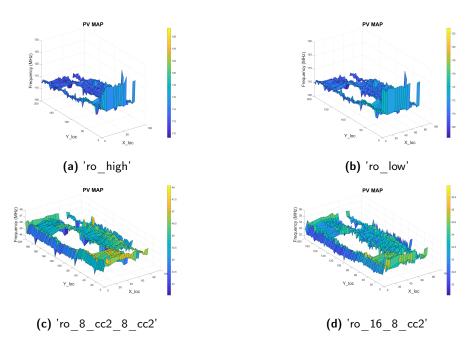

| B.1  | PV Maps of Board D591881                                                                                                  |

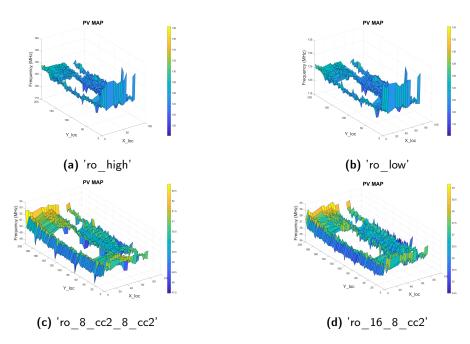

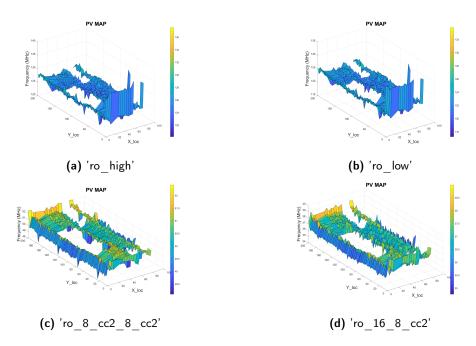

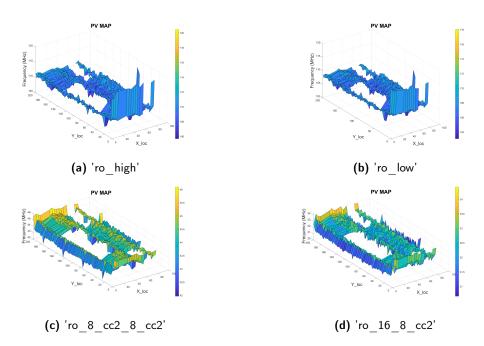

| B.2  | PV Maps of Board D592141                                                                                                  |

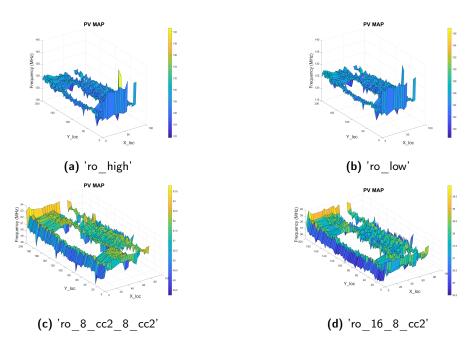

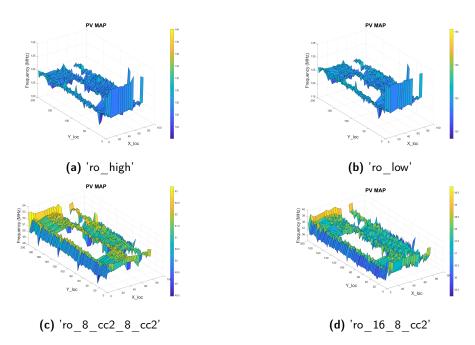

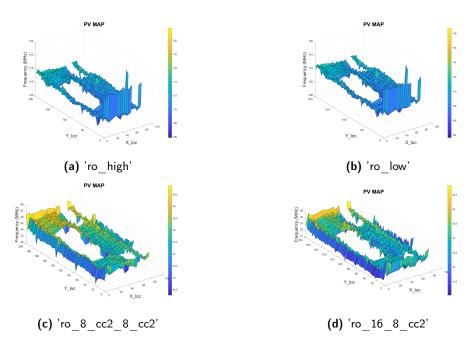

| B.3  | PV Maps of Board D592199                                                                                                  |

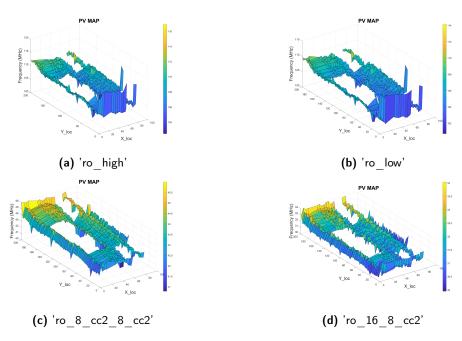

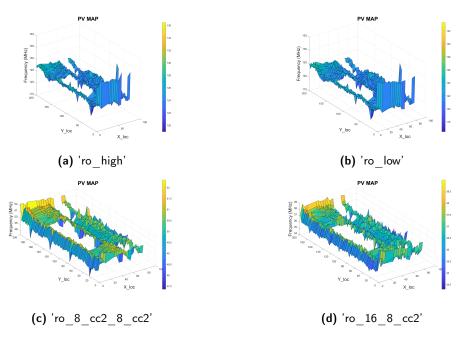

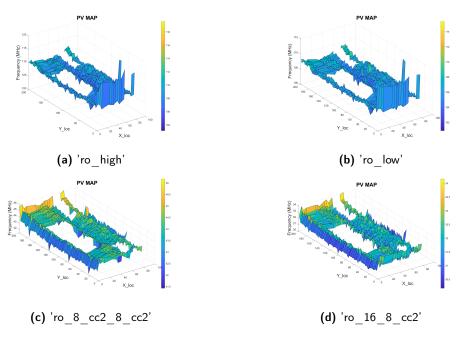

| B.4  | PV Maps of Board D592246                                                                                                  |

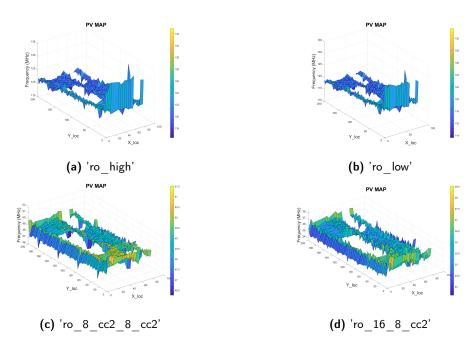

| B.5  | PV Maps of Board D592306                                                                                                  |

| B.6  | PV Maps of Board D592350                                                                                                  |

| B.7  | PV Maps of Board D592374                                                                                                  |

| B.8  | PV Maps of Board D592378                                                                                                  |

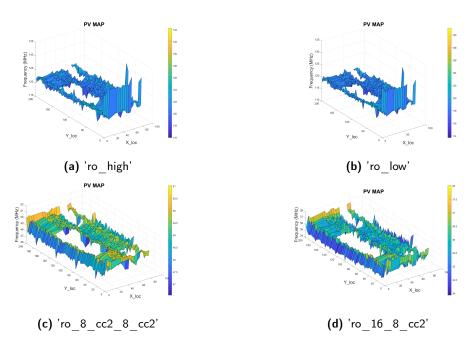

| B.9  | PV Maps of Board D592387                                                                                                  |

| B.10 | PV Maps of Board D592414                                                                                                  |

|      | PV Maps of Board D592420                                                                                                  |

|      | PV Maps of Board D592429                                                                                                  |

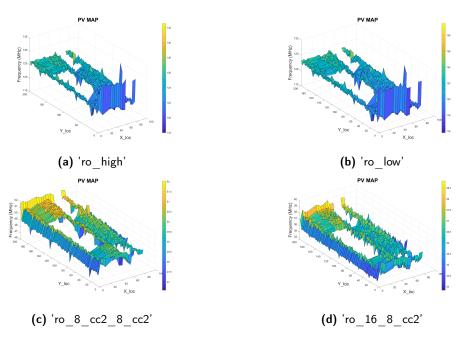

|      | PV Maps of Board D592519                                                                                                  |

|      | PV Maps of Board D592987                                                                                                  |

|      | PV Maps of Board D674756                                                                                                  |

|      | PV Maps of Board D674766                                                                                                  |

|      | PV Maps of Board D674777                                                                                                  |

|      | PV Maps of Board D674897                                                                                                  |

|      | PV Maps of Board D674906                                                                                                  |

| B.20 | PV Maps of Board D675088                                                                                                  |

# List of Tables

| 2.1 | Comparison of degradation mechanisms                                                                                     |

|-----|--------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Comparison of counter implementations assuming a maximum period of $2^{13}$                                              |

| 3.2 | A summary of the reviewed methods                                                                                        |

| 4.1 | Resources utilization of four ROs                                                                                        |

| 5.1 | Actual and measured frequencies during simulation, as well as measurement accuracy for 'ro_8_cc2_8_cc2' and 'ro_16_8cc2' |

| 5.2 | Actual and measured frequencies during simulation, as well as measurement accuracy for 'ro_low' and 'ro_high'            |

| 5.3 | Maximum, minimum and average difference between 'ro_high' and 'ro_low'                                                   |

| 5.4 | Frequencies (MHz) of 8x7 sensors in a dense patch                                                                        |

| 5.5 | Frequency inferred by linear interpolation                                                                               |

| 5.6 | Error in MHz between the inferred frequency and the measured                                                             |

|     | frequency                                                                                                                |

| 5.7 | Difference between maximum and minimum frequency (MHz) mea-<br>sured for each of the 140 sensors                         |

| A.1 | FPGA board information                                                                                                   |

# List of Abbreviations

| ALU  | Arithmetic Logic Unit                   |

|------|-----------------------------------------|

| BTI  | Bias Temperature Instability            |

| CLB  | Configurable Logic Block                |

| CMOS | Complementary Metal Oxide Semiconductor |

| СР   | Critical Path                           |

| DCM  | Digital Clock Manager                   |

| DSP  | Digital Signal Processing               |

| EM   | Electro-Migration                       |

| FF   | Flip-Flop                               |

| FPGA | Field-Programmable Gate Array           |

| HCI  | Hot Carrier Injection                   |

| IOB  | I/O block                               |

| LE   | Logic Element                           |

| LFSR | Linear-Feedback Shift-Register          |

| NBTI | Negative Bias Temperature Instability   |

| PBTI | Positive Bias Temperature Instability   |

| PLL  | Phase-Locked Loop                       |

| PV   | Performance Variation                   |

| PV   | Process Variation                       |

| RCP  | Representative Critical Path            |

| RNS  | Residue Number System                   |

| RO   | Ring Oscillator                         |

| SM   | Stress Migration                    |

|------|-------------------------------------|

| SR   | Shadow-Register                     |

| SRL  | Shift Register LUT                  |

| TCL  | Tool Command Language               |

| TDDB | Time Dependent Dielectric Breakdown |

| TP   | Transition Probability              |

| XADC | On-chip Analog-to-Digital Converter |

# \_\_\_\_ <sub>Chapter</sub> L Introduction

### 1.1 Motivation

As scaling of Complementary Metal Oxide Semiconductor (CMOS) devices continues, billions of transistors can be integrated on a single die. Such a high level of integration is the enabler for meeting the requirements for performance. Unfortunately, such higher integration comes at the expense of several manufacturing and reliability issues such as process variation, soft errors, thermal challenges, and ageing. One of the most important reliability challenges at nano-scale CMOS technology is transistor ageing [5]. Transistor ageing refers to phenomena such as Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), and Time Dependent Dielectric Breakdown (TDDB). Besides, interconnect ageing cannot be ignored, which includes Stress Migration (SM) and Electro-Migration (EM).

An important family of CMOS devices is Field-Programmable Gate Arrays (FPGAs), which are semiconductor devices with a matrix of configurable blocks connected via programmable interconnects. FPGAs can be configured after manufacturing to meet functionality requirements or desired applications. FPGAs fabricated with the most advanced CMOS technologies and the highest level of integration are broadly used today because of the low power consumption and high-performance demands. FPGAs are widely deployed to accelerate computation in various applications from embedded applications to data center applications.

Due to the effect of degradation mechanisms on transistor threshold voltage, HCI and BTI seriously limit the performance of CMOS devices by increasing the transistor switching and thus the path delay. In addition, the scaling rate of transistor size is larger than that of the supply voltage. As a result, once the delay of critical paths (CPs) exceeds the clock period, timing failures occur and the correct functionality of the circuit will be affected [7]. This trend increases temperature and current density, thus accelerating device degradation in future CMOS devices. Since lifetime decreases due to an increase in path delays, it is important to address the ageing problem. So far, design-time methods such as specific design rules have been used to ensure that ageing does not affect the desired useful life of a product. However, given the increased variation (that leads to reduced design margins) and use of new materials in future process nodes, it becomes necessary to also monitor for ageing.

Ageing monitoring is achieved by implementing circuitry that is able to detect and measure the degree of degradation. In previous works, there are several mainstream

methods to monitor ageing, such as an approach based on ring oscillators and frequency counters, and a technique by monitoring the correct functionality of critical paths.

As FPGAs use the most advanced CMOS technologies [8], it is crucial to address nano-scale reliability concerns for FPGAs. To ensure performance, it is important to propose an effective ageing monitoring system to address these problems.

Given the regular architecture of Field-Programmable Gate Arrays (FPGAs) and the ability to program each resource of its structure at a very low level, many works have been devoted to ageing effects and ageing monitoring on this type of device. In this thesis work, we review these works and devise a method suitable for in-field monitoring of FPGA devices, as detailed in the next section.

### 1.2 Goal and Objectives

This thesis work investigates the design of effective monitoring circuitry for ageing in FPGAs. It conducts a comprehensive survey of prior work on monitoring of FPGA degradation, reports the findings as well as presents a comparison of monitors with respect to resource consumption, the accuracy of measurements, and targeted degradation mechanisms. The main objective of this work is to find several effective ageing monitoring methods from previous works, in terms of the ability to detect degradation of the fabric resources with high accuracy and high precision. In particular, we find the most suitable for in-field monitoring of ageing in a wide range of products and experiment with this method. With the experiments, we aim to get more insights into the practical aspects of the implementation, as well as knowledge about the resource utilization, precision, and accuracy of the chosen measurement method.

### 1.3 Thesis Organization

The rest of this thesis is organized as follows. The overview of general FPGA structure and background about degradation mechanisms are presented in Chapter 2. Chapter 3 presents a survey of related work on aging monitoring. In Chapter 4, we present our implementation of the method we chose as the most suitable for monitoring ageing in FPGAs. The experimental setup and results are discussed in Chapter 5. In the end, the thesis is concluded in Chapter 6.

| Chapter 2  |  |

|------------|--|

| Background |  |

In order to monitor degradation mechanisms in FPGAs, it is crucial to have a basic understanding of the FPGA architecture and its main components, as well as degradation mechanisms in CMOS technology. Currently, SRAM-based FPGAs are the most common commercial type owing to the use of standard CMOS processing technology and its re-programmability. In this thesis, the main focus is the FPGA from Xilinx. Thus, the FP-GAs from other vendors are not presented. FPGA architecture, and its main components and degradation mechanisms are described in this chapter.

### 2.1 FPGA Overview

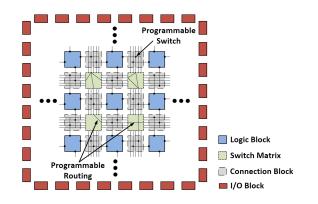

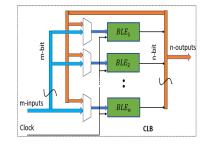

A Xilinx FPGA comprises of the Configurable Logic Blocks (CLBs) implementing logic functions, which are connected together via switch matrices and interconnect wires, and surrounded by I/O blocks (IOBs). The I/Os are the bridge between the logic blocks and peripheral components. In addition, some specific applications might be integrated into modern FPGAs, such as Digital Clock Managers (DCMs), Digital Signal Processing blocks (DSPs), and On-chip analog-to-digital converters (XADC). Figure 2.1 depicts the FPGA architecture. These components are introduced in the following sections.

Figure 2.1: An abstracted FPGA architecture (island-style) [1], Copyright © 2013, IEEE

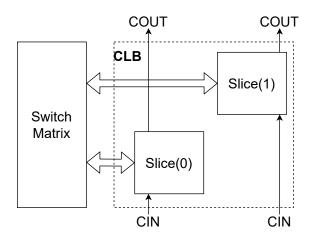

#### 2.1.1 CLBs

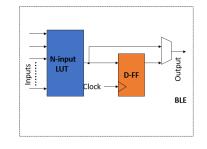

As the main logic component of an FPGA, CLBs allow the user to implement any logic function within the chip. Each CLB contains a pair of slices<sup>1</sup> as shown in Figure 2.2. Each CLB consists of a set of Basic Logic Elements (BLEs), containing a Look-Up Table (LUT), a storage element and a multiplexer. Figures 2.3, and 2.4 show the basic structure of the CLB.

Figure 2.2: Arrangement of Slices within the CLBs [2]

Figure 2.3: The BLE structure

Figure 2.4: The CLB structure

In order to improve the performance, several additional components are integrated into CLBs, which are carry chain and shift register. For example, in Xilinx 7 Series FP-GAs, where each SLICE consists of 4 LUTs, 8 flip-flops (FFs), wide-function multiplexers, and one carry logic. There are two types of slices: SLICEM and SLICEL, where 'M' signifies a memory slice and 'L' signifies a logic slice. In addition, LUTs in SLICEMs can be implemented as distributed RAM or shift registers.

<sup>&</sup>lt;sup>1</sup>This is relevant to the 7 Series, as in newer Xilinx FPGA families, the number of Slices per CLB is different.

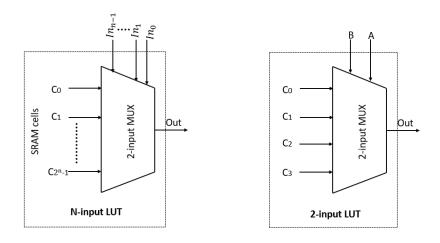

#### Look-up Tables (LUTs)

The Lookup Table (LUT) is the basic logic element in CLB, which can implement Boolean functions. The truth table value of an n-input Boolean function is stored in  $2^n$ -bit SRAM cells. An n-input LUT can calculate an arbitrary n-input Boolean function. The input pins control the multiplexers which can be implemented with pass transistors or transmission gates to pass the value to the output. For example, a general n-input LUT and a two-input LUT are shown in Figures 2.5 and 2.6. The function values are stored in SRAM bits  $C_0$  to  $C_{2n-1}$ .

Figure 2.5: N-inputs LUT

Figure 2.6: Two-input LUT

#### Storage Elements

Storage elements are used in sequential circuits in the FPGAs, to store the output values of LUTs. These can be configured as a level-sensitive latch or edge-triggered D-type flip-flops.

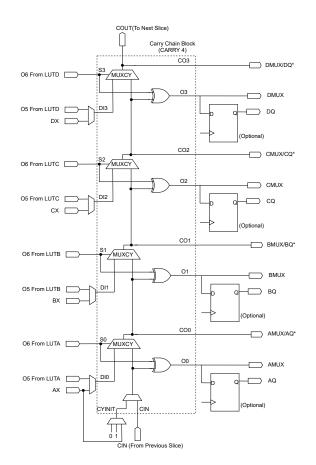

#### Carry Chain

The dedicated fast look-ahead carry is used to perform fast arithmetic including subtraction and addition with using fewer resources. The Carry Chain contains four MUXs and four two-input XOR gates, and its structure is shown in Figure 2.7.

#### Shift Registers

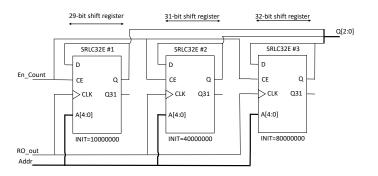

Shift Registers, such as 32-bit shift register (SRL32) and 16-bit shift register (SRL16), can be configured via LUTs in the SLICEM without using flip-flops available in the SLICE. The serial data can be delayed from 1 to 32 clock cycles using SRL32 that can be built to larger or smaller shift registers to satisfy the variable requirements. For example, a 29-bit shift register can be created by setting the address to the 29th bit.

Figure 2.7: Schematic of the Carry Chain [2]

#### 2.1.2 Switch Matrix

According to the requirements of the circuit mapped to the FPGA, the switch matrix uses a set of programmable switches to activate/deactivate the connections as needed to provide the required routing to achieve the connection between the CLBs, to and from I/O blocks.

The number of possible connections between wires in each matrix is usually too large. In order to reach a better balance among the routing flexibility, area and delay, modern FPGAs provide different-length interconnect wires.

#### 2.1.3 Other Components

#### Digital Clock Managers (DCMs)

The digital clock manager (DCM) can generate multiple clock signals with different duty cycles or a wide range of frequencies. In addition, it can also be used as a phase shift synthesizer, a dynamic frequency synthesizer, and a jitter filter for the input clock. These functions can be easily implemented via a clocking wizard.

#### Digital Signal Processing (DSP) Applications

As an arithmetic logic unit (ALU) embedded into the fabric of the FPGA, DSP applications consist of many binary multipliers and accumulators, which are designed to perform "multiply and add" operations. It has higher power efficiency and operates at far higher frequencies than the equivalent circuits in a soft implementation.

#### Xilinx Analog Mixed Signal Module

Xilinx analog mixed signal module, referred to as the XADC, is a new flexible analog interface. When combined with the programmable logic function of the Xilinx Artix-7 FPGAs, it can handle various data acquisition and monitoring requirements.

### 2.2 Degradation Mechanisms

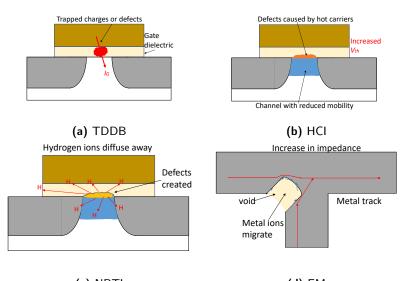

As mentioned earlier, degradation is one of the most important reliability challenges in CMOS technology. Ageing happens over a long time, which leads to timing failures and adversely affected the performance of CMOS devices. Ageing (also known as wearout) effects can be observed in the transistors (i.e. BTI, HCI, TDDB) as well as the interconnects (i.e. EM, SM) inside the chip [1]. Each of these mechanisms is briefly explained in the following sections.

#### 2.2.1 Transistor Degradation Mechanisms

Transistor degradation mechanisms cause an increase of threshold voltage, as a result, drain current, mobility, and trans-conductance of the transistor degrade. Consequently, the switching speed of the transistor decreases, and thus, the delay of the circuit's functional paths might exceed the timing requirements. Correspondingly, failures start to happen in the circuits and the operational lifetime of FPGA chips will decrease. There are three transistor degradation mechanisms named TDDB, BTI and HCI [1], which are demonstrated in Figure 2.8.

#### Time Dependent Dielectric Breakdown (TDDB)

TDDB is a breakdown in the gate oxide layer of a transistor. The breakdown is a result of a conductive path through the gate dielectric which is formed by trapped charges or defects that gradually accumulate over time. TDDB inflicts a rise in leakage current and power consumption and a slowdown of switching activities, and eventually, the dielectric layer will lose its insulating properties, which leads to a permanent failure [3] [1].

#### Bias Temperature Instability (BTI)

There are two phenomena: NBTI affecting PMOS and PBTI affecting NMOS. Compared with NBTI, the PBTI effect was negligible and ignored mostly in previous technology. However, the PBTI effect should be considered since the introduction of high- $\kappa$ / metal

gates transistors in sub 45 nm technology. NBTI is a static mechanism driven by gate potential, which is caused by hydrogen ions diffusing away in the interface region. BTI has a stress phase and a recovery phase. The magnitude of threshold voltage increases in the stress phase, and on the contrary, it decreases back toward its initial value in the recovery phase. Nonetheless, this recovery cannot be complete [3] [1]. BTI is a static mechanism and is triggered when a transistor is on [7], which is mostly independent from signal duty cycle.

Hot Carrier Injection (HCI)

HCI, also called hot-electron effect or hot-carrier, is based on defect accumulation in the interface region between the gate dielectric and the channel. Hot carriers (electrons) in the channel cause interface defects, and some of them overcome the barrier of the gate dielectric due to obtain enough energy and are accelerated by the gate field. HCI leads to a rise of threshold voltage and a slowdown of carrier mobility, and consequently, which leads to a decrease of switching activities. HCI is primarily dynamic since the procedure is driven by a high-energy carrier flowing into the channel, and it happens when transistors switch. However, unlike the BTI, there is no recovery phase , and thus, the effect, threshold voltage increasing is permanent [3] [1].

HCI is a dynamic mechanism, which is dependent directly on switching activities (speed). HCI degradation mechanism has greater effects on the fall delay than the rise delay. TDDB is also a static mechanism.

#### 2.2.2 Interconnects Degradation Mechanisms

There are two degradation mechanisms, Electro-Migration (EM) and the Stress Migration (SM) affecting interconnects. EM causes atoms to migrate from one side of the wire to the other side in the direction of the electrons due to current flows in wires. In SM, the atoms migrate from the high-stressed side to less-stressed areas due to the thermal differences in the wires without applying current. Consequently, EM and SM leads to voids where the atoms migrate from and creates hillocks where the atoms migrate to, and which in turn leads to short circuit failures [3]. The procedures of main degradation mechanisms are demonstrated in Figure 2.8. The features of these degradation mechanisms are presented in Table 2.1.

(c) NBTI (d) EM

Figure 2.8: Degradation Mechanisms [3]

| Ageing mechanisms      | NBTI                                   | HCI                                    | TDDB                                   | EM                                                                      |  |

|------------------------|----------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------------------------------------|--|

| Defects                | Vt increase                            | Vt increase                            | Leakage increase                       | Impedance<br>increase                                                   |  |

| Causes                 | Hydrogen<br>ions<br>diffuse away       | Hot carriers                           | Defects (traps)<br>overlap             | Metal ions<br>movement<br>High DC<br>current and<br>high<br>temperature |  |

| Accelerators<br>in lab | Elevated<br>voltage and<br>temperature | Elevated<br>voltage and<br>temperature | Elevated<br>voltage and<br>temperature |                                                                         |  |

| Recovery               | Partial recovery                       | Permanent<br>failure                   | Permanent<br>failure                   | Permanent<br>failure                                                    |  |

| Sensitivity            | Duty cycle                             | Switching activities                   |                                        | Current<br>in wire                                                      |  |

| Symptoms               | Slower<br>switching                    | Slower<br>switching                    | Failure                                | Slower<br>switching                                                     |  |

Table 2.1: Comparison of degradation mechanisms

In this chapter, we review approaches for detecting ageing in FPGAs, and we will discuss pros and cons of each approach.

Ageing in FPGAs can be monitored by measuring the reduction of the maximum operating frequency, which indicates the worst case path delay. There are three kinds of sensors to monitor ageing. The most common ageing sensor is based on arrays of ring oscillators (ROs), which will be referred to as RO sensor in the rest of this thesis report. The sencond kind is based on the Razor approach using shadow registers (SR) placed at the end of combinational paths [4], which is referred to as the SR sensor in this work. The third kind is based on detecting changes in transition probability (TP) [6], referred to as TP sensor. The RO sensor monitors ageing by comparing the RO's frequencies measured at different times. SR and TP sensors monitor the ageing by detecting timing failures. These three types of sensors are described in the following sections.

### 3.1 RO Sensor

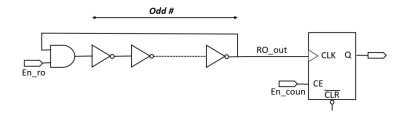

RO sensor is composed of an RO and a frequency counter, an traditional RO sensors structure is depicted in Figure 3.1. The frequency counter is used to capture the RO's frequency that reflects the FPGA's performance and capture the frequency change due to aging degradation.

Figure 3.1: Traditional Ring Oscillator Structure

In an RO, traditionally an odd number of inverter gates are connected in a loop to form a ring. The RO output toggles between zero and one since the number of inverters is

odd. Consequently, a square wave signal is generated at the output. The frequency of RO is given by Equation 3.1:

$$f = \frac{1}{2 \times n \times t} \tag{3.1}$$

where, f represents the frequency of oscillation, t is the time delay for a single inverter, and n is the number of inverters in the RO. In general, in order to control the RO's oscillations, control logic (e.g., And gate) is employed to build RO. As illustrated in Figure 3.1, the RO is controlled by control logic (e.g., AND gate), which could reduce the effect of self-heating or counter overflow [9]. In [10], the authors set  $T_s$  to be  $50\mu s$  in order to avoid self-heating phenomena due to longer measurement time.

The frequency counter is used to capture the RO's oscillations for a predefined period of time, called sample period. The oscillation period,  $T_d$  of an RO is given by Equation 3.2:

$$T_d = \frac{T_s}{N} \tag{3.2}$$

where  $T_s$  is the sample period, N represents the number of cycles obtained by frequency counter.

ROs have been extensively studied in the past, not only to analyze process variations (Process variation is the natural variation in transistor properties (length, width, oxide thickness) when manufacturing integrated circuits.), but also to analyze ageing effects. In addition, there are a large number of ROs with different structures designed to satisfy different study purposes. ROs with different structures mean that sensors have different LUT configurations, different number of LUTs in each RO and different types of and frequency counter.

In next section, process variation analysis based on RO sensors is presented.

#### 3.1.1 Performance Variation Analysis

Performance variation is a measure of both process variation and the degradation induced by ageing. In [10], [11] and [12], ROs were implemented to characterize process variations, which is decomposed into stochastic and systematic intra-die process variability, in 16nm Zynq XCZU7EV FPGAs, 90nm Cyclone II, and 65nm Virtex-5, respectively. In addition, counters were used to measure the frequency of ring oscillators. Moreover, in order to guarantee the resolution, an array of ROs were placed on the die. In [10], performance variation in logic and interconnect resources was characterized and the impact of diverse temperatures and voltages is analyzed. The experimental results showed that, under certain operating conditions, the intra-die and inter-die performance variation can reach up to 9.9 % and 12%, respectively. In addition, the authors concluded that there is a low correlation between logic and interconnect variations. However, in [11] and [12], the authors conducted the experiments without temperature control and did not study the effect of ambient temperature. In [12], all CLBs are used to map 6,480 ROs, which are split into multiple configuration bit-streams to measure. Thus, this test has higher resolution and coverage than the experiments in [10] and [11]. It can also be noticed that the

measurement system's impact on measurement accuracy is not reported in these works.

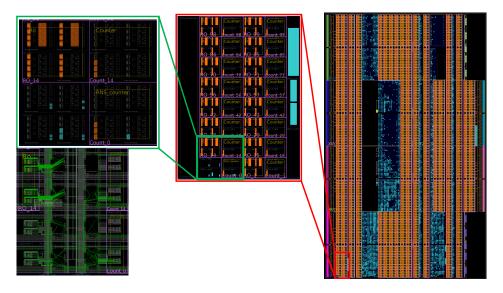

In [13], the authors employed ROs to measure intra-die variation in 65nm Virtex-5 FPGAs. A novel and highly-efficient counter, residue number system (RNS) ring counter using SRLs was utilized, which is more resource-efficient compared with other types of counters such as binary counter and linear feedback shift register (LFSR) using SRLs counter. These three counters will be described in detail in Section 3.1.4. In [13], RO required just eight LUTs, composed of seven inverters and one AND gate to control the oscillation. In addition, four physical parameters were analyzed, namely, variation in delay, static and dynamic power and temperature.

In [14], an array of different sizes of ROs are implemented on 90nm Spartan FPGA. In order to analyze LE characterization and derive the differences in LE delay, the authors built two sizes of ROs, namely an eight-stage RO using all LEs in a CLB and a sevenstage RO utilizing seven LEs. In addition, the authors create a calibration RO utilizing two LEs and a pair of interconnects (e.g., Direct connection, Double, and Hex wires) to analyze interconnect delay characterization. The authors accurately characterize process variation of logic elements (LEs) and interconnects, but the impact of the counter is not analyzed.

In [15], a matrix of ROs was implemented to perform process characterization in 90 nm Spartan-3 FPGA. A different measurement method based on Electro-Magnetic Analysis (EMA) was implemented to measure the frequency from the ROs. It should be noted that the experiments were conducted with complete control, temperature and voltage relatively at constant by using a thermal chamber and a core voltage control. Thus, the differences between measured frequencies is only due to process variation. Compared with the approaches in [10], [11], [12] and [13], this approach has higher accuracy. However, this method makes the experiment more complicated since the lab equipment is used (eg., EM probe and oscilloscope) making this method impractical for in-field monitoring.

#### 3.1.2 Ageing Effect Analysis

Previous work has employed ROs to characterize the effects of degradation on FPGAs in 45nm Spartan 6 [8], 65nm Altera Cyclone III [16], 65nm Altera Cyclone III [17], 65nm Altera Cyclone III [18] and 28nm ARTIX-7 FPGAs [19], respectively. In these papers, different stress conditions were tested to accelerate the ageing process and identify the mechanisms.

In [8], the authors employed a group of controlled ROs with adjustable switching activity and different frequencies. The ageing process was emulated by stressing the FPGA with elevated voltages and temperatures. The experiment was conducted in three steps including capturing the oscillating frequencies in nominal conditions, accelerated ageing in elevated temperature and voltages, and measuring. Like [15], sensors' frequencies were captured using Electro-Magnetic (EM) analysis rather than frequency counter, and the experiment setup is also performed with complete control of voltage and temperature. The EM method is utilized to ensure that only variations caused by ageing are captured in order to monitor the changes in the sensors' performance before and after stress. The frequencies are measured with the help of Electromagnetic Sensing Probe. In [8], the authors concluded that, compared with HCI, BTI ageing is the principal factor in ageing of the used 45 nm technology node.

In [17] and [18], the authors analyzed FPGA LUT delay degradation due to NBTI and HCI under different types of electrical stress signals. The approach has two phases of operation, consisting of measurement mode and stress mode controlled by a Mode input. The sensor contains nine buffers and one inverter, its frequency is measured by a K-bit counter. In [17], a low-frequency signal with varied duty cycles was stressed into LUT. However, in [18], three kinds of frequencies signal with different duty cycles were applied as stress signals. The authors identified that NBTI and HCI degradation mechanisms depend on the duty cycles and frequency of input signals, respectively. NBTI affects the fall delay more than the rise delay, while, HCI has the opposite effect.

In [19], like approaches in [8], [16], [17] and [18], the author also adopts two phases of operation to analyze ageing effects. The difference is that ROs with varied LUT configurations and different sizes were employed. In addition, the impact of variable temperatures was analyzed. It shows that the NBTI ageing effect is the dominant factor of timing degradation.

#### 3.1.3 Temperature Monitoring

In [9], to monitor the thermal distribution of FPGAs, an array of RO-based temperature sensors are implemented on Virtex-5 LX50T FPGA. It should be noted that the propagation delay of an inverter is related to its temperature, and the interconnect resistance has a linear relationship with its temperature, an increase of temperature will lead to an increase of inverter path delay and interconnect delay. Thus, the frequency of an RO is decreased as its temperature increases. In order to find the best design, the authors study various types of sensors for variant RO lengths and counters (e.g., Binary counter and RNS ring counter) with variant widths. The authors also introduce four useful criteria to evaluate the relative performance. Comparing these designs, one sensor with the highest efficiency is found to monitor the temperature distribution of FPGAs.

#### 3.1.4 Counter

In previous work, there are three types of counters implemented. A standard binary counter counts by using a binary representation, and its results can be read without special decoding. However, it costs a relatively high number of hardware resources. An alternative design is a linear feedback shift register (LFSR) counter. Another counter is the residue number system (RNS) ring counter [13]. LFSR and RNS counters can implemented in a compact way using Xilinx's shift register LUTs (SRLs). Compared with binary counter and LFSR counter, an RNS ring counter is far more compact and needs fewer resources.

In [13], assuming the requirement for 2<sup>13</sup> count cycles, the authors compared three types of counters, which is shown in Table 3.1. A binary counter can be implemented with 13 LUTs. An LFSR counter requires an SRL, a flip-flop and a LUT configured as an XOR, two LUTs and hundreds of bytes of memory [13]. However, an RNS counter can be built from 2 SRLs, on Virtex-5/6 FPGA, one acts as a 32-bit SRL, and the other acts as two 16 bits SRLs, using moduli of 33, 17, and 16.

| Counter type        | Logic (LUTs) | Memory (Bytes) |

|---------------------|--------------|----------------|

| Binary              | 13           | 0              |

| LFSR using SRLs     | 2            | Hundreds       |

| RNS ring using SRLs | 2            | 0              |

**Table 3.1:** Comparison of counter implementations assuming a maximum period of  $2^{13}$

## 3.2 SR Sensor

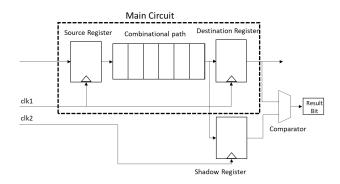

In this approach, a register called shadow register<sup>1</sup> is placed at the end of combinational paths, which is independent of the main circuit. One type of SR sensor is shown in Figure 3.2. SR is triggered by an auxiliary clock with a negative skew from the main clock that used to trigger the destination register. Due to the existence of clock skew, the combinational outputs are latched by destination register and shadow register at different times, respectively. During the test, two clocks have the same frequency and the clock skew is changed gradually until two registers capture two different values [4]. With the help of clock skew and frequency values, the combinational path delay can be calculated. Based on the above method, this approach not only measures the path delay but also monitors the ageing phenomena.

Figure 3.2: Basic principle of delay characterization circuits with shadow register [4]

#### 3.2.1 Performance Variation Analysis

In [4], the authors analyzed the path delay by placing additional shadow registers alongside main register on 130nm Virtex-II FPGAs, respectively. Three different combinational

<sup>&</sup>lt;sup>1</sup>In this work, it is referred to as shadow register.

logic paths of five 32-bit floating-point adders placed in five different locations are analyzed. In order to measure the path delay, the clock skew was increased step by step until an incorrect value was captured in the shadow register. According to the [4], addition of shadow registers have no adverse impact on the monitored paths. However, the sensor inclusion increase the path delay due to additional loads introduced.

In [20], a method named built-in self-test to accurately measure the path delay is implemented on 90 nm Virtex-4 FPGA. The maximum frequency of path can be captured by increasing the clock frequency until detecting a timing failure. In this experiment, the timing resolution can reach 1ps or lower. However, the authors just tested simple combinatorial circuits. In addition, in this method, another FPGA was required for clock generation, which makes the test setup a bit complicated. Fortunately, this method could be implemented in modern FPGAs without an additional FPGA for clock generation. This method has a limitation to only work for combinational paths.

In [21], the authors focus on the analysis of clock tree variability, a part of performance variations, by using the method [20] on 65nm Virtex-5 FPGAs. In addition, to analyze the variance of clock skew, the authors create a measurement system for detecting clock skew and measure 336 differential path circuits. The approach can be used to alleviate the variation due to clock skew from different components in the clock networks.

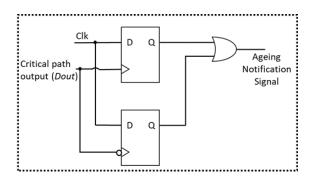

#### 3.2.2 Ageing Monitoring

In [5], an ageing sensor based on shadow register was mapped on 40nm Virtex-6 FPGAs. This approach is to capture transitions happening after the rising edge of the clock cycle, and the reason behind using two flip-flops with different clock polarities. Unlike the approaches in [4], [21], and [20], the critical path output is fed to the clock inputs of two registers and the system clock is connected to the inputs of two registers. The schematic is shown in Figure 3.3. Due to the adjustable sensitivity of the ageing sensor, it not only generates a warning signal before ageing, but also detects the timing failure caused by ageing phenomena and sends an error signal. Once the warning signal is detected, effective actions can be taken to ease ageing.

Figure 3.3: Schematic diagram of the aging sensor [5]

In [22] and [23], the authors employed a programmable ageing sensor to monitor ageing along with CPs on 90nm Spartan-3 FPGA. Compared with the method in [20],

this approach sets an observation interval  $(T_g)$  as a constant clock offset between the main clock and auxiliary clock, it does not need to increase the clock offset step by step. As a result, it costs fewer resources. In addition, the sensor could be activated at some intervals, which means that it does not need to work continuously. Ageing is detected when signal transitions occur during  $T_g$ . For this kind of sensor, multiple clock generators are required for inserting various sensors since they need different  $T_g$ . It is mentioned that The sensor inclusion leads to an increase in path delay due to additional loads introduced.

Compared with the ageing sensors in [5], [22] and [23], the authors in [7], [24] and [25], proposed a different ageing sensor for critical path delay monitoring on 40nm Virtex-6, 28nm Artix-7, and 28nm Artix-7 FPGAs, respectively. This sensor has two advantages. First, it does not need multiple clock generators for inserting multiple sensors, which could reduce clock routing complexity. Moreover, the sensor could be mapped into one slice rather than two slices, thus, it costs less area and power overheads. The authors insert ageing sensors alongside the Representative Critical Paths (RCPs) to monitor ageing. RCPs, which are paths with higher ageing rates than Critical Paths (CPs), are selected with the help of the RCP selection algorithm in [24], which can avoid unnecessary sensor insertion. Therefore, the sensors with higher accuracy placed along RCPs are able to detect ageing earlier than the ageing sensors [5] [23].

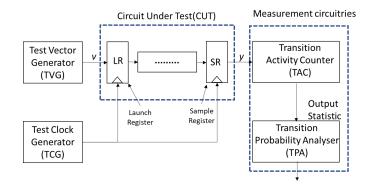

### 3.3 TP Sensor

Like the SR sensor, the TP sensor also measures the path delay and monitors ageing effects by detecting circuit failures. Normally, a steady TP is generated at the output node if the input is fed a source with stationary TP. TP of output node depends on input and clock frequency. It changes once the input clock frequency ramps beyond a certain threshold (maximum operating frequency), where the circuit starts to fail. Correspondingly, the path propagation delay can be measured. TP will change due to the ageing effect accumulate. Based on the above method, a sensor based on TP can be employed to monitor ageing phenomena.

Previous work has employed this circuits on 65nm Altera Cyclone III FPGAs [3] [6] and [26]. Figure 3.4 shows the general structure of the TP sensor.

Figure 3.4: Basic principle of the TP sensor [6]

This technique can be implemented to measure the path delay and monitor the ageing phenomena of arbitrary circuits on FPGAs. In [6], three typical circuits were tested, which are an adder carry chain, a linear-feedback shift-register (LFSR), and an embedded multiplier. In [3], 684 test circuits were tested, which consist of three different types of resources: LUTs, interconnect, and registers. In [26], the authors proposed three degradation mitigation strategies to improve longevity by replacing the aged with spare resources.

### 3.4 Comparison of the Three Types of Sensors

In the previous sections, we surveyed the three main sensor types used in ageing detection in FPGAs. Table 3.2 presents a summary of the reviewed methods. In this section, we will present a comparison of these three sensor types in the context of in-field ageing monitoring.

RO sensors can be utilized to monitor the development of ageing (that is, the current degree of degradation). However, our observation from the existing literature is that the RO sensors have been only used for studying the process variation and ageing effects in the lab environment, and not for in-field monitoring of ageing. Compared with the RO sensor, without sweeping the clock frequency, the TP sensor can only be used for diagnostics (that is, for detecting if malfunctioning in a circuit is due to ageing), and not for monitoring the development of ageing. The reason is that on the one hand, without sweeping the frequency, the change in the transition probability of the output node can only be observed when ageing has already increased the delay of the critical path beyond the period of the circuit's clock signal. On the other hand, sweeping the frequency when the device is in the functional mode will interrupt the operation. Moreover, the TP and SR sensors should be incorporated into the circuit and, therefore, the sensor insertion should become part of the design process. This way, the sensor insertion (which involves choosing suitable locations with regard to CPs and NCPs) might slow down the overall design process (unless the sensor insertion process is fully automated and integrated in the design flow). On the other hand, the overall resource consumption might be a limiting

factor in the number of sensors inserted. In this regard, we should note that the FPGA design might be updated several times throughout the lifetime of a product (the ability to upgrade and update is one of the reasons that FPGAs are used instead of ASICs), and therefore each time any update is applied, the CP and RCPs should be re-evaluated for the SR sensor, and the TPs should be calculated for the TP sensor. Moreover, the TP sensor has the additional disadvantage that calculating the threshold is not straightforward, and even for the same exact circuit the threshold might change depending on the load and usage conditions of that product (the so called, mission profile). Additionally, adding extra registers to CP (for the TP and SR methods) might add additional capacitive load to the CP and can thus negatively impact the timing margins [23]. On other hand, the TP method has the advantage that its application is not limited to the combinational circuits, and can be used even for detecting ageing DSP blocks and larger sequential modules.

The different variants of the SR method surveyed in this chapter have been shown to have reasonably low resource overhead and performance impact. In this regard, this type of sensor is sufficiently well studied and different variants can be used depending on available resources [5]. Therefore, if the SR sensor insertion is automatically performed as part of the design process and implementation flow, the SR method can be seen as an attractive ageing monitoring solution for FPGAs.

None of the surveyed work has discussed the matter of ageing in the monitoring circuitry itself, which is something we would like to investigate more.

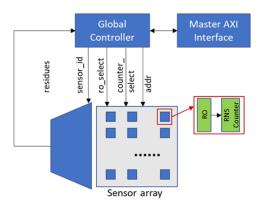

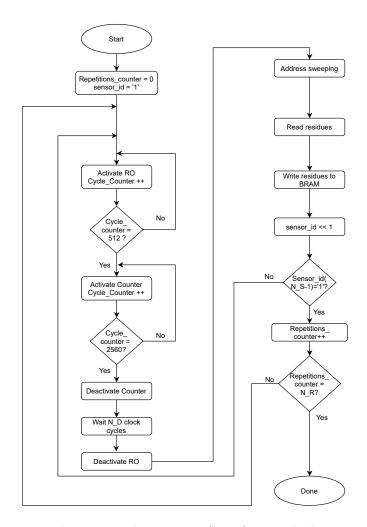

For this thesis work, we decided to take a different approach compared with the existing work, in the sense that instead of mixing the ageing monitors with the product RTL implemented in the FPGA as a product bit-file, we propose using a separate FPGA bit file dedicated solely to monitoring of ageing. This approach, addresses some of the abovementioned shortcomings by being non-intrusive to the design flow and independent of any circuitry that is to be implemented in the design. It should be noted that ageing is a relatively slow process and the ageing monitoring (as was also noted in some of the surveyed articles, such as [5]) does not need to be performed for every clock cycle. It is, therefore, possible to program the FPGAs in products with a special monitoring bit file every now and then (for example, as part of the power-on self-test process) and collect information on the status of ageing, and then reprogram the FPGA with the product bit file to operate in its normal operational mode. In this type of ageing monitoring, a mix of different methods can be used in order to cover as many FPGA resources as possible. For example, the DSP blocks can be tested by using the TP sensors while LUTs are tested via RO sensors. For this thesis work, we will implement one such monitoring bit file for 28nm Artix-7 FPGAs from Xilinx, and we will limit the scope of monitoring to CLBs and switch boxes, for which we will use RO sensors to create a performance variation map (PV map) of an FPGA. The main idea is to observe the trend in the frequency measured by each sensor and alert when the recorded frequency is getting close to the slowest acceptable value (which is calculated by simulating the design for the slow process corner). The knowledge from the maps can also be used in the place and route flow (a.k.a. implementation or fitting in the FPGA nomenclature) to avoid using the much-aged elements or regions of the FPGA fabric. This method, has the additional benefit that the collected data can help give more insight into the used fabrication process in terms of process variation and ageing (which can be shared with the FPGA vendors). In the next chapter, we will detail our implementation of the proposed PV map.

| Pros and Cons from Authors                | Pros: Avoiding potential voltage effects<br>and RO self-heating phenomena | Pros: Avoiding RO self-heating phenomena<br>and accurately characterizing | Pros: Higher resolution and coverage                | Pros: Improving temperature sensitivity    | Pros: Higher accuracy and feasibility<br>Cons: Higher complexity | Cons: No explicitly characterizing the delay<br>of a single wire | Pros: Higher accuracy and feasibility<br>Cons: Higher complexity | Pros: Predicting the degradation due to<br>NRT1 | Cons: Not able to compute transistors | agung parameters varaes |               | Pros: Higher sensitivity and fewer resources | Cons: Difference between the experiment results and results under natural ageing | Pros: Measuring path delay of arbitrary<br>circuits and highly efficient<br>Cons: Completing the theoretical framework | Pros: Presenting degradation mitigation<br>strategies                      | Pros: Measuring the delay of all paths and<br>not increasing the complexity of the main<br>circuit | Cons: Resolution 160ps | Pros: Isolating the effects on clock skew from<br>different components in the clock network. |

|-------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------|---------------------------------------|-------------------------|---------------|----------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|

| Measurement<br>parameter and<br>subsystem | Measuring frequency<br>by Binary counter                                  |                                                                           |                                                     | Measuring frequency<br>by RNS ring counter | Measuring frequency<br>by EMA (EM probe)                         | Measuring frequency<br>by Binary counter                         | Measuring frequency<br>by EMA (EM probe)                         | Measuring frequency                             | by Binary counter                     |                         |               | Measuring frequency by<br>RNS ring counter   | Detecting changes in the<br>Transition probability by                            | Sweeping frequency                                                                                                     |                                                                            | Measuring delay by<br>sweening clock skew                                                          |                        | Measuring frequency by<br>sweeping frequency                                                 |

| Target<br>Resources                       | CLBs and<br>Interconnects                                                 | CLBs and<br>Interconnects                                                 | CLBs and<br>Interconnects                           | IIIICICOIIIICCIS                           |                                                                  | CLBs and<br>Interconnects                                        |                                                                  | LUTs                                            |                                       |                         |               | LUTs                                         | LUTs and                                                                         | Interconnects                                                                                                          |                                                                            | Combination                                                                                        |                        | Clock networks                                                                               |

| Target Boards                             | 16nm Zynq<br>XCZU7EV                                                      | 90nm Altera<br>Cyclone II                                                 | 65nm Virtex-5                                       |                                            | 90nm Spartan-3                                                   | 90nm Spartan-3                                                   | 45nm Spartan-6                                                   | 65nm Altera<br>Cvclone III                      | 65nm Altera                           | 28nm Artix-7            |               | 65nm Virtex-5                                | 65nm Altera                                                                      | Cyclone III                                                                                                            |                                                                            | 130nm Virtex-II                                                                                    |                        | 65nm Virtex-5                                                                                |

| Research Target                           | Performance variation<br>(Systematic and<br>stochastic)                   | Process variation<br>(Systematic and<br>stochastic)                       | Process variation<br>(Systematic and<br>stochastic) | Process variation                          | Process variation                                                | Process variation                                                | Ageing effects<br>(BTI vs HCI)                                   | Ageing effects<br>(NBTI)                        | Ageing effects                        | Ageing effects          | (NBTI vs HCI) | Temperature<br>distribution                  | Monitoring<br>degradation<br>(NBTI)                                              | Delay measurement                                                                                                      | Degradation analysis<br>(NBTI) and<br>degradation<br>mitigation strategies | Performance<br>variation                                                                           |                        | Process<br>variation                                                                         |

| Previous<br>Articles                      | [10]                                                                      | [11]                                                                      | [12]                                                | [13]                                       | [15]                                                             | [14]                                                             | [8]                                                              | [17]                                            | [18]                                  | [19]                    | []            | [6]                                          | [3]                                                                              | [9]                                                                                                                    | [26]                                                                       | [4]                                                                                                |                        | [21]                                                                                         |

| Sensor<br>Type                            |                                                                           |                                                                           | RO                                                  |                                            |                                                                  |                                                                  |                                                                  |                                                 |                                       |                         |               |                                              | dL                                                                               |                                                                                                                        |                                                                            | as                                                                                                 |                        |                                                                                              |

Table 3.2: A summary of the reviewed methods

|                                        | Pros and Cons from Authors                | Pros: Resolution 1ps or lower<br>Cons: External clock generation require and<br>limitation to only work for combinational<br>paths. | Pros: Detecting transistor aging and erroneous glitches due to intermittent and transient faults | Pros: Not affected by the power supply voltage<br>variations and requiring fewer resources | Pros: Lower overhead<br>Cons: Improving the robustness of the sensor<br>and increasing path delay due to the sensor<br>inclusion | Pros: Presenting a sensor insertion algorithm to<br>avoid sensors inaccuracy | Pros: Fewer resources      | Pros: Avoiding unnecessary sensor insertion<br>and performance loss due to sensor insertion |

|----------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------|

| previous page                          | Measurement<br>parameter and<br>subsystem | Measuring frequency by<br>sweeping frequency                                                                                        | Monitoring late transition                                                                       | Monitoring late transition                                                                 | Monitoring late transition                                                                                                       |                                                                              | Monitoring late transition | Frequencies (Counter)<br>and Time                                                           |

| Table 3.2 continued from previous page | Target<br>Resources                       | CLBs                                                                                                                                | CLBs                                                                                             | CLBs                                                                                       | CLBs                                                                                                                             | CLBs                                                                         | CLBs                       | CLBs                                                                                        |

| Table                                  | Target Boards                             | 90nm Altera<br>Cyclone-II                                                                                                           | 65nm Virtex-5                                                                                    | 90nm Spartan-3                                                                             | 28nm Virtex7                                                                                                                     | 40nm Virtex6                                                                 | 28nm Virtex7               | 28nm Virtex7                                                                                |

|                                        | Research Target                           | Performance<br>variation                                                                                                            |                                                                                                  | Aging monitoring                                                                           |                                                                                                                                  |                                                                              |                            | Process variation<br>and ageing monitoring                                                  |

|                                        | Previous<br>Articles                      | [20]                                                                                                                                | [2]                                                                                              | [22]                                                                                       | [23]                                                                                                                             | [24]                                                                         | [25]                       | [7]                                                                                         |

|                                        | Sensor<br>Type                            |                                                                                                                                     | SR                                                                                               |                                                                                            |                                                                                                                                  | ·                                                                            |                            |                                                                                             |

| e.        |

|-----------|

| pag       |

| previous  |

| from      |

| continued |

| 32        |

|           |

# The Proposed PV Mapping Method

Chapter 4