# Cost-Effective Design Solution for GAIM Shooting Trigger PCB & Improving the Power Distribution Network

Master's Thesis

By Marko Pajovic

Department of Electrical and Information Technology Faculty of Engineering, LTH, Lund University SE-221 00 Lund, Sweden

> Supervisor: Baktash Behmanesh Examiner: Pietro Andreani

> > 2023

#### **Abstract**

Virtual Reality (VR) shooting simulators have gained popularity as effective training and entertainment tools. GAIM is a Swedish company specializing in VR shooting simulators, offering VR headsets with physical dummy guns and rifles. These dummy weapons contain complex electronics that are prone to compilations, especially because the Printed Circuit Board (PCB) is fitted in very compact spaces inside the weapons. Small PCB size constraints will affect various aspects such as design complexity, Radio Frequency (RF) performance, Power Integrity (PI), cost etc.

This report investigates the process of replacing an RF module (ANNA-B112) with an RF chipset (nRF52832) & discrete components (crystals, chip antenna, decoupling components etc), on the already existing PCBs inside the guns/rifles, with the basis of maintaining optimal RF performance, and significantly decrease the cost (depending on the production quantity). Power integrity analysis and simulations will be conducted for both the old and new design, with a focus on enhancing the impedance characteristics of the power distribution network (PDN).

To achieve this, various processes will be tackled. Starting with the design process, which consists of symbol/footprint creation, schematic and PCB layout design. Simulations of the PCB to optimize the power integrity (PI) with PDN impedance analysis. Once the design process is finished we move on to the manufacturing and assembly process. After the assembly we have a finished PCB with mounted components, which will be ready for RF/antenna measurements and functionality verification.

# Acknowledgments

Firstly I would like to thank Sigma Connectivity and GAIM for proposing the project idea, as well as supplying software tools for designing/simulating the PCB & hardware tools for assembly and testing of the boards. Among the many helpful engineers at Sigma I in particular thank Johan Mercke for putting this project in motion, Johannes Mesfin for being an amazing supervisor, Peter Jones & Sadik Masar (RF team) for their assistance and support when it came to the RF aspect, Sasha Karadinovic & Martin Connor (e-CAD) for their deep and complex understanding of PCB design, Carl Rehnstedt for helping me with the simulations, Poon Kar Yu, Berne Svensson, and Theofilos Kotanidis for their assistance during the assembly process.

Secondly I thank my main supervisor Baktash Behmanesh for providing very helpful feedback and always steering me in the right direction.

Lastly I thank my family and friends for their support and encouragement over the last 5 months of work.

# Contents

| 1. Introduction                                       | 14 |

|-------------------------------------------------------|----|

| 1.1 Project aims and challenges                       | 15 |

| 1.1.1 Fitting the nRF chip & discrete components      | 15 |

| 1.1.2 Cost considerations                             | 15 |

| 1.1.3 Implementing ESD protection                     | 16 |

| 1.1.4 Power Integrity (PI) optimization               | 16 |

| 2. Theory                                             | 17 |

| 2.1 PCB design                                        | 17 |

| 2.1.1 Defining the stack-up                           | 18 |

| 2.1.2 What are vias?                                  | 19 |

| 2.1.3 ESD protection design techniques                | 20 |

| 2.2 RF & Antenna theory                               | 22 |

| 2.2.1 Basic building blocks of an RF system           | 22 |

| 2.2.2 Power ratios & levels                           | 25 |

| 2.2.3 Antenna power gain                              | 25 |

| 2.2.4 Sensitivity & ITU indoor propagation model      | 25 |

| 2.3 Power Integrity (PI)                              | 27 |

| 2.3.1 Power Distribution Network (PDN) bypassing      | 27 |

| 2.3.2 Dynamic voltage drop                            | 28 |

| 2.3.3 Bypassing of the Power Distribution Network     | 29 |

| 2.3.4 Defining cut-off frequency and target impedance | 30 |

| 2.3.5 Selecting the correct capacitor                 | 31 |

| 3. Methodology                                        | 37 |

| 3.1 Design process of the PCB                         | 37 |

| 3.1.1 Component library & Component creation          | 37 |

| 3.1.2 Schematic design                                | 39 |

| 3.1.3 Bill Of Materials (BOM)                         | 40 |

| 3.1.4 Setting design rules & Layout design            | 41 |

| 3.1.5 Output manufacturing files                      | 50 |

| 3.2 Analysis of the PDN                               | 50 |

| 3.2.1 Impedance of the modeled RLC network            | 51 |

|      |     | 3.2.2 Impedance measurements of the PDN on the PCB                | 52       |

|------|-----|-------------------------------------------------------------------|----------|

|      | 3.3 | Manufacturing & Assembly                                          | 53       |

|      |     | 3.3.1 Manufactured PCB before assembly                            | 53       |

|      |     | 3.3.2 Manufactured PCB after assembly                             | 53       |

|      | 3.4 | Flashing & Functionality verification                             | 54       |

|      |     | 3.4.1 Flashing the PCB with software                              | 54       |

|      |     | 3.4.2 Functionality verification protocol                         | 55       |

|      | 3.5 | RF/Antenna measurements                                           | 56       |

|      |     | 3.5.1 Total Radiated Power (TRP) measurements                     | 56       |

|      |     | 3.5.2 Conducted power measurements on the RF trace                | 57       |

|      |     | 3.5.3 Sensitivity measurements on the RF trace                    | 59       |

| 4. I | Res | ults                                                              | 60       |

|      | 4.1 | PCB design                                                        | 60       |

|      |     | 4.1.1 Fitting the nRF and discrete components                     | 60       |

|      |     | 4.1.2 ESD protection optimization                                 | 61       |

|      | 4.2 | Cost aspect                                                       | 62       |

|      |     | 4.2.1 Component cost reduction                                    | 62       |

|      |     | 4.2.2 Certification cost                                          | 64       |

|      | 4.3 | PDN impedance simulations/measurements                            | 68       |

|      |     | 4.3.1 Transient simulations on the modeled RLC network            | 68       |

|      |     | 4.3.2 Impedance simulations on the modeled RLC network            | 76       |

|      |     | 4.3.3 Impedance measurements on the PDN of GAIM 3.0 8             |          |

|      |     | 4.0 PCBs                                                          | 78       |

|      | 4.4 | Functionality verification                                        | 84       |

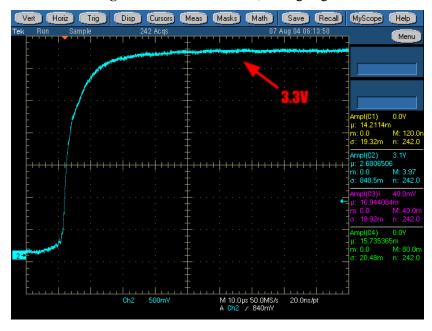

|      |     | 4.4.1 VBAT PWR measurements (GAIM 4.0)                            | 84       |

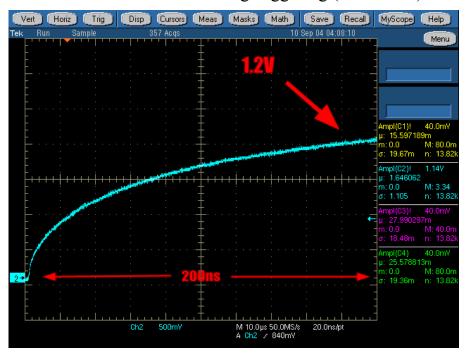

|      |     | 4.4.2 VDD measurements                                            | 86       |

|      |     | 4.4.3 GPIO measurements during triggering (GAIM 4.0)              | 91       |

|      | 4 - | 4.4.4 GPIO measurement during triggering (GAIM 3.0)               | 93       |

|      | 4.5 | RF/Antenna measurements                                           | 95       |

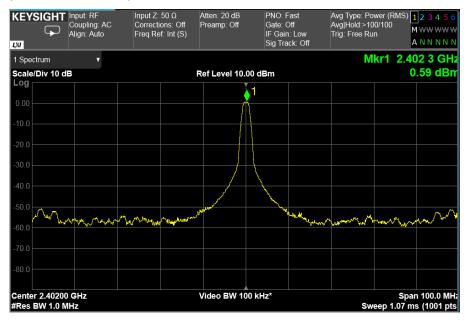

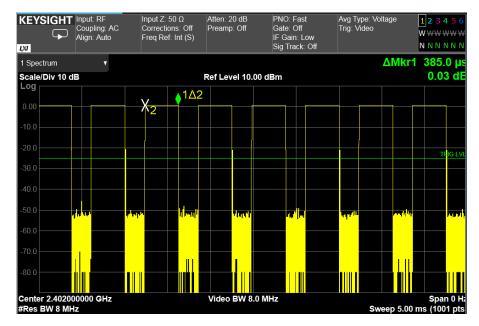

|      |     | 4.5.1 Conducted power measurements for one channel                | 95       |

|      |     | 4.5.2 Conducted power measurements for all channels               | 97       |

|      |     | 4.5.3 Total Radiated Power (TRP) measurements & Antenn efficiency | ıa<br>98 |

| 4.5.4 Sensitivity & Distance measurements | 99  |

|-------------------------------------------|-----|

| Conclusion                                | 100 |

| 5.1 PCB design                            | 101 |

| 5.2 Cost aspect                           | 102 |

| 5.3 PDN analysis                          | 103 |

| 5.4 Functionality verification            | 105 |

| 5.5 RF/Antenna measurements               | 106 |

| 5. Future Work                            | 108 |

| 6. Appendix A: Extended material          | 109 |

| A.1 Schematic                             | 110 |

| A.2 Assembly Drawing                      | 111 |

| A.3 Bill of Materials (BOM)               | 113 |

| 7. References                             | 114 |

# List of figures

| 1.1  | GAIM product, dummy gun and the trigger unit.             | 14 |

|------|-----------------------------------------------------------|----|

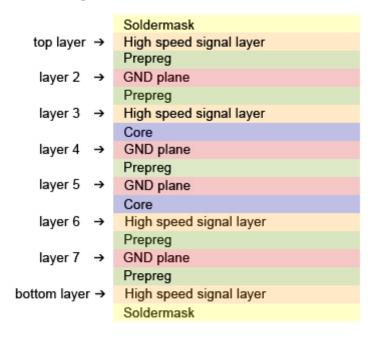

| 2.1  | Layer stack-up for an 8-layer PCB.                        | 18 |

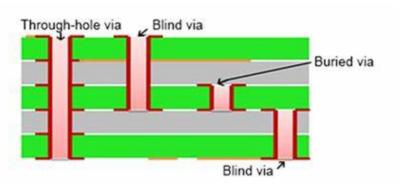

| 2.2  | Types of vias.                                            | 19 |

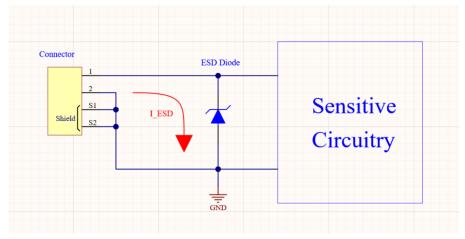

| 2.3  | Schematic representation of the ESD diode.                | 20 |

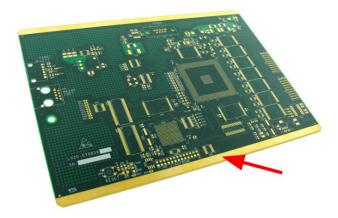

| 2.4  | PCB with exposed copper ground on the edges.              | 21 |

| 2.5  | Basic building blocks of a wireless communication system. | 22 |

| 2.6  | Basic building blocks of an RF system.                    | 23 |

| 2.7  | Simplified building blocks for the GAIM PCB.              | 24 |

| 2.8  | (a) Charging of the load cap (b) discharging of the       | 28 |

| 2.9  | Simplified model of the PDN divided into three levels     | 29 |

| 2.10 | Ideal output impedance of a passive PDN as a function     | 30 |

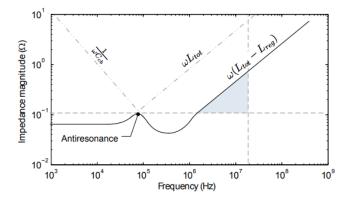

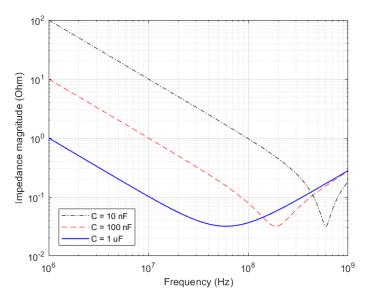

| 2.11 | Typical impedance magnitude as a function of frequency    | 31 |

| 2.12 | Bypassing capacitors will form new current loops          | 32 |

| 2.13 | Typical impedance magnitude, as a function of frequency   | 33 |

| 2.14 | Impedance when varying the number of capacitors in        | 35 |

| 2.15 | Impedance when varying the ESR.                           | 35 |

| 2.16 | Impedance when varying the ESL.                           | 36 |

| 2.17 | Impedance when varying the capacitance value.             | 36 |

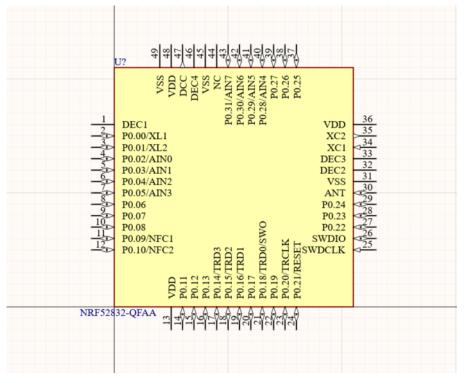

| 3.1  | Schematic symbol of the nRF chip.                         | 37 |

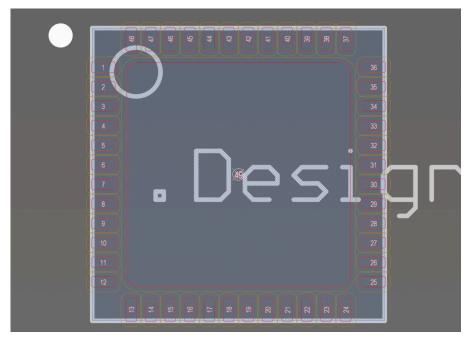

| 3.2  | Footprint for the nRF chip.                               | 38 |

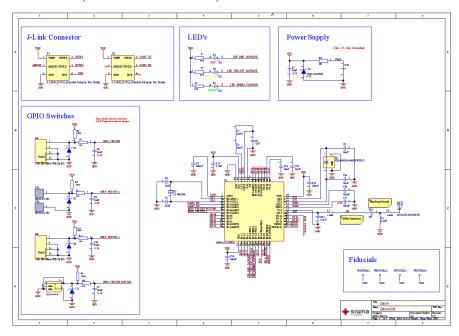

| 3.3  | GAIM Schematic.                                           | 39 |

| 3.4  | GAIM BOM.                                                 | 40 |

| 3.5  | Layer stack-up for the GAIM PCB.                          | 41 |

| 3.6  | $50\Omega$ impedance profile for GAIM PCB.                | 42 |

| 3.7  | Floorplan for GAIM 4.0.                                   | 45 |

| 3.8  | Top Layer (Signal/Power).                                 | 47 |

| 3.9  | Layer 2 (Signal).                                         | 47 |

| 3.10 | Layer 3 (GND).                                             | 48 |

|------|------------------------------------------------------------|----|

| 3.11 | Bottom Layer (Signal).                                     | 48 |

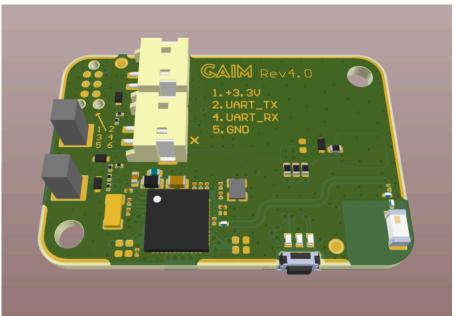

| 3.12 | GAIM 4.0 PCB.                                              | 49 |

| 3.13 | Modeled GAIM PCB using an RLC network.                     | 50 |

| 3.14 | Impedance network, including the decoupling capacitor.     | 51 |

| 3.15 | Impedance network, excluding the decoupling capacitor.     | 52 |

| 3.16 | (a) Top side of the manufactured PCB (b) Bottom side of    | 53 |

| 3.17 | Top and bottom side of the assembled GAIM PCB.             | 53 |

| 3.18 | Flashing the PCB using J-Link.                             | 54 |

| 3.19 | RF chamber for radiated measurements.                      | 56 |

| 3.20 | GAIM 4.0 PCB with smp connector, soldered to the RF trace. | 57 |

| 3.21 | Conducted measurements, by manually sweeping               | 58 |

| 4.1  | PCB from the previous revision of GAIM (Rev3.0)            | 60 |

| 4.2  | New revision of the GAIM PCB, fitted with nRF              | 61 |

| 4.3  | The total production cost per board, proportional to       | 66 |

| 4.4  | Interception point between the ANNA module and nRF chip.   | 67 |

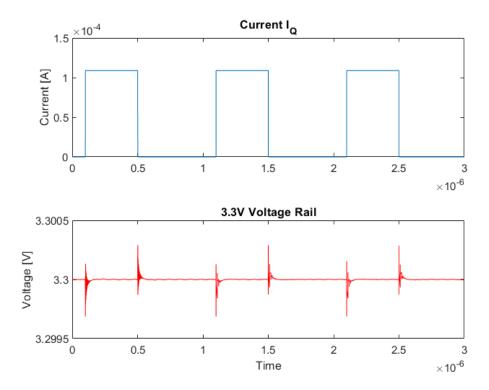

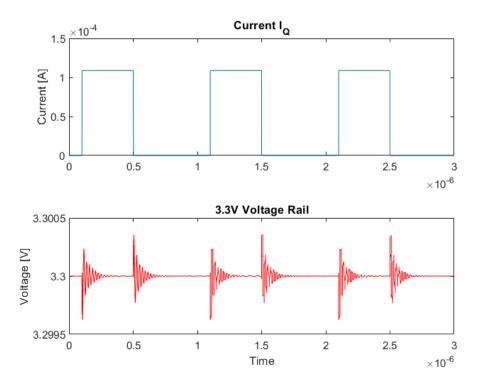

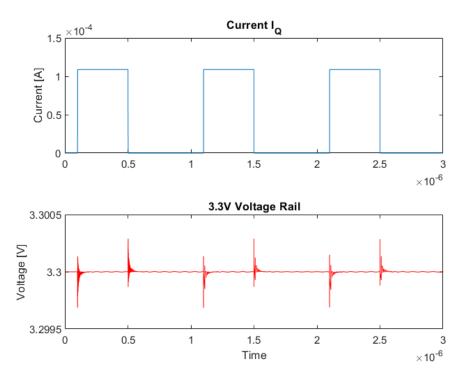

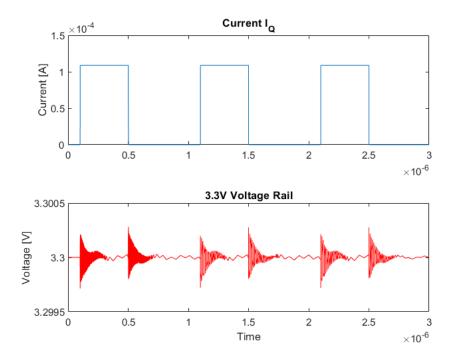

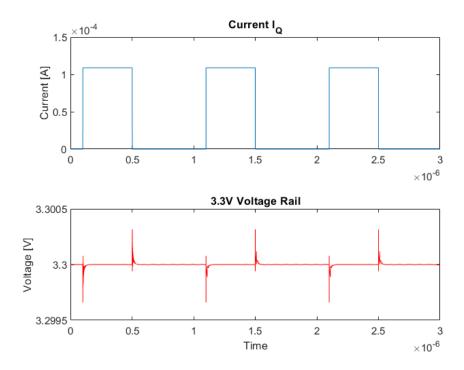

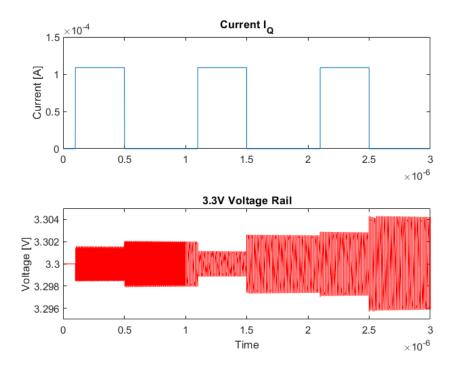

| 4.5  | Transient simulation, C=100nF, ESR=0.50hm, ESL=1nH.        | 68 |

| 4.6  | C=1nF, ESR=0.5Ohm, ESL=1nH.                                | 69 |

| 4.7  | C=1000nF, ESR=0.50hm, ESL=1nH.                             | 70 |

| 4.8  | C=100nF, ESR=0.05Ohm, ESL=1nH.                             | 71 |

| 4.9  | C=100nH, ESR=1 Ohm, ESL=1nH.                               | 72 |

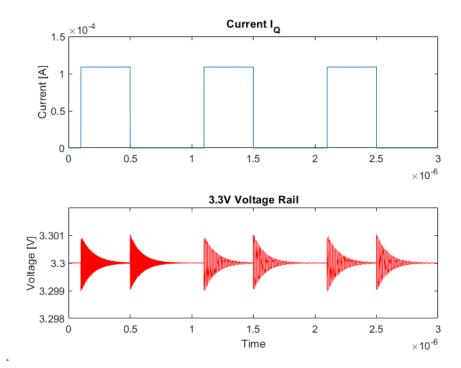

| 4.10 | C=100nF, ESR=0.50hm, ESL=10nH.                             | 73 |

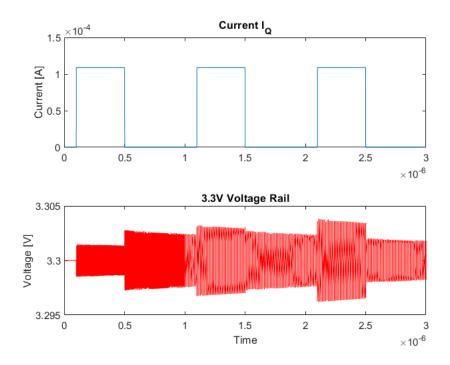

| 4.11 | C=100nF, ESR=0.50hm, ESL=100nH.                            | 74 |

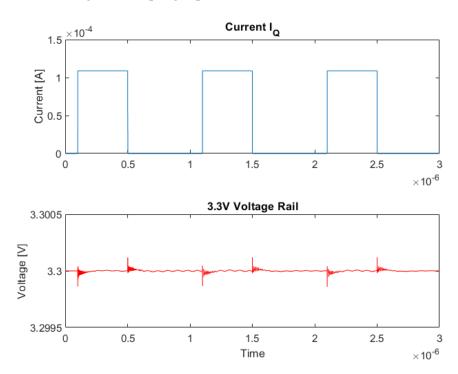

| 4.12 | C=100nF, ESR=0.50hm, ESL=1nH, with multiple decoupl        | 75 |

| 4.13 | No decoupling capacitors.                                  | 76 |

| 4.14 | Impedance simulations of the modeled GAIM RLC network.     | 77 |

| 4.15 | AC impedance simulation, with no decoupling capacitors.    | 78 |

| 4.16 | AC sim, all decoupling capacitors are C=100nF.             | 79 |

| 4.17 | AC sim, all decoupling capacitors are C=1uF.                    | 80 |

|------|-----------------------------------------------------------------|----|

| 4.18 | AC sim, all decoupling capacitors are C=4.7uF.                  | 80 |

| 4.19 | All decoupling capacitors are C=100nF in parallel with C=1uF.   | 81 |

| 4.20 | AC sim, all decoupling capacitors are C=1nF.                    | 82 |

| 4.21 | AC impedance simulation, no decoupling capacitors (GAIM 3.0).   | 83 |

| 4.22 | Measurements on the main VBAT power node.                       | 84 |

| 4.23 | Measurements on the first (and only) VBAT node.                 | 85 |

| 4.24 | VDD measurements on the LED resistors.                          | 86 |

| 4.25 | VDD measurements on the big capacitor near nRF.                 | 87 |

| 4.26 | VDD measurements on the small capacitor near nRF.               | 87 |

| 4.27 | VDD measurements on the PU resistor on connector 1.             | 88 |

| 4.28 | VDD measurements on the PU resistor on connector 2.             | 88 |

| 4.29 | VDD measurements on the PU resistor on the button.              | 89 |

| 4.30 | VDD on the big capacitor near nRF during switch-on.             | 90 |

| 4.31 | Measurements on switch 1, falling edge during a trigger switch. | 91 |

| 4.32 | Connector 1, rising edge during a trigger switch.               | 91 |

| 4.33 | Button switch, falling edge.                                    | 92 |

| 4.34 | Button switch, rising edge.                                     | 92 |

| 4.35 | Connector 1, rising edge during a trigger switch on GAIM 3.0.   | 93 |

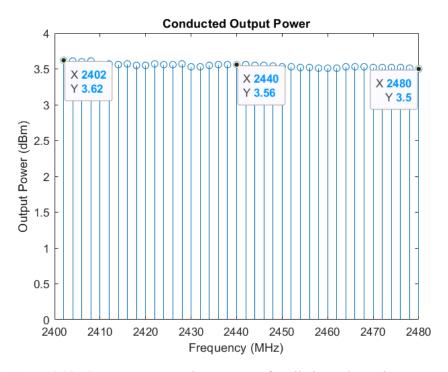

| 4.36 | Signal on the RF trace in the frequency domain.                 | 95 |

| 4.37 | Signal on the RF trace in the time domain.                      | 96 |

| 4.38 | Output power on the RF trace, for all channels on the BLF       | 97 |

# List of tables

| Table 3.1 | Clearances for different nets.                          | 43  |

|-----------|---------------------------------------------------------|-----|

| Table 3.2 | Clearances with 50 OHM impedance characteristics        | 43  |

| Table 3.3 | Trace width for any arbitrary signal                    | 44  |

| Table 3.4 | Trace width for power signals                           | 44  |

| Table 3.5 | Trace width for a 50 OHM impedance trace                | 44  |

| Table 4.1 | Total component cost of the old revision of GAIM (SEK). | 62  |

| Table 4.2 | Component cost for the new revision of the board (SEK). | 63  |

| Table 4.3 | The certification cost per unit, proportional to the    | 64  |

| Table 4.4 | The certification cost per unit, proportional to the    | 65  |

| Table 4.5 | TRP measurements and antenna efficiency on the new      | 98  |

| Table 4.6 | TRP measurements and antenna efficiency on the new      | 98  |

| Table 4.7 | TRP measurements and antenna efficiency on the old      | 99  |

| Table 4.8 | RF performance for GAIM 4.0 PCB.                        | 100 |

| Table 4.9 | RF performance for GAIM 3.0 PCB.                        | 100 |

# List of acronyms

BOM Bill Of Materials

BLE Bluetooth Low Energy

CF Carrier Frequency

CPU Central Processing Unit

DUT Device Under Test

DRC Design Rule Check

e-CAD Electronic Computer-Aided Design

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

ESD Electro-Static Discharge

ESL Equivalent Series Inductance

ESR Equivalent Series Resistance

GND Ground

GPIO General Purpose I/O

HF High-frequency

HFCLK High Frequency Clock

I/O Input/Output

LFCLK Low Frequency Clock

LO Local Oscillator

L1 Layer 1

L2 Layer 2

L3 Layer 3

L4 Layer 4

PCB Printed Circuit Board

PDN Power Distribution Network

PI Power Integrity

PWR Power

Rev Revision

RF Radio Frequency

SMD Surface-Mounted Device

SoC System-On-Chip

TRP Total Radiated Power

VCO Voltage Controlled Oscillator

VR Virtual Reality

# Popular Science Summary

Virtual Reality (VR) has transformed various industries and had a significant impact in the training arena [23]. Industries such as shooting simulators have gained popularity as training and entertainment tools. Everything from effective training for law-enforcement and military, to having a fun night with some friends in the living room hunting animals in a simulated VR world. Virtual reality aims to replicate an environment that stimulates the senses, primarily sight and sound, to create an artificial world that feels real [23].

Dummy guns and rifles with complex electronics that connect via bluetooth to the VR headset, are prone to complications with the rapid development of technology and the miniaturization of the printed circuit board (PCB). Complications such as design complexity and expensive components.

This thesis project aims to investigate a more cost-effective solution for an already existing electronics trigger device, situated in a dummy gun that is used for shooting simulations. The goal is to reduce the component cost and upgrade some electrical properties for the new PCB, while still maintaining the desired bluetooth connection with the VR headset. To achieve this, various processes will be tackled. Processes such as a full re-design of the PCB, therefore decreasing the component cost and upgrading the electrical properties. Various simulations, verifications and measurements will be systematically performed on the manufactured PCB to ensure proper functionality, and desired bluetooth connection is maintained

## 1. Introduction

Virtual Reality (VR) shooting simulators have gained popularity as effective training and entertainment tools. GAIM is a Swedish company specializing in VR shooting simulators, offering VR headsets with physical dummy guns and rifles.

**Figure 1.1:** GAIM product, dummy gun and the trigger unit [1].

These dummy weapons contain a trigger unit with complex electronics that are prone to compilations, especially because the Printed Circuit Board (PCB) is fitted in very compact space. Small PCB size constraints will affect various aspects such as design complexity, Radio Frequency (RF) performance, power consumption, cost etc.

In order for the simulations to be operating as smoothly as possible the communication between the electronics in the trigger unit and the VR headset needs to be optimal. The communication protocol between the electronics and the VR headset are done through an RF module using Bluetooth. These RF modules are usually very expensive, and are major components that affect the profit margins, especially when the production quantity is very high. Replacing the RF module with an RF chipset and discrete components is a solution for the cost aspect, and can decrease the component cost upwards to 30%.

## 1.1 Project aims and challenges

The goal of this master's thesis is to re-design the PCB, by replacing the currently used RF module (ANNA-B112 [3]) with an RF chipset (nRF52832 [4]) and some discrete components. Discrete components such as, crystals (32.768kHz & 32MHz), chip antenna (2450AT18A0100001E [5]) which is a 2.4GHz surface-mounted device (SMD), matching network for the antenna that consists of capacitors and high-frequency (HF) inductors, and a bunch of decoupling components such as capacitors, inductors and resistors, making a fully functional trigger PCB for the VR shooting simulation.

## 1.1.1 Fitting the nRF chip & discrete components

Swapping the RF module with an RF chipset presents a major challenge in the design process. Fitting the nRF chipset and discrete components on the same PCB outline that is currently used with the ANNA module. The reason GAIM does not want to change the PCB outline is because they want to use the same mechanical parts for the trigger that are currently used in their weapons. A major goal is to find a suitable floorplan for the components to make sure all the new components fit on the same board, while following design and RF rules. A floorplan is essentially the most ideal component placement considering the board outline.

#### 1.1.2 Cost considerations

As mentioned in the first section of the introduction, RF modules can be very expensive. Swapping the modules with discrete components might reduce the component cost upwards to 30%, which on a large production scale can have a large impact on the profit margins. However, having discrete components introduces another cost aspect. Certifications. Usually when dealing with RF modules you only need to undertake one certification ,which measures radiated emissions. However, dealing with discrete components there are two certifications that need to be done. Certification for radiated emissions (just like the RF module), and conducted emissions.

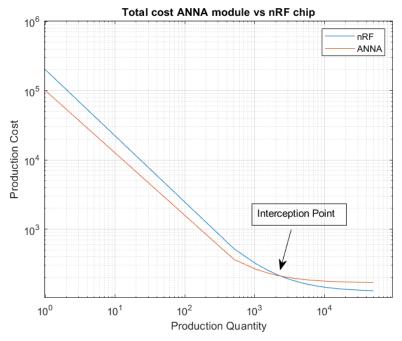

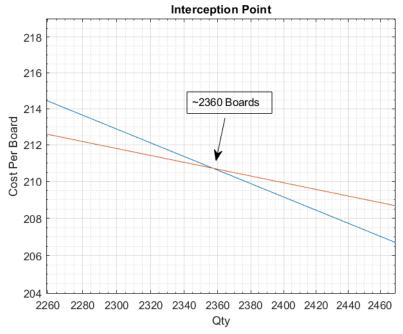

In this report we will investigate the cost aspect. Depending on the production quantity, what will be less costly? Using an RF module or using the RF chipset with discrete components? Small quantities will result in the certification costs for the chipset with discrete components being much more expensive than the certification cost for the RF module. Very large quantities will result in the certification costs being negligible for both the

module and chipset, thus the cost factor will mostly be defined by the component cost.

#### 1.1.3 Implementing ESD protection

On the previous PCB design there were no electro-static discharge (ESD) protection design techniques implemented. Electrostatic discharge is the sudden release of built-up charge between objects, causing electricity to flow between them. Electrostatic discharge is enough to damage many semiconductor parts including MOSFETs, diodes and CMOS IC chips such as CPUs and graphic ICs.

In this report we will implement various ESD protection circuitry and ESD design techniques.

#### 1.1.4 Power Integrity (PI) optimization

As electronic circuits have been scaled down, so have their absolute voltage margins. It is therefore getting increasingly important to be able to control that the supply voltage is steadily kept at the right level. Alternating currents in the power delivery network (PDN) will cause the voltage to vary outside the margins if the power network impedance is not correctly adjusted. This means that there could be induced voltages in the power distribution network in the circuit, causing components on the PCB to get lower reference voltages. In this report we will investigate such adjustments in the power distribution network (PDN) of our design, by simulating and incorporating different design techniques such as bypassing for better impedance control on the PDN.

# 2. Theory

In order to understand the discoveries of this project we will go through some theoretical aspects, such as PCB design, techniques, and standards used in the 21th century. We will also dive into the realm of Radio Frequency (RF), and discuss the basics of RF communication systems and their central building blocks (which is implemented in both the RF module and the RF chipset). Lastly we will discuss the importance of power integrity optimization and how it is done in the power distribution network of the design.

# 2.1 PCB design

The basic building blocks of modern electronics are printed circuit boards (PCBs), which link and interconnect different components to create working systems. PCB design is a crucial stage of the product development cycle, enabling us to convert theoretical concepts of electronic circuits to physical devices.

The quality of the PCB design plays a major role in determining the performance, reliability, and manufacturability for the final product. It is your job as an electronics engineer to design the PCB such that it follows all desired specifications for the application it is intended for, while adhering to all the design rules in order for the PCB to be manufacturable.

The rapid development of modern electronics has been pushing PCBs towards miniaturization, high speed, better functionality, reliability, and longer lifetime, resulting in the popularity of multilayer boards. Using a semi-solid adhesive called prepreg to combine two or more single and/or double-sided PCBs, creating multilayer PCBs, with a solid and thick core in the middle. With the increase of complexity and densities, it is plausible for issues to arise, such as noise, stray capacitance, and crosstalk when layer arrangement is inefficiently designed [6].

Optimal arrangement for a multilayer stack-up is one of the crucial elements in determining the electromagnetic compatibility (EMC) performance of a device. A correctly defined stack-up can minimize the radiation, but also protect the circuit board from external noise interference. However a poorly designed stack-up may encounter electromagnetic interference (EMI) radiation. In the next section we will discuss and define a PCB stack-up.

### 2.1.1 Defining the stack-up

Stack-up illustrates the arrangement of copper and insulating layers that construct the printed circuit board. There are many advantages of having a well-defined multilayer stack-up.

Firstly a multilayer stack-up allows you to get more circuitry on a single board through the various layers inside the PCB.

Secondly the PCB stack-up can help minimize circuit vulnerability, such as external noise, minimize radiation, and help with impedance mismatch [20].

Lastly a well-defined stack-up can minimize for low-cost, staying well above the minimum manufacturing capabilities will decrease the manufacturing cost.

General layers for a well-designed stack-up may include ground planes (GND), power planes (PWR), and signal layers. Here is an example of an 8-layer PCB stack-up.

Figure 2.1: Layer stack-up for an 8-layer PCB [6].

#### 2.1.2 What are vias?

As mentioned in section 2.1.1, multilayer stack-ups allow us to fit more circuitry in the various layers inside the PCB. This raises some questions. How are the layers inside connected to each other? Can the same signal be on every layer? Introducing vias, vias are small drilled holes that go through two or more adjacent layers. It allows signals to move between layers, which means the same signal can be on every layer. Vias are commonly categorized into three types—blind via, buried via and through-hole via. In this project only through-hole vias are used, and are the least expensive to drill during the manufacturing process.

Through-hole vias span from one outer layer (top layer) all the way to the other outer layer (bottom layer), and is the most commonly used type of via. While spanning from one outer layer to the other, it connects all the inner layers [7] [19].

Figure 2.2: Types of vias [7].

Figure (2.2) demonstrates the different types of vias on a 6-layer PCB stack-up. The through-hole via goes through the entire board, connecting each and every of the six layers.

#### 2.1.3 ESD protection design techniques

During a lifetime of a PCB there is a high likelihood of encountering electrostatic discharge, especially circuits that are meant to interface with the physical environment [8]. The design for this project will be enclosed in a trigger unit as mentioned in section 1.1.1. However that does not mean it is not prone for electrostatic discharge, since there are connectors on the PCB intended for external communication. ESD protection is an important aspect when it comes to design techniques, and is intended to protect sensitive components from blowing during an ESD event. Commonly, static charge accumulates during the operation of a PCB, which causes the electrostatic discharge to occur. By strategically placing ESD protection in the design, it will protect sensitive circuitry [8] [17].

There are various ESD protection techniques, but in this project I will only discuss the ESD protection that will be implemented in the GAIM PCB.

First ESD protection design technique implemented is ESD diodes on every external connector. Regarding the placement of ESD diodes on the PCB, it is important to keep the diodes as close as possible to the external connectors. Keeping the diodes close to the connectors will make the travel path for the static electricity miniscule, and protect the circuitry that comes after the diode [18].

**Figure 2.3:** Schematic representation of the ESD diode.

Figure (2.3) illustrates the intended use of an ESD protection diode. Where  $I\_ESD$  is the electrostatic discharge current, going from the connector through the ESD diode.

The second ESD protection technique implemented in this design is solely done in the layout design, where no extra components are needed. As we know from section 2.1.1, the top and bottom of the stack-up are covered in a non-conductive insulating thin layer called solder mask, which gives a circuit board the green color. By removing the solder mask on the edges of the board, we expose the copper ground plane. During an ESD event the discharge will go directly to ground from the edges and protect sensitive components.

**Figure 2.4:** PCB with exposed copper ground on the edges [9].

Figure (2.4) illustrates the exposed copper ground on a PCB. This ESD protection design technique will be implemented on the GAIM PCB.

## 2.2 RF & Antenna theory

Since this master's thesis is not extensively about RF communication, I will not go into great details about this topic. Only the most basic principles and equations will be discussed.

### 2.2.1 Basic building blocks of an RF system

The basic building blocks of a wireless communication system is shown in figure (2.5):

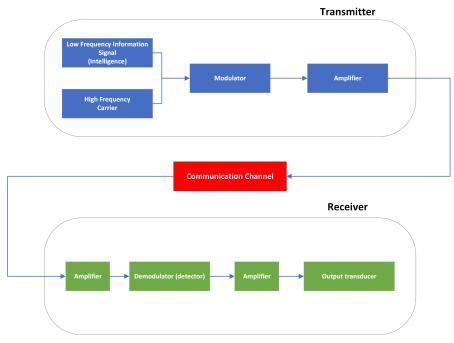

Figure 2.5: Basic building blocks of a wireless communication system [22].

There are three major aspects in a wireless communication system, the transmitter, a communication channel, and the receiver. To simplify the theory, a transmitter transformers information into signals, and sends it through a communication channel (such as power lines, cables, air etc). The receiver then converts those signals back into the same information.

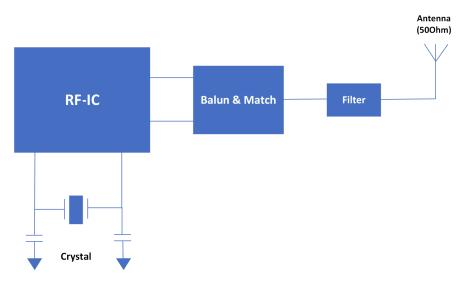

Figure 2.6: Basic building blocks of an RF system [22].

Figure (2.6) illustrates the basic building blocks for a typical RF system. It consists of a central processing unit (CPU), such as a transmitter, receiver, transceiver, or a system-on-chip (SoC) with an integrated microcontroller.

There is a crystal, which is typically used for the reference frequency for the local oscillator (LO) and the carrier frequency (CF).

The balun circuitry converts a differential signal to a single-ended signal, or vice versa.

A matching network for the antenna, which is used for impedance matching. In electronics, impedance matching is the practice of designing or adjusting the input impedance or output impedance of an electrical device for a desired value. Often, the desired value is selected to maximize power transfer or minimize signal reflection.

Filters are used to improve selectivity, which means filtering un-desired frequencies such as high frequency noise.

Lastly there is an antenna with 50 OHM impedance, intended for correct impedance matching.

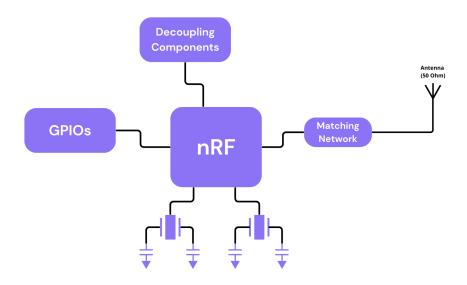

Figure 2.7: Simplified building blocks for the GAIM PCB.

Figure (2.7) illustrates a simplified RF block diagram for the new GAIM PCB. It consists of two crystal oscillators, one for the high frequency clock (HFCLK), and the other one for the low frequency clock (LFCLK). The HFCLK is for the CPU and requires a 64MHz clock signal for optimal operation. The LFCLK is distributed to different peripherals, and requires a 32.768kHz clock signal.

For this project only two general purpose I/Os (GPIOs) will be used. A button (will be used for reset, and other tasks), and a connector (that will be connected to the mechanical trigger unit, refer to figure (1.1)).

The matching network, used for 50 OHM impedance matching with the 2.4 GHz antenna. Which is an industry standard frequency for bluetooth.

A cluster of decoupling components will be used for supplying power for the nRF chip, and controlling the impedance on the power distribution network.

#### 2.2.2 Power ratios & levels

When dealing with RF most voltages and powers are referred to in dB. Here are some relevant power ratios and power levels [13]:

$$P = 10 * log(\frac{P_1}{P_2})$$

$[P] = dB$  (2.2.1)

$$P' = 10 * log(\frac{P_3}{1mW})$$

$[P'] = dBm$  (2.2.2)

Where P is the power represented in dB, P' is the power represented in dBm and is referenced with 1mW.  $P_1$ ,  $P_2$ , and  $P_3$  are in watts.

#### 2.2.3 Antenna power gain

Antennas are made with conductors with finite conductivity, which makes them susceptible to ohmic power loss [13]. The total input power is:

$$P_{in} = P_{i} + P_{rad} (2.2.3)$$

Where  $P_{in}$  is the power accepted by the antenna at its terminals during the radiation process,  $P_{rad}$  is the power radiated by the antenna, and  $P_l$  the power dissipated within the antenna [13].

To calculate the efficiency we use:

$$\eta_r = \frac{P_{rad}}{P_{in}} \tag{2.2.4}$$

Where  $\eta_r$  is the radiation efficiency of the antenna.

#### 2.2.4 ITU indoor propagation model & Sensitivity

This section will provide a brief overview of sensitivity and the ITU indoor propagation model.

The ITU indoor propagation model is a radio propagation model that estimates the path loss in a closed area, such as a building with any form of walls. This model is suitable for appliances designed for indoor applications that use the lower microwave bands, such as 2.4GHz [24] [25].

The ITU model is formally expressed like this:

$$L = 20log_{10}(f) + Nlog_{10}(d) + P_f(n) - 28$$

(2.2.5)

$$L = |S - P_{out}| \tag{2.2.6}$$

Where L is the path loss expressed in dB, f is the frequency of transmission in MHz, N is the distance power loss coefficient, d is the distance in meter,  $P_f$  is the floor loss penetration factor, which will be zero in this case, n is number of floors between the transmitter and receiver, also zero. S is the sensitivity after the antenna,  $P_{out}$  is the total radiated power, also called  $P_{rad}$ .

For this project we are interested in solving for the distance d, on both the old and new PCB. Comparing the distances we can figure out which PCB has better RF performance.

Sensitivity serves as an indicator, reflecting a device's ability to receive and decode a signal within a specified 'satisfactory error rate,' which is typically defined by the specifications of each application. The measurement of sensitivity is expressed in power levels, such as -100 dBm [26].

# 2.3 Power Integrity (PI)

The circuitry on a modern PCB requires the voltages and currents to be maintained at necessary levels within the power delivery networks (PDN), with minimal fluctuation. Variations in the PDN can cause performance degradation of the signals and cause false responses [11].

### 2.3.1 Power Distribution Network (PDN) bypassing

As electronic circuits have been scaled down, so have their drive voltages. This means that the absolute voltage margins are decreasing and it is getting increasingly important to be able to control that the drive voltage is steadily kept at the right level [12]. If the voltage ends up outside the margins, the digital logic might run slow or even malfunction [11].

The power distribution system connects the power domains of the chip to a voltage regulator that supplies the drive voltage (in this project the supply voltage comes from a cell battery). There are two aspects to consider when keeping the drive voltage controlled: the impedance of the PDN and the characteristics of the current flowing in the PDN. Combined they cause a total voltage drop [13]:

$$\Delta V = IR + L \frac{di}{dt} \tag{2.3.1}$$

There is a quasi static part called the IR drop, and a dynamic part. The focus will be on lowering the resistances related to the power grid of the chip, the bondwires, and the planes and traces of the package and the PCB.

The next section will deal with dynamic voltage drop. However, it will be shown that it is important to manage the PDN impedance over a wide frequency range including DC.

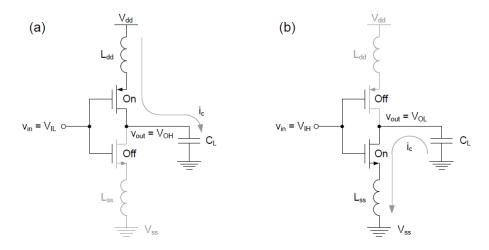

#### 2.3.2 Dynamic voltage drop

Most of the modern digital circuits are based on CMOS technology (including the nRF chip used in this project). To illustrate the dynamic voltage drop we will use complementary MOSFET transistors that are connected in series between power and ground, as shown in figure (2.8). The inductances of the power and ground conductors, connecting the circuit to the voltage regulator, are represented by  $L_{DD}$  and  $L_{SS}$ , while the capacitive load is shown as  $C_L$ . For simplicity the model  $C_L$  includes the output capacitance of the circuit, pad, package, and trace capacitances.

**Figure 2.8:** (a) Charging of the load capacitance when switching from low to high on the output and (b) discharging of the load when switching from high to low on the output [10].

During a switch when the MOSFETs change states, the current will either charge or discharge the load capacitance. This means that there will be a current flowing through the inductances [14]:

$$i_c = C_L \frac{v_c}{dt} \tag{2.3.2}$$

From Faraday's law of induction we know that variations in current flow will induce a voltage drop across inductive circuitry [13]:

$$V_L = L \frac{di}{dt} \tag{2.3.3}$$

Where L is the inductance,  $V_L$  is the voltage across the inductor, and di is the current variations. The rapid charging / discharging will therefore change the power / ground potential at the circuit relative to the Vdd / Vss regulator reference. The potential difference  $\Delta V$  is proportional to the inductances  $L_{dd}$  /  $L_{ss}$  of the PDN.

A way to decrease these voltage variations is to lower the inductance of the PDN current loop. For instance, the inductance scales linearly with the length of the conductors, which hence should be kept as short as possible. It is also affected by a number of other parameters related to the routing and PCB layer dimensions, such as the thickness of the dielectric layers between planes and traces. Another method for decreasing the effective inductance is bypassing. The impedance is then decreased by shortening the current loops with capacitors.

#### 2.3.3 Bypassing of the Power Distribution Network

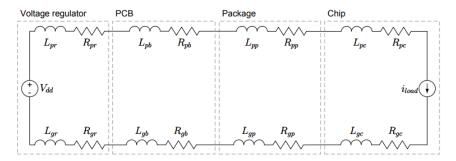

There are three stages of a PDN: chip, package, and PCB [15]. The power and ground rails on the chip are connected to the power and ground conductors on the package, which in turn are connected to the power and ground planes on the PCB where the regulator is situated. The simplified model of a PDN can be seen in figure (2.9). The indices describe what net the element belongs to. The p stands for power, g ground, r regulator, p board, p package, and p chip. Meaning p would represent the power on the board net.

**Figure 2.9:** Simplified model of the PDN divided into three levels (PCB, package, and chip) [10].

From figure (2.9) we see that the PDN can be represented as a RL network. The impedance, as a function of frequency, becomes:

$$Z(\omega) = R_{tot} + j\omega L_{tot}$$

(2.3.4)

Where  $R_{tot}$  and  $L_{tot}$  are the total power and ground conductor resistances and inductances. This means that the distance between the chip and the regulator can be a couple of centimeters depending on how long the traces/planes are on the PCB, thereby making this current loop very inductive.

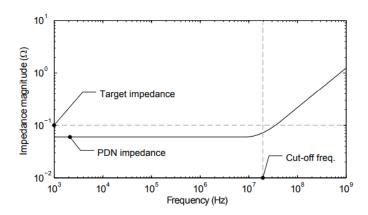

The supply current is in general composed of frequency components covering a broad spectrum starting at DC. The overall aim is to assure that the magnitude of the output impedance of the PDN is low for the whole bandwidth of the current waveform. This is illustrated in figure (2.10), where the cut-off frequency defines the current bandwidth, while the target impedance defines the impedance to meet or reach below. In our applications, where we only control the board level PDN, the cut-off frequency is often set to a value defining the frequency beyond which the package and chip are designed to handle the bypassing.

**Figure 2.10:** Ideal output impedance of a passive PDN as a function of frequency. The cut-off frequency defines the current bandwidth, while the target impedance defines the impedance to meet or stay below [10].

# 2.3.4 Defining cut-off frequency and target impedance

The target impedance is calculated by Ohms law:

$$Z_{target} = \frac{\Delta V}{\Delta I_{MAX}} \tag{2.3.5}$$

$\Delta V$  is the maximum allowed voltage fluctuation for the components (IC),  $\Delta I_{MAX}$  is the maximum current variations, meaning it is not the maximum current drawn at any specific moment, but instead the change in

rate of the current. As an example, let us assume that a chip will step the current from 700mA to 1500mA in 25ns. If the voltage drop across the PDN is estimated to be 50mV, the target impedance would then be according to (2.3.5):

$$Z_{target} = \frac{50mV}{(1500-700)mA} = 62.5m\Omega$$

When optimizing the PDN impedance it is relevant to have a decent estimation of the current bandwidth, meaning the highest frequency component of the current waveform during normal operation of the chip. Which will represent the cut-off frequency:

$$f_{co} = \frac{1}{\pi \cdot t_r} \tag{2.3.6}$$

Where  $t_r$  is the rise-time of the waveform, and  $f_{co}$  is the cut-off frequency/bandwidth [16].

Next section will discuss the actual impedance of the PDN, in the frequency range that needs to be addressed by the PCB and packaging bypass capacitors.

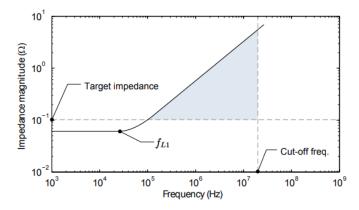

# 2.3.5 Selecting the correct capacitor

As shown in figure (2.9) the PDN can be described as an RL network. Plotting the magnitude of the impedance will give us the figure (2.11).

**Figure 2.11:** Typical impedance magnitude as a function of frequency for a PDN without bypassing capacitors. The shaded area indicates a violation of the impedance requirement.

The total impedance is mostly determined by the resistance up to the frequency  $f_{Ll}$ , which is determined by [16]:

$$f_{L1} = \frac{R_{tot}}{2\pi L_{tot}} \tag{2.3.7}$$

Above  $f_{LI}$  the inductance  $L_{tot}$  will be the main contributor for the impedance of the PDN according to (2.3.4).

In order to keep the impedance low on the PDN, we need to create new current loops when the impedance exceeds the target impedance:

$$f = \frac{Z_{target}}{2\pi L_{tot}} \tag{2.3.8}$$

To create new current loops that decouples the high inductances on the regulator, is done by placing one or more capacitors on the PCB between power and ground. As shown in figure (2.12), there will be two current loops.

**Figure 2.12:** Bypassing capacitors will form new current loops in the PDN, here shown as a new loop created by a capacitor on the PCB.

The capacitor is placed in parallel to the voltage regulator, and the impedance seen from the load will therefore be:

$$Z(\omega) = (R_{cb} + \frac{1}{j\omega C_{cb}} + j\omega L_{cb})||(R_{pr} + R_{gr} + j\omega (L_{pr} + L_{gr}))$$

Which can be simplified to:

$$\begin{split} R_{reg} &= R_{pr} + R_{gr} \\ L_{reg} &= L_{pr} + L_{gr} \\ Z(\omega) &= (R_{cb} + j(\omega L_{cb} - \frac{1}{\omega C_{cb}}))||(R_{reg} + j\omega L_{reg}) \end{split} \tag{2.3.9}$$

The bypassing capacitance and the regulator inductance will form a parallel resonant circuit damped by the resistances of the regulator and the capacitor.

**Figure 2.13**: Typical impedance magnitude, as a function of frequency, for a PDN with a single set of bypassing capacitors.

The parallel resonance, also called antiresonance will cause the impedance to peak, as seen on figure (2.13). The peak impedance can be calculated using the quality factor Q and the characteristic impedance  $Z_0$  of the resonance circuit [10][16]:

$$Z_{peak} = QZ_0 = \frac{\omega_0 L_{reg}}{R_{reg} + R_{cb}} \sqrt{\frac{L_{reg}}{C_{cb}}} = \frac{L_{reg}}{(R_{reg} + R_{cb})C_{cb}}$$

(2.3.10)

Given that the peak impedance  $Z_{peak}$  should not exceed the target impedance  $Z_{target}$  we get:

$$Z_{peak} < Z_{target} <=> C_{cb} > \frac{L_{reg}}{(R_{reg} + R_{cb})Z_{target}}$$

(2.3.11)

This will give a minimal requirement on the bypass capacitance  $C_{cb}$ . We see from (2.3.11) that the series resistances of the capacitor  $R_{cb}$  (ESR) can lower the capacitor requirement by damping the resonance. The best results will be obtained with both  $R_{reg}$  and  $R_{cb}$  being equal to the characteristic impedance since the system then is critically damped [16].

For frequencies above the anti-resonance the PDN impedance will decrease and mainly depend on the bypass capacitance, as seen in figure (2.13). Moving up in frequency the first series resonance is found, the resonance between the capacitance from the bypass capacitor and the inductance of the new loop. This is approximated by:

$$f_{res} = \frac{1}{2\pi\sqrt{L_{reg}C_{ch}}}$$

(2.3.12)

Contrary to the parallel resonance which has a peak, the series resonance has a minimum, thereby the PDN impedance will be mostly resistive. Even higher frequencies the PDN impedance will yet again depend on the RL network, and needs to be decoupled once again, not to exceed the target impedance at:

$$f = \frac{Z_{target}}{2\pi (L_{tot} - L_{reg})} \tag{2.3.13}$$

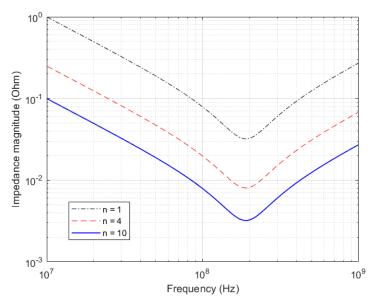

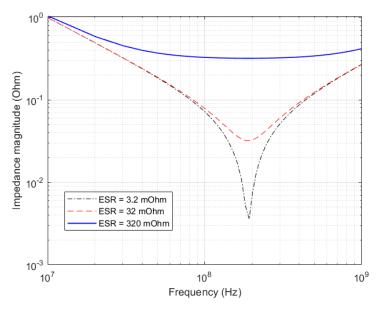

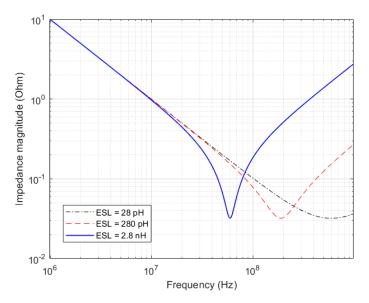

The same procedure will hence be repeated until the target impedance is met for the whole bandwidth, putting new bypassing capacitors on the PCB, closer and closer to the IC chip. A way to keep the resistive and inductive parts low on a capacitor, while increasing the capacitance, is to put several capacitors in parallel at each level of bypassing. How the impedance is affected by putting capacitors in parallel or altering their capacitance, equivalent series resistance (ESR), or inductance (ESL), is shown in figures (2.14),(2.15),(2.16), and (2.17).

**Figure 2.14:** Impedance when varying the number of capacitors in parallel, where n is the number of capacitors.

Figure 2.15: Impedance when varying the ESR.

Figure 2.16: Impedance when varying the ESL.

Figure 2.17: Impedance when varying the capacitance value.

# 3. Methodology

The following chapter explains what hardware and software were used in the design, assembly and testing process of the GAIM PCB.

## 3.1 Design process of the PCB

Software used for the design of this PCB was Altium Designer.

## 3.1.1 Component library & Component creation

For this project the existing library from the previous revision of GAIM was used. The nRF chipset and discrete component symbols and footprints were made by me using the design tool inside the library.

**Figure 3.1:** Schematic symbol of the nRF chip made by me.

Figure 3.2: Footprint for the nRF chip made by me.

The same thing is done for the rest of the discrete components that are not already in the library.

Once the symbol and footprint is created for all the necessary components, they are linked and ready for use.

## 3.1.2 Schematic design

Drawing the schematic is done by placing all the necessary components, section it out by the specific circuitry and connecting everything.

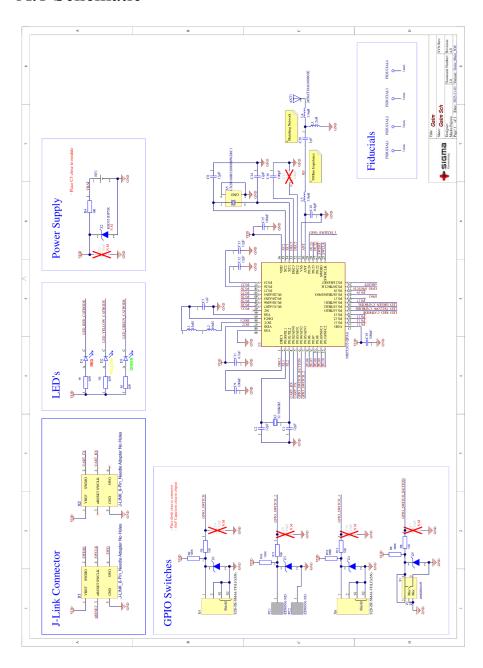

Once every component has been connected properly, with correct net-labels etc, the schematic is done, and we have a finished canvas.

Figure 3.3: GAIM Schematic.

Fig (3.3) illustrates the finished schematic, where we can clearly see each different section with specific circuitry, annotated components, and all net-names that were manually placed. For a better view of the schematic refer to Appendix A section A.1.

### 3.1.3 Bill Of Materials (BOM)

The bill of materials (BOM) is essentially a list with all the components needed for the PCB to be assembled. The BOM is divided into columns and rows. Each row represents a component. Each column represents different information about that specific component, such as a description, the designator (used for identification of a component on the board), manufacturing part number etc, as shown in figure (3.4) below.

| Designator           | Quantity | Comment                 | Description                                          | Value              | Manufacturer         | Manufacturer Part N | Supplier 1 | Supplier Part Number 1  | Rating            | Fitted |

|----------------------|----------|-------------------------|------------------------------------------------------|--------------------|----------------------|---------------------|------------|-------------------------|-------------------|--------|

| NT1                  | 1        | 2450AT18A0100001E       | Antenna RF ANT 2.4GHZ CHIP SOLDER SMD M3216          | 2.4GHz             | Johanson Technolog   | 2450AT18B100E       | Digi-Key   | 712-1006-1-ND           |                   |        |

| BT1                  | 1        | SMTU2032-LF             | BATTERY HOLDER Renata Battery Holder                 |                    | Renata               | SMTU2032-If         | farnell    | 1216354                 |                   |        |

| C1, C2, C8, C12, C13 | 6        | 12pF                    | CAP CER 12pF 25V COG, NPO 1% MO603                   | 12pF               | Murata               | GJM0335C1E120FB0    | Digi-Key   | 490-GJM0335C1E120FB01D  | 25V               |        |

| 3                    | 1        | 1uF                     | CAP CER 1uF 10% 16V X7R M1608                        | 1uF                | Murata               | GCM188R71C105KA     | Digi-Key   | 490-5241-1-ND           | 16V               |        |

| 9, C15, C19          | 3        | 100nF                   | CAP CER 100nF 16V X7R 10% M0603                      | 100nF              | Murata               | GRM033Z71C104KE     | DigiKey    | 490-GRM033Z71C104KE14D  | TR-ND             |        |

| 11                   | 1        | 4.7uF                   | CAP CER 4.7uF 10V XSR 10% M1005                      | 4.7uF              | Samsung Electro-M    | CL05A475KP5NRNC     | Digi-Key   | 1276-1480-2-ND          |                   |        |

| 16                   | 1        | 100pF                   | CAP CER 100pF 25V COG 5% M0603                       | 100pF              | Murata               | GRM0335C1E101JA0    | Digi-Key   | 490-3160-2-ND           | 25V               |        |

| 18                   | 1        | 0.8pF                   | CAP CER 0.8pF ±0.05pF 25V COG, NPO, M0603            | 0.8pF              | Murata               | GJM0335C1ER80WB     | Digi-Key   |                         | 25V               |        |

| 20                   | 1        | 1pF                     | 1 pF ±0.1pF 50V Ceramic Capacitor COG, NPO M0603     | 1pF                | Murata               | GJM0335C1H1R0BB     | DigiKey    | 490-GJM0335C1H1R0BB01E  | 50V               |        |

| 01                   | 1        | APHHS1005LSECK/J3-PF    | LED RED Colour M1005                                 | RED                | Kingbright           | APHHS1005LSECK/J3   | Digi-key   | 754-2123-2-ND           | 2mA, 1.85V        |        |

| 02                   | 1        | APHHS1005LSYCK/J3-PF    | LED Yellow Colour M1005                              | Yellow             | Kingbright           | APHHS1005LSYCK/J3   | Digi-key   | 754-2125-2-ND           | 2mA, 1.85V        |        |

| 13                   | 1        | APHHS1005LCGCK          | LED Green Colour M1005                               | Green              | Kingbright           | APHHS1005LCGCK      | Digi-key   | 754-2121-2-ND           | 2mA, 1.9V         |        |

| 1                    | 1        | 15nH                    | IND CER 15nH 560mA ±10% M1005 172 mOHM               | 15nH               | Delta Electronics/Co | 0402HS-150EKTS      | Digi-Key   | 2035-0402HS-150EKTSTR-N | 560mA             |        |

| .2                   | 1        | 10uH                    | IND CER 10uH 300mA ±20% M1608 1.37 OHM               | 10µH               | Murata               | LQM18DZ100M70L      | Mouser     | 81-LQM18DZ100M70L       | 300mA             |        |

| .3, L4               | 2        | 3.9nH                   | IND CER 3.9nH High Frequency Inductor, 500 mA, .17 ( | 3.9nH              | Murata               | LQP03HQ3N9C02D      | Mouser     | 81-LQP03HQ3N9C02D       | 500mA             |        |

| .5                   | 1        | 2.2nH                   | IND CER 2.2nH High Frequency Inductor, 600 mA, .12 ( | 2.2nH              | Murata               | LQP03HQ2N2C02D      | Mouser     | 81-LQP03HQ2N2C02D       | 600mA             |        |

| C1, PC2              | 2        | ED90501-ND              | CONN PC PIN GOLD                                     | 7937               | Mill-Max Manufact    | ED90501-ND          |            | 7937-0-00-15-00-00-03-0 |                   |        |

| R1, R3, R7           | 3        | 62R                     | RES 62R 1% 1/16W M1005                               | 62R                | Yageo                | 311-62.0LRCT-ND     | Digi-Key   | 311-1.00LRCT-ND         | 1/16W             |        |

| R2, R6, R10, R12     | 4        | 100K                    | RES 100K 1% 1/20W M0603                              | 10K                | Yageo                | RC0201FR-07100KL    | Digi-Key   | 311-100KMCT-ND          | 1/20W             |        |

| 84                   | 1        | OR                      | RES OR 1/10W M1005                                   | OR                 | Panasonic            | ERJ-2GEOROOX        | Digi-Key   | PO.OJCT-ND              | 1/10W             |        |

| R5, R8, R11, R13     |          | 10K                     | RES 10K 1% 1/20W M0603                               | 10K                | Stackpole            | RMCF0201FT10K0      | Digi-Key   | RMCF0201FT10K0CT-ND     | 1/20W             |        |

| 1                    |          |                         | SWITCH TACTILE Right Angle 160gf                     | 160gf              | CTS Electrocompon    | 223GMSAAR           | Digi-key   | 223GMSAAR-ND            |                   |        |

| 11                   | 1        | NRF52832-QFAA           | IC RF TXRX+MCU BLUETOOTH 48-VFQFN                    |                    | Nordic               | NRF52832-QFAA-R     | Digi-key   | 4823-NRF52832-QFAA-RCT- | ND                |        |

| 1, X2                | 2        | J-LINK_6-Pin_Needle Ada | J-LINK_6-Pin_Needle Adapter without holes            | J-LINK_6-Pin_Needl |                      |                     |            |                         |                   |        |

| 3                    | 1        | 32.768KHZ               | XTAL 32.768kHz, 9pF, ±20ppm                          | 32.768kHz          | Micro Crystal AG     | CM7V-T1A-32.768KF   | Digi-Key   | 2195-CM7V-T1A-32.768KHZ | -9PF-20PPM-TA-QCC | T-ND   |

| 4, X6                | 2        | S2B-ZR-SM4A-TF(LF)(SN)  | CON 4 Positions Header 0.100" (1.5mm)                |                    | JST Sales America In | S2B-ZR-SM4A-TF(LF)  | Digi-key   | 455-1693-1-ND           | 1.5mm             |        |

| 5                    | 1        | CX2016DB32000D0WZR0     | 32MHz ű25ppm Crystal 8pF 60 Ohms 4-SMD, No Lead      | 32MHz              | KYOCERA AVX          | CX2016DB32000D0V    | Digi-Key   | 478-CX2016DB32000D0WZI  | RC1TR-ND          |        |

| 1, Z3, Z4, Z5        | 4        | ESD351DPYR              | Diode TVS 6.5V 16A M1006                             | 6.5V Clamp 16A lpp | Texas Instruments    | ESD351DPYR          | Digi-Key   | 296-51109-1-ND          |                   |        |

Figure 3.4: GAIM BOM.

BOM is sent off to the assembler who will order the components, and start the assembly process once the components and the PCB arrives from the manufacturer. For a more detailed view of the BOM refer to Appendix A section A.3.

### 3.1.4 Setting design rules & Layout design

Once the schematic is done and approved it is time to import that schematic to the PCB editor.

This will import all the component footprints and nets that are linked with each symbol on the schematic to the PCB Editor.

Before we start placing components on the board we need to set the stack-up and design rules. That is done in the stack-up manager and design rules settings. The rules can vary from project to project and from manufacturer to manufacturer. In this project the manufacturing company is called Brandner. The manufacturing company capabilities is what will set our design rules and stack-up, meaning the minimum clearance/width between components, traces, holes etc.

| # | Name           | Material      | Type        | Weight | Thickness | Dk  | Сорр  |

|---|----------------|---------------|-------------|--------|-----------|-----|-------|

|   | Top Overlay    |               | Overlay     |        |           |     |       |

|   | Top Solder     | Solder Resist | Solder Mask |        |           | 4.2 |       |

| 1 | Top Layer      | CF-004        | Signal      | 1oz    | 0.047mm   |     | Above |

|   | Dielectric 2   | PP-006        |             |        | 0.18mm    | 4.1 |       |

| 2 | 2              |               |             | 1oz    | 0.035mm   |     | Abov€ |

|   | Dielectric 1   | Core-025      | Core        |        | 1.08mm    | 4.6 |       |

| 3 |                |               | Signal      |        |           |     | Below |

|   | Dielectric 3   | PP-006        | Prepreg     |        | 0.18mm    | 4.1 |       |

| 4 | Bottom Layer   | CF-004        | Signal      |        | 0.047mm   |     | Below |

|   | Bottom Solder  | Solder Resist | Solder Mask |        | 0.025mm   | 4.2 |       |

|   | Bottom Overlay |               | Overlay     |        |           |     |       |

Figure 3.5: Layer stack-up for the GAIM PCB.

The stack-up for this project is shown in figure (3.5). It is a 4 layer board and where we can see the different copper pours, dielectric materials and thicknesses etc. The stack-up contains all the information about what materials will be used to manufacture the PCB.

Since there is an RF section in the design, we need to consider impedance matching as discussed in RF theory. This means that the RF trace on the board needs to be 50 OHMS. Setting impedance on traces in Altium is done by a built-in tool that will set the clearance and width on the RF traces to achieve 50 OHM impedance.

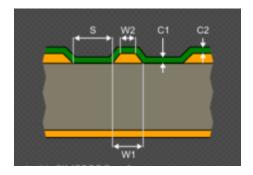

**Figure 3.6:**  $50\Omega$  impedance profile for GAIM PCB.

Where:

$$S = 0.3mm$$

$W1 = 0.28mm$

$W2 = 0.27mm$

$C1 = 0.025mm$

$C2 = 0.025mm$

$Z_0 = 50.41\Omega$

$\gamma = 0.82\%$

$\tau_p = 5.96ns/m$

$L = 300.28nH/m$

$C = 118.17pF/m$

S is the clearance between the trace and the planes, WI and W2 is the width of the trace, CI and C2 is the solder mask thickness,  $Z_0$  is the impedance,  $\gamma$  is the deviation,  $\tau_p$  is the delay per meter, L is the inductance per meter, and C is the capacitance per meter.

After viewing the manufacturing capabilities from the Brandner website, it is time to set the design rules. In tables (3.1), (3.2), (3.3), (3.4), and (3.5) we see the clearances and widths that are used for this board.

| (mm)    | Track | SMD Pad | TH Pad | Via  | Copper | Text |

|---------|-------|---------|--------|------|--------|------|

| Track   | 0.15  |         |        |      |        |      |

| SMD Pad | 0.15  | 0.15    |        |      |        |      |

| TH Pad  | 0.15  | 0.15    | 0.15   |      |        |      |

| Via     | 0.15  | 0.15    | 0.15   | 0.15 |        |      |

| Copper  | 0.15  | 0.15    | 0.15   | 0.15 | 0.15   |      |

| Text    | 0.15  | 0.15    | 0.15   | 0.15 | 0.15   | 0.15 |

| Hole    | 0     | 0       | 0      | 0    | 0      | 0    |

**Tabel 3.1:** Clearances for different nets.

| (mm)    | Track | SMD Pad | TH Pad | Via | Copper | Text |

|---------|-------|---------|--------|-----|--------|------|

| Track   | 0.3   |         |        |     |        |      |

| SMD Pad | 0.3   | 0.3     |        |     |        |      |

| TH Pad  | 0.3   | 0.3     | 0.3    |     |        |      |

| Via     | 0.3   | 0.3     | 0.3    | 0.3 |        |      |

| Copper  | 0.3   | 0.3     | 0.3    | 0.3 | 0.3    |      |

| Text    | 0.3   | 0.3     | 0.3    | 0.3 | 0.3    | 0.3  |

| Hole    | 0     | 0       | 0      | 0   | 0      | 0    |

**Tabel 3.2:** Clearances with 50 OHM impedance characteristics. Taken from the impedance profile in **figure 3.6**.

| (mm)/Layer | L1 (Top) | L2    | L3    | L4 (Bottom) |

|------------|----------|-------|-------|-------------|

| Min        | 0.125    | 0.125 | 0.125 | 0.125       |

| Preferred  | 0.15     | 0.15  | 0.15  | 0.15        |

| Max        | 1        | 1     | 1     | 1           |

**Tabel 3.3:** Trace width for any arbitrary signal. Shows the minimum, preferred and maximum width on each layer

| (mm)/Layer | L1 (Top) | L2   | L3   | L4 (Bottom) |

|------------|----------|------|------|-------------|

| Min        | 0.15     | 0.15 | 0.15 | 0.15        |

| Preferred  | 0.3      | 0.3  | 0.3  | 0.3         |

| Max        | 5        | 5    | 5    | 5           |

**Table 3.4:** Trace width for power signals.

| (mm)/Layer | L1 (Top) | L4 (Bottom) |

|------------|----------|-------------|

| Min        | 0.28     | 0.28        |

| Preferred  | 0.28     | 0.28        |

| Max        | 0.28     | 0.28        |

**Table 3.5:** Trace width for a 50 OHM impedance trace. Taken from the impedance profile in **figure 3.6**.

Upon the establishment of all design rules, the layout design phase can start.

Firstly, the floorplan is devised, determining the most optimal and logically sound placement for all components. Some components have a fixed placement from a mechanical perspective, such as the battery holder,

connectors and button. This makes the placement for the nRF chip and the discrete components limited. Given GAIM's requirements to maintain identical mechanical functionalities, it is imperative to position the nRF chip in a location approximating the placement of the ANNA RF module in the previous design.

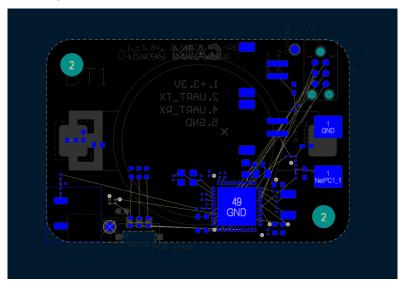

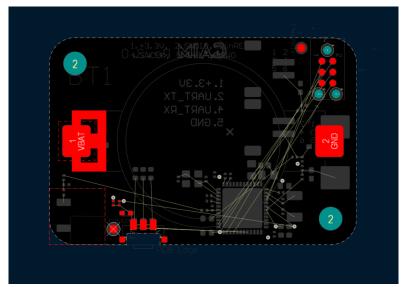

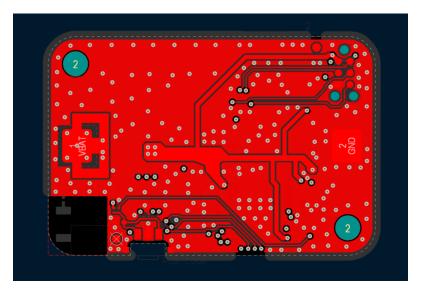

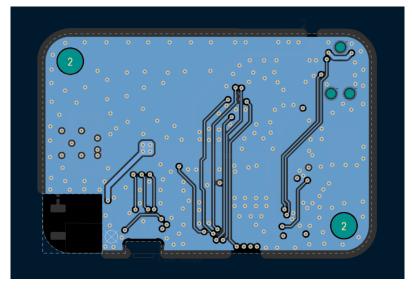

**Figure 3.7:** Floorplan for GAIM 4.0.

Once the floorplan is set, I can start the routing process. I start routing the most important and sensitive traces/components. In this case the most sensitive aspect is the RF impedance controlled trace. When routing these types of traces we want to keep ground all the way around the trace, including ground vias. This is shown in figure (3.11). In the lower left corner the RF trace goes from the nRF chip to the matching network and the antenna.

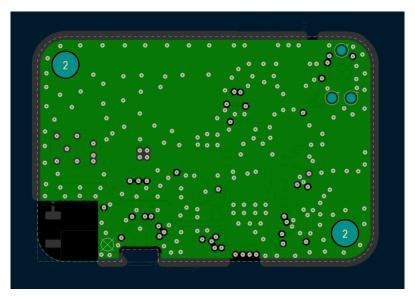

For the antenna it is important to follow the datasheet [5]. To address the challenge of degradation and alteration in the antenna radiation pattern caused by the presence of ground underneath on the PCB, a solution involves removing a 6.5mm\*6.5mm section from the ground planes on each layer, seen in the left corner of figures (3.8), (3.9), (3.10), and (3.11).

Another sensitive component in this design are the crystals. For crystals it is important to keep ground directly below, on layer 3 (since the crystals are placed on the bottom layer (L4)). Routing traces below the crystals may generate crosstalk, since crystals are considered high-speed signals. Crosstalk is avoided by having ground planes below the crystals. In fact as shown in figure (3.10) (L3), the entire plane is GND with no other signals routed. I purposefully avoided routing any signals on layer 3 to keep the entire plane GND, for the reason to not accidentally create crosstalk or degrade the impedance controlled RF trace below on layer 4.

Leveraging creative routing techniques, I successfully directed the remaining arbitrary signals across the top layer, layer two, and layer four. Finishing off with the power network on the top layer shown in figure (3.8). This is called a power tree, since the power traces look like branches with a big stem.

Upon completion of all routing, we have a finished PCB, shown in figure (3.12), and ready for review. The reviewing process is done by the RF team to check the RF routing and antenna placement, and also done by another PCB designer to make sure all the routing is done correctly. Running the built-in tool DRC in Altium will display all design errors.

Once the review process is done and approved, we are ready to send the board for manufacturing, which will be discussed in the next section.

**Figure 3.8:** Top Layer (Signal/Power)

Figure 3.9: Layer 2 (Signal)

**Figure 3.10:** Layer 3 (GND)

Figure 3.11: Bottom Layer (Signal)

**Figure 3.12:** GAIM 4.0 PCB.

## 3.1.5 Output manufacturing files

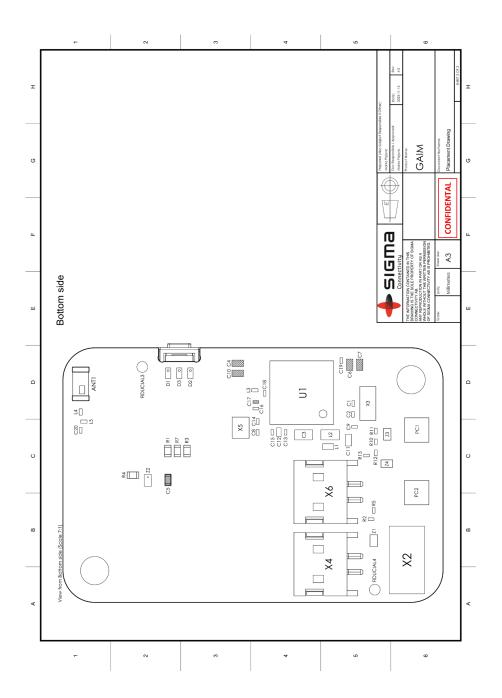

Once the design process is finished it is time to order and manufacture the boards. Within Altium you can export manufacturing files. The manufacturing files consist of gerber, ODB++, and P&P. Gerber and ODB++ are files for creating the PCB, using either a drill for vias or laser for small traces/vias. P&P files stands for pick and place, which is a file for all component placements.

Other manufacturing files are schematic, BOM and assembly drawing. Schematic and BOM are discussed in section 3.1.2 and 3.1.3, assembly drawing is essentially a schematic for the assembler that displays the position and orientation for each component. For a more detailed view of the assembly drawing check section A.2 in Appendix A.

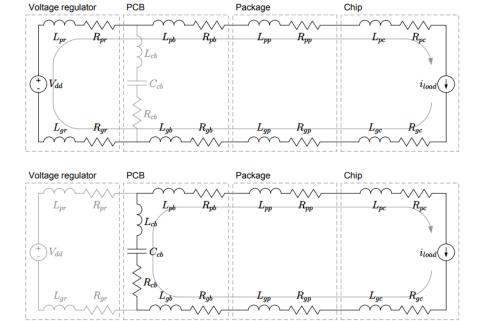

## 3.2 Analysis of the PDN

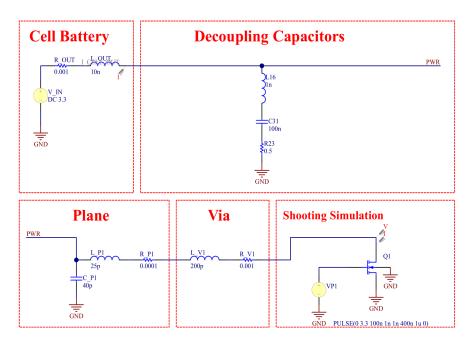

Using SPICE on Altium I modeled the GAIM PCB using an RLC network, with typical capacitance, resistance and inductance for a 4-layer board

Figure 3.13: Modeled GAIM PCB using an RLC network.

From figure (3.13) we see all the different sections of the PCB, where the shooting simulation will model when the trigger is pulled. The *VP1* voltage source will generate rapid pulses with a 1us period and a rise/fall time of 1ns. In reality the period, and rise/fall time are much slower which will give more stable results. But we want to simulate in the more extreme zones.

The plane section is a simplification of the power distribution network of the PCB.

Current probes are placed at the output of the cell battery and at the drain of the MOSFET, and a voltage probe is placed at the drain of the MOSFET.

The first simulations were transient simulations that ran for three periods, with 25 points per period. There were in total nine transient simulations, varying the ESR, ESL, capacitance value, and the number of decoupling capacitors in parallel for each simulation. The effects on varying different values are presented in section 4.3.1 of the results.

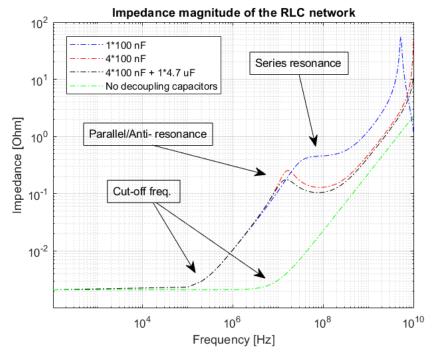

### 3.2.1 Impedance of the modeled RLC network

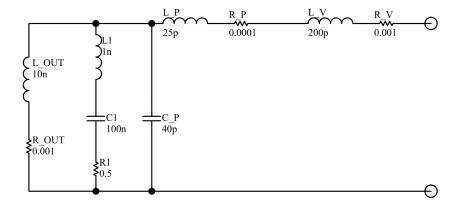

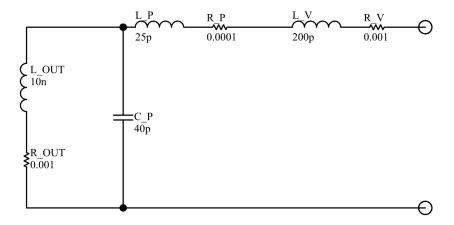

Let us now investigate the impedance magnitude proportional to the frequency. By modeling the impedance network that is equivalent to figure (3.13), we get:

Figure 3.14: Impedance network, including the decoupling capacitor.

Figure 3.15: Impedance network, excluding the decoupling capacitor.

Calculations of the impedance magnitude with respect to the frequency for figure (3.14) and (3.15) are shown in section 4.3.2 of the results.

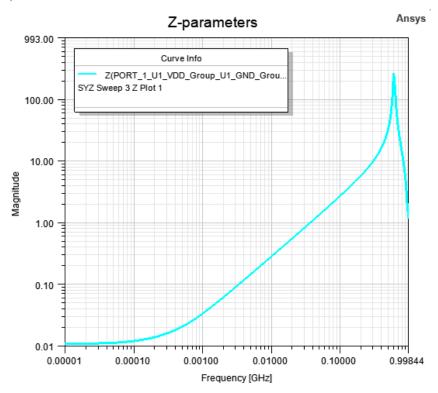

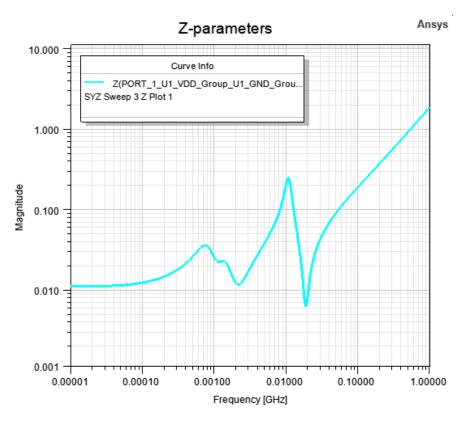

## 3.2.2 Impedance measurements of the PDN on the PCB

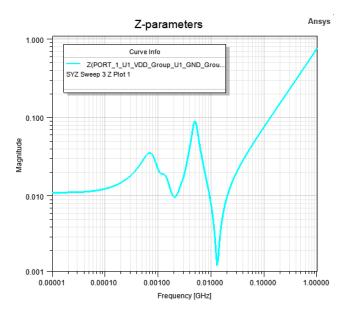

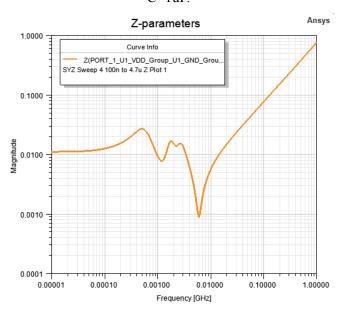

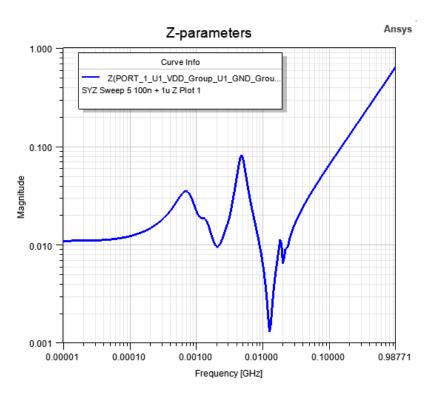

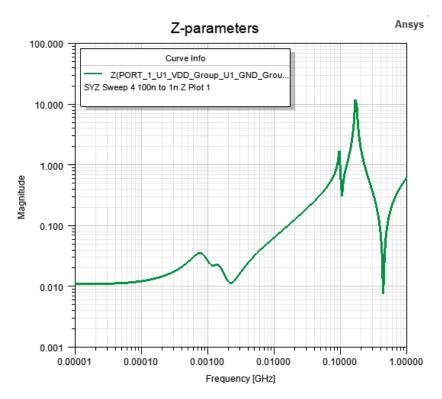

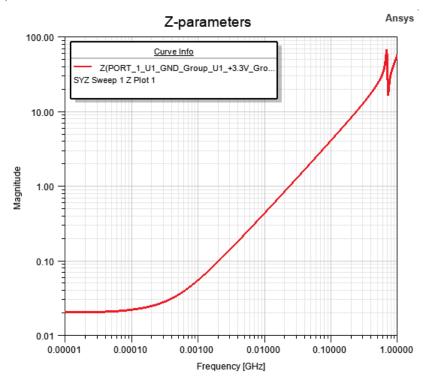

To perform real AC impedance simulations for the power delivery network (PDN) on GAIM PCB, the software SIWave was used. ODB++ output files from Altium were used to import the real PCB layout into the simulation program. Running AC impedance simulations will tell us what decoupling capacitors are most optimal to use, and the overall impedance of our power network. Determining the target impedance is very difficult, judging by the substantially allowed voltage margins for the nRF chip, my guess is that the target impedance is in the 10s of ohms. However for simplicity and more extreme zones I will approximate the target impedance to be 0.1 ohm. The cut-off frequency is defined when the PDN impedance magnitude is equal to the target impedance.

The AC simulations of the GAIM PCB are presented in section 4.3.3 of the results.

# 3.3 Manufacturing & Assembly

## 3.3.1 Manufactured PCB before assembly

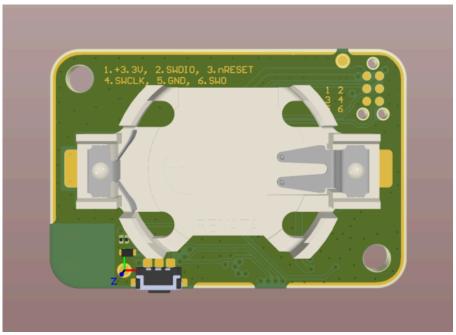

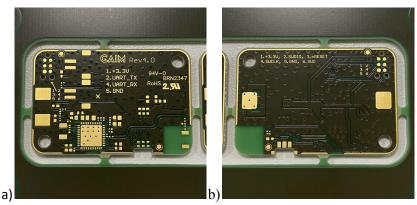

**Figure 3.16:** (a) Top side of the manufactured PCB (b) Bottom side of the PCB.

# 3.3.2 Manufactured PCB after assembly

Figure 3.17: Top and bottom side of the assembled GAIM PCB.

In figures (3.16) and (3.17), we have manufactured and assembled boards. The assembly process was done in the lab using a soldering station, microscope and various different tools.

# 3.4 Flashing & Functionality verification

# 3.4.1 Flashing the PCB with software

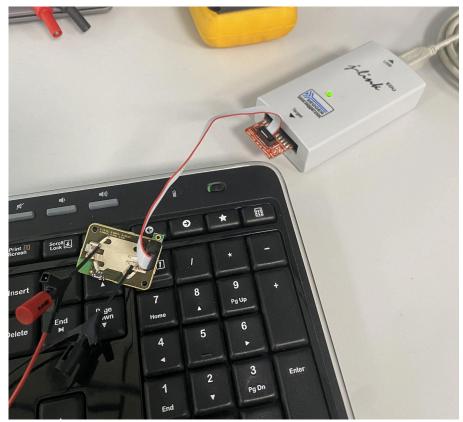

Figure 3.18: Flashing the PCB using J-Link.

Figure (3.18) elucidates the procedure of programming the nRF chip and instilling vitality into the board.

For functionality verification there was a protocol I followed. The protocol is a standard protocol used by SIGMA, for testing PCBs and verifying their functionality.

## 3.4.2 Functionality verification protocol

The verification protocol follows:

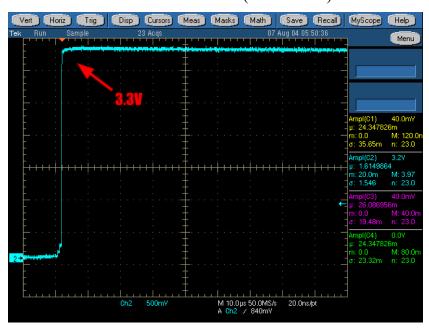

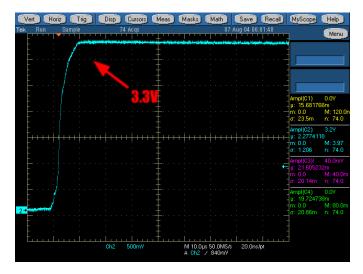

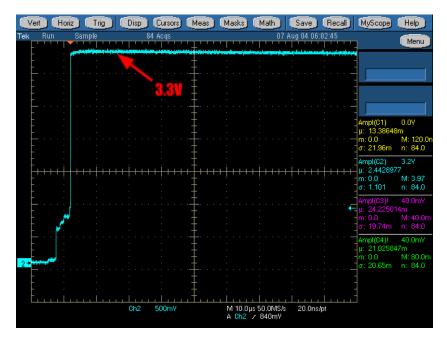

#### "Bring-up DUT main battery (Vbat) Power:

- Note the DUT power consumption in off mode, check that it does not draw excessive power i.e. is internally shorted.

- Probe all Vbat test & service points to confirm that the voltage is as expected in all nodes i.e. all nodes are physically connected to Vbat.

#### **Bring-up DUT Switch ON:**

- Note the DUT total power consumption during power on, check that it does not draw excessive power i.e. is internally shorted. Note max value and value after stabilizing (i.e. boot up is finished)

- Probe all power nodes during startup and verify that they reach correct values (as per product or component specification), note the values. It is common that some power nodes are set to incorrect voltages if SW has not finished, usually then to the power management ICs default values. This is not critical but should be noted and reported. What is critical is if voltages are incorrect due to leakage to other power nodes or ground.

For all GPIO signals, Interrupt, etc., read the component specification to confirm how the pin should be configured, active high / low etc. Measure the voltage level to confirm. Any intermediate voltage level at any time (also measured at startup / shutdown and during operation) is a sign that something is wrongly configured and there is a current leakage.

#### CPU power up and down:

- Measure Start-up and shut-down sequence of inputs to the CPU, especially the supply voltages. Look at timing and levels, look out for glitches. Verify according to the CPU or platform specification."

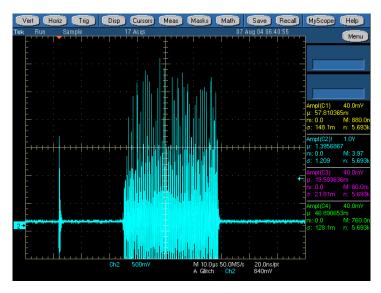

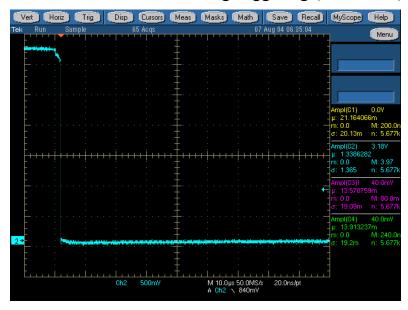

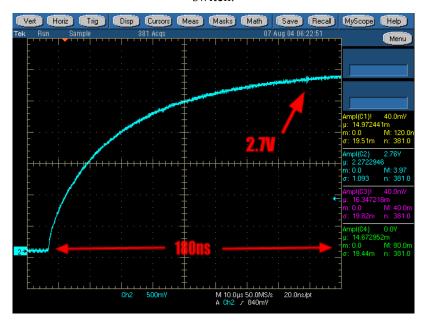

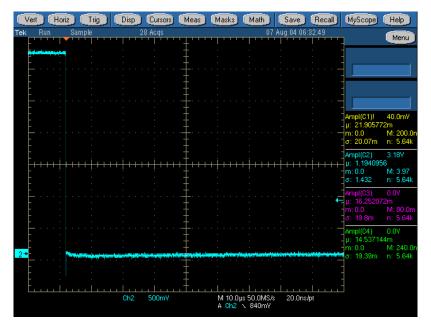

Using a switching power supply connected to the GAIM PCB, and an oscilloscope, some measurements were taken by following the protocol above. The measurements are presented in section 4.4 of the results.

#### 3.5 RF/Antenna measurements

Once the PCB is assembled and tested with functionality, I move on to RF and antenna measurements. There are two types of measurements done on the PCB, radiated and conducted.

### 3.5.1 Total Radiated Power (TRP) measurements

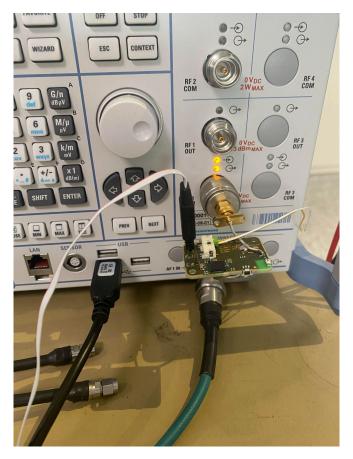

Radiated measurements were done in an antenna chamber that measures total radiated power (TRP) in dBm. As seen below in figure (3.19), the PCB was placed inside the chamber.

Figure 3.19: RF chamber for radiated measurements.

The new PCB (GAIM 4.0) is flashed with a special test program that emits at three different frequencies (not at the same time, but by pressing the button it will switch between the frequencies). The frequencies are 2402MHz, 2440MHz, and 2480MHz, and thus measuring the trp for each frequency. The flashed program on the chip is set to have a conducted power (power that goes into the antenna, also called input power) of 0 dBm. By referring to the theory in section 2.2.3, we can calculate the antenna efficiency by using equations (2.2.3) and (2.2.4). We measure the total

radiated power, and use the 0 dBm input power to calculate the antenna efficiency.

The measurements were done in three different scenarios. Firstly done with just the GAIM 4.0 PCB, secondly GAIM 4.0 PCB placed in the trigger mechanical unit (refer to figure 1.1), and lastly done with the old design, GAIM 3.0 PCB also placed in the trigger mechanical unit. The results are presented in section 4.5.

### 3.5.2 Conducted power measurements on the RF trace

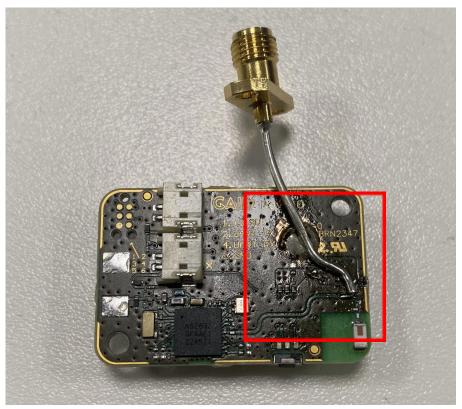

Conducted measurements are directly measured on the RF trace on the PCB. By scratching the solder mask (green color) to expose the copper, both on the RF trace and ground plane, I soldered an SMP connector as illustrated in figure (3.20) below.

Figure 3.20: GAIM 4.0 PCB with smp connector, soldered to the RF trace.

The smp connector will be directly connected to a spectrum analyzer, to measure the total conducted power, using a different program that will have a conducted power of 4 dBm. The program will allow me to manually sweep through all channels on the bluetooth low energy (BLE) frequency spectrum, and measure the output power on the RF trace, as seen in figure (3.21).

**Figure 3.21:** Conducted measurements, by manually sweeping through all channels.

The main reason for conducted power measurements is to see the power loss on the RF trace throughout the entire frequency spectrum. For ideal situations the measured conducted power should be 4 dBm on the entire spectrum, however nothing is ideal. The conducted power measurements are presented in section 4.5.2.

## 3.5.3 Sensitivity measurements on the RF trace

The same setup is used as in figure (3.21) to measure the conducted sensitivity of the new PCB (GAIM 4.0). It is done by starting with a conducted power of -85dBm and sending 300 data packages each time, with a specified checksum. This checksum is used to calculate bit errors. On each iteration the conducted power is lowered by 0.1dBm. The power is lowered all the way until the measured error rate is more than 30%. The lowest conducted power that gives us an error rate less than 30% will be the conducted sensitivity of the chip.

The conducted sensitivity for the RF module on the old PCB can be seen in the ANNA module datasheet [3].

## 4. Results

## 4.1 PCB design

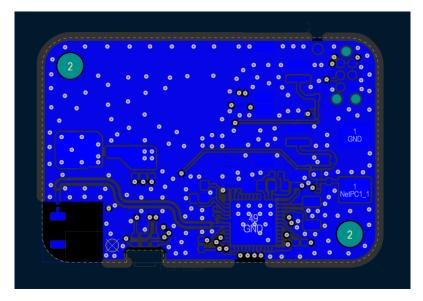

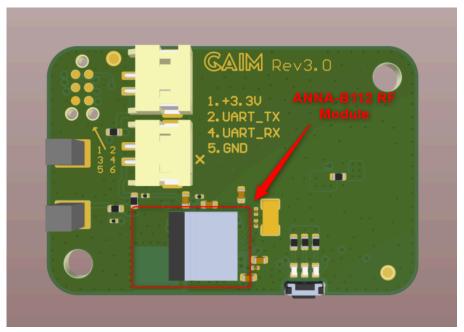

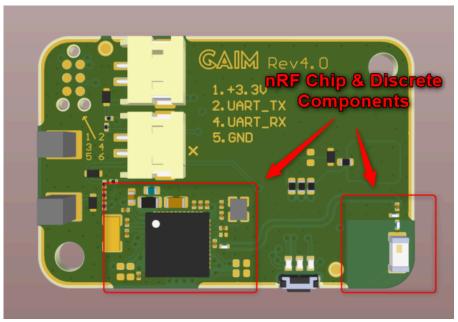

This section presents the solution and complexity of swapping out the ANNA-B112 RF module, and fitting the nRF chip with discrete components, which are shown in figures (4.1) and (4.2). Additionally some optimizations from an ESD protection aspect were made to the new revision.

## 4.1.1 Fitting the nRF and discrete components

**Figure 4.1:** PCB from the previous design of GAIM (Rev3.0), with the ANNA-B112 RF module.

**Figure 4.2:** New revision of the GAIM PCB, fitted with nRF chip and discrete components (Rev4.0).

## 4.1.2 ESD protection optimization

From figures (4.2) and (3.16), we see the ESD protection design technique implemented. The soldermask has been removed on the edges of the PCB exposing the GND copper plane, and various ESD diodes were placed near each external connector (including the two big connectors and the button).

# 4.2 Cost aspect

In this section the cost considerations are presented. We will look at the reduction of component cost and the cost for certification of the boards.

## 4.2.1 Component cost reduction

| Manufacturer Part No               | Quantity | Supplier 1 | Average Component Price | Total Unit Cost |

|------------------------------------|----------|------------|-------------------------|-----------------|

| ERJ-2GE0R00X                       | 1        | Digi-Key   | 0,2305833333            | 168,114177      |

| RMCF0201FT10K0                     | 4        | Digi-Key   | 0,2469657143            |                 |

| CBR02C120F3GAC                     | 2        | Digi-Key   | 1,874705                |                 |

| RC0402FR-0762RL                    | 3        | Digi-Key   | 0,2213214286            |                 |

| RC0402FR-07100KL                   | 4        | Digi-Key   | 0,2213214286            |                 |

| 0201X104K6R3CT                     | 1        | Mouser     | 0,26122625              |                 |

| 223GMSAAR                          | 1        | Digi-key   | 2,54895                 |                 |

| ANNA-B112                          | 1        | Digi-key   | 93,485196               |                 |

| APHHS1005LCGCK                     | 1        | Digi-key   | 2,413238                |                 |