### True-Time Delay Cancellers for Full-Duplex

Vejde Nilsson & Vilgot Snygg

Department of Electrical and Information Technology Lund University

Supervisor: Jonas Lindstrand, Rehman Akbar & Henrik Sjöland

Examiner: Pietro Andreani

February 29, 2024

### **Abstract**

The concept of simultaneously receiving and transmitting at the same frequency is known as Full-Duplex (FD). Such a wireless system is a novel technique which could effectively half the required channel Bandwidth (BW) for the same data rate. In FD systems, the leakage of the Transmitter (Tx), called Self-Interference (SI) signal, leaks into the Receiver (Rx) which is a major hardware-related obstacle for reliable FD operation. Multiple leakage paths exists for the SI signal, such as direct path (DP) antenna-to-antenna feed through or environment-based multisurface reflection paths (RP). By taking the output of the Tx, introducing delay and amplitude compensation, then subtracting this signal from the SI signal in the Rx front end, the SI can effectively be canceled in the analog Radio Frequency (RF) domain. This thesis is investigating how such a SIC circuit, targeting cancellation in the RF analog domain, could be designed. Large focus is given to True-Time Delay (TTD) generation, which is a major part of the SIC system. The proposed RF SIC is a hybrid solution with passive pre-LNA (Low-Noise Amplifier) SIC and an active post-LNA SIC aimed at an operating frequency of 10 GHz with 100 MHz of carrier bandwidth. The passive TTD is implemented as a binary weighted delay chain with cascaded lumped LC transmission line filters for course tuning and an *LR-RL* lattice all-pass filter with tunable coupled inductors for fine tuning. For the active TTD, a Time Interleaved (TI) N-path circuit was used. The passive TTD achieves a delay range of 62-1661 ps with an estimated rms (Root Mean Square) cancellation of 18.64 dB over the BW. For the active TI N-path TDD, a delay range of 22-1772 ps is showcased with an estimated rms cancellation of 19.53 dB over the BW. The TI N-path TTD can be scaled up to achieve longer delays and branched to generate multiple outputs for cancellation of multipath reflections with reduced chip-area.

### Popular Science Summary

You have two friends called Adam and Bob. Imagine Adam standing next to you and shouting to Bob across the street. Meanwhile, Bob is trying to communicate with you. It will be very difficult for you to hear what Bob is saying because Adam will be overpowering him.

This is an analogy for a radio system trying to operate in full-duplex where you represent the receiver, Adam the transmitter and Bob another radio device. In more technical terms, full-duplex is the concept of simultaneously sending and receiving signals at the same frequency. The problem with such radios is that the transmitter (Adam) overpowers the received signal from another radio device (Bob), such that the receiver (you) can not interpret the information. This signal coming from the transmitter is called self-interference (SI) and in order for full-duplex to work, the SI must be cancelled.

If we could recreate the SI signal perfectly we could cancel the SI by combining it with the inverse of the recreated signal. The transmitted signal is an electromagnetic wave which when traveling through the air will lose some of its power and bounce off objects in the environment around the radio. All of this gives the SI signal some delay and some amplitude loss before entering the receiver. Therefore, some delay also needs to be applied to the recreated SI signal.

This thesis is focused on how to generate this delay using modern semiconductor circuits, which is more difficult than you might think when considering that the delay must be adjustable down to only one picosecond. This is the time it takes for light to travel 0.3 mm!

### **Preface**

This master thesis is the final project of an engineering master's degree within high frequency electronics. The project has been carried out at Ericsson AB who have been providing the authors with office space, computers, knowledge and guidance on top of an inspiring and innovative environment. We would like to thank Stefan Andersson, manager for RF frontend and PA at Ericsson Research in Lund, for approving this thesis project. We want to thank Jonas Lindstrand and Rehman Akbar, the project supervisors at Ericsson, who has been very generous in their commitment. They provided both insightful feedback and learning opportunities. A final word of appreciations is also dedicated to Henrik Sjöland, the Lund University supervisor.

## **Table of Contents**

| 1 | Intro | duction                                                                     |  |  |  |  |  |

|---|-------|-----------------------------------------------------------------------------|--|--|--|--|--|

| 2 | Full  | Ouplex System Overview                                                      |  |  |  |  |  |

| _ | 2.1   | Full-duplex vs Half-duplex                                                  |  |  |  |  |  |

|   | 2.2   | Self-Interference Paths                                                     |  |  |  |  |  |

|   | 2.3   | Rate gain region                                                            |  |  |  |  |  |

|   | 2.4   | Different SIC-Techniques                                                    |  |  |  |  |  |

|   |       | 2.4.1 Antenna domain                                                        |  |  |  |  |  |

|   |       | 2.4.2 Analog domain                                                         |  |  |  |  |  |

|   |       | 2.4.3 Digital domain                                                        |  |  |  |  |  |

|   | 2.5   | System Specifications                                                       |  |  |  |  |  |

| 3 | Con   | iderations for RF SIC                                                       |  |  |  |  |  |

|   | 3.1   | System Hardware with ideal sub-blocks                                       |  |  |  |  |  |

|   | 3.2   | Noise Figure degradation from noise injection and non-linear distortions 13 |  |  |  |  |  |

|   | 3.3   | Attenuation Balance and Injection Points                                    |  |  |  |  |  |

|   | 3.4   | Cancellation Required in the analog RF domain                               |  |  |  |  |  |

|   | 3.5   | Cancellation vs Delay and Amplitude Error                                   |  |  |  |  |  |

|   | 3.6   | Proposed Hybrid Topology                                                    |  |  |  |  |  |

| 4 | True  | Time Delay Circuits                                                         |  |  |  |  |  |

|   | 4.1   | Passive TTD Circuits                                                        |  |  |  |  |  |

|   |       | 4.1.1 Delay generation                                                      |  |  |  |  |  |

|   |       | 4.1.2 Tuning                                                                |  |  |  |  |  |

|   | 4.2   | Active TTD Circuits                                                         |  |  |  |  |  |

|   |       | 4.2.1 N-path Circuit                                                        |  |  |  |  |  |

|   |       | 4.2.2 Time Interleaved N-path                                               |  |  |  |  |  |

|   |       | 4.2.3 Adding a Second Time Interleaved Stage and Branching the TI N-path    |  |  |  |  |  |

|   |       | 4.2.4 g <sub>m</sub> based delays                                           |  |  |  |  |  |

| 5 | Circ  | it Design                                                                   |  |  |  |  |  |

|   | 5.1   | Design of Passive TTD                                                       |  |  |  |  |  |

|   |       | 5.1.1 Binary weighted delay with lumped I C transmission lines              |  |  |  |  |  |

|   |      | 5.1.2    | LR-RL lattice fine tuning filter with coupled inductors | 56   |

|---|------|----------|---------------------------------------------------------|------|

|   | 5.2  | Desig    | n of the N-path TTD circuit                             | 62   |

|   |      | 5.2.1    | Original N-path                                         | 62   |

|   |      | 5.2.2    | Time-Interleaving the N-path                            | 69   |

|   |      | 5.2.3    | Branched Time-Interleaved N-path                        | 74   |

| 6 | Resi | ults and | d Discussion                                            | _ 77 |

|   | 6.1  | True-T   | ime Delay Performance for Active and Passive Techniques | 77   |

|   |      | 6.1.1    | Results of the Passive Binary Weighted TTD              | 78   |

|   |      | 6.1.2    | Results of the TI N-path TTD                            | 83   |

|   | 6.2  | Show     | casing high delay with Branched Double TI N-path        | 87   |

|   | 6.3  | Estima   | ated Performance of the Combined Hybrid SIC             | 88   |

| 7 | Sum  | ımary a  | nd Conclusion                                           | _ 91 |

| Α | Арр  | endix_   |                                                         | 97   |

|   | A.1  | RF SI    | C Block Level Calculations                              | 97   |

# List of Figures

| 2.1  | The difference between half-duplex and full-duplex illustrated in a time-frequency graph | 4  |

|------|------------------------------------------------------------------------------------------|----|

| 2.2  | Self-interference paths from Tx to Rx for different antenna structures.                  | 5  |

| 2.3  | The three domains of the transceiver where SIC can be performed [5]                      | 7  |

| 2.4  | Overview of the SIC techniques in a tree diagram [5]                                     | 7  |

| 3.1  | Overview of the transceiver topology and the different signal levels                     | 12 |

| 3.2  | Noise injection from the SIC into the Rx                                                 | 13 |

| 3.3  | Simplified model of an SIC block                                                         | 14 |

| 3.4  | The trade-off in attenuation distribution for the SIC. Both power levels                 |    |

|      | in this figure are output referred                                                       | 15 |

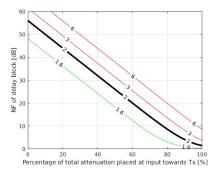

| 3.5  | Contour line of NF degradation for pre-LNA injection                                     | 16 |

| 3.6  | Contour line of NF degradation for post-LNA injection                                    | 16 |

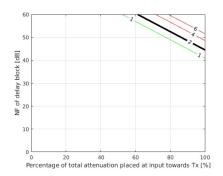

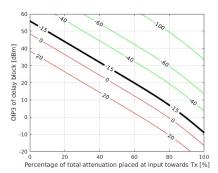

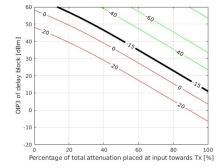

| 3.7  | Contour line of IMD3 power levels normalized to the noise floor for                      |    |

|      | pre-LNA injection                                                                        | 16 |

| 3.8  | Contour line of IMD3 power levels normalized to the noise floor for                      |    |

|      | post-LNA injection.                                                                      | 16 |

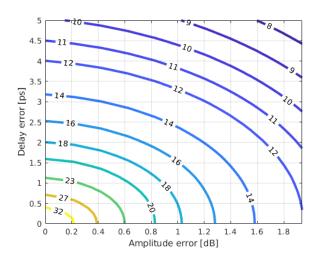

| 3.9  | Simulated contour plot of cancellation versus amplitude error and de-                    |    |

|      | lay error                                                                                | 19 |

| 4.1  | General lattice all-pass filter                                                          | 22 |

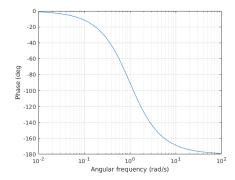

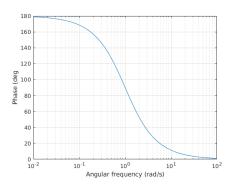

| 4.2  | Phase response of a lattice low-in-phase filter                                          | 23 |

| 4.3  | Phase response of a lattice high-in-phase filter                                         | 23 |

| 4.4  | RC-CR lattice filter                                                                     | 24 |

| 4.5  | LR-RL lattice filter                                                                     | 24 |

| 4.6  | LC-CL lattice filter                                                                     | 25 |

| 4.7  | Differential lumped LC transmission line                                                 | 26 |

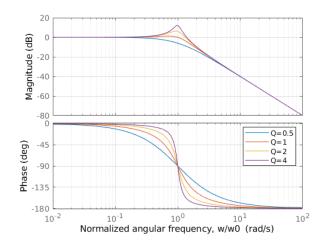

| 4.8  | Bode diagram of a second order low-pass filter for different quality                     |    |

|      | factors                                                                                  | 26 |

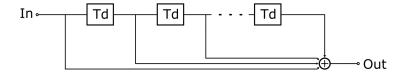

| 4.9  | Equally sized delay blocks in a tapped topology                                          | 27 |

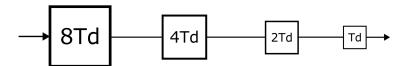

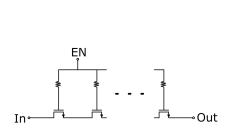

| 4.10 | Binary weighted delay chain                                                              | 28 |

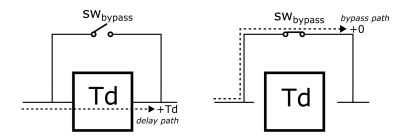

| 4.11 | The delay path and bypass path of a delay block                                          | 28 |

| 4.12 | Transistors stacked in series for increased linearity and isolation                      | 29 |

| 4 40       | Overved as a second transition for increased is a lating                                 | 00 |

|------------|------------------------------------------------------------------------------------------|----|

| 4.13       |                                                                                          | 29 |

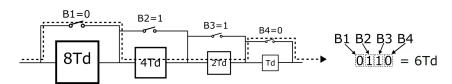

| 4.14       | Tuning of a binary weighted delay chain                                                  | 29 |

| 4.15       | Mutually coupled inductors with a capacitor in the secondary circuit .                   | 30 |

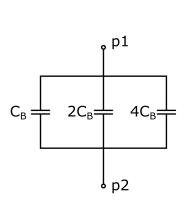

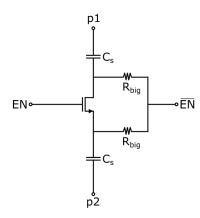

| 4.16       | Binary weighted tunable capacitor with three bits                                        | 31 |

| 4.17       | Switchable capacitor                                                                     | 31 |

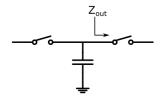

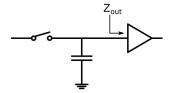

| 4.18       | N-path sample and hold. The next stage needs to provide high output                      |    |

|            | impedance                                                                                | 33 |

| 4.19       | Simple sample and hold circuit. The input impedance of the buffer                        |    |

|            | $(Z_{out})$ is high to not load the sample node                                          | 33 |

| 4.20       | N sample and reconstruct branches of an N-path circuit                                   | 33 |

| 4.21       | Visualization of the sample and hold mechanism of an $N=8$ N-path                        |    |

|            | TTD                                                                                      | 33 |

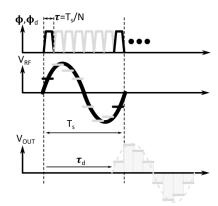

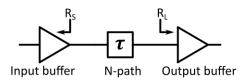

| 4.22       | Output and input matching of the N-path                                                  | 34 |

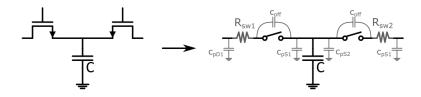

| 4.23       | Parasitic effects of the MOSFET as a switch for N-path circuit                           | 35 |

| 4.24       | Summary of the parasitic elements in the full N-path circuit                             | 36 |

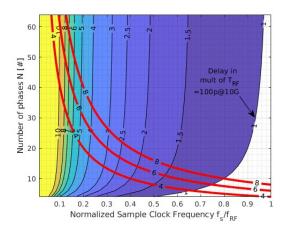

| 4.25       | Contour plot of the maximum achievable delay normalized by the in-                       |    |

|            | put signal time period $T_{rf}$ . This is plotted against the number of                  |    |

|            | phases $N$ on the vertical axis and the sample clock frequency $f_s$                     |    |

|            | normalized against $f_{rf}$ . The red curves shows the sample rate in                    |    |

|            | sample/waveform                                                                          | 37 |

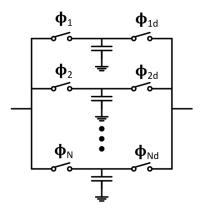

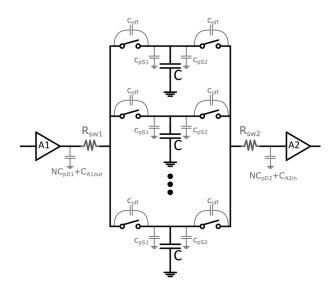

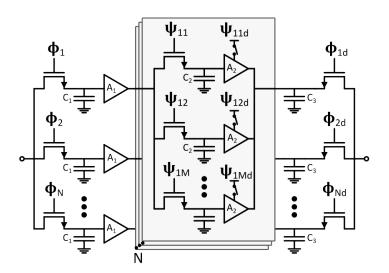

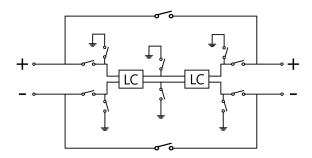

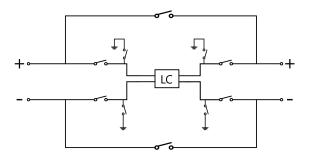

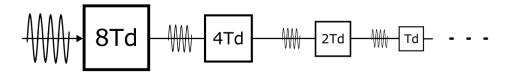

| 4.26       | Schematic of an $N$ by $M$ TI N-path                                                     | 38 |

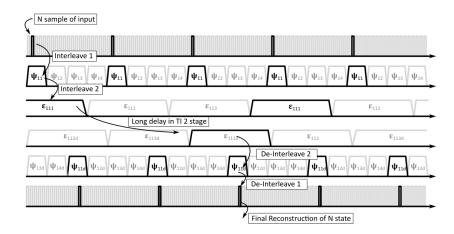

| 4.27       | · · · · · · · · · · · · · · · · · · ·                                                    |    |

|            | and output reconstruct ( $\Phi$ and $\Phi_d$ respectively) is set to the same            |    |

|            | phase. $d_{clk\Psi}$ and $d_{clk\Psi d}$ is the delay of the interleaved clocks relative |    |

|            | to the input sample clock                                                                | 39 |

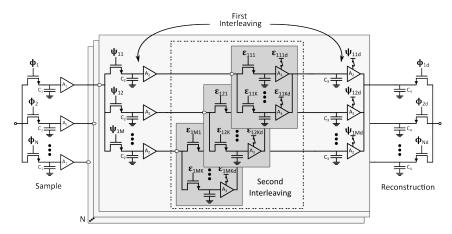

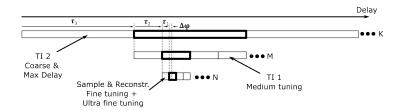

| 4.28       | Introducing a second TI stage into the N-path circuit                                    | 41 |

| 4.29       | Clock programming of a double TI N-path circuit with the following                       |    |

|            | number of stages: $N = 5$ , $M = 4$ , $K = 3$                                            | 42 |

| 4.30       | Visual representation of the delay tuning mechanism for a double TI                      |    |

|            | N-path circuit.                                                                          | 43 |

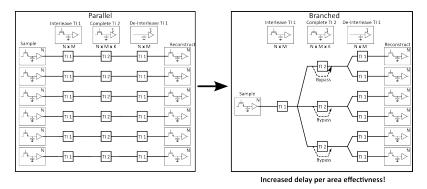

| 4.31       | Comparison of the conventional parallel TI N-path and the proposed                       |    |

| 7.01       | branched TI N-path                                                                       | 43 |

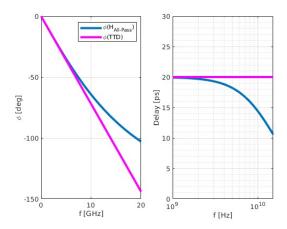

| 4.32       | The left side plot presents the phase of an ideal TTD, the magenta                       |    |

| T.U∠       | line, compared to a first order approximation, the blue line. To the                     |    |

|            | right, the resulting time delay is plotted                                               | 45 |

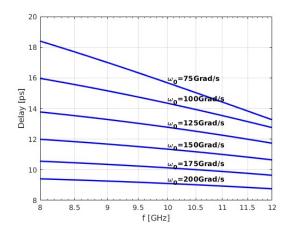

| 4.33       | Delay plots for different values of $\omega_0$ to showcase the increased delay           | 40 |

| 4.33       |                                                                                          | 45 |

|            | variation over frequency                                                                 | 40 |

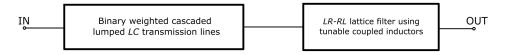

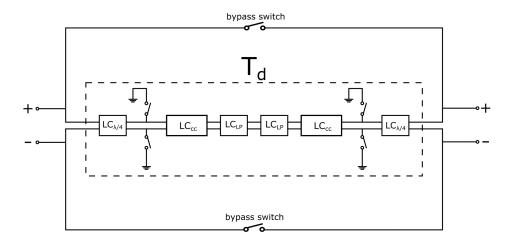

| 5.1        | The entire passive binary weighted TTD, with its two fundamental parts                   | 48 |

| 5.2        | Delay block with $\lambda$ or longer delay time $\dots \dots \dots \dots \dots$          | 50 |

| 5.3        | The impedance is inverted when switching on and off the switch after                     |    |

| 5.5        | the quarter wavelength transmission line                                                 | 51 |

| 5.4        | The $LC_{LP}$ stage with a low-pass switching mechanism                                  | 51 |

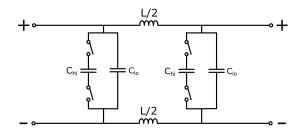

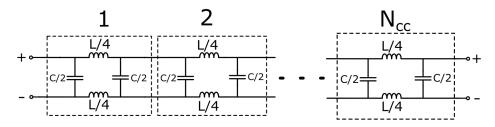

| 5.4<br>5.5 | The $LC_{CC}$ stage with $N_{CC}$ cascaded $LC$ stages                                   | 52 |

|            | Topology for the $\lambda/2$ delay block                                                 | 53 |

| 5.6<br>5.7 |                                                                                          |    |

| 5.7        | Topology for the $\lambda/4$ and $\lambda/8$ delay blocks                                | 53 |

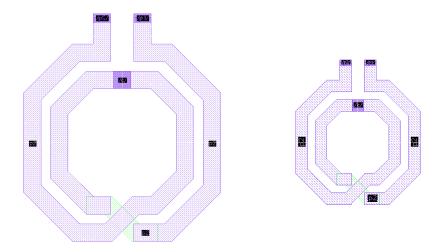

| 5.8        | Layout of the inductor for the <i>LC</i> stage with 25 ps of delay                       | 54 |

| 5.9           | Layout of the inductor for the <i>LC</i> stage with 12.5 ps of delay                                                                                                                     | 54       |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.10          | Signal power being attenuated the most by the biggest delay block                                                                                                                        | 54       |

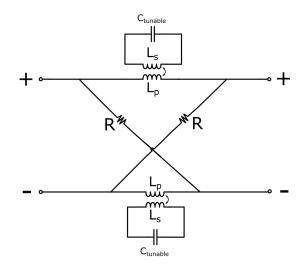

| 5.11          | The tunable coupled inductor implemented in an LR-RL lattice filter                                                                                                                      | 56       |

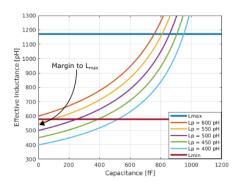

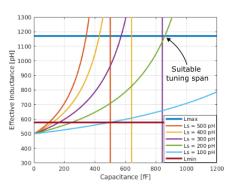

| 5.12          | Effective inductance as a function of capacitance for different primary                                                                                                                  |          |

|               | inductances                                                                                                                                                                              | 58       |

| 5.13          | Effective inductance as a function of capacitance for different sec-                                                                                                                     |          |

|               | ondary inductances                                                                                                                                                                       | 58       |

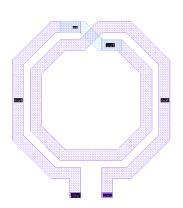

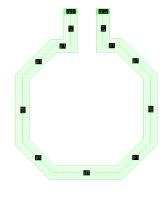

| 5.14          | Layout of the primary inductor coil                                                                                                                                                      | 58       |

| 5.15          | Layout of the secondary inductor coil                                                                                                                                                    | 58       |

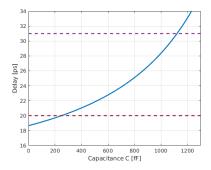

| 5.16          | Delay vs capacitance of the LR-RL lattice filter using the drawn cou-                                                                                                                    |          |

|               | pled inductor and an ideal capacitor                                                                                                                                                     | 59       |

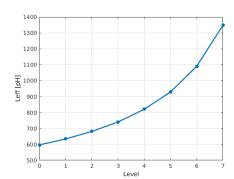

| 5.17          | Capacitance of the tunable capacitor for all the levels                                                                                                                                  | 61       |

| 5.18          | Effective inductance for all the levels                                                                                                                                                  | 61       |

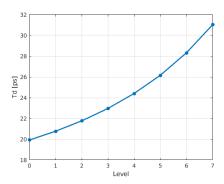

| 5.19          | Delay of the <i>LR-RL</i> lattice filter for all levels at 10 GHz                                                                                                                        | 61       |

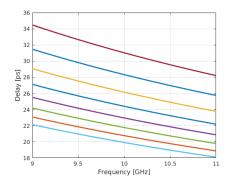

| 5.20          | Delay of the <i>LR-RL</i> lattice filter for all levels over frequency                                                                                                                   | 61       |

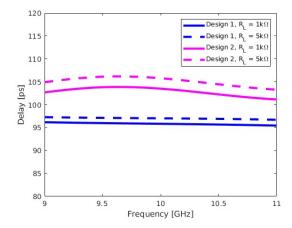

| 5.21          | Impact of output buffer input impedance $R_L$ on TTD performance of                                                                                                                      |          |

|               | the original N-path. Both design were set to generate around 100                                                                                                                         |          |

|               | ps of delay. For design one, this means a total of four clock pulses                                                                                                                     |          |

|               | $(\tau = 1/(8 \cdot 5 \text{GHz}) = 25 \text{ ps})$ and for the second delay a total of five clock pulses $(\tau = 1/(16 \cdot 3 \text{GHz}) = 20.8 \text{ ps}) \dots \dots \dots \dots$ | 64       |

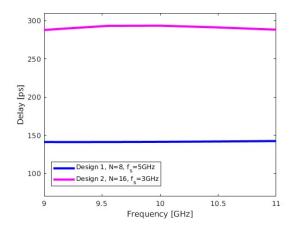

| 5.22          | Total delay for design one versus design two                                                                                                                                             | 65       |

| 5.23          | Output magnitude of first design ( $f_s$ = 5GHz, $N$ = 8) N-path circuit with                                                                                                            | 03       |

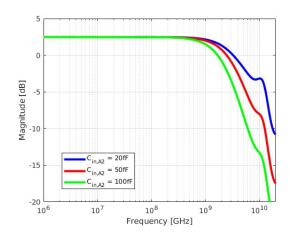

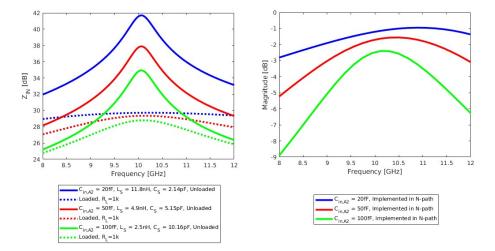

| J. <b>Z</b> J | increasing output buffer input capacitance $C_{in,A2}$                                                                                                                                   | 66       |

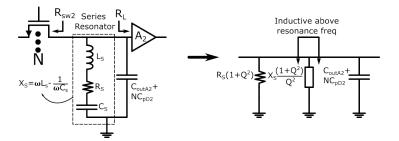

| 5.24          | LC resonator placed at the reconstruction node to resonate the para-                                                                                                                     | 00       |

| J. <b>Z</b> ¬ | sitic capacitance of the output buffer and switches. $C_S$ prevents a DC                                                                                                                 |          |

|               | short to ground through the inductor.                                                                                                                                                    | 66       |

| 5.25          | Isolated simulations of LC resonator to be implemented at the re-                                                                                                                        |          |

|               | construction node of the N-path carried out for unloaded and loaded                                                                                                                      |          |

|               | circuits with $C_{in,A2}$ =20f, 50f & 100f and $Q_L$ = 20                                                                                                                                | 68       |

| 5.26          | Magnitude of the output signal of the N-path after the LC Resonator                                                                                                                      |          |

|               | from figure 5.25 is implemented                                                                                                                                                          | 68       |

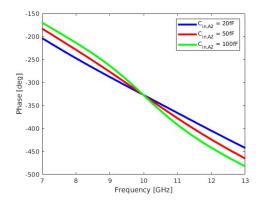

| 5.27          | Phase response of the N-path with an LC resonator at the reconstruc-                                                                                                                     |          |

|               | tion node for different values of $C_{in,A2}$ . As the capacitance increase,                                                                                                             |          |

|               | the quality factor also increases and the 90 degree phase shift is more                                                                                                                  | 00       |

| - 00          | visible                                                                                                                                                                                  | 68       |

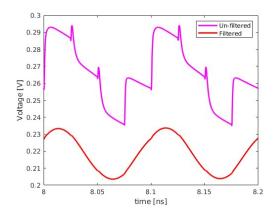

| 5.28          | Transient output signal of the N-path without the resonator (in magenta) and with the reconstar (in rad)                                                                                 | 60       |

| E 00          | genta) and with the resonator (in red)                                                                                                                                                   | 69       |

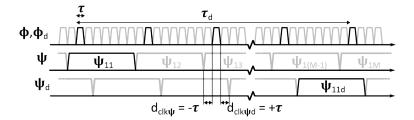

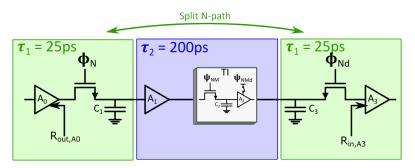

| 5.29          | Different clock settle times in TI part versus the fast sampling and reconstruction stages                                                                                               | 70       |

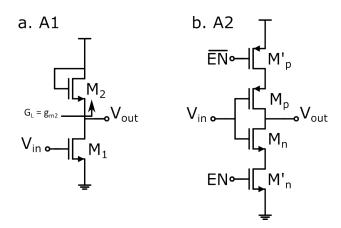

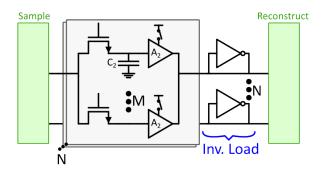

| 5.30          | Buffer topologies used in the TI N-path[28]                                                                                                                                              | 70<br>72 |

| 5.31          | Inverter loading of the output of the TI part                                                                                                                                            | 73       |

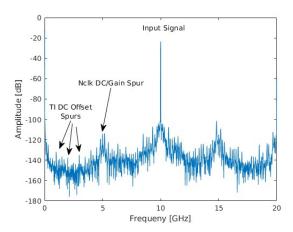

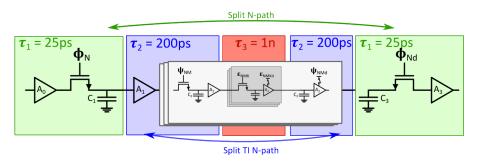

| 5.32          | Simulated frequency content of the output signal of TI N-path with an                                                                                                                    | 73       |

| J.JZ          | input signal power of -20dBm                                                                                                                                                             | 74       |

| 5.33          | The principle of introducing a second TI stage, effectively splitting the                                                                                                                | , -т     |

|               | already interleaved N-path once again.                                                                                                                                                   | 74       |

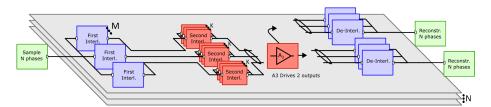

| 5.34 | Showcase of the implemented branching structure. One RF input is sampled by the N-path sample stage, interleaved twice and branched after the second TI into two reconstructed RF outputs | 75  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

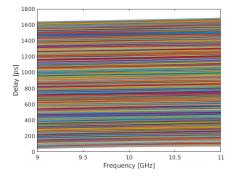

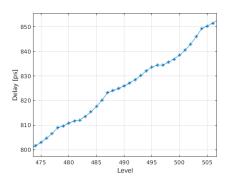

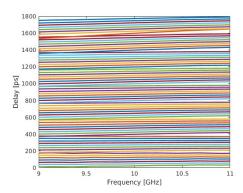

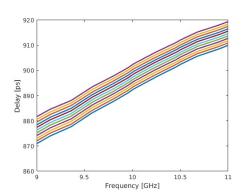

| 6.1  | Delay for the passive TTD circuit for all levels vs frequency                                                                                                                             | 78  |

| 6.2  | Zoomed in view of delay vs frequency for the passive TTD circuit                                                                                                                          | 78  |

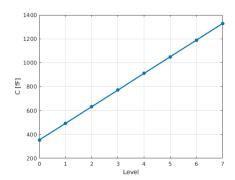

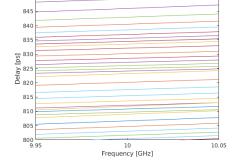

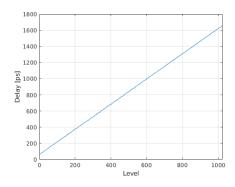

| 6.3  | Delay GHz vs level at 10 for the passive TTD circuit                                                                                                                                      | 79  |

| 6.4  | Zoomed in view of delay vs level at 10 for the passive TTD circuit                                                                                                                        | 79  |

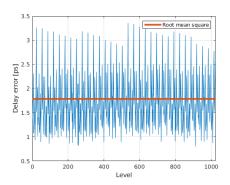

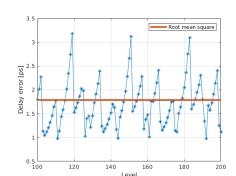

| 6.5  | Delay error for the passive TTD circuit at 10 GHz vs level with the rms of all levels                                                                                                     | 79  |

| 6.6  | Zoomed in view of delay error vs level at 10 for the passive TTD circuit                                                                                                                  | 79  |

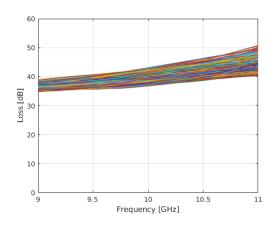

| 6.7  | Loss for all the levels vs frequency for the passive TTD circuit                                                                                                                          | 80  |

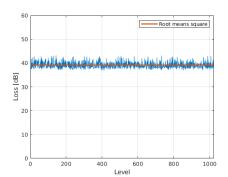

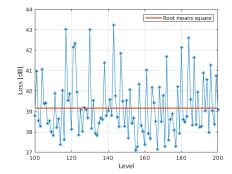

| 6.8  | Loss for the passive TTD circuit vs level with the rms of all levels                                                                                                                      | 80  |

| 6.9  | Zoomed in view of Loss vs level for the passive TTD circuit                                                                                                                               | 80  |

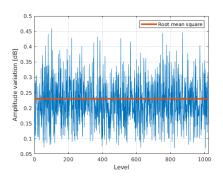

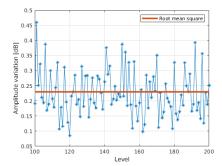

| 6.10 | Amplitude variation for the passive TTD circuit vs level with the rms of                                                                                                                  |     |

|      | all levels                                                                                                                                                                                | 81  |

| 6.11 | Zoomed in view of amplitude variation vs level for the passive TTD                                                                                                                        |     |

| 0.40 | circuit                                                                                                                                                                                   | 81  |

| 6.12 | '                                                                                                                                                                                         | 82  |

| 6.13 | IP3 for the passive TTD circuit with the $8\lambda$ -delay block turned <b>off</b> Noise figure and loss for the passive TTD circuit with the $8\lambda$ delay                            | 82  |

| 6.14 | block turned on and turned off                                                                                                                                                            | 82  |

| 6.15 | Full delay range of the N-path using coarse tuning. The $\Psi_d$ clock sets                                                                                                               | 02  |

| 0.10 | coarse tuning by steps of 200ps and clock programming sets medium                                                                                                                         |     |

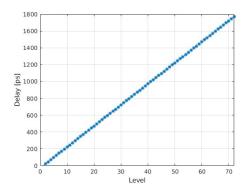

|      | tuning in steps of 25ps                                                                                                                                                                   | 83  |

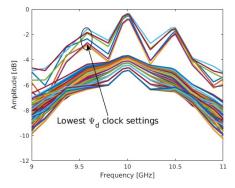

| 6.16 | Amplitude of the output signal for the coarse tuning settings. Note the                                                                                                                   |     |

|      | discrepancy of the lowest TI clock $(\Psi_d)$ highlighted in the figure                                                                                                                   | 83  |

| 6.17 | Delay at 10 GHz for the TI N-path with all the coarse tuning levels                                                                                                                       | 84  |

| 6.18 | Delay variation over the 100 MHz band width at 10 GHz for all coarse                                                                                                                      |     |

|      | tuning levels                                                                                                                                                                             | 84  |

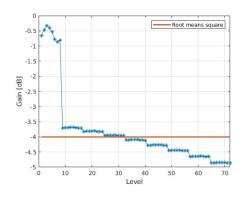

| 6.19 | Gain for all coarse tuning levels                                                                                                                                                         | 85  |

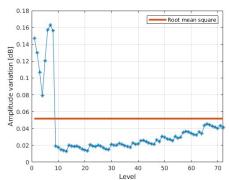

| 6.20 | Amplitude variation of the output signal for all coarse tuning levels                                                                                                                     | 85  |

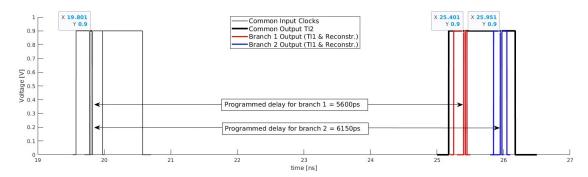

| 6.21 | Showcase of the fine tuning mechanism in which a delay is applied to                                                                                                                      |     |

|      | the output reconstruction clock to tune the delay achieved by the TI                                                                                                                      | 0.5 |

| c 00 | N-path                                                                                                                                                                                    | 85  |

| 6.22 | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                   | 85  |

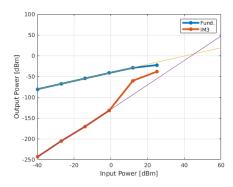

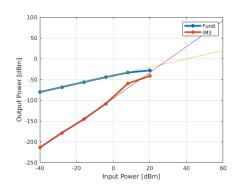

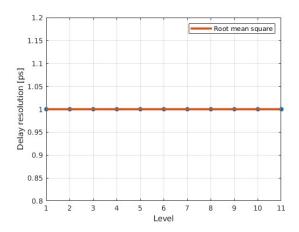

|      | Simulated delay resolution of the TI N-path for 1ps tuning increment Simulated large signal compression curve of the output power for the                                                 | 86  |

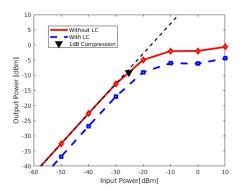

| 0.24 | TI N-path. The black marker marks the 1dB compression point at                                                                                                                            |     |

|      | -9.07dB when the LC is not implemented                                                                                                                                                    | 87  |

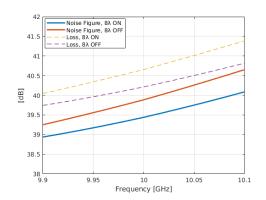

| 6.25 | Simulated noise figure for the TI N-path with and without the LC res-                                                                                                                     | 0.  |

|      | onator at the output. The LC tank increases the integrated NF of from                                                                                                                     |     |

|      | 4.06dB to 6.35dB in the bandwidth of 9.95-10.05GHz                                                                                                                                        | 87  |

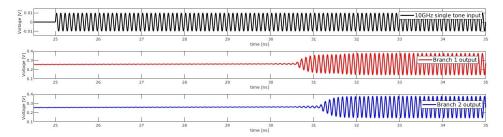

| 6.26 | Transient simulation of Branched TI N-path. Both outputs are shown                                                                                                                        |     |

|      | to achieve different delays of 5600ps and 6150ps respectively                                                                                                                             | 88  |

| 6.27 | Clock timing used to achieve the delay presented in figure 6.26                                                                                                                           | 88  |

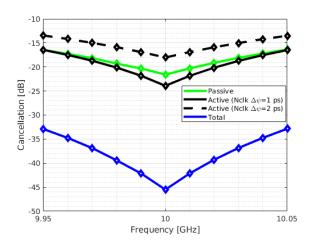

| 6.28 | Estimated cancellation across the entire 100 MHz BW for the passive pre-LNA SIC, the TI N-path post-LNA SIC using 1ps and 2ps of clock resolution and the combined pre- and post-LNA SIC using 1ps | 00 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Λ 1  | of clock resolution                                                                                                                                                                                | 89 |

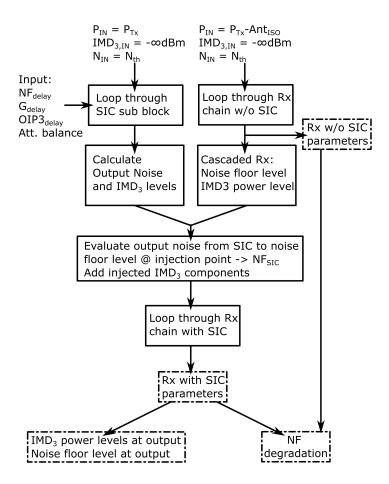

|      | Visualisation of the looped calculation method for the system calculations                                                                                                                         | 98 |

| A.2  | Flow chart displaying the method by which the performance degrada-<br>tion parameters was calculated                                                                                               | 90 |

## List of Tables

| 2.1                                    | System specifications                                                                                                          | 9                                |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.1                                    | Rx Specifications                                                                                                              | 12                               |

| 4.1                                    | The different modes of operation for the N-path circuit                                                                        | 34                               |

| 5.1<br>5.2                             | Delay requirements of the passive delay                                                                                        | 49                               |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | of delay                                                                                                                       | 52<br>54<br>55<br>59<br>60<br>60 |

| 5.9<br>5.10<br>5.11                    | straints from [31]                                                                                                             | 63<br>64<br>71<br>72             |

| 6.1<br>6.2<br>6.3<br>6.4               | Summary of the delay results for the passive TTD Summary of the amplitude results for the passive TTD                          | 80<br>81<br>83                   |

| 6.5                                    | across the entire delay range using the coarse tuning steps Summary of the output amplitude of the TI N-path across the entire | 86                               |

| 6.6                                    | tuning range                                                                                                                   | <ul><li>86</li><li>90</li></ul>  |

### **Abbreviations**

**FD** Full-Duplex

Tx Transmitter

SI Self-Interference

Rx Receiver

**SIC** Self-Interference Cancellation

**RF** Radio Frequency

**TTD** True-Time Delay

**BW** Bandwidth

LNA Low-Noise Amplifier

HD Half-Duplex

FDD Frequency-Division Duplexing

**TDD** Time-Division Duplexing

**DP** Direct Path

AR Antenna Reflection

**RP** Reflection Path

**EBD** Electrical Balancing-Duplexer

**SNR** Signal-to-Noise ratio

SINR Signal-to-Interference plus Noise Ratio

**PA** Power Amplifier

IF Intermediate Frequency

**BB** Baseband frequency

ADC Analog-to-Digital Converter

IMD3 Third-order Intermodulation Distortion

**NF** Noise Figure

OIP3 Output refered Third order Intercept Point

FIR Finite Impulse Response

LSB Least Significant Bit

LO Local Oscillator

**NMOS** *n*-type Metal-Oxide Semiconductor

TI Time InterleavedDC Direct Current

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

rms Root Mean Square

IP3 Third order Intercept Point

\_ Chapter

### Introduction

The monthly data traffic deployed by radio systems world-wide surpassed 140 Exabytes in Q3 of 2023 and are expected to increase by almost 30% during 2024 [1]. Meanwhile, spectrum licenses are ever increasing in value, not only for the crowded sub 6 GHz spectrum used in 5G New Radio. Exemplifying this is the recent license purchase in Sweden by operator Telia AB of 120MHz in the 3.50 to 3.62 GHz frequency range with a total price tag of SEK 760 millions [2]. Technologies which increases spectral efficiency could save the industry money and effectively help push towards higher data rates. A candidate for such technologies is full-duplex (FD) radio, which can theoretically double the data rate for a single channel by allowing the Receiver (Rx) and Transmitter (Tx) to both send and receive simultaneously at the same frequency, thus sharing time and frequency resources. One mayor hardware-related obstacle in FD communication is the strong Tx to Rx self interference (SI) signal, which consists of both high power direct path (DP) signals and lower power, multi path reflections (RP). The characteristic of the DP SI signals is short delay and transceiver specific, correlated to antenna isolation, while the RP SI signals may consists of many environment based multi-surface reflections.

This thesis investigates the implementation of a Self Interference Canceler (SIC) circuit, for the analog radio frequency (RF) domain cancellation at an operational frequency of 10 GHz. Such a circuit would be benchmarked by the ability to recreate the SI signals in terms of amplitude and delay, but also by the degradation in Rx performance due to noise and distortion injection. Main focus has been directed towards the true time delay (TTD) generation circuits where two techniques, categorized into passive and active, are investigated. A passive TTD circuit, intended for pre-LNA (Low-Noise Amplifier) injection, is designed containing two parts; a binary weighted delay chain using lumped *LC* transmission lines for course tuning, and an *LR-RL* lattice filter with tunable coupled inductors for fine tuning. Further, an active TTD is designed using a Time Interleaved (TI) N-path circuit including an innovative way of branching the N-path to reduce chip-area for multiple delay generation scenarios.

2 Introduction

The report begins with an overview of the entire FD system in chapter 2, before moving on to a pre-study about the analog RF SIC in chapter 3. The SIC pre-study covers the specific considerations for an analog RF SIC and is concluded with the proposed hybrid SIC topology. This is then followed by the principle of operation of the designed TTD circuits in chapter 4, where passive and active TTD circuits are covered separately. In chapter 5, detailed designs of these circuits are presented. Chapter 6 covers the simulation results for each TTD circuit. The TTD results is first presented separately before estimating the cancellation that these circuits could achieve implemented in an SIC. Finally, the work is summarized and concluded in chapter 7.

In this work, neither layout nor tape-out for any circuit is considered as an end goal. The main aim is to understand the dynamics and requirements of the SIC block in an FD system and based on this, propose different TTD circuits topologies that could be considered as candidates for future FD transceivers. The authors conducted the FD overview and SIC pre-study together, but the work on the passive and active TTD was done separately. Vejde investigated a passive binary weighted TDD circuit while Vilgot focused on an active TI N-path TTD circuit. The results and discussion regarding the implementation of a hybrid SIC was made jointly.

Ericsson AB provided the necessary CAD tools; Cadence Virtuoso and ADE for circuit simulations, Layout XL suite and Momentum plugin for inductor layout and simulations. The work was carried out in 22nm fully depleted silicon on insulator CMOS technology. Office space and computers were also provided by Ericsson AB.

### **Full Duplex System Overview**

FD communication could in theory double the capacity in comparison with half-duplex (HD) communication. However, the use of FD introduces the new challenge of Tx-to-Rx SI. This chapter gives an overview of the different challenges and advantages of FD along with a summary of the many different SIC techniques used to cancel the SI. Finally, a set of system specifications is set for which this thesis is aimed at.

#### 2.1 Full-duplex vs Half-duplex

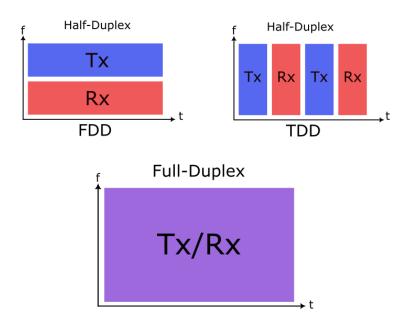

A fundamental challenge for telecommunication systems is to separate the Rx signal from the Tx signal. The down-link from the base station is transmitted at far higher signal power than the up-link power received from the user end. Therefore, these signals needs to be separated in order for the received up-link signal to be distinguishable for the base station and vice versa for the user end. The most common way to do this has for long been the half-duplex system. A HD system allows communication in both directions but not at the same frequencies or at the same time. HD systems differentiates the Rx signals from the Tx signals using frequency-division duplexing (FDD) or time-division duplexing (TDD). This way the Tx signals are transmitted on other frequencies or at other time slots than the Rx signals are received. This is an efficient way of isolating the Tx signals from the Rx signals in order to ensure clean bidirectional communication, by minimizing the interference and ensuring co-existence with other wireless equipment. [3]

However, a drawback of half-duplex systems is that the spectral efficiency is not as high as it could be because of the frequency- or time-division. In order to get the maximum spectral efficiency one should use the entire allocated BW for both Rx and Tx simultaneously. Therefore, full-duplex, or as it is also called inband full-duplex (IBFD), should be used in order to achieve maximum spectral efficiency. This is because FD instead transmits and receives signal on the same frequencies and at all times. The difference between HD and FD is illustrated in figure 2.1. [4]

**Figure 2.1:** The difference between half-duplex and full-duplex illustrated in a time-frequency graph

A FD system, however, have the inherent problem of self-interference (SI), i.e. because the strong Tx signal, the SI, will leak into the Rx path and drown out the weaker Rx signals. This results in a desensitization of the Rx, by either, drowning the Rx signal with the SI signal, compressing the Rx and/or introducing in-band distortion from the Rx non-linearities. Therefore, an FD system needs SIC in order to suppress the Tx signal to an acceptable level for the reliable signal detection in the Rx. [3]

#### 2.2 Self-Interference Paths

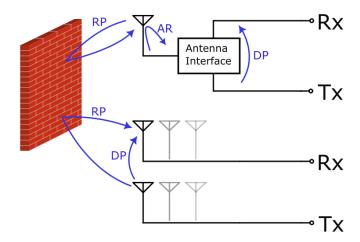

In a FD system, the Tx signal can take different paths from the Tx side of the transceiver to the Rx side, which are usually divided into three different categories of interference paths: direct path (DP), antenna reflection (AR) and multipath reflection path (RP). The paths will be different depending on whether a single antenna is used for both Tx and Rx or the Tx and Rx have separated antennas or antenna panels, this is shown in figure 2.2.[3]

**Figure 2.2:** Self-interference paths from Tx to Rx for different antenna structures.

If a single antenna is used for both Tx and Rx, then an antenna interface is needed to isolate the incoming Rx signal from the outgoing Tx signal. For a single antenna solution, the antenna interface is usually implemented using a circulator or an electrical balancing-duplexer (EBD) and in either case there will inevitably be some leakage of the Tx signal into the Rx chain, and this is the DP interference. In the the single antenna case, the antenna will cause some small reflections of the Tx signal back into the Rx path. This is the AR interference and only exists for the single antenna case. [3]

When separate antennas are used for Tx and Rx there will be no interference paths through any antenna interface or the antenna itself. For the separated antenna case, the DP path refers the to shortest path over the air from the Tx antenna to the Rx antenna. In both the single and separate antenna case, there will also be multipath reflections, caused by the Tx signal reflecting off of different objects in the environment. [5]

The Tx signal will appear in the receiver with different signal levels and after different delay times depending on which path of propagation the signal has taken. The DP and AR signals will have a constant signal level and delay time since these paths only depends on the transceiver itself. The RP signals will instead have a dynamic behavior since the environment surrounding the transceiver could change. The self-interference from these different types of paths must therefore be cancelled differently by the SIC. [5]

For this report separate antennas for Tx and Rx is assumed and no further consideration for an antenna interface with the AR and DP interference is needed. A normal antenna array is assumed with 4x2 antenna panels with 2  $\lambda$  of antenna element spacing and 4  $\lambda$  Tx-to-Rx panel separation. This antenna solution has a

maximum distance from a Tx antenna element to a Rx antenna element of  $14 \lambda$ . Therefore, the maximum delay time of the DP interference will be  $14 \lambda$ . The RP interferences can be estimated to have up to several 100s of  $\lambda s$  of propagation, but with much lower signal level. To note, the signal level of this interference decrease and the delay time increase with increased distance to the object of reflection.

#### 2.3 Rate gain region

The rate gain region is the region of system parameters where FD outperforms the conventional HD in terms of bit-rate. This is investigated in order to determine how much is gained from using FD instead of HD. According to the Shannon-Hartleys theorem, the maximum channel capacity *C* is [4]:

$$C = BW \cdot log_2(1 + SNR) \tag{2.1}$$

where *BW* is the bandwidth in [Hz], *SNR* is the Signal-to-Noise Ratio in linear scale and channel capacity *C* is given in bits per second [bits/s].

In FD systems, the achieved SNR can be rewritten in terms of Signal-to-Interference plus Noise Ratio (SINR). This term takes into account the self-interfere signal (SI) coming from the adjacent Tx which will leak into the Rx, assuming a single base station and a single user end. FD utilizes double the bandwidth for both Rx and TX compared to FDD since they share the entire BW instead of splitting it up in half. The capacity for FD is also doubled compared to TDD because both Tx and Rx is operated during double the amount of time when using FD instead of TDD. This means that double the amount of bits can be sent during this doubled amount of time. Therefore, the ratio k of increase in maximum channel capacity for FD compared to HD is

$$k = \frac{C_{FD}}{C_{HD}} = \frac{2 \cdot BW \cdot log_2(1 + SINR_{FD})}{BW \cdot log_2(1 + SNR_{HD})} = 2 \cdot \frac{log_2(1 + SINR_{FD})}{log_2(1 + SNR_{HD})}$$

(2.2)

To gain the benefits of a FD system compared to a HD system, the  $SINR_{FD}$  needs to be increased. To achieve this, the interfering Tx signal needs to be cancelled. Further, the method by which the SI is mitigated should not increase the noise floor of the Rx significantly. It is also evident, that theoretical maximum rate gain in bit-rate for an FD system is 2 when  $SINR_{FD} = SNR_{HD}$ , i.e. when the SI power is well below Rx thermal noise floor. [4]

#### 2.4 Different SIC-Techniques

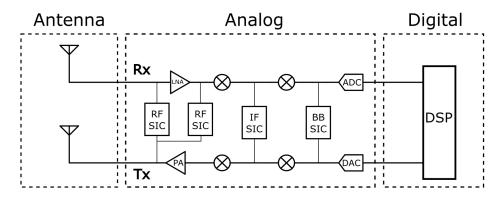

The total SIC needed for FD operation is usually more than 100 dB[6], [3], [7]. For achieving this, different SIC-techniques in the different domains, antenna domain, analog domain and digital domain, are all needed to be used together. The different domains of the transceiver where SIC can be used are illustrated in figure 2.3. In this chapter a brief summary of SIC in each domain is presented in order to get an overview of the entire area of the FD system.

**Figure 2.3:** The three domains of the transceiver where SIC can be performed [5]

Figure 2.4: Overview of the SIC techniques in a tree diagram [5]

Within each domain there are a lot of different approaches for SIC. An overview of the different techniques within each domain is shown in figure 2.4. In the following subsections, a brief summary of the SIC techniques within each domain is presented.[5]

#### 2.4.1 Antenna domain

In the antenna domain, a main factor for SIC is whether the transceiver uses a shared antenna for both Tx and Rx or if they are separated. For use of a shared antenna, the only way of separating the Tx and Rx is by use of an antenna interface which usually is a circulator [8] or an EBD [9].

When separated antennas are used there are many ways of suppressing the Tx signal from entering the Rx antenna. The most basic method is to simply separate the antennas physically a further distance from each other [10]. Another method is to use Rx and Tx antennas operating on orthogonal polarizations since different polarizations do not couple [11]. If multiple Tx and Rx antennas are used the method of beamforming in the antenna domain could be used for steering the Tx and Rx beams away from each other [12].

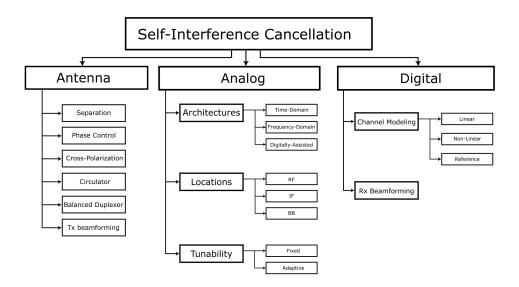

#### 2.4.2 Analog domain

For analog SIC, the Tx signal from the output of the power amplifier (PA) is injected into the analog domain of the Rx chain after being modified to match the SI. By recreating the SI using time-domain or frequency-domain approaches and inverting it, the recreated SI will cancel out the original SI when injected into the Rx. For frequency-domain approaches, tunable band-pass filters are used to modify the center frequency, phase response and quality factor to match the SI response [13]. For the time-domain approach, true-time delays are used to match the delay from the propagation via the interference paths [14].

The modified Tx signal can be injected at either radio frequency [15], intermediate frequency (IF) [16] or baseband frequency (BB) [5] which all have different advantages and disadvantages. For RF injection both pre-LNA [15] and post-LNA [14] injection is possible. The analog SIC techniques can also be divided into either fixed or adaptive SIC. Fixed SIC do not use any feedback and targets the DP and AR interference which do not change over time[17]. Adaptive SIC is able to change its tuning according to changes in the surrounding using a feedback control circuit and can therefore target the dynamic RP interference[15].

Analog SIC can also be digitally assisted by using digitally implemented canceller taps. This allows for significantly higher number of taps which can improve canceller flexibility. [18]

#### 2.4.3 Digital domain

In the digital domain, a common SIC method is channel modelling, where the SI is reconstructed using the knowledge of the Tx signal. After correct filtering of the Tx signal it can be combined with the received signal after the analog-to-digital converter (ADC) to provide further interference suppression. There are multiple channel modeling techniques divided into linear[19] and non-linear methods[20].

Apart from digital channel modelling, one can also use beamforming in the digital domain instead of the antenna domain. By use of digital signal processing, the beams of the Tx and Rx antennas can be steered away from each other and isolate the Rx antennas from the Tx signal. [21]

#### 2.5 System Specifications

There are many different types of radio transceivers and a FD system will have to be designed individually for different transceivers. Therefore, a set of assumptions are assumed for the radio system and for the rest of the FD system. The system specifications are showed in table 2.1 and are chosen for a general radio transceiver.

Table 2.1: System specifications

| Parameter                    | Value   |

|------------------------------|---------|

| Transmitter Power            | 23 dBm  |

| Carrier Frequency            | 10 GHz  |

| Operational Bandwidth        | 100 MHz |

| Antenna Isolation            | 60 dB   |

| Digital Cancellation         | 30 dB   |

| Analog Baseband Cancellation | 15 dB   |

It is not crucial for these specifications to be founded on strong scientific research since it serves as a benchmark for the specific full-duplex system designed in this report. It is however important that these values are realistically chosen in order for the system to be a viable option for real life application. Thus, these values are general for modern day mobile telecommunication systems. A main take-away is the carrier frequency at 10 GHz, which is higher than what most other full-duplex research aims at [22].

### Considerations for RF SIC

To ensure proper design of the TTD, the effect of non-idealities need to be considered when looking at the implementation of the SIC system as a whole. In this section, system considerations such as: Rx-specifications, total cancellation, delay resolution, injection points and attenuation is discussed together with the non-idealities, such as noise and distortion. Along with this, a sub-chapter covering the required cancellation and delay resolution is also included. Concluding this chapter is a section which introduces a proposed hybrid topology, in which a pre-LNA SIC is implemented with a passive TTD circuit and a post-LNA SIC is implemented with an active TTD circuit.

#### 3.1 System Hardware with ideal sub-blocks

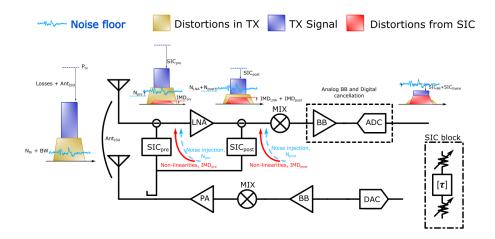

To understand and calculate performance degradation of the Rx depending on SIC parameters, a general FD transceiver block schematic was used. The transceiver utilizes two SIC paths, injecting both pre- and post-LNA. Each SIC is modeled as a delay cell in series with two variable attenuators. The attenuators are assumed to have infinite linearity and a noise figure equal to their attenuation (passive components). The Rx and Tx antennas are considered to be ideal split panel antennas and isolated by 60dB. This system is presented in figure 3.1 along with an illustration of the different signals and non-idealities.

Figure 3.1: Overview of the transceiver topology and the different signal levels

Starting at the Rx antenna, the received signal will include the interfering Tx signal and distortions from the PA, i.e. the SI - both attenuated by the antenna isolation and path losses. Before the LNA, the first SIC block will cancel some of the SI signal. However, the SIC block will also inject noise ( $N_{pre}$ ) and nonlinearities ( $IMD_{pre}$ ) created within the block itself and these non-idealities will not be cancelled since they are not correlated to the Tx non-linearities nor the Tx noise received by the Rx antenna.

After the LNA, an additional SIC block injects a second cancellation signal with its non-idealities ( $N_{post}$  and  $IMD_{post}$ ). Continuing on, the signal passes through the BB processing, where some additional analog cancellation takes place, by additional baseband SIC blocks (not shown in figure 3.1), and this may occur prior to the ADC, but also after the ADC in the digital domain. Finally, at the output of the Rx, the interfering Tx signal has gone through the Rx signal chain and is suppressed through numerous cancellation stages, but at the cost of increased Rx noise figure which reduce the Rx sensitivity. Note that it is assumed in this analysis that the combiner element of the SIC does not add any losses or add any noise to the system. The Rx specifications, presented in table 3.1, where chosen to reflect an Rx operating at 10 GHz in typical cellular application.

Table 3.1: Rx Specifications

| Block        | Gain [dB] | NF [dB] | OIP3 [dBm] |

|--------------|-----------|---------|------------|

| LNA          | 20        | 3       | 10         |

| Mixer        | -10       | 10      | 5          |

| BB Amplifier | 30        | 6       | 10         |

| ADC          | 0         | 20      | 10.5       |

# 3.2 Noise Figure degradation from noise injection and non-linear distortions

If it would be possible to construct a SIC block that is able to fully cancel the SI signal, ideally this SIC should not degrade the sensitivity of the receiver in any way. However, this is not the case due to the injection of noise and nonlinear distortion, such as Third-order Intermodulation Distortion (IMD3), from the SIC into the Rx chain. Surveying the research within FD cancellation circuits shows that a sub 2 dB noise figure (NF) degradation of the Rx chain would be a reasonable benchmark to aim for [23][24][25][26]. Degradation in NF of the Rx depends on the total noise power generated within the SIC itself. This noise power, will consist of amplified or attenuated thermal noise from the input source and additional noise introduced within the SIC. The noise figure is given by [27]:

$$NF = SNR_{in[dB]} - SNR_{out[dB]} = (S_{in[dB]} - S_{out[dB]}) + (N_{out[dB]} - N_{in[dB]})$$

(3.1)

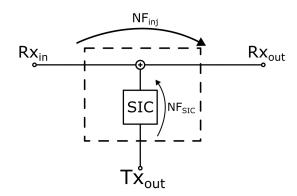

If the input source and and output load are considered to have the same noise temperature, then the only factor which determines the total degradation of the output noise floor is the additional noise created within the SIC. For circuits where the additional noise is zero, for example in a purely passive circuit, the total noise power at the output is limited by the thermal noise, and therefore not correlated with the NF of the circuit itself. To quantify the noise injection, the total output noise of the SIC was calculated and added to noise floor of the receiver at the injection point as shown in figure 3.2. The injected noise figure  $NF_{inj}$  gives the actual NF related to the Rx input and is used when calculating Rx link-budget.

Figure 3.2: Noise injection from the SIC into the Rx

The non-linear distortions are tackled by ensuring that the linearity of the SIC chain is high enough to not inject IMD3 distortion at a power level of 15 dB below the noise floor at the point of injection. It is shown in the calculations below that this margin would degrade an arbitrary noise floor level of N by only 0.135 dB

$$N_{tot} = 10 \cdot log(10^{N/10} + 10^{(N-15dB)/10}) = 10 \cdot log(10^{N/10}(1 + 10^{-15dB/10})) =$$

$$= N + 10 \cdot log(1 + 10^{-15dB/10}) = N + 0.135$$

It is noted that more non-linear distortions are created within the SIC, apart from IMD3. Even order intermodulation products are also created but can be suppressed by using a differential design. Harmonic distortion from the Tx signal is not a concern for this system, since these frequencies will be far above the channel band. Depending on the implementation of the delay circuit, spurious tones may be injected to the Rx. If this is the case, these delay cells needs to be well designed since they could also degrade the sensitivity of the Rx.

#### 3.3 Attenuation Balance and Injection Points

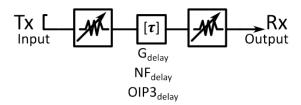

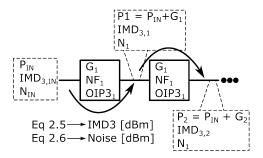

The model of the SIC block, as seen in figure 3.3, consists of a TTD between two variable attenuators. The total attenuation if the SIC block should match the combined attenuation from the fixed antenna isolation and the dynamic multipath propagation loss. The distribution of the attenuation between the input Tx side and output Rx side is very important since it affects the impact of the non-linearities.

Figure 3.3: Simplified model of an SIC block

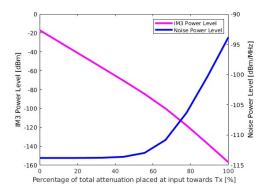

If all attenuation is distributed towards the Tx, the TTD sees a much smaller input signal power and the linearity requirement is eased. However, if all attenuation happens before the delay, the noise injection into the Rx is increased since the noise is not attenuated at the end of the SIC block. Note that this is not the case for delay blocks that are limited by thermal noise, i.e passive delay circuits, since these do not increase the noise above the thermal limit. The opposite is true when most of the attenuation is placed towards the Rx - higher linearity requirement of the SIC but better noise performance. This trade-off is shown in figure 3.4. As the attenuation is placed towards the Rx, noise power injection is low while the non-linear IMD3 products increases. Placing the attenuation towards the Tx side results in higher noise power injection but lower distortion requirements. In figure 3.4, this trade-off is showcased, and the TTD circuit was given an arbitrary

specification. The calculations used to generate figure 3.4 and all further graphs in this sub section are described in the appendix, section A.1. As mentioned before, the attenuation blocks are assumed to be ideal passive attenuators with a NF equal its attenuation. The extraction of the Tx signal and injection of the SIC output signal into the Rx is assumed to be ideal with no losses.

**Figure 3.4:** The trade-off in attenuation distribution for the SIC. Both power levels in this figure are output referred.

Another design aspect is the different injection points. For pre-LNA injection, adding anything to the signal path before the LNA will heavily impact the Rx NF and is required to have a low noise power level. This can be achieved with low noise circuits, or with highly linear circuits which would allow to shift most of the attenuation towards the Rx side and thus, attenuate the noise. Post-LNA injection is less sensitive to noise since the signal is already amplified by the gain of the LNA. This behavior can be seen in figure 3.5 and 3.6 below. The figures shows two contour plots of the NF degradation in the Rx, for pre- and post-LNA injection, as a function of the noise figure of the delay and attenuation distribution, at a Tx output power of 23 dBm. The thick, black lines indicates the 2 dB noise figure degradation target for both cases and it is evident that the more attenuation shifted to the input, the more stringent the NF requirements of the delay become.

**Figure 3.5:** Contour line of NF degradation for pre-LNA injection.

**Figure 3.6:** Contour line of NF degradation for post-LNA injection.

In the case of linearity, the requirements for the pre-LNA injection point is less stringent compared to that of the post-LNA injection. The reason for this is that the post-LNA SIC have less total attenuation due to the gain of the LNA. In section 3.2, a goal was introduced for linearity in which the IMD3 products were supposed to be suppressed 15 dB below the noise floor. For the delay block parameters, this can be translated into an Output referred Third Order Intercept Point (OIP3). By sweeping the OIP3 of the delay and the attenuation balance the following plots where created in figure 3.7 and 3.8. The figures shows the contour plots of the IMD3 power levels normalized to the noise floor. On the horizontal and vertical axis the OIP3 and the attenuation balance are swept respectively.

Figure 3.7: Contour line of IMD3 power levels normalized to the noise floor for pre-LNA injection.

Figure 3.8: Contour line of IMD3 power levels normalized to the noise floor for post-LNA injection.

From figure 3.5 and 3.6, a certain NF of the TTD circuit will give some upper limit for the attenuation fraction towards the Tx, based on the crossing point of the 2 dB NF degradation line. If instead the figures 3.7 and 3.8 are analysed, a lower limit for the attenuation fraction towards the Tx is given, based on the crossing

point of the -15 dBm IMD3 line.

In the case of the pre-LNA SIC, the attenuation balance ought to be shifted towards the Rx side to alleviate the required NF of the delay block. However, this shift would put greater requirements on the linearity of the delay cell. When considering the fact that the noise and linearity requirement can be interchanged like this, it is obvious that pre-LNA injection puts greater demands on the delay block compared to post-LNA. In the post-LNA SIC, the linearity completely dominates the non-idealities while the NF degradation due to noise injection is very small even for a large NF of the TTD circuit. This implies that the trade-off in attenuation balance is less severe and that most of the attenuation ought to be biased towards the Tx.

To further show the difference between pre- and post-LNA injection, consider a TTD circuit with NF equal to 20 dB. For the pre-LNA injection case this means that maximum fraction of attenuation shifted towards the Tx is 60% (figure 3.5), which in turn requires an OIP3 of at least 20 dBm (figure 3.7). Now, looking at the post-LNA case in figure 3.6. A NF of 20 dB would not result in any unacceptable NF degradation regardless of attenuation balance. In other words, all of the attenuation balance should be shifted towards the Tx which would give a required OIP3 of 10 dBm from figure 3.8. From this example it is evident that even though the linearity requirements is more stringent for the post-LNA injection, the combined effect of noise and linearity requirements for the pre-LNA injection makes it overall harder to design delay blocks for the pre-LNA SIC.

# 3.4 Cancellation Required in the analog RF domain

As discussed previously, a fundamental prerequisite of any FD system is the need to suppress the interference coming from the Tx. From section 2.5, additional cancellation coming from the digital domain, antenna domain and BB analog domain is covered. The aim for the SIC block in this work is to, together with the cancellation from other domains, suppress the interfering Tx signal 15 dB below the noise floor of the receiver. In figure 3.1, one can follow the Tx interference signal throughout the Rx chain to arrive at the following expression for the required cancellation:

$$P_{tx} - Ant_{ISO} + G_{Rx} - (SIC_{pre} + SIC_{post} + SIC_{BB} + SIC_{Digital}) < N_{Floor_{Rx}} - 15dB$$

(3.2)

Where  $G_{Rx}$  is the cascaded gain of the Rx chain,  $N_{FloorRx}$  is the noise floor power level after the ADC,  $SIC_{pre}$ ,  $SIC_{post}$ ,  $SIC_{BB}$ ,  $SIC_{Digital}$  is the different sources of cancellation. With the specification for the Rx chain presented in table 3.1, the cascaded gain is equal to 40 dB and the cascaded NF is 3.8 dB. The input noise floor level is -93.8 dBm for a 100 MHz bandwidth according to eq.A.1. Thus, the

total noise power at the output of the Rx is:

$$N_{Floor_{Rx}} = -113.8$$

[dBm] +  $10log(BW[MHz]) + G_{Rx} + NF_{Rx} = -113.8$ dBm +  $10log(100MHz) + 40dB + 3.8$ dB =  $-50$ dBm

Using the digital, analog BB cancellation and antenna isolation specified in table 2.1 and the noise floor calculated above, the minimum required cancellation in the analog RF domain ( $SIC_{post} + SIC_{pre}$ ) is:

$$SIC_{post} + SIC_{pre} = P_{Tx} - Ant_{ISO} + G_{Rx} - (SIC_{BB} + SIC_{Digital}) - N_{floorRx} + 15dB = 23dBm - 60dB + 40dB - (15dB + 30dB) - (-50dBm) + 15dB = 23dB$$

Note that the noise floor used in this calculation assumes that the SIC is not introduced into the system or that it is noise-less. In reality, when the SIC is added to the Rx, the noise floor will increase which will relax the cancellation requirement but decrease the achieved SINR. Further, this is the required RF cancellation for suppressing DP SI since this interferer is only attenuated by the antenna isolation. The RP SI is however attenuated further because of multipath propagation losses.

# 3.5 Cancellation vs Delay and Amplitude Error

All self interfering signals will have some random delay. If the goal is to cancel all of these interfering signals by 23 dB, then there will be some minimum delay resolution that can achieve this. To actually cancel an interfering signal successfully, the SIC block needs to match its delay down to some small error. Otherwise, the delay mismatch will cause the cancellation to be very weak since the signals overlap very little in time. To calculate the minimum delay resolution needed for the above specified cancellation, a simple test bench was used. The channel was simulated by a transmission line, tuned to the wavelength of 10 GHz. At the output, an SIC signal was injected which could be tuned by some delay error and amplitude error. The achieved cancellation at 10 GHz was simulated for different delay and amplitude errors. The results of this is presented in figure 3.9.

**Figure 3.9:** Simulated contour plot of cancellation versus amplitude error and delay error

The maximum delay error that achieves 23 dB of cancellation is around 1 ps for amplitude errors up to 0.5 dB. However, the error is not directly corresponding to the resolution. The worst case scenario happens when the delay of an interfering signal happens to be exactly in the middle between two delay tuning steps. The distance between these two steps is the resolution. Thus, the minimum resolution is the maximum error times two which in this case is 2 ps.

# 3.6 Proposed Hybrid Topology

An SIC circuit can be implemented using either passive or active TTD, which have different advantages and disadvantages. It is possible for active TTD topologies to generate long delays [28], which is more difficult for passive topologies without introducing too much loss or using too much chip-area. Unlike an SIC built with active components, a purely passive SIC will not inject any additional noise, apart from the thermal noise, into the Rx chain as discussed in section 3.2. Furthermore, the linearity of an active SIC is limited by the rail-to-rail voltage swing, while the passive components are completely linear until the circuit breaks down.

For a split antenna, as considered in this report, the DP interference have high signal power and short delays of up to 15  $\lambda$ . Because of its high power, the DP SI will desensitize the LNA and distort the signal if not cancelled beforehand. The RP interference on the other hand, consists of multi-path reflections which have lower signal power and longer delays of up to several tens of  $\lambda$ . Thus, a pre-LNA SIC must cancel the short delayed DP SI, but not necessarily the longer RP SI which instead can be cancelled post-LNA.

It can thus be concluded, that the active SIC should be placed post-LNA in order to alleviate noise and linearity requirements, and target the RP SI. In order to cancel the DP SI and avoid saturation of the LNA, the passive SIC is placed pre-LNA. This is possible since the passive SIC generates no additional noise and have no linearity limitations due to rail-to-rail voltage swing. In this report, the authors propose a hybrid technique which uses both passive and active TTD elements to achieve the full RF SIC block.

Chapter 4

# True Time Delay Circuits

This chapter is split into two parts, where passive and active TTD generation are covered separately. Active delays have low linearity and high noise figure, which can limit their usage for pre-LNA injection. However, active delays are also known for achieving longer delays in smaller silicon area compared to passive delays. The low noise and high linearity performance of passive TTD circuits are better suited for pre-LNA injection. The combination of the active and passive delays can be required in FD SIC systems. This chapter presents common topologies of analog active and passive TTD circuits along with their limitations.

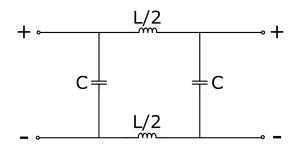

#### 4.1 Passive TTD Circuits

The passive TTD circuits sub-chapters are divided into two parts. The first part is regarding how to generate a delay using only passive circuit elements and this part covers known circuits that could be used in a TTD system. There are many ways of generating a delay using passive elements and they are all based on utilizing the negative phase shift from some sort of filter. A negative phase shift translates into a delay time that may be independent on the operating frequency. The two topologies for creating a negative phase shift covered in this report are the lattice filter and the lumped transmission line filter. Within the field of lattice filters, three types of filters are presented. For both topologies the TTD circuit is designed differentially for lower electromagnetic interference, ground noise and voltage handling.

The second part is about how to tune a passive TTD, and here two technologies are proposed; a binary weighted delay chain and a tunable coupled inductor. An advantage of passive TTD circuits is that the noise and non-linearity contributions are very low. However, to tune the delay time, some sort of switching mechanism is needed, which introduces more loss and non-linearities contributions to the SIC system. Therefore, an important aim for the tuning methods is to avoid the need for switches in the signal path.

#### 4.1.1 Delay generation

#### 4.1.1.1 Lattice All-Pass Filters

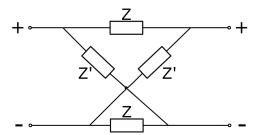

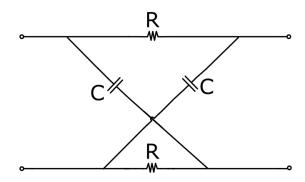

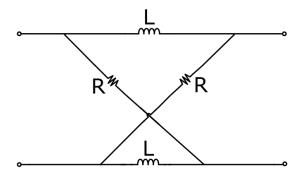

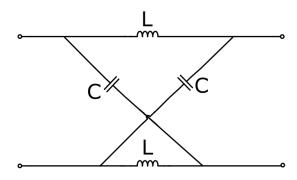

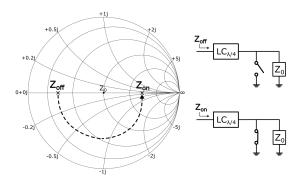

A lattice filter, also called an X-section, is a differential all-pass filter formed by crossing two parallel impedance's between the two differential paths as shown in figure 4.1. This filter is symmetric, meaning the input and output are reciprocal.[29]

Figure 4.1: General lattice all-pass filter

The impedance for the lattice filter  $Z_{lat}$  is given by eq.4.1. [29]

$$Z_{lat} = \sqrt{Z \cdot Z'} \tag{4.1}$$

The crossed elements Z' are called the lattice elements, and they should be designed to be the dual of the series element Z with respect to the characteristic impedance  $Z_0$  according to eq.4.2. The lattice and series elements can be implemented as either resistances, capacitances or inductances.[29]

$$\frac{Z}{Z_0} = \frac{Z_0}{Z'} \tag{4.2}$$

If eq.4.2 is fulfilled, the circuit will have the same impedance for all frequencies. Since the impedance is the same for all frequencies, the filter will also have the same attenuation for all frequencies, making it an all-pass filter. The transfer function for the lattice filter is given by eq.4.3.[29]

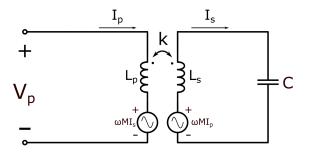

$$H(j\omega) = \frac{Z_{lat} - Z}{Z_{lat} + Z} \tag{4.3}$$