# Integration of Ferroelectric HfxZr1-xO2 on Vertical III-V Nanowire Gate-All-Around FETs on Silicon

Persson, Anton E. O.; Zhu, Zhongyunshen; Athle, Robin; Wernersson, Lars-Erik

Published in: **IEEE Electron Device Letters**

10.1109/LED.2022.3171597

2022

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA):

Persson, A. E. O., Zhu, Z., Athle, R., & Wernersson, L.-E. (2022). Integration of Ferroelectric HfxZr1-xO2 on Vertical III-V Nanowire Gate-All-Around FETs on Silicon. *IEEE Electron Device Letters*, *43*(6), 854 - 857. https://doi.org/10.1109/LED.2022.3171597

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply: Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights

- Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

# Integration of ferroelectric Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub> on Vertical III-V Nanowire Gate-all-around FETs on Silicon

Anton E. O. Persson, Zhongyunshen Zhu, Robin Athle, and Lars-Erik Wernersson

Abstract—We demonstrate a successful process scheme for the integration of a CMOS-compatible ferroelectric gate stack on a scaled vertical InAs nanowire gate-all-around MOSFET on silicon. The devices show promising device characteristics with nanosecond write time and large memory window of >1.5 V. In the current implementation, the device performance is mainly limited by access resistance, which is attributed to the thermal sensitivity of InAs. The findings indicate that the ferroelectricity is not intrinsically preventing future improvements of scaled III-V FeFETs.

Index Terms—Ferroelectrics, Ferroelectric field effect transistor (FeFET), gate-all-around MOSFET, hafnium zirconium oxide, InAs, vertical nanowire.

#### I. INTRODUCTION

ERROELECTRIC MOSFETs (FeFETs) have been extensively studied on Si and Ge platforms and show great promise especially for non-volatile memories and neuromorphic applications [1], but are also expected to be used in highfrequency applications [2]. The integration of ferroelectric high-κ in the gate stack introduces new functionalities but does not otherwise change the technology's advantages and drawbacks regarding scalability and performance. III-V materials are promising candidates to complement Si and to extend Moore's law thanks to their exceptional electron transport properties [3] that have enabled performance improvement in transconductance [4] and low-power applications [5]. However, contrary to the Si and Ge platforms where high-temperature annealing often is used for dopant activation or high-k defect reduction, the thermal budget of III–Vs is stricter [6][7]. It is important to explore strategies for the implementation of HfO2-based ferroelectric gate-stacks also on the III-V technology platform as the technology is not directly transferable due to the annealing step.

Initial results indicate that it is possible to integrate ferroelectric high-κ on III-V using Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub> (HZO) that has

Manuscript submitted on April 1. This work was supported in part by the Swedish Research Council and in part by European Research Council

(Corresponding author: Anton Persson.)

Anton E. O. Persson, Zhongyunshen Zhu, and Lars-Erik Wernersson are with the Department of Electrical and Information Technology, Lund University, 221 00 Lund, Sweden. (e-mail:

anton.persson@eit.lth.se)

Robin Athle is with the Department of Electrical and Information Technology, Lund University, 221 00 Lund, Sweden, and also with NanoLund, Lund University, 221 00 Lund, Sweden

a low crystallization temperature [8]. However, those results were obtained on large planar capacitor structures [9] or micrometer scale planar transistors [10][11] and might therefore not be transferable to considerably more scaled dimensions or other geometries. In this work, we present a process flow for a scaled vertical InAs gate-all-around nanowire FeFET on silicon that demonstrates promising device characteristics. InAs is a suitable case material as it is both one of the most thermally sensitive III-V semiconductors[6] and used in high-performance MOSFETs[4]. The gate-all-around architecture enables the ultimate scaling for gate control [12] and important for FeFETs, vertical nanowires decouple contact- and channellength from the footprint. Since FeFETs transition from digital to analog (multibit) switching with increasing gate length [13], the vertical geometry enables analog switching even at scaled nodes. Vertical integration further supports future technology generations with 3D integration allowing higher integration densities.

### II. DEVICE FABRICATION

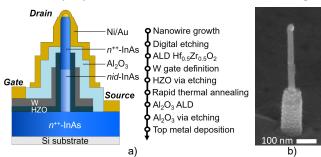

A schematic of the VNW-FeFET together with a summarized process flow is shown in Fig. 1a. Using Metalorganic Vapor Phase Epitaxy (MOVPE), a 300-nm-thick n<sup>++</sup>-InAs buffer layer was grown on a p-type Si(111) substrate. Gold seed particles were patterned using electron beam lithography (EBL), which were used to grow vertical InAs nanowires by Vapor-Liquid-Solid (VLS) growth in MOVPE at 570 °C. The transistor channel consists of 200-nm non-intentionally doped (nid) InAs followed by a 300-nm-long n<sup>++</sup>-drain InAs segment at the top. The core of the nanowire has a diameter of 30 nm and during the growth of the highly doped top segment, a 3-nm-thick highly doped shell overgrows the channel region.

The first step in the transistor fabrication was to thin the nanowire by cyclic ozone oxidation and HCl etching to

Fig. 1. (a) Schematic and process flow of the devices and (b) SEM micrograph of the structure after the rapid thermal annealing step.

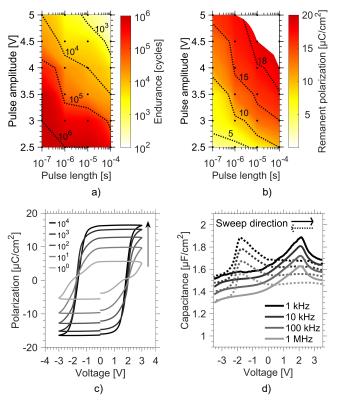

Fig. 2. Measurements performed on planar capacitors identical to the gate structure but without the nanowire. (a) Endurance as a function of voltage and pulse time. (b) Remanent polarization after 1000 cycles of wake up as a function of voltage and pulse time. The white upper right corner indicates a hard breakdown before 1000 wake-up cycles. (c) PE curve after wake up applying 5 V with 100 ns pulses from 1 to 10<sup>4</sup> cycles. (d) Capacitance voltage characteristics.

remove the highly doped shell at the channel region. After the desired channel thickness was achieved, 12 nm HZO was deposited at 200 °C using a thermal Atomic Layer Deposition (ALD) reactor with a 1:1 alternation between the precursors TDMAHf and TEMAZr using water as the oxygen source. A 50 nm W gate metal was sputtered and patterned using UVlithography S1813 masks and reactive ion etch (RIE). Vias through the HZO were BOE etched using S1813 masks. The sample was annealed at 550 °C for 30 s in N2 atmosphere in a rapid thermal anneal (RTA) to crystallize the HZO into the ferroelectric orthorhombic phase. In Fig. 1b, a SEM micrograph shows the structure at this stage. 30 nm of ALD grown Al<sub>2</sub>O<sub>3</sub> was subsequently deposited as a top spacer and vias were once again patterned by S1813 masks and BOE wet etching. The device was finally contacted by sputtering 10 nm Ni and 200 nm Au that was patterned using S1813 and wet etched by Au and Ni etchants.

## III. ELECTRICAL CHARACTERIZATION

Electrical characterization was performed in a MPI TS2000-SE probe station using a Keysight B1500A Parameter Analyzer. To enable pulsed measurements, a B1530A waveform generator module was used and for current-voltage measurements, high-resolution SMUs coupled with E5288A Atto-sense units were used. Capacitance-voltage measurements were performed in a Lake Shore CRX-4K

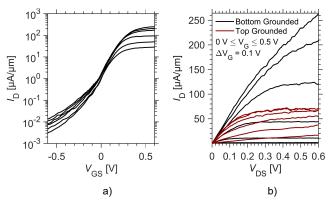

Fig. 3. (a) Transfer characteristic of bottom grounded transistor before pulsing showing  $V_{DS}$ =100-500 mV in steps of 100 mV and  $V_{DS}$ =50 mV. (b) Output characteristic of the same transistor before pulsing showing  $V_{GS}$ =0-500 mV in steps of 100 mV. Black indicates bottom grounded and red top grounded.

cryogenic probe station using an Agilent 4294A Impedance Analyzer.

Initially, on-chip MOS devices identical to the transistor gate structure but without the nanowire were investigated using square pulses with pulse lengths and amplitudes as described in Fig. 2a-b. The data follow the reported trends from Si- and metal-technologies, i.e., degraded endurance and higher polarization for longer pulses with high voltage [14]. All pulsing conditions generate some wake-up of the film compared to only applying the read-out PUND sequence. In Fig. 2c, the evolution of the ferroelectric hysteresis loop for 5V, 100 ns wake up pulses shows a remanent polarization of 17  $\mu$ C/cm<sup>2</sup> after 10<sup>4</sup> wake up cycles with a coercive voltage of ~1.7 V. The CV-curves in Fig. 2d show the two peaks that are characteristic of ferroelectricity. The frequency dispersion in accumulation at room temperature is ~3.9%/dec, which is slightly lower than reported values for ferroelectric TiN/HZO/InAs capacitors [15].

In Fig. 3a, the DC transfer characteristics of the initial state before any polarization switching are shown for a transistor with a channel length of 200 nm and diameter of 25 nm. The transistor has an on-current of 230  $\mu A/\mu m$  at  $V_{GS}$ =0.5 V and  $V_{DS} = 500$  mV, with peak  $g_m = 0.9$  mS/ $\mu$ m. In addition, its subthreshold characteristics including slope (113 mV/dec) and off-state (10 nA/µm) are in line with state-of-the-art gate-first VNW InAs transistors [16][17]. The change in subthreshold swing at negative bias conditions is attributed to a U-shaped trap density with a minimum around the threshold voltage[18]. The output characteristics in Fig. 3b are strongly asymmetric with higher on-state current when the bottom substrate is grounded compared to the top grounded case, which we attribute to a large top contact resistance. [19] As the selected annealing temperature is close to the growth temperature of the nanowires, it is assumed that the RTA is causing the degradation of the top contact as it, contrary to the bottom contact, is not encapsulated by HZO during the annealing. Previous studies indicate a high quality HZO/InAs-interface after annealing at elevated temperatures [15] whereas similar on-state degradation has been seen in RTA studies of VNW III-V MOSFETs already at lower temperatures of 350°C [20].

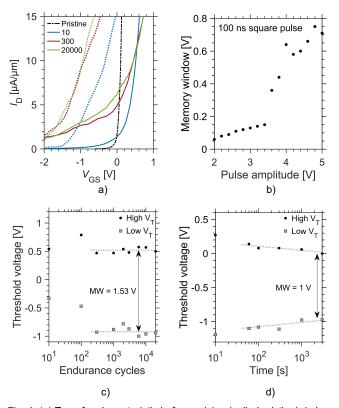

In the bottom grounded transistor in Fig. 4a, the typical transfer characteristic demonstrating a ferroelectric hysteresis is observed for 5V, 100-ns-square-pulses. Although having lower currents and degraded gate control, a top grounded transistor is apparently having the same memory window as in the bottom grounded case. The required write voltages are further tested in Fig. 4b where the gradual increase in memory window above 3.6V is an indication of partial domain switching, i.e., more than one domain contributes to the ferroelectric properties. The analog rather than digital switching behavior is in line with the properties of similarly sized planar Si-transistors[21]. It is assumed that domains switching on the planar InAs are not contributing to the characteristics due to the high doping and the 300 nm thickness of the buffer layer. The required pulse amplitude for ferroelectric switching at this time scale is in line with planar MIM devices,[22] however, comparing this to a similarly scaled state-of-the-art SiGe VNW-FeFET [23], this InAs FeFET has less than half the write voltage which partly can be explained by the intentional choice of not using an interfacial layer. Fig. 4c shows an endurance of the device of >20000 polarization switches followed by an abrupt HZO breakdown. As seen in Fig. 4a, both the off-state and on-state deteriorates with pulsing, which we attribute to defect generation in the HZO during the ferroelectric switching[24]. To evaluate the

Fig. 4. (a) Transfer characteristic before pulsing (called pristine), in low V<sub>T</sub>-state (dotted), and high V<sub>T</sub>-state (solid) as a function of wake-up cycles of 5V, 100 ns square pulses. (b) Memory window as a function of pulse amplitude for 100 ns square pulses. (c) Memory window as a function of endurance cycling. Dotted lines serve as guides to the eye. (d) Memory window as a function of retention time. Dotted lines serve as guides to the eye.

potential endurance of these III-V VNW-FeFETs, we in this case define the memory window at 10  $\mu$ A/ $\mu$ m when DC sweeping  $V_{GS}$  from +1 V to -2 V having  $V_{DS} = 0.5$  V. The memory window increases with wake-up and reaches >1.5V with rather stable threshold voltages for both the write and erase pulses after the initial wake-up. As the breakdown occurs at a similar endurance as for the capacitors in Fig. 2a, the properties are not deteriorated by the nanowire transistor channel. Adding a spacer between gate and substrate would shrink the area by five orders of magnitude and as the endurance to hard breakdown is strongly area dependent [25], it is expected that the endurance will increase considerably with this addition. In Fig. 4d, the retention on another device is measured at room temperature by defining the memory window at 1  $\mu$ A/ $\mu$ m when DC sweeping  $V_{GS}$  from +1 V to -2 V keeping  $V_{DS} = 0.5$  V. Given the defect concentrations indicated by the deteriorated off-state of the devices after switching, charge trapping is expected to be the dominating factor for the shrinkage of the memory window rather than depolarization fields.

To summarize, the performance of these FeFETs is mainly limited by the top-contact resistance and the amount of defects in the high-κ after polarization switching. This is similar to the early reports on VNW III-V MOSFETs [26] and we expect that similar implementations of gate-last processing, interfacial high-κ-layers, less temperature sensitive III-V materials, and especially decreased annealing temperatures will improve the properties also for VNW III-V FeFETs. Based on our findings, we anticipate future VNW III-V FeFET applications to be in line with III-V MOSFETs. RF- and mmwave applications are prime candidates provided the high oncurrents and lower voltage overdrive compared to Si. Exchanging InAs for more advanced heterostructures within the transistor channel with wider bandgaps (e.g., InGaAs) should decrease off-state current leakage[4] and thereby enable memory applications, whereas the inclusion of e.g. might enable ferroelectric tunnel FETs reconfigurable sub-60 mv/dec transistors.

#### IV. CONCLUSION

In this letter, we have successfully demonstrated a process flow for a scaled vertical III-V nanowire gate-all-around FeFET on silicon and show good performance also when using a thermally sensitive material like InAs. We conclude from this proof-of-concept device's performance that it is limited by effects introduced during the annealing step. These issues are thought to be resolvable and thus these results indicate the suitability of ferroelectric high-κ integration on the VNW III–V technology platform, especially for future applications in the RF- and mm-wave domain.

#### **V.REFERENCES**

- A. I. Khan, A. Keshavarzi, and S. Datta, "The future of ferroelectric field-effect transistor technology," *Nature Electronics*, vol. 3, no. 10, pp. 588-597, Oct. 2020, DOI: 10.1038/s41928-020-00492-7.

- [2] H. Mulaosmanovic, E. T. Breyer, T. Mikolajick, and S. Slesazeck, "Reconfigurable frequency multiplication with a ferroelectric transistor," *Nature Electronics*, vol. 3, no. 7, pp. 391-397, May 2020, DOI: 10.1038/s41928-020-0413-0.

- [3] J. A. Del Alamo, "Nanometre-scale electronics with III--V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317-323, Nov. 2011, DOI: 10.1038/nature10677.

- [4] O.-P. Kilpi, J. Svensson, E. Lind, and L.-E. Wernersson, "Electrical Properties of Vertical InAs/InGaAs Heterostructure MOSFETs," *IEEE Journal of the Electron Devices Society*, vol. 7, pp. 70-75, Oct. 2018, DOI: 10.1109/JEDS.2018.2878659.

- [5] E. Memisevic, J. Svensson, E. Lind and L.-E. Wernersson, "InAs/InGaAsSb/GaSb Nanowire Tunnel Field-Effect Transistors," *IEEE Transactions on Electron Devices*, vol. 64, no. 11, pp. 4746-4751, Sep. 2017, DOI: 10.1109/TED.2017.2750763.

- [6] N. Kobayashi and Y. Kobayashi, "As and P Desorption from III-V Semiconductor Surface in Metalorganic Chemical Vapor Deposition Studied by Surface Photo-Absorption," *Japanese Journal of Applied Physics*, Aug. 1991, DOI: 10.1143/jjap.30.11699.

[7] H. Yamaguchi and Y. Horikoshi, "As desorption from GaAs and InAs

- [7] H. Yamaguchi and Y. Horikoshi, "As desorption from GaAs and InAs surfaces studied by improved high-energy electron reflectivity measurements," *Applied Surface Science*, vol. 60, pp. 224-227, Dec. 1992, DOI: 10.1016/0169-4332(92)90420-3.

- [8] T. Onaya, T. Nabatame, N. Sawamoto, A. Ohi, N. Ikeda, T. Nagata and A. Ogura, "Ferroelectricity of Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub> thin films fabricated by 300 °C low temperature process with plasma-enhanced atomic layer deposition," *Microelectronic Engineering*, vol. 215, pp. 1-5, May 2019, DOI: 10.1016/j.mee.2019.111013.

- [9] A. E. O. Persson, R. Athle, P. Littow, K.-M. Persson, J. Svensson, M. Borg and L.-E. Wernersson, "Reduced annealing temperature for ferroelectric HZO on InAs with enhanced polarization," *Applied Physics Letters*, vol. 116, no. 062902, pp. 1-4, Feb. 2020, DOI: 10.1063/1.5141403.

- [10] Q. H. Luc, C. C. Fan-Chiang, S. H. Huynh, P. Huang, H. B. Do, M. T. H. Ha, Y. D. Jin, T. A. Nguyen, K. Y. Zhang, H. C. Wang, Y. K. Lin, Y. C. Lin, C. Hu, H. Iwai and E. Y. Chang, "First Experimental Demonstration of Negative Capacitance InGaAs MOSFETs," 2018 Symposium on VLSI Technology Digest of Technical Papers, pp. 47-48, Jun. 2018, DOI: 10.1109/VLSIT.2018.8510644.

- [11] C. Wu, H. Ye, N. Shaju, J. Smith, B. Grisafe, S. Datta and P. Fay, "Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>-Based Ferroelectric Gate HEMTs With Large Threshold Voltage Tuning Range," *IEEE Electron Device Letters*, vol. 41, no. 3, pp. 337-340, Jan. 2020, DOI: 10.1109/LED.2020.2965330.

- [12] E. Lind, "High frequency III-V nanowire MOSFETs," Semiconductor Science and Technology, vol. 31, no. 9, p. 1-13, Aug. 2016, DOI: 10.1088/0268-1242/31/9/093005.

- [13] F. Müller, M. Lederer, R. Olivo, T. Ali, R. Hoffmann, H. Mulaosmanovic, S. Beyer, S. Dünkel, J. Müller, S. Müller, K. Seidel and G. Gerlach, "Current percolation path impacting switching behavior of ferroelectric FETs," 2021 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Apr. 2021, pp. 1-2, DOI: 10.1109/VLSI-TSA51926.2021.9440081.

- [14] K. Tahara, K. Toprasertpong, Y. Hikosaka, K. Nakamura, H. Saito, M. Takenaka, and S. Takagi, "Strategy toward HZO BEOL-FeRAM with low-voltage operation (≤ 1.2 V), low process temperature, and high endurance by thickness scaling," presented at the Symp. VLSI Technol. Kyoto, Jpn., vol. 17, Jun. 2021.

- [15] A. E. O. Persson, R. Athle, J. Svensson, M. Borg and L.-E. Wernersson, "A method for estimating defects in ferroelectric thin film MOSCAPs," *Applied Physics Letters*, vol. 117, no. 242902, pp. 1-5, Dec. 2020, DOI: 10.1063/5.0029210.

- [16] K.-M. Persson, M. Berg, M. B. Borg, J. Wu, S. Johansson, S. Johannes, K. Jansson, E. Lind and L.-E. Wernersson, "Extrinsic and intrinsic performance of vertical InAs nanowire MOSFETs on Si substrates," *IEEE Transactions on Electron Devices*, vol. 60, no. 9, pp. 2761-2767, Sep. 2013, DOI: 10.1109/TED.2013.2272324.

- [17] K. Tomioka, F. Izhizaka and T. Fukui, "Selective-Area Growth of InAs Nanowires on Ge and Vertical Transistor Application," *Nano Letters*, vol. 15, no. 11, pp. 7253-7257, Oct. 2015, DOI: 10.1021/acs.nanolett.5b02165.

- [18] M. Hellenbrand, O.-P. Kilpi, J. Svensson, E. Lind and L.-E. Wernersson, "Low-frequency noise in nanowire and planar III-V MOSFETs," *Microelectronic Engineering*, vol. 215, no. 8, pp. 1-5, May. 2019, DOI: 10.1016/j.mee.2019.110986.

- [19] X. Zhao, C. Heidelberger, E. A. Fitzgerald and J. A. del Alamo, "Source/Drain Asymmetry in InGaAs Vertical Nanowire MOSFETs," *IEEE Transactions on Electron Devices*, vol. 64, no. 5, pp. 2161-2165, Apr. 2017, DOI: 10.1109/TED.2017.2684707.

- [20] Z. Zhu, J. Svensson, A. Jönsson and L.-E. Wernersson, "Performance enhancement of GaSb vertical nanowire p-type MOSFETs on Si by rapid thermal annealing," *Nanotechnology*, vol. 33, no. 7, pp. 1-10, Nov. 2021, DOI: 10.1088/1361-6528/ac3689.

- [21] F. Müller, M. Lederer, R. Olivo, T. Ali, R. Hoffmann, H. Mulaosmanovic, S. Beyer, S. Dünkel, J. Müller, S. Müller, K. Seidel and G. Gerlach, "Current percolation path impacting switching behavior of ferroelectric FETs," 2021 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Apr. 2021, pp. 1-2, DOI: 10.1109/VLSI-TSA51926.2021.9440081.

- [22] X. Lyu, M. Si, P. R. Shrestha, K. P. Cheung and P. D. Ye, "First Direct Measurement of Sub-Nanosecond Polarization Switching in Ferroelectric Hafnium Zirconium Oxide," 2019 IEEE International Electron Devices Meeting (IEDM), 2019, pp. 15.2.1-15.2.4, DOI: 10.1109/IEDM19573.2019.8993509.

- [23] W. Huang, H. Zhu, Y. Zhang, X. Yin, X. Ai, J. Li, C. Li, Y. Li, L. Xie, Y. Liu, J. Xiang, K. Jia, J. Li and T. C. Ye, "Ferroelectric Vertical Gate-All-Around Field-Effect-Transistors With High Speed, High Density, and Large Memory Window," *IEEE Electron Device Letters*, vol. 43, no. 1, pp. 25-28, Nov. 2021, DOI: 10.1109/LED.2021.3126771.

- [24] M. Pesic, F. P. G. Fengler, S. Slesazeck, U. Schroeder, T. Mikolajick, L. Larcher and A. Padovani, "Root cause of degradation in novel HfO<sub>2</sub>-based ferroelectric memories," 2016 IEEE International Reliability Physics Symposium (IRPS), 2016, pp. MY-3-1-MY-3-5, DOI: 10.1109/IRPS.2016.7574619.

- [25] T. Francois, L. Grenouillet, J. Coignus, N. Vaxelaire, C. Carabasse, F. Aussenac, S. Chevalliez, S. Slesazeck, C. Richter, P. Chiquet, M. Bocquet, U. Schroeder, T. Mikolajick, F. Gaillard and E. Nowak, "Impact of area scaling on the ferroelectric properties of back-end of line compatible Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> and Si:HfO<sub>2</sub>-based MFM capacitors," *Applied Physics Letters*, vol. 118, no. 6, p. 1-5, Feb. 2021, DOI: 10.1063/5.0035650.

- [26] H. Riel, L.-E. Wernersson, M. Hong and J. A. Del Alamo, "III-V compound semiconductor transistors—from planar to nanowire structures," MRS Bulletin, vol. 39, no. 8, pp. 668-677, Aug. 2014, DOI: 10.1557/mrs.2014.137.