Persson, Anton E. O.

2023

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Persson, A. E. O. (2023). Integration of Ferroelectric HfO\_onto a III-V Nanowire Platform. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**Doctoral Thesis**

Anton E. O. Persson

Department of Electrical and Information Technology Lund, April 2023

Academic thesis for the degree of Doctor of Philosophy, which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, 12 May, 2023, at 9:15 a.m. in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers Väg 3, 223 63 Lund, Sweden. The thesis will be defended in English.

| Organization: LUND UNIVERSITY Department of Electrical and Information Technology Ole Römers Väg 3 223 63 Lund Sweden | Document Type:<br>DOCTORAL THESIS                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

|                                                                                                                       | Date of Issue:<br>April 2023                                                                            |  |

|                                                                                                                       | Sponsoring Organization(s):                                                                             |  |

| Author:<br>Anton E. O. Persson                                                                                        | Swedish Foundation for Strategic Research (SSF)<br>Swedish Research Council (VR)<br>European Union (EU) |  |

| Title:                                                                                                                | anatuira Platform                                                                                       |  |

The discovery of ferroelectricity in CMOS-compatible oxides, such as doped hafnium oxide, has opened new paths for electronics by a resurgence for ferroelectric implementations on modern technology platforms. This thesis presents the ground-up integration of ferroelectric HfO2 on a thermally sensitive III-V nanowire platform leading to the successful implementation of ferroelectric transistors (FeFETs), tunnel junctions (FTJs), and varactors for mm-wave applications. As ferroelectric HfO2 on III-V semiconductors is a nascent technology, a special emphasis is put on the fundamental integration issues and the various engineering challenges facing the technology.

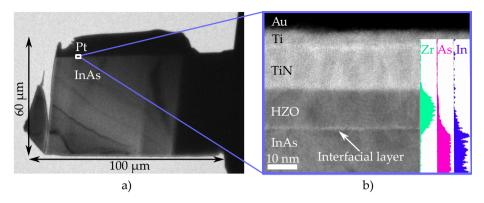

The fabrication of metal-oxide-semiconductor (MOS) capacitors is treated as well as the measurement methods developed to investigate the interfacial quality to the narrow bandgap III-V materials using both electrical and in-operando synchrotron light source techniques. After optimization of both the films and the top electrode, the gate stack is integrated onto vertical InAs nanowires on Si in order to successfully implement FeFETs. Their performance and reliability can be explained from the deeper physical understanding obtained from the capacitor structures.

By introducing an InAs/(In)GaAsSb/GaSb heterostructure in the nanowire, a ferroelectric tunnel field effect transistor (ferro-TFET) is fabricated. Based on the ultra-short effective channel created by the band-to-band tunneling process, the localized potential variations induced by single ultra-scaled ferroelectric domains and individual defects are sensed and investigated. By intentionally introducing a gate-source overlap in the ferro-TFET, a non-volatile reconfigurable singletransistor solution for modulating an input signal with diverse modes including signal transmission, phase shift, frequency doubling, and mixing is implemented.

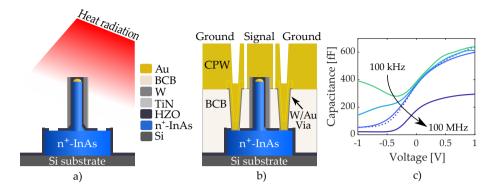

Finally, by fabricating scaled ferroelectric MOS capacitors in the front-end with a dedicated and adopted RF and mm-wave backend-of-line (BEOL) implementation, the ferroelectric behavior is captured at RF and mm-wave frequencies.

#### Keywords:

Ferroelectricity, FeFET, FTJ, TFET, HZO, III-V, Nanowire.

| Language:<br>English  ISBN (printed): 978-91-8039-673-8                                                  |  |

|----------------------------------------------------------------------------------------------------------|--|

| ISBN (printed):<br>978-91-8039-673-8                                                                     |  |

| 978-91-8039-673-8                                                                                        |  |

| 978-91-8039-673-8                                                                                        |  |

|                                                                                                          |  |

| 70777 (11 11 1)                                                                                          |  |

| TOP2 7 (11 1: 1)                                                                                         |  |

| ISBN (digital):                                                                                          |  |

| .56 978-91-8039-674-5                                                                                    |  |

|                                                                                                          |  |

| of Pages: Price:                                                                                         |  |

|                                                                                                          |  |

| Classification:                                                                                          |  |

| Unclassified                                                                                             |  |

| Series of Licentiate and Doctoral Theses; 1654-790X, No. 156  Recipient's Notes:    Number of Pages: 240 |  |

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature: Inton Person Date: 17 April 2023

**Doctoral Thesis**

Anton E. O. Persson

Department of Electrical and Information Technology Lund, April 2023 Anton E. O. Persson Department of Electrical and Information Technology Lund University Ole Römers Väg 3, 223 63 Lund, Sweden

Series of Licentiate and Doctoral Theses ISSN 1654-790X, No. 156 ISBN 978-91-8039-673-8 (printed) ISBN 978-91-8039-674-5 (digital)

© 2023 Anton E. O. Persson This thesis is typeset using LATEX  $2_{\epsilon}$ .

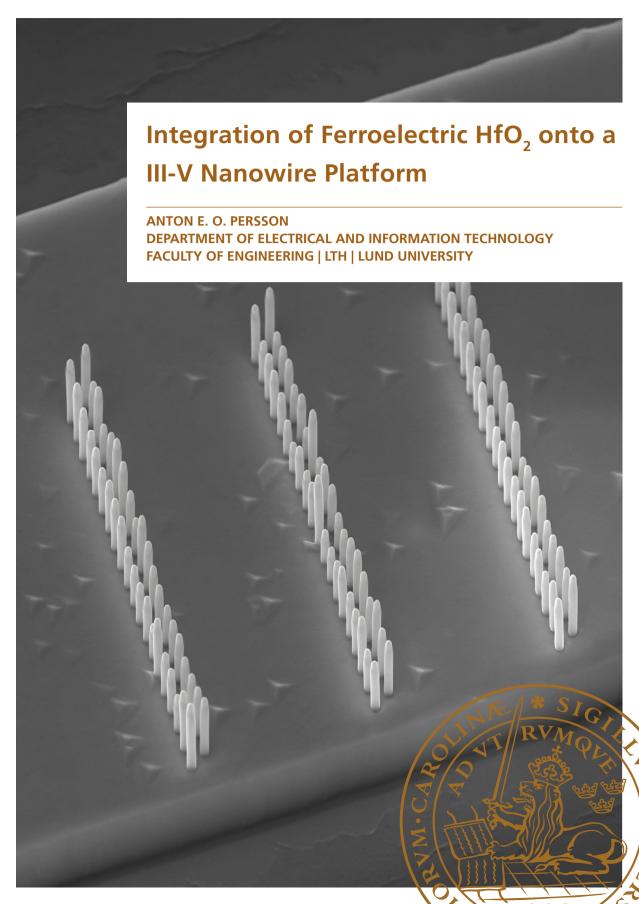

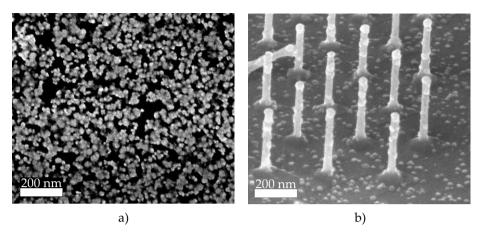

Frontispiece: Scanning electron microscopy image of an InAs mesa on silicon with InAs nanowire arrays covered by a ferroelectric zirconium-doped hafnium oxide and tungsten.

Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

## **Abstract**

HE discovery of ferroelectricity in CMOS-compatible oxides, such as doped hafnium oxide, has opened new possibilities for electronics by reviving the use of ferroelectric implementations on modern technology platforms. This thesis presents the ground-up integration of ferroelectric HfO<sub>2</sub> on a thermally sensitive III-V nanowire platform leading to the successful implementation of ferroelectric transistors (FeFETs), tunnel junctions (FTJs), and varactors for mm-wave applications. As ferroelectric HfO<sub>2</sub> on III-V semiconductors is a nascent technology, a special emphasis is put on the fundamental integration issues and the various engineering challenges facing the technology.

The fabrication of metal-oxide-semiconductor (MOS) capacitors is treated as well as the measurement methods developed to investigate the interfacial quality to the narrow bandgap III-V materials using both electrical and operando synchrotron light source techniques. After optimizing both the films and the top electrode, the gate stack is integrated onto vertical InAs nanowires on Si in order to successfully implement FeFETs. Their performance and reliability can be explained from the deeper physical understanding obtained from the capacitor structures.

By introducing an InAs/(In)GaAsSb/GaSb heterostructure in the nanowire, a ferroelectric tunnel field effect transistor (ferro-TFET) is fabricated. Based on the ultra-short effective channel created by the band-to-band tunneling process, the localized potential variations induced by single ultra-scaled ferroelectric domains and individual defects are sensed and investigated. By intentionally introducing a gate-source overlap in the ferro-TFET, a non-volatile

reconfigurable single-transistor solution for modulating an input signal with diverse modes including signal transmission, phase shift, frequency doubling, and mixing is implemented.

Finally, by fabricating scaled ferroelectric MOS capacitors in the front-end with a dedicated and adopted RF and mm-wave backend-of-line (BEOL) implementation, the ferroelectric behavior is captured at RF and mm-wave frequencies.

## Populärvetenskaplig sammanfattning

ofta för den tredje industriella revolutionen i analogi till den första (ångmaskinen) och den andra industriella revolutionen (elektrifieringen och förbränningsmotorn). Oavsett om digitaliseringen ska tillskrivas samma vikt som ångmaskinen och elektrifieringen, så råder det ingen tvekan om att elektronikutvecklingen har haft och kommer att ha en stor påverkan på vårt samhälle. Nu börjar det talas om en fjärde industriell revolution som kännetecknas av en fusion av teknologier som suddar ut gränserna mellan de traditionellt digitala och biologiska sfärerna.

När man blickar framåt så börjar den tekniska forskningen tala om kvantdatorer, sakernas internet och elektriska kretsar som efterliknar den mänskliga hjärnan. En anledning till detta är att elektronikindustrin under flera decennier har förlitat sig på att beräkningskraft och effektivitet förbättras genom att minska kiseltransistorers storlek (den så kallade Moores lag). På grund av kostnaden för fortsatt nedskalning och kvantmekaniska effekter som orsakar problem vid dessa storleksordningar så har denna utveckling saktat in. Utvecklingen av elektronik rör sig därför in på okänt territorium, vilket kräver nya material, komponenter och kretsarkitekturer. Denna tes berör dessa frågeställningar och undersöker möjligheterna att kombinera så kallade ferroelektriska material med III-V material för att möjliggöra nya komponenter och kretsarkitekturer.

Ett ferroelektriskt material är en elektrisk motsvarighet till de ferromagnetiska material som bildar det vi i vardagligt tal kallar för magneter. Men i stället för en magnetisk nordpol respektive sydpol, så bildas istället elektriska

poler med en positiv respektive negativ laddning på var sin sida av materialet. Dessa attraherar och repellerar negativ respektive positiv laddning i omkringliggande material. Precis som när nordpolen och sydpolen byter plats på en magnet genom ett pålagt magnetfält (såsom i datorhårddiskar) så kan ett ferroelektrisk materials positiva och negativa sida byta plats genom en pålagd spänning. I analogi med hårddiskars ferromagnetiska minnen så kan man därigenom skapa ferroelektriska minnen. III-V material är liksom kisel halvledare och fyller en kompletterande roll inom elektroniken då de har vissa avgörande egenskaper som gör dem väl lämpade till högfrekvenselektronik samt i lågeffektselektronik för mycket energieffektiva applikationer.

I denna tes undersöks nya ferroelektriska minnen, i form av ferroelektriska transistorer och ferroelektriska tunnlingsbarriärer, för nya kretsarkitekturer. Dels undersöks deras funktion såsom memristorer, d.v.s. resistorer vars resistans kan ändras och sedan "minnas" av komponenten, och dels i form av en rekonfigurerbar komponent för högfrekvenselektronik. Målet är att kunna åstadkomma så kallade neuromorfa kretsar, d.v.s. kretsar anpassade för artificiell intelligens genom att de i sin uppbyggnad efterliknar den mänskliga hjärnan med synapser (memristorer) och neuroner.

## Acknowledgments

URING the years leading up to this thesis, I have had the opportunity to work with a lot of great and inspiring people. First and foremost, thank you *Lars-Erik Wernersson* for offering me this journey. Without your expertise and inspiring discussions, I would never have reached the end of it. I also want to thank my second supervisor *Mattias Borg* who always had the door open and answered my barrage of questions.

A great thank you to *Robin Athle* who were the first to join me on this ferroelectric endeavor and who more than anyone has listen to my problems. *André Andersen, Hannes Dahlberg,* and *Zhongyunshen Zhu* may have joined the endeavor later, but your contributions to ferroelectricity in Lund are equally important! A big thank you to *Erik Lind* to whom I often went with my trickiest questions and to my surprise often answered them. A big thank you to *Johannes Svensson, Olli-Pekka Kilpi,* and *Karl-Magnus Persson* to whom I owe most of my cleanroom skills! And to *Lars Ohlsson Fhager* who has spent more hours than I want to admit teaching me how to perform proper electrical measurements. Thank you, *Saketh Ram Mamidala* for the early days of my PhD when you stayed happy even at midnight in the lab!

The group is big and writing memories for all of you would go beyond the scope of this thesis. But I would like to thank all of my colleagues for these years. Not only have we spent countless hours in the lab and office together, but we have also become good friends and enjoyed many non-work activities together. To the remaining co-workers *Andrea*, *Stefan*, *Markus*, *Gautham*, *Adam*, *Marcus*, *Anette*, *Abinaya*, *Lasse*, *Heera*, *Fredrik*, *Navya*, *Philipp*, *Duc*, *Patrik*, *Louise*, *Sebastian*, *Pramoda*, *Tobias*, *Ben*, *Niklas*, *Alexandros*, *Johan*, *Daniel*, and *Mats*: a big thank you for this time! I have also had great collaborations with people outside of my own department who have taught me about synchrotron measurements. *Austin*, *Rainer*, *Yen-Po*, *Zhihua*, *Sandra*, and *Anders*, thank you!

I have had many teachers inspiring me throughout the years and even if all of you should be acknowledged, a special thank you goes to *Eva*, *Nedzad*, *Per*, *Bengt-Olof*, and *Jonas* who made physics, chemistry, and mathematics my favorite topics in school! I would also like thank the professors of Chalmers who built my basis in physics and the professors of TU Munich who inspired me into choosing a path towards semiconductor devices. A big thank you to *Eva Olsson* to whom I owe my choice of an academic career. Without you believing in me, I would never have discovered academia!

I would also like to thank *Martin*, *Martin*, and *Antti* for being great and loyal floorball players.

My grandfathers *Erkki* and late *Olle* who during my early days showed me their workshops and made me want to become an inventor. A special thanks goes to *Clara*, for all your love and care, even in the most stressful moments. And my parents *Arne* and *Marja* who have been my biggest cheerleaders throughout the years. You deserve the biggest thanks!

Lund, April 2023

Anton Persson

## Contents

| Abstract                           | iii  |

|------------------------------------|------|

| Populärvetenskaplig sammanfattning | v    |

| Acknowledgments                    | vii  |

| Contents                           | ix   |

| Preface                            | xiii |

| Structure of the Thesis            | xiii |

| Included Papers                    | xiv  |

| Related Work                       | xvi  |

| Acronyms and Symbols               | xvii |

| Acronyms and Abbreviations         | xvii |

| Latin Symbols                      |      |

| Greek Symbols                      | xx   |

| INTRODUCTION                       | 1    |

| 1 Background                       | 3    |

| 1.1 The Future of Electronics      | 5    |

| 1.1.1 III-V Nanowires              | 5    |

| 1.1.2 Unconventional Transistors   | 6    |

| 1.1.3 Neuromorphics                | 8    |

| 2 Ferroelectricity                                              | 11 |

|-----------------------------------------------------------------|----|

| 2.1 A Simple Ferroelectric Model                                | 11 |

| 2.1.1 Antiferroelectricity                                      | 14 |

| 2.2 Ferroelectricity in Electronics                             | 14 |

| 2.2.1 Memory Devices                                            | 15 |

| 2.2.2 High-frequency Electronics                                | 19 |

| 2.3 Ferroelectricity in Hafnium Oxide                           | 22 |

| 2.3.1 Material Characteristics of Ferroelectric Hafnium Oxide . | 22 |

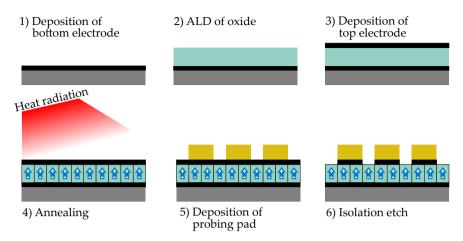

| 3 Fabrication of Ferroelectric Devices                          | 27 |

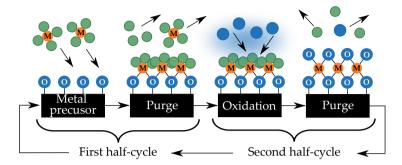

| 3.1 Atomic Layer Deposition                                     | 27 |

| 3.2 Thermal Processing                                          | 29 |

| 3.3 Planar Structures                                           | 30 |

| 3.3.1 MIMCAP                                                    | 31 |

| 3.3.2 MOSCAP                                                    | 32 |

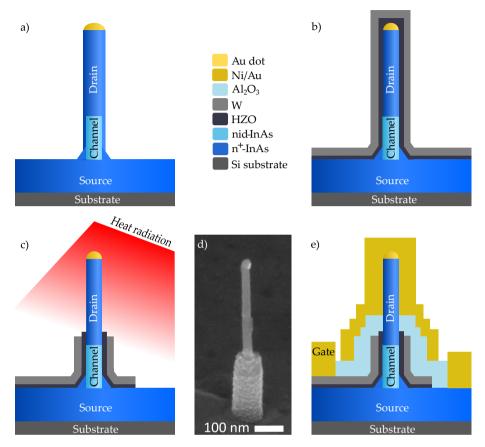

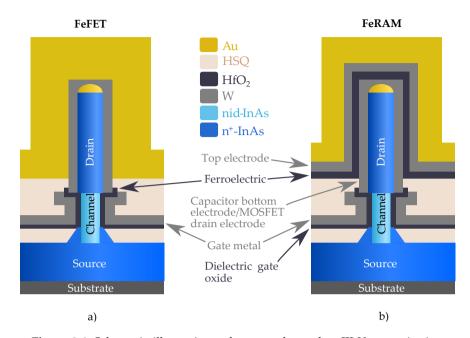

| 3.4 Vertical Transistor Integration                             | 34 |

| 3.4.1 Vertical Ferroelectric FET                                | 34 |

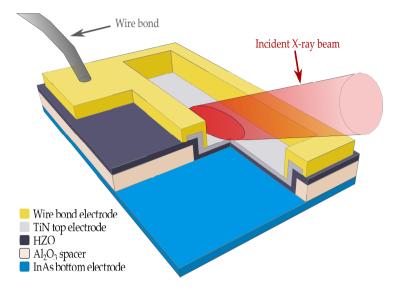

| 3.5 mm-wave Integration                                         | 38 |

| 4 Microstructural Analysis                                      | 43 |

| 4.1 Electron Microscopy                                         | 43 |

| 4.1.1 Scanning Electron Microscopy                              | 44 |

| 4.1.2 Transmission Electron Microscopy                          | 45 |

| 4.2 Scanning Probe Microscopy                                   | 46 |

| 4.3 Optical Measurements                                        | 46 |

| 4.3.1 Interferometry and Ellipsometry                           | 46 |

| 4.3.2 Photoelectron Spectroscopy                                | 48 |

| 4.3.3 Diffractometry                                            | 49 |

| 5 Electrical Characterization                                   | 51 |

| 5.1 Capacitor Measurements                                      | 51 |

| 5.1.1 Polarization Measurements                                 | 51 |

| 5.1.2 Cycling Behavior                                          | 55 |

| 5.1.3 Switching Dynamics                                        | 57 |

| 5.1.4 Capacitance-Voltage                                       | 58 |

| 5.2 Transistor Measurements                                     | 63 |

| 5.2.1 Programmability                                                                                                                                        | 63<br>64              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 6 Summary and Outlook                                                                                                                                        | 67                    |

| Bibliography                                                                                                                                                 | 71                    |

| APPENDICES                                                                                                                                                   | 87                    |

| A Fabrication Details  A.1 Standardized MIMCAP                                                                                                               | <b>89</b><br>89<br>90 |

| PAPERS                                                                                                                                                       | 95                    |

| I Integration of ferroelectric $Hf_xZr_{1-x}O_2$ on Vertical III-V Nanowire Gate-all-around MOSFETs on Silicon                                               | 97                    |

| II A method for estimating defects in ferroelectric thin film MOSCAPs                                                                                        | 103                   |

| III Reduced annealing temperature for ferroelectric HZO on InAs with enhanced polarization                                                                   | 111                   |

| IV Millimeter-Wave Characterization of Ferroelectric MOS Capacitors                                                                                          | 117                   |

| V Top Electrode Engineering for Freedom in Design and Implementation of Ferroelectric Tunnel Junctions Based on $Hf_xZr_{1-x}O_2$                            | 123                   |

| VI As-deposited ferroelectric HZO on a III-V platform                                                                                                        | 133                   |

| VII Ferroelectric-Antiferroelectric Transition of $Hf_{1-x}Zr_xO_2$ on Indium Arsenide with Enhanced Ferroelectric Characteristics for $Hf_{0.2}Zr_{0.8}O_2$ | 141                   |

| VIII Effects of TiN Top Electrode Texturing on Ferroelectricity in $Hf_{1-x}Zr_xO_2$                                                                         | 151                   |

| IX Sensing single domains and individual defects in scaled ferroelectrics                                                                                    | 161                   |

| X Signal Modulation in a Ferroelectric Tunnel Field-Effect<br>Transistor           | 173 |

|------------------------------------------------------------------------------------|-----|

| XI Switching Dynamics and Interface Chemistry of Ferro-<br>electric Hafnia Devices | 199 |

### Preface

HIS thesis is the culmination of more than five years of work in the Electromagnetics and Nanoelectronics division at the Department of Electrical and Information Technology, Lund University, and investigates the functional integration of ferroelectric hafnium oxide onto III-V nanowires for various ferroelectric device implementations. The work was supervised by Professor Lars-Erik Wernersson and Associate Professor Mattias Borg.

#### STRUCTURE OF THE THESIS

This is a compilation thesis, meaning that it is a collection of research papers with an introductory section providing a summary of the research field comprehensible for aspiring researchers with a M.Sc. degree interested in pursuing similar research. The appended publications form the main body of the thesis.

#### INTRODUCTION

The aim of the introduction is to provide a broader and more comprehensive view than the focused publications that are written for researchers in the field. That is, the textbook required for someone with a general physics and electronics background to be able to understand most of the content in the appended publications. I expect the reader to have a basic prior knowledge of semiconductors, electronic devices, and material characterization techniques.

#### PAPERS

The papers forming the main body of the thesis are reproduced in the back and listed in the following section.

#### **INCLUDED PAPERS**

The following papers form the main body of this thesis and the respective published or draft versions are appended in the back.

- **Paper I:** A. E. O. Persson, Z. Zhu, R. Athle, and L.-E. Wernersson, "Integration of ferroelectric  $Hf_xZr_{1-x}O_2$  on Vertical III-V Nanowire Gateall-around MOSFETs on Silicon", *IEEE Electron Device Letters*, vol. 43, pp. 854-857, May 2022, doi: 10.1109/LED.2022.3171597.

- ▶ I developed the process flow, fabricated the structures, carried out all measurements and analyses and wrote the paper.

- Paper II: A. E. O. Persson, R. Athle, J. Svensson, M. Borg, and L.-E. Wernersson, "A method for estimating defects in ferroelectric thin film MOSCAPs", *Applied Physics Letters*, vol. 117, pp. 242902, Dec 2020, doi: 10.1063/5.0029210.

- ▶ I developed the process flow, fabricated the structures, carried out all measurements and analyses and wrote the paper.

- Paper III: A. E. O. Persson, R. Athle, P. Littow, K.-M. Persson, J. Svensson, M. Borg, and L.-E. Wernersson, "Reduced annealing temperature for ferroelectric HZO on InAs with enhanced polarization", Applied Physics Letters, vol. 116, pp. 062902, Feb 2020, doi: 10.1063/1.5141403.

- ▶ I developed the process flow, fabricated the structures, carried out all measurements and analyses and wrote the paper.

- **Paper IV:** A. E. O. Persson, S. Andrić, and L.-E. Wernersson, "Millimeter-Wave Characterization of Ferroelectric MOS Capacitors", Manuscript in preparation.

- ▶ I fabricated the structures, helped measure the sample, analyzed parts of the results, and wrote the paper.

- **Paper V:** R. Athle, <u>A. E. O. Persson</u>, A. Troian, and M. Borg, "Top Electrode Engineering for Freedom in Design and Implementation of Ferroelectric Tunnel Junctions Based on  $Hf_xZr_{1-x}O_2$ ", *ACS Applied Electronic Materials*, vol. 4, pp. 1002-1009, Feb 2022, doi: 10.1021/acsaelm.1c01181.

- ▶ I helped develop the process flow, the measurement methods, the analyses, and the writing of the paper.

- Paper VI: A. Andersen, <u>A. E. O. Persson</u>, and L.-E. Wernersson, "Asdeposited ferroelectric HZO on a III-V platform", *Applied Physics Letters*, vol. 121, pp. 012901, Jul 2022, doi: 10.1063/5.0097462.

- ▶ I developed the process flow, and helped fabricate the structures, carry out the measurements, the analyses, and the writing of the paper.

- **Paper VII:** H. Dahlberg, <u>A. E. O. Persson</u>, R. Athle, and L.-E. Wernersson, "Ferroelectric-Antiferroelectric Transition of  $Hf_{1-x}Zr_xO_2$  on Indium Arsenide with Enhanced Ferroelectric Characteristics for  $Hf_{0.2}Zr_{0.8}O_2$ ", *ACS Applied Electronic Materials*, vol. 4, pp. 6357-6363, Dec 2022, doi: 10.1021/acsaelm.2c01483.

- ▶ I developed the process flow, and helped fabricate the structures, carry out the measurements, the analyses, and the writing of the paper.

- **Paper VIII:** R. Athle, <u>A. E. O. Persson</u>, A. Irish, H. Menon, R. Timm, and M. Borg, "Effects of TiN Top Electrode Texturing on Ferroelectricity in  $\mathrm{Hf}_{1-x}\mathrm{Zr}_x\mathrm{O}_2$ ", *Applied materials & interfaces*, vol. 13, pp. 11089-11095, Feb 2021, doi: 10.1021/acsami.1c01734.

- ▶ I helped develop the process flow, the measurement methods, the analyses, and the writing of the paper.

- **Paper IX:** Z. Zhu, <u>A. E. O. Persson</u>, and L.-E. Wernersson, "Sensing single domains and individual defects in scaled ferroelectrics", *Science Advances*, vol. 9, pp. eade7098, Feb 2023, doi: 10.1126/sciadv.ade7098.

- ▶ I developed the process flow, helped in the fabrication, the measurement methods, the analyses, and the writing of the paper.

- **Paper X:** Z. Zhu, <u>A. E. O. Persson</u>, and L.-E. Wernersson, "Signal Modulation in a Ferroelectric Tunnel Field-Effect Transistor", accepted in *Nature Communications*.

- ▶ I developed the process flow, helped in the fabrication, the measurement methods, the analyses, and the writing of the paper.

- **Paper XI:** A. IRISH, <u>A. E. O. PERSSON</u>, V. FLODGREN, R. ATHLE, L.-E. WERNERSSON, AND R. TIMM, "Switching Dynamics and Interface Chemistry of Ferroelectric Hafnia Devices", Manuscript in preparation.

- ▶ I developed the process and did the fabrication, performed the electrical measurements, and helped with analysis and writing of the paper.

#### **RELATED WORK**

The following publication is not included in the thesis, but is a related work that I was involved in.

- **Paper I:** R. Athle, T. Blom, A. Irish, <u>A. E. O. Persson</u>, L.-E. Wernersson, R. Timm, and M. Borg, "Improved Endurance of Ferroelectric  $Hf_{1-x}Zr_xO_2$  Integrated on InAs by using Millisecond Annealing", *Advanced Materials Interfaces*, vol. 9, pp. 2201038, Aug 2022, doi: 10.1002/admi.202201038.

- ▶ I helped develop the process flow, the measurement methods, the analyses, and the writing of the paper.

## Acronyms and Symbols

Here, important acronyms, abbreviations, and symbols are listed, which are recurring throughout the thesis. Some parameters, which only occur in a narrow context, are intentionally omitted; some parameters are used in more than one way, but the context is always explicitly clarified in the corresponding text. Some (compound) units are provided with prefixes to reflect the most commonly encountered notations in literature.

#### ACRONYMS AND ABBREVIATIONS

**1T1C** One-transistor, One-capacitor

**AC** Alternating current

AFM Atomic force microscopy

ALD Atomic layer deposition

BEOL Benzocyclobutene

BEOL Back end of line

BERT Bit error tester

**BOE** Buffered oxide etch, a mixture of NH<sub>4</sub>F, HF, and H<sub>2</sub>O

**CMOS** Complementary metal–oxide–semiconductor

CPU Central processing unit CPW Coplanar waveguides

**CSD** Chemical solution deposition

**CV** Capacitance-voltage

DC Direct current

**DRAM** Dynamic random-access memory

EBSD Electron beam lithography

Electron backscatter diffraction

**EDX** Energy-dispersive X-ray spectroscopy

**FeFET** Ferroelectric field-effect transistor

**FEOL** Front end of line

**FeRAM** Ferroelectric random-access memory

FIB Focused ion beam

FLA Flash lamp annealing

FTJ Ferroelectric tunnel junction

**GIXRD** Grazing incidence X-ray diffraction

**HAXPES** Hard X-ray photoelectron spectroscopy

**HEMT** High-electron-mobility transistor

**HSQ** Hydrogen silsesquioxane **HZO** Zr-doped  $HfO_2$ ,  $Hf_xZr_{1-x}O_2$

IC Integrated circuit

ICP Inductively coupled plasma

IMPF Inelastic mean free path

KAI Kolmogorov-Avrami-Ishibashi model

LRRM Line-Reflect-Reflect-Match

MIM Metal insulator metal

MIMCAP Metal insulator metal capacitor

MLA Maskless aligner

mm-wave Millimeter wave (30–300 GHz)MOS Metal oxide semiconductor

MOSCAP Metal oxide semiconductor capacitor

MOSFET Metal oxide semiconductor field effect transistor

MOVPE Metalorganic vapor phase epitaxy

MW Memory window

nid Non-intentionally dopedNLS Nucleation limited switching

**PCM** Phase change memory

**PFM** Piezoresponse force microscopy

PLD Pulsed laser deposition PUND Positive-Up-Negative-Down

PV Polarization-voltage

**PZT** Lead zirconate titanate,  $Pb(Zr_{1-x}Ti_x)O_3$

RF Radio frequency

RIE Reactive ion etching

**RRAM** Resistive random-access memory

RT Room temperature

RTA Rapid thermal anneal, synonymous with RTP

RTN Random telegraph noise

RTP Rapid thermal processing, synonymous with RTA

SEM Scanning electron microscope SPM Scanning probe microscopy SRAM Static random-access memory

SRAM Scanning transmission electron microscope

**STT-MRAM** Spin-transfer-torque magnetic random-access memory

**TEM** Transmission electron microscope

TER Tunnel electroresistance

TFET Tunnel field-effect transistor

TFR Thin-film resistor

UV Ultraviolet

VLS Vapor-liquid-solid

**WGFMU** Waveform generator module

**XPS** X-ray photoelectron spectroscopy

#### **LATIN SYMBOLS**

A m<sup>2</sup> Area

Al<sub>2</sub>O<sub>3</sub> Aluminum Oxide

D C m<sup>-2</sup> Displacement field

E V m<sup>-1</sup> Electric field

| $E_{ m C} \ E_{ m F} \ E_{ m g}$   | $ m MVcm^{-1}$ eV eV                             | Coercive field<br>Fermi Level Energy<br>Band Gap                               |

|------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------|

| f                                  | Hz                                               | Frequency                                                                      |

| GaSb                               |                                                  | Gallium Antimonide                                                             |

| I<br>I <sub>D</sub>                | A, A A $\mu m^{-1}$                              | Current Drain Current, often normalized by the gate width                      |

| $I_{\mathrm{DS}}$                  | A, $mA \mu m^{-1}$                               | Source-to-Drain Current, often normalized by the gate width                    |

| $I_{G}$                            | A, $mA \mu m^{-1}$                               | Gate Current, often normalized by the gate width                               |

| InAs<br>I <sub>S</sub>             | A, $mA \mu m^{-1}$                               | Indium Arsenide Source Current, often normalized by the gate width             |

| $k_{\mathrm{B}}$                   |                                                  | $\approx 1.381 \times 10^{-23} \ kg  m^2  K^{-1}  s^{-1}$ , Boltzmann Constant |

| $L_{\mathrm{G}}$                   | m                                                | Gate Length                                                                    |

| $m_0$                              |                                                  | $\approx 9.109 \times 10^{-31}$ kg, Electron Rest Mass                         |

| P<br>P <sub>R</sub>                | $\mu \text{C cm}^{-2}$<br>$\mu \text{C cm}^{-2}$ | Polarization<br>Remanent polarization                                          |

| Q<br>q                             | С                                                | Charge $\approx 1.602 \times 10^{-19}$ C, Elemental Charge                     |

| TDMAHf<br>TEMAZr                   |                                                  | Tetrakis(dimethylamido)hafnium<br>Tetrakis(ethylmethylamido)zirconium          |

| $V_{ m DS} \ V_{ m GS} \ V_{ m T}$ | V<br>V<br>V                                      | Drain-to-Source Voltage<br>Gate-to-Source Voltage<br>Threshold Voltage         |

#### **GREEK SYMBOLS**

- $\varepsilon_0$   $\approx 8.854 \times 10^{12} \, \mathrm{F \, m^{-1}}$ , Vacuum permittivity

- $\varepsilon_{\rm r}$  Relative permittivity

- $\kappa$  Relative Permittivity

- $\chi_e$  Electric susceptibility

## **INTRODUCTION**

## Background

"One should not work on semiconductors, that is a filthy mess; who knows whether there are semiconductors at all!"

Wolfgang Pauli, 1931

HEN researchers started investigating the theory of electronic conduction in semiconductors in the early 1930s, they had no idea that they were soon to change the lives of future generations. They laid the foundation for the perhaps most important invention of the century, the transfer resistor (transistor) by Bardeen, Brattain, and Shockley in 1947, i.e., a device in which the electrical current between two electrodes can be controlled by a third electrode. The transistor is the most important device in electronics and constitutes the foundation of the digital revolution, also known as the third industrial revolution. It has truly revolutionized society by providing an incredible increase in computational power, memory storage, and transfer of information. On its own, a transistor can serve as a signal amplifier, which is very important for communication engineering. But it was not until the late 1950s and the invention of the integrated circuit (IC) that the true impact would be felt. By integrating a number of transistors as one indivisible unit, rather than interconnected after individual device fabrication, the cost of advanced circuits could be dramatically decreased [1].

Until the 1980s, the dominating technology was the bipolar transistor, but its power consumption became unsustainable, and the industry instead moved to the self-aligned silicon metal–oxide–semiconductor field-effect transistor (MOSFET) that was first invented in 1960. With this came the com-

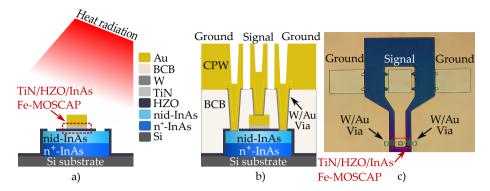

**Figure 1.1:** Schematic representations of a) a planar MOSFET, b) a tri-gate MOSFET in which the gate covers three sides of the semiconductor instead of one, and c) a gate-all-around structure in which the gate covers all sides of the semiconductor.

plementary metal-oxide-semiconductor (CMOS) technology that is still the workhorse of the semiconductor industry [2]. Further technological development has relied on an incremental downscaling of silicon MOSFETs that for each new generation has improved speed, power efficiency, and fabrication cost. In 1965, the CEO of Intel, Gordon Moore, predicted that the number of transistors in an IC would double every other year for the coming decade [3]. This, perhaps self-fulfilling prophecy, has basically remained true until today and there are nowadays ICs with trillions of transistors [4]. The total number of transistors ever fabricated was in 2018 estimated to be  $\sim 1.3 \times 10^{22}$ , i.e., the most fabricated thing in the history of humanity [5]. Given the exponential yearly growth, it is reasonable to assume that the number by great margin is bigger than both the number of grains of sand on planet Earth ( $\sim 8 \times 10^{18}$ ) [6] and similar to the number of stars in the known universe ( $3 - 7 \times 10^{22}$ ) [7].

Even if the CMOS technology has prevailed, the massive size downscaling has meant considerable changes to the transistor design and the used manufacturing processes. In 1974, Robert Dennard and IBM colleagues introduced the geometric MOSFET scaling rules that steered the development for decades [8]. While keeping the general planar structure of the MOSFET the same, Fig. 1.1a), the physical gate length of transistors shrunk from 1  $\mu$ m in 1974 to 35 nm in 2003, whereas the clock frequency increased from 2 MHz to 3 GHz. But in the beginning of the 2000s, Dennard's scaling laws had made the threshold voltage so low that the off-state leakage current made the standby power unsustainable whereas an increasingly thinner gate oxide (~1.2 nm SiO<sub>2</sub>) caused gate leakage through quantum mechanical tunneling. A new approach was needed, and the research field changed to the equivalent scaling era. The SiO<sub>2</sub> gate oxide was exchanged with alternative high permittivity (high- $\kappa$ ) materials such as HfO<sub>2</sub> and the geometry was, as shown in Fig. 1.1, changed

from planar to nonplanar multigate architectures. This allows for superior electrostatic control of the channel and since the electronic conduction occurs on three sides of the fin, the current per chip area increases [9]. The tri-gate FinFET remained the flagship design until 2022, when Samsung finally moved over to a gate-all-around approach using nanosheets as in Fig. 1.1c) in order to increase the electrostatic control of the channel even further [10].

#### 1.1 THE FUTURE OF ELECTRONICS

Through incremental downscaling, new materials, and innovative architectures, transistors have become a powerful tool whose impact will continue to shape the future. The current trends point towards stacking several gate-all-around structures on top of each other to further increase current per chip area, and even stacking NMOS and PMOS devices on top of each other. According to the latest version of the International Roadmap for Devices and Systems 2022 (IRDS) [11], i.e., the leading roadmap for electronics development, the outlined approaches are expected to keep up development for the coming decade. But the silicon MOSFET scaling is coming to an end. To enable computing system advances, IRDS predicts that new types of devices and circuit architectures are required by the end of the 2020s. Ferroelectric transistors and memristors for neuro-inspired computing are mentioned among the most promising technologies, whereas Ge and III-V materials are mentioned as leading semiconductor candidates to complement Si.

The work presented in this thesis is positioned at the center of this development and involves research on ferroelectric integration on III-V materials and its applications. Below, the case for III-V materials in MOSFETs, tunnel field-effect transistors (TFETs), and neuromorphic circuit architectures is made while the topic of ferroelectricity has been granted its own chapter.

#### 1.1.1 III-V NANOWIRES

III-V compound semiconductors are alloys of elements from groups III (B, Al, Ga, and In) and V (N, P, As, and Sb) in the periodic table of elements. The mobility of III-V materials, i.e., how fast an electron moves through a material under an applied electric field, is several times that of silicon making them well suited for high-frequency electronics as this property decides how fast electrons can cross the channel of a transistor [12]. Faster means a quicker response to a varying gate potential and this has enabled III-V high-electron-mobility transistors (HEMTs) to excel in high-frequency applications having an operational frequency above 1 THz [13].

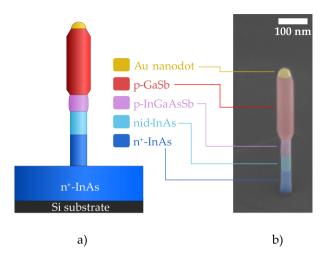

**Figure 1.2:** a) A schematic of a VLS-grown III-V nanowire with a complex heterostructure and b) a corresponding scanning electron microscope (SEM) image of the structure.

In this thesis, III-V nanowires similar to the one depicted in Fig. 1.2 are used for all transistor implementations. Besides the outstanding carrier transport properties of III-V semiconductors combined with the optimal gate-all-around geometry for electrostatic control, the vertical implementation is beneficial as it decouples contact and channel length from the chip footprint. This enables dense implementation of devices, even for relatively large contacts and long gate lengths. Furthermore, as indicated by Fig. 1.2, the vertical geometry enables advanced semiconductor heterostructures as the strain from mismatched lattice constants can relax radially. Thereby, advanced band structures can be achieved, which in this thesis is utilized for implementing the energy-efficient steep-slope devices described below in section 1.1.2. For compatibility with industrial fabrication methods, all nanowire devices in this thesis are integrated on standard silicon substrates.

#### 1.1.2 UNCONVENTIONAL TRANSISTORS

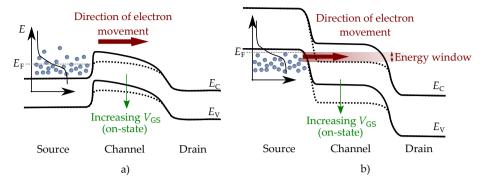

As schematically indicated in Fig. 1.3a), the current flow in a conventional MOSFET is modulated by the height of the potential barrier in the channel region which is changed by the gate voltage. Only charge carriers with an energy higher than the top of the barrier contributes to the current, but as the charge carriers follow Boltzmann statistics, high-energy electrons in the tail of the distribution are injected across the channel even in the off-state. This causes a thermal limit (the so-called Boltzmann tyranny) for which the gate

**Figure 1.3:** Schematic illustration of the band diagrams and working principles of a) MOSFETs and b) TFETs. Full lines correspond to the off-state and dotted lines to the on-state. In the MOSFET in a), charge carriers easily overcome the channel energy barrier in the on-state. Due to the band tails caused by the Boltzmann statistics, a few charge carriers can overcome the channel energy barrier even in the off-state. In the TFET in b), the charge carriers can tunnel when the conduction band in the channel is lower than the Fermi level in the source, but not when the energy window closes with the decreased gate voltage in the off-state.

voltage must be decreased by 60 mV to decrease the source-drain current by one magnitude. To have off-state leakage acceptably low, these 60 mV/decade sets a lower threshold voltage limit of  $\sim$ 200 mV, whereas overdrive voltage need to be  $\sim$ 300 mV. In total, an operating voltage of 500 mV is required, which sets a practical limit on MOSFET power efficiency [9].

To overcome the Boltzmann tyranny to allow for sub-500 mV operating voltage, several unconventional transistor designs exist such as tunnel field-effect transistors (TFET) [14], negative capacitance transistors, [15] and Dirac-Source transistors [16]. Even if the basic transistor functionality of a TFET is the same as for a MOSFET, the carrier transport is fundamentally different. Instead of thermionic injection over a barrier, TFETs utilize the quantum mechanical band-to-band tunneling between the valence band in the source and the conduction band in the channel. The current is still modulated by moving the bands in the channel region by applying a voltage to the gate, but due to the filtering of high-energy carriers in the Fermi-tail, the devices can obtain a subthreshold swing below the thermal limit of 60 mV/dec. Due to their reliance on tunneling, TFETs usually have lower current densities than MOSFETs. However, by using III-V heterojunctions, this may be partially avoided due to a low bandgap and low effective mass providing a small tunneling distance and tunneling mass [14]. In depth treatments of the vertical

III-V nanowire MOSFETs and TFETs developed in Lund can be found in [17] and [18], respectively.

The introduction of a material with negative capacitance [19] in the gate oxide of a MOSFET is also a suggested method to overcome the Boltzmann tyranny [15, 20]. As the commonly stated approach is to stabilize the negative capacitance of a ferroelectric material by the positive capacitance of a semiconductor, it must be noted that the sub-60 mV/decade behavior in the ferroelectric TFETs in this thesis is not thought to arise from the concept of negative capacitance, but from the previously described energy filtering in TFETs.

#### 1.1.3 NEUROMORPHICS

To enable further development in computing system advances beyond transistor scaling, even the foundation of computer architecture, the von Neumann architecture (VNA) from 1945 that physically separates the computation and memory units, is being reconsidered. Large data sets in the VNA must be shuttled back and forth between computing and memory chips, making data-centric applications struggle with latency and power inefficiency. To solve this problem, non-von Neumann architectures are being investigated and especially neuro-inspired approaches, such as in-memory computation, have caught interest. This approach merges the computation and memory into one unit, similar to the brain, where memory and processing are deeply intertwined [21]. The complexity and use of neuro-inspired systems varies, but the most common application is as artificial intelligence (AI) accelerators, i.e., computer chips specialized for the matrix-vector-multiplications (y = Ax) that are extremely abundant in machine learning computation. There have been implementations of AI accelerators using different kinds of memristors such as spin-torque-transfer memories [22], phase change memories [23], and resistive random-access memories [24] proving the viability of the technology.

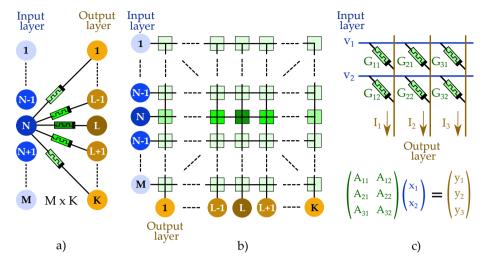

The memristor is a device storing information as distinct and stable conductance states caused by differences in the atomic arrangements of a material [21]. This makes them useful as highly scalable synapses in neuroinspired systems as they provide a tunable connection strength (conductance) between the neurons as in Fig. 1.4a). In IRDS, it is predicted that ferroelectric transistors and memristors for neuro-inspired computing will be needed in the coming decade [11] in order to enable computing system advances. The ferroelectric field-effect transistors (FeFETs) and ferroelectric tunnel junctions (FTJs) investigated in this thesis are potential solutions.

As seen in Fig. 1.4b), memristors can be used as the weight elements in  $M \times K(A)$  matrices and are on the chip implemented in a fully connected crossbar array, i.e., every input is connected to every output through a memristor. In

**Figure 1.4:** Illustration of an artificial neural network in a crossbar array. a) Each neuron is a node in one layer (blue) connected to all other nodes in the next layer (brown) via memristors (green) that correspond to the connections of biological axon-synapse-dendrites. b) This is implemented through a fully connected crossbar array which has a memristor at every cross point. c) Matrix-vector multiplication in a crossbar array.

practice, this is commonly implemented by long lines of metal strips of word and bit lines with a memristor at each cross point [25]. The conductance of the memristor multiplied by the input voltage gives the output current. If there is a linear mapping between the conductance of the memristors and the elements in the matrix A (Fig. 1.4c), the *x* values can be encoded into the voltage of the input layer. The currents measured at the output layer will then, due to Ohm's law and Kirchhoff's current law, be proportional to the matrix vector result *y*. If the input is instead duration rather than voltage, the output becomes the total charge (i.e., the time integral of the current). By applying the input at the output, the matrix multiplication is instead performed on the transpose of *A*. In principle this could be implemented using resistors, but the strength of using memristors is that the matrix values are reprogrammable which enables on-chip training of the neural network [26,27].

# Ferroelectricity

ferroelectric material has a spontaneous electric polarization which can be switched by applying an external electric field. The property is caused by the crystal structure of the material in which a remanent polarization is created by a non-centrosymmetric lattice. A theoretical prediction of ferroelectricity was made in 1912 by Debye, drawing on an analogy to ferromagnetism, [28] which in turn made Schrödinger coin the term ferroelectricity (ferroelektrisch) the same year [29]. Hysteresis, nonlinearity, saturation, large permeability, and a Curie temperature all have a counterpart. Ferroelectricity was experimentally discovered when Prof. Swann, apparently unaware of the previous predictions, speculated that the abnormal dielectric behavior reported for Rochelle salt might be explained by some kind of electrical hysteresis. His student Valasek investigated the topic and could in 1920 indeed verify a polarization hysteresis in the material. Until the finding of ferroelectric BaTiO<sub>3</sub> during World War II, the fragility of ferroelectric materials made them mainly a theoretical interest [30]. However, with  $BaTiO_3$ , Devonshire [31] was able to formulate a model of ferroelectricity based on previous work on phase transitions by Landau [32] and Ginzburg [33].

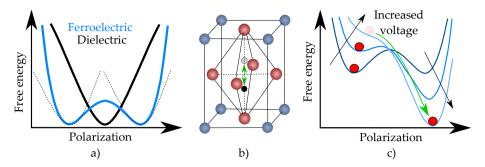

#### 2.1 A SIMPLE FERROELECTRIC MODEL

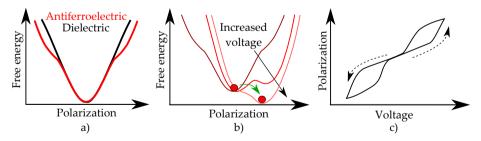

Although phenomenological, the Landau-Ginzburg-Devonshire model of dielectric and ferroelectric materials is useful for understanding ferroelectricity. As shown in Fig. 2.1a), it describes a ferroelectric as having two (dielectric) states separated by an energy barrier, i.e., a double-well potential. In the model material lead zirconate titanate ( $Pb(Zr_{1-x}Ti_x)O_3$ , PZT) in Fig. 2.1b),

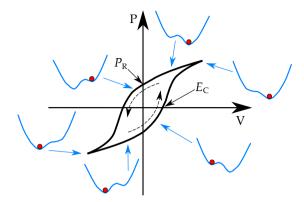

**Figure 2.1:** a) The free energy of a ferroelectric as a function of the electric polarization P forms a double-well landscape. b) Lead zirconate titanate ( $Pb(Zr_{1-x}Ti_x)O_3$ , PZT) has become a model ferroelectric material in which an ion moves between two stable off-center positions marked by the green arrow. c) When applying an electric field, the free energy landscape gets distorted and the current state might no longer be the one with lowest energy, making the state switch as indicated by the green arrow.

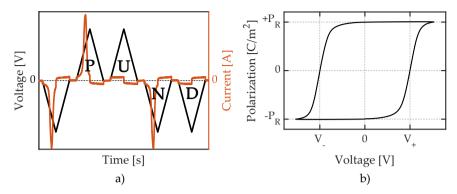

these states can be thought of as two thermodynamically stable atomic configurations, in between which a Ti/Zr ion can move if a strong enough electric field is applied. The movement makes the polarization dipole of the unit cell switch. As seen in Fig. 2.1c), this occurs as the electric field distorts the double well landscape and at a certain field, the energy minimum is no longer the state currently occupied and the state switches. This creates a relationship between the polarization and the applied field (voltage) that is described by a hysteresis curve as in Fig. 2.2. The measurement of the hysteresis curve will be explained in section 5.1.1. The curve can be used to retrieve the characteristic parameters of a ferroelectric material: the remanent polarization ( $P_R$ ) and the coercive field ( $E_C$ ).  $P_R$  represents the macroscopic polarization of the material when no electric field is applied, while  $E_C$  is the electric field where the macroscopic polarization becomes zero [34].

A volume of the ferroelectric having an identically oriented spontaneous polarization is referred to as a domain. Domains are in this simple model assumed to have a constant spontaneous polarization with an abrupt wall towards the surrounding. Due to energy minimization, ferroelectric materials are normally multidomain and this is especially true for polycrystalline thin films such as those studied in this thesis. A commonly used model for polycrystalline multidomain thin film ferroelectrics is an Ising-like one as in Fig. 2.3a). The assumptions are 1) that the polarization magnitude is intrinsically connected to the crystal structure of the material and 2) that the crystal orientation, i.e., the direction of the polarization axis, of each crystallite is statistically distributed. All crystallites are assumed to have the

**Figure 2.2:** A characteristic polarization-voltage hysteresis loop for a ferroelectric material and the corresponding thermodynamic free energy landscape at the corresponding voltage.

**Figure 2.3:** a) In a simplified model, ferroelectric films can be regarded as similar to an Ising model but with electric dipoles instead of magnetic dipole moments. b) A crystal whose polarization axis aligns to the applied electric field ( $E_{\rm Aligned}$ ) has a considerably smaller coercive field than one with a nonaligned polarization axis ( $E_{\rm Tilted}$ ).

same coercive field,  $E_{\rm C}$  in Fig. 2.3b), but only the electric field component parallel to the polarization axis contributes to the switching of the remanent polarization. This leads to a spread in the coercive field across the material and the effective polarization with which it affects its surroundings. A more in-plane switching has a higher coercive field and contributes less to the macroscopic polarization [34].

The above view of a ferroelectric as a Landau-based Ising-like model is highly useful as an idealized conceptualization of the phenomena, however, it is a simplification that rarely holds if used for actual modeling of material properties. For instance, the thermodynamic switching described by the Landau approach typically overestimates the coercive fields by orders of magnitudes, whereas inhomogeneities such as impurities, crystal defects, and charge trapping are also needed to explain switching dynamics [35]. For this

thesis, an Ising-like view is mostly sufficient and further refinements will be treated when necessary to understand the results.

# 2.1.1 ANTIFERROELECTRICITY

In line with the analogy of ferroelectricity and ferromagnetism, antiferroelectricity is the electrical counterpart of antiferromagnetism. Here, the electrical dipoles of the material are understood as being antiparallel when no voltage is applied, i.e., adjacent dipoles point in opposite directions making the remanent polarization cancel out to zero. Thermodynamically this can be understood as in Fig. 2.4a) where there is a single minimum when no voltage is applied, but that an energy barrier emerges at a certain voltage causing a new stable state at high electric fields as in Fig. 2.4b). This means that a sufficiently large electric field results in an alignment of the dipoles as in a ferroelectric material, however, when the voltage is removed the dipoles relax back to their antiparallel ground state again [36]. As the free energy landscape is symmetric in Fig. 2.4a), the same phenomena arise for both negative and positive voltages and when plotted in a polarization-voltage graph a double hysteresis loop arises as in Fig. 2.4c).

# 2.2 FERROELECTRICITY IN ELECTRONICS

Ferroelectricity has been connected to electronics ever since its discovery while trying to fabricate a new kind of seismometer during World War I [30]. The scientific research soared in the 1940s and it got recognized that a stable electrically switchable device could be used as a binary computer

**Figure 2.4:** a) The free energy of an antiferroelectric material as a function of the electric polarization P forms a single stable state at P=0. b) But due to the shape of the free energy two other states become lower in energy for high applied fields and the state switch as indicated by the green arrow. c) A characteristic polarization-voltage hysteresis loop for an antiferroelectric material.

memory. Already in the 1950s, the first initial ferroelectric memories were developed [37], but it was not until the 1990s that they found widespread use in memories and radio frequency (RF) devices. For instance, they were mass produced for Sony PlayStation 2 which contained a ferroelectric random-access memory (FeRAM) chip [38].

But then they slowly faded out of use as the perovskite ferroelectrics were incompatible with standard fabrication processes in semiconductor industry (i.e., CMOS-incompatible). They degrade under forming gas annealing [39], cannot be conformally deposited, and are difficult to scale due to a complicated structure [40,41]. Device downscaling is essential for the semiconductor industry, and a device technology must be scalable in order to enable implementation in future technology nodes. Other ferroelectric material classes exist, e.g., polymer-based [42], triglycine sulfates [43], moiré pattern based [44], or even ice [45,46], but as with perovskites, they have not been able to compete with more conventional memory technologies.

Instead, it has been the lately discovered HfO<sub>2</sub>-based fluorite-type ferroelectrics that have caught industrial interest. HfO<sub>2</sub> is a well-established oxide material in semiconductor industry and thus fully CMOS-compatible [9]. The films are highly scalable and a 1.5 nm thick film has been shown ferroelectric by back-to-back connecting two films [47]. By more heavily relying on material characterization rather than electrical characterization, ferroelectricity has been indicated for ferroelectric HfO<sub>2</sub> in even thinner films [48,49]. HfO<sub>2</sub>-based fluorite-type ferroelectrics will be treated more in depth in section 2.3.

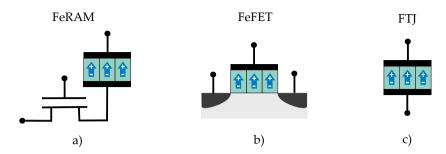

# 2.2.1 MEMORY DEVICES

There are many potential applications for ferroelectricity in electronics, but as with the past, memory will probably remain the main application. Below, the three most promising technologies summarized in Fig. 2.5 are presented in their order of technological maturity. Ferroelectric random-access memory (FeRAM) has successfully been commercialized using perovskites and is one of the most energy efficient memory technologies. The ferroelectric field-effect transistor (FeFET) is a versatile complement to flash technology and may become the key component in future data-centric computer applications. The ferroelectric tunnel junctions (FTJ), as with other memristive technologies, might on top of being a binary memory also enable neuromorphic computing. Less commonly, ferroelectric RF and mm-wave technologies are discussed, but there is reason to believe that ferroelectric HfO<sub>2</sub> will find applications also in that field [50–52].

**Figure 2.5:** a) The 1T1C structure of a ferroelectric random-access memory, b) the 1T structure of a ferroelectric field-effect transistor, and c) the 1C structure of a ferroelectric tunnel junction.

#### **FeRAMs**

The dynamic random-access memory (DRAM) cell was developed in the mid-1960s and has become the standard technology for main memory in computers. Just like the FeRAM in Fig. 2.5a), it uses a 1T1C architecture, i.e., a capacitor as the storage element and an access transistor to control the charge stored on said capacitor. The transistor gate is activated by a voltage to read or write data to the storage capacitor and the data is sensed on the transistor source as the current response is dependent on whether the capacitor was charged or not ("1" or "0"). The memory is cheap, fast, and durable; however, it comes with caveats such as 1) the storage capacitor must be large in order to store a measurable amount of charge and 2) the access transistor will inevitably leak current making the memory eventually lose its state. Because of reason 2), to keep the stored data, the memory must be periodically refreshed and is therefore a volatile memory solution. When powered off, its data is lost [53].

Ferroelectric random-access memory (FeRAM), based on ferroelectric per-ovskites, was commercialized in the early 1990s and is still used in certain niche applications where ultra-low-power non-volatile memory is critical [54]. The 1T1C technology is similar to DRAM, but the charge is non-volatile as the storage capacitor is ferroelectric rather than dielectric, see Fig. 2.5a). The data is read by activating the transistor by a gate voltage and then applying a voltage across the ferroelectric. If the ferroelectric switches ("1"), the current response will be considerably bigger than if it does not switch ("0"). Furthermore, compared to DRAM, there is the benefit that the capacitor area can be reduced as the polarization charge density in a ferroelectric is high compared to a dielectric charge density (e.g.,  $\sim 20-30~\mu\text{C/cm}^2$  for ferroelectric HfO2 compared to  $\sim 2-3~\mu\text{C/cm}^2$  for dielectric HfO2). This enables area shrinkage and reduction in manufacturing complexity, i.e., it lowers the cost.

The major issue is currently cycling endurance, which is considerably lower than for DRAM [55], but at least for the current niche applications it is virtually unlimited [54].

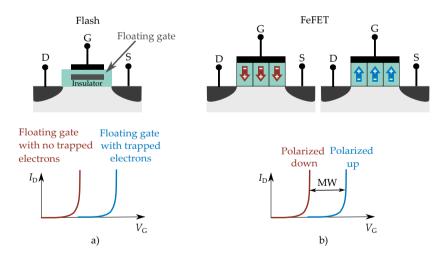

#### **FeFETs**

As indicated in Fig. 2.6a), flash memories resemble standard MOSFETs, however, they have an extra floating gate which is insulated all around. Through direct tunneling or hot electron injection, electrons can be trapped at this floating gate by applying a voltage. The trapped charges change the electrostatics of the MOSFET and by screening the electric field from the regular gate electrode, the threshold voltage ( $V_T$ ) of the transistor can be changed. By reading out the current at a certain gate voltage, one can readily assign the two  $V_T$ -states to "1" and "0". The major issue of flash memories is the endurance and the energy consumption during the write cycle [56]. The market for non-volatile memory is currently dominated by flash memory and hard disk drives (HDD). The electro-mechanical HDDs are cheap but slow, and with the market trend being towards portable devices, flash memory is preferred due to its mechanical shock resistance [53].

The ferroelectric field-effect transistor (FeFET) effectively fills the same function as flash memory, but with several advantages. The FeFET is a device

**Figure 2.6:** Schematic illustrations of a) a flash memory cell with a floating gate encapsulated by the oxide insulator and b) ferroelectric field-effect transistors with the ferroelectric domains polarized in opposite direction. The two technologies have similar transfer characteristics, and their threshold voltages are both changed by the application of a voltage pulse to the gate.

integrating a ferroelectric material in the gate stack of a standard MOSFET, see Fig. 2.5b). Like the floating gate of a flash memory, the ferroelectric polarization changes the electrostatics of the MOSFET and depending on the polarization state, the threshold voltage of the transistor shifts as in Fig. 2.6b). By applying a voltage bigger than the coercive voltage of the ferroelectric to the gate, the polarization state switches. The difference between the high- $V_T$  state and the low- $V_T$  state is commonly referred to as the memory window (MW). To a first order approximation, the memory window is twice the coercive voltage of the ferroelectric film. By only switching a portion of the ferroelectric state, intermediate threshold voltages are obtainable which makes it possible to use the device as a three-terminal memristor [57]. State-of-the-art FeFETs have an endurance ranging from  $10^5$ – $10^9$  cycles, which is significantly better than flash memories while at the same time considerably more energy efficient [58].

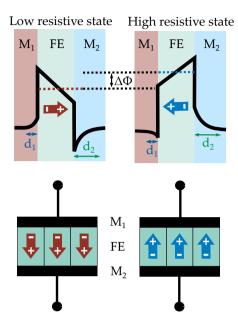

# **FTJs**

Memristors have found some commercialization in e.g., Intel's product Optane, however, they are in general less industrially mature than previously mentioned technologies of DRAM and flash. Commonly, three memory technologies are identified as the most promising memristor technologies: spin-torque-transfer memory, phase change memory, and resistive random-access memories (RRAMs) [21]. Ferroelectric tunnel junctions (FTJ) are an emerging alternative and, as seen in Fig. 2.7, they consist of a thin ferroelectric sandwiched between two electrodes. When applying a bias, the tunneling transmission probability through the film is strongly dependent on the ferroelectric polarization, i.e., there is an OFF/ON resistance ratio called the tunnel electroresistance (TER) that changes with the reversal of the ferroelectric polarization [59].

The polarization charges present at the surface of the ferroelectric repel or attract electrons and holes depending on the polarization state. In metal electrodes, this happens over a short distance as the electron density is high (usually a few tenths of nanometers), whereas in semiconductors, the screening length can reach tens or hundreds of nanometers. The imperfect screening creates a potential drop at the electrode/ferroelectric interface which in turn creates a band bending. By using two different electrodes, different screening lengths ( $d_1$  and  $d_2$  in Fig. 2.7) create an asymmetric device with an average barrier height that depends on the ferroelectric polarization. As the tunneling transmission probability is dependent on the barrier height, the resistance of the device is dependent on the ferroelectric polarization state [59, 60]. FTJs are commonly fabricated with two metal electrodes, i.e., metal-insulator-metal (MIM), as presented in this thesis. The highest TER is though usually

Figure 2.7: Schematic of the band diagram of an asymmetric metal-insulator-metal ferroelectric tunnel junction (FTJ). Without the ferroelectric polarization, the energy barrier would have been a square potential. Due to different screening lengths in the metals ( $d_1$  and  $d_2$ ), the electronic potential profile is altered by the polarization state. As the average energy barrier height is lower in the left state (by  $\Delta\Phi$ ), the tunnelling current becomes bigger and the FTJ is in the low resistive state (the ON-state). In the opposite state, the average energy barrier height is higher resulting in the high-resistive state.

found when one of the electrodes is a semiconductor, which probably can be attributed to the even more asymmetric screening length in a metal-insulator-semiconductor (MIS) compared to a MIM [61].

# 2.2.2 HIGH-FREQUENCY ELECTRONICS

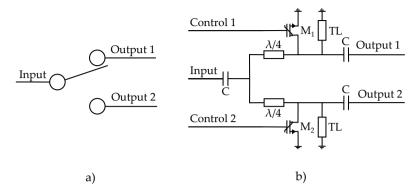

Microwave communication systems are expected to be increasingly more flexible and adaptable, requiring reconfigurability [62]. This means that ferroelectric devices might make a comeback due to the ferroelectric HfO<sub>2</sub> as it in contrast to perovskites is CMOS-compatible and scalable. The high-frequency applications of HfO<sub>2</sub>-based ferroelectrics are barely treated in literature even if it has been an active field of research for ferroelectric perovskites for decades. The benefit of ferroelectrics is that they provide a frequency independent tunable permittivity (capacitance) which can be

Figure 2.8: a) The symbol of an SPDT (single pole, double throw) switch, i.e., a break-before-make switch in which the input is either connected to output 1 or 2. b) A schematic circuit for a FeFET SPDT. The transistors M are FeFETs with control lines connected so that the remanent polarization can be switched. By utilizing both a NMOS FeFET and a PMOS FeFET, a single control input can be used but that would also remove the possibility of implementing simultaneous transmission through both or none of the outputs. Capacitors are added to block DC signals from both the input and outputs. When a FeFET is in the on-state, the corresponding output will be shorted to ground, while in the off-state the signal is transmitted. The  $\lambda/4$ -lines transforms a short to a high impedance which reflects the input power making the output low. The transmission lines TL are inductive stubs designed to resonate the parasitic capacitances of the FeFETs, thus minimizing losses at the output.

applied in varactors for implementations in amplifiers, filters, phase shifters, and voltage-controlled oscillators.

For mm-wave applications, ferroelectric HfO<sub>2</sub> has a clear disadvantage compared to perovskite ferroelectrics due to its high Curie temperature of several hundred degrees Celsius [63]. Although seldom mentioned, there is a general assumption that polar ferroelectrics should not be used for high-frequency devices. This is due to their piezoelectricity, which creates big microwave losses at <10 GHz, and their domain wall movements that contribute to further losses. The hysteresis associated with the polar phases makes them less desirable as it sets further design restrictions. Therefore, the proposed applications in HfO<sub>2</sub>-based applications have mainly focused on using the capacitance tunability of the ferroelectric response in the sub-coercive voltage region, where domain switching can be neglected [64]. This allows for a capacitance tunability of a couple of tens of percent that with simulated filters have shown promising results. However, at a high enough frequency it is expected that domain walls and piezoelectricity stop responding to the small signal and will therefore not contribute to losses, e.g., at frequencies up to 50

GHz in a ferroelectric perovskite [65]. The same is expected to remain true for HfO<sub>2</sub>-based ferroelectrics, however, it is yet to be investigated. Metalinsulator-metal capacitors of ferroelectric HfO<sub>2</sub> have been investigated up to mm-wave frequencies (30-300 GHz) by Abdulazhanov et al. [66], but the films show a high permittivity and loss tangent which is assumed to be caused by the deembeddning procedure. Nevertheless, the results indicate the applicability of the technology and are in line with the metal-insulator-semiconductor results in paper IV in this thesis.

Combining ferroelectrics with semiconductors might create even further flexibility and functionality. Contrary to the historical usage of ferroelectricity as tunable capacitors (varactors), the integration of ferroelectricity on III-V materials in this thesis is mainly to add reconfigurability to the III-V technology platform. For instance, among transistor-based RF-switches, III-V semiconductor devices have achieved the highest operation frequency [67]. In its simplest form, an RF-switch fills the same purpose as a regular light switch (a SPST, Single pole single throw), i.e., either the two terminals are connected or they are not. The simplest possible SPST FeFET RF-switch is to configure the polarization so that the transistor is in either the off-state or the on-state, i.e., either blocking or transmitting the signal. Commonly, RF-switches are used for routing signals on a chip for which the SPDT (Single pole double throw) switch, Fig. 2.8a), can choose whether the input signal passes to output 1 or 2. RF-compatible FeFETs would in these circuits fulfill the same purpose as the currently used MOSFETs, but doing it in a non-volatile reconfigurable fashion which does not need a continuous control signal. For the circuit in 2.8b), only short polarization switching voltage pulses are required to set whether the signal is transmitted through both outputs, routed up, down or not transmitted at all.

From a security perspective, this is useful for hardware obfuscation in which one intentionally can conceal the functionality of the circuitry as it will behave differently depending on the state of each ferroelectric element. Without the correct key, normal functionality is not enabled and can, depending on the complexity of the circuitry, be very difficult to reverse-engineer even if having the blueprint or a physical example of an unlocked device. This concept has in Paper X been implemented in a ferroelectric TFET which has different functionality depending on the ferroelectric state and in Paper IV, in which the reconfigurable varactor has different capacitance depending on the ferroelectric state. By intentionally designing the circuit using a ferroelectric with a short retention time, it is even possible to fabricate a circuit whose functionality is lost a short time after the key is used. This would enable usage of a functioning device without the risk of a competitor reverse-engineering even an unlocked device as it effectively becomes "self-destructive".

# 2.3 FERROELECTRICITY IN HAFNIUM OXIDE

Ferroelectricity in HfO<sub>2</sub> was discovered by Tim Böscke at Qimonda in 2006 when trying to replicate an earlier study by Toriumi's group showing a permittivity maximum for annealed films when doped by 4-5 atomic percent Si [68]. Through extensive electrical and structural analysis, Böscke et al. [69] were able to show that the permittivity enhancement was not due to the assumed increase of tetragonal crystal phase (P4<sub>2</sub>/nmc) but due to a ferroelectric orthorhombic phase (Pca2<sub>1</sub>). As industrial research at a memory company, the work focused on scaled ferroelectric field-effect transistors (FeFET) and ferroelectric random-access memory (FeRAM). Finally, in 2011, several important papers were published with material analysis of ferroelectric HfO<sub>2</sub> [69–72] and importantly a 65-nm technology node Si FeFET [69]. This was followed up in 2012 by a 28-nm Si FeFET [73] together with the first report of Zr-doped ferroelectric HfO<sub>2</sub> (HZO) [74], which has by time become the de facto standard material choice.

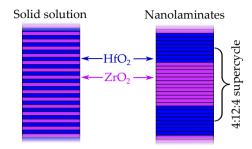

The following section will treat the material properties of ferroelectric  $HfO_2$  as it in some regards differs from the conventional perovskites. In this thesis, unless otherwise specified, any reference to ferroelectric  $HfO_2$  will from this point on assume Zr-doping ( $Hf_xZr_{1-x}O_2$ , HZO). The fabrication and deposition methods for ferroelectric  $HfO_2$  will be treated in chapter 3, while the electrical properties of ferroelectric  $HfO_2$  will be treated together with the measurement methods in chapter 5.

# 2.3.1 MATERIAL CHARACTERISTICS OF FERROELECTRIC HAFNIUM OXIDE

The intuitive model for ferroelectricity introduced in section 2.1, in which an off-center ion in a non-centrosymmetric sublattice is moving between two stable states is true for many perovskite ferroelectrics but has been proven too simplistic for ferroelectric HfO<sub>2</sub>. The ferroelectricity in HfO<sub>2</sub> is rather described as arising from a fluorite structured crystal lattice (crystallographically similar to calcium fluorite) in which the remanent polarization is caused by an off-centering of half of the eight oxygen ions in the unit cell [75]. The unconventional polarization mechanism with a strong atomic bonding compared to perovskites creates robust properties that in most cases are beneficial for implementation in electronic devices. Most importantly, it gives rise to a coercive field that is ten times higher than in conventional perovskites, which enables relatively big coercive voltages and memory windows even at scaled thicknesses [76].

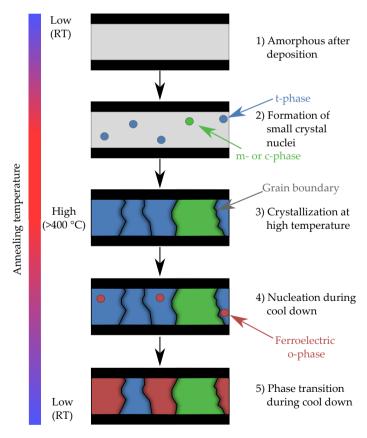

Bulk crystalline  $HfO_2$  and  $ZrO_2$  have been shown to exist in several polymorphs: monoclinic (space group:  $P2_1/c$ ), tetragonal (space group:  $P4_2/nmc$ ), and cubic (space group:  $Fm\overline{3}m$ ). All these crystal phases are centrosymmetric

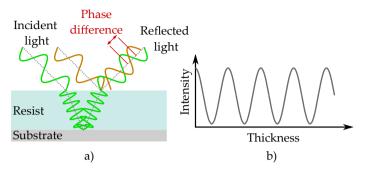

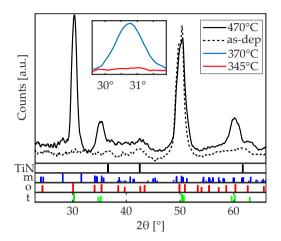

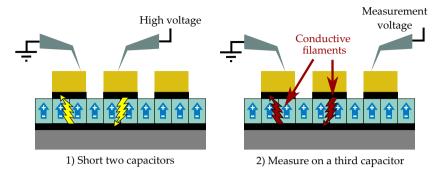

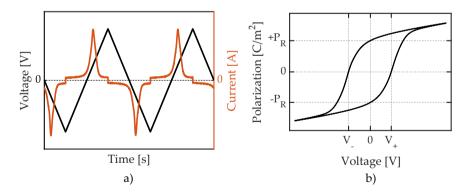

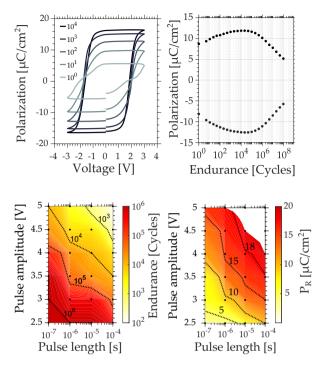

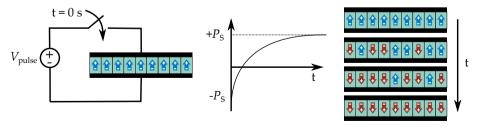

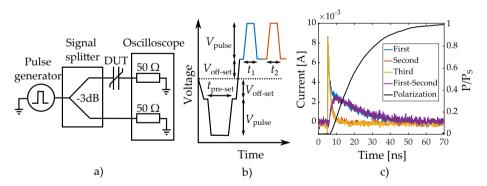

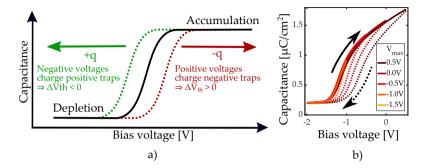

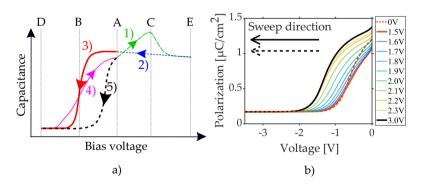

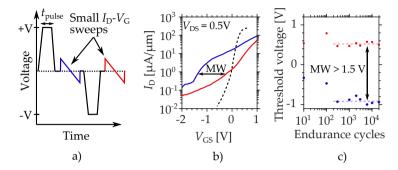

and thus not ferroelectric. However, for thin polycrystalline films, the surface energy becomes comparable to the volume energy and other phases can occur. Several forms of orthorhombic phases have been reported: antipolar orthorhombic-I (space group: Pbca), orthorhombic-II (space group: Pnma), and nonpolar orthorhombic-V (space group: Pbca). The two orthorhombic phases oIII (space group: Pca2<sub>1</sub>) and oIV (space group: Pmn2<sub>1</sub>, never observed experimentally) are ferroelectric. Also the polar rhombohedral phase (space group: R3m) has been reported ferroelectric [77]. Following what is conventional in the research field, this thesis will refer to the phases as monoclinic (m), tetragonal (t), cubic (c), and orthorhombic (o) where the last one is assumed to be the ferroelectric oIII-phase.