### Radio Frequency InGaAs MOSFETs

Garigapati, Navya Sri

2023

#### Link to publication

Citation for published version (APA):

Garigapati, N. S. (2023). Radio Fréquency InGaAs MOSFETs. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Radio Frequency InGaAs MOSFETs

**Doctoral Thesis**

Navya Sri Garigapati

Department of Electrical and Information Technology Lund, September 2023

Academic thesis for the degree of Doctor of Philosophy, which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Wednesday, 27 September, 2023, at 9:15 a.m. in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers Väg 3, 223 63 Lund, Sweden. The thesis will be defended in English.

The Faculty Opponent will be Prof. David Moran, Electronic & Nanoscale Engineering, University of Glasgow, United Kingdom.

| Organisation: LUND UNIVERSITY Department of Electrical and Information Technology Ole Römers Väg 3 223 63 Lund Sweden  Author: Navya Sri Garigapati | Document Type:<br>DOCTORAL THESIS                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                     | Date of Issue:<br>September 2023                                                                                                      |

|                                                                                                                                                     | Sponsoring Organisation(s): Swedish Foundation for Strategic Research (SSI Swedish Research Council (VR) European Union (EU) NanoLund |

Title:

Radio Frequency InGaAs MOSFETs

#### Abstract

III-V-based Indium gallium arsenide is a promising channel material for high-frequency applications due to its superior electron mobility property. In this thesis, InGaAs/InP heterostructure radio frequency MOSFETs are designed, fabricated, and characterized. Various spacer technologies, from high dielectric spacers to air spacers, are implemented to reduce parasitic capacitances, and  $f_T/f_{max}$  are evaluated. Three types of RF MOSFETs with different spacer technologies are fabricated in this work.

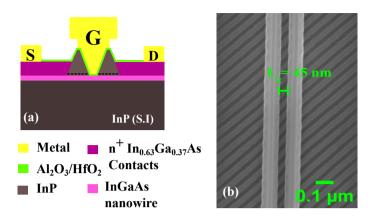

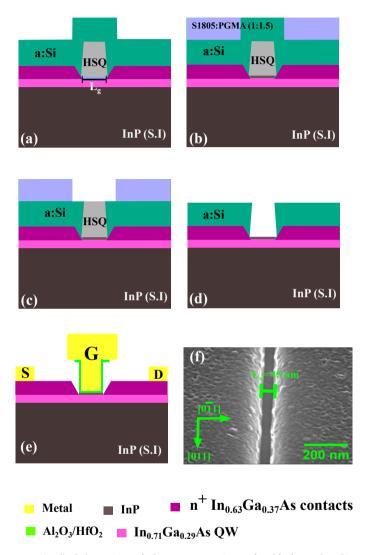

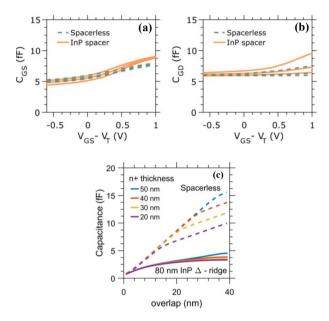

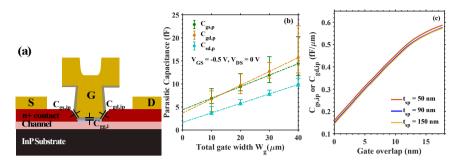

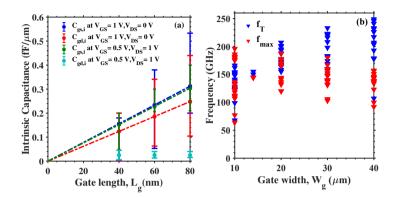

InP  $\Lambda$ -ridge spacers are integrated on InGaAs Nanowire MOSFET in an attempt to decrease parasitic capacitances; however, due to a high-dielectric constant of the spacers and smaller transistors transconductance, the  $f_T/f_{max}$  are limited to 75/100 GHz. InGaAs quantum well MOSFETs with a sacrificial amorphous silicon spacer are fabricated, and they have capacitances of a similar magnitude to other existing high-performing RF InGaAs FETs. An 80 nm InGaAs MOSFET has  $f_T/f_{max}=243/147$  GHz is demonstrated, and further optimization of the channel and layout would improve the performance. Next, InGaAs MOSFETs with nitride spacer are fabricated in a top-down approach, where the heterostructure is designed to reduce contact resistance and thus improve transconductance. In the first attempt, from the electrical characterization, it is concluded that the ON resistance of these MOSFETs is comparable to state-of-the-art HEMTs. Complete non-quasi-static small-signal modeling is performed on these transistors, and the discrepancy in the magnitude of  $f_{max}$  is discussed. InGaAs/InP 3D-nanosheet/nanowire FETs' high-frequency performance is studied by combining intrinsic analytical and extrinsic numerical models to estimate  $f_T/f_{max}$ . 3D vertical stacking results in smaller parasitic capacitances due to electric field perturbance because of screening.

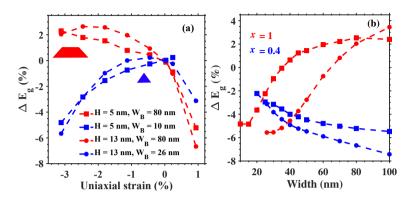

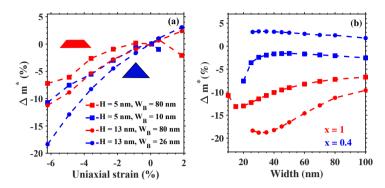

An 8-band  $\mathbf{k} \cdot \mathbf{p}$  model is implemented to calculate the electronic parameters of strained  $\ln_x Ga_{1-x} As/\ln P$  heterostructure-based quantum wells and nanowires. Bandgap, conduction band energy levels, and their effective masses and non-parabolicity factors are studied for various indium compositions and channel dimensions. These calculated parameters are used to model the long channel quantum well  $\ln GaAs$  MOSFET at cryogenic temperatures, and the importance of band tails limiting the subthreshold slope is discussed.

| ingaAs, Nanoelectronics, Kadio Frequency                     |                                      |  |  |

|--------------------------------------------------------------|--------------------------------------|--|--|

| Classification System and/or Index Terms                     | Language:                            |  |  |

| e.g. Electronic Engineering, Nanotechnology                  | English                              |  |  |

| Supplementary Bibliographical Information:  -                | ISBN (printed):<br>978-91-8039-780-3 |  |  |

| Key title and ISSN:                                          | ISBN (digital):                      |  |  |

| Series of Licentiate and Doctoral Theses; 1654-790X, No. 162 | 978-91-8039-779-7                    |  |  |

General Permissions:

G. Naya Svil.

Recipient's Notes:

Keywords:

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature:

Date: 27 September 2023

Number of Pages:

Security Classification: Unclassified Price: -

## Radio Frequency InGaAs MOSFETs

**Doctoral Thesis**

Navya Sri Garigapati

Department of Electrical and Information Technology Lund, September 2023

Navya Sri Garigapati Department of Electrical and Information Technology Lund University Ole Römers Väg 3, 223 63 Lund, Sweden

Series of Licentiate and Doctoral Theses ISSN 1654-790X, No. 162 ISBN 978-91-8039-780-3 (printed) ISBN 978-91-8039-779-7 (digital)

#### © 2023 Navya Sri Garigapati

This thesis is typeset using  $\LaTeX$  with the body text in Palatino and Goudy Initials, headings in Helvetica, text in figures in Arial, and the body text in Appendix B in Computer Modern.

Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

To the teachers, who educate with passion and patience.

### **Abstract**

III-V-based Indium gallium arsenide is a promising channel material for high-frequency applications due to its superior electron mobility property. In this thesis, InGaAs/InP heterostructure radio frequency MOSFETs are designed, fabricated, and characterized. Various spacer technologies, from high dielectric spacers to air spacers, are implemented to reduce parasitic capacitances, and  $f_T/f_{max}$  are evaluated. Three types of RF MOSFETs with different spacer technologies are fabricated in this work.

InP \(\triangle\)-ridge spacers are integrated on InGaAs Nanowire MOSFET in an attempt to decrease parasitic capacitances; however, due to a high-dielectric constant of the spacers and smaller transistors transconductance, the  $f_T/f_{max}$ are limited to 75/100 GHz. InGaAs quantum well MOSFETs with a sacrificial amorphous silicon spacer are fabricated, and they have capacitances of a similar magnitude to other existing high-performing RF InGaAs FETs. An 80 nm InGaAs MOSFET has  $f_T/f_{max} = 243/147$  GHz is demonstrated, and further optimization of the channel and layout would improve the performance. Next, InGaAs MOSFETs with nitride spacer are fabricated in a top-down approach, where the heterostructure is designed to reduce contact resistance and thus improve transconductance. In the first attempt, from the electrical characterization, it is concluded that the ON resistance of these MOSFETs is comparable to state-of-the-art HEMTs. Complete non-quasi-static smallsignal modeling is performed on these transistors, and the discrepancy in the magnitude of  $f_{max}$  is discussed. InGaAs/InP 3D-nanosheet/nanowire FETs' high-frequency performance is studied by combining intrinsic analytical and extrinsic numerical models to estimate  $f_T/f_{max}$ . 3D vertical stacking results

in smaller parasitic capacitances due to electric field perturbance because of screening.

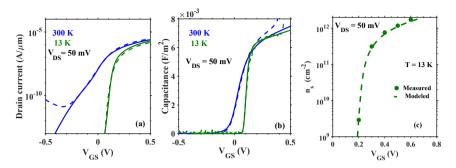

An 8-band  $\mathbf{k} \cdot \mathbf{p}$  model is implemented to calculate the electronic parameters of strained  $\text{In}_x \text{Ga}_{1-x} \text{As}/\text{InP}$  heterostructure-based quantum wells and nanowires. Bandgap, conduction band energy levels, and their effective masses and non-parabolicity factors are studied for various indium compositions and channel dimensions. These calculated parameters are used to model the long channel quantum well InGaAs MOSFET at cryogenic temperatures, and the importance of band tails limiting the subthreshold slope is discussed.

## Popular Science Summary

Imagine a world without smartphones, computers, or modern electronics. Our lives have been drastically transformed due to the great and powerful invention of the transistor. A *transistor* is a tiny device that controls the flow of electricity between two contacts and acts as a switch. It is like the traffic cop of the electronic world, directing the flow of electrical signals. Before transistors existed, electronic devices used bulky vacuum tubes like old-fashioned light bulbs with heated filaments. These tubes were bulky, expensive, and consumed a lot of power. However, in the late 1940s, the invention of the transistor changed everything.

The transistor is incredibly small, and this unique feature made it possible to create compact and lighter electronic devices for our daily lives. Without transistors, the size of a smartphone would be bigger than a brick. Not only did transistors make devices smaller, but they also made them more reliable and efficient. They allowed us to build computers that were faster, smarter, and capable of handling complex tasks. The birth of microprocessors, which are like the brains of computers, was made possible by transistors. These powerful chips can perform billions of calculations in a second, making our modern digital world a reality.

In this work, high-frequency or radio-frequency transistors, the backbone of radio communication, are designed, fabricated, and characterized. These transistors are built using advanced materials and techniques to handle the demanding requirements of high-frequency applications. They are like supercharged versions of regular transistors, capable of operating at frequencies that range from tens of megahertz to several gigahertz. The increase in

maximum operating frequency is attributed to transistor size scaling, mainly the distance the carrier travels between two contact leads. However, over time, due to limited carrier mobility of the channel material, i.e., how fast the carriers move in the channel, and dominant external parasitics, i.e., the outer part of the transistor contributing significant unwanted capacitances and resistances, have started to limit the high-frequency performance.

Indium gallium arsenide (InGaAs) compound semiconductor material is a newly explored material possible to replace Silicon due to its carrier mobility  $\times$ 10 that of the latter, and thus, InGaAs high-frequency transistors can handle higher frequency signal with low power consumption. The next challenge is reducing the external parasitics, which dominate at smaller transistor sizes. The low- $\kappa$  spacer technology is introduced to get smaller parasitic capacitances without degrading resistance. In this work, InGaAs metal oxide semiconductor field effect transistors (MOSFETs) are a type of transistor where the semiconductor channel is separated from the gate metal contact by high-dielectric oxide. Various spacers with a high dielectric constant to the least possible dielectric constant of 1, i.e., an air spacer, are implemented to reduce the external parasitics.

InGaAs nanowire MOSFETs, where the gate is covered on three sides of the channel, and two different quantum well MOSFETs are designed, fabricated, and characterized. The device's electrical characterization includes DC and high-frequency from 10 MHz to 67 GHz using a vector network analyzer. The importance of accurate mathematical modeling of the measured high-frequency data in estimating the  $f_T/f_{max}$  is highlighted. These advancements promise faster data processing, more efficient wireless networks, and exciting possibilities in emerging technologies like 5G, autonomous vehicles, and the Internet of Things (IoT).

## Acknowledgements

I want to express my sincere gratitude and appreciation to all those who have supported and assisted me throughout my doctoral journey, without whom this thesis would not have been possible.

First and foremost, I am deeply indebted to my supervisor, *Prof. Erik Lind*, for his guidance, expertise, and unwavering support. Thank you for giving me this incredible opportunity and believing in me. Your invaluable insights, constructive feedback, and patience have been instrumental in shaping this research and my overall growth as a scholar. I am truly grateful for your mentorship and dedication. I thank my co-supervisors, *Johannes Svensson* and *Mattias Borg*, for their support and guidance. *Prof. Lars Erik Wernersson*, your vision and leadership qualities always inspire me. *Fredrik*, thank you for introducing me to the clean room; you taught me how to hold a tweezer to fabricate the transistor to characterization. Lars and Stefan, thank you for teaching and helping me with the RF measurement set-up. *Lasse* and *Patrik*, thank you for collaboration.

Furthermore, I would like to acknowledge wonderful colleagues, *Gautham*, *Heera*, *Anton*, *Saketh*, *Michael*, *Abinaya*, *Robin*, *Marcus*, *Hannes*, *Andre*, *Louise*, thank you for creating such a learning environment and your all inspiring work. I thank the administrative staff at the Electrical and Information Technology for their support, resource provision, and logistical assistance. I also sincerely thank the NanoLund lab staff for promptly assisting with the tools.

My family, Amma, Nanna, and Annayya, thank you for your unconditional love, understanding, and encouragement throughout this demanding academic journey. To my Srinu brother and Vadina, thank you so much for your support during the difficult times of my academic career, and I am always grateful to you both. To my remaining family, thank you for showering me

with love and care. I am always thankful for having an amazing and loving big family. I look forward to spending more time with you all.

Finally, I thank my dearest Bangu.

Lund, Sept 2023

C. Naya Svi/.

# Contents

| ADSTract                        | V          |

|---------------------------------|------------|

| Popular Science Summary         | vii        |

| Acknowledgements                | ix         |

| Contents                        | xi         |

| Preface                         | xv         |

| Structure of the Thesis         | <br>. xv   |

| Included Papers                 | <br>. xv   |

| Related Work                    | <br>. xvi  |

| Acronyms and Symbols            | xix        |

| Acronyms and Abbreviations      | <br>. xix  |

| Latin Symbols                   |            |

| Greek Symbols                   | <br>. xxiv |

| INTRODUCTION                    | 1          |

| 1 Introduction                  | 3          |

| 1.1 Transistor History          | <br>. 3    |

| 1.1.1 Transistor Scaling        |            |

| 1.2 III-V Channel Material      | <br>. 5    |

| 1.3 Radio Frequency Transistors | <br>. 6    |

| 1.4 Motivation                                                                      | 8  |

|-------------------------------------------------------------------------------------|----|

| 1.5 Thesis Outline                                                                  | 8  |

| 2 k · p Theory                                                                      | 11 |

| 2.1 Schrödinger Equation                                                            | 11 |

| 2.1.1 Envelope Function Approximation (EFA)                                         | 13 |

| $2.2 \mathbf{k} \cdot \mathbf{p}$ Formalism                                         | 14 |

| 2.2.1 Spin-Orbit Coupling (SO)                                                      | 16 |

| 2.2.2 Strain                                                                        | 16 |

| 2.2.3 Hamiltonian of Confined Structures                                            | 18 |

| 2.2.4 Implementation in COMSOL Multiphysics                                         | 19 |

| 3 MOS Theory                                                                        | 23 |

| 3.1 MOSFET Background                                                               | 23 |

| 3.2 MOS Electrostatics                                                              | 25 |

| 3.2.1 Gate Capacitance                                                              | 29 |

| 3.3 MOS Transport                                                                   | 32 |

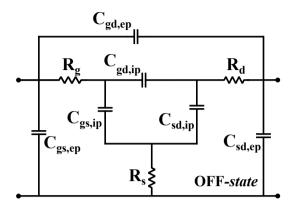

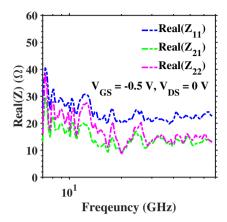

| 3.4 High-frequency Small-signal Characterization                                    | 35 |

| 3.4.1 High-Frequency Small-Signal Model                                             | 36 |

| 3.4.2 Intrinsic Parameter Extraction                                                | 40 |

| 3.4.3 High-Frequency Gains                                                          | 41 |

| 4 MOSFET Fabrication                                                                | 43 |

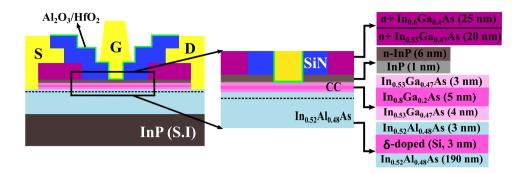

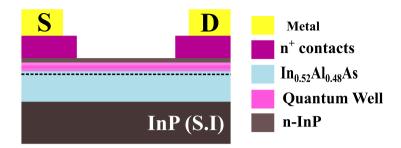

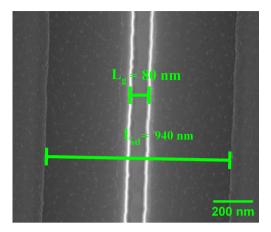

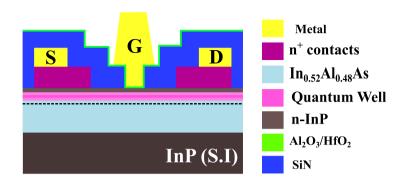

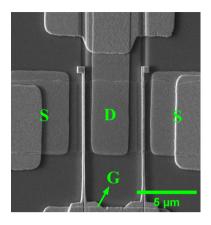

| 4.1 InGaAs Quantum Well MOSFETs with Nitride Spacers                                | 43 |

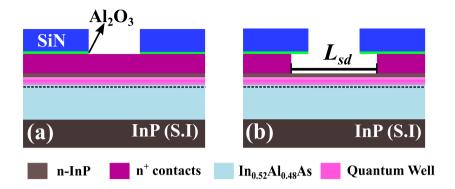

| 4.1.1 MBE Epitaxial Stack                                                           | 43 |

| 4.1.2 n <sup>+</sup> Etch or $L_{sd}$ Definition                                    | 44 |

| 4.1.3 Device Isolation                                                              | 45 |

| 4.1.4 Contacts Metallization                                                        | 45 |

| 4.1.5 Gate Recess Etch Etep-II                                                      | 46 |

| 4.1.6 Gate Contact Formation                                                        | 47 |

| 4.2 InP ∧-ridge Spacer MOSFET Process                                               | 48 |

| 4.3 Sacrificial a:Si Spacer MOSFET Process                                          | 49 |

| 5 Device Characterization                                                           | 53 |

| 5.1 8-band $\mathbf{k} \cdot \mathbf{p}$ Band Structure Simulation Results          | 53 |

| $5.1.1  \text{In}_x  \text{Ga}_{1-x}  \text{As/InP Quantum Well} \dots \dots \dots$ | 53 |

| 512 In Gar As/InP Nanowire                                                          | 54 |

| 5.1.3 Long $L_g$ MOSFET Modeling                                                                             | 56   |

|--------------------------------------------------------------------------------------------------------------|------|

| 5.2 InGaAs Radio Frequency MOSFETs                                                                           | 57   |

| 5.2.1 $In_{0.85}Ga_{0.15}As$ Nanowire MOSFETs with InP $\land$ -ridge Spacers                                | s 57 |

| 5.2.2 In <sub>0.71</sub> Ga <sub>0.29</sub> As/InP Quantum Well MOSFETs with Sacrifi-                        |      |

| cial a:Si Spacers                                                                                            | 58   |

| 5.2.3 InGaAs Composite Channel Quantum Well MOSFET with                                                      |      |

| SiN Spacers                                                                                                  | 62   |

| 5.2.4 High-Frequency Small-Signal Modeling                                                                   | 63   |

| 5.2.5 Benchmarking                                                                                           | 64   |

| 6 Summary and Future Work                                                                                    | 67   |

| 6.1 Summary                                                                                                  | 67   |

| 6.2 Conclusion                                                                                               | 68   |

| 6.3 Future Work                                                                                              | 69   |

| Bibliography                                                                                                 | 71   |

| APPENDICES                                                                                                   | 83   |

| A k · p Theory                                                                                               | 85   |

| B Fabrication Details                                                                                        | 89   |

| b radrication Details                                                                                        | 89   |

| PAPERS                                                                                                       | 95   |

| I Capacitance Scaling in In <sub>0.71</sub> Ga <sub>0.29</sub> As/InP MOSFETs With Self-Aligned a:Si Spacers | 97   |

| II III-V nanowire MOSFETs with novel self-limiting $\land$ -ridge spacers for RF applications                | 105  |

| III Strained $In_xGa_{(1-x)}As/InP$ near surface quantum wells and MOSFETs                                   | 113  |

| IV 8-band $k \cdot p$ modeling of strained $In_xGa_{(1-x)}As/InP$ heterostructure nanowires                  | 123  |

| V RF performance comparison of III-V InAs/InP Quantum well, 3D-Nanosheet/Nanowire MOSFETs                    | 133  |

| VI High-Frequency small-signal modeling of CC Quantum Well InGaAs MOSFETs                                    | 143  |

### **Preface**

This thesis is the culmination of more than five years of work in the *Electromagnetism and Nanoelectronics* group at Lund University and presents detailed studies of very fascinating topics. The work was supervised by Prof. *Erik Lind*.

#### STRUCTURE OF THE THESIS

#### INTRODUCTION

The main body of the thesis consists of the publications appended in the back. The Introduction provides a broader and more comprehensive view than the very focussed publications and ties their work together. The Introduction is intended to be comprehensible for aspiring researchers with a Master's degree in physics or a related subject.

#### APPENDICES

#### A k∙p Theory

Appendix A provides the  $In_xGa_{1-x}As$  and InP material parameters and Hamiltonian parameters used in the  $\mathbf{k} \cdot \mathbf{p}$  model formalism. Also,  $\mathbf{k} \cdot \mathbf{p}$  and strain matrices of bulk and confined structures are given.

#### **B** Fabrication Details

Appendix B provides detail process flow summary of InGaAs quantum well RF MOSFETs with nitride spacers.

#### PAPERS

The papers forming the main body of the thesis are reproduced in the back and listed in the following.

#### LIST OF PUBLICATIONS

The following papers form the main body of this thesis and the respective published or draft versions are appended in the back.

- **Paper I:** N. S. Garigapati, F. Lindelöw, L. Södergren, and E. Lind, "Capacitance Scaling in In<sub>0.71</sub>Ga<sub>0.29</sub>As/InP MOSFETs With Self-Aligned a:Si Spacers", *IEEE Transactions on Electron Devices*, vol. 68, pp. 3762-3767, Aug 2021, doi: 10.1109/TED.2021.3092299.

- ▶ I fabricated the devices, carried out all measurements and analysis and wrote the paper.

- Paper II: F. LINDELÖW, N. S. GARIGAPATI, L. SÖDERGREN, M. BORG AND E. LIND, "III-V nanowire MOSFETs with novel self-limiting ∧-ridge spacers for RF applications", Semiconductor Science and Technology, vol. 35, no. 6, pp. 065015, May. 2020, doi:10.1088/1361-6641/ab8398.

- ▶ I fabricated the devices, participated in measurement, analysis and paper writing.

- **Paper III:** N. S. Garigapati, L. Södergren, P. Olausson, and E. Lind, "Strained  $In_xGa_{(1-x)}As/InP$  near surface quantum wells and MOS-FETs", *Applied Physics Letters*, vol. 120, no. 9, pp. 092105, Feb. 2022, doi:10.1063/5.0073918.

- ▶ I performed all modeling, analysis and wrote the paper.

- **Paper IV:** N. S. Garigapati And E. Lind, "8-band k·p modeling of strained  $In_xGa_{(1-x)}As/InP$  heterostructure nanowires", *Journal of Applied Physics*, vol. 133, no. 1, pp. 015701, Jan. 2023, doi:10.1063/5.0133229.

- ▶ I performed complete modeling, analysis and wrote the paper.

- **Paper V:** N. S. GARIGAPATI AND E. LIND, "RF performance comparison of III-V InAs/InP Quantum Well, 3D-Nanosheet/Nanowire MOSFETs", *IEEE Transactions on Electron Devices*, Aug. 2023, TED-2023-08-2293-R (Under review)

- ▶ I performed complete device design, modeling, analysis and wrote the paper.

- **Paper VI:** N. S. GARIGAPATI AND E. LIND, "High-Frequency small-signal modeling of CC Quantum Well InGaAs MOSFETs", (Manuscript)

- ▶ I desinged, developed the process flow and fabricated the devices, carried out all measurements and data analysis and wrote paper.

#### **RELATED WORK**

The following publications are not included in the thesis but summarised related work I contributed.

#### **JOURNAL PAPERS**

Paper vii: L. SÖDERGREN, N.S. GARIGAPATI, MATTIAS BORG, AND E. LIND, "Mobility of near surface MOVPE grown InGaAs/InP quantum wells", *Applied Physics Letters*, vol. 117, no. 1, pp. 013102, July. 2020, doi: 10.1063/5.0006530.

#### **CONFERENCE CONTRIBUTIONS**

- **Paper viii:** N. S. Garigapati and E. Lind, "Self-aligned InGaAs composite channel MOSFET with  $f_T = 207$  GHz", *Swedish Microwave days*, May. 2023.

- Paper ix: N. S. Garigapati and E. Lind, "Fabrication of Self-aligned Quantum Well InGaAs MOSFETs for High-Frequency Applications", EMRS Spring meeting, May-Jun. 2023.

## Acronyms and Symbols

#### **ACRONYMS AND ABBREVIATIONS**

AC Alternating current

$Al_2O_3$  Aluminum oxide

ALD Atomic layer deposition

BJT Bipolar junction transistor

**BOE** Buffered oxide etch

**CB** Conduction band

**CBO** Conduction band offset

CMOS Complementary metal oxide semiconductor

DC Direct current

**DE** Digital etch

**DG** Dummy gate

**DIW** Deionized water

**DOS** Density of states

**DUT** Device under test

**EBL** Electron beam lithography

**EOT** Effective oxide thickness

FDSOI Fully depleted silicon on insulator

**FET** Field-effect transistor

GAA Gate-all-around

**GaAs** Gallium arsenide

H<sub>2</sub>O<sub>2</sub> Hydrogen peroxide

H<sub>3</sub>PO<sub>4</sub> Phosphoric acid

**HCl** Hydrochloric acid

**HEMT** High-electron-mobility transistor

**HF** Hydrofluoric acid

**HfO**<sub>2</sub> Hafnium dioxide

**hh** Heavy-hole

**HSQ** Hydrogen silsequioxane

ICP Inductively coupled plasma

II Impact ionization

In Indium

**InAlAs** Inidum aluminum arsenide

InAs Indium arsenide

InGaAs Indium gallium arsenide

InP Indium phosphide

IPA Isopropyl alcohol

ITRS International technology roadmap for semiconductors

lh Light-hole

LNA Low noise amplifier

MAG Maximum available gain

MOCVD Metal-organic chemical vapor deposition

MOSFET Metal-oxide-semiconductor field-effect transistor

MOVPE Metalorganic vapor-phase epitaxy

MSG Maximum stable gain

NH<sub>4</sub>S Ammonium sulfide

**NSFET** Nanosheet field effect transistor

NSQ Non-quasi-static

**NWFET** Nanowire field effect transistor

Pd Palladium

PDA Post deposition annealing

PECVD Plasma enhanced chemical vapor deposition

**PMMA** Polymethyl methacrylate

QCL Quantum capacitance limit

**QW** Quantum well

RF Radio frequency

**RIE** Reactive ion etching

S.I Semi-insulating

S/D Source/Drain

**SEM** Scanning electron microscope

Si Silicon

**SiO**<sub>2</sub> Silicon dioxide

Sn Tin

**SOI** Silicon on insulator

**S-parameter** Scattering parameter

SO Spin-orbit

**SPL** Single pixel line

SS Subthreshold swing

Ti Titanium

**TLM** Transfer length method

TMAH Tetramethylammonium hydroxide

TMRR Through-match-reflect-reflect

TRL Through-reflect-line

VB Valence band

VBO Valence band offset

VLSI Very large scale integration

VNA Vector network analyzer

W Tungsten

**Y-parameter** Admittance parameter

**Z-parameter** Impedance parameter

**ZrO**<sub>2</sub> Zirconium oxide

#### **LATIN SYMBOLS**

$C_{xx}$  F, fF/ $\mu$ m Trans capacitances in FET, where x = {S, G,

D}, often normalised by total gate width.

$C_{it}$  F, F cm<sup>-2</sup> Interface trap capacitance

$D_{\rm it}$  cm<sup>-2</sup>eV<sup>-1</sup> Interface trap density

$E_{\rm F}$  eV Fermi energy level

E<sub>g</sub> eV Bandgap

f Hz Frequency

$f_{\rm T}$  Hz Transition frequency

$f_{\text{max}}$  Hz Maximum oscillation frequency

gme S Extrinsic transconductance

| $g_{de}$               | S                  | Extrinsic output conductance                                           |  |

|------------------------|--------------------|------------------------------------------------------------------------|--|

| $g_{ m mi}$            | S                  | Intrinsic transconductance                                             |  |

| <i>g</i> <sub>di</sub> | S                  | Intrinsic output conductance                                           |  |

| ħ                      | Js                 | Reduced Planck constant and $\approx 1.055 \times 10^{-34} \text{ Js}$ |  |

| h                      | Js                 | Planck constant and $\approx 6.626 \times 10^{-34} \ \text{Js}$        |  |

| h <sub>21</sub>        | dB                 | Current gain                                                           |  |

| $I_{\mathrm{D}}$       | A, $mA \mu m^{-1}$ | Drain Current, often normalised by the gate width                      |  |

| $I_{\mathrm{DS}}$      | A, $mA \mu m^{-1}$ | Drain-to-Source current, often normalised by the gate width            |  |

| $I_{G}$                | A, $mA \mu m^{-1}$ | Gate current, often normalised by the gate width                       |  |

| $I_{S}$                | A, $mA \mu m^{-1}$ | Source current, often normalised by the gate width                     |  |

| $k_{\rm B}$            | J/K                | Boltzmann constant and $\approx 1.381 \times 10^{-23} \ J/K$           |  |

| k                      | $\mathrm{m}^{-1}$  | Wave vector                                                            |  |

| K                      |                    | Stability factor                                                       |  |

| $L_{G}$                | m                  | Gate length                                                            |  |

| $m_0$                  |                    | $\approx 9.109 \times 10^{-31}$ kg, Electron rest mass                 |  |

| m*                     | $m_0$              | Effective mass                                                         |  |

| $N_d$                  | $\mathrm{cm}^{-3}$ | Donor doping density                                                   |  |

| q                      | С                  | $\approx 1.602 \times 10^{-19}$ C, Elemental charge                    |  |

| T                      | K or °C            | Temperature                                                            |  |

| U                      | dB                 | Mason's unilateral power gain                                          |  |

| $V_{\mathrm{DS}}$      | V                  | Drain-to-Source voltage                                                |  |

| $V_{\mathrm{GD}}$      | V                  | Gate-to-Drain voltage                                                  |  |

$V_{

m GS}$  V Gate-to-Source voltage  $V_{

m T}$  V Threshold voltage x Indium composition

#### **GREEK SYMBOLS**

$eV^{-1}$ Nonparabolicity factor α relative permitivitty  $\varepsilon_r$ Free space permitivitty and  $\approx$  8.85  $\times$  $\varepsilon_0$ F/m  $10^{-12} \, \text{F/m}$ Center of the first Brillouin zone Γ Natural length  $\lambda_n$ m Average mean free path  $\lambda_{MF}$ m  $m^2/Vs$ Electron/hole mobility  $\mu_{e/h}$  $\rm rads^{-1}$ Angular frequency  $\rm rads^{-1}$ Angular trap cut-off frequency  $\omega_0$ Eigenstate φ  $\Psi_s$ eV Surface potential

Poisson's ratio

$\sigma$

# **INTRODUCTION**

## Introduction

This chapter discusses the history of transistor invention and how transistor size scaling has shaped the electronics industry. Various radio frequency transistors are introduced, which are the fundamental components for today's mmWave applications like high-speed mobile networks, data transfer, and high-performance radar. The motivation for this thesis work and thesis outline are discussed at the end of this chapter.

#### 1.1 TRANSISTOR HISTORY

Vacuum tubes were one of the earliest electronic devices, where the electric charge is transported between the filament and charged plate in a vacuum. They saw rapid development and applications in various fields, like signal amplification and modulation, computing, and radio broadcasting, to name a few [1]. However, they had several drawbacks because of their large size and significant power consumption. The invention of the 3-terminal device called transistor in the late 1940s marked a significant advancement in electronic technology. The first point-contact transistor was invented at Bell Labs by John Bardeen, Walter Brattin, and William Shockley 1948 [2] for which the three were awarded the Nobel prize later in 1956. The transistor is a 3-terminal device, where the third terminal controls the current flow between the other two terminals. Transistors were smaller, more reliable, and consumed less power than vacuum tubes. They later became the fundamental building blocks of modern electronic devices, including computers, smartphones, televisions, and countless other technologies. They have a vital impact on the progression of technology and the formation of our contemporary world.

The development of integrated circuits (ICs), which combine multiple transistors, resistors, and capacitors on a single semiconductor chip, revolutionized the miniaturization and increased functionality of electronic systems. In 1960s, metal-oxide-semiconductor field-effect transistors (MOSFETs) were introduced, offering improved performance, lower power consumption, and compatibility with integrated circuits. Complementary metal-oxidesemiconductor (CMOS) technology, which uses both p-type and n-type MOS-FETs, emerged as the dominant design for integrated circuits due to its low power consumption and high noise immunity. Since then, transistors have continued evolving, becoming smaller, faster, and more efficient. CMOS technology has become more powerful by integrating them with real-world interaction. New exciting applications in radio-frequency, power, sensors, and photonics have emerged, and the performance demands of these types of transistors differ from logic devices. The International technology roadmap for semiconductors (ITRS) [3] has released a white paper discussing the performance requirements and naming it as more than Moore demands.

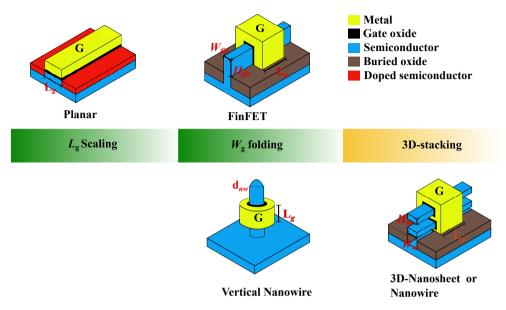

#### 1.1.1 TRANSISTOR SCALING

Moore's law [4] has been a driving force for the electronic industry; by this law, the transistor density on a semiconductor chip doubles every two years. This law is realized by decreasing the device area by 50%, i.e., gate length and width are decreased by  $\times 0.7$ . Figure 1.1 illustrates the transistor geometries that kept the transistor scaling alive over the last 50 years and plausible future novel device geometries that would extend Moore's law. Dennard scaling [5] sets the transistor scaling based on constant field scaling, where the drive voltage, oxide thickness, and channel dimensions are scaled equally to improve electrical performance and maintain constant power density. Advancement in manufacturing tools, mainly lithography, has helped in decreasing the transistor's feature size, or in other words, process node, as per the industry standard. This process node number has been more or less the same as the gate length, which is the smallest feature size of MOSFET. Chip density has doubled in each generation by halving gate length, and more processors are made in the same chip area, which works faster due to minor RC delay. In the early 2000s, devices entered power constrained regime, where power density increased to 100 W/cm<sup>2</sup> [6], and more effort in the system-level design was advised. Also, further scaling the gate length below 30 nm, transistor behavior is lost due to strong short channel effects (SCE), and this has encouraged the researchers to look for new device architectures and channel materials.

As a continuation of Moore's law, chip density can be increased by width folding even at more considerable gate lengths, as demonstrated in FinFET 22 nm technology [7], where the decoupling between the gate length and

process node has started. FinFETs have excellent electrostatics due to tri-gate architecture and a larger effective width for a small physical footprint. At smaller gate lengths, very high aspect ratio fins are required; for example, for a gate length of 6 nm, required fin height and width are 65 and 6 nm, respectively [8], and realizing taller fins have their process difficulties. Recently, gate-all-around (GAA) stacked nanosheet or nanowire FETs have been proposed, and IBM was able to realize a 2 nm technology node with nanosheet transistors [9]. Nanosheet transistors with vertical stacking have a larger effective width and drive current; the latter is not limited by the device footprint, unlike FinFETs. In addition to this, they also have excellent gate electrostatics due to the GAA gate structure. Nanowire transistors are similar to nanosheet transistors; however, drive current is limited due to smaller channel dimensions. Nanosheets and nanowires are slightly different; in the former, the width is more than ×2 the thickness, whereas, in nanowires, the width and thickness are comparable. Even in GAA transistors, short channel effects emerge if the ratio between channel length and width is less than 5 [8]. Another GAA transistor geometry is the vertical nanowire transistors, where the device footprint and gate length are decoupled, and gate length is not limited by standard lithography but by the spacer thickness.

Vertical stacking technique has been used in flash memories [10] and has not been implemented for logic applications. Stacking different layers is one of the alternatives to increase the chip density and regain Moore's law. Another alternative approach for device improvement is changing the channel material with high mobility material, like strained Si or indium-rich InGaAs, where higher drive currents are realized with smaller drive voltages.

#### 1.2 III-V CHANNEL MATERIAL

An alternate approach is to switch to larger mobility channel materials, which would deliver higher current density at smaller operating voltages. III-V materials have a wide range of applications due to their direct bandgap nature and superior high electron mobility, such as optoelectronic devices like lasers, LEDs, high-speed wireless networks, and high-frequency radar, to name a few [11]. III-V-based InGaAs as n-channel transistors have electron mobility higher than 10,000 cm<sup>2</sup>/V-s in sub-100 nm regime [12]. InGaAs-based planar and nonplanar MOSFETs have exhibited record transconductance and > 3 mS/ $\mu$ m [13–15]. Unlike Si, III-V-based InGaAs material does not have defect-free native oxide, thus limiting achieving the ideal minimum subthreshold swing ( $SS_{min}$ ). A remarkable effort is put into the high permittivity gate oxides, which exhibited the same order of interface trap density as that of Si/SiO<sub>2</sub> [16,17].

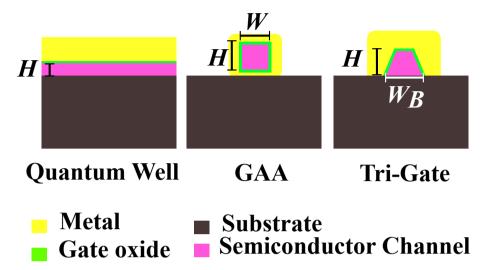

**Figure 1.1:** Transformation of transistor configurations caused by the scaling of transistor dimensions.

#### 1.3 RADIO FREQUENCY TRANSISTORS

Radio frequency (RF) devices are the ones that operate in the frequency range of 3 kHz to 300 GHz. They have applications ranging from new-generation cellular networks (e.g., 5G and 6G) to long-range Wi-Fi networks and from global positioning systems to high-frequency radar and automotive sensing, to name a few [18,19]. The development of radio frequency devices has come a long way from the Germanium bipolar transistor operating at a frequency of 1 GHz back in 1958 to III-V-based high-electron-mobility transistors (HEMTs) with oscillation frequency greater than 1 THz [20,21]. The prominent figure of metrics of high-frequency performance is transition frequency  $(f_T)$ , where the current gain of the device is 1, and maximum oscillation frequency  $(f_{max})$ , where the maximum available gain (MAG) of the device is unity or 0 dB. Another important small-signal and high-frequency metric of the transistor is the minimum noise figure  $(NF_{min})$ , which is the minimum noise of the transistor for the optimized source impedance. Output power  $(P_{out})$  is the transistor's power handling capacity at high frequencies or the frequency of interest. The output power requirements are well diversified, ranging from a few mW in the case of Bluetooth to 100's of W in power base stations [8]. RF transistor performance requirements depend on the interested mmWave application; hence, transistor technology has become application-specific.

III-V-based HEMTs are one of the industry standards for radio frequency devices because of their superior electrical and high-frequency performance with  $f_T > 650$  GHz [22, 23]. The epitaxial structure of HEMT involves a wide bandgap barrier layer with delta doping in contact with the narrow bandgap channel, leading to higher channel carrier mobility and, hence, transconductance. The wide bandgap barrier, which separates the gate contact from the channel, should be scaled down as the gate length scales to maintain the gate electrostatics, which resulted in significant gate-leakage under sub-100 nm gate length devices [24]. Another challenge is the dominant parasitic capacitance for gate length less than 30 nm [23] and larger source resistance [22], which requires optimization of epitaxial layers in the contact stack.

In the early 2000's, the RF performance of Si MOSFETs has been enhanced considerably. They have delivered  $f_T$  of 445 GHz with 32 nm gate length [25], given their smaller electron mobility, the larger density of states, and larger parasitic capacitance due to their closely spaced highly doped contacts. Fully depleted silicon on insulator (FDSOI), where the Si channel is placed on buried oxide, has also exhibited promising RF figure of metrics, with  $f_T$  and  $f_{max}$  of 375 and 290 GHz in 22 nm technology [26]. FDSOI FETs would have smaller parasitic capacitances than planar Si MOSFET due to buried oxide. Theoretical RF performance assessment of 28 nm UTBB FDSOI MOSFETs is presented in [27], and the effect of parasitic capacitances is discussed mainly.

Non-planar device technologies like tri-gate FinFETs have high intrinsic gain due to excellent gate electrostatics. Fin height and spacing between the fins are optimized for better high-frequency performance. Si 14 nm FinFET technology has delivered  $f_T$  over 250 GHz at lower gate overdrive voltage [28] and  $f_T$  = 314 GHz [29]. However, taller and thinner fins are demanded for sub-10 nm technology, where mobility is degraded due to surface scattering, and taller fins would increase the parasitic capacitance.

III-V-based lateral and vertical nanowires have drawn attention with their larger transconductance and excellent gate control over the channel. Lateral nanowire MOSFETs have reported  $f_{max}$  of 400 GHz [30] and vertical nanowire MOSFETs [31] have exhibited  $f_T$  and  $f_{max}$  both over 140 GHz, where optimization of the gate contact and spacer thickness could improve high-frequency performance.

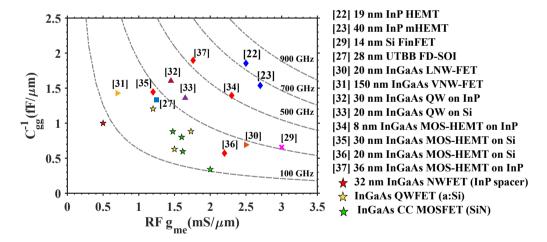

Finally, we have III-V-based InGaAs MOSFETs, which manifested similar transconductance as that of HEMTs, and, however, poor RF metrics compared to the latter due to large parasitic capacitances. InGaAs quantum well MOSFET on InP has exhibited  $f_T/f_{max} = 357/410$  GHz [32] and 20 nm InGaAs MOSFET on Si has exhibited record  $f_T/f_{max} = 370/310$  GHz [33]. However, these FETs' parasitic capacitance is larger than HEMTs, and efficient spacer designs must be investigated to optimize and improve high-

frequency performance. III-V-based MOS-HEMTs, which inherit the HEMTs heterostructure design to provide high-mobility and high- $\kappa$  gate oxide from MOSFETs to decrease gate leakage current, have exhibited excellent high-frequency metrics [34–36]. In [37], In<sub>0.8</sub>Ga<sub>0.2</sub>As MOS-HEMT with gate length,  $L_g = 36$  nm has exhibited  $f_{max} > 1$  THz.

#### 1.4 MOTIVATION

From the earlier discussion on FET-based transistors for high-frequency applications, it can be concluded that parasitic capacitance and resistances are limiting factors, and the trade-off between these two parameters made the problem even more challenging. A low- $\kappa$  dielectrics (ideally, air spacer) spacer introduction into the device design without a substantial increase in resistance is the main goal in designing the RF FETs. In this work, InGaAs/InP heterostructure-based quantum confined 1D nanowires and 2D quantum well FETs are designed, fabricated, characterized, and modeled. MOSFETs are fabricated from the bottom-up approach, where the channel and highly doped contacts are selectively regrown, and in the top-down approach, where the epitaxial layers are etched down to define the device. Various spacers like delta-doped InP  $\wedge$ -ridge spacers, a:Si, and nitride spacers are used to reduce parasitic capacitances. The main goal is to realize a spacer technology to achieve parasitics similar to HEMTs and improve the high-frequency metrics, mainly  $f_T/f_{max}$ .

#### 1.5 THESIS OUTLINE

The introduction chapter provides a brief transistor evolution history and challenges to regain Moore's law. Various radio frequency transistors overview and their challenges are discussed in brief, and ended the discussion with the motivation for the thesis work.

In Chapter 2, an introduction to 8-band  $\mathbf{k} \cdot \mathbf{p}$  theory is given, starting from the stationary Schrödinger equation and  $\mathbf{k} \cdot \mathbf{p}$  matrix formation. Spin-orbit and strain matrices for bulk semiconductors are defined. Envelope function approximation explains how the bulk Hamiltonian matrices are modified for confined structures like  $\text{In}_x \text{Ga}_{1-x} \text{As}/\text{InP 2D}$  quantum well and 1D nanowires. At this chapter's end, the discussion focuses on implementing  $\mathbf{k} \cdot \mathbf{p}$  in the COMSOL Multiphysics FEM solver. Papers III and IV summarise the results on electronic parameters behavior of strained heterostructure quantum well and nanowire structures, respectively.

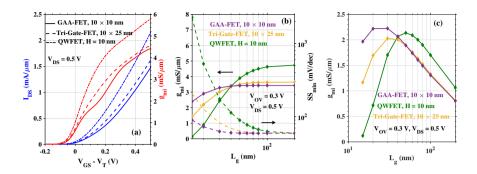

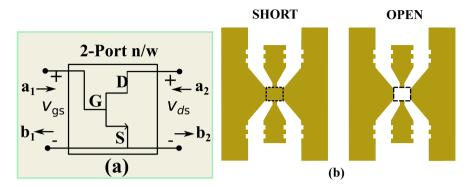

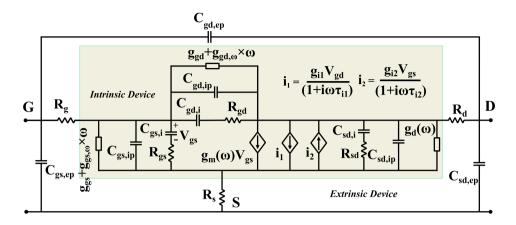

In Chapter 3, MOSFET DC and the high-frequency small-signal model are discussed in detail. The electrical performance of InGaAs/InP heterostructure-based planar, tri-gate nanowire, and gate-all-around FETs are modeled using the top-of-the-barrier model in combination with the Landauer model. FET high-frequency small-signal model, including impact ionization, band-to-band tunneling, and high-κ gate oxide loss, is presented, and extrinsic and intrinsic parameter extraction is explained. Various high-frequency gains, like unity power gain, maximum available gain, and maximum stable gain, are discussed in detail at the end of this chapter. The discussed transistor model is used to design the 3D-vertically stacked horizontal nanosheet/nanowire MOSFETs, and their RF metrics are estimated. Paper V summarises the results on InAs/InP 3D nanosheet/nanowire FETs RF performance.

In Chapter 4, the main fabrication steps in realizing the RF MOSFET are discussed, and various RF MOSFET process designs implemented in this work are presented in brief.

Chapter 5 discusses the electronic parameter behavior of  $In_xGa_{1-x}As/InP$  quantum well and nanowire and long channel quantum well MOSFET I-V and C-V modeling. This is followed by the discussion on the high-frequency characterization of various RF MOSFETs designed and implemented in this thesis work. Paper I, II, and VI details the various RF MOSFETs realized in this work.

A summary of the thesis work, followed by the potential future continuation of the presented work, is given in Chapter 6.

Appendix A presents 8-band  $\mathbf{k} \cdot \mathbf{p}$  and strain Hamiltonian matrices of bulk and confined structures. Also,  $\operatorname{In}_x \operatorname{Ga}_{1-x} \operatorname{As}$  and  $\operatorname{InP}$  material parameters and Hamiltonian parameters expressions are provided.

In Appendix B, fabrication details of the InGaAs quantum well MOSFET with nitride spacer are given in more detail.

# **k** ⋅ **p** Theory

A comprehensive understanding of the confined channel electronic parameters, like conduction band subband energies, effective masses, and non-parabolicity factors, is necessary for precise transistor modeling. Additionally, the employed theoretical modeling helps to provide insights into the experimental data. This chapter presents a detailed 8-band  $\mathbf{k} \cdot \mathbf{p}$  model to calculate the strained heterostructure electronic parameters. The implementation of the developed model in the COMSOL Multiphysics FEM solver and results, including insights into the inhomogeneous strain distribution in the 1D nanowire, is presented in the end. This  $\mathbf{k} \cdot \mathbf{p}$  model is inspired from [38], and more details can be found there.

#### 2.1 SCHRÖDINGER EQUATION

In the realm of nanometer-scale semiconductors, quantum mechanics takes precedence as it governs the evolution of quantum states within the system, delineated by the single particle real space time-dependent Schrödinger equation,

$$\left(-\frac{\hbar^2}{2m}\nabla^2 + V(r,t)\right)\psi(r,t) = i\hbar\frac{\partial\psi(r,t)}{\partial t}$$

(2.1)

Where m is the particle mass,  $\hbar$  is the reduced Planck constant, r is the position vector, t is time, V(r,t) is the potential energy.  $\psi(r,t)$  corresponds to the wave function of system. The term in the bracket in the above equation (2.1) is known as the Hamiltonian of the system, which constitutes the system's kinetic and potential energy. Solving this equation is not straightforward and

involves assumptions valid in crystalline semiconductors. First, stationary crystal potential is assumed, resulting in time and position-dependent solutions, i.e.,  $\psi(r,t) = \phi(r)\zeta(t)$ . The time-dependent Schrödinger equation becomes,

$$\frac{1}{\phi(r)} \left( -\frac{\hbar^2}{2m} \nabla^2 + V(r) \right) \phi(r) = \frac{1}{\zeta(t)} i\hbar \frac{\partial \zeta(t)}{\partial t}$$

(2.2)

This solution is divided into two eigenvalue problems with the same eigenvalue, *E*. The two equations are as follows,

$$\left(-\frac{\hbar^2}{2m}\nabla^2 + V(r)\right)\phi(r) = E\phi(r) \tag{2.3}$$

$$i\hbar \frac{\partial \zeta(t)}{\partial t} = E\zeta(t) \tag{2.4}$$

The equation (2.3) is famously known as the stationary Schrödinger equation and also the so-called eigenvalue problem for the Hamiltonian, where  $\phi(r)$  is the eigenstate with the eigenvalue corresponding to energy, E. The equation (2.4) describes the temporal evolution of the state, and the solution is harmonic and E dependent. This work mainly focuses on solving the stationary Schrödinger equation for bulk and confined structures. Hamiltonian incorporates every electron's energy and their interactions, making it complex and requiring additional assumptions for solutions. The adiabatic approximation allows us to consider a stationary ion core, and thus, electrons in the outer shell experience a stationary potential due to the core. All electrons are assumed to experience the same average potential defined by mean-field theory. In equation (2.3), the potential energy term, V(r) contains the lattice periodic potential due to the crystalline nature of semiconductors,  $V_{cr}(r)$  and also any external applied electric field,  $V_{ex}(r)$ .

Translation symmetry invariance in the crystalline semiconductors leads to the Bloch theorem, which provides the solution to the stationary Schrödinger equation. There exist many solutions for equation (2.3), and they are identified by index, n, and are given by

$$\phi_n(r) = \frac{1}{\sqrt{\Omega_v}} e^{i\mathbf{k}\cdot r} u_{nk}(r)$$

(2.5)

Where  $\phi_n(r)$  is the so-called Bloch function of the  $n^{th}$  state with a wave vector **k** in reciprocal space and normalized to the unit cell volume,  $\Omega_v$ , and  $u_{nk}(r)$ , is the lattice-periodic function having the same periodicity as the lattice potential. So, the solution of the system is periodic and enveloped by a plane

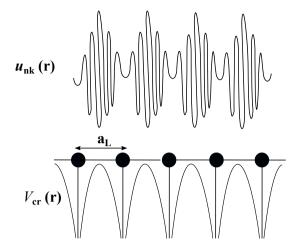

**Figure 2.1:** A 1D crystalline semiconductor with lattice constant,  $a_L$ , and illustration of its periodic crystal potential and the Bloch wave function.

wave with wave vector  $\mathbf{k}$ . The energies that are calculated for every  $\mathbf{k}$  in the reciprocal space form bands, which is the band structure  $E_n(k)$  of the system, which is periodic; hence the discussion is limited to the primitive cell in the reciprocal space, or the first Brillouin zone (BZ) [39]. Figure 2.1 illustrates the periodic crystal potential and block wave function of a 1D semiconductor with lattice constant,  $a_L$ .

#### 2.1.1 ENVELOPE FUNCTION APPROXIMATION (EFA)

In confined structures, such as quantum wells and nanowires, the translational symmetry breaks, and the wave function is not a plane wave anymore in the confined direction. In a case where the structure is confined in r direction and is free in z direction, the Bloch wavefunction is scaled by slowly varying envelop function  $\xi_{nk,m}(r)$ . The modified wave function, in general, is given by [40],

$$\phi_{nk}(r,z) = \sum_{m} e^{i\mathbf{k}\cdot z} u_m(r) \xi_{nk,m}(r)$$

(2.6)

The crystal momentum,  $\hbar \mathbf{k}$ , is no longer continuous in the confined direction and is quantized due to boundary conditions. Thus, the bands are split in a confined direction and form what are known as subbands. The crystal momentum is replaced with its momentum operator,  $\hat{p} = -i\hbar \nabla_r$ , where  $\nabla_r$  is defined in the confined r direction. The wave vector becomes an operator [41],

$\hat{\mathbf{k_r}}$

$$k_r \to \hat{\mathbf{k_r}} = -i\frac{\partial}{\partial r}$$

(2.7)

The Hamiltonian problem after applying the envelop function approximation becomes,

$$H\xi(r) = E\xi(r) \tag{2.8}$$

Assuming that the lattice constant is smaller than the confined dimension, the spatial probabilistic distribution of the states in the confined direction is given by  $|\xi_{n,k}(r)|^2 = \xi_{n,k}(r).\xi_{n,k}^*(r)$ . From here on, we will discuss the wave function referring to the envelope function.

#### 2.2 K · P FORMALISM

Solving for the  $E_n(k)$  involves many assumptions and approximations, and there are proposed models from simple, effective mass approximation to fully atomistic models. It is always a compromise in choosing the model in terms of complexity, accuracy, and computational cost. This theory was first developed by [42,43].  $\mathbf{k} \cdot \mathbf{p}$  theory is a continuum model with the advantages of including additional symmetry-breaking perturbations such as strain and spin-orbit coupling (SO) and empirically adjusting the parameters to obtain accurate and spurious-free solutions. This theory follows the envelope function approximation to extend the model for nanostructures. It also has a few drawbacks, like the expected decrease in the model's accuracy far from the high symmetry point in the reciprocal space and the complexity of the Hamiltonian for nanostructures. Nevertheless, it has been implemented in many numerical tools to calculate band structure [44–47]. In [48], the band structure analytical expressions are developed using symmetry and experimental data to get high-precision electronic parameter estimation around the  $\Gamma$ -point.

The model formalism starts with substituting the Bloch wave function equation (2.5) into the stationary Schrödinger equation (2.3) and introducing the momentum operator. The stationary Schrödinger equation becomes,

$$\left(\frac{\hat{p}^2}{2m_0} + V(r) + \frac{\hbar}{m_0} \mathbf{k} \cdot \hat{\mathbf{p}}\right) u_{nk}(r) = \left(E_n(k) - \frac{\hbar^2 \mathbf{k}^2}{2m_0}\right) u_{nk}(r) \tag{2.9}$$

Where the unperturbed Hamiltonian,  $H_0$ , is

$$H_0 = \frac{\hat{p}^2}{2m_0} + V(r) \tag{2.10}$$

and the Hamiltonian of the perturbation,  $H_1$ , is

$$H_1 = \frac{\hbar}{m_0} \mathbf{k} \cdot \hat{\mathbf{p}} \tag{2.11}$$

$\mathbf{k} \cdot \mathbf{p}$  term in the Hamiltonian is why this theory is named  $\mathbf{k} \cdot \mathbf{p}$  theory. Using perturbation theory, equation (2.9) can be solved easily. According to this theory, the solution to the perturbed system close to the  $\mathbf{k}_0$  is calculated with high accuracy with the known solution of the unperturbed system at  $\mathbf{k}_0$ . Assuming non-degenerate condition, applying second-order perturbation theory, and performing additional simplifications, the eigenvalue of the total perturbed system becomes,

$$E_n(k) = E_{n0} + \frac{\hbar^2 \mathbf{k}^2}{2m_0} + \sum_{m \neq n} \frac{|\mathbf{k} \cdot p_{mn}|^2}{E_{m0} - E_{n0}}$$

(2.12)

Where the momentum matrix element

$$p_{mn} = \langle u_{m0} | \hat{p} | u_{n0} \rangle \tag{2.13}$$

The next step is to choose the basis of the Hamiltonian, which decides how many bands should be considered in modeling the band structure around the symmetry point. In III-V direct narrow bandgap semiconductors, coupling between the remote conduction and valence bands is strong. CB and three VBs are considered in calculating the eigenvalues of the total Hamiltonian, and the interaction with the remaining states is neglected. The conduction band is composed by s-type states,  $|S\rangle$  and valence band has 3 p-type states,  $|p_x\rangle$ ,  $|p_y\rangle$ , and  $|p_z\rangle$ . The spin is ignored for now. The complete derivation of the unperturbed  $\mathbf{k} \cdot \mathbf{p}$  Hamiltonian of bulk semiconductor considering four bands can be found in [38], and this Hamiltonian matrix,  $H_{kp,4}$ is given in Appendix A. The diagonal elements account for the coupling of states with themselves, and the off-diagonal elements account for the coupling among them.  $E_c$  is the conduction band energy, and  $E_v'$  is the valence band energy without spin-orbit (SO) coupling.  $k_x$ ,  $k_y$  and  $k_z$  are the wave vectors in x, y and z direction. Table A.2 in Appendix A summarises Hamiltonian parameter expression in detail.  $A_c$  is related to the curvature of the band structure with remote states coupling included. The interband momentum parameter, P, contains the coupling between the s and 3 p-type states. The three more parameters L, M, N define the valence band states evolution from the unperturbed coupled states. Finally, considering the spin of the states will extend the  $4\times4$  Hamiltonian matrix to  $8\times8$  matrix,

$$H_{kp,8} = \begin{bmatrix} H_{kp,4} & 0\\ 0 & H_{kp,4} \end{bmatrix}$$

(2.14)

## 2.2.1 SPIN-ORBIT COUPLING (SO)

The spin-orbit interaction arises due to the spin and angular moment coupling, which contributes to the system's total energy. The narrow bandgap semiconductors exhibit strong spin-orbit coupling, which must be considered while calculating the band structure at the conduction band minima. The Hamiltonian for spin-orbit coupling is taken from [38].

$\Delta_{so}$  is the spin-orbit splitting parameter, an intrinsic material property. The SO perturbation lifts the 6-fold degeneracy at the valence band maxima into 4-fold degeneracy and 2-fold degeneracy separated by  $\Delta_{so}$ .

#### **2.2.2 STRAIN**

The lattice mismatch between the grown epitaxial layer and substrate results in deformation in the grown layer and leads to strain. The linear relationship between strain ( $\epsilon$ ) and stress ( $\sigma$ ) is given by Hooke's law [49], and the proportionality constant is called the elastic stiffness tensor. The elastic stiffness tensor for cubic semiconductors is given by,

$$D = \begin{bmatrix} C_{11} & C_{12} & C_{12} & 0 & 0 & 0 \\ C_{12} & C_{11} & C_{12} & 0 & 0 & 0 \\ C_{12} & C_{12} & C_{11} & 0 & 0 & 0 \\ 0 & 0 & 0 & C_{44} & 0 & 0 \\ 0 & 0 & 0 & 0 & C_{44} & 0 \\ 0 & 0 & 0 & 0 & 0 & C_{44} \end{bmatrix}$$

(2.16)

The  $C_{ij}$  is the stiffness coefficient. Due to the translation symmetry nature of the crystalline semiconductor, most of the elements in D matrix are zero, and only three nonzero independent coefficients ( $C_{11}$ ,  $C_{12}$ ,  $C_{44}$ ) exist. Bardeen introduced the deformation potential theory, which was later developed by

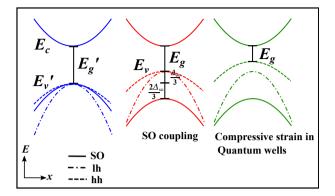

**Figure 2.2:** From left to right: a simple direct bandgap semiconductor band structure and the SO coupling reduces the 6-fold VB degeneracy to 4-fold degeneracy by pushing the spin-orbit (SO) band down in energy. The light-hole (lh) and heavy-hole (hh) degeneracy are removed when strain is included. For example, in compressively strained quantum wells, hh is pushed higher in energy than lh, and the opposite in the case of tensile strain.

Herring [50,51], and the same is used to define the strain interaction matrix. The coupling between CB and VB contains a shear strain component, which is quite small and can be neglected and considered only the term containing wave vector. The strain matrix for 3D bulk material,  $H_{st,4}$ , and parameter expressions are given in Appendix A. The strain coefficients are (l, m, n) and  $a_c$  is the deformation potential. Here, as well, including the spin of the states results in  $8\times8$  strain matrix,

$$H_{st} = \begin{bmatrix} H_{st,4} & 0\\ 0 & H_{st,4} \end{bmatrix}$$

(2.17)

The total  $\mathbf{k} \cdot \mathbf{p}$  Hamiltonian matrices, including the spin-orbit coupling and strain for 3D bulk, are given in Appendix A. Figure 2.2 illustrates the effect of strain and SO coupling on the valence bands and bandgap. The behavior of various valence bands with strain becomes very complex, and the main focus here is to discuss conduction band properties. The  $E_v = E_v' + \frac{\Delta_{so}}{3}$ , where  $E_v = E_c - E_g$  and  $E_g$  is the semiconductor bandgap.

The strain matrix elements are all the same for quantum well and nanowires except for strain tensor elements. In quantum wells, the strain in the epitaxial layer is homogeneous, and tensor element calculation is straightforward. In quantum wells,  $\epsilon_{21} = 0$ ,  $\epsilon_{12} = 0$ ,  $\epsilon_{11} = \epsilon_{22} = f$ ,  $\epsilon_{33} = -\frac{C_{12}}{C_{11}}f$ , where f is the lattice misfit between the epitaxial layer and substrate. The lattice mismatch is defined as  $f = \frac{a_L - a_S}{a_S}$ , where  $a_L$  and  $a_S$  are lattice constants of the epitaxial

layer and substrate. In heterostructure nanowires, calculating the tensor elements becomes intricate because of inhomogeneous strain distribution and complex geometry.

#### 2.2.3 HAMILTONIAN OF CONFINED STRUCTURES

Now that the Hamiltonian of the bulk semiconductors is discussed, this subsection presents the transformation of this Hamiltonian for confined nanostructures. Following the EFA, the wave vector,  $k_r$  in the confined direction, is replaced by its respective momentum operator,  $\hat{\mathbf{k}}_r$ . This transformation results in Hamiltonian with the first and second-order operator terms. The second-order operator ordering concerns the model's numerical stability, mainly spurious solutions. The Burt-Foreman formalism [52] is widely used in the appropriate operator ordering, which maintains the hermiticity of the Hamiltonian. For example, the *s*-type states coupling term is rewritten as,

$$A_c k_r^2 = k_r A_c k_r \tag{2.18}$$

In the same way, Burt-Foreman summarization is used in ordering the p-type coupling term. The parameter N is divided into  $N_+$  and  $N_-$ , obtained from the remaining two parameters, M and L. For example, the term

$$Nk_x k_y = k_x N_+ k_y + k_y N_- k_x (2.19)$$

Appendix A discusses the modified Hamiltonian matrices for quantum wells and nanowires in more detail. The Hamiltonian transforms into the partial differential equation system in quantum-confined structures after replacing the wave vector with the momentum operator.

#### **ELIMINATING SPURIOUS SOLUTIONS**

In numerical modeling, it is necessary to eliminate spurious solutions. They account for the odd behavior of CB and VB energy levels and forbidden energy levels in the bandgap. A few ways of eliminating the spurious solutions are putting constraints on input parameters to the model or simply discarding the unwanted solutions. It was argued in [38] that the wrong selection of parameters is the reason for spurious solutions and not the choice of mathematical modeling. It is proposed that the main motive is to preserve the ellipticity of the  $\mathbf{k} \cdot \mathbf{p}$  operators to get real eigenvalues. In [53], the operator's ellipticity is assured if the following parameter constraints are satisfied.

$$A_c > 0, M - N_- < 0, M + N_- < 0, L - N_- < 0, L + 2N_+ < 0$$

(2.20)

$E_P$ , the optical energy parameter is generally used to fit the experimental data, and it can be varied to satisfy the constraints described in equation (2.20). The momentum interband matrix element P is set by  $E_P$ , and the relation is given by

$$E_P = \frac{2m_0}{\hbar^2} P^2 \tag{2.21}$$

The renormalization of other parameters is necessary to produce accurate, effective mass even at reduced  $E_P$  values. The  $E_P$  value of  $In_xGa_{1-x}As$  used in this work is fitted with indium composition, x while satisfying conditions given in equation (2.20):

$$E_p = 17x + 23(1-x) - 4.97x(1-x)$$

(2.22)

The remaining  $In_xGa_{1-x}As$  and InP material parameter expressions are summarized in Appendix A in Table A.1.

#### 2.2.4 IMPLEMENTATION IN COMSOL MULTIPHYSICS

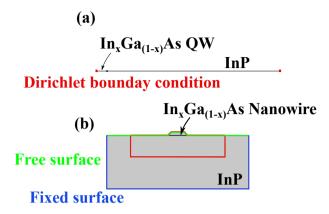

The heterostructure nanowire is assumed to be infinite in length, which converts the 3D nanowire structure into a more straightforward 2D problem and quantum well into a pure 1D problem. The geometry of these structures is illustrated in Figure 2.3, and boundary conditions used to solve for strain and eigenvalue calculations are highlighted. We use the COMSOL Multiphysics FEM solver and especially the solid mechanic's module to solve for deformation in the heterostructure nanowire. For simplicity, the model uses the linear elastic model and fixed and free boundary conditions to evaluate the strain matrix elements in the case of 1D heterostructure nanowire.

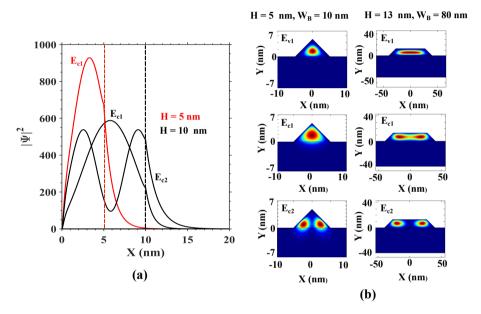

Next, we add the Eigenvalue study to the model in COMSOL Multiphysics and provide the energy value around which the eigenvalues (or subband energies either in CB or VB) are to be found. We can parameterize the wave vector in an unconfined direction to get E-K relation at the  $\Gamma$ -point from which the electronic parameters are extracted from this relation. Plotting the spatial probability distribution of the eigenstates of the CB and VB and strain tensor elements distribution in different parts of the geometry is possible. Figure 2.4 (a) plots the conduction band eigenstate distribution of InAs/InP heterostructure quantum well with thickness, H = 5 and 10 nm. It is observed that wave function leakage into the InP is larger in thin quantum wells compared to thicker quantum wells. Similarly, In Figure 2.4 (b), conduction band eigenstates of InAs/InP heterostructure nanowires are plotted for various nanowire dimensions.

**Figure 2.3:** The geometry of  $In_xGa_{1-x}As/InP$  heterostructure (a) quantum well and (b) nanowire with implemented Dirichlet boundary conditions for calculating eigenvalues are highlighted. Fixed and free boundary conditions are used to calculate the strain tensor elements of the heterostructure nanowire.

# STRAIN DISTRIBUTION IN 2D AND 1D $IN_XGA_{1-X}AS/INP$ HETEROSTRUCTURE

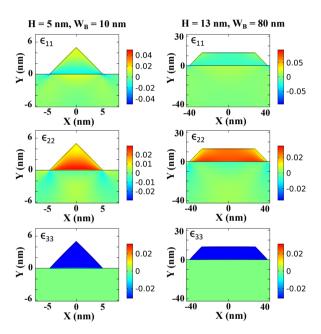

The main elastic strain tensor components  $\epsilon_{11}$ ,  $\epsilon_{22}$ , and  $\epsilon_{33}$  are defined along the X, Y, and Z directions. Strain tensor elements are homogenous in 2D quantum well and are independent of the quantum well thickness, whereas, in heterostructure nanowires, the strain distribution becomes size-dependent. These strain tensors are plotted for InAs/InP nanowires with different sizes in Figure 2.5. The  $\epsilon_{33}$  is uniform throughout the nanowire irrespective of nanowire size due to infinite nanowire length; in this case, the nanowire is compressed in the axial direction. The magnitude of  $\epsilon_{33}$  is -0.03, equal to the lattice mismatch at the interface. Further, the inplane elastic strain tensor elements are maximum at the interface and gradually decrease towards the surface of the nanowire due to free surfaces. The lattice mismatch between InP and InAs leads to compression in the *X* direction, i.e.,  $\epsilon_{11}$  is negative at the interface, and expansion in the Y direction, i.e.,  $\epsilon_{22}$  is positive at the interface.  $\epsilon_{11}$  and  $\epsilon_{22}$  in wider nanowires become approximately uniform around the X = 0 axis, and strain relaxes at the top corners of the nanowire. This behavior is reflected in the  $E_{c1}$  probability distribution of a nanowire with H = 13 nm and  $W_B = 80$  nm. It is illustrated in Figure 2.4, and the probability distribution is split into two peaks away from the center of the nanowire instead of a single peak located in the center.

**Figure 2.4:** (a) InAs/InP heterostructure quantum well with thickness, H = 5 and 10 nm. The available eigenstates probability distributions of the conduction band are plotted as a function of position. (b) The conduction band and valence band eigenmodes of the InAs/InP H = 5 nm,  $W_B = 10$  nm (left) and H = 13 nm,  $W_B = 80$  nm (right).

**Figure 2.5:** The main elastic strain tensor elements,  $\epsilon_{11}$ ,  $\epsilon_{22}$  and  $\epsilon_{33}$  are plotted for InAs/InP heterostructure nanowire strain distribution for various heights and widths.

# **MOS Theory**

In this chapter, MOSFET DC and small-signal high-frequency models are presented. III-V InGaAs/InP based quantum well, tri-gate, and GAA FETs electrical performance are discussed in the first half of the chapter. An extended high-frequency small-signal model is presented in the second half of the chapter.

### 3.1 MOSFET BACKGROUND

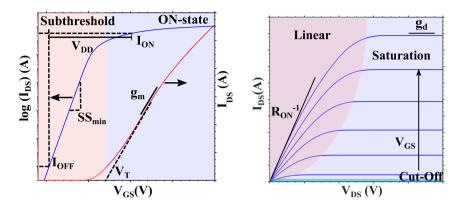

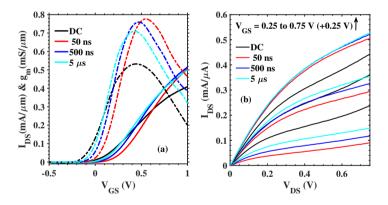

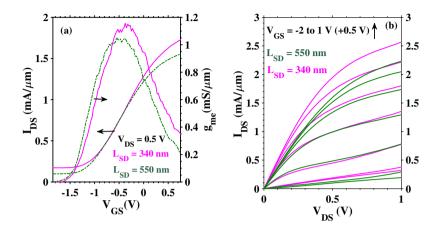

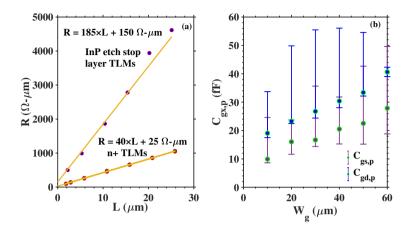

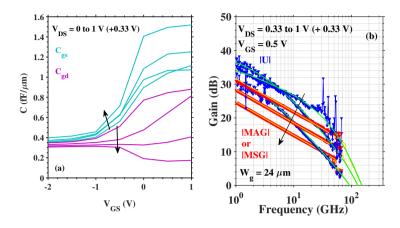

A MOSFET is a 3-terminal device, where the input gate to source voltage,  $V_{GS}$  controls the output drain to source current  $I_{DS}$  at a given drain to source voltage  $V_{DS}$ . General transfer and output characteristics of a MOSFET are plotted in Figure 3.1(a) and (b), respectively. From the transfer characteristics, the transistor's DC performance metrics such as threshold voltage,  $(V_T)$ , minimum subthreshold swing ( $SS_{min}$ ), OFF-current ( $I_{OFF}$ ) and ON-current ( $I_{ON}$ ) and transconductance  $(g_m)$  are extracted. From the output characteristics, ON resistance  $(R_{ON})$  and output conductance  $(g_d)$  are derived. The threshold voltage is the minimum  $V_{GS}$  required for the drain current to increase exponentially; in other words, the  $V_T$  point separates the off and on-state of the device. It is an important metric for logic devices and their scaling to maintain power efficiency. The gate metal work function, gate oxide bandgap, semiconductor surface potential, and oxide capacitance set  $V_T$ . The  $SS_{min}$  is the  $V_{GS}$  required to increase the drain current by one order (or  $\times 10$ ) at given  $V_{DS}$ . In subthreshold region,  $I_{DS} \propto e^{\left(\frac{V_{GS} - V_T}{k_B T}\right)}$ , where  $k_B$  and T are Boltzmann constant and temperature, respectively. The ideal  $SS_{min} = ln(10) \frac{k_B T}{a}$  and

Figure 3.1: (a) Transfer and (b) output characteristics of a MOSFET.

at room temperature,  $SS_{min}$  is approximately 60 mV/dec. Larger  $\frac{I_{ON}}{I_{OFF}}$  is an important metric for digital applications, and this ratio is decided for a given  $I_{OFF}$  and  $V_{DD}$  as illustrated in Figure 3.1(a). Next, transconductance is the ability of the FET to convert the small change in the input voltage to a large change in the output current and is defined as  $g_m = \frac{\partial I_{DS}}{\partial V_{GS}}$  at a given  $V_{DS}$ . It is one of the important metrics for DC and analog transistors and is a measure of the gain of the transistor. MOSFET operating regions are highlighted in Figure 3.1(b). FET is in cut-off region for  $V_{GS} - V_T < 0$  and triode or linear region for  $(V_{GS} - V_T) > V_{DS}$  and saturation region for  $V_{DS} > (V_{GS} - V_T)$ . The ON resistance is calculated when FET is operating in the linear region.  $R_{ON}$  includes the channel resistance  $(R_{ch})$ , which scales linearly with  $L_g$  and total access or contact resistance  $(2R_c)$ . A smaller  $R_{ON}$  is required for low power consumption when the transistor is ON. In short gate length devices, large total contact resistance limits  $R_{ON}$ . The output conductance,  $g_d = \frac{\partial I_{DS}}{\partial V_{DC}}$ is the measure of  $V_{DS}$  influence on  $I_{DS}$  at a given  $V_{GS}$ . Ideally, in MOSFET operating in the saturation region, the drain current is independent of  $V_{DS}$ ; however, due to the dominant short channel effects (SCE) in short gate length devices,  $g_d$  increases.

According to Moore's prophecy, the device density increases  $\times 2$  every 18 months [4]. It is achieved by scaling down transistor width and length while maintaining gate-to-channel electrostatics by proportionally scaling down oxide and channel thicknesses [5]. As the separation between source and drain decreases, short channel effects such as roll-off of  $V_T$ , increase in all  $SS_{min}$ ,  $I_{OFF}$ , and  $g_d$ . Researchers have started to look for alternate non-traditional device geometries such as GAA and Tri-Gate FETs. Typical gate

Figure 3.2: Gate metal-oxide-semiconductor channel geometry of Quantum well, GAA, and Tri-Gate FETs.

metal-oxide-channel structures of the quantum well, GAA, and Tri-Gate FET are shown in Figure 3.2.

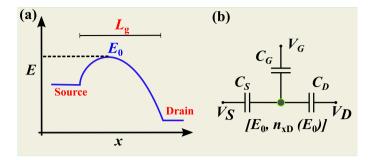

#### 3.2 MOS ELECTROSTATICS

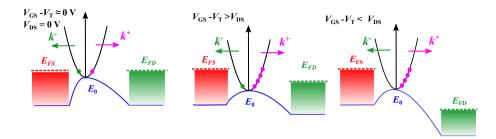

In a MOSFET, the drain and source are separated by an energy barrier, with the top of the potential barrier being  $(E_0)$  [54], which ideally is controlled solely by  $V_{GS}$ . However, in real MOSFET at smaller gate lengths, drain voltage influences  $E_0$  and thus drain to source current. Hence, 2D electrostatics are considered for current calculations to account for short-channel effects. The potential channel profile and 2D circuit level representation of the gate network are shown in Figure 3.3. In ballistic transistors, the electrons with positive k states at  $(E_0)$  move towards the drain without any scattering, and the carrier density is set by the difference between source fermi level  $(E_{FS})$  and  $E_0$ . The electrons with negative k states move towards the source, and their density is regulated by the drain fermi energy level  $(E_{FD})$ . The  $E_0$  is controlled by external biases and the presence of mobile carriers in the channel due to external biases is given by,

$$U_{ext} = -g\left(\alpha_G(V_G - V_T) + \alpha_D V_D + \alpha_S V_S\right) \tag{3.1}$$

**Figure 3.3:** (a) Potential profile from source to drain reservoirs, (b) 2D capacitive network of the channel. The top of the barrier potential is set by source, gate, and drain capacitances through external biases and carrier concentration at the top of the barrier.