### LUND UNIVERSITY

#### Vertical III-V Nanowire Transistors for Low-Power Logic and Reconfigurable **Applications**

Zhu, Zhongyunshen

2023

#### Link to publication

Citation for published version (APA): Zhu, Z. (2023). Vertical III-V Nanowire Transistors for Low-Power Logic and Reconfigurable Applications. Lund University.

Total number of authors: 1

Creative Commons License: CC BY

#### **General rights**

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

### Vertical III-V Nanowire Transistors for Low-Power Logic and Reconfigurable Applications

ZHONGYUNSHEN ZHU DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

### Vertical III-V Nanowire Transistors for Low-Power Logic and Reconfigurable Applications

**Doctoral Thesis**

Zhongyunshen Zhu

### LUND UNIVERSITY

Department of Electrical and Information Technology Lund, October 2023

Academic thesis for the degree of Doctor of Philosophy, which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, 13 October, 2023, at 9:15 a.m. in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers Väg 3, 223 63 Lund, Sweden. The thesis will be defended in English.

The Faculty Opponent will be Professor Kirsten Moselund, from Paul Scherrer Institute and EPFL.

| <i>Organisation:</i><br>LUND UNIVERSITY<br>Department of Electrical and | Document Type:<br>DOCTORAL THESIS                                                                                                                  |  |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Information Technology<br>Ole Römers Väg 3                              | Date of Issue:<br>September 2023                                                                                                                   |  |

| 223 63 Lund<br>Sweden                                                   | Sponsoring Organisation(s):<br>European Research Council (ERC)<br>Swedish Research Council (VR)<br>Swedish Foundation for Strategic Research (SSF) |  |

| Author:<br>Zhongyunshen Zhu                                             |                                                                                                                                                    |  |

Title:

#### Vertical III-V Nanowire Transistors for Low-Power Logic and Reconfigurable Applications

#### Abstract:

With rapid increase in energy consumption of electronics used in our daily life, the building blocks — transistors — need to work in a way that has high energy efficiency and functional density to meet the demand of further scaling. III-V channel combined with vertical nanowire gate-all-around (GAA) device architecture is a promising alternative to conventional Si transistors due to its excellent electrical properties in the channel and electrostatic control across the gate oxide in addition to reduced footprint. Based on this platform, two major objectives of this thesis are included: 1) to improve the performance of III-V p-type metal-oxide-semiconductor field-effect transistors (MOSFETs) and tunnel FETs (TFETs) for low-power digital applications; 2) to integrate HfO<sub>2</sub>-based ferroelectric gate onto III-V FETs (FeFETs) and TFETs (fero-TFETs) to enable reconfigurable operation for high functional density.

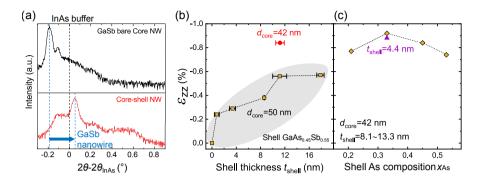

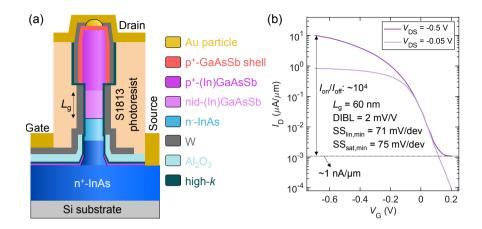

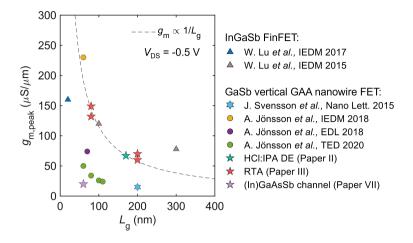

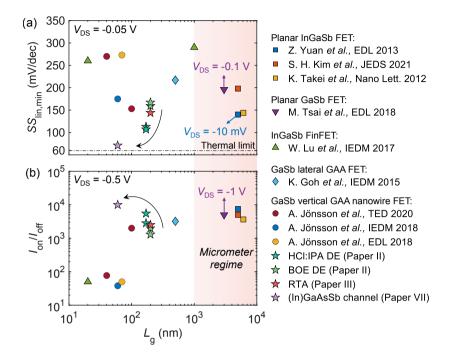

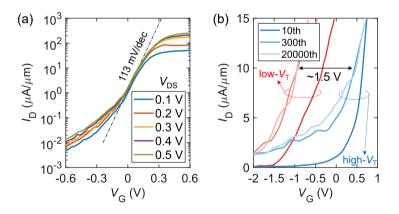

The key bottleneck for all-III-V CMOS is its p-type MOSFETs (p-FETs) which are mainly made of GaSb or InGaSb. Rich surface states of III-Sb materials not only lead to decreased effective channel mobility due to more scattering, but also deteriorate the electrostatics. In this thesis, several approaches to improve p-FET performance have been explored. One strategy is to enhance the hole mobility by introducing compressive strain into III-Sb channel. For the first time, a high and uniform compressive strain near 1% along the transport direction has been achieved in downscaled GaSb nanowires by growing and engineering GaSb-GaAsSb core-shell structure, aiming for potential hole mobility enhancement. In addition, surface passivation using digital etch has been developed to improve the electrostatics with subthreshold swing (SS) down to 107 mV/dec. Moreover, the on-state performance including on-current ( $l_{on}$ ) and transconductance ( $g_m$ ) have been enhanced by ~50% using annealing with H<sub>2</sub>-based forming gas. Lastly, a novel p-FET structure with (ln)GaAsSb channel has been developed and further improved off-state performance with SS = 71 mV/dec, which is the lowest value among all reported III-V p-FETs.

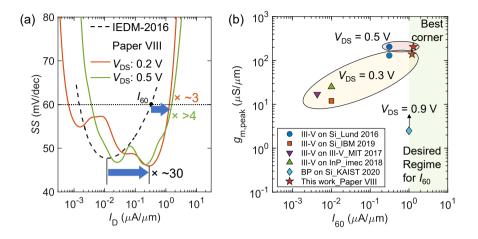

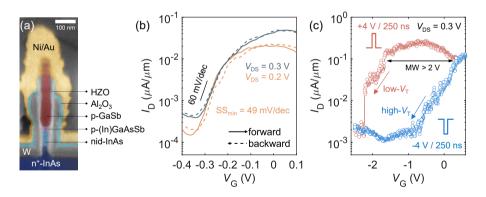

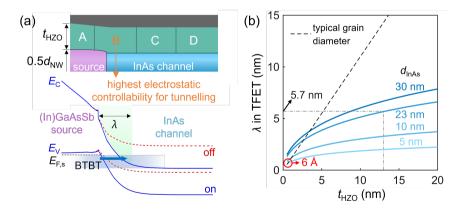

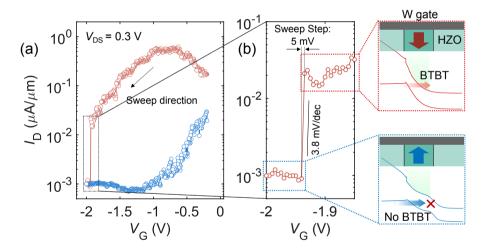

Despite subthermionic operation, TFETs usually suffer from low drive current as well as the current operating below 60 mV/dec ( $l_{60}$ ). The second focus of this thesis is to fine-tune the InAs/(In)GaAsSb heterostructure tunnel junction and the doping in the source segment during epitaxy. As a result, a substantially increased  $l_{60}$  (> 1  $\mu$ A/ $\mu$ m) and  $l_{on}$  up to 40  $\mu$ A/ $\mu$ m at source-drain bias of 0.5 V have been achieved, reaching a record compared to other reported TFETs.

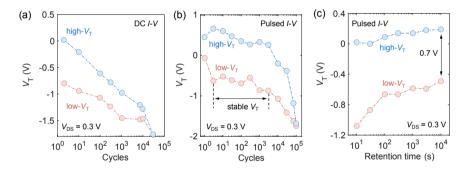

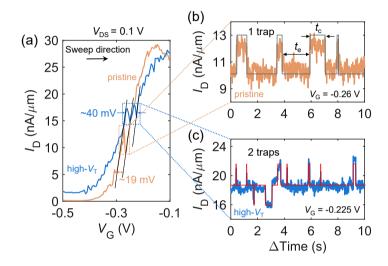

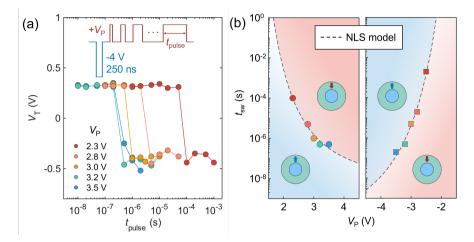

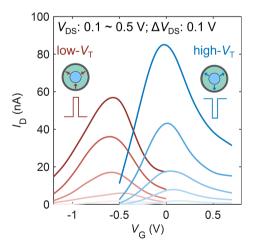

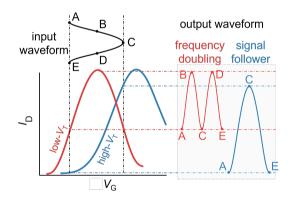

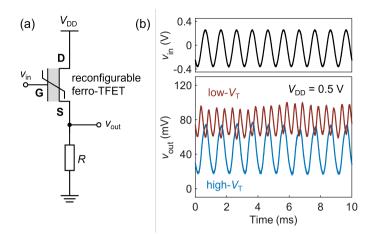

Finally, emerging ferroelectric oxide based on Zr-doped HfO<sub>2</sub> (HZO) has been successfully integrated onto III-V vertical nanowire transistors to form FeFEIs and ferro-TFETs with GAA architecture. The corresponding electrical performance and reliability have been carefully characterized with both DC and pulsed *I-V* measurements. The unique band-to-band tunneling in InAs/(In)GaASb/GaSb heterostructure TFET creates an ultrashort effective channel, leading to detection of localized potential variation induced by single domains and defects in nanoscale ferroelectric HZO without physical gate-length scaling. By introducing gate/source overlap structure in the ferro-TFET, nonvolatile reconfigurable signal modulation with multiple modes including signal transmission, phase shift, frequency doubling, and mixing has been achieved in a single device with low drive voltage and only ~0.01  $\mu$ m<sup>2</sup> footprint, thus increasing both functional density and energy efficiency.

Keywords:

III-V Nanowires, MOSFET, TFET, Ferroelectrics, Reconfigurable.

| Classification System and/or Index Terms                     |                                          | <i>Language:</i>  |  |

|--------------------------------------------------------------|------------------------------------------|-------------------|--|

| Electronic Engineering, Nano Technology                      |                                          | English           |  |

| Supplementary Bibliographical Information:                   |                                          | ISBN (printed):   |  |

| –                                                            |                                          | 978-91-8039-830-5 |  |

| <i>Key title and ISSN:</i>                                   |                                          | ISBN (digital):   |  |

| Series of Licentiate and Doctoral Theses; 1654-790X, No. 163 |                                          | 978-91-8039-829-9 |  |

| Recipient's Notes:                                           | Number of Pages:<br>163                  | Price:            |  |

|                                                              | Security Classification:<br>Unclassified |                   |  |

General Permissions:

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature:

Znorgynden Zen J. Fill it

Date: 19 September 2023

### Vertical III-V Nanowire Transistors for Low-Power Logic and Reconfigurable Applications

**Doctoral Thesis**

Zhongyunshen Zhu

Department of Electrical and Information Technology Lund, October 2023 Zhongyunshen Zhu Department of Electrical and Information Technology Lund University Ole Römers Väg 3, 223 63 Lund, Sweden

Series of Licentiate and Doctoral Theses ISSN 1654-790X, No. 163 ISBN 978-91-8039-830-5 (printed) ISBN 978-91-8039-829-9 (digital)

© 2023 Zhongyunshen Zhu

This thesis is typeset using  $IATEX 2_{\mathcal{E}}$  with the body text in Palatino and Goudy Initials, headings in Helvetica, text in figures in Arial, and the body text in Appendix B in Computer Modern. All can of course be changed to your linking.

Frontispiece: A semiconductor chip made from nanowire transistors rests on a leaf.

Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

### Abstract

TTH rapid increase in energy consumption of electronics used in our daily life, the building blocks — transistors — need to work in a way that has high energy efficiency and functional density to meet the demand of further scaling. III-V channel combined with vertical nanowire gate-all-around (GAA) device architecture is a promising alternative to conventional Si transistors due to its excellent electrical properties in the channel and electrostatic control across the gate oxide in addition to reduced footprint. Based on this platform, two major objectives of this thesis are included: 1) to improve the performance of III-V p-type metal-oxide-semiconductor fieldeffect transistors (MOSFETs) and tunnel FETs (TFETs) for low-power digital applications; 2) to integrate HfO<sub>2</sub>-based ferroelectric gate onto III-V FETs (FeFETs) and TFETs (ferro-TFETs) to enable reconfigurable operation for high functional density.

The key bottleneck for all-III-V CMOS is its p-type MOSFETs (p-FETs) which are mainly made of GaSb or InGaSb. Rich surface states of III-Sb materials not only lead to decreased effective channel mobility due to more scattering, but also deteriorate the electrostatics. In this thesis, several approaches to improve p-FET performance have been explored. One strategy is to enhance the hole mobility by introducing compressive strain into III-Sb channel. For the first time, a high and uniform compressive strain near 1% along the transport direction has been achieved in downscaled GaSb nanowires by growing and engineering GaSb-GaAsSb core-shell structure, aiming for potential hole mobility enhancement. In addition, surface passivation using digital etch has been developed to improve the electrostatics with subthreshold swing (SS) down to 107 mV/dec. Moreover, the on-state

performance including on-current ( $I_{on}$ ) and transconductance ( $g_m$ ) have been enhanced by ~50% using annealing with H<sub>2</sub>-based forming gas. Lastly, a novel p-FET structure with (In)GaAsSb channel has been developed and further improved off-state performance with SS = 71 mV/dec, which is the lowest value among all reported III-V p-FETs.

Despite subthermionic operation, TFETs usually suffer from low drive current as well as the current operating below 60 mV/dec ( $I_{60}$ ). The second focus of this thesis is to fine-tune the InAs/(In)GaAsSb heterostructure tunnel junction and the doping in the source segment during epitaxy. As a result, a substantially increased  $I_{60}$  (> 1  $\mu$ A/ $\mu$ m) and  $I_{on}$  up to 40  $\mu$ A/ $\mu$ m at source-drain bias of 0.5 V have been achieved, reaching a record compared to other reported TFETs.

Finally, emerging ferroelectric oxide based on Zr-doped HfO<sub>2</sub> (HZO) has been successfully integrated onto III-V vertical nanowire transistors to form FeFETs and ferro-TFETs with GAA architecture. The corresponding electrical performance and reliability have been carefully characterized with both DC and pulsed *I-V* measurements. The unique band-to-band tunneling in InAs/(In)GaAsSb/GaSb heterostructure TFET creates an ultrashort effective channel, leading to detection of localized potential variation induced by single domains and defects in nanoscale ferroelectric HZO without physical gatelength scaling. By introducing gate/source overlap structure in the ferro-TFET, non-volatile reconfigurable signal modulation with multiple modes including signal transmission, phase shift, frequency doubling, and mixing has been achieved in a single device with low drive voltage and only ~0.01  $\mu$ m<sup>2</sup> footprint, thus increasing both functional density and energy efficiency.

### Popular Science Summary

OU may have heard of **ChatGPT**, one of the hottest terms recently. It is a powerful chat robot with the capability to generate human-like text based on the given input. What is even more amazing is that the latest version of **ChatGPT** reaches the knowledge level of an undergraduate student from Stanford University. Incredible, right? Even many years ago, **Alpha Go** from *DeepMind Inc.* could already beat the best human Go player in the world. All these achievements mainly rely on the AI revolution where a large-scale deep learning model is utilized to process massive information. However, behind such an amazing AI system, a huge amount of energy is actually consumed. This is already causing severe environmental problems on our living planet. Therefore, we must find new approaches to tackle this issue. Fundamentally, the essential reason behind it is that the basic building blocks of all our current electrical devices, transistors, are working in a way that is not energy-efficient enough. This thesis aims to develop new structure transistors to work with low power consumption and more functionality.

The transistors are essentially a switch that can be turned on and off by an electrode called gate. It is pretty like the water-tap (gate) which controls whether the water flowing (current flow in transistors) out or not. The onand off-state of the transistor are encoded as binary data of "0" and "1", respectively. When putting millions or even billions of transistors (e.g. A16 chip in iPhone 14 contains 16 billion transistors) together in a specific way, they can do extremely complicated computations that are almost impossible for the human brain. To package such a dense system, transistors need to be very tiny, which can reach around 10 nm regime, a size about 5000 times thinner than human hair. Unfortunately, the leakage current when you switch off the transistor increases with the size downscaling, leading to a large amount of energy wasted. This will also heat up the system, which then significantly affects the performance.

In this thesis, we attempt to develop transistors with new structures that can operate at low power conditions. We basically combine three aspects to realize this. First, a vertical nanowire is used to reduce the footprint yet bring the transistor size scaling to the vertical direction. In this 3D architecture, you can expect a larger transistor out of the plane but remaining a small planar area. Therefore, the leakage can be well suppressed while a high package density can be still achieved. Second, we change the transistor material from silicon to III-V compound semiconductors which are alloys of group-III and V elements in the periodic table. These materials show better electrical performance compared to silicon. Therefore, lower supplied voltage can be used to achieve the same performance as silicon transistors which dominate in most electronics. Based on these two points, combining lower leakage current and supplied voltage results in lower power consumption. Moreover, we have taken one step forward to add more functionality into one transistor so that it can do the work that several transistors used to do (just imagine that you have a fancy multi-level adjustable showerhead). This is achieved by integrating new materials called ferroelectrics onto our III-V vertical nanowire transistors. As a result, either the number of transistors is reduced but with the same functions, or more functions are realized but with the same number of transistors. Thus, the power consumption can be lowered without compromising the performance. We believe that our study on such a transistor structure will trigger more potential applications for systems requiring energy efficiency, such as AI chips and IoT devices.

### Acknowledgments

HIS is the last section I wrote in my thesis, and as the Chinese saying goes, the most important thing comes at the end. There were many remarkable individuals who have guided, inspired, and supported me throughout this unique journey of my life, so I would like to express my deepest gratitude to you at this moment. Without you, the thesis would not be complete. Firstly, I would like to thank my main supervisor, *Lars-Erik Wernersson*, who gave me the opportunity to start this journey. Your guidance and support made me feel comfortable and confident in doing research. I have been always inspired by your broad vision and motivated by your encouragement in every project.

I also want to thank my second supervisor, *Johannes Svensson*. Thank you for leading me to the lab and teaching me the growth hand by hand. I appreciate very much that you always said "Yes" when I asked you "Do you have time to discuss?" and patiently answered my sometimes even stupid questions. You are definitely more than only a supervisor to me.

A big thanks to those who gave me special help and inspiration during my PhD research. Thank you, *Anton Persson*, I enjoyed a lot with you for fantastic exploration of the first ferroelectric transistors here in Lund. Thank you, *Gautham Rangasamy* and *Abinaya Krishnaraja*, those great discussions made me learn a lot about TFETs. *Adam Jönsson*, thank you for introducing me to the vertical processing step by step. *Robin Atle*, thank you for your incredible assistance in making beautiful FIB images of the nanowires. Thank you, *Erik Lind*, for your great discussions about TFET physics and constructive inputs in the first ferro-TFET paper.

I would also like to extend my gratitude to all the remarkable colleagues within the division who made the work environment not only vibrant but also relaxing with full of fun. I will never forget the moments we spent together from lab to office, from fika to innebandy. So a great thanks goes to you, *Marcus, Saketh, Phillipp, André, Hannes, Karthik, Ben, Ngoc Duc, Heera, Lars, Mattias, Anette, Navya, Patrik, Louise, Lasse, Markus, Fredrik, Karl-Magnus, Stefan, Sebastian, Olli-Pekka, Paula, Niklas, Daniel, Mats, Johan, Andrea, and Alexandros.* A special thanks to *André, Gautham*, and *Guoda* for proofreading of this thesis. Beyond the department, I want to thank Yen-Po and Rainer from the Physics Department, and Axel from the Chemistry Department for providing excellent material characterizations in our collaborations.

Furthermore, I want to thank all the engineers and technicians in both *NanoLund* and *EIT* lab. My thesis wouldn't be possible to be completed without your tremendous help. A special thank you to *Sebastian Lehmann* and *Sungyoun Ju* for your professional maintenance of the growth machine so that I could grow samples in an expected way.

I thank all my friends in Sweden and in China. You made my life far from boring. Thank you, *Guoda*, for your generous assistance in our several relocations and for playing Pingpong with me after work. Thank you, *Shang*, for having wonderful experiences together over the years and I believe there will be more to come.

Finally, I would like to thank my family for your unconditional love and forever support in my entire life. My deepest appreciation goes to *Yuyu*, who has been always supportive and understanding throughout this journey. Your patience and wisdom in life have influenced me to be a better person. Living thousands of miles away from my hometown and family is not easy, but you make me feel at home wherever I am.

Znongyuden Zen J. Zigt 24

Lund, Sept. 2023

### Contents

| Abstract i                                             | ii  |

|--------------------------------------------------------|-----|

| Popular Science Summary                                | v   |

| Acknowledgments v                                      | ii  |

| Contents                                               | ix  |

| Preface xi                                             | ii  |

| Structure of the Thesis                                | iii |

| Included Papers                                        | iv  |

| Related Work                                           | w   |

| Acronyms and Symbols xv                                | ii  |

| Acronyms and Abbreviations                             | 7ii |

| Latin Symbols                                          | iii |

| Greek Symbols                                          | x   |

| INTRODUCTION                                           | 1   |

| 1 Background                                           | 3   |

| 1.1 Transistor architecture: past, present, and future | 4   |

| 1.2 III-V semiconductor: opportunity and challenge     | 5   |

| 1.3 Heterogeneous integration                          | 8   |

| 2 Transistor Fundamentals                                 | 11 |

|-----------------------------------------------------------|----|

| 2.1 Basics of MOSFETs and TFETs                           | 11 |

| 2.1.1 Metrics of transistor performance                   | 12 |

| 2.1.2 Interface traps                                     | 15 |

| 2.1.3 Negative differential resistance                    | 16 |

| 2.1.4 Negative transconductance                           | 17 |

| 2.2 Ferroelectric FETs                                    | 18 |

| 2.2.1 Remanent polarization                               | 19 |

| 2.2.2 Memory window and reconfigurability                 | 20 |

| 3 Device fabrication                                      | 23 |

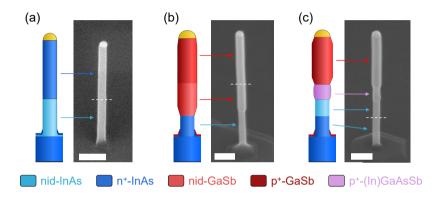

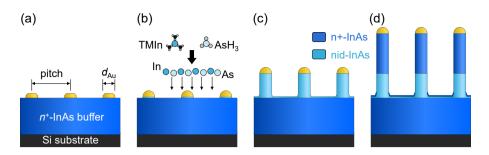

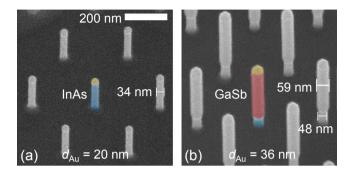

| 3.1 Nanowire epitaxy                                      | 23 |

| 3.1.1 Vapor-Liquid-Solid growth                           | 24 |

| 3.1.2 Challenges in thin GaSb nanowires                   | 25 |

| 3.1.3 Heterojunction engineering in TFETs                 | 26 |

| 3.2 Strain effect in GaSb-related nanowires               | 27 |

| 3.3 Fabrication process for vertical nanowire transistors | 31 |

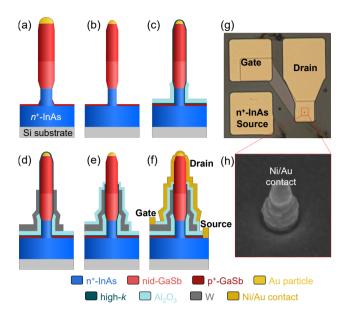

| 3.3.1 Basic process flow                                  | 31 |

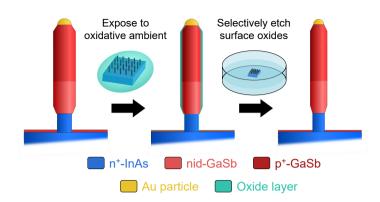

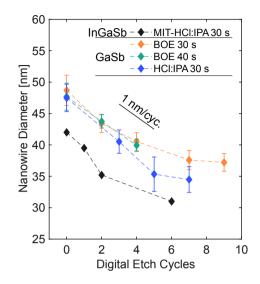

| 3.3.2 Digital etch on nanowires                           | 31 |

| 3.3.3 Gate-last process                                   | 35 |

| 3.4 Ferroelectric gate-stack integration                  | 38 |

| 4 Electrical measurements and results                     | 41 |

| 4.1 III-V nanowire p-FETs                                 | 41 |

| 4.1.1 Channel surface pretreatment                        | 41 |

| 4.1.2 Annealing with forming gas                          | 42 |

| 4.1.3 (In)GaAsSb channel                                  | 44 |

| 4.1.4 benchmarking                                        | 45 |

| 4.2 InAsSb channel nanowire TFETs                         | 45 |

| 4.3 III-V nanowire FeFETs                                 | 46 |

| 4.4 III-V nanowire Ferro-TFETs                            | 49 |

| 4.4.1 Reliability                                         | 50 |

| 4.4.2 Individual defects in ferroelectric HZO             | 50 |

| 5 Applications of ferro-TFETs                             | 53 |

| 5.1 Single domain detection                               | 53 |

| 5.1.1 effective short channel in TFETs                                                                          | 53  |

|-----------------------------------------------------------------------------------------------------------------|-----|

| 5.1.2 Characterization of Single domain switching                                                               | 55  |

| 5.2 Reconfigurable signal modulation                                                                            | 57  |

| 5.2.1 Reconfigurable NTC                                                                                        | 57  |

| 5.2.2 Programmable modulation modes                                                                             | 58  |

| 5.3 Other potential applications                                                                                | 59  |

| 6 Summary and Outlook                                                                                           | 61  |

| Bibliography                                                                                                    | 65  |

|                                                                                                                 |     |

| APPENDICES                                                                                                      | 79  |

| A Nanowire Epitaxy Recipes                                                                                      | 81  |

| <b>B</b> Fabrication Steps of Vertical Nanowire Transistors                                                     | 83  |

| PAPERS                                                                                                          | 87  |

| I Compressively-strained GaSb nanowires with core-shell heterostructures                                        | 89  |

| II Improved Electrostatics through Digital Etch Schemes in<br>Vertical GaSb Nanowire p-MOSFETs on Si            | 99  |

| III Performance enhancement of GaSb vertical nanowire p-<br>type MOSFETs on Si by rapid thermal annealing       | 109 |

| IV Integration of Ferroelectric $Hf_xZr_{1-x}O_2$ on Vertical III-V<br>Nanowire Gate-All-Around FETs on Silicon | 121 |

| V Sensing single domains and individual defects in scaled ferroelectrics                                        | 127 |

| VI Reconfigurable signal modulation in a ferroelectric tunnel field-effect transistor                           | 139 |

| VII Low-power, Self-aligned Vertical InGaAsSb NW PMOS<br>with S < 100 mV/dec                                    | 151 |

| VIII High Current Density Vertical Nanowire TFETs with $I_{60}$ > 1 $\mu$ A/ $\mu$ m                            | 157 |

### Preface

HIS thesis is a summary of five-year work in *Nanoelectronics Group* (belonging to the *Division of Electromagnetics & Nanoelectronics* since 2022) at the Department of Electrical and Information Technology, Lund University. This work presents a systematic investigation of III-V-based vertical nanowire transistors and their integration with emerging ferroelectric gate-stack, aiming for low-power and multiple-function systems. The work was supervised by Professor *Lars-Erik Wernersson* and Dr. *Johannes Svensson*.

#### STRUCTURE OF THE THESIS

This is a thesis with a collection of research papers, including an introductory section providing a summary of the research field. The appended publications together with the introduction are comprehensible for aspiring researchers with a master's degree interested in pursuing similar research topics.

#### INTRODUCTION

The Introduction provides a broad and comprehensive view of the included publications and combines related work together. The Introduction is intended to be comprehensible for aspiring readers with a Master's degree in physics, electrical engineering, or a related subject.

#### APPENDICES

#### A Nanowire Epitaxy Recipes

Appendix A provides details of nanowire growth procedures by MOVPE.

#### **B** Fabrication Steps of Vertical Nanowire Transistors

Appendix B provides detailed steps of vertical device fabrication included in this thesis.

#### • PAPERS

The papers forming the main body of the thesis are reproduced in the back and listed in the following.

#### **INCLUDED PAPERS**

The following published papers form the main body of this thesis and are appended at the back of the thesis.

Paper I: <u>Z. ZHU</u>, J. SVENSSON, A. R. PERSSON, R. WALLENBERG, A. V. GROMOV, AND L.-E. WERNERSSON, "Compressively-strained GaSb nanowires with core-shell heterostructures", *Nano Research*, vol. 13, no. 9, pp. 2517–2524, Jun. 2020, doi: 10.1007/s12274-020-2889-3.

► I performed the nanowire growth, sample preparation for TEM and  $\mu$ -Raman characterizations, data analysis, and wrote the paper.

Paper II: Z. ZHU, A. JÖNSSON, Y.-P. LIU, J. SVENSSON, R. TIMM, AND L.-E. WERNERSSON, "Improved Electrostatics through Digital Etch Schemes in Vertical GaSb Nanowire p-MOSFETs on Si", ACS Applied Electronic Materials, vol. 4, no. 1, pp. 531–538, Jan. 2022, doi: 10.1021/acsaelm.1c01134.

► I performed the nanowire growth, part of sample fabrication, part of electrical measurements, and wrote the paper.

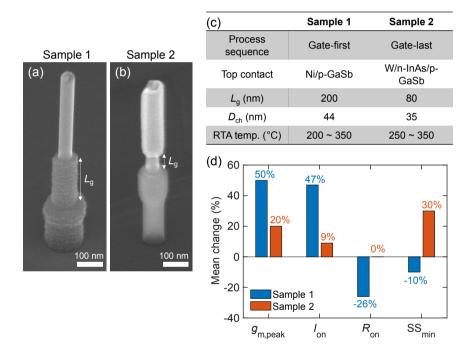

Paper III: <u>Z. ZHU</u>, J. SVENSSON, A. JÖNSSON, AND L.-E. WERNERSSON, "Performance enhancement of GaSb vertical nanowire p-type MOSFETs on Si by rapid thermal annealing", *Nanotechnology*, vol. 33, no. 7, pp. 075202, Nov. 2021, doi: 10.1088/1361-6528/ac3689.

► I performed the nanowire growth, sample fabrication, part of electrical measurements, and wrote the paper.

**Paper IV:** A. E. O. PERSSON, <u>Z. ZHU</u>, AND L.-E. WERNERSSON, "Integration of Ferroelectric  $Hf_xZr_{1-x}O_2$  on Vertical III-V Nanowire Gate-All-Around FETs on Silicon", *IEEE Electron Device Letters*, vol. 43, no. 6, pp. 854–857, Jun. 2022, doi: 10.1109/LED.2022.3171597.

► I performed the nanowire growth, part of sample fabrication, and part of electrical measurements.

Paper V: Z. ZHU, A. E. O. PERSSON, AND L.-E. WERNERSSON, "Sensing single domains and individual defects in scaled ferroelectrics", *Science Advances*, vol. 9, no. 5, pp. eade7098, Feb. 2023, doi: 10.1126/sciadv.ade7098. ► I performed the nanowire growth, part of sample fabrication, part of electrical measurements, and wrote the paper.

Paper VI: <u>Z. ZHU</u>, A. E. O. PERSSON, AND L.-E. WERNERSSON, "Reconfigurable Signal Modulation in a Ferroelectric Tunnel Field-Effect Transistor.", *Nature Communications*, vol. 14, no. 1, pp. 2530, May. 2023, doi: 10.1038/s41467-023-38242-w.

► I performed the nanowire growth, part of sample fabrication, part of electrical measurements, and wrote the paper.

- Paper VII: A. KRISHNARAJA, Z. ZHU, J. SVENSSON, AND L.-E. WERNERSSON, "Low-power, Self-aligned Vertical InGaAsSb NW PMOS with S < 100 mV/dec.", IEEE Electron Device Letters, vol. 44, no. 7, pp. 1064–1067, Jul. 2023, doi: 10.1109/LED.2023.3277917.</p>

- ▶ I partly designed the device structure and performed the nanowire growth.

- **Paper VIII:** G. RANGASAMY, <u>Z. ZHU</u>, AND L.-E. WERNERSSON, "High Current Density Vertical Nanowire TFETs with  $I_{60} > 1 \ \mu\text{A}/\mu\text{m}$ .", *IEEE Access*, vol. 11, pp. 95692–95696, Aug. 2023, doi: 10.1109/ACCESS.2023.3310253.

► I partly designed the device structure and performed the nanowire growth and modeling.

#### **RELATED WORK**

The following publications and manuscripts in preparation are not included in this thesis, but summarize related work that I was involved in.

- Paper ix: G. RANGASAMY, Z. ZHU, L. O. FHAGER, AND L.-E. WERNERSSON, "TFET Circuit Configurations Operating Below 60 mV/dec", IEEE Transactions on Nanotechnology, (2022, Under Review)

- **Paper x:** G. RANGASAMY, <u>Z. ZHU</u>, L. O. FHAGER, AND L.-E. WERNERSSON, " $g_m/I_d$ Analysis of Vertical Nanowire III–V TFETs", *Electronics Letters*, (Sept. 2023, accepted)

- Paper xi: A. KRISHNARAJA, J. SVENSSON, E. MEMISEVIC, <u>Z. ZHU</u>, A. R. PERSSON, E. LIND, L. R. WALLENBERG, AND L.-E. WERNERSSON, "Tuning of source material for InAs/InGaAsSb/GaSb application-specific vertical nanowire tunnel FETs", ACS Applied Electronic Materials, vol. 2, no. 9, pp. 2882–2887, Sep. 2020, doi: 10.1021/acsaelm.0c00521.

- Paper xii: A. KRISHNARAJA, J. SVENSSON, <u>Z. ZHU</u>, AND L.-E. WERNERSSON, "Tunnel Field-Effect Transistor Operation at Different Temperature Regimes", *Applied Physics Letters*, (2023, In Revision)

- Paper xiii: D. DZHIGAEVC, J. SVENSSON, A. KRISHNARAJA, <u>Z. ZHU</u>, Z. REN, Y. LIU, S. KALBFLEISCH, A. BJÖRLING, F. LENRICK, Z. I. BALOGH, S. HAMMAR-BERG, J. WALLENTIN, R. TIMM, L.-E. WERNERSSON, AND A. MIKKELSEN, "Strain mapping inside an individual processed vertical nanowire transistor using scanning X-ray nanodiffraction", *Nanoscale*, vol. 12, no. 27, pp. 14487–14493, Jun. 2020, doi: 10.1039/D0NR02260H.

### Acronyms and Symbols

Here, important acronyms, abbreviations, and symbols are listed, which are recurring throughout the thesis. Some parameters, which only occur in a narrow context, are intentionally omitted; some parameters are used in more than one way, but the context is always explicitly clarified in the corresponding text. Some (compound) units are provided with prefixes to reflect the most commonly encountered notations in the literature.

#### ACRONYMS AND ABBREVIATIONS

| 3D   | Three Dimensional                                           |

|------|-------------------------------------------------------------|

| 5G   | Fifth-Generation Technology Standard for Broadband Cellular |

|      | Networks                                                    |

| AC   | Alternating Current                                         |

| AI   | Artificial Intelligence                                     |

| ALD  | Atomic Layer Deposition                                     |

| BEOL | Back-End-of-Line                                            |

| BOE  | Buffered Oxide Etchant                                      |

| BTBT | Band-to-Band Tunneling                                      |

| CMOS | Complementary Metal-Oxide-Semiconductor                     |

| DC   | Direct Current                                              |

| DE   | Digital Etch                                                |

| DI   | Deionized                                                   |

| EBL                          | Electron-Beam Lithography                                                                                                                    |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FeFET<br>FEOL                | Ferroelectric Field-Effect Transistor<br>Front-End-of-Line                                                                                   |  |  |  |

| GAA                          | Gate-All-Around                                                                                                                              |  |  |  |

| IC<br>ICP<br>IoT<br>IPA      | Integrated circuit<br>Inductively Coupled Plasma<br>Internet-of-Things<br>Isopropyl Alcohol                                                  |  |  |  |

| MFS<br>MOSFET<br>MOVPE<br>MW | Metal-Ferroelectric-Semiconductor<br>Metal-Oxide-Semiconductor Field-Effect Transistor<br>Metal-Organic Vapor-Phase Epitaxy<br>Memory Window |  |  |  |

| NAND<br>NDR<br>NTC           | Not And<br>Negative Differential Resistance<br>Negative Transconductance                                                                     |  |  |  |

| PUND                         | Positive-Up Negative-Down                                                                                                                    |  |  |  |

| RIE<br>RRAM<br>RTA           | Reactive-Ion Etch<br>Resistive Random-Access Memory<br>Rapid Thermal Annealing                                                               |  |  |  |

| SEM                          | Scanning Electron Microscopy                                                                                                                 |  |  |  |

| TEM                          | Transmission Electron Microscopy                                                                                                             |  |  |  |

| UV                           | Ultraviolet                                                                                                                                  |  |  |  |

| WZ                           | Wurtzite                                                                                                                                     |  |  |  |

| XEDS<br>XPS<br>XRD           | Energy-dispersive X-ray spectroscopy<br>X-ray Photoelectron Spectroscopy<br>X-Ray Diffraction                                                |  |  |  |

| ZB                           | Zink-Blende                                                                                                                                  |  |  |  |

#### LATIN SYMBOLS

| Al <sub>2</sub> O <sub>3</sub><br>AsH <sub>3</sub> |                                  | Aluminium Oxide<br>Arsine                                                                                               |  |  |  |  |

|----------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Cox                                                | F/m                              | Gate Oxide Capacitance                                                                                                  |  |  |  |  |

| d<br>Di                                            | m $eV^{-1}cm^{-2}$               | Nanowire Diameter, subscript indicates<br>the specific object                                                           |  |  |  |  |

| D <sub>it</sub>                                    |                                  | Interface Trap Density                                                                                                  |  |  |  |  |

| Eg<br>F                                            | eV<br>eV                         | Band Gap                                                                                                                |  |  |  |  |

| E <sub>C</sub><br>E <sub>F,D</sub>                 | eV<br>eV                         | Conduction Band Edge<br>Fermi Level Energy at the Drain                                                                 |  |  |  |  |

| $E_{\rm F,S}$                                      | eV                               | Fermi Level Energy at the Source                                                                                        |  |  |  |  |

| $E_{\rm V}$                                        | eV                               | Valence Band Edge                                                                                                       |  |  |  |  |

| f                                                  | Hz                               | Frequency, subscript indicates the specific case                                                                        |  |  |  |  |

| GaAsSb<br>GaSb                                     |                                  | Gallium Arsenide Antimonide<br>Gallium Antimonide                                                                       |  |  |  |  |

| g <sub>m</sub>                                     | S, $\mu$ S $\mu$ m <sup>-1</sup> | Transconductance, often normalised by the<br>gate width<br>Peak Transconductance, often normalised<br>by the gate width |  |  |  |  |

| <i>g</i> m,peak                                    | S, $\mu S \mu m^{-1}$            |                                                                                                                         |  |  |  |  |

| HfO <sub>2</sub>                                   |                                  | Hafnium Oxide                                                                                                           |  |  |  |  |

| HZO                                                |                                  | Hafnium Zirconium Oxide (Zirconium-<br>doped Hafnium Oxide)                                                             |  |  |  |  |

| I <sub>D</sub>                                     | A, $\mu A \mu m^{-1}$            | Drain Current, often normalised by the gate width                                                                       |  |  |  |  |

| I <sub>off</sub>                                   | A, $\mu A \mu m^{-1}$            | Off-Current, often normalised by the gate width                                                                         |  |  |  |  |

| I <sub>on</sub>                                    | A, $\mu A \mu m^{-1}$            | On-Current, often normalised by the gate width                                                                          |  |  |  |  |

| InAs                                               |                                  | Indium Arsenide                                                                                                         |  |  |  |  |

| InAsSb<br>InGaAsSb                                 |                                  | Indium Arsenide Antimonide<br>Indium Gallium Arsenide Antimonide                                                        |  |  |  |  |

| k <sub>B</sub>                                     |                                  | $\approx 1.381 \times 10^{-23} \mbox{ kg m}^2 \mbox{ K}^{-1} \mbox{ s}^{-1}$ , Boltzmann Constant                       |  |  |  |  |

| Lg                                                 | m Gate Length                    |                                                                                                                         |  |  |  |  |

| m <sub>0</sub><br>m* | kg<br>m <sub>0</sub> | $\approx 9.109 \times 10^{-31}$ kg, Electron Rest Mass Effective Mass |  |  |  |  |

|----------------------|----------------------|-----------------------------------------------------------------------|--|--|--|--|

| q                    | С                    | $pprox 1.602 	imes 10^{-19}$ C, Elemental Charge                      |  |  |  |  |

| Ron                  | $\Omega\mu m$        | On Resistance, often normalised by the gate width                     |  |  |  |  |

| SS                   | mV/dec               | Subthreshold Swing                                                    |  |  |  |  |

| t                    | s                    | Time, subscript indicates the specific case                           |  |  |  |  |

| Т                    | K, °C                | Temperature                                                           |  |  |  |  |

| VD                   | V                    | Drain Bias                                                            |  |  |  |  |

| V <sub>DS</sub>      | V                    | Drain-to-Source Voltage                                               |  |  |  |  |

| V <sub>G</sub>       | V                    | Gate Bias, here equivalent to Gate-to-                                |  |  |  |  |

|                      |                      | Source Voltage ( $V_{GS}$ )                                           |  |  |  |  |

| V <sub>OV</sub>      | V                    | Overdrive Voltage, $V_{\rm G} - V_{\rm T}$                            |  |  |  |  |

| Vs                   | V                    | Source Bias                                                           |  |  |  |  |

| V <sub>T</sub>       | V                    | Threshold Voltage                                                     |  |  |  |  |

#### **GREEK SYMBOLS**

| α              | $eV^{-1}$ | Exponential Coefficient Associated with the Material Properties |  |  |  |

|----------------|-----------|-----------------------------------------------------------------|--|--|--|

| к              |           | Relative Permittivity                                           |  |  |  |

| φs             | V         | Surface Potential                                               |  |  |  |

| $	au_{ m e/c}$ | s         | Time constant of single electron emis-<br>sion/capture (e/c)    |  |  |  |

### INTRODUCTION

## 1

### Background

"Opposites are not contradictory but complementary."

- Niels Bohr

transistor is a device in which the conduction between two electrodes can be controlled by its third electrode. Since this unique device was first invented in 1947 at Bell Laboratories, the era of semiconductor electronics has been opened and has remarkably changed our daily life. According to the Semiconductor Industry Association (SIA), sales in the global semiconductor industry reached \$574.1 billion in 2022, marking the highest annual total to date and a 3.3% increase from 2021 [1] due to the continuously strong demand in the market particularly in consumer electronics and electrical vehicles driven by emerging technologies mainly including IoT, cloud computing, 5G network, and AI. When amazed by the capability of modern electronics, a huge amount of power consumed by data computing and storage has become a big concern in industry. For instance, over the past few years, the energy consumption in large data centers has been on the rise, increasing by 10-30% annually, due to the significant increase in workloads being processed [2]. Therefore, many measures including optimizing the thermal management and hardware architecture have been taken to improve the energy efficiency. As the essential building block for microelectronics, the development of a single transistor with improved performance and reduced power consumption is crucial to directly impact circuits and further systems. In fact, back to 1980s, with the same regard on the power consumption, Si bipolar transistors which used to be the mainstream in the early stage of integrated circuits (ICs) were replaced by CMOS technology where both ntype and p-type MOSFET are connected in a certain way. In the following decades, MOSFETs have dominated the digital circuits and enabled very largescale integrated (VLSI) circuits owing to their high scalability and energy efficiency.

In this chapter, we will generally go through the basic history of MOSFET architectures, the potential and challenges for III-V transistors and their integration with emerging technologies. The key motivation and contribution of this thesis will be briefly addressed. We mainly discuss MOSFETs in the entire thesis when mentioning transistors without specification.

#### 1.1 TRANSISTOR ARCHITECTURE: PAST, PRESENT, AND FUTURE

Dennard's scaling indicates that shrinking transistor size allows high density package in the same chip area and lowers the operating voltage, thereby reducing power consumption and the cost per transistor [3]. By consuming less energy per switching event per transistor, it is possible to fit more logic gates into the IC, resulting in faster switching speed while keeping the same power budget.

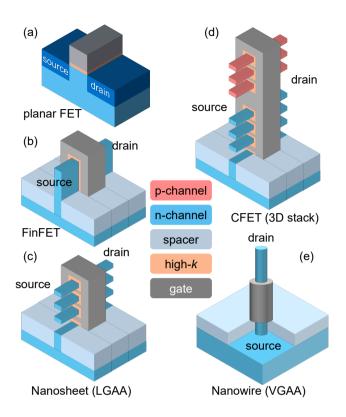

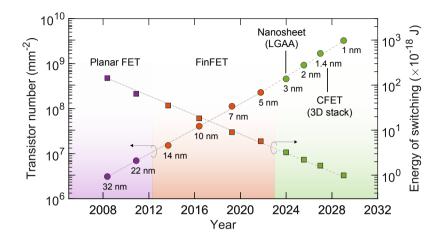

In 1965, the founder of Intel, Gordon Moore, predicted that the transistor density would be doubled every 2 years based on the aggressive scaling of the geometry. This so-called Moore's law was proved to exactly fit the industrial roadmap of transistor scaling in planar MOSFETs whose structure is presented in Fig 1.1a. In such a device, a planar channel along with a high-permittivity (high- $\kappa$ ) dielectric and metal gate is used to control the current flow injected from the source to the drain which is typically highly doped. However, when miniaturizing towards 22 nm or downward, the electrostatics over the MOS structure degrades dramatically, deteriorating the switching behavior and skyrocketing the power dissipation. This led to inhibition in further gate-length downscaling. The invention of FinFET saved the continuation of Moore's law by using a fin as the channel with a trigate to improve the electrostatic control of the transistor (Fig. 1.1b). This architecture is still used in most of electronics requiring advanced technology nodes, including CPUs in laptops and smart phones. Figure 1.2 shows the excellent extension of Moore's law and reduced switching energy with FinFET architecture. Gate-all-around (GAA) geometry with a wrapped gate surrounding the channel is regarded to give the best electrostatics for the transistor. Nanosheets with LGAA structure (Fig. 1.1c) has been demonstrated for the next technology node beyond 3 nm (Fig. 1.2). By vertically stacking multiple layers of nanosheets, the transistor performance can be enhanced [4]. The same architecture can be extrapolated to complementary FETs (CFETs)

with vertically stacking both n- and p-type MOSFETs (Fig. 1.1d), which have been demonstrated experimentally [5] for 3D IC. In accordance with IEEE International Roadmap for Device and Systems (IRDS) 2022 [6], the CFET structure can possibly extend Moore's law to 0.5-nm equivalent technology node in 2037, leading to attojoule switching energy per transistor as indicated in Fig. 1.2. Compared to lateral FETs, further scaling of footprint can be achieved in vertical GAA (VGAA) nanowire/nanosheet FET (Fig. 1.1e) which allows independent optimization of gate-length and spacer width to possibly minimize the device area [7].

#### **1.2 III-V SEMICONDUCTOR: OPPORTUNITY AND CHALLENGE**

In MOSFETs, high carrier mobility in the channel is desirable to increase the current at the drain side ( $I_D$ ) and a higher  $I_D$  results in a higher operating frequency. III-V compound semiconductors (an alloy with group-III and group-IV elements) are one of the potential candidates that may replace Si as the channel of MOSFETs due to their superior electrical properties (see Table 1.1) such as high mobility and injection velocity [9]. Given this III-Vs have been widely explored in high frequency applications. For instance, GaAs-based heterojunction bipolar transistors (HBTs) have been already commercially available for power amplifiers in wireless communications [10] and InAs-based high electron mobility transistors (HEMTs) have reached a cutoff frequency up to 628 GHz [11]. Furthermore, with the rapid revolution in quantum computers using superconducting or spin qubits as the quantum circuits, III-V-based MOSFETs [12] and HEMTs [13] have also shown tremendous attraction with fast switching for peripheral modules of signal readout at cryogenic temperatures.

In digital applications, it is difficult to take the most advantage of both electron and hole mobility in a single III-V material, leading to challenges in competing with Si CMOS. Nevertheless, as noted in Table 1.1, InAs and GaSb are almost lattice-matched and have the highest electron and hole mobility, respectively. Many efforts have been made to co-integrate InAs n-MOSFET (n-FET) and GaSb p-MOSFET (p-FET) for CMOS logic gates. So far, various device architectures including planar InAs/GaSb on Si box [14], LGAA nanowires [15], VGAA monolithic InAs/GaSb co-integration [16, 17] have been reported. Although arsenide-based n-FETs can well outperform their Si counterparts, antimonide-based p-FETs are still far below the expectation, resulting in unmatched performance. There are two major challenges constraining the development of high-performance antimonide-based p-FETs. First, ohmic contact with low resistance is still lacking for antimonides, which hinders further enhancement of the drive current in the on-state. Some recent

**Figure 1.1:** Evolution of MOSFET architecture with footprint scaling. (a) Planar high- $\kappa$  metal-gate (HKMG) MOSFET. The dielectric with high permittivity such as HfO<sub>2</sub> combined with metal gate electrode is used for improving the electrostatic control beyond SiO<sub>2</sub>/poly-Si gate-stack. (b) FinFET has been utilized beyond 22-nm node and has boosted the transistor performance. A tri-gate is used for retaining electrostatics with gate-length scaling. (c) LGAA configuration with nanosheets is considered as the device architecture of the technology nodes beyond 5 nm to improve the electrostatic confinement. (d) Continuous scaling for higher transistor density, CFETs with 3D stack of n and p-type nanosheet FETs can be used. (e) VGAA nanowire FETs can further scale the pitch between gates which is a limit of lateral FETs. This VGAA architecture may continue the Moore's law beyond 2040.

efforts such as capping III-Sb with p-type InAsSb thin layer [18] and alloying Ni into antimonide source and drain by annealing [19] have been investigated to improve the contact resistance. Second, high-quality high- $\kappa$  oxide/III-Sb interface is lacking. As seen in Table 1.1, a high interface trap density typically exists in GaSb due to rich oxide states at the surface [20], causing

**Figure 1.2:** MOSFET scaling can still follow Moore's law nicely with future hyper scaling technologies. The energy of per switching per transistor can be further reduced towards atto-joule regime. Data are from Ref. [8].

a detrimental electrostatic control for MOSFETs. As a result, the effective hole mobility in GaSb MOSFETs is only one tenth ( $\sim 100 \text{ cm}^2/\text{Vs}$ ) [21] of its bulk value (Table 1.1). In scaled nanowire MOSFETs, higher surface-volume ratio could introduce more surface scattering to the channel, leading to even lower mobility ( $\sim 70 \text{ cm}^2/\text{Vs}$ ) [22]. This limits the switching behavior when further downscaling the device. Recently, an unconventional approach using template-assisted selective epitaxy, a high hall-effect hole mobility of  $\sim 760 \text{ cm}^2/\text{Vs}$  has been achieved in an ultra-scaled dimension down to 20 nm [23], close to the bulk value although no MOSFETs have been fabricated.

In line with the goal of energy efficiency, novel device concepts beyond CMOS technology have been investigated recently. Steep-slope transistors are a promising device variant that allows transistors to switch on/off using a voltage swing below the physical limit of conventional MOSFETs. TFETs whose transport mechanism relies on band-to-band tunneling (BTBT) are one of these steep-slope devices [26, 27], aiming for low-power circuits and systems such as IoT and biosensors. Among many semiconductors, III-V heterostructures stand out for this type of devices due to their rich alloy combinations in optimization of band alignment for tunnel junction [28, 29], thereby being additional opportunity for future III-V based electronics.

| Kei. [24]). Lattice and mobility data are from Kei. [25]. |       |             |              |                                    |                   |

|-----------------------------------------------------------|-------|-------------|--------------|------------------------------------|-------------------|

| material                                                  | $a_0$ | $\mu_{e}$   | $\mu_{ m h}$ | D <sub>it</sub> level <sup>a</sup> | $k_{\mathrm{th}}$ |

|                                                           | (Å)   | $(cm^2/Vs)$ | $(cm^2/Vs)$  | $(eV/cm^2)$                        | (W/mK)            |

| Si                                                        | 5.43  | 1400        | 450          | $\sim 10^{10}$                     | 145               |

| GaAs                                                      | 5.65  | 8500        | 400          | $\sim 10^{12}$                     | 44                |

| InAs                                                      | 6.06  | 13000       | 500          | $\sim 10^{12}$                     | 27                |

| GaSb                                                      | 6.09  | 3000        | 1000         | $\sim 10^{13}$                     | 33                |

**Table 1.1:** Comparison of Si and common III-V materials with various parameters at 300 K: lattice constant ( $a_0$ ), electron ( $\mu_e$ ) and hole mobility ( $\mu_h$ ), interface trap density ( $D_{it}$ ), and thermal conductivity ( $k_{th}$ , data from Ref. [24]). Lattice and mobility data are from Ref. [25].

<sup>a</sup> Typical order of magnitude regardless interface treatment.

#### **1.3 HETEROGENEOUS INTEGRATION**

By following the geometrical scaling (shrinking size) and the equivalent scaling (strained Si, HKMG, and non-planar FETs), advanced electronics will enter a hyper-scaling era through future innovations at different levels including from materials and devices to systems [30], enabling possible avenue to continue Moore's law beyond the physical dimension of a single transistor.

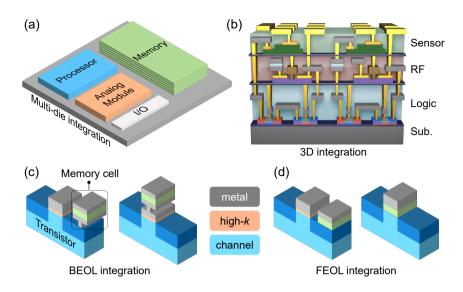

One of the key approaches is heterogeneous integration where various technological platforms are assembled in a dense way to realize diverse functionalities while keeping the total area. At the system level, multidie integration technology (Fig. 1.3a) offers a possible way to interconnect different function chips on one platform rather than separately packaging them, enabling a low-cost, low-power, and low-latency system [31]. To further increase the package density as well as to maximize the performance of different technologies (e.g. Si CMOS for logic while III-V HEMTs for RF component) on a one IC wafer, 3D vertically stacked integration (Fig. 1.3b) has been proposed and demonstrated using bonding technique which can mitigate the monolithic integration of III-V on Si due to the large mismatch in lattice constant and thermal expansion (see  $a_0$  and  $k_{th}$  in Table 1.1) [32].

At the device level, integration of memory cells directly into a computing device (e.g. MOSFET) has been under intensive investigation for braininspired or in-memory computation due to the high potential to break through the bottle-neck of conventional von Neumann architectures which physically separate the computing and memory chips thus being latencyand energy-inefficient. Depending on the practical purpose and the technical approach, there are typically two integration schemes of memory cells on a

**Figure 1.3:** Schematics of potential heterogeneous integration at different levels. (a) A multi-die system with all die-to-die interconnections on the same package wafer. (b) 3D IC integration of different function dies in a vertical direction, thus shrinking the package area. Device-level in-memory computing unit with (c) BEOL and (d) FEOL integration.

transistor: on the drain or on the gate. Moreover, the memory cell can be integrated after the computing devices (e.g. CMOS) are fabricated (BEOL, see Fig. 1.3c) or directly integrated during the computing device fabrication process (FEOL, see Fig. 1.3d). Recently, the rapid development of non-volatile memories based on diverse materials such as ferroelectrics, resistive oxides, and phase-change materials has boosted the research of in-memory computing [30].

An energy- and area-efficient hardware architecture for artificial neural networks (ANN) is crossbar arrays with massive multiply-and-accumulate (MAC) operations in parallel, enabling high-speed matrix-based computations. In this regard, a VGAA device structure with both logic and memory in one nanowire is preferred to achieve the theoretical minimum feature size of one cell. Given this a high-density VGAA-nanowire-based device has been recently reported by using a nanowire transistor as a selector to activate the FEOL-integrated RRAM cell and an NAND logic gate has also been implemented in the same structure, thereby realizing in-memory computing [33]. Specifically, part of this thesis aims for integrating HfO<sub>2</sub>-based ferroelectric gate-stack onto a III-V nanowire platform (Paper IV, V & VI) to add reconfigurability into conventional transistors, thus realizing high functional diversity in a single device.

# 2

### **Transistor Fundamentals**

HE general work principles and key concerns of III-V vertical nanowire MOSFET, TFETs, and FeFETs will be discussed in this chapter. Note that a detailed discussion of ferroelectric material and device physics is out of the scope of this thesis.

#### 2.1 BASICS OF MOSFETS AND TFETS

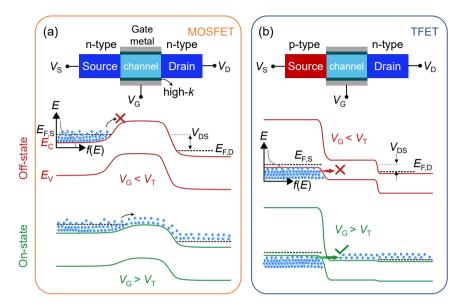

In a n-type MOSFET as shown in Fig. 2.1a, the source and drain are highly n-type doped with a Fermi level ( $E_{F,S}$  or  $E_{F,D}$ ) close or higher than the conduction band edge ( $E_C$ ), leading to high electron concentration (obeying Fermi-Dirac distribution, f(E)). A source-drain bias ( $V_{DS}$ ) is applied to create an electrical field for electrons to flow from the source to the drain. The channel between the source and drain is like the traffic lights which allow (on-state,  $V_G > V_T$ ) or block (off-state,  $V_G < V_T$ ) the electron flow by setting the height of the energy barrier through a gate voltage ( $V_G$ ) across the MOS structure. In the case of p-FETs, the source and drain are p-type doped, thus the corresponding  $E_F$  close to the valence band edge ( $E_V$ ). For III-V materials, group IV elements such as C, Si, and Sn are commonly used as the dopant since they can be either donors (n-type) or acceptors (p-type) depending on which site (group-III or group-V) in the crystal is replaced [34].

Unlike MOSFETs where charge carriers are thermally injected over a barrier, interband tunneling, or BTBT, is the primary injection mechanism in TFETs in which a gated p-i-n structure typically exists (Fig. 2.1b). By controlling the band bending in the unintentionally doped channel via  $V_G$ , TFETs can be switched on and off abruptly. In the off-state of a n-type TFET (Fig. 2.1b), the  $E_{\text{FS}}$  is located below the channel  $E_C$ , and thus BTBT is suppressed, resulting

in a low off-state current ( $I_{off}$ ). In the on-state when applying a larger  $V_G$ , the  $E_C$  in the channel is pulled down to the position below the source  $E_V$  so that many vacancies above the channel  $E_C$  are available for electrons to tunnel, leading to strong BTBT and increased tunneling current.

**Figure 2.1:** Basic mechanism from the perspective of band diagram in (a) MOSFETs and (b) TFETs. The main difference between the two device structures is that only one type of doping (either n- or p-type) is needed for source and drain in MOSFETs while a p-i-n structure is conventionally used for TFETs. In the off-state of MOSFETs,  $E_C$  of the channel is much lower than  $E_{F,S}$ , so the electrons barely cross the barrier to the drain; in the on-state, the energy barrier is lower enough and  $E_{F,S}$  is above the channel  $E_C$  so that electrons can freely flow to the drain. In the case of TFETs, electrons can tunnel from the source to the channel through the tunneling barrier only when the channel  $E_C$  is lower than  $E_{F,S}$ . The schematics denote the ideal cross-section of GAA nanowire transistors.

#### 2.1.1 METRICS OF TRANSISTOR PERFORMANCE

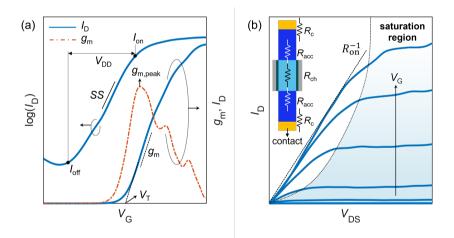

The current collected from the drain side ( $I_D$ ) is the essential metric when evaluating the performance of a transistor. The relationship of  $I_D$  and the voltage applied to the three terminals can reflect the intrinsic properties of the device. Two major characteristics named transfer characteristic ( $I_D - V_G$ ) and output characteristic ( $I_D - V_{DS}$ ) are illustrated in Fig. 2.2 a and b, respectively, deriving many key performance metrics that are discussed below.

- On- and off-current: *I*on and *I*off

- $I_{\rm on}$  and  $I_{\rm off}$  are commonly defined as the minimum and maximum  $I_{\rm D}$ in the voltage span of a certain  $V_{\rm DS}$  in the transfer curve (Fig. 2.2a), respectively. The ratio between  $I_{\rm on}$  and  $I_{\rm off}$  is called on-off current ratio  $(I_{\rm on}/I_{\rm off})$ , which is expected as large as possible to distinguish the on- and off-state within a small  $V_{\rm G}$ . A typical assessment of transistor performance made from various technologies is to compare their  $I_{\rm on}$  at the same  $I_{\rm off}$ and  $V_{\rm DS}$ . In industry,  $I_{\rm off}$  is usually application-dependent. For instance, in the low-power system an  $I_{\rm off} = 5$  nA/ $\mu$ m is required to lower the static power dissipation according to the specification under low operation power (LOP) condition [35].

- Threshold voltage: V<sub>T</sub>

$V_{\rm T}$  is the critical voltage that distinguishes the on- and off-state (Fig. 2.2a). Many factors such as temperature, channel size, and dielectric thickness affect  $V_{\rm T}$  of a transistor. The difference between  $V_{\rm G}$  and  $V_{\rm T}$  is called overdrive voltage ( $V_{\rm OV} = V_{\rm G} - V_{\rm T}$ ).

• Subthreshold swing: SS SS is defined as how much voltage needs to change *I*<sub>D</sub> by one order of magnitude in the subthreshold region (Fig. 2.2a) with the expression given by,

$$SS = \frac{\partial V_{G}}{\partial log(I_{D})} = \ln(10)\frac{k_{B}T}{q}(1 + \frac{C_{dep}}{C_{ox}}) \ge \ln(10)\frac{k_{B}T}{q} \approx 60 \,\text{mV/dec}\,(300 \,\text{K})$$

(2.1)

where  $k_{\rm B}$  is the Boltzmann constant, *T* the temperature, *q* the electron charge,  $C_{\rm dep}$  and  $C_{\rm ox}$  the depleted and the gate oxide capacitance, respectively. SS mainly describes the steepness of the switching, thereby depending on the electrostatic control over the MOS capacitor. As Eq. (2.1) points out, the minimum SS at room temperature (300 K) of a conventional MOSFET is limited to 60 mV/dec due to the thermal injection of the carrier. However, SS can be further reduced below this limit in TFETs where the BTBT governs the carrier transport. As seen in Fig. 2.1b, the bandgap of the source cuts off the band tail of f(E), thereby filtering out the high-energy electrons. This well suppresses the thermionic leakage in the off-state compared to MOSFETs. Consequently, a larger  $I_{\rm on}/I_{\rm off}$  can be (ideally) achieved in TFETs with the same  $V_{\rm G}$  swing. In other words, a smaller  $V_{\rm G}$  swing is needed in TFETs than in MOSFETs to switch the current to the same level, thus lowering the power consumption.

• Transconductance:  $g_m$  $g_m = \partial I_D / \partial V_G$  is defined as the linear slope in the transfer curve shown in Fig. 2.2a, representing the efficiency of gate modulation of the transistor. The maximum value of  $g_m$  ( $g_{m,peak}$ ) is an important metric that effectively influences  $f_T$  and the maximum oscillation frequency ( $f_{max}$ ) in the RF performance of a transistor. A high  $g_m$  also means a larger gain through a transistor as it relates the input ( $V_G$ ) and the output signal ( $I_D$ ). Thus,  $g_m$  is also crucial for amplifiers and logic gates.

• On-resistance: Ron

$R_{\rm on}$  is typically the reciprocal of the largest slope of  $I_{\rm D} - V_{\rm DS}$  relation in the output characteristic as shown in Fig. 2.2b and is the total series resistance in the on-state consisting of contact resistance ( $R_{\rm c}$ ), access resistance of both the source and drain side ( $R_{\rm acc}$ ), and the channel resistance ( $R_{\rm ch}$ ) as the inset shows. Therefore, the reduction in any component of the resistance can lower  $R_{\rm on}$ , resulting in an improved on-state performance.

**Figure 2.2:** Typical performance metrics in MOSFETs. (a) Transfer characteristics. (b) Output characteristics with good saturation region. The inset illustrates all the components of ( $R_{on}$ ). The color codes are identical to Fig. 2.1a

Other metrics such as output conductance ( $g_d = \partial I_D / \partial V_{DS}$  reflects the transistor ideality in the saturation region of the output characteristic, see Fig. 2.2b) are also important but not highly relevant, and hence deep discussion of those metrics is out of the scope in this thesis.

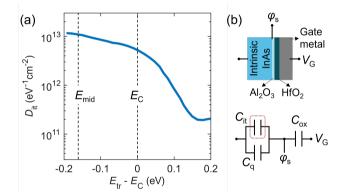

#### 2.1.2 INTERFACE TRAPS

As discussed in Chapter 1,  $D_{it}$  is considerably higher at the III-V/oxide interface as compared to Si since there is no suitable native oxide that can be used as dielectric like Si/SiO<sub>2</sub> in III-V materials. The surface of III-V materials may thus be oxidized or contaminated in the unvacuumed environment before depositing the gate oxide, leading to surface states due to imperfection. For example, faulty III-V bonds or dangling bonds can cause interface traps with the energies above  $E_C$  of InAs [36]. Also, the imperfection of gate oxide such as oxygen vacancies can generate interface defects with energies either above  $E_C$  and below  $E_C$  of III-V materials [37], being detrimental to n- or p-channel. As the gate oxide is typically amorphous, interface traps are expected to have distributions as a function of energy states. For instance, Fig. 2.3a shows the  $D_{it}$  distribution as the trap energy level ( $E_{tr}$ ) with respect to  $E_C$  in the intrinsic InAs nanowires.

**Figure 2.3:** (a) A representative  $D_{it}$  distribution of intrinsic InAs nanowires extracted by *C-V* measurements from Ref. [38]. (b) Schematic of the InAs/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/metal MOS structure and the corresponding capacitance model.

The existence of interface defects is considered as an extra charging event, which can be modeled as a paralleled capacitance ( $C_{it} = qD_{it}$ ) with the quantum capacitance ( $C_q$ ), and then in series with the gate-oxide capacitance ( $C_{ox}$ ), see Fig. 2.3b. Hence, the surface potential  $\varphi_s$  can be written as the voltage division of  $V_G$  and then SS can be related to  $D_{it}$  as below,

SS = ln(10)

$$\frac{k_{\rm B}T}{q}(1 + \frac{C_{\rm q} + qD_{\rm it}}{C_{\rm ox}})$$

, (2.2)

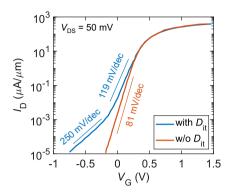

reflecting that SS linearly depends on  $D_{it}$ . As shown in Fig. 2.4, SS evidently degrades when the transistor has higher  $D_{it}$ .

**Figure 2.4:** The impact of  $D_{it}$  on the simulated transfer characteristics of an InGaAs MOSFET. Data are from Ref. [39]. The SS degrades with presence of high  $D_{it}$  (~ 10<sup>13</sup> eV<sup>-1</sup>cm<sup>-2</sup>) due to the donor-like interface defects.

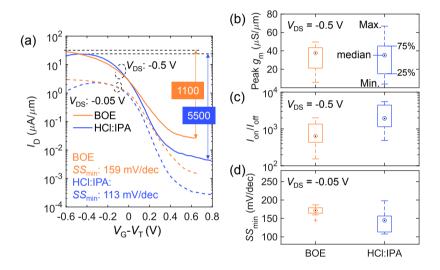

Numerous investigations have aimed to suppress  $D_{it}$  or displace them beyond the energy range that is operated in MOSFETs. Various methods of III-V surface passivation via certain chemicals by wet etching [40] or using forming gas [41] while annealing has been suggested to decrease  $D_{it}$  and improve SS. Additionally, the self-cleaning phenomenon during the ALD process with inserting an Al<sub>2</sub>O<sub>3</sub> interfacial layer at high growth temperature between III-V channel and HfO<sub>2</sub> high- $\kappa$  has been detected [42], and thus such bilayer Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> (1 nm/3 nm) high- $\kappa$  is used for transistor fabrication in this thesis.

As discussed before, GaSb has a large number of surface oxide states due to its thick native oxide easily growing even during the air [43]. One of the main goal of this thesis is to improve the quality of GaSb/gate-oxide interface using different ways (see Chapter 4), lowering SS and  $I_{off}$  to enhance the switching performance in III-V p-FETs.

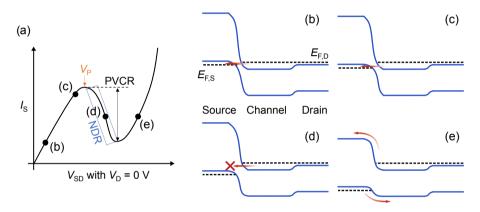

#### 2.1.3 NEGATIVE DIFFERENTIAL RESISTANCE

When reversely biasing the source and drain (common drain configuration,  $V_{\rm SD} > 0$ ) in a TFET, a featured negative differential resistance (NDR) can be generally observed (Fig. 2.5), being evidence of tunneling junction within the device. This effect has been also studied well in Esaki diodes which is a reversely-biased p-n junction [44,45]. Figures 2.5b–e elucidate the cause of this phenomenon. By gradually sweeping  $V_{\rm SD}$ , the band edges at the source move down and enlarge the tunneling window (difference between  $E_{\rm F,S}$  and  $E_{\rm F,D}$ , see Fig. 2.5b–c). This increases the tunneling current until  $E_{\rm V}$  at the source aligns  $E_{\rm C}$  at the channel reaching the peak current at  $V_{\rm SD} = V_{\rm P}$ .

Further increasing  $V_{SD}$ , the tunneling path is prohibited, and the current decreases (Fig. 2.5d), leading to an NDR region (Fig. 2.5a). When source bands are lowered enough so that carriers are able to thermally overcome the energy barrier (Fig. 2.5e), the current substantially increases again. Therefore, a current peak and valley are typically observed and their ratio (PVCR) is defined as a metric to evaluate the quality of the tunnel junction. However, NDR effect is unnecessary to be seen in all TFETs and depends on the structure design and material selection [46].

**Figure 2.5:** NDR effect in TFETs. (a) NDR *I-V* curve of a TFET at a fixed  $V_{\rm G}$ .  $V_{\rm P}$  is the corresponding voltage at the current peak and the peak-valley current ratio (PVCR) typically describes how strong the NDR effect is. (b–e) Schematics of band diagrams at different  $V_{\rm SD}$  indicated in (a).

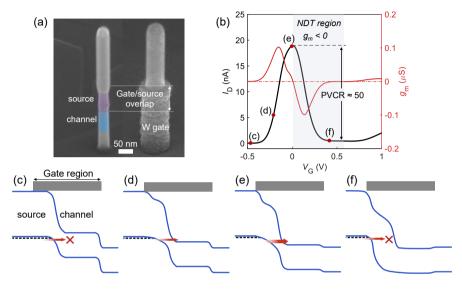

# 2.1.4 NEGATIVE TRANSCONDUCTANCE

In heterostructure TFETs, the gate placement is critical. Earlier work has shown that aligning the gate position overlaying more with the source segment (see Fig. 2.6a) gives lower  $I_D$  due to the strong source depletion [47, 48], leading to a small region with negative transconductance (NTC). This phenomenon can be explained by the band diagram in Fig. 2.6c–f where the bands of gate-overlapped source segment move down at high  $V_G$ , leading to the prohibition of BTBT, thus lowering the current. By intentionally modifying the source doping and increasing the overlapped region, even strong NTC can be achieved [49] and a parabola-shaped symmetric transfer is then obtained with equally large positive and negative  $g_m$  (Fig. 2.6b). Although from the performance perspective of TFETs, the presence of NTC is undesirable, many recent investigations with wide range of materials [50–52] have suggested wide potentials with NTC for multi-valued logic gates [52,53],

artificial synapses [50], and frequency doubling [54, 55], which may expand the application of using TFETs in a different way. We, in this thesis explore, this NTC feature in III-V TFETs for its application in signal modulation by carefully designing the gate/source overlap structure.

**Figure 2.6:** NTC in gate/source overlapped TFETs. (a) SEM image of a nanowire TFET post growth and during the fabrication after gate-length definition with gate/source overlap. (b) Representative transfer characteristic with strong NTC effect. A high PVCR of ~50 is obtained in this device. (c–f) Schematics of band diagram at various  $V_{\rm G}$  indicated in (a).

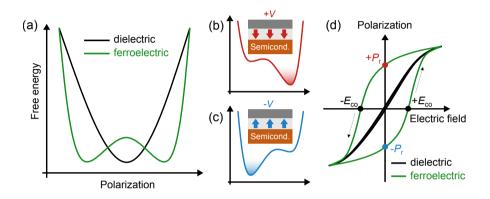

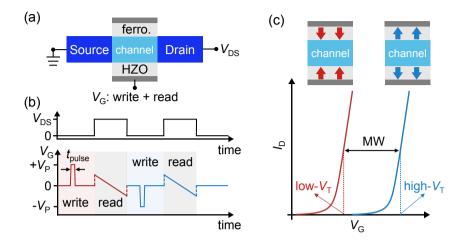

# 2.2 FERROELECTRIC FETS

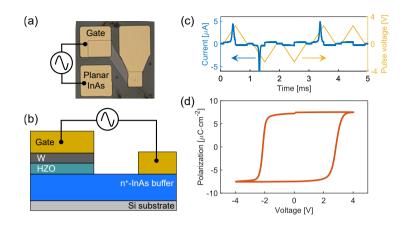

Ferroelectrics are materials with spontaneous electric polarization, which can be utilized for non-volatile memories and neuromorphic devices. Ferroelectric FETs (FeFETs) are a class of FETs that replace the dielectric gate-oxide with ferroelectric material in conventional MOSFETs. The first FeFET was proposed in 1963 by using triglycine sulphate as the ferroelectric gate insulator [56] and then had been under high interest in research and industry. However, the continuous development of FeFETs was constrained by the low compatibility with IC manufacturing, challenging scalability, and unstable performance. The discovery of ferroelectricity in doped HfO<sub>2</sub> [57] has then changed this situation and triggered a rethink of FeFETs. As we discussed in Chapter 1, non-ferroelectric HfO<sub>2</sub> has been already used in industrial Si MOSFETs as a high- $\kappa$  dielectric, so HfO<sub>2</sub>-based ferroelectrics are completely compatible with CMOS technology. Recently, robust ferroelectricity in ultra-thin HfO<sub>2</sub>-based films has been found [58, 59], in line with the trend of scalability of future electronics, leading to high promise for further studies of HfO<sub>2</sub>-based FeFETs. In this thesis, we mainly focus on the integration of Zr-doped HfO<sub>2</sub> (HZO) ferroelectric gate-stack on III-V vertical nanowire transistors as FeFETs rather than an in-depth discussion of HZO ferroelectrics.

**Figure 2.7:** (a) A double-well energy landscape of ferroelectrics as a function of electric polarization. (b–c) Two polarization states can be achieved by applying corresponding external voltages ( $\pm V$ ) at the ferroelectric MOS structure. Semiconductor is denoted by Semicond. (d) P - E hysteresis in dielectrics and ferroelectrics.  $P_{\rm r}$  is defined by the macroscopic polarization when no external electric field is applied while  $E_{\rm co}$  is the electric field at  $P_{\rm r} = 0$  macroscopically [60]. The arrows indicate a counterclockwise sweeping direction.

#### 2.2.1 REMANENT POLARIZATION

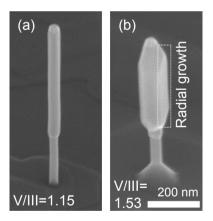

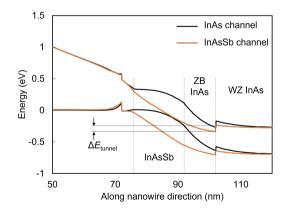

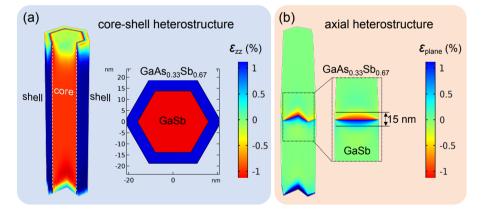

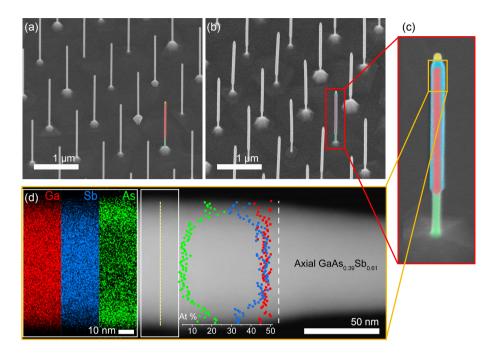

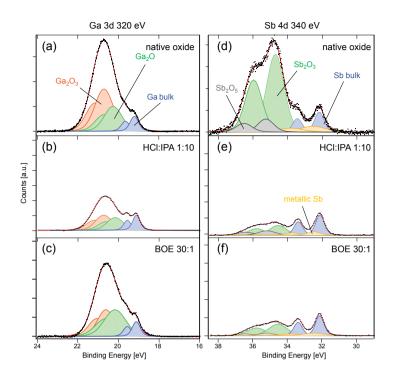

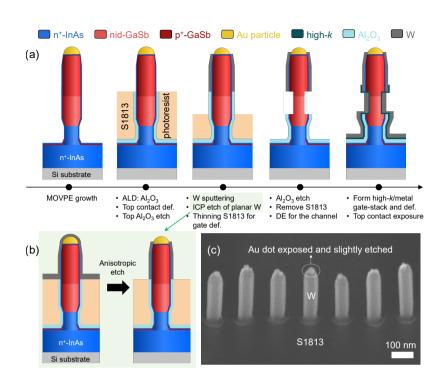

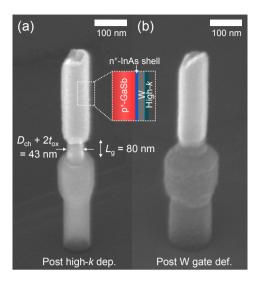

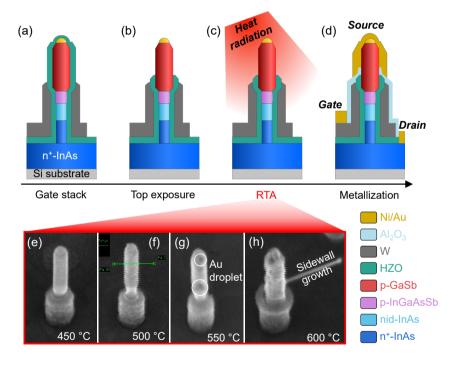

In amorphous dielectric materials, the lowest free energy is stabilized at zero polarization due to the isotropic nature as indicated in Fig. 2.7a. In contrast, ferroelectrics have two thermally stable lowest free energy point (double-well energy landscape) at different polarization states (Fig. 2.7a) due to the phase transitions during crystallization processing (e.g. rapid thermal annealing) in doped HfO<sub>2</sub> such as HZO [61]. The key element in FeFETs is the ferroelectric MOS structure in which the polarization switching can be controlled by applying an external electric field (voltage) as shown in Fig. 2.7b–c, leading to only one free energy minimum with one dominated polarization. The relationship between polarization and the applied electric field is shown in Fig. 2.7d where a representative polarization-field (P - E) hysteresis exists