#### Integrated millimeter Wave CMOS Power Amplifiers for 5G Systems

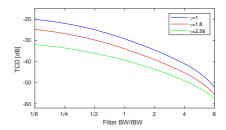

Elgaard, Christian

2024

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Elgaard, C. (2024). Integrated millimeter Wave CMOS Power Amplifiers for 5G Systems. Department of Industrial Electrical Engineering and Automation, Lund Institute of Technology.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Integrated millimeter Wave CMOS Power Amplifiers for 5G Systems

## Christian Elgaard

Doctoral Dissertation Lund, April 2024

Department for Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

ISSN 1654-790X-172 ISBN 978-91-8039-944-9 (print) ISBN 978-91-8039-945-6 (electronic) Series of licentiate and doctoral dissertations.

© Christian Elgaard 2024. Produced using IATEX Documentation System. Printed in Sweden by *Tryckeriet i E-huset*, Lund. April 2024.

### Abstract

The anticipated continuation of the last three decades of growth of global demand for high-speed high-coverage mobile data, calls for massive investments in cellular infrastructure, for the ongoing roll out of the fifth generation of mobile systems, but also later for the sixth generation. A key enabler, for the high-speed part, is for the cellular system to move up in frequency and support communication at millimeter-wave (mmW) frequencies (24 – 70 GHz), where available wideband spectrum exist. One of the most challenging building blocks for communication at mmW frequencies is the power amplifier, which has the function to amplify the transmission signal before feeding it to the antenna. The power amplifier should ideally provide high output power, without distorting the signal, while consuming as little power as possible. These requirements stand in stark contrast with each other and is particularly troublesome for high-speed communication at high frequencies. This dissertation is about mmW power amplifiers and it starts with introductory chapters, placing the power amplifier in its context and presenting theory about power amplifiers in general. Then follows a brief summary of the scientific contribution with conclusions and some suggestions for future work, of the four papers, which are the foundation of the dissertation.

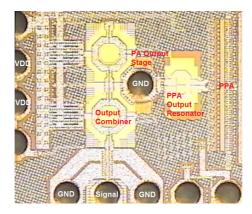

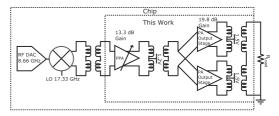

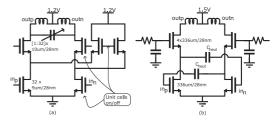

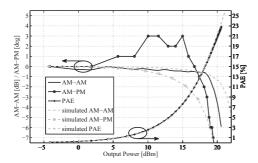

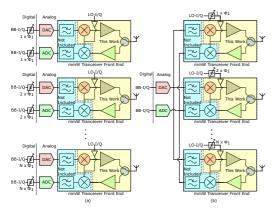

Paper I presents a CMOS mmW power amplifier and pre-power amplifier, with aim for integration in an antenna array system. To increase the output power, while still reducing the maximum needed supply voltage, the circuit utilizes a "two way" output combiner prior to the load. The PA, measured using continuous wave signals, reached, at the time, state-of-the-art performance for both saturated output power and 1 dB compression point, combined with low AM-PM distortion below the compression point.

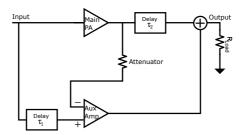

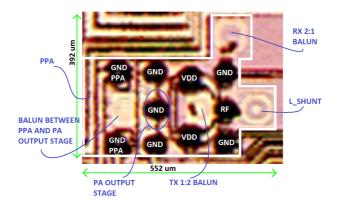

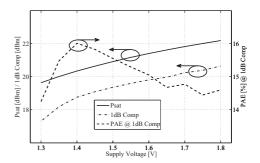

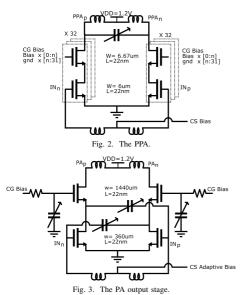

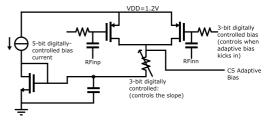

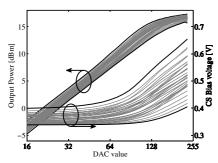

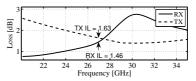

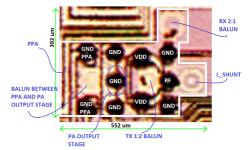

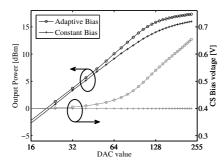

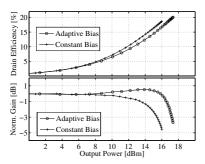

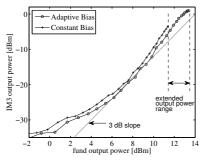

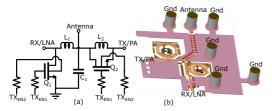

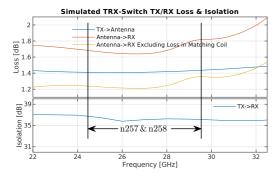

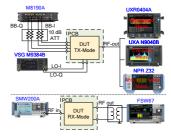

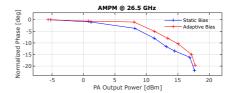

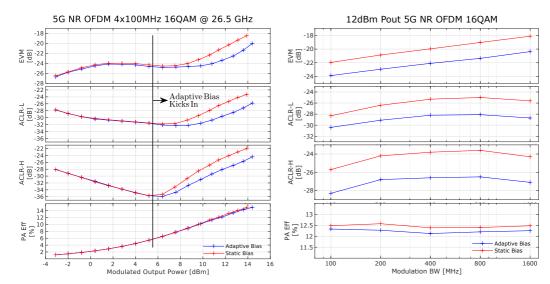

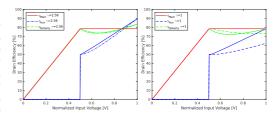

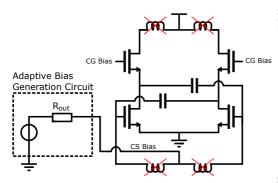

Paper II describes a CMOS mmW Transmit/Receive (TRX)-switch, power amplifier, and pre-power amplifier, targeted for integration in an antenna array system. To linearise the output signal the PA input transistors gate bias is adjusted based on the input signal level, i.e. it uses adaptive bias. The TRX-switch provides a downward 1:2 impedance transformation in TX-mode to boost reachable output power, and in RX-mode it provides an upward impedance transformation of 2:1 for optimal noise figure. The adaptive bias brings significant improvement of both saturated output power and 1 dB output compression point, and simulations for the TRX-switch show low insertion loss in both TX and RX mode.

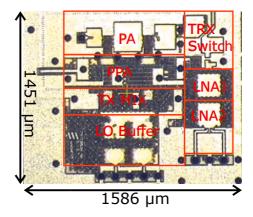

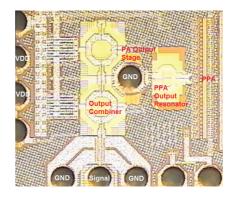

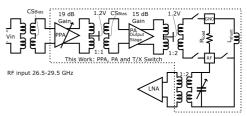

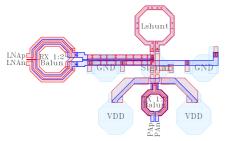

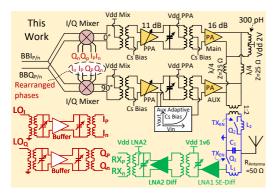

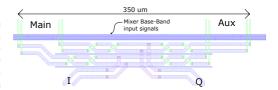

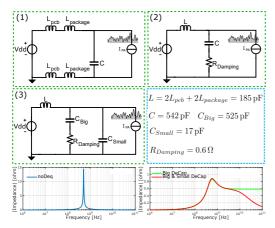

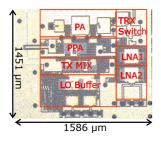

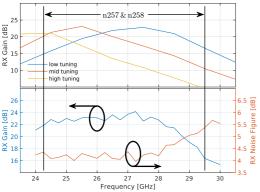

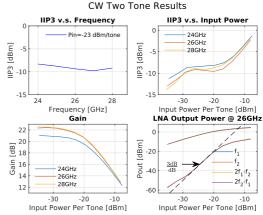

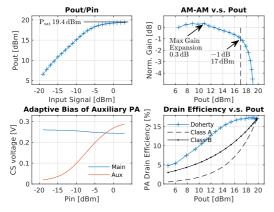

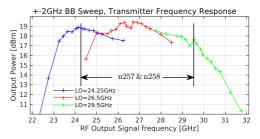

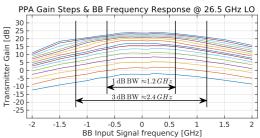

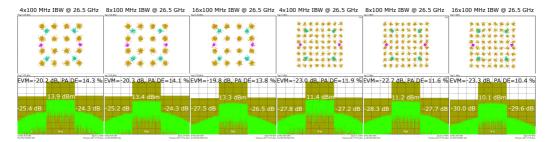

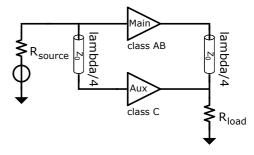

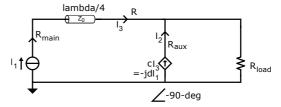

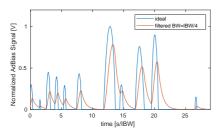

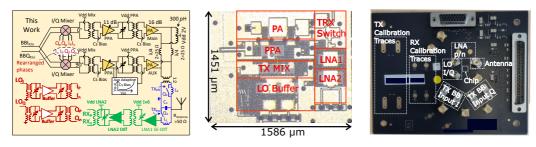

In **Paper III** a CMOS mmW transceiver front-end including a novel TRX-switch is presented. For high efficiency the transmitter is equipped with a Doherty PA, which uses a high bandwidth adaptive bias circuit to reduce the fundamental nonlinearity associated with Doherty PAs. In addition, an innovative method is implemented that breaks the fundamental bandwidth limi-

iv Abstract

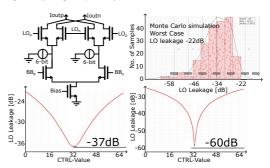

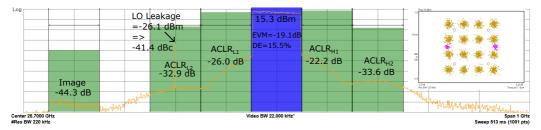

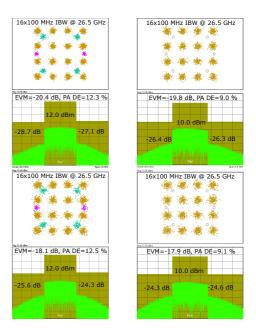

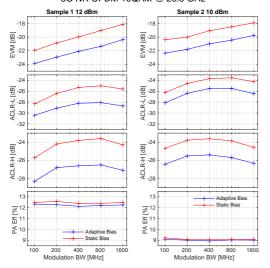

tation for the input signal of Doherty PAs. The transceiver was extensively measured in both transmit and receive mode. In transmit mode, continuous wave as well as OFDM-modulated measurements were performed. State-of-the-art output power and efficiency for integrated transceivers for high bandwidth OFDM-modulated signals were demonstrated, and for the receiver state-of-the-art noise figure was achieved when compared in the same category. Significant improvements on ACLR and EVM when using the adaptive bias for wideband modulated signals were demonstrated. Furthermore, excellent image rejection ratio and LO leakage suppression were measured.

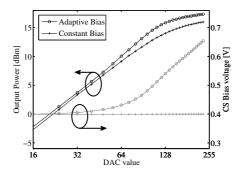

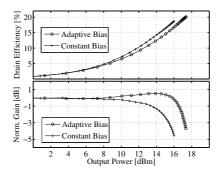

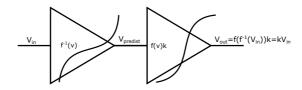

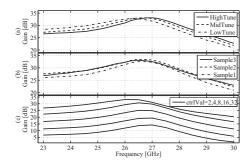

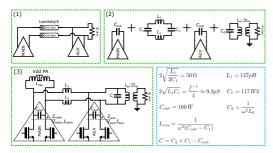

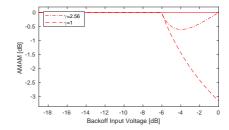

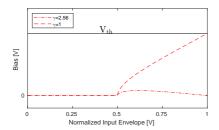

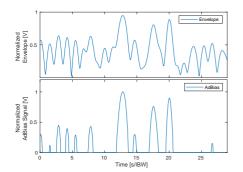

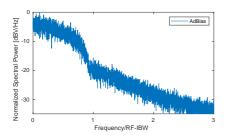

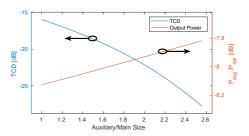

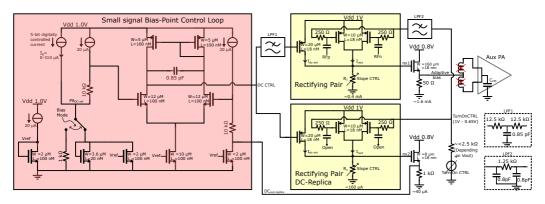

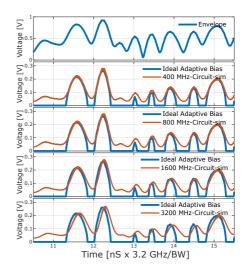

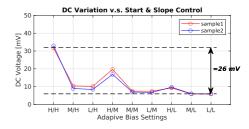

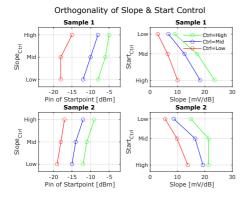

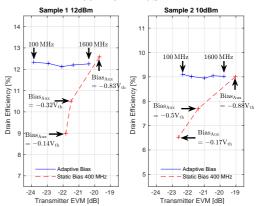

Paper IV derives fundamental equations related to a Doherty amplifier, using a simplified transistor model suitable for hand calculations, and thus the fundamental nonlinearity of the Doherty amplifier is explained and investigated. Furthermore, the paper analyses the use of adaptive bias, which offers the possibility to mitigate the fundamental nonlinearity as explained by the theory. To verify the theoretical predictions, the design and measurements of the adaptive bias circuit tailored for high PAR high bandwidth modulated signals, for the mmW Doherty amplifier in paper III, are presented in detail. Controllability of the adaptive bias circuit, which is needed to fully benefit from using adaptive bias, was measured using continuous wave tone stimuli. Multiple measurements with wideband OFDM-modulated signals were also conducted which largely verified the predictions by the theory. For increased reliability the measurements were repeated using two different samples.

# Populärvetenskaplig sammanfattning

I takt med att vi människor använder våra mobiltelefoner mer och mer och att vi samtidigt efterfrågar en allt högre datahastighet måste även mobilnätverken, som mobiltelefonerna kommunicerar med, anpassas för att klara av att leverera och ta emot den ökande datahastigheten och datamängden. Utvecklingen av de mobila nätverken och mobiltelefonerna går mycket snabbt och både datatrafiken och den genomsnittliga datahastigheten har fördubblats de senaste tre åren, och förväntningarna är att denna utveckling kommer att fortsätta. Varje mobiltelefon har både en sändare och en mottagare och det samma gäller basstationerna i mobilnätverken. I sändaren, både i basstationen och i telefonen sitter det, något förenklat, en effektförstärkare precis innan antennen. Effektförstärkaren i sändaren, som är huvudfokus för den här avhandlingen, har som uppgift att förstärka radiosignalen som skall skickas ut av antennen, så att signalen kan tas emot även om mottagaren befinner sig långt bort.

Ett sätt att kunna skicka mycket data snabbt är att använda en hög bandbredd. Det är tyvärr väldigt begränsat med tillgänglig bandbredd, men vid mycket höga frekvenser finns det fortfarande tillgängligt. Tyvärr finns det många svårigheter med att skicka trådlös information vid höga frekvenser. Det kanske mest problematiska är att eftersom antennstorleken minskar med ökad frekvens så kommer även mottagen signalstyrka att minska. Det är även svårare för signalen att penetrera byggnader, regn eller till och med löven på ett träd och elektroniken som sänder och tar emot signalerna fungerar generellt sämre. Frekvensområdet som ligger vid ca 30 GHz till 300 GHz kallas för millimetervågor eftersom våglängden för elektromagnetiska vågor i det området är 1 till 10 mm. För att kompensera för den stora signalförlusten mellan basstation och mobiltelefon vid millimetervågskommunikation använder man många antenner, flera hundra eller kanske till och med tusentals så kallade antennelement, vilket gör att man kan öka den mottagna signalstyrkan väldigt mycket

Den här avhandlingen handlar om effektförstärkare för millimetervågor konstruerade i en vanlig och billig kiselbaserad teknik som kallas för CMOS, för femte generationens mobilsystem, men även för kommande generationer. I avhandlingen ingår fyra vetenskapliga publikationer baserade på tre uppmätta effektförstärkare med gradvis ökande komplexitet där den tredje även innefattar i princip en hel sändare och även delar av en mottagare. Den tredje kretsen är uppmätt med en signal där effektförstärkaren skickar hela 9.6 Gbit/s, vilket är en väldigt hög datahastighet. För att exemplifiera skulle det motsvara att ladda ner cirka en hel timmes video på bara en sekund. För att klara av att skicka en signal med hög uteffekt och med så hög datatakt, utan förvränga den så att det blir svårt eller till och med omöjligt för mottagaren att avkoda

de digitala bitarna, och samtidigt förbruka så lite ström som möjligt, används en Dohertyförstärkare kombinerat med adaptiv bias. Dohertyförstärkaren är en välkänd förstärkartyp som uppfanns redan 1936, och den har den speciella egenskapen att den, jämfört med andra förstärkartyper, förbrukar väldigt lite ström när den förstärker signaler med kraftigt varierande amplitud, vilket är en en egenskap som signalerna i 5G (och 6G) har. För att spara ström har Dohertyförstärkaren två förstärkare som samarbetar. En av dessa är på hela tiden (huvudförstärkaren), medan den andra (hjälpförstärkaren) bara är på vid höga amplituder, vilket minskar förbrukningen. Det är dock en svår utmaning att konstruera en Dohertyförstärkare vid så höga frekvenser som millimetervågor vilket gör det intressant ur ett forskningsperspektiv. För att transistorerna skall förstärka signalen på önskvärt sätt behöver man ställa in en lämplig arbetspunkt, vilket kallas för att man förspänner transistorerna. Normalt använder man en konstant arbetspunkt, men vid adaptiv bias justerar man istället transistorernas arbetspunkter i takt med att signalen ändrar sin amplitud. Som framgått av forskningen i avhandlingen är Doherty förstärkare med adaptiv bias för hjälpförstärkaren ett bra sätt att minska de problem som uppstår när en effektförstärkare på ett strömsnålt sätt skall hantera de komplexa signalerna i 5G och framtidens mobilsystem. I den fjärde artikeln undersöks och förklaras de teoretiska aspekterna för hur en adaptiv bias signal skall utformas för att fungera optimalt ihop med hjälpförstärkaren, och artikeln innehåller även en detaljerad beskrivning av konstruktionen av en krets som klarar av skapa en sådan adaptiv bias signal och därmed kan ändra arbetspunkten för hjälpförstärkaren mycket snabbt, dvs. med hög bandbredd. Kretsen skapar adaptiv bias signalen genom att först extrahera amplitudinformationen ifrån Dohertyförstärkarens insignal. Ett viktigt teoretiskt resultat är att en ideal adaptiv bias signal sedan skall konstrueras genom en olinjär överföringsfunktion ifrån amplitudinformationen. Mätningar och simuleringar visar att kretsen klarar av att göra detta på ett effektivt sätt.

# Contents

| Abstract                           | iii                                       |

|------------------------------------|-------------------------------------------|

| Populärvetenskaplig sammanfattning | v                                         |

| Contents                           | vii                                       |

| Preface                            | xi                                        |

| Acknowledgments                    | xv                                        |

| List of Acronyms                   | xvii                                      |

| List of Symbols                    | xxi                                       |

| 1 Introduction                     | 5                                         |

| 2 Transmitter Architectures        | 7<br>9<br>12<br>13                        |

| 3 Power Amplifiers Metrics         | 17                                        |

| 4 Power Amplifier Classes          | 23<br>25<br>26<br>27<br>28<br>Gain,<br>29 |

| 4.2 Switched Mode PAs              | 32<br>35<br>35<br>39<br>41<br>43          |

| 5 Power Amplifier Linearity        |                                           |

viii Contents

|   | 5.1  | Time Invariant and Time Variant Systems 49 |                                                      |  |  |  |

|---|------|--------------------------------------------|------------------------------------------------------|--|--|--|

|   | 5.2  | Classi                                     | fication of Time Invariant Electrical Systems 50     |  |  |  |

|   |      | 5.2.1                                      | Linear Without Memory -Instantaneous Linear Sys-     |  |  |  |

|   |      |                                            | tem                                                  |  |  |  |

|   |      | 5.2.2                                      | Nonlinear Without Memory -Instantaneous Nonlinear    |  |  |  |

|   |      |                                            | System                                               |  |  |  |

|   |      | 5.2.3                                      | Linear With Memory -Stationary Linear System 51      |  |  |  |

|   |      | 5.2.4                                      | Nonlinear With Memory -Stationary Nonlinear Sys-     |  |  |  |

|   |      |                                            | tem                                                  |  |  |  |

|   | 5.3  | Source                                     | es of Nonlinearities and Memories in Electronic Sys- |  |  |  |

|   |      | tems                                       | 52                                                   |  |  |  |

|   |      | 5.3.1                                      | Sources of Nonlinearities                            |  |  |  |

|   |      |                                            | Nonlinear Transconductance 53                        |  |  |  |

|   |      |                                            | Nonlinear Output Conductance                         |  |  |  |

|   |      |                                            | Nonlinear Parasitic Capacitances 54                  |  |  |  |

|   |      |                                            | Passive Components                                   |  |  |  |

|   |      | 5.3.2                                      | Sources of Memories                                  |  |  |  |

|   |      |                                            | Electrical Memories                                  |  |  |  |

|   |      |                                            | Thermal Memories                                     |  |  |  |

|   | 5.4  | Impro                                      | ving Linearty                                        |  |  |  |

|   |      | 5.4.1                                      | Linearity Enhancements Techniques                    |  |  |  |

|   |      |                                            | Polar Loop Feedback                                  |  |  |  |

|   |      |                                            | Cartesian Loop Feedback 60                           |  |  |  |

|   |      |                                            | Feedforward                                          |  |  |  |

|   |      |                                            | Other Linearisation Methods 61                       |  |  |  |

|   |      |                                            | Adaptive Bias 61                                     |  |  |  |

|   |      |                                            | Derivative Superposition                             |  |  |  |

|   | 5.5  | Reduc                                      | ing Effects of Nonlinearty by Predistortion 63       |  |  |  |

|   |      | 5.5.1                                      | Analog Predistortion                                 |  |  |  |

|   |      | 5.5.2                                      | Digital Predistortion                                |  |  |  |

|   | 5.6  |                                            | ation Example of Memory Effects in an idealized CMOS |  |  |  |

|   |      |                                            | Power Amplifier                                      |  |  |  |

| 6 | Effi | cient                                      | Power Amplifiers                                     |  |  |  |

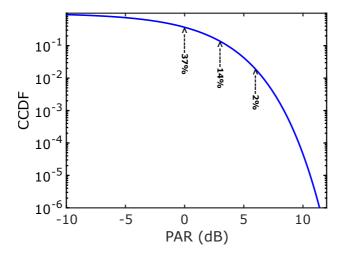

|   | 6.1  |                                            | to Average Ratio                                     |  |  |  |

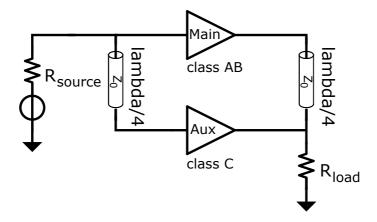

|   | 6.2  |                                            | ty Power Amplifier                                   |  |  |  |

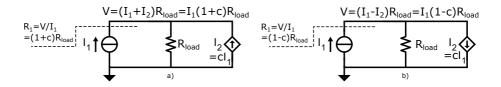

|   |      |                                            | Load Modulation                                      |  |  |  |

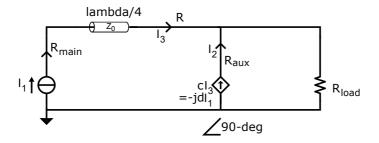

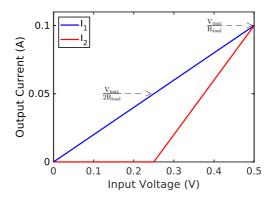

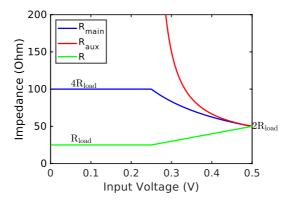

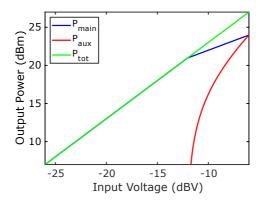

|   |      |                                            | Load Modulation in a Doherty Power Ampifier 79       |  |  |  |

|   |      |                                            | Conduction angle of Auxiliary Amplifier 83           |  |  |  |

|   |      |                                            | Efficiency of Ideal Doherty Amplifier                |  |  |  |

|   | 6.3  |                                            | nasing Power Amplifier                               |  |  |  |

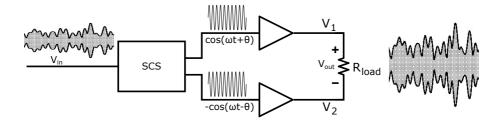

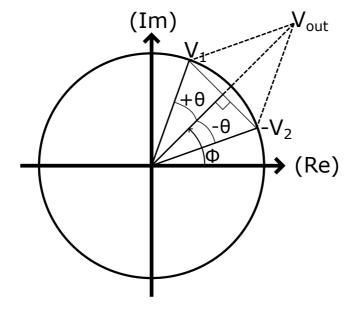

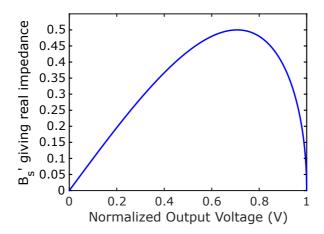

|   |      | 6.3.1                                      | Analysis of Simple Outphasing System 87              |  |  |  |

|   |      | 6.3.2                                      |                                                      |  |  |  |

|   |      | •                                          | 1 0 7                                                |  |  |  |

Contents ix

| 7 Sun<br>tion | mary of Included Papers with Scientific Contribu-                                                 | 95         |

|---------------|---------------------------------------------------------------------------------------------------|------------|

|               | Paper I: A 26 GHz 22.2 dBm Variable Gain Power Amplifier                                          | 55         |

|               | in 28 nm FD-SOI CMOS for 5G Antenna Arrays                                                        | 96         |

|               | 7.1.1 Overview                                                                                    | 96         |

|               | 7.1.2 Scientific Contribution                                                                     | 96         |

|               | 7.1.3 Comparison With State-of-the-art                                                            | 96         |

|               | 7.1.4 My Contribution                                                                             | 97         |

|               | Paper II: A 27 GHz Adaptive Bias Variable Gain Power Am-                                          |            |

|               | plifier and T/R Switch in $22\mathrm{nm}$ FD-SOI CMOS for 5G An-                                  |            |

|               | tenna Arrays                                                                                      | 98         |

|               | 7.2.1 Overview                                                                                    | 98         |

|               | 7.2.2 Scientific Contribution                                                                     | 98         |

|               | 7.2.3 Comparison With State-of-the-art                                                            | 99         |

|               | 7.2.4 My Contribution                                                                             | 99         |

|               | Paper III: Efficient Wideband mmW Transceiver Front-End for 5G Base Stations in 22 nm FD-SOI CMOS | 100        |

|               | 7.3.1 Overview                                                                                    | 100<br>100 |

|               | 7.3.2 Scientific Contribution                                                                     | 100        |

|               | 7.3.3 Comparison With State-of-the-art                                                            | 100        |

|               | 7.3.4 My Contribution                                                                             | 101        |

|               | Paper IV: Analysis and Design of a GHz Bandwidth Adaptive                                         | 101        |

|               | Bias Circuit for an mmW Doherty Amplifier                                                         | 102        |

|               | 7.4.1 Overview                                                                                    | 102        |

|               | 7.4.2 Scientific Contribution                                                                     | 103        |

|               | 7.4.3 Comparison With State-of-the-art                                                            | 103        |

|               | 7.4.4 My Contribution                                                                             | 103        |

|               | clusions, Discussion, and Future Work                                                             | 105        |

|               | Conclusions and Discussion                                                                        | 105        |

|               | Future Work                                                                                       | 106        |

| 0.2           | Tavaro Work                                                                                       | 100        |

| Appendi       | x A                                                                                               | 107        |

| A Fre         | quency Spectrum of a Two Tone Stimuli of an In-                                                   |            |

|               | taneous Third-Order Nonlinear System                                                              | 107        |

| Referenc      | ees                                                                                               | 109        |

|               | Hz 22.2dBm Variable Gain Power Amplifier<br>nm FD-SOI CMOS for 5G Antenna Arrays                  | 119        |

| plifie        | GHz Adaptive Bias Variable Gain Power Amrand T/R Switch in 22nm FD-SOI CMOS G Antenna Arrays      | 125        |

<u>x</u> Contents

| III Efficient Wideband mmW Transceiver Front-End for 5G Base Stations in $22\mathrm{nm}$ FD-SOI CMOS | 133 |

|------------------------------------------------------------------------------------------------------|-----|

| IV Analysis and Design of a GHz Bandwidth Adaptive Bias Circuit for an mmW Doherty Amplifier         |     |

### Preface

This dissertation concludes my academic contribution for a Ph.D degree in Electrical Engineering at Lund University, Sweden. The Ph.D studies were performed in the form of an industrial Ph.D in close cooperation with the section of RF Frontend and Power Amplifier Design at Ericsson Research in Lund, Sweden. The dissertation consists of two parts, the first contains a general overview and introduction to the field of power amplifier design, and the second part consists of the published research papers, listed below.

#### **Included Research Papers**

The contribution to the research field is summarized by the following publications:

- Paper I C. Elgaard, A. Axholt, E. Westesson and H. Sjöland, A 26 GHz 22.2 dBm Variable Gain Power Amplifier in 28 nm FD-SOI CMOS for 5G Antenna Arrays, 2018 Asia-Pacific Microwave Conference (APMC), Kyoto, Japan, 2018, pp. 965-967, doi: 10.23919/APMC.2018.8617416. [1]

- Paper II C. Elgaard, S. Andersson, P. Caputa, E. Westesson and H. Sjöland, A 27 GHz Adaptive Bias Variable Gain Power Amplifier and T/R Switch in 22nm FD-SOI CMOS for 5G Antenna Arrays, 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019, pp. 303-306, doi: 10.1109/RFIC.2019.8701819. [2]

- Paper III C. Elgaard, M. Özen, E. Westesson, A. Mahmoud, F. Torres, S. Bint Reyaz, T. Forsberg, R. Akbar, H. Hagberg and H. Sjöland, Efficient Wideband mmW Transceiver Front-End for 5G Base Stations in 22 nm FD-SOI CMOS, IEEE Journal of Solid State Circuits (JSSC), pp. 1-16, 2023. [3]

- Paper IV C. Elgaard and H. Sjöland, Analysis and Design of a GHz Bandwidth Adaptive Bias Circuit for an mmW Doherty Amplifier, IEEE Transactions on Microwave Theory and Techniques, Regular Papers, Submitted Feb. 2024. [4]

#### Related publications

I have also authored and co-authored two papers, listed below, that are not considered a part of this dissertation.

Paper V C. Elgaard and L. Sundström, A 491.52 MHz 840 uW Crystal Oscillator in 28 nm FD-SOI CMOS for 5G Applications, ESSCIRC 2017 - 43rd IEEE European Solid State Circuits Conference, Leuven, Belgium, 2017, pp. 247-250, doi: 10.1109/ESSCIRC.2017.8094572. [5]

xii Preface

Paper VI S. Ek, T. Påhlsson, C. Elgaard, A. Carlsson, A. Axholt, A. Stenman, L. Sundström, and H. Sjöland, A 28-nm FD-SOI 115-fs Jitter PLL-Based LO System for 24–30-GHz Sliding-IF 5G Transceivers, in IEEE Journal of Solid-State Circuits, vol. 53, no. 7, pp. 1988-2000, July 2018, doi: 10.1109/JSSC.2018.2820149. [6]

#### Patent applications

- 1. C. Elgaard "Oscillator Circuit" US2016308491A1 US9692354B2 2013-12-16

- 2. J. Peltonen, C. Elgaard, and A. Stenman "Oscillator Circuit with Bias Current Generator" US10333526B2 US2017237441A1 2014-06-02

- 3. C. Elgaard and L. Sundström "Low-Noise Oscillator Amplitude Regulator"  $\rm HK1250847A1~2015\text{-}06\text{-}05$

- 4. C. Elgaard, A. Carlsson, and H. Sjöland "A Reference Signal for Noise Reduction" WO2017162275A1 2016-03-22

- C. Elgaard, S. Andersson, A. Axholt, and I. Ud Din "Power Amplifier" US10848108B2 US2019245493A1 2016-10-14

- H. Sjöland, A. Axholt, and C. Elgaard "An Integrated Transformer" WO2018188719A1 2017-04-10

- L. Sundström, S. Ek, and C. Elgaard "Transceiver Circuit" US11095335B2 US2020145041A1 2017-06-22

- 8. C. Elgaard, M. Åström, and F. Tillman "Integrated Circuit With Clock Distribution" WO2019029819A1 2017-08-11

- 9. C. Elgaard, S. Andersson, and L. Sundström "Power Amplifier Arrangement" US11258413B2 US2020389136A1 2018-01-17

- C. Elgaard and H. Sjöland "Power Amplifier Circuit" WO2020126054A1 2018-12-21

- C. Elgaard and H. Sjöland "Bias Circuit and Power Amplifier Circuit" EP3909127A1 2019-01-10

- 12. M. Hamid, C. Elgaard, A. Al-Qamaji, and F. Abdalrahman "Interleaved Antenna Array Configuration in a Radio Node" US2023155290A1 2020-04-09

- F. Torres, C. Elgaard, S. Andersson, and H. Sjöland "Transmitter Arrangement, Transceiver, Radio Communication System and Method" WO2021209151A1 2020-04-17

Preface xiii

C. Elgaard, S. Mattisson, and S. Andersson "Envelope Controlled Biasing of an Auxiliary Transmitter of a Doherty Power Amplifier" WO2021228396A1 2020-05-14

- 15. C. Elgaard and H. Sjöland "Transmitter Circuit" WO2021259448A1 2020-06-22

- I. Ud Din, C. Elgaard, and S. Andersson "A Transceiver Switch Circuitry" WO2022069037A1 2020-09-30

- 17. I. Ud Din, C. Elgaard, and S. Andersson "A Transceiver Switch Circuitry" WO2022069038A1 2020-09-30

- I. Ud Din and C. Elgaard "A Differential Transceiver Switch Circuitry" WO2022111814A1 2020-11-27

- 19. C. Elgaard and H. Sjöland "Mitigation of Memory Effects in a Power Amplifier" WO2023117083A1 2021-12-22

- C. Elgaard and H. Sjöland "Digital Phase Locked Loop Amplitude Modulation-to-Phase Modulation (AM-PM) Compensation" WO2023126054A1 2021-12-28

- 21. C. Elgaard, H. Sjöland, and M. Hamid "Concurrent Digital Post-Distortion of Multiple Signals" WO2023160783A1 2022-02-24

- 22. C. Elgaard, R. Kasri, F. Mesquita, and H. Sjöland "Receiver Beamforming" WO2023208362A1 2022-04-29

- C. Elgaard, H. Sjöland, and M. Åström "Co-Located Back-Lobe Cross Link Interference (CLI) Digital Canceler Interface" WO2023217680A1 2022-05-09

- 24. C. Elgaard, H. Sjöland, I. Ud Din, and H. Hagberg "Antenna Array Power Amplifier Mismatch Mitigation" WO2023241806A1 2022-06-16

- 25. H. Sjöland and C. Elgaard "Dual Polarity Power Amplifier With Nonlinear Supply Modulation" WO2024008306A1 2022-07-08

### Acknowledgments

Ever since I joined Ericsson Research I have felt a sense of pride to be part of such an amazing highly talented group. One of my first assignments after joining the group was to design a high frequency crystal oscillator and after completing the design my colleague Lars Sundström said "if it works we can write a paper" and since it worked we wrote a paper. So, thanks Lars for directing my in a way that came to become the first spark of this dissertation. Somewhere around this time I realized that maybe there is a possibility for me to formalize the research work I do at Ericsson in collaboration with academia. Sometimes later I asked another colleague, Professor Henrik Sjöland if he and the university would be willing to formally take me on as a PhD student. After some internal discussions at Ericsson I had a final meeting about the matter with Fredrik Tillman and Sven Mattisson which ended with Sven saying the words "Then I will be invited to a dissertation party". I am sincerely grateful for given the rare opportunity to pursue an industrial PhD at Lund University while still being able to continue and grow in my research position in the Integrated Radio System RF frontend and PA group at Ericsson Research. Thanks Fredrik and Sven for making this happen. After some time I got a new manager, Stefan Andersson who has been kind enough to turn a blind eye to the fact that the somewhat optimistic plan, which stated that my PhD studies should be completed in four years with 50% allocation (and 50% on other Ericsson stuff) was long overdue. Thanks a lot Stefan for, as far as possible, allocating me on projects which allowed me to advance my dissertation. Through this whole time, I would like to thank my closest team members which were, and still are, always very supportive, no matter what the problem was. Nevertheless, I want to mention Imad Ud Din who has been my companion on this journey and especially thanks for the good times we had completing those early PhD courses.

However, as I embarked on my endeavor, **Henrik Sjöland** became not only my colleague but also my supervisor during my PhD studies. For this I'm very grateful and I cannot think of a better choice of supervisor. Henrik, with extremely impressive hands-on knowledge, on all kind of matters that relate to our field, is always willing to help and spend the time to do it, even though it means sacrificing his own time during the weekend. There is a long list of truly impressive qualities and behaviours that could be listed.

In the background to the research conducted at Ericsson there was always support from family and friends. I would like to start by expressing gratitude to **Johan Löfgren** who inspired me to switch from finance/economics to physics by simply saying "Engineering Physics is considered to be the hardest to study"- back in 1996, upon which I immediately started preparing for getting accepted to LTH. I also want to thank **Pierre**, **Henrik**, and **Magnus** for being

the best possible friends. Pierre who never would hesitate to any request for support, Henrik for those daily small adventures, such as discussing polarized light or group delays while sailing, and Magnus for those never-ending deep discussions late at night and racket sport matches.

I would also like to thank, my father **Bent**, mother **Majvi**, and sister **Jenny**, with whom I grew up. I think that at this time my interest for natural science was developed that lead to my choices later in life. When deciding to pursue the PhD I was already a father of four wonderful children **Oscar**, **August**, **Molly**, and **Elliot** together with my fantastic, always generous and supportive fiancé **Maria**. My goal was to absorb the time needed for the PhD studies during office hours to minimize the absence from my family. I hope that that has also been the case, at least for most of the time, even though there has been some late evenings towards the end. Anyhow, to my family, I want you to know that I love you and thank you for your support. When having a bad day at the office I know that you are always there when I come home.

(  $\bigcirc$   $\bigcirc$

# List of Acronyms

AAS Antenna Array System

AC Alternating Current

ACLR Adjacent Channel Leakage Ratio

ACPR Adjacent Channel Power Ratio

ADC Analog-to-Digital Converter

AM-AM Amplitude Modulation to Amplitude Modulation

AM-PM Amplitude Modulation to Phase Modulation

BB Baseband

BPF Band Pass Filter

BW Bandwidth

CMOS Complementary Metal Oxide Semiconductor

CW Continuous Wave

DAC Digital-to-Analog Converter

DE Drain Efficiency

DC Direct Current

DCO Digital Controlled Oscillator

DPLL Digital Phase Locked Loop

EIRP Effective Isotropic Radiated Power

EV Error Vector

EVM Error Vector Magnitude

DIBL Drain Induced Barrier Lowering

DPD Digital PreDistortion

EVM Error Vector Magnitude

FD-SOI Fully Depleted Silicon on Insulator

FSPL Free Space Path Loss

IBW Instantaneous Bandwidth IF Intermediate Frequency

IIPn n-th order Input-Referred Intercept Point

IMn n-th order Intermodulation distortion

IPn n-th order Intercept Point

IRR Image Reject RatioLNA Low-Noise Amplifier

LO Local Oscillator

LPF Low Pass Filter

LTI Linear Time-Invariant LTV Linear Time-Variant

mmW millimeter Wave

NF Noise Figure

NMOS n-channel metal-oxide-semiconductor field-effect transistor

OCP Output-referred Compression Point

$N^{th}G$   $N^{th}$ -Generation Technology for Cellular Networks System

OFDM Orthogonal Frequency Division Multiplexing

PA Power Amplifier

PAE Power Added Efficiency

PAR Peak-to-Average Ratio

PCB Printed Circuit Board

PLL Phase Locked Loop

PMOS p-channel metal-oxide-semiconductor field-effect transistor

PPA Pre Power Amplifier

PSD Power Spectral Density

PWM Pulse Width Modulation

RMS Root Mean Square RF Radio Frequency

RX Receiver

SCS Signal Component Separator SMPA Switch Mode Power Amplifier

SSBW Small Signal Bandwidth

SSG Small Signal Gain

List of Acronyms xix

TDD Time Division Duplex

TRP Total Radiated Power

TRX Transceiver

TTD True Time Delay

ZVDS Zero Voltage Derivative Switching

UE User Equipment

ZVS Zero Voltage Switching

QAM Quadrature Amplitude Modulation

# List of Symbols

$B'_{\circ}$

A Amplitude in polar coordinate system

$A_I$  Amplitude of (fundamental) current [A]

Normalized shunt susceptance [S]

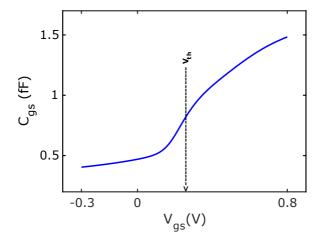

$C_{as}$  Gate to source capacitance [F]

$C_{in}$  Input capacitance [F]  $C_{out}$  Output capacitance [F]  $f_T$  Cut-off frequency [Hz]  $g_m$  Transconductance [S]

$\mathrm{HD}_n$   $\mathrm{n^{th}}$  order harmonic distortion  $h_n$   $\mathrm{n^{th}}$  order convolution term

h(s) Transfer function  $I_{dc}$  Direct current [A]

$i_{DS}$  Drain to source current [A]  $i_{D max}$  Maximum drain current [A]

$I_{fund}$  Current at fundamental harmonic [A]  $IM_n$  n<sup>th</sup> order intermodulation distortion  $IIP_n$  Input-referred n<sup>th</sup> order intercept point  $IP_{ndB}$  Input-referred n dB compression point

$i_S$  Switch current [A]

$k_n$  n<sup>th</sup> order power series expansion coefficient

$Nbr_{transistors}$  Number of transistors

NF Noise figure [dB]

OIP $_n$  Output-referred n<sup>th</sup> order intercept point OP $_{ndB}$  Output-referred n dB compression point

$P_{DC}$  Power from DC source [W]

$P_{diss}$  Dissipated power [W]  $P_{EV}$  Power of error vector [W]

$P_{fund}$  Power at fundamental harmonic [W]

xxii List of Symbols

$P_{in}$  Input power [W]  $P_{loss}$  Power of losses [W]

$P_N$  Normalized power output capability

$P_{out}$  Output power [W]

$P_{Ref}$  Power of reference vector [W]  $P_{R_{Load}}$  Power dissipated in  $R_{Load}$  [W]

$P_{R_{ON}}$  Power dissipated in on resistance [W]

$P_{sat}$  Saturated output power [W]

$R_{Load}$  Load resistance  $[\Omega]$   $R_{on}$  On resistance  $[\Omega]$  T Signal period [s] $V_{dd}$  Supply voltage [V]

$v_{DS}$  Drain to source voltage [V]

$v_{DS,max}$  Maximum drain to source voltage [V]

$V_{in}$  Input voltage [V]  $V_{out}$  Output voltage [V]

$V_{pp}$  Peak to peak voltage [V]

$V_{\rm th}$  MOS transistor threshold voltage [V]

$Z_{aux}$  Output impedance of auxiliary amplifier  $[\Omega]$

$Z_{load}$  Load impedance  $[\Omega]$

$Z_{main}$  Output impedance of main amplifier  $[\Omega]$

$Z_{\lambda/4}$  Characteristic impedance of  $\lambda/4$ -transmission line  $[\Omega]$

Q Quality factor

$\gamma$  Ratio of transconductance for main and auxiliary amplifier

$\varepsilon$  Fractional gain mismatch

$\eta$  Efficiency [%]

$\theta$  Phase mismatch, outphasing angle, or polar phase [rad]

$\lambda$  Wavelength of Electromagnetic Wave [m]

$\phi$  Common mode phase [rad]

$2\Phi$  Conduction angle [rad]

### Chapter 1

### Introduction

#### 1.1 Motivation

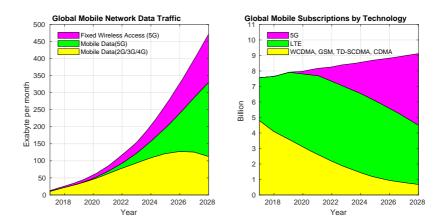

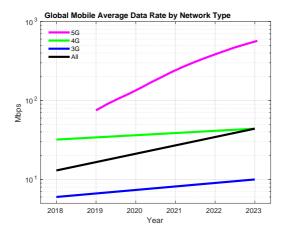

Figure 1 shows recent years development of global mobile network data traffic and global subscriptions by technology and predictions of how they will evolve to 2028, and Fig. 2 shows the average mobile data rate and how it has increased in recent years [7,8].

**Figure 1:** Left: Global mobile network data traffic per month 2017-2023 and predictions 2023 - 2028. Right: Global number of mobile subscribers 2017 - 2023 and predictions 2023 - 2028

Figure 2: Global mobile average data rate by network type

The tremendous anticipated growth in mobile data traffic and data rate calls for massive research, development, and investments in cellular network infrastructure.

In 1948 Shannon formulated his famous equation for the capability to transfer information with an electronic signal [9]:

$$C = B \cdot \log_2 \left( 1 + \frac{S}{N_t} \right) \tag{1}$$

Where C is the channel capacity in bits per second, B is the bandwidth (BW) of the channel in Hz, and S and  $N_t$  are the power of the signal and the total noise including interference, respectively. Shannons channel capacity equation combined with the anticipated mobile network data traffic growth and increased user data rates pinpoint the motivation for this dissertation. To increase the BW of the communication channel, to satisfy the need for more network data traffic and higher user data rates, higher and higher carrier frequencies are constantly being explored. The main driver is that at higher carrier frequencies there is more available spectrum. The increasing demand for data traffic and data rates, with a chase for more available bandwidth, has been a key driving force within the telecommunications industry for many years. This was thus the case at the beginning of my PhD studies, when exploration of millimetre wave (mmW) frequencies (about 24-70 GHz) for 5G cellular communication was still quite new, and it is true now when writing this dissertation as sub-THz frequencies are more frequently being discussed for high BW 6G cellular communications.

However, reaching more available spectrum by increasing the carrier frequency comes at a high cost. Firstly, at higher frequencies the attenuation

of the signal power from the transmit to receive antenna becomes much more severe. This was first captured by H. T. Friis in 1946 by his transmission formula [10], which can be used to derive what is commonly known as the Friis free space path loss (FSPL) formula. If assuming isotropic transmit and receive antennas, i.e. antennas with no directivity, the FSPL becomes:

$$FSPL = \left(\frac{4\pi d}{\lambda}\right)^2 \tag{2}$$

where d is the distance between the antennas, and  $\lambda$  is the electromagnetic wavelength. Friis path loss formula dictates that when the frequency increases tenfold, e.g. from 3 GHz to 30 GHz, so that  $\lambda$  decreases tenfold, the path loss increases a hundredfold.

Secondly, in 1965 Johnson concluded that the optimal trade-off between the maximum usable frequency, the cut-off frequency  $(f_T)$ , and the maximum voltage  $(V_m)$ , for a transistor, can be expressed as [11]:

$$V_m \cdot f_T = \frac{E \cdot v_s}{2\pi} \tag{3}$$

Where E and  $v_s$  are material constants that depend on the used semiconductor material. For silicon  $E \cdot v_s/2\pi = 2 \cdot 10^{11} V \cdot Hz$ , which gives a maximum voltage of 1 V for an  $f_T$  of 200 GHz. This is particularly troublesome for power amplifiers (PAs) operating at high frequencies, since to increase  $f_T$  for a transistor in a given semiconductor material, to boost gain and efficiency, one must reduce the voltage levels in the device, which limits the output power that the PA can deliver.

To summarize the discussion so far; the increased mobile network data traffic and increased user data rates call for more available spectrum, which is found at higher frequencies. Higher frequencies, however, gives significantly more path loss, and the analog circuits will, for a given semiconductor material, have lower gain and deliver a lower maximum output power.

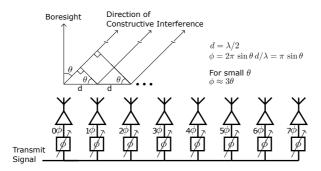

To overcome the aforementioned obstacles, mmW cellular communication relies on using antenna arrays that increases transmit output power and receive and transmit antenna gain. Many antennas are then used, arranged in rows and columns, often with a spacing of half a wavelength, which at 30 GHz becomes just 5 mm. On the base station side the antenna arrays can thus be rather large when it comes to number of antennas, in the order of a hundreds or even thousands. Even the user equipment (UE), most commonly a mobile phone, will typically be equipped with a small antenna array. A large antenna array is often referred to as an antenna array system (AAS). Assuming a separate PA to be used for each antenna element, the total radiated power (TRP) from an AAS increases linearly with the number of antenna elements, which relaxes the output power requirement on each PA. Furthermore, and perhaps even more important, if the individual antenna signals are phase shifted to produce

constructive interference in a desired direction, the antenna gain also increases linearly in that direction, effectively producing antenna directivity. The antenna directivity, accomplished by phase shifting the signals to the individual antennas, is called beamforming gain and by adjusting the phase gradient over the array it is possible to steer the beam. The basic principle of beamsteering in an AAS is illustrated in Fig. 3.

Figure 3: Principle of beamsteering for an 8x1 antenna array.

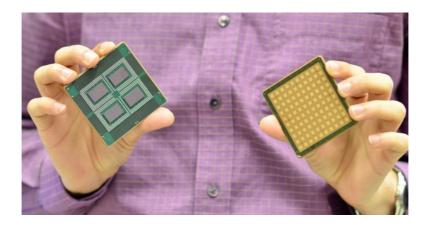

The effective isotropic radiated power (EIRP), which is the how much power an isotropic antenna would have to radiate to give equal radiated power in the direction of the beam from the AAS, will increase quadratically with the number of antennas in an AAS. Firstly, it increases as more PAs provide increased radiated output power. Secondly, it increases as the beamforming gain increases as more antenna elements are added. Since the AAS is rather small and contains many antennas, each connected to a transceiver (TRX) or at least a front-end of a transceiver, not much space is available for the electronics that form each TRX. This necessitates a high level of integration both due to the limited space, but also to reduce the overall cost as the number of transceivers becomes large. Both integration level and cost push in a direction towards CMOS technologies, which have excellent integration level and physical size, as well as low cost per unit in large scale production. However, it is challenging to integrate the PA in a CMOS TRX, due to multiple reasons, of which the most severe ones are its high output power requirements combined with the CMOS poor ability to withstand high device voltages and the heat dissipation from multiple PAs in a single integrated circuit. Figure 4 shows an example of a highly integrated mmW AAS, with the backside shown to the left and the front side to the right. The frontside has 8x8 dual polarized antennas, requiring in total 128 transceivers. The backside shows four integrated circuits, each with 32 transceivers.

**Figure 4:** A highly integrated mmW AAS. Left: backside, four dies with 32 transceivers on each die. Right: frontside, 8x8 dual polarized mmW AAS, including an outer ring of dummy antennas. Picture from [12]. IBM/Ericsson silicon-based mmWave phased array antenna module operating at 28 GHz.

To summarize; AASs with beamforming are used to mitigate the effects of increased path loss and reduced output power at mmW. One major challenge then becomes how to accomplish the necessary integration of the PA into a CMOS chip containing multiple transceivers, due to the limited space in the AAS and the required reduced cost per transceiver. To meet targets in range and data rates of the transmission, the PA must be able to deliver high enough output power to the antenna, and it must perform the amplification in a power efficient way not to dissipate too much heat and to reduce power consumption in general. Furthermore, the PA must amplify the transmit signal while adding low level of distortion, also for wideband signals with high data rate modulation, which stands in stark contrast to the efficiency requirement, and it must allocate a relatively small die area. All things considered, the PA suitable for cellular mmW communication, highly integrated in a low-cost CMOS process, with high output power, high efficiency, wide bandwidth, low distortion, high reliability, and small size offers significant research challenges.

#### 1.2 Outline

- Chapter 1 introduces mmW communication, motivates why research in integrated mmW power amplifiers for wireless systems is needed, and organizes the dissertation.

- Chapter 2 describes important transmitter architectures to place the

power amplifier in its context.

• Chapter 3 defines, with examples, the most commonly used power amplifiers metrics.

- Chapter 4 summarizes the most commonly referred power amplifier classes.

- Chapter 5 presents, in brief, some theory about power amplifier linearity.

- Chapter 6 analyses two efficient power amplifiers, the Doherty PA and the Chireix outphasing PA.

- Chapter 7 presents the included papers with their scientific contribution and the author's contribution to the papers.

- Chapter 8 concludes the dissertation with some suggestions for future work.

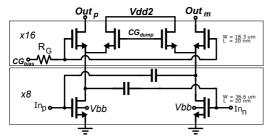

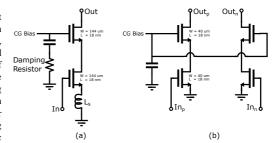

- Paper I presents a mmW variable gain PA driver and a PA in 28 nm FD-SOI CMOS, suitable for a highly integrated antenna array system for a 5G basestation.

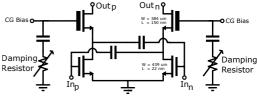

- Paper II presents a mmW variable gain PA driver and PA, and a transmit/receive switch (TRX-switch) in 22 nm FD-SOI CMOS, suitable for a highly integrated antenna array system for a 5G basestation.

- Paper III presents a mmW transceiver with a Doherty amplifier in 22 nm FD-SOI CMOS, suitable for a highly integrated antenna array system for a 5G basestation.

- Paper IV presents analytical derivations of why a Doherty PA gains from dynamically altering the bias level depending on the input signal amplitude, so called adaptive bias.

### Chapter 2

### Transmitter Architectures

To place the PA in its context, some of the most well-known transmitter architectures are presented in this chapter. The task of the transmitter is to generate the analog signal to be radiated by the antenna, with a certain output power, carrier frequency, bandwidth, and modulation type. The output power should be large enough that the receiver can correctly decode the transmitted signal information, and if the targeted range of communication is increased more output power is required. The carrier frequency and bandwidth depends on in which part of the spectrum that the wireless communication should occur. The modulation type can be seen as a predetermined agreement between the transmitter and receiver on how the information should be coded into the analog signal. The bandwidth and modulation type will determine the maximum data-rate of the communication link.

### 2.1 Signal Fidelity and Constellation Diagram

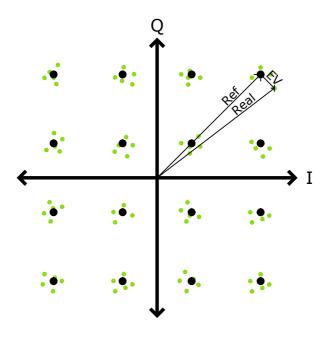

In digital communication systems, where the analog signal carries digital information bits, the bits are typically represented by the phase and amplitude of the signal. A so-called 16-QAM constellation diagram, see Fig. 5, is used to visualise how the digital bits can be coded in the analog signal.

**Figure 5:** 16-QAM constellation diagram showning, I and Q vectors, Real, Ref and EV (Error Vector).

In QAM the signal is constructed from two carrier components, one called the (I)-component, which is  $I \times \cos(\omega_c t)$ , and one called the Q-component, which is  $Q \times \sin(\omega_c t)$ . The I and Q are amplitudes that can have both postive and negative values, the letters stand for in-phase and quadrature-phase which relates to the 90-degree phase shift between sinus and cosinus. Each of the I and Q components are then independently amplitude modulated. For the 16-QAM signal there are four possible values of I and Q, which gives in total 16 combinations as marked in the I,Q plane in Fig. 5. The distance from the origin represents the signal amplitude, and the phase is represented by the phase from the I-axis. Each black dot represents an ideal position, i.e. amplitude and phase of the total carrier signal, for transmission of a certain digital information symbol. In Fig. 5 there are in total 16 black dots, which each represent four digital bits, i.e. the information in a symbol. The green dots represent some actual, or non-ideal symbol transmissions due to transmitter imperfections. The Ref vector is the desired ideal transmission, the Real vector is the actual transmission, and the error vector (EV) is the vector between the actual transmission and the desired ideal point. To quantify how severe the deviations from the desired ideal points are, the average magnitude of the EV is compared with the average Reference vector magnitude and often reported in percent as the error vector magnitude (EVM):

$$EVM(\%) = \sqrt{\frac{\overline{P_{EV}}}{\overline{P_{Ref}}}} \cdot 100 \tag{4}$$

Where  $\overline{P_{EV}}$  and  $\overline{P_{Ref}}$  are defined as the average power for a number of symbols. As long as the EVM is low enough it will be possible to determine with high probability which symbols were transmitted, i.e. to decode the information correctly. The limit on how large EVM that a signal transmission can tolerate depends on how densely the constellation points are packed. The example shown in Fig. 5 has 16 constellation points, which requires an EVM below 12%. But if more points are added, the points gets closer to each other, which requires lower EVM. Table 1 summarizes the EVM requirements for some QAM constellation sizes, and as can be seen the EVM requirements are much more stringent at 256-QAM than at 16-QAM [13].

**Table 1:** EVM Requirement for a selection of QAM signals

| Modulation                | Rec | quired EVM | Bits/sym |

|---------------------------|-----|------------|----------|

|                           | [%] | [dB]       |          |

| 16-QAM                    | 12  | -18.4      | 4        |

| $64\text{-}\mathrm{QAM}$  | 6   | -24.4      | 6        |

| $256\text{-}\mathrm{QAM}$ | 3   | -30.5      | 8        |

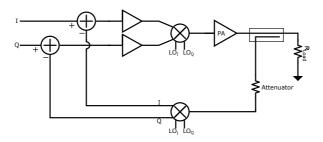

#### 2.2 Cartesian Transmitters

The input signal to a Cartesian transmitter is represented in a Cartesian coordinate system and the baseband (BB) input signal consists of the two components I and Q (corresponding to x and y of a Cartesian coordinate system). Each component carries half the information, and consequently half the data-rate.

The central component of both the homodyne and heterodyne transmitter, which will be presented below, is the IQ-modulator (also known as image reject mixer or IQ-mixer), which comprises two mixers. One mixer produces the modulated I signal at the carrier frequency by multiplying the BB I component  $BB_I(t)$  with  $\cos(\omega_{LO}t)$  and the other mixer produces the modulated Q signal at the carrier frequency by multiplying the BB Q component  $(BB_Q(t))$  with  $\sin(\omega_{LO}t)$ . The modulated I and Q signals from the two mixers are then combined into one signal by summation. The modulation of I and Q makes it possible to control both the amplitude and phase of the output signal, and thereby to represent any signal. Naturally, the goal is to control the signal such that it moves between the constellation points that represents the transmission bit sequence. An ideal IQ-modulator has identical gain in the BB I and Q paths and upconverts to carrier frequency with exactly 90° phase separation

between the cosine and sine functions. A single mixer operation is equivalent to a multiplication of the input baseband signal with the LO and will produce spectrum at both sides of the LO, i.e. at  $\omega_{LO} \pm \omega_{BB}$  for a baseband input tone at  $\omega_{BB}$ . The IQ-Modulator, however, can generate signal with different spectrum at the two sides of the LO, e.g. a tone at  $\omega_{LO} + \omega_{BB}$  but no tone at  $\omega_{LO} - \omega_{BB}$ , called image rejection. How well the IQ-modulator suppresses the unwanted image depends on how accurately the mixers output signals are matched to the ideal 90-degrees phase difference, and also how accurately the amplitude of the two paths match. For small phase and amplitude deviations the image reject ratio (IRR) can be approximated as [14]:

$$IRR \approx \frac{4}{\varepsilon^2 + \theta^2}$$

(5)

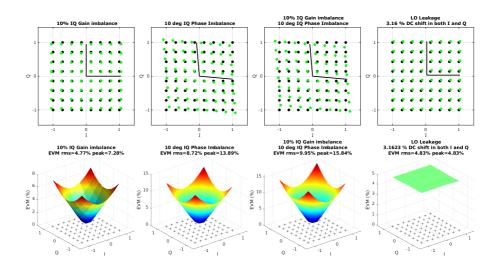

where  $\theta$  is the phase mismatch in radians and  $\varepsilon$  is the fractional gain mismatch. In practice, a typical design produces an IRR of about 25-35 dB [14]. Furthermore, ideally there should be no non-modulated LO signal present at the output of the IQ-modulator, i.e. no LO-leakage. In reality though, all IQ-modulators suffer from IQ-gain imbalance, IQ-phase mismatch, and LOleakage. Gain and phase imbalance might arise from global and local process variations and the unavoidable deviation from a perfectly symmetric layout. The LO-leakage originates from DC offset(s) at the BB input of the mixer, which is upconverted to the LO frequency, and from direct leakage from the LO input to the output of the mixer. Gain imbalance will effectively make the I and Q components (vectors) have unequal length. Phase imbalance will make the I and Q vectors to deviate from a 90° phase relation in the IQ-plane. An LO leakage will add a DC shift to the constellation points. The effects on the symbols of a 64-QAM constellation diagram when introducing gain imbalance, phase imbalance, a combination of gain and phase imbalance, and an LO-leakage, and how the EVM varies over the IQ-plane are illustrated in Fig. 6.

**Figure 6:** Upper: A 64-QAM constellation diagram showing green constellation points for a 10% gain imbalance, a 10° degree phase imbalance, a combined 10% gain imbalance with 10° degree phase imbalance, and a 5% DC shift caused by an LO-leakage. The black dots represent the ideal constellation points. Lower: Corresponding EVM contributions for the upper four plots.

Gain and phase imbalances will result in EVM that increases with the distance from origin. Table 2 summarizes the EVM contribution of various degrees of gain and phase imbalance.

| Table 2: 64-QAM EVM contrib | oution from gain and phase imbalance |

|-----------------------------|--------------------------------------|

|                             |                                      |

| Imbalance    | Gain    |      | Phase       |      | Gain & Phase        |      |

|--------------|---------|------|-------------|------|---------------------|------|

|              | EVM [%] |      | EVM [%]     |      | $\mathbf{EVM}~[\%]$ |      |

| $[\%, \deg]$ | rms     | peak | $_{ m rms}$ | peak | rms                 | peak |

| 0.1          | 0.05    | 0.08 | 0.09        | 0.13 | 0.10                | 0.15 |

| 1            | 0.5     | 0.8  | 0.9         | 1.3  | 1.0                 | 1.5  |

| 10           | 4.8     | 7.3  | 8.7         | 13.9 | 10                  | 15.8 |

| 20           | 9.1     | 14   | 17.4        | 28.9 | 19.7                | 32.6 |

LO-leakage produces a flat EVM, effecting all symbols equally and thereby making the rms and peak values the same. Table 3 summaries the EVM contribution of various degrees of LO-leakage for 16-QAM to 1024-QAM modulations. The small difference of EVM for the different constellation diagrams depends

on the small variation of average energy in the ideal symbols. The required EVM, on the other hand, is very different for 16-QAM and 1024-QAM.

| LO-leakage  | 16-QAM   | 64-QAM     | 256-QAM             | 1024-QAM   |

|-------------|----------|------------|---------------------|------------|

| Below Max   | EVM [%]  | EVM [%]    | $\mathbf{EVM}~[\%]$ | EVM [%]    |

| Ampli. [dB] | rms/peak | m rms/peak | m rms/peak          | m rms/peak |

| -60         | 0.13     | 0.15       | 0.16                | 0.17       |

| -50         | 0.42     | 0.5        | 0.51                | 0.53       |

| -40         | 1.34     | 1.5        | 1.63                | 1.68       |

| -30         | 4.24     | 4.8        | 5.14                | 5.31       |

| -20         | 13.4     | 15.3       | 16.3                | 16.8       |

**Table 3:** EVM contribution from LO-leakage

From Fig. 6 it is clear that the gain and phase errors between the I and Q signal components will impact the EVM of the transmitted signal. However, for such deterministic errors, as a constant gain and/or phase imbalance, the receiver could perform IQ-imbalance compensation algorithms as in [15], significantly reducing their EVM impact. On the other hand, even with ideal compensation of IQ-imbalance and LO-leakage in the receiver, the constellation points have been shifted from their intended positions in the transmission signal. This will affect how the signal gets distorted and reduce the useful signal power, as part of the transmitted power is allocated to transmit undesired signal components such as image and LO-leakage.

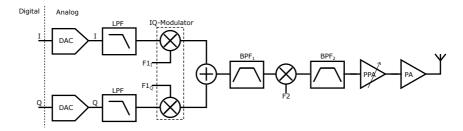

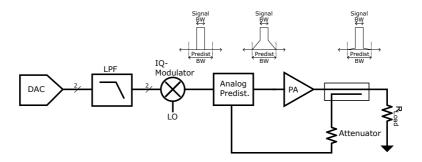

## 2.2.1 The Heterodyne Transmitter

The heterodyne (or superheterodyne) transmitter, see Fig. 7, uses multiple (at least two) stages for frequency upconversion from BB input signal to output carrier frequency. The analog input signals I and Q are created from digital input signals using digital to analog converters (DACs), and low pass filters (LPF) that suppresses repetitive spectrum due to limited sampling frequency in the DACs. An IQ-Modulator upconverts the baseband signals to an intermediate frequency (IF), which typically is band pass filtered (BPF) to suppress unwanted out-of-band signals. Then follows a mixer which will produce signal at both  $\omega_{F2} + \omega_{F1}$  and  $\omega_{F2} - \omega_{F1}$ . The second BPF is needed to suppress the unwanted one of these two signals, the image signal. A variable gain amplifier is then used to adjust the signal amplitude such that the PA produces the desired output power level. A benefit with the heterodyne transmitter is that it allows for a simpler LO design as the challenging LO quadrature phase accuracy, needed in the IQ-Modulator, can occur at a lower frequency (IF). Another thing worth mentioning is that LO-leakage from the second mixer ends up out-of-band, which causes less problem for EVM, but might violate a possible stringent out-of-band emission requirement, or put increased requirements on  $BPF_2$ . Simply speaking, quite a large part of the design takes place at a lower frequency than the high output frequency. The drawback is the obvious problem with the needed image suppression after the second mixer, but also that the heterodyne transmitter requires two LO frequencies for upconversion and a multitude of analog subblocks.

Figure 7: A heterodyne transmitter.

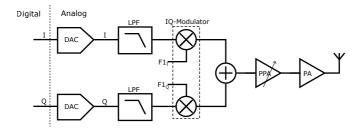

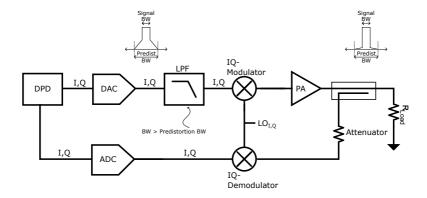

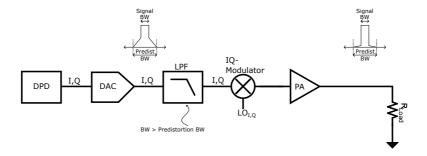

## 2.2.2 The Homodyne Transmitter

The homodyne transmitter, see Fig. 8, uses a single stage frequency upconversion from baseband to carrier frequency. As for the heterodyne, LPFs are used to suppress aliasing products from the input signal generated by the DACs. After frequency upconversion by the IQ-modulator, a variable gain amplifier adjusts the signal to the PA for appropriate output power level. The homodyne transmitter has a couple of benefits, but also disadvantages compared to the heterodyne. The obvious advantages are that the homodyne transmitter requires fewer sub-blocks and it does not require generation of two different LO frequencies for up-conversion. However, perhaps more importantly, it does not require any band pass filters since it does not produce an out-of-band image. On the downside, depending on the operating frequency and choice of process, it can be a much harder design task, especially the IQ modulator. To avoid a significant EVM contribution from the IQ-imbalance, which would effectively limit the use of high order modulation, see table 1 and table 2, the requirements on amplitude and phase match becomes very challenging at high frequencies. As an example, to achieve an EVM contribution of 1\% at 30 GHz, and assuming perfect amplitude match, the phase mismatch should be below 1°, which corresponds to a time error below 0.1 ps between the LO I and Q signals, and since in reality a small amplitude mismatch is unavoidable the time mismatch must be even lower than that. To reduce the level of LO-leakage, which causes a DC offset in the constellation diagram, careful mixer design is needed. The most important is to avoid introducing DC offset at the BB input of the two mixers in the IQ-modulator, by using well-known design and layout strategies to reduce the local mismatch, and to plan the layout such that the coupling from the LO input to the output is minimized, thereby reducing the direct LO-leakage. Even after careful design, the LO-leakage might still be too large for system specifications. Luckily there are various LO-leakage suppression techniques available, such as presented in [3], which uses programmable DC current sources that inject current into the Gilbert mixer, to cancel the effect of LO-leakage. Another weak spot of the homodyne transmitter is that since the PA operates at the same center frequency as the LO signal, used for frequency upconversion, pulling by the PA of the LO circuitry (oscillator or possibly by quadrature generation dividers) can become a challenging problem. This problem can, however, quite often be mitigated by careful planning of the LO frequency generation. It also helps that the signal is often wideband in mmW systems, as LO circuitry is more sensitive to narrowband pulling.

Figure 8: A homodyne transmitter.

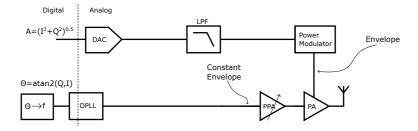

## 2.3 The Polar Transmitter

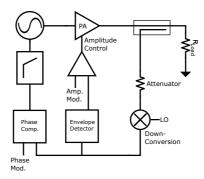

This section presents a polar transmitter architecture along with some considerations. The input signal to a polar transmitter is represented in a polar coordinate system. Rather than Cartesian I and Q, the baseband input signal then consists of amplitude (A) and phase  $(\theta)$ , corresponding to r and  $\phi$  of the polar coordinate system often used in mathematics. Figure 9 shows a polar transmitter architecture [16,17]. In the digital domain the phase modulation signal  $\theta$  is derived from the Cartesian IQ signals using the nonlinear arctan 2 function, but since the input signal to the digital phase locked loop (DPLL) is a digital frequency control word, a conversion from phase modulation  $\theta$  to frequency modulation is also performed (including phase unwrapping). The digital frequency modulation is then input to the DPLL, which generates a constant envelope phase modulated signal at the carrier frequency. The amplitude modulation is applied directly at the supply voltage of the PA. The main advantage of the polar transmitter is that since the input signal to the PA has a constant envelope, it becomes possible to use a highly efficient switched mode PA (SMPA). One major challenge with polar transmitters is the bandwidth ex-

pansion due to the nonlinear transfer from Cartesian to polar coordinates, the drawback being similar to that of the outphasing PA as described in chapter 6, both in text and with Eq. 68 - 71. The bandwidth of the amplitude and phase signals can be more than ten times the bandwidth of the signals in a Cartesian coordinate system, and it is most severe for the phase signal [18]. To increase the phase modulation bandwidth, the PLL may employ so-called two-point modulation. This means that the frequency control word in the digital domain is fed to the DPLL using two modulation paths, one slow and one fast, where the slow path controls the division ratio in the feedback frequency divider of the DPLL and the fast one controls capacitors in the resonance tank of the digitally controlled oscillator (DCO) to quickly steer the frequency. The bandwidth expansion is particularly troublesome for 5G mmW communication as the transmission bandwidths have increased significantly compared to 4G. Another drawback of the polar transmitter is the timing accuracy requirement between the amplitude and phase modulation, which becomes difficult for high modulation bandwidths. In a Cartesian transmitter the I and Q paths are identical parallel paths, which makes matching relatively easy, whereas in the polar transmitter the two modulation paths are completely different and still must be very accurately matched in time. A final remark about the polar transmitter is that it requires an effective and wide bandwidth supply modulator, typically a DC-DC converter, to control the PA output amplitude, and that the switching frequency of the DC-DC converter risks introducing additional supply noise degrading EVM and causing out-of-band emissions. EVM contributions and emissions will also originate from the mis-alignments, bandwidth limitations, and nonlinear behaviour of the PA at low supply voltages.

**Figure 9:** A transmitter using polar modulation.

# Chapter 3

# Power Amplifiers Metrics

This chapter presents a list with a brief explanation of the most commonly used PA metrics. Understanding them is vital when designing or evaluating a PA, transmitter, or a complete system for transmission and reception of wireless signals. The most commonly used unit for the metric is indicated within brackets. To facilitate the understanding of how the metrics are used, an example for most of the metrics indicating the performance of a mmW PA is provided in the list. All the examples are taken from the PA presented in [3].

• Power gain [dB] is the output power (P<sub>out</sub>) [dBm] minus the input power (P<sub>in</sub>) [dBm] of the PA. Typically it is desirable to have high gain such that a lower input signal is required.

$$Gain = P_{out} - P_{in} \tag{6}$$

Example: The Power gain of the PA at 26.5 GHz is 16 dB

- The gain for small signals is referred to as small signal gain (SSG) [dB]. Example: The SSG of the PA at 26.5 GHz is 16 dB

- Saturated output power (P<sub>sat</sub>) [dBm], see Fig. 12, is the maximum output power that the PA can deliver. However, typically the PA cannot deliver a useful output power all the way up to P<sub>sat</sub> due to nonlinearities.

Example:  $P_{sat}$  at 26.5 GHz is 19.4 dBm

• Input referred 1 dB compression point (IP<sub>1dB</sub>) [dBm], see Fig. 12, is the input power for which the gain has compressed by 1 dB compared to the SSG. Using a third order power series expansion to express the output signal as a function of the intput signal  $v_{out}(t) = k_1 v_{in}(t) + k_2 v_{in}^2(t) + k_3 v_{in}^3(t)$ , as proposed in Eq. 53 in chapter 5 and presuming that the PA has a compressive behaviour, then IP<sub>1dB</sub> can be calculated as [19]:

$$IP_{1dB} = \sqrt{\left|\frac{4k_1}{3k_3}\right|}\sqrt{0.11} = IIP3 - 9.6 dB$$

(7)

Example:  $IP_{1dB}$  at 26.5 GHz is 2 dBm

• Output referred 1 dB compression point (OP<sub>1dB</sub>) [dBm], see Fig. 12, is the output power for which it has compressed by 1 dB compared to a linear gain of the input signal. Ideally the OP<sub>1dB</sub> should be close to P<sub>sat</sub>. According to definitions OP<sub>1dB</sub> is equal to IP<sub>1dB</sub> plus the SSG, minus 1 dB:

$$OP_{1dB} = IP_{1dB} + SSG - 1dB \tag{8}$$

Example:  $OP_{1dB}$  at 26.5 GHz is 17 dBm

• Drain efficiency (DE) or  $(\eta)$  [%], is the output power in Watts divided by the DC power consumption of the PA in Watts and defined as:

$$\eta = \frac{P_{out}}{P_{DC}} \tag{9}$$

The efficiency is signal dependent, and needs to be specified for a certain signal type and level.

Example: The DE at 26.5 GHz for a 13.3 dBm orthogonal frequency division multiplex (OFDM) signal with 1600 MHz bandwidth is 13.8 %

• Power added efficiency (PAE) [%], is the output power in Watts minus the input power in Watts, divided by the DC power consumption of the PA in Watts, and consequently defined as:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{10}$$

By taking into account also the input power required, this provides a more complete performance measure than DE.

Example: The PAE at 26.5 GHz for a 18 dBm CW tone is 17.5 %

• 1- or 3 dB small signal bandwidth (SSBW) [Hz], is the frequency bandwidth in which the SSG has decreased by less than 1- or 3 dB relative to the peak SSG.

Example: The 3 dB SSBW is 2.4 GHz

• Fractional bandwidth [%], is the ratio between the absolute bandwidth and the center frequency.

Example: The fractional bandwidth when transmitting a 1.6 GHz wide-band signal at 26.5 GHz is 6 %

- Instantaneous bandwidth [Hz], is the bandwidth that can be used concurrently for transmission.

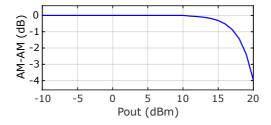

- Amplitude modulation to amplitude modulation (AM-AM), typically reported in dB as a function of input or output power in dBm, is a measure of how the signal amplification varies with the amplitude of the output signal. For low input signal levels the amplification is typically linear and the output amplitude follows the input signal amplitude with constant gain, but for large input signals the gain compresses. AM-AM shows how linear the amplification of an amplifier is, i.e. for which input and output signal levels it can be used. Fig. 10 is an example of an AM-AM plot.

Figure 10: Example of an AM-AM plot.

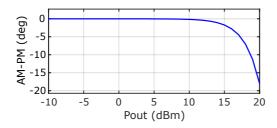

• Amplitude modulation to phase modulation (AM-PM), typically reported in degrees as a function of input or output power in dBm, is a measure of how the output phase varies with the amplitude of the output signal. For low input signal levels the amplification is typically linear and the output phase follows the phase of the input signal with a constant phase shift. As the amplitude of the input signal increases, however, the PA starts to deviate from linear amplification and the output phase might might lead or lag compared to the phase for low signal levels. AM-PM shows how well an amplifier preserves the phase information, for various output signal levels, i.e. for which input and output signal levels it can be used. Fig. 11 is an example of an AM-PM plot.

Figure 11: Example of an AM-PM plot.

- Second order output referred intercept point  $(OIP_2)$  [dBm], see Fig. 12, is the intersection of the fundamental and  $2^{\rm nd}$  order intermodulation  $(IM_2)$  products when extrapolated with a slope of  $1\,{\rm dB}/1\,{\rm dB}$  of increased input power for the fundamental and  $2\,{\rm dB}/1\,{\rm dB}$  of increased input power for the  $IM_2$  products.

- Third order output referred intercept point  $(OIP_3)$  [dBm], see Fig. 12, is the intersection of the fundamental and  $3^{\rm rd}$  order intermodulation  $(IM_3)$  products when extrapolated with a slope of  $1\,{\rm dB}/1\,{\rm dB}$  of increased input power for the fundamental and  $3\,{\rm dB}/1\,{\rm dB}$  of increased input power for the  $IM_3$  products.

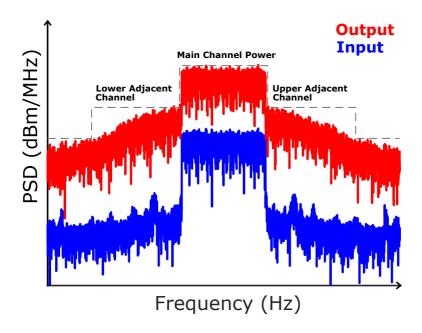

- Main channel power [dBm], is the power that is transmitted inside the intended frequency channel as shown in Fig. 13.

Example: The main channel power at 26.5 GHz for a 16-QAM OFDM signal with 1600 MHz bandwidth is 13.3 dBm

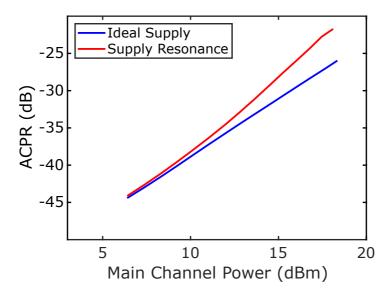

• Adjacent channel leakage ratio (ACLR) [dB], is the ratio between the transmitted power in the main channel and the power in one of the adjacent channels as shown in Fig. 13.

Example: ACLR at  $26.5\,GHz$  for a  $13.3\,dBm$  16-QAM OFDM signal with  $1600\,MHz$  bandwidth is  $27.5\,dB$

• Error Vector Magnitude (EVM) [% or dB], is the rms deviation from the desired points in the constellation diagram compared with the desired points rms amplitude.

Example: The EVM at  $26.5\,\mathrm{GHz}$  for a  $13.3\,\mathrm{dBm}$  16-QAM OFDM signal with  $1600\,\mathrm{MHz}$  bandwidth is -19.8 dB

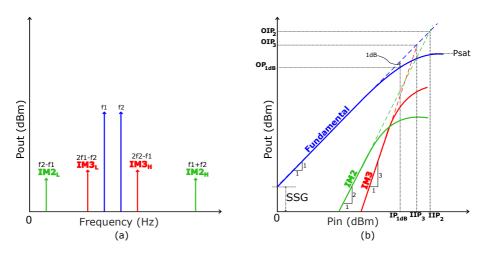

Figure 12 (a) shows a subset of the frequency tones generated from a third order nonlinearity in a two tone test. The subset in the figure consists of the two fundamentals and  $2^{\rm nd}$  and  $3^{\rm rd}$  order intermodulation products. Appendix A

shows a complete list of the frequency response from a third order nonlinearity in a two tone test. Figure 12 (b) shows the power levels of fundamental, IM2, and IM3 products as a function of input tone power. At small signal levels the fundamental tones increase linearly with input level (1 dB per 1 dB), IM2 increases quadratically (2 dB per 1 dB), and IM3 increases cubically (3 dB per 1 dB). Figure 12 (b) offers a graphical visualization of the SSG,  $OP_{1dB}$ ,  $OIP_3$ ,  $OIP_2$ ,  $IP_{1dB}$ ,  $IIP_3$ ,  $IIP_2$ , and  $P_{sat}$ .

**Figure 12:** (a): Frequency spectrum from a two tone test producing  $2^{\rm nd}$  and  $3^{\rm rd}$  order intermodulation products. (b) Pin/Pout of fundamental, IM2, and IM3, which in (a) is f1 & f2, IM2<sub>L</sub> & IM2<sub>H</sub>, and IM3<sub>L</sub> & IM3<sub>H</sub>, respectively

Figure 13 shows an example of the power spectral density (PSD) of the input and output signals to/from a PA, simulated in a  $22\,\mathrm{nm}$  FD-SOI CMOS process.

Figure 13: Example of a modulated input signal that has been amplified by a nonlinear PA. Due to third order nonlinearities power has leaked into the adjacent channels.

# Chapter 4

# Power Amplifier Classes

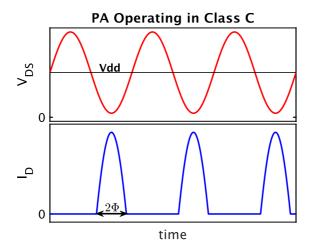

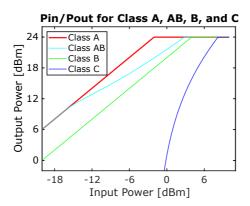

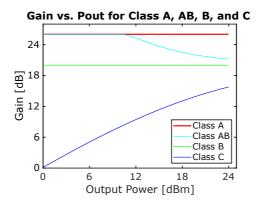

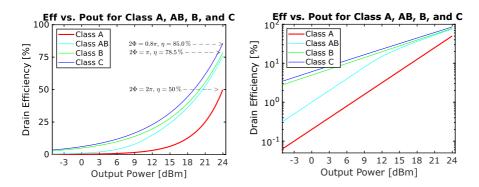

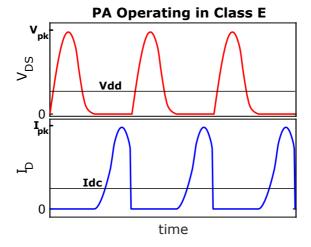

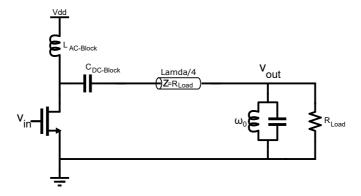

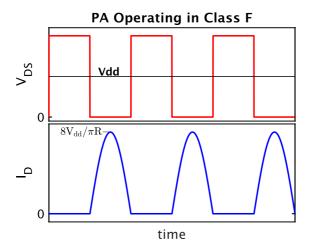

Power amplifiers classification depends on their bias, harmonic termination, and the operation mode of the transistor. In this chapter, class A to class F are discussed. More PA classes exist, but for brevity, they are left out from the discussion here. In the first three classes (A-C), the transistor operates in active mode as a voltage controlled current source, and these are referred to as transconductance mode PA classes. For the last three classes (D-F), the transistor operates in triode or cut-off region and acts as a voltage controlled switch, which are referred to as switched mode power amplifier (SMPA) classes.

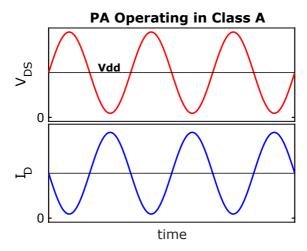

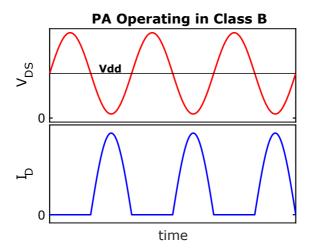

## 4.1 Transconductance PAs

In transconductance mode PAs, which are also called linear PAs, the transistor operates as a voltage controlled current source. For this the transistor needs to be biased so it remains in the active region for all input signal levels were the transistor is turned on, i.e. the voltage across the transistor, between drain and source, must not drop below the pinch-off voltage  $V_{\rm ds} > V_{\rm pinch-off}$ . Such a bias provides possibility for good linearity as the output signal is a direct representation of the input signal, at least for some portion of the cycle, but unfortunately it also results in high voltage and large current through the transistor at the same time. The power dissipated in the transistor is directly proportional to the drain-to-source voltage multiplied by the drain-to-source current, and the average power dissipation over a signal period T becomes:

$$P_{diss} = \frac{1}{T} \int_{0}^{T} v_{DS(t)} i_{DS(t)} dt$$

(11)

Which implies that to minimize the dissipated power in the transistor, the voltage across, and the current through, the transistor should be separated in time. Separation in time of the two quantities, voltage and current, is controlled by the so-called conduction angle of the PA. Generally speaking, reduced conduction angle reduces losses in the transistor and increases the efficiency of the PA. Nevertheless, as the conduction angle decreases, the part of the cycle for

which the output signal, to the first approximation, is a linear representation of the input signal, decreases, which naturally reduces the linearity of the PA, and hence the trade-off between efficiency and linearity becomes clear. However, this is a bit simplified as, theoretically, perfect linearity can be achieved not only for conduction all the time, but also for conduction of exactly half the time, i.e. for a conduction angle of  $\pi$ . Furthermore, the transistors also have a non-linear transfer from input voltage to output current, i.e. a signal level dependent transconductance that limits the PA linearity. There are also other non-linear impedances in real transistors.

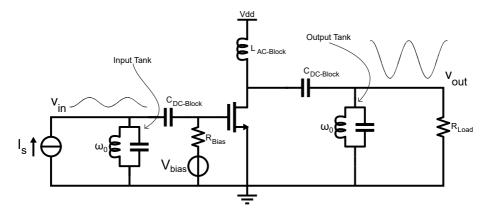

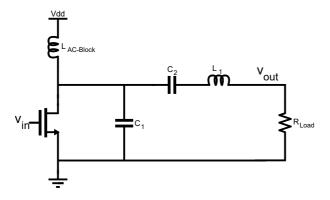

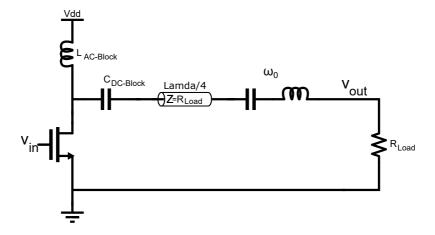

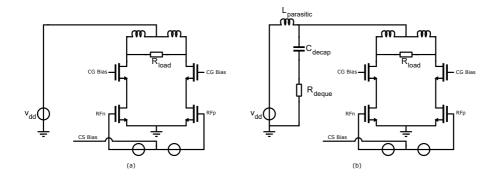

A simplified schematic of a transconductance mode PA operating at radio frequency (RF) is depicted in Fig. 14.

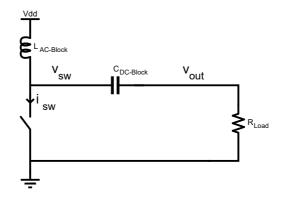

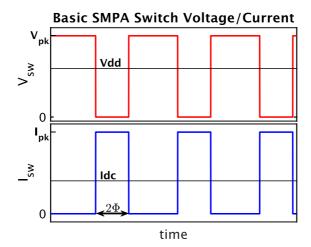

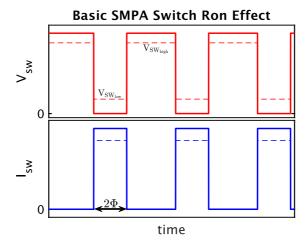

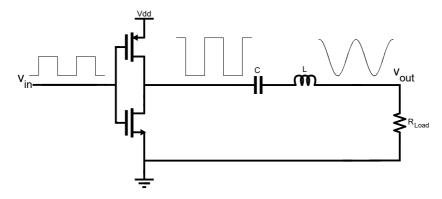

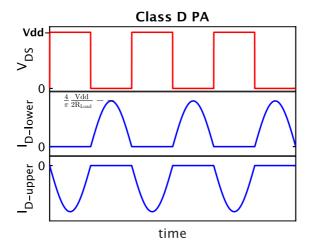

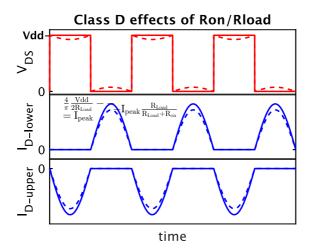

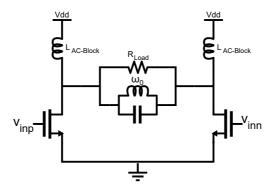

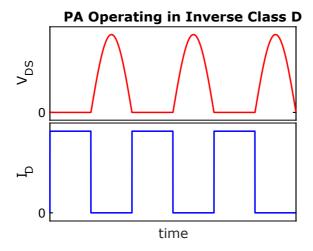

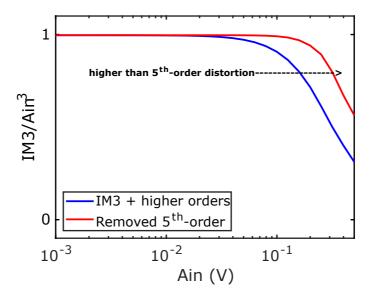

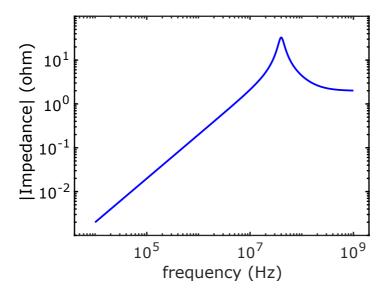

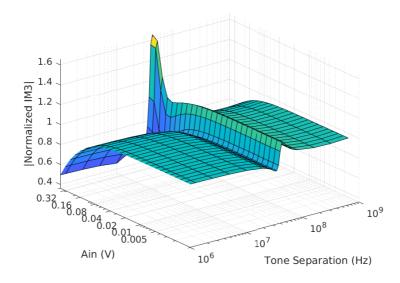

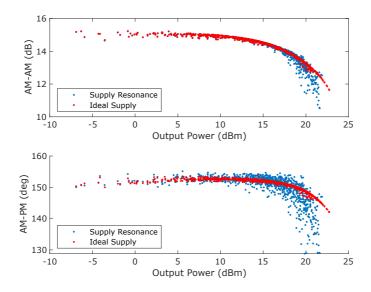

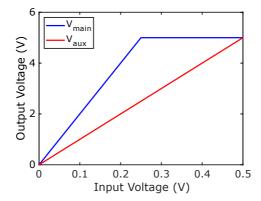

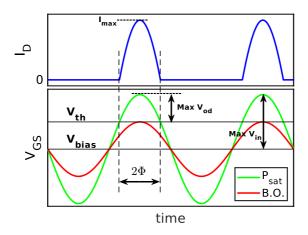

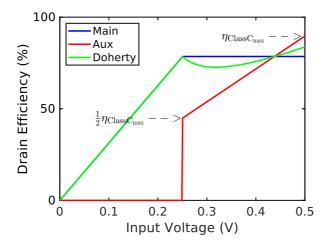

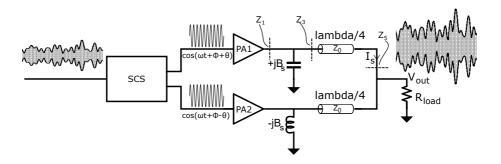

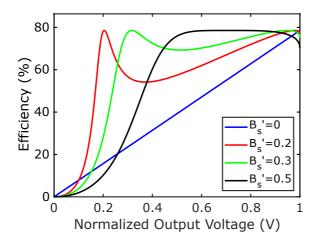

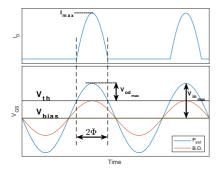

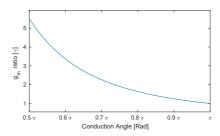

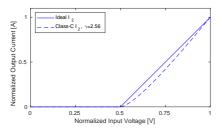

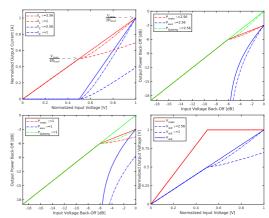

Figure 14: A general schematic of a single stage, single ended, single transistor PA