# Cryogenic ferroelectricity of HZO with an aluminum oxide interlayer

Mamidala, Karthik Ram; Wernersson, Lars-Erik

Published in:

IEEE Transactions on Electron Devices

DOI:

10.1109/TED.2025.3629590

2025

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA):

Mamidala, K. R., & Wernersson, L.-E. (2025). Cryogenic ferroelectricity of HZO with an aluminum oxide interlayer. *IEEE Transactions on Electron Devices*. Advance online publication. https://doi.org/10.1109/TED.2025.3629590

Total number of authors:

Creative Commons License:

Other

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 27. Dec. 2025

# Cryogenic Ferroelectricity of HZO with an Aluminium Oxide Inter-layer

Mamidala Karthik Ram and Lars-Erik Wernersson

Abstract— In this work, we investigate the cryogenic performance of hafnia-based ferroelectric capacitors with and without an aluminium oxide (ALO) inter-layer, comparing conventional Metal-Ferroelectric-Metal (MFM) structures to Metal-Ferroelectric-Insulator-Metal (MFIM) counterparts. Devices employing Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> as the ferroelectric layer were characterized from 300 K down to 10 K, targeting temperature ranges relevant to cryogenic logic and quantum memory. Our results reveal that the ultra-thin ALO interlaver effectively suppresses leakage across all temperatures while altering the coercive field symmetry and reducing remnant polarization as the temperature is reduced. Dynamic switching measurements and analysis show that MFM capacitors achieve near temperature-independent polarization switching at a 3.0 V WRITE amplitude. In contrast, MFIM devices show more pronounced temperature dependence in the switching behavior, particularly at temperatures below 77 K. While both the MFM and MFIM devices exhibit endurance > 10<sup>7</sup> cycles at 77 K and 10 K, the MFIM devices are more affected by polarization fatigue. Benchmarking against state-of-theart literature values confirms that our MFM and MFIM structures demonstrate among the highest reported 2Pr values below 77 K at low operating voltages (≤ 3.5 V). These results highlight the promise of inter-layer-engineered hafnia capacitors for low-power cryogenic memory applications.

Index Terms— Cryogenic, Ferroelectric, HZO, Phase Transition, FeRAM, Non-volatile Memory, Switching Dynamics, Inter-layer, Aluminium Oxide.

## I. INTRODUCTION

THE pursuit of non-volatile memory (NVM) technologies capable of operating at cryogenic temperatures (4.2 K to 77 K) is gaining momentum, driven by the demands of emerging quantum and high-performance computing architectures [1]. Proximal integration of memory with qubits and logic offers advantages such as reduced operating voltage, lower system latency, and a more compact hardware footprint [1],[2],[3]. Hafnium oxide-based ferroelectric materials have emerged as promising candidates for this role, thanks to their CMOS process compatibility and energy-efficient switching behavior [4],[5],[6],[7],[8],[9],[10]. However, gaining deeper insight into their switching characteristics across cryogenic temperatures is essential to evaluate their full potential for integration in future memory technologies.

This work is supported in part by Chips-JU (ARCTIC) under Grant 101139908 and in part by European Research Council (DYNAMISM) under Grant 101019147. Both authors are with the Department of

Many studies have explored the effect of inter-layers on improving reliability in ferroelectrics and enhancing Resistive Random Access Memory (RRAM) performance. Still, most focus on room-temperature (RT) conditions [11],[12],[13]. Studies on memory devices incorporating inter-layers at cryogenic temperatures are scarce [6],[14]. Moreover, performance comparisons of inter-layer effects at cryogenic temperatures have been explored primarily for RRAMs rather than ferroelectrics [15],[16],[17].

In this study, we systematically evaluate the cryogenic performance of hafnia-based ferroelectric capacitors by comparing Metal-Ferroelectric-Metal (MFM) and Metal-Ferroelectric-Insulator-Metal (MFIM) structures, incorporating an ultra-scaled aluminium oxide (ALO) interlayer between Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO) and the bottom electrode. Both static and dynamic polarization characteristics are studied from 300 K down to 10 K, with measurements taken at 14 intermediate temperatures spanning the cryogenic regime. To the best of our knowledge thus far, this is the first study to systematically compare MFM and MFIM capacitor performance across such a broad temperature range, with a particular focus on the 4.2 K to 77 K quantum memory window. The analysis includes leakage current measurements, coercive field evolution, polarization switching dynamics, capacitance-voltage characteristics, and endurance measurements up to 10<sup>7</sup> cycles. This comparison directly reveals the design trade-offs between the two structures. While the Al<sub>2</sub>O<sub>3</sub> inter-layer suppresses leakage and stabilizes coercive fields under endurance cycling, it does so at the expense of remnant polarization amplitude. In contrast, MFM capacitors maintain a stronger remnant polarization but exhibit higher leakage and more field-cycling-induced imprint. These insights, combined with benchmarking against prior reports, offer preliminary guidelines for tailoring hafnia-based ferroelectrics toward different cryogenic memory applications such as ferroelectric Field-Effect Transistors (FeFETs), where leakage and switching stability are critical, versus ferroelectric random access memory (FeRAM), where higher polarization is prioritized.

## II. DEVICE FABRICATION AND MEASUREMENT SETUP

To investigate the cryogenic properties of ferroelectric capacitors with  $Hf_{0.5}Zr_{0.5}O_2$  as the switching layer, both Metal-Ferroelectric-Metal (MFM) and Metal-Ferroelectric-Insulator-Metal (MFIM) stacks are fabricated. The fabrication begins with a 10-nm-thick TiN bottom electrode (BE) deposition on a

Electrical and Information Technology, Lund University, 221 00 Lund, Sweden (e-mail: karthik ram.mamidala@eit.lth.se).

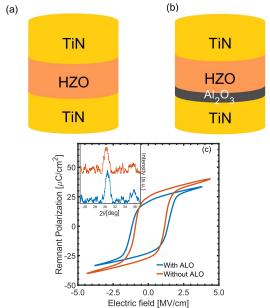

Fig. 1. (a) and (b) Cross-sectional schematics of the MFM and MFIM capacitor structures respectively. (c) *P–E* characteristics of both devices at room temperature after wake-up (10 kHz, 3.5 V), with inset showing GI-XRD confirming the presence of the o(111)/t(011) phase.

thermally oxidized Si substrate using physical vapor deposition (PVD). For MFIM capacitors, about 1.2-nm-thick Al<sub>2</sub>O<sub>3</sub> (12 cycles) (ALO) inter-layer is subsequently deposited via atomic layer deposition (ALD) using trimethylaluminum (TMAI) and H<sub>2</sub>O as precursors. This deposition is followed by an about 8nm-thick Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> layer deposited using ALD with alternating pulses of TDMA-Hf and TEMA-Zr for 40 cycles each. A 10 nm TiN top electrode (TE) is deposited via PVD, completing the stack. All samples undergo rapid thermal annealing (RTA) at 550 °C for 30 s to crystallize the ferroelectric layer. Device patterning is carried out using UV lithography followed by Ti/Au (5 nm/200 nm) contact deposition via electron-beam evaporation. Schematic illustrations of the MFM and MFIM capacitors are shown in Fig. 1(a) and (b), respectively. Electrical characterization is performed using a Keysight B1500 parameter analyzer equipped with B1530A waveform generators in a Lakeshore CRX-4K cryogenic probe station and the grazing incidence xray diffraction (GI-XRD) was obtained using a Bruker D8 Discover X-ray diffraction system.

## III. ELECTRICAL CHARACTERIZATION AND ANALYSIS

All measurements (except leakage and GI-XRD measurements) are performed on devices first subjected to a wake-up operation (WU) at room temperature (RT). The wake-up operation consists of a 1 kHz bipolar signal with one thousand square pulses and a peak amplitude of 3.0 V at RT. Further, due to the differing insulator thicknesses of the MFM and MFIM capacitors, the total dielectric thickness is used for electric field calculation. Specifically, an 8 nm thickness corresponding to the HZO layer is used for the sample without ALO, while a combined thickness of 9.2 nm (8 nm HZO + 1.2 nm Al<sub>2</sub>O<sub>3</sub>) is

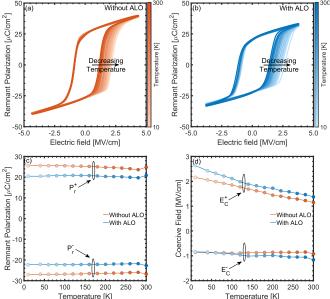

Fig. 2. *P-E* characteristics of the same Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> capacitor after WU at RT and measured from 300 K to 10 K for the samples (a) without ALO and (b) with ALO where the colour bars indicate the temperatures. (c) Remnant polarization and (d) coercive field across the temperature range for both samples.

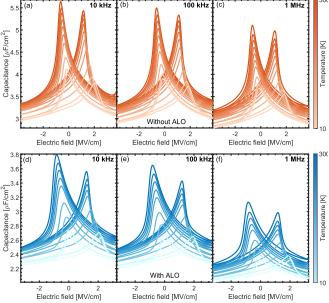

Fig. 3. C-V characteristics of the same  $Hf_{0.5}Zr_{0.5}O_2$  capacitor after WU at RT and measured from 300 K to 10 K for the sample without ALO at (a) 10 kHz, (b) 100 kHz and (c) 1 MHz; for the sample with ALO at (d) 10 kHz, (e) 100 kHz and (f) 1 MHz

used for the sample with ALO. The electric field is calculated as  $E = V/t_{ox}$ , where  $t_{ox}$  is the total insulator thickness, to maintain consistency across all electrical measurements performed in this study. Fig. 1(c) shows the polarization–electric field (P-E) characteristics of both devices measured at room temperature after wake-up, using a 10 kHz triangular bipolar signal with a peak amplitude of 3.5 V. The addition of the ALO inter-layer results in a slightly reduced remnant polarization and larger coercive fields [25]. The inset in Fig. 1(c) presents grazing-incidence X-ray diffraction patterns of the

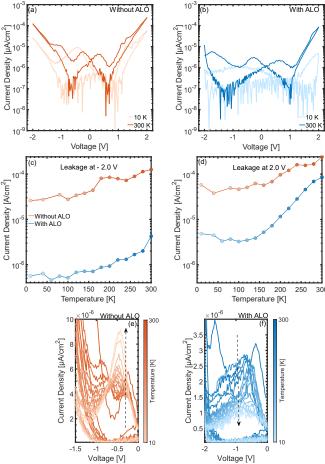

Fig. 4. *J-E* characteristics of the same pristine  $Hf_{0.5}Zr_{0.5}O_2$  capacitor first measured at RT and measured from 300 K to 10 K for the samples (a) without ALO and (b) with ALO. Leakage currents at (c) -2.0 V and (d) 2.0 V across the temperature range for both the samples. Linear scale leakage current across all temperatures for the (e) without ALO and (f) with ALO samples where the colour bars indicate the temperatures.

two structures, recorded at an incidence angle of  $0.5^{\circ}$ . Both devices exhibit a diffraction peak at  $\approx 30.5^{\circ}$ , corresponding to the o(111)/t(011) phase, confirming the presence of the orthorhombic ferroelectric phase in HZO.

To study the temperature dependence of remnant polarization (P<sub>r</sub>) and coercive fields (E<sub>C</sub>), P-E characteristics are evaluated at multiple temperatures and can be seen in Figs. 2(a) and (b). Similar to Fig. 1(c), the devices are exposed to a 10 kHz triangular bipolar signal with a peak amplitude of 3.5 V after a wake-up operation, then cooled to 10 K, and the measurements are repeated. This measurement method ensures that temperature is the only variable in the study. As the temperature is lowered for either device, the gradual shift in the positive coercive field is quite evident. In contrast, no notable visual difference in the remnant polarization can be observed from the P-E characteristics for either device. To visualize the effect of temperature in more detail, the positive and negative remnant polarizations (P<sub>r</sub><sup>+</sup> and P<sub>r</sub><sup>-</sup>) for both devices at each temperature can be seen in Fig. 2(c). A minor initial decrease in the remnant polarization is observed for both samples from 300 K to 280 K. However, beyond this point, the device without ALO exhibits a monotonic increase in remnant polarization down to 10 K. Notably, the remnant polarization at 10 K

slightly exceeds its value at 300 K. This behavior is consistent with reports attributing enhanced low-temperature polarization to increased stabilization of the ferroelectric orthorhombic (o) phase, accompanied by a reduction in the monoclinic (m) and anti-ferroelectric tetragonal (t) phases at cryogenic temperatures [18],[19],[20],[21],[22]. The device with ALO shows a different trend, Pr increases from 280 K to approximately 140 K, beyond which it begins to saturate and subsequently decline. At 10 K, its P<sub>r</sub> falls below the roomtemperature value unlike the device without ALO. Earlier studies have reported that for thicker ferroelectric films, there is an expansion of the dead layer at the interfaces at cryogenic temperatures, which could lead to a reduction in remnant polarization [19]. Perhaps, the addition of an ultra-scaled approximately 1.2-nm-thick aluminium oxide inter-layer is sufficient to cause this phenomenon. Fig. 2(d) shows the temperature dependence on the positive and negative coercive fields  $(E_C^+)$  and  $E_C^-$  for both the devices. As the temperature decreases, a clear increase in Ec+ is observed for both samples which agrees with the Vopsaroiu model [23] extending it to lower temperatures. A similar temperature dependence was reported and modelled in [23], where a linear increase in the coercive field was observed between 493 K and 274 K, supported by electrical measurements. Reduced thermal energy and enhanced domain wall pinning at low temperatures necessitate higher fields for polarization reversal [6],[23],[24]. Interestingly, E<sub>C</sub><sup>-</sup> remains nearly constant in the device without ALO, which may point to an underlying asymmetry in the energy landscape, potentially stemming from intrinsic material properties or asymmetric defect concentrations at the interfaces, favouring one polarization orientation. In contrast, the device with ALO exhibits a slight increase in E<sub>C</sub> with decreasing temperature. This increase may suggest that the ALO interlayer contributes to a partial reduction in switching asymmetry, potentially by screening internal built-in fields. It is also possible that the inter-layer modifies the spatial distribution of defects relative to free carriers, which could influence local field profiles and polarization switching behavior. The observed increase in coercive fields with decreasing temperature may be attributed to a combination of reduced trapmediated screening and interfacial depolarization. At room temperature, trap-assisted tunneling likely provides additional charge that helps to screen ferroelectric polarization. As the temperature is lowered, this process becomes progressively weaker, reducing the availability of compensating charge [19]. In MFIM capacitors, this effect could be further amplified by the series-capacitance penalty of the ALO inter-layer, which redistributes the applied voltage between HZO and ALO. As a result, the effective field across the ferroelectric may be reduced, requiring a higher external field for polarization reversal. A related explanation was reported in [22], where suppressed charge-injection-assisted switching at low temperatures was linked to a reduction in remnant polarization at lower temperatures. While the exact interplay between these mechanisms remains open to further study, our results are

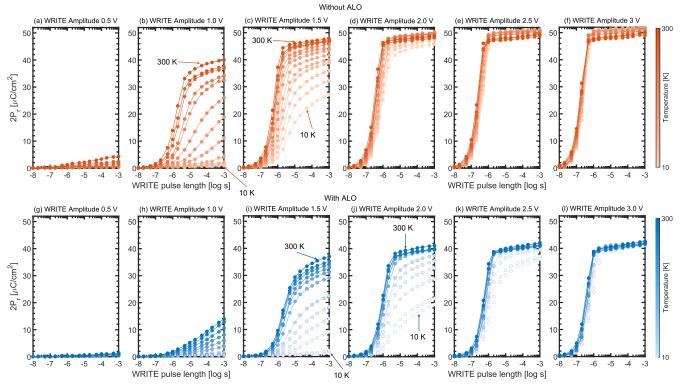

Fig. 5. Polarization switching dynamics of HZO capacitors with and without an ALO interlayer as a function of WRITE pulse width at various temperatures with different WRITE amplitudes where the colour bar indicates the temperatures. (a)–(f) correspond to the sample without ALO at WRITE amplitudes of 0.5 V to 3.0 V, respectively. (g)–(l) show the same for the sample with ALO.

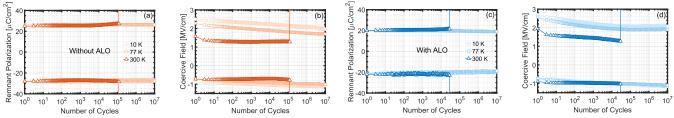

Fig. 6. Evolution of remnant polarization and coercive fields during endurance cycling of devices (a)—(b) without ALO and (c)—(d) with ALO at 300 K, 77 K, and 10 K. For all, the circular marker is 10 K, square marker is 77 K, and triangular marker is 300 K.

consistent with such interpretations.

Capacitance–voltage (C-V) characteristics of devices with and without ALO are shown in Fig. 3 for temperatures ranging from 300 K down to 10 K, measured at three frequencies (10 kHz, 100 kHz, and 1 MHz). At all frequencies, both devices exhibit the characteristic butterfly-shaped C-V response of ferroelectric HZO. With decreasing temperature, the C-Vcurves shift toward higher applied voltages while retaining the butterfly form, consistent with the trend observed in the P-Echaracteristics. In agreement with earlier reports [18], the overall capacitance magnitude decreases as temperature is lowered. The device with ALO consistently shows a lower peak capacitance than the device without ALO, which is attributed to the series addition of the Al<sub>2</sub>O<sub>3</sub> interlayer capacitance and the associated depolarization effects. A frequency dependence is also evident. While both device types display dispersion between 10 kHz and 1 MHz, it is more pronounced in the device with ALO.

Current leakage measurements were conducted to investigate

further the temperature dependence of leakage behavior in both capacitors. A pristine device was first measured at 300 K using a voltage sweep from -2 V to +2 V and back to -2 V. The same device was subsequently cooled to 10 K, and the measurement was repeated. The device was then heated in steps back to 300 K, with the same leakage measurements performed at each intermediate temperature. Figs. 4(a) and (b) show the leakage current at 300 K and 10 K for the devices without ALO and with ALO, respectively. In either device, the leakage current is significantly lower at 10 K compared to 300 K, which is attributed to the suppression of thermionic emission at cryogenic temperatures. Figs. 4(c) and (d) display the leakage current values across the entire temperature range for both capacitors at  $\pm$  2 V. For the device without ALO, the leakage currents at -2 V and +2 V are nearly symmetrical and exhibit a near linear decrease with temperature, consistent with a thermionic emission-dominated transport mechanism. In contrast, the sample with ALO exhibits consistently lower leakage current across all temperatures and voltages, owing to

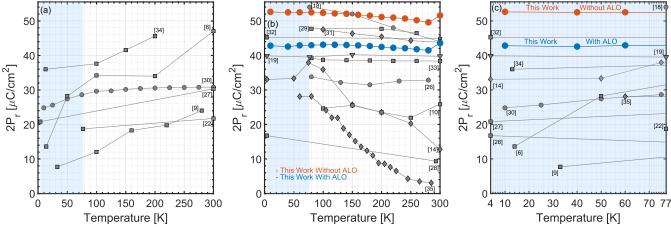

Fig. 7. Benchmarking of  $2P_r$  at different temperatures reported in literature for devices operated at  $\leq 3.5$  V. (a) Studies where  $2P_r$  decreases with decreasing temperature. (b) Studies where  $2P_r$  remains stable or increases with decreasing temperature, including this work (with and without ALO). (c) Comparison within the cryogenic CMOS memory window (4 K -77 K), relevant for quantum computing applications. The regions coloured in blue highlight the cryoCMOS memory temperature range.

the added tunneling barrier introduced by the aluminum oxide inter-layer. Interestingly, a pronounced asymmetry is observed in the device with ALO. The leakage current at -2 V is nearly an order of magnitude lower than at + 2 V. This could be due to the ALO layer increasing the tunneling barrier under negative bias. Additionally, in Fig. 4(a), while the leakage current at  $\pm 2$  V decreases at 10 K, a localized increase is seen near  $\approx 0.6$  V during the negative sweep, potentially due to polarization switching. To investigate this further, Figs. 4(e) and (f) show the negative sweep leakage currents for both devices on a linear scale. For the sample without ALO in Fig. 4(e), we observe that a current bump appears and becomes more pronounced as temperature decreases (as indicated by the arrow in the figure). This feature can be attributed to the polarization switching current, which may be enhanced by the emergence of the orthorhombic ferroelectric phase and suppression monoclinic and tetragonal anti-ferroelectric phases at cryogenic temperatures [18],[19],[20],[21],[22]. At the same time, even having an ultra-scaled ≈ 1.2 nm aluminium oxide interlayer seems to prohibit this phenomenon. In contrast, a current peak is visible at room temperature for the sample with ALO in Fig. 4(f) but diminishes progressively at lower temperatures. This current variation suggests that the ultra-scaled ( $\approx 1.2$  nm) ALO interlayer may inhibit phase evolution or suppress switching currents, possibly due to increased depolarization effects or interface-induced screening.

Fig. 5 illustrates the polarization switching dynamics of HZO capacitors with and without an ALO interlayer, as a function of WRITE pulse width, WRITE amplitude, and temperature. At a WRITE amplitude of 0.5 V [Figs. 5(a) and (g)], both devices exhibit negligible switching across all temperatures, with 2P<sub>r</sub> remaining near zero. This behaviour confirms that 0.5 V is insufficient to overcome the coercive voltage in either device, consistent with previous findings on minimum switching thresholds in hafnia-based ferroelectrics. At 1.0 V, the sample without ALO [Fig. 5(b)] begins to show noticeable switching at higher temperatures, although switching remains suppressed at

cryogenic temperatures. In contrast, the ALO sample [Fig. 5(h)] continues to exhibit minimal switching across the temperature range. This discrepancy aligns with the higher coercive fields measured in the ALO device [Fig. 2(d)], as reported in other studies where inter-layers increased the required switching voltage by altering the internal field distribution [11],[25]. With a WRITE amplitude of 1.5 V, the ALO sample [Fig. 5(i)] shows improved switching at higher temperatures, resembling the non-ALO device's behavior at 1.0 V. However, switching at 10 K remains negligible. Meanwhile, the non-ALO device [Fig. 5(c)] shows consistent polarization reversal across all temperatures, albeit with lower 2P<sub>r</sub> at reduced temperatures. This behavior is expected due to stronger domain wall pinning and reduced domain mobility at low thermal energies. As the WRITE amplitude increases further from 2.0 - 3.0 V [Figs. 5(d-f), and (j-l)], both devices show enhanced switching. At 3.0 V, the non-ALO device demonstrates nearly uniform switching across all temperatures for pulse widths up to ~500 ns, with the 2P<sub>r</sub> at 10 K even exceeding that at 300 K [Fig. 5(f)]. This observation agrees with the low-temperature trends seen in Fig. 2(c) and supports the view that higher fields can compensate for kinetic limitations at cryogenic temperatures [6],[9]. While improved at higher voltages, the ALO device still exhibits stronger temperature dependence. The 2P<sub>r</sub> at 10 K remains below that at room temperature, and the switching uniformity is not as robust as in the non-ALO counterpart. This behavior may result from increased depolarization fields, interface screening, or inhibited domain wall motion introduced by the ultra-thin ALO layer, all of which are known to influence switching performance in scaled ferroelectric stacks. These results highlight a fundamental trade-off: while the ALO interlayer effectively suppresses leakage (see Fig. 4), it also imposes switching limitations that must be balanced when designing ferroelectric devices for cryogenic logic and memory applications. The effect of this trade-off is found to be stronger at cryogenic conditions as compared to room temperature operation.

Fig. 6 summarizes the evolution of remnant polarization and coercive fields during endurance cycling for devices with and without the ALO inter-layer. All devices were first subjected to a wake-up sequence of 1000 bipolar square pulses (3.0 V, 1 kHz, RT). Endurance cycling was then carried out using triangular bipolar pulses (3.5 V, 10 kHz), consistent with the P-E measurements in Fig. 1(c) and Fig. 2, at 300 K, 77 K, and 10 K. For the MFM devices [Figs. 6(a)-(b)], robust switching is observed at 77 K and 10 K up to 10<sup>7</sup> cycles, while the 300 K device experiences breakdown earlier. In contrast, the MFIM devices [Figs. 6(c)-(d)] also maintain endurance beyond 107 cycles at cryogenic temperatures but exhibit a modest reduction in remnant polarization with cycling. These observations mirror the trends in Fig. 2, where the ALO devices consistently show slightly lower 2P<sub>r</sub> than their non-ALO counterparts. A gradual imprint effect, reflected in the shift of the coercive field with cycling, is evident at 77 K and 10 K in both device types. However, the imprint appears more stabilized in the MFIM devices, where the change in the positive coercive field begins to saturate with cycling. At 300 K, however, the MFIM devices exhibit marginally lower endurance than their MFM counterparts, consistent with earlier reports on similar interlayer-based stacks [13]. This behaviour can be attributed to the role of the ALO inter-layer in suppressing leakage and limiting charge injection during field cycling. In addition, the presence of the inter-layer introduces voltage division across the stack, requiring a higher external field to achieve polarization switching [25]. The increased external stress and limited dynamic charge compensation, may accelerate interfacial degradation and contribute to earlier breakdown at room temperature. At cryogenic temperatures, where trap activity and leakage are inherently reduced, this trade-off becomes less pronounced, and the MFIM devices demonstrate stable switching and endurance beyond 10<sup>7</sup> cycles. This behaviour suggests that while the ALO devices sacrifice some polarization amplitude, they exhibit more stable switching fields under prolonged cycling at cryogenic temperatures. Taken together with their reduced leakage (Fig. 4), the capacitors with the ALO inter-layer may offer advantages for FeFET integration where memory window stability is critical, whereas the capacitors without the inter-layer, with higher remnant polarization, may be more suitable for FeRAM type cryogenic applications.

Finally, to assess the performance of our HZO-based ferroelectric capacitors, we benchmarked the 2 × remanent polarization (2P<sub>r</sub>) against state-of-the-art ferroelectric capacitors reported in the literature, focusing on measurements performed at cryogenic temperatures under an operating voltage  $\leq$  3.5 V. The benchmarking results are summarized in Fig. 7. Specifically, Fig. 7(a) includes reports where 2P<sub>r</sub> decreases with decreasing temperature ([6], [9], [22], [27], [30], [34]), while Fig. 7(b) shows studies where 2P<sub>r</sub> remains stable or increases as temperature is reduced ([10], [14], [18], [19], [26], [28], [29], [31]–[33], [35]), along with the results of this work (with and without ALO). Fig. 7(c) highlights the temperature

window relevant for CMOS-compatible cryogenic memory in quantum computing applications (4 K – 77 K, shaded in blue [1]). Within this regime, our devices exhibit competitive reported 2P<sub>r</sub> values, with the sample without the ALO interlayer consistently  $\sim 10 \,\mu\text{C/cm}^2$  higher than the inter-layer case. To further substantiate these trends, the Supplementary Information includes: (i) a comprehensive benchmarking table listing ferroelectric material, thickness, interlayer material and thickness, applied voltage, and observed temperature dependence across reported studies, (ii) measured variation across five independent devices each for both samples with and without ALO, showing consistent 2P<sub>r</sub> trends with temperature from 300 K down to 10 K and (iii) an inter-layer benchmarking comparison, where our MFIM devices are evaluated against other inter-layer-based capacitors from the literature. While many of these prior reports show strong temperature-driven variation in 2P<sub>r</sub>, our MFIM structures exhibit comparatively more stable and consistent performance, across the cryogenic temperature range. These results confirm that our HZO capacitors, with or without an ALO inter-layer, deliver competitive and consistent polarization performance at cryogenic temperatures and are promising candidates for future low-temperature memory applications.

#### IV. CONCLUSION

This study comprehensively evaluates the role of an ultrathin aluminium oxide inter-layer on the cryogenic behaviour of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>-based ferroelectric capacitors. We demonstrate that MFIM structures significantly reduce leakage and modify coercive switching behavior, albeit with some suppression in remnant polarization and switching robustness at cryogenic temperatures. In contrast, MFM structures maintain strong and uniform switching even at 10 K, especially under a 3.0 V WRITE bias. Endurance measurements confirm stable operation up to 10<sup>7</sup> cycles without hard breakdown at cryogenic temperatures, and C-V analysis reveals consistent ferroelectric switching across frequencies. Comparative benchmarking reveals that both configurations provide top-performing cryogenic ferroelectric devices at low operating voltages. Similar trends were observed across multiple devices. These findings offer valuable design guidelines for advancing lowpower, non-volatile cryogenic memory systems and integrating ferroelectric components into quantum computing infrastructure.

#### **ACKNOWLEDGEMENTS**

The authors would like to thank André Andersen and Erik Wikare from the Department of Electrical and Information Technology, Lund University for their respective assistance with characterization.

## **REFERNCES**

[1] S. Alam, M. S. Hossain, S. R. Srinivasa, and A. Aziz, "Cryogenic Memory Technologies," *Nature Electronics*, vol. 6, no. 3, pp. 185–198, 2023. doi:10.1038/s41928-023-00930-2

- [2] B. Patra et al., "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," in *IEEE Journal of Solid-State Circuits*, vol. 53, no. 1, pp. 309-321, Jan. 2018, doi: 10.1109/JSSC.2017.2737549

- [3] S. S. Tannu, D. M. Carmean, and M. K. Qureshi, "Cryogenic-DRAM based memory system for scalable quantum computers," *Proceedings* of the International Symposium on Memory Systems, 2017. doi:10.1145/3132402.3132436

- [4] M. K. Ram, Z. Zhu and L. -E. Wernersson, "Multi-level Vertical III-V Nanowire Gate-All-Around Ferroelectric FETs for In-Memory Computing," 2025 Device Research Conference (DRC), Durham, NC, USA, 2025, pp. 1-2, doi: 10.1109/DRC66027.2025.11105745.

- [5] C.-Y. Liao et al., "Multibit Ferroelectric FET Based on Nonidentical Double HfZrO<sub>2</sub> for High-Density Nonvolatile Memory," in *IEEE Electron Device Letters*, vol. 42, no. 4, pp. 617-620, April 2021, doi: 10.1109/LED.2021.3060589.

- [6] M. K. Ram, H. Dahlberg and L. -E. Wernersson, "Cryogenic Ferroelectricity of HZO Capacitors on a III–V Semiconductor," in *IEEE Electron Device Letters*, vol. 45, no. 10, pp. 1827-1830, Oct. 2024, doi: 10.1109/LED.2024.3448378.

- [7] Z. Zhu, M. Karthik Ram, A. E. O. Persson and L. -E. Wernersson, "Low-Frequency Noise in Ferroelectric III–V Vertical Gate-All-Around FETs," in *IEEE Electron Device Letters*, vol. 46, no. 5, pp. 741-744, May 2025, doi: 10.1109/LED.2025.3546165.

- [8] T. Ali et al., "A Multilevel FeFET Memory Device based on Laminated HSO and HZO Ferroelectric Layers for High-Density Storage," 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 28.7.1-28.7.4, doi: 10.1109/IEDM19573.2019.8993642.

- [9] J. W. Adkins, I. Fina, F. Sánchez, S. R. Bakaul, and J. T. Abiade, "Thermal evolution of ferroelectric behavior in epitaxial HF<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>," Applied Physics Letters, vol. 117, no. 14, Oct. 2020. doi:10.1063/5.0015547.

- [10] D. Wang et al., "Stable ferroelectric properties of HF<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films within a broad working temperature range," *Japanese Journal of Applied Physics*, vol. 58, no. 9, p. 090910, Aug. 2019. doi:10.7567/1347-4065/ab3844.

- [11] K. Ni et al., "Critical Role of Interlayer in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Ferroelectric FET Nonvolatile Memory Performance," in *IEEE Transactions on Electron Devices*, vol. 65, no. 6, pp. 2461-2469, June 2018, doi: 10.1109/TED.2018.2829122.

- [12] K.-M. Persson, M. S. Ram and L.-E. Wernersson, "Ultra-Scaled AlOx Diffusion Barriers for Multibit HfOx RRAM Operation," in *IEEE Journal of the Electron Devices Society*, vol. 9, pp. 564-569, 2021, doi: 10.1109/JEDS.2021.3079398.

- [13] R. Alcala, F. Mehmood, P. Vishnumurthy, T. Mittmann, T. Mikolajick and U. Schroeder, "Influence of Interfacial Oxide Layers in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> based ferroelectric capacitors on reliability performance," 2022 IEEE International Memory Workshop (IMW), Dresden, Germany, 2022, pp. 1-4, doi: 10.1109/IMW52921.2022.9779287.

- [14] H. Bohuslavskyi, K. Grigoras, M. Ribeiro, M. Prunnila, and S. Majumdar, "Ferroelectric hf<sub>0.5</sub>zr<sub>0.5</sub>O<sub>2</sub> for analog memory and inmemory computing applications down to deep cryogenic temperatures," *Advanced Electronic Materials*, May 2024. doi:10.1002/aelm.202300879.

- [15] M. Saketh Ram, M. Karthik Ram and L. -E. Wernersson, "Cryogenic Evaluation of Resistive Random Access Memory With Enhanced Endurance at 14 K," in *IEEE Transactions on Electron Devices*, vol. 72, no. 2, pp. 678-682, Feb. 2025, doi: 10.1109/TED.2024.3520948.

- [16] Z. Hao et al., "Cryogenic HfO<sub>x</sub>-Based Resistive Memory With a Thermal Enhancement Capping Layer," in *IEEE Electron Device Letters*, vol. 42, no. 9, pp. 1276-1279, Sept. 2021, doi: 10.1109/LED.2021.3099725.

- [17] A. Andersen, S. R. Mamidala, and L. Wernersson, "Interface Characterization of plasma-treated inas electrodes for resistive randomaccess memories using capacitance-voltage methods," *physica status* solidi (a), Jan. 2025. doi:10.1002/pssa.202400689

- [18] Y. Xing et al., "Improved Ferroelectricity in Cryogenic Phase Transition of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>," in *IEEE Journal of the Electron Devices Society*, vol. 10, pp. 996-1002, 2022, doi: 10.1109/JEDS.2022.3218004.

- [19] D. Zhang et al., "Unveiling Ferroelectric HZO Cryogenic Performance (4–300 K): Kinetic Barrier Engineering and Underlying Mechanism," in *IEEE Transactions on Electron Devices*, vol. 72, no. 4, pp. 1788-1794, April 2025, doi: 10.1109/TED.2025.3546871.

- [20] Y. -C. Chen, K. -Y. Hsiang, M. -H. Lee and P. Su, "NLS based Modeling of Temperature-dependent Phase Transition Characteristics for Antiferroelectric/Ferroelectric Hafnium Zirconium Oxides," 2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT), HsinChu, Taiwan, 2023, pp. 1-2, doi: 10.1109/VLSI-TSA/VLSI-DAT57221.2023.10133951.

- [21] M. H. Park et al., "Origin of temperature-dependent ferroelectricity in SI-doped HFO2," Advanced Electronic Materials, vol. 4, no. 4, Mar. 2018. doi:10.1002/aelm.201700489

- [22] J. Hwang, C. Kim, J. Ahn, and S. Jeon, "Enhanced performance of hafnia self-rectifying ferroelectric tunnel junctions at cryogenic temperatures," *Nano Convergence*, vol. 11, no. 1, Dec. 2024. doi:10.1186/s40580-024-00461-2

- [23] M. Vopsaroiu, P. M. Weaver, M. G. Cain, M. J. Reece, and Kok Boon Chong, "Polarization dynamics and non-equilibrium switching processes in Ferroelectrics," *IEEE Transactions on Ultrasonics*, Ferroelectrics and Frequency Control, vol. 58, no. 9, pp. 1867–1873, Sep. 2011. doi:10.1109/tuffc.2011.2025

- [24] D. Zhao et al., "Depolarization of multidomain ferroelectric materials," Nature Communications, vol. 10, no. 1, Jun. 2019. doi:10.1038/s41467-019-10530-4

- [25] H. Dahlberg, A. E. Persson, R. Athle, and L.-E. Wernersson, "Ferroelectric-antiferroelectric transition of HF<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> on indium arsenide with enhanced ferroelectric characteristics for HF<sub>0.2</sub>Zr<sub>0.8</sub>O<sub>2</sub>," ACS Applied Electronic Materials, vol. 4, no. 12, pp. 6357–6363, Dec. 2022. doi:10.1021/acsaelm.2c01483.

- [26] F. Mehmood, T. Mikolajick, and U. Schroeder, "Wake-up mechanisms in ferroelectric lanthanum-doped Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films," *physica status* solidi (a), vol. 217, no. 22, Sep. 2020. doi:10.1002/pssa.202000281

- [27] J. Hur, Y. -C. Luo, Z. Wang, S. Lombardo, A. I. Khan and S. Yu, "Characterizing Ferroelectric Properties of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> From Deep-Cryogenic Temperature (4 K) to 400 K," in *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 7, no. 2, pp. 168-174, Dec. 2021, doi: 10.1109/JXCDC.2021.3130783.

- [28] M. D. Henry, S. W. Smith, R. M. Lewis, and J. F. Ihlefeld, "Stabilization of ferroelectric phase of Hf<sub>0.58</sub>Zr<sub>0.42</sub>O<sub>2</sub> on NBN at 4 K," *Applied Physics Letters*, vol. 114, no. 9, Mar. 2019. doi:10.1063/1.5052435

- [29] S. Li et al., "Temperature-dependent subcycling behavior of si-doped HFO<sub>2</sub> ferroelectric thin films," ACS Applied Electronic Materials, vol. 3, no. 5, pp. 2415–2422, May 2021. doi:10.1021/acsaelm.1c00330.

- [30] Y. Zhou et al., "Anomalous polarization-switching phenomena and noteworthy pyroelectricity in Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> polycrystalline films," *Materials Today Physics*, vol. 43, p. 101414, Apr. 2024. doi:10.1016/j.mtphys.2024.101414

- [31] D. Zhou et al., "Electric field and temperature scaling of polarization reversal in silicon doped hafnium oxide ferroelectric thin films," *Acta Materialia*, vol. 99, pp. 240–246, Oct. 2015. doi:10.1016/j.actamat.2015.07.035

- [32] A. Agarwal et al., "Yttrium Doped Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Based Ferroelectric Capacitor Exhibiting Fatigue Free (>10<sup>12</sup> cycles), Long Retention, and Imprint Immune Performance at 4 K," in *IEEE Electron Device Letters*, doi: 10.1109/LED.2025.3562798.

- [33] K.-Y. Hsiang et al., "Cryogenic Endurance of Anti-ferroelectric and Ferroelectric Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> for Quantum Computing Applications," 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2023, pp. 1-4, doi: 10.1109/IRPS48203.2023.10118311

- [34] A. E. O. Persson, R. Athle, J. Svensson, M. Borg, and L.-E. Wernersson, "A method for estimating defects in ferroelectric thin-film MOSCAPs," *Applied Physics Letters*, vol. 117, no. 24, p. 242902, Dec. 2020. doi: 10.1063/5.0029210.

- [35] M. Hoffmann, U. Schröder, C. Künneth, A. Kersch, S. Starschich, U. Böttger, and T. Mikolajick, "Ferroelectric phase transitions in nanoscale HfO<sub>2</sub> films enable giant pyroelectric energy conversion and highly efficient supercapacitors," *Nano Energy*, vol. 18, pp. 154–164, Nov. 2015, doi: 10.1016/j.nanoen.2015.10.008.