#### **III-V MOSFETs for High-Frequency and Digital Applications**

Zota, Cezar

2017

Document Version: Publisher's PDF, also known as Version of record

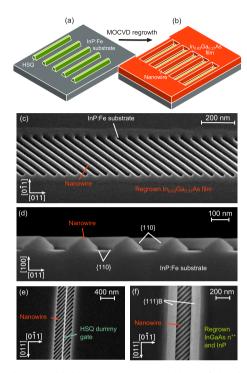

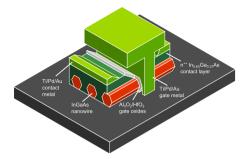

Link to publication

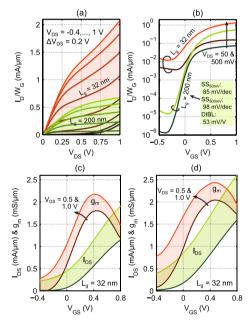

Citation for published version (APA):

Zota, C. (2017). *III-V MOSFETs for High-Frequency and Digital Applications*. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 19. Dec. 2025

# III-V MOSFETs for High-Frequency and Digital Applications

Doctoral Thesis

Cezar Bogdan Zota

Electrical Engineering Lund, May 2017

Cezar Bogdan Zota Department of Electrical and Information Technology Lund University Ole Römers väg 3, 223 63 Lund, Sweden

Series of licentiate and doctoral theses ISSN 1654-790X; No. 96 ISBN 978-91-7753-144-9 (printed) ISBN 978-91-7753-145-6 (digital)

© 2017 Cezar Bogdan Zota Typeset in Palatino and Helvetica using  $\LaTeX 2_{\varepsilon}$ . Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

### **Abstract**

III-V compound semiconductors are used in, among many other things, high-frequency electronics. They are also considered as a replacement for silicon in CMOS technology. Yet, a III-V transistor outperforming state-of-the-art silicon devices in VLSI-relevant metrics has not yet decisively been demonstrated. In this work, the limits of III-V FET performance, for both RF and VLSI applications, are explored experimentally.

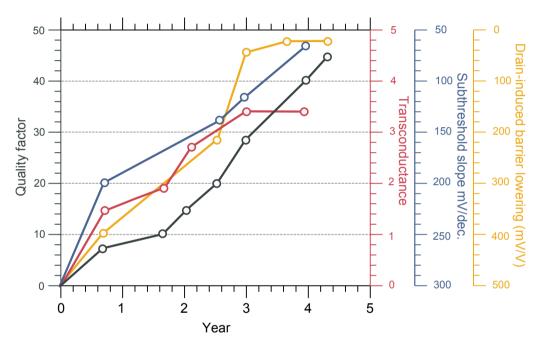

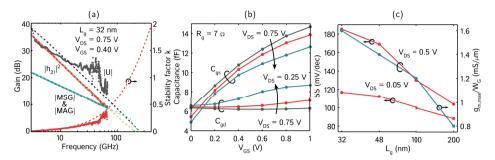

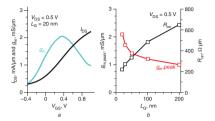

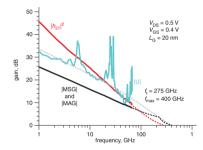

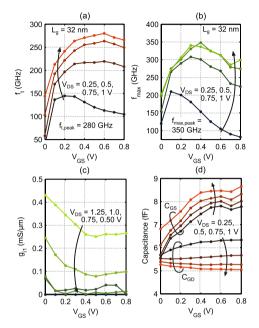

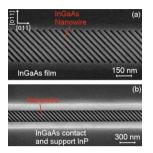

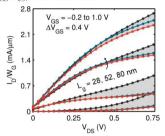

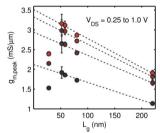

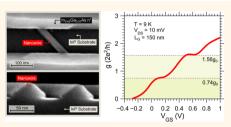

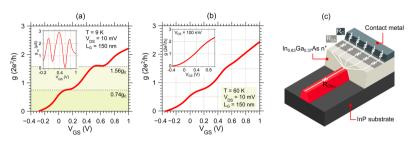

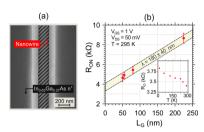

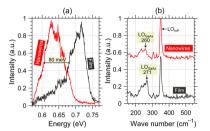

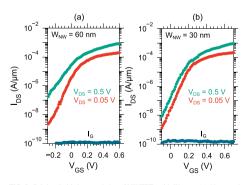

MOSFETs using selectively grown lateral InGaAs nanowires as the channel are demonstrated. The performance of devices using this technology includes among the highest reported transconductance for any transistor of 3.3 mS/µm, among the lowest subthreshold slope of a III-V FET at sub-100 nm gate length of 66 mV/decade, as well as the highest reported on-current (at  $I_{OFF}=100$  nA/µm and  $V_{DD}=0.5$  V) of 650 µA/µm, for any transistor, thus outperforming current industrial silicon MOSFETs. RF-compatible devices exhibit extrapolated  $f_t$  and  $f_{max}$  of 275 GHz and 400 GHz, respectively, the highest combined values for a III-V MOSFET. Junctionless InGaAs transistors where also fabricated, demonstrating a simplified process scheme and record performance for junctionless devices, with  $g_m=1.6$  mS/µm and SS = 76 mV/decade.

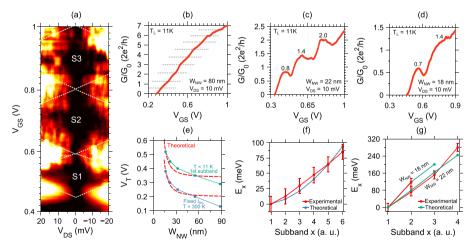

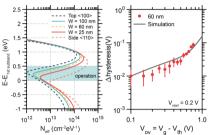

Several techniques for characterization of these kinds of devices have also been developed. Low-temperature measurement of single nanowire transistors revealed the presence of quantized conductance, among the first reports for a high-performance device. From the quantized conductance, the electron mean free path was determined in the range of 140 to 180 nm, indicating excellent material quality and device operation deep in the ballistic regime. Furthermore, it was shown that subband quantization significantly impacts device performance through threshold voltage variability.

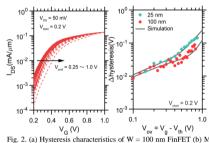

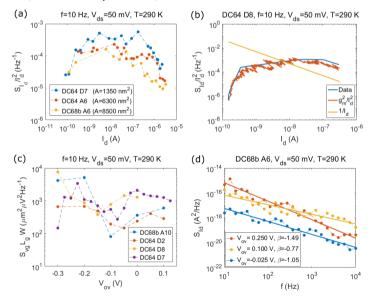

Oxide characterization was performed through hysteresis measurements, leading to a general method of determining trap distributions of specific surfaces in a multigate FET. Finally, noise characterization in terms of 1/f and RF noise was performed on single nanowire devices and RF-compatible devices, respectively, showing low input gate voltage noise and promising RF noise performance.

### Populärvetenskaplig Sammanfattning

Bara sedan de senaste 50 åren har datorerna förändrat våra liv och vårt samhälle i grunden. De har skapat den digitala eran och informationsåldern. Allt detta började 1947, då Shockley, Bardeen och Brattain, tre forskare vid Bell Labs i USA uppfann transistorn, för vilken de senare vann Nobelpriset i fysik. Transistorn föddes ur ett behov av att förstärka elektriska signaler, något som man tidigare hade gjort främst med elektronrör. Dessa hade många användningsområden, till exempel för radio och telefoni, men begränsades av hög effektförbrukning och av att de lätt gick sönder. Den första transistorn bestod av en halvledarkristall, germanium, med tre metallkontakter, och den visade sig inte bara fungera som utmärkt förstärkare av elektriska signaler, utan också lösa de problem som hörde till elektronrören.

Elektronikindustrin tog fart på riktigt först med uppfinnandet av den integrerade kretsen, på slutet av 50-talet, av forskare på Texas Instrument. Där man tidigare satte ihop elektriska kretsar för hand med pincetter, kunde man med den integrerade kretsen tillverka alla kretselementen direkt på halvledarkristallen. Detta underlättade tillverkningen enormt, och tillät en kontinuerlig utveckling, med mindre, snabbare och energisnålare kretsar– en utveckling som fortsätter ännu idag, och bygger främst på halvedaren kisel.

Dagens teknologi har emellertid blivit så komplex, och de minsta beståndsdelarna av transistorn har blivit så små, att en vidare utveckling snart förespås bli svår. Ett av problemen är att energiförbrukningen per area i en processor, som består av flera miljarder transistorer på en yta av någon kvadratcentimer, har blivit exceptionellt hög– snart lika hög som i en kärnreaktor. Detta gör chippet svårt att kyla, och kan leda till att det slutar fungera.

Där den tidigare utvecklingen främst byggt på att göra transistorn mindre, har forskare på senare år börjat se till andra typer av förbättringar. En sådan möjlig förbättring är användandet av III-V sammansatta halvledare, till exempel indiumgallium-arsenid, även kallad InGaAs. Elektroner i InGaAs har en högre hastighet än i kisel, vid samma spänning. Genom att sänka drivspänningen till ett chip byggt med InGaAs, kan det fungera lika bra som ett byggt med kisel, men förbruka mindre energi. Denna avhandling omfattar design och tillverkning av InGaAs-transistorer som visas slå kisel-transistorer i viktiga prestandamått, och representerar de bäst presterande transistorerna för lågenergiapplikationer som någonsin tillverkats.

### **Acknowledgments**

This thesis is dedicated to my mother for her unwaivering support and endless kindness. Time flies, but some things remain the same, and I am thankful for that.

I would like to express my gratitude to my supervisor Erik. We have shared many things over these last few years, have had many ideas, some excellent, some merely good, and the rest forgotten. But personally, I will never forget my time here, and I hope our friendship will last through the years.

Lars-Erik, you have been a role model to me, in arts both technical and not. The many things I have learned from you, I will value for life.

My gratitude also to my co-supervisor Mattias, and my friends and colleagues in our group. Johannes, thank you for your friendship. Elvedin, we have had many laughs togethers, and a more dependable friend I could hardly find. Fredrik, Guntrade, Aein, Jun, Sebastian, Sofia, Olli-Pekka, Kristofer, Markus, Stefan and Adam, I hope these years have been only the beginning of our friendships. And to my fellow prospectors Anil, Karl-Magnus, Martin— our pursuit has been a crash course in the ups and downs of life, but ultimately, the dream is still alive.

Also, my colleagues at the department of Solid State Physics and friends in the lab, Tim, Peter, Bekmurat, David, Robert, Erik, Malin, Simon, Neimantas, Vishal, to name a few.

My sincere gratitude is also dedicated professor Takagi-sensei and professor Takenaka-sensei, under whose supervision I began my journey into science. Sang-Hyeon, Noguchi, Chang, Sang-Hoon and all my colleagues from Tokyo University, have my sincerest gratitude and friendship.

My gratitude also to the head of the department, Daniel, as well as Pia, Elisabeth and the rest of the administrative staff at EIT. The lab staff at the Lund Nano Lab have done much to make this work possible, Maria, Ivan, Anders, George, Håkan, Mariusz, Dmitry, Peter, David and Sara.

And, of course, my friends and family, my girlfriend and our dog. Sniff, from your love of playing with rocks, we all have much to learn.

Cezar Bogdan Zota Lund, June 2017

## **Contents**

| Abstract                                           |  |  |         | iii   |

|----------------------------------------------------|--|--|---------|-------|

| Populärvetenskaplig Sammanfattning                 |  |  |         | V     |

| Acknowledgments                                    |  |  |         | vii   |

| Contents                                           |  |  |         | ix    |

| List of Papers                                     |  |  |         | xiii  |

| Abbreviations and Symbols                          |  |  | 7       | xvii  |

| Abbreviations                                      |  |  |         | xvii  |

| Greek Symbols                                      |  |  | <br>. > | xviii |

| Latin Symbols                                      |  |  |         | xix   |

| 1: Background                                      |  |  |         | 1     |

| 1.1: Early History of the Transistor               |  |  |         | 1     |

| 1.2: Transistor Scaling                            |  |  |         | 2     |

| 1.3: III-V Compound Semiconductors                 |  |  |         | 3     |

| 1.4: Digital Applications                          |  |  |         | 5     |

| 1.5: High-Frequency Applications                   |  |  |         | 6     |

| 1.6: Motivation                                    |  |  |         | 7     |

| 2: Transistor Theory                               |  |  |         | 9     |

| 2.1: Benchmarking MOSFETs for Digital Applications |  |  |         | 9     |

| 2.2: Theory of Ballistic 1D MOSFETs                |  |  |         | 9     |

| 2.2.1: Ballistic Transconductance                  |  |  |         | 13    |

| 2.2.2: Quasi-ballistic Devices                     |  |  |         | 14    |

| 2.2.3: Multiple Sub-bands                          |  |  |         | 16    |

| 2.2.4. Non-Parabolicity                            |  |  |         | 17    |

|    | 2.2.5: The Density of States Bottleneck | 17  |

|----|-----------------------------------------|-----|

|    | 2.2.6: Interface Traps                  | 18  |

|    | 2.3: Device Characteristics             | 19  |

|    | 2.3.1: Extrinsic Transconductance       | 19  |

|    | 2.3.2: Oxide Capacitance                | 20  |

|    | 2.3.3: Natural Length Scale             | 22  |

| 3: | RF-Transistors                          | 25  |

|    | 3.1: High-Frequency Characterization    | 25  |

|    | 3.2: The Small-Signal Model             | 26  |

|    | 3.3: High-Frequency Performance         | 28  |

| 4: | Transistor Design & Fabrication         | 31  |

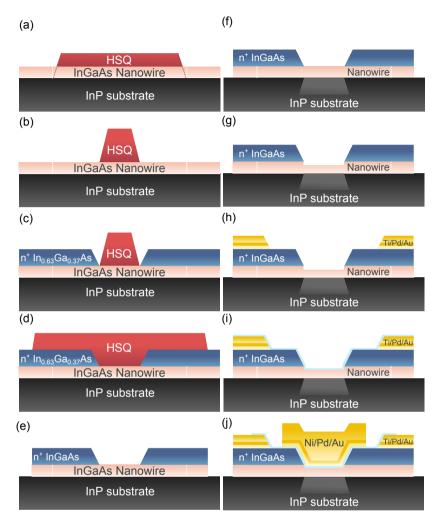

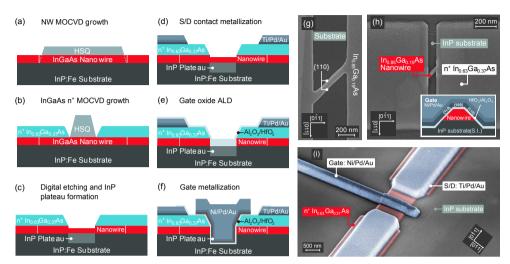

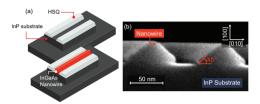

|    | 4.1: Selective Area Nanowire Growth     | 31  |

|    | 4.1.1: Mask-Induced Enrichment          | 33  |

|    | 4.1.2: Nanowire Facets                  | 34  |

|    | 4.2: Contact Regrowth                   | 34  |

|    | 4.2.1: Silicide-like Formation          | 35  |

|    | 4.2.2: MOCVD Contact Growth             | 36  |

|    | 4.3: Mesa Definition                    | 38  |

|    | 4.4: Source and Drain Metallization     | 38  |

|    | 4.5: Gate Oxide Deposition              | 39  |

|    | 4.6: Gate Metallization                 | 40  |

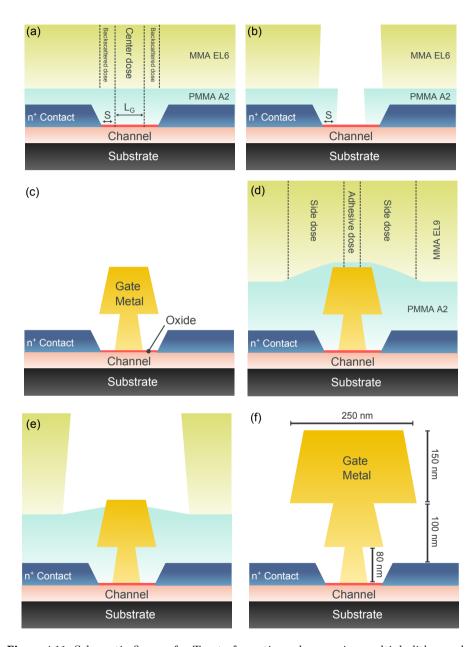

|    | 4.6.1: T-Gate Formation                 | 41  |

| 5: | Summary and Conclusions                 | 47  |

|    | 5.1: Summary of Papers                  | 47  |

|    | 5.2: Future Work                        | 52  |

|    | 5.2.1: Off-state Improvements           | 52  |

|    | 5.2.2: On-state Improvements            | 52  |

|    | 5.2.3: RF-performance Improvements      | 53  |

|    | F. 2. Canalysians                       | E / |

| A: Appendix A                                                                                                                                                      | 57    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| A.1: Device Fabrication                                                                                                                                            | . 57  |

| A.1.1: Single Nanowire MOSFETs                                                                                                                                     | . 57  |

| A.1.2: RF-Compatible MOSFETs                                                                                                                                       | . 61  |

| Bibliography                                                                                                                                                       | 65    |

| PAPERS                                                                                                                                                             | 77    |

| I: InGaAs Tri-gate MOSFETs With Record On-current                                                                                                                  | 79    |

| II: High-Performance Lateral Nanowire InGaAs MOSFETs With Improved On-Current                                                                                      | 85    |

| III: InGaAs Nanowire MOSFETs With I $_{\rm ON}=555$ uA/um at I $_{\rm OFF}=100$ nA/um and V $_{\rm DD}=0.5$                                                        | 91    |

| IV: Single Suspended InGaAs Nanowire MOSFETs                                                                                                                       | 95    |

| V: $In_{0.53}Ga_{0.47}As$ Multiple-Gate Field-Effect Transistors With Selectively Regrown Channels                                                                 | 101   |

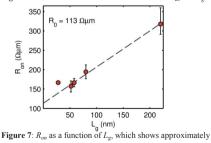

| VI: High-Frequency InGaAs Tri-Gate MOSFETs With $f_{ m max}$ of 400 GH                                                                                             | Iz107 |

| VII: Radio-Frequency Characterization of Selectively Regrown InGaAs<br>Lateral Nanowire MOSFETs                                                                    | 111   |

| VIII: ${ m In}_{0.63}{ m Ga}_{0.37}{ m As}$ FinFETs using selectively regrown nanowires with peak transconductance of 2.85 mS/ $\mu{ m m}$ at ${ m V}_{ds}=$ 0.5 V | 119   |

| IX: Quantized Conduction and High Mobility in Selectively Grown $\text{In}_x \text{Ga}_{x-1} \text{As Nanowires}$                                                  | 123   |

| X: Size-Effects in Indium Gallium Arsenide Nanowire Field-Effect Transistors                                                                                       | 131   |

| XI: A Method for Determining Trap Distributions of Specific Channel Surfaces in InGaAs Tri-gate MOSFETs                                                            | 137   |

| XII: 1/f and RTS Noise in InGaAs Nanowire MOSFETs                                                                                                                  | 143   |

### **List of Papers**

This thesis is based on the work presented in the following papers, referred to by their roman numerals. They are organized here into three groups: low-power digital applications, high-frequency applications and device and material characterization.

#### LOW-POWER DIGITAL APPLICATIONS

- Paper I: C. B. ZOTA, F. LINDELÖW, L.-E. WERNERSSON AND E. LIND, "In-GaAs Tri-gate MOSFETs With Record On-current," 2016 IEEE Int. Electron Devices Meeting (IEDM), pp. 3.2.1–3.2.4, Dec. 2016.

- ▶ I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper II: C. B. ZOTA, L.-E. WERNERSSON AND E. LIND, "High-Performance Lateral Nanowire InGaAs MOSFETs With Improved On-Current", *IEEE Electron Device Letters*, vol. 37, no. 10, pp. 1264–1267, Oct. 2016.

- ▶ I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper III: C. B. ZOTA, F. LINDELÖW, L.-E. WERNERSSON AND E. LIND, "In-GaAs Nanowire MOSFETs With  $I_{\rm ON}=555~{\rm uA/um}$  at  $I_{\rm OFF}=100~{\rm nA/um}$  and  $V_{\rm DD}=0.5$ " Symposium on Very Large Scale Integrated Circuits and Technology (VLSI), Jun. 2016.

- ▶ I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper IV: <u>C. B. Zota</u>, L.-E. Wernersson and E. Lind, "Single Suspended InGaAs Nanowire MOSFETs," 2015 IEEE Int. Electron Devices Meeting (IEDM), pp. 31.2.1–31.2.4, Dec. 2015.

- ightharpoonup I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper V: C. B. ZOTA, L.-E. WERNERSSON AND E. LIND, "In<sub>0.53</sub>Ga<sub>0.47</sub>As Multiple-Gate Field-Effect Transistors With Selectively Regrown Channels," *IEEE Electron Device Letters*, vol. 35, no. 3, pp. 342–344, Mar. 2014.

▶ I designed, fabricated and measured the devices, as well as wrote the paper.

#### **HIGH-FREQUENCY APPLICATIONS**

- Paper VI: <u>C. B. ZOTA</u>, F. LINDELÖW, L.-E. WERNERSSON AND E. LIND, "High-Frequency InGaAs Tri-Gate MOSFETs With f<sub>max</sub> of 400 GHz," *Electronics Letters*, vol. 55, no. 22, pp. 1869–1871, Sept. 2016.

- ▶ I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper VII: C. B. ZOTA, G. ROLL, L.-E. WERNERSSON AND E. LIND, "Radio-Frequency Characterization of Selectively Regrown InGaAs Lateral Nanowire MOSFETs," *IEEE Transactions on Electron Devices*, vol. 61, no. 12, pp. 4078–4083, Dec. 2014.

- ▶ I designed, fabricated and measured the devices, as well as wrote the paper.

- **Paper VIII:** C. B. ZOTA, L.-E. WERNERSSON AND E. LIND, "In<sub>0.63</sub>Ga<sub>0.37</sub>As Fin-FETs using selectively regrown nanowires with peak transconductance of 2.85 mS/ $\mu$ m at V<sub>ds</sub> = 0.5 V," 72nd Annual Device Research Conference (DRC), pp. 209–210, Jun. 2014.

- ▶ This paper won the 72nd DRC best student paper award.

- ightharpoonup I designed, fabricated and measured the devices, as well as wrote the paper.

#### **DEVICE AND MATERIAL CHARACTERIZATION**

- **Paper IX:** <u>C. B. ZOTA</u>, D. LINDGREN, L.-E. WERNERSSON AND E. LIND, "Quantized Conduction and High Mobility in Selectively Grown  $In_xGa_{x-1}As$  Nanowires," *ACS Nano*, vol. 9, no. 10, pp. 9892–9897, 2015.

- ightharpoonup I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper X: C. B. ZOTA AND E. LIND, "Size-Effects in Indium Gallium Arsenide Nanowire Field-Effect Transistors," Applied Physics Letters, vol. 108, no. 6, p. 063505, 2016.

- ightharpoonup I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper XI: S. Netsu, M. Hellenbrand, <u>C. B. Zota</u>, Y. Miyamoto and E. Lind, "A Method for Determining Trap Distributions of Specific Channel Surfaces in InGaAs Tri-gate MOSFETs," *IEEE Journal of the Electron Device Society*, in review, 2017.

- ▶ I performed the device fabrication and helped to write the paper.

- Paper XII: C. MÖHLE, <u>C. B. ZOTA</u>, M. HELLENBRAND AND E. LIND, "1/f and RTS Noise in InGaAs Nanowire MOSFETs," *Microelectronics Journal*, accepted for publication, 2017.

- ▶ I performed the device fabrication and helped to write the paper.

#### **EXTRANEOUS PAPERS**

The following papers are not included in the thesis, but summarise related work which I have contributed to.

- Paper XIII: C. B. ZOTA, M. BORG, L.-E. WERNERSSON AND E. LIND, "Record Performance for Junctionless Transistors in InGaAs MOSFETs" Symposium on Very Large Scale Integrated Circuits and Technology (VLSI), Jun. 2017.

- ightharpoonup I designed, fabricated and measured the devices, as well as wrote the paper.

- Paper XIV: C. B. ZOTA, L.-E. WERNERSSON AND E. LIND, "High transconductance,  $f_{\rm t}$  and  $f_{\rm max}$  in In<sub>0.63</sub>Ga<sub>0.37</sub>As FinFETs using a novel fin formation technique," 26th International Conference on Indium Phosphide and Related Materials (IPRM), May 2014.

- $\blacktriangleright$  Invited paper, presented at the conference by the author of this thesis.

- ▶ I designed, fabricated and measured the devices; wrote the paper.

- Paper XV: C. B. ZOTA, S.-H. KIM, M. YOKOYAMA, M. TAKENAKA AND S. TAKAGI, "Characterization of Ni-GaSb alloys formed by direct reaction of Ni with GaSb," *Applied Physics Express*, vol. 5, no. 7, pp. 071201, 2012.

- Paper XVI: C. B. ZOTA, S.-H. KIM, Y. ASAKURA, M. TAKENAKA AND S. TAK-AGI, "Self-aligned metal S/D GaSb p-MOSFETs using Ni-GaSb alloys," 70th Annual Device Research Conference (DRC), pp. 71–72, Jun. 2012.

- Paper XVII: C. B. ZOTA, L.-E. WERNERSSON AND E. LIND, "Self-aligned metal S/D GaSb p-MOSFETs using Ni-GaSb alloys," *GigaHertz 2014*, Gothenburg, Sweden, Mar. 2014.

- Paper XVIII: C. B. ZOTA, L.-E. WERNERSSON AND E. LIND, "Conductance quantization in Quasi-ballistic InGaAs nanowire MOSFETs," 73rd Annual Device Research Conference (DRC), pp. 257–258, Jun. 2015.

- Paper XIX: F. LINDELÖW, <u>C. B. ZOTA</u>, L.-E. WERNERSSON AND E. LIND, "High transconductance InGaAs Nanowire MOSFETs," *GigaHertz 2016*, Linkoping, Sweden, Mar. 2016.

- **Paper XX:** F. LINDELÖW, <u>C. B. ZOTA</u> AND E. LIND, "Hall effect measurements on lateral InGaAs nanowire transistors," *Nanowire Week 2017*, accepted for poster presentation, 2017.

- Paper XXI: F. LINDELÖW, <u>C. B. ZOTA</u>, L.-E. WERNERSSON AND E. LIND, "Gated Hall Effect Measurements on Selectively grown InGaAs Nanowires," *Nanotechnology*, accepted for publication, 2017.

- Paper XXII: C. MÖHLE, <u>C. B. ZOTA</u>, M. HELLENBRAND AND E. LIND, "1/f and RTS Noise in InGaAs Nanowire MOSFETs," *Conference on Insulating Films on Semiconductors (INFOS)*, Jun., 2017.

- Paper XXIII: C. B. ZOTA, F. LINDELÖW, L.-E. WERNERSSON AND E. LIND, "High-Performance Field-Effect Transistors Using Selectively Grown Lateral InGaAs Nanowires," *Nanowire Week 2017*, Jun., 2017.

- Paper XXIV: L. Ohlsson, F. Lindelöw, <u>C. B. Zota</u>, M. Ohlrogge, T. Merkle, L.-E. Wernersson and E. Lind, "First InGaAs Lateral Nanowire MOSFET RF Noise Measurements and Model," 75rd Annual Device Research Conference (DRC), Jun., 2017.

### **Abbreviations and Symbols**

#### **ABBREVIATIONS**

$(NH_4)_2S$  diammonium sulphide

AC alternating current

Al aluminum

$Al_2O_3$  aluminum oxide

**ALD** atomic layer deposition

CMOS complementary metal-oxide-semiconductor

**CPU** central processing unit

**DOS** density of states

**DUT** device under test

**EOT** effective oxide thickness

**FET** field-effect transistor

GAA gate-all-around

GaAs gallium arsenide

GaSb gallium antimonide

$\mathbf{H}_2\mathbf{O}_2$  hydrogen peroxide

$\mathbf{H}_3\mathbf{PO}_4$  phosphoric acid

HCl hydrochloric acid

**HEMT** high-electron-mobility transistor

**HF** hydrofluoric acid

**HfO**<sub>2</sub> Hafnium oxide

**HSQ** hydrogen silsesquixane

In indium

InAlAs indium aluminum arsenide

InAs indium arsenide

InGaAs indium gallium arsenide

InP indium phosphide

ITRS international technology roadmap for semiconductors

$\mathbf{La}_2\mathbf{O}_3$  lanthanum oxide

Mo molybdenum

${f MOCVD}$  metal organic chemical vapor deposition

MOSCAP metal-oxide-semiconductor capacitor

MOSFET metal-oxide-semiconductor field-effect transistor

NH<sub>4</sub>OH ammonium hydroxide

Ni nickel

Pd palladium

PDA post-deposition annealing

PMMA poly(methyl methacrylate)

QCL quantum capacitance limit

RF radio-frequency

S. I. semi-insulating

$\mathbf{S}/\mathbf{D}$  source and drain

Si silicon

$\mathbf{SiO}_2$  silicon dioxide

Sn tin

SPL single pixel line

${\bf SRAM}$  static random access memory

${f SS}$  inverse subthreshold slope

$\mathbf{TESn} \ \ \mathbf{tetraethyltin}$

Ti titanium

TiN titanium nitride

VLS vapour-liquid-solid

VLSI very-large-scale integration

W tungsten

$\mathbf{Y}_2\mathbf{O}_3$  yttrium oxide

$\mathbf{ZrO}_2$  Zirconium oxide

#### **GREEK SYMBOLS**

$\varepsilon(0)$  top of the barrier energy

$\lambda$  mean free path

$\mu$  carrier mobility

$\sigma$  surface energy

$\boldsymbol{\beta}$  adhesion energy

$\rho_C$  specific contact resistivity

$\kappa$  dielectric constant

#### LATIN SYMBOLS

$\boldsymbol{C_{it}}$  capacitance due to interface traps

${\cal C}_L$  load capacitance

$\boldsymbol{C_{OX}}$  oxide capacitance

$C_Q$  quantum capacitance

D diffusion constant

$\boldsymbol{D_{it}}$  density of interface traps

$\boldsymbol{E_F}$  Fermi level

$E_G$  band gap

$f_{max}$  maximum oscillation frequency

$f_t$  cut-off frequency

$\boldsymbol{G}$  Gibb's free energy

$g_d$  output conductance

$\boldsymbol{g_m}$  transconductance

$I_{OFF}$  off-state current

$I_{ON}$  on-state current

$\boldsymbol{k}$  wave vector

$\boldsymbol{L_G}$  gate length

${m M}$  number of conducting subbands

$m^*$  effective electron mass

$N_D$  donor doping concentration

$n_{1D}$  1-D carrier density under bias  $n_0$  carrier density under zero bias

$\boldsymbol{Q}$  channel charge

$R_g$  gate resistance  $R_{ON}$  on-resistance

T ballistic transmission  $T_L$  crystal lattice temperature

$egin{aligned} V_{DD} & ext{drive bias} \\ V_T & ext{threshold voltage} \end{aligned}$

### **Background**

#### 1.1 EARLY HISTORY OF THE TRANSISTOR

During the last century, humanity has experienced a tremendous advancement of computational power. An important step in this advancement was made in 1907 by Lee De Forest, with his invention of the triode. The triode is an amplifying vacuum tube, consisting of an anode, a cathode and a control grid inside a vacuum sealed glass container. This is a transconductance device: A voltage signal applied to the control grid results in an amplified current signal at the anode. Five years later, De Forest sold his triode patent to AT&T, who intended to use it for amplification of long-distance telephone communication signals. These devices, however, proved unreliable and consuming much power, and in the 1930's, it was recognized that a better amplifier was needed.

Meanwhile, semiconductor diodes made of high-purity germanium were developed at Bell labs during the war, for use in radar applications. Using this newly gained expertise in semiconductors, William Shockley secured funding for the work on a semiconductor amplifier. John Bardeen and Walter Brattain were also recruited to his team at the AT&T Laboratories, where they began work on what would be the point-contact transistor, demonstrated in December of 1947 (Figure 1.1). This device consisted of two closely spaced gold contacts on one side of a germanium crystal which was placed on a metal plate. A small current applied to one of the gold contacts amplified the current flowing from the other gold contact to the metal plate. This was the first experimental demonstration of what was termed a transistor - a contraction of transresistance, for which the three where jointly awarded the Nobel Prize in Physics in 1956.

Commercialization of transistors began in the 1950's, after the invention of the bipolar junction transistor by Shockley. Applications at the time included hearing aids and transistor radios. The first transistor-based commercial computer was the IBM 7070, introduced in 1958 by IBM. By that time, transistors had become common in various electrical products. Circuits where manufactured by hand using tweezers to connect the various components. In 1958, Jack Kilby at Texas Instruments built the first integrated circuit – all the circuit components where made directly on the same semiconductor crystal, this allowed smaller and easier

Figure 1.1: The first transistor fabricated used a germanium crystal substrate on a metal plate, and two gold contacts, one on each side of the triangular wedge, which is pushed onto the crystal by the spring. (Photo by Jacopo Werther.)

to produce circuits. Kilby was awarded the Nobel Prize in Physics in 2000 for this invention.

Independently, Robert Noyce of Fairchild Semiconductor invented a similar circuit in 1959. In 1968, he and colleague Gordon Moore started Intel (a contraction of Integrated Electronics), initially manufacturing bipolar static random access memory (SRAM), and in 1969 the first commercial metal-oxide-semiconductor field-effect transistor (MOSFET) SRAM based on silicon. Gordon Moore summarized the pursuit of the integrated circuit industry in the title of his paper from 1965, "Cramming more components onto integrated circuits", and in the prediction later called Moore's law, from the same paper: The number of transistors in an integrated circuit approximately doubles every year (later revised to two years) [1]. A fortuitous circumstance was that this pursuit was accompanied by both vast technological possibilities and huge economical incentives. These factors drove the increase of transistor count in a central processing unit (CPU) from thousands in the 1970's to billions in 2017, and gave rise to the digital era.

#### 1.2 TRANSISTOR SCALING

The prevailing rule guiding the improvement of transistor performance through most of its history was Dennard scaling [2]. Dennard observed in 1974 that the drive bias and current of a transistor should be kept proportional to its dimensions. Thus,

as the transistor dimensions are scaled down, so is its power consumption reduced. This rule of thumb keeps the power density of the chip constant. At the same time, due to the reduced transistor area, leading to a reduction of the capacitance, the performance of the transistor improved, allowing operation at higher frequencies [3].

What Dennard scaling did not account for was the off-state leakage current, which does not scale with device dimensions. This can be understood in terms of the inverse subthreshold slope, the parameter describing the voltage required to switch the transistor between on and off states. In a MOSFET device, the inverse subthreshold slope can be no smaller than 60 mV per decade of current at room temperature, and so the drive voltage cannot be reduced much below about  $0.5 \mathrm{~V}$  [4].

For this reason, Dennard scaling could not be maintained, and in the beginning of the 21st century, transistor scaling entered a power-constrained regime, meaning that the power density of about 100 Wcm<sup>-2</sup>, could not be further increased without placing unacceptable requirements on chip cooling and packaging [5]. As a result, CPU clock frequency has remained at around 4 GHz since 2006.

In addition to scaling, many other performance enhancing technologies have been implemented in silicon complementary metal-oxide-semiconductor (CMOS). For instance, high- $\kappa$  gate oxides, FinFET architecture and strained channels. The FinFET architecture, i.e. the use of a non-planar high-aspect ratio channel, allowed for, in part, reduced leakage currents at scaled gate length and, in part, increased drive current per chip area, due to the vertical elements of the channel [6]. Strained channels included the use of SiGe and improved the carrier mobility, meaning that the supply voltage could be reduced while still obtaining a sufficiently large drive current [7]. For a similar reason, i.e. due to their high carrier mobilities, III-V compound semiconductors were envisioned as a replacement for the silicon channel [8].

#### 1.3 III-V COMPOUND SEMICONDUCTORS

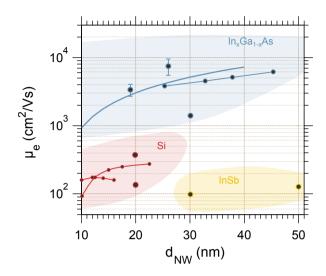

III-V electronics already constitute a multi-billion dollar industry, with a plethora of applications, such as lasers, LEDs, wireless networks, radar and smart phones, to name a few [9]. These applications make use of the favorable optical properties of III-V, as well as their high electron mobility in high-frequency applications [10]. Figure 1.2 shows experimental electron mobility versus nanowire diameter for various material systems, as reported in the literature. At scaled nanowire dimensions, an order of magnitude higher electron mobility is observed in indium gallium arsenide (InGaAs), as compared to silicon. For use in CMOS technology, however, III-V

Figure 1.2: Experimental values for the electron mobility versus nanowire diameter in non-planar channels reported in literature as well as in Paper IX. For non-symmetrical channel structures, an effective diameter, giving the same cross-sectional channel area, was used.

FETs must also meet a number of other performance marks to enable low enough power consumption in scaled technology nodes.

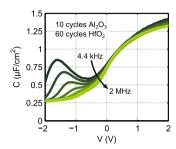

One of these performance marks is an inverse subthreshold slope of close to 60 mV per decade of current at room temperature. The gate oxide is a key component of the transistor to enable this. Silicon has a native oxide, silicon dioxide ( $SiO_2$ ), which forms an interface to the semiconductor relatively free of defects. This allows the gate potential to effectively modulate the potential of the channel, strongly improving the inverse subthreshold slope. On the other hand, III-Vs, and InGaAs in particular, form a variety of poor quality native oxides which are unsuitable for device operation [11]. However, since 2003, when aluminum oxide ( $Al_2O_3$ ) was discovered to be an excellent gate oxide on the InGaAs system, progress has been very strong, and state-of-the-art gate stacks now exhibit defect densities approaching those of silicon FETs [12,13].

Nevertheless, III-V FETs decisively outperforming industrial silicon FETs for CMOS applications have not been reported, in part due to the gate oxide problem, in part due to other key issues, such as the formation of low-resistance ohmic contacts, and establishing a proper scheme for the formation of a non-planar III-V channel [14].

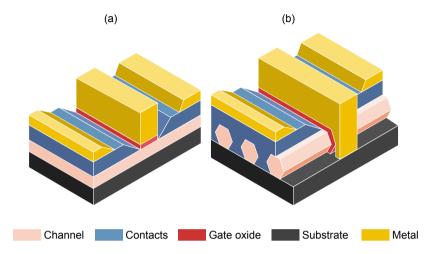

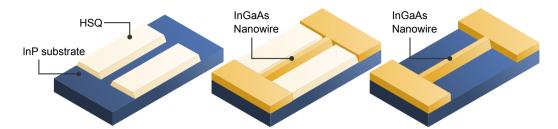

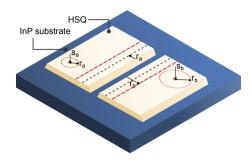

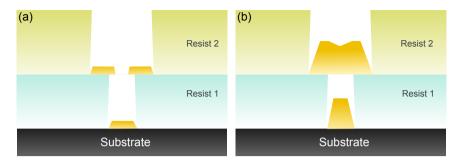

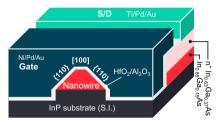

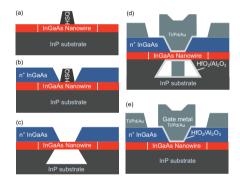

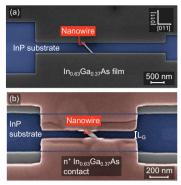

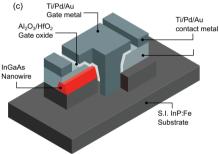

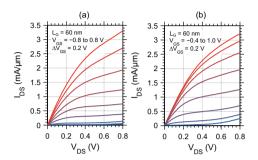

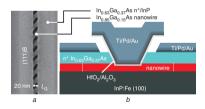

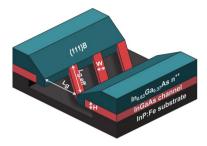

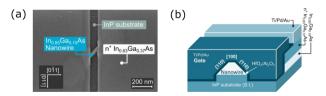

Figure 1.3: Schematic illustration of (a) planar and (b) non-planar device structures. Here, the non-planar device employs lateral nanowires as the channel, with an omega gate configuration.

#### 1.4 DIGITAL APPLICATIONS

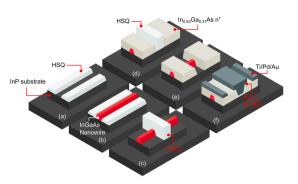

Digital transistor applications, or very-large-scale integration (VLSI) compatibility, requires highly scaled devices, with small footprints and low power consumption. The use of a non-planar channel, i.e. a channel architecture where gate covers the channel in three dimensions, allows for enhanced scalability (Figure 1.3). In contrast, a planar device has a channel which is 2-dimensional. The non-planar device, as compared to the planar device at similar dimensions, more strongly suppresses the influence of the source and drain fields on the channel potential [15]. This enables a lower subthreshold slope at a given gate length, or further scaled gate length while keeping the subthreshold slope constant.

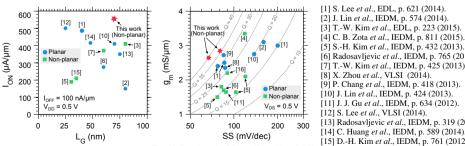

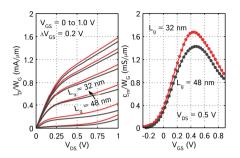

III-V MOSFETs for digital applications have recently been studied extensively. Different material choices, device architectures and channel geometries have been examined. Planar indium arsenide (InAs) FETs with a 2.5 nm thick channel layer and a gate length ( $L_G$ ) of 25 nm, were reported by Lee et~al., demonstrating a very high on-current of 500  $\mu$ A/ $\mu$ m (at  $V_{DD}=0.5$  V and  $I_{OFF}=100$  nA/ $\mu$ m) [16,17]. Lin et~al. also reported planar III-V FETs, using a 9 nm thick InGaAs/InAs channel, demonstrating a very high transconductance of 3.45 mS/ $\mu$ m [18]. Kim et~al. reported planar InAs FETs utilizing a Silicide-like nickel (Ni)-alloy self-aligned contact formation scheme [19].

Techniques for integration of III-V channels on silicon substrate include the use

of a metamorphic buffer layer, as reported by Huang et al. [20] and wafer bonding, as reported by Kim et al. [21] and Deshpande et al. [22].

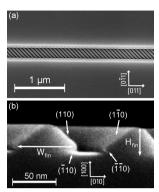

For non-planar geometries, Kim et~al. demonstrated InGaAs tri-gate FETs with channel width and height of 20 nm, exhibiting on-current of 410  $\mu$ A/ $\mu$ m (at  $V_{DD}=0.5V$  and  $I_{OFF}=100$  nA/ $\mu$ m). Radosavljevic et~al. also reported tri-gate InGaAs FETs, demonstrating good electrostatic control and relatively high-quality oxide interface [23,24]. Gu et~al. demonstrated gate-all-around InGaAs FETs with strong electrostatic control [25]. Waldron et~al. also demonstrated gate-all-around InGaAs devices fabricated on Si substrate with excellent performance [26]. In all these reports, the non-planar channels were formed by etching using a mask to define the channel. There are also reports of non-planar III-V FETs with channels not defined by etching, for instance by Schmid et~al. using templated-assisted selective epitaxy, allowing for integration on Si substrate as well as implementation of heterostructure systems [27, 28].

Vertical transistors are a class of non-planar transistors, which are characterized by that the carriers in the channel travel vertically from source to drain. State-of-the-art vertical transistors utilizing vapour-liquid-solid (VLS) catalyst-based growth to form the nanowire channel, have been reported by, for instance, Berg *et al.*, demonstrating InAs channel with excellent performance, as well as by Svensson *et al.*, demonstrating cointegration with gallium antimonide (GaSb) p-channel FETs and CMOS circuits [29, 30].

#### 1.5 HIGH-FREQUENCY APPLICATIONS

III-V materials have successfully been used in commercial high-frequency applications, for instance in high electron mobility transistors (HEMTs). These devices differ from MOSFETs by using a semiconductor gate barrier layer, rather than a gate oxide, as the gate insulator. The barrier layer, usually indium aluminum arsenide (InAlAs) or indium phosphide (InP), allows for a high-quality semiconductor-semiconductor interface at the channel surface, and avoids the issue of detrimental gate oxide interface defects [10]. HEMTs also typically use delta-doping, a thin highly doped layer which is placed just outside the channel. The delta-doping allows for increased carrier concentration in the channel, without degraded mobility due to ionized dopant scattering. These characteristics allow HEMTs to reach field-effect mobility values of 10 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and above [31].

In<sub>0.70</sub>Ga<sub>0.30</sub>As HEMTs with maximum oscillation frequency of above 1 THz, and cut-off frequency of approaching 700 GHz have been demonstrated [10, 32]. These

devices show a transconductance of  $1.75~\mathrm{mS/\mu m}$  at a gate length of 50 nm and barrier thickness of 4 nm. To further improve the transconductance, and thus the high-frequency performance, increasing the gate capacitance would be beneficial. However, due to their relatively small band gap, semiconductor gate barriers cannot be scaled much further without a significant increase of the gate leakage current. For this reason, MOSFETs, which allow for aggressive gate oxide scaling, may be useful in high-frequency applications.

III-V MOSFETs are relevant for two classes of high-frequency applications. The first class is as a replacement technology for HEMTs, that is in applications requiring low noise at high gain and frequency, for instance millimetre wave wireless communication. These kinds of devices will aim to minimize parasitic effects and maximize high-frequency performance at the cost of increased device dimensions and the use of expensive substrates such as InP.

The second class is as a replacement for silicon CMOS. Silicon CMOS has several drawbacks compared to III-V technologies in high-frequency applications, such as lower carrier mobility and smaller band gap (than e.g. InP and GaAs) [33]. However, key high-frequency figures of merits have improved substantially for silicon CMOS in the last decade, with the cut-off frequency approaching 400 GHz. Importantly, silicon CMOS allows for cointegration of high-frequency functionality with digital logic for on-chip performance tuning and signal processing. III-V MOSFETs aiming for these kinds of applications must demonstrate a highly scaleable device structure, preferably integrated on silicon substrates, as well as exhibit strong performance in logic-relevant metrics.

#### 1.6 MOTIVATION

This thesis aims to explore the potential of III-V MOSFETs both as replacements for silicon FETs in CMOS applications, and as amplifiers operating at high frequencies. This will be done through design and fabrication of InGaAs MOSFETs, as well as characterization of oxide and channel material quality through various means. In particular, selective area growth techniques will be used to form the nanowire channel used in these devices.

Chapter 2 concerns the theory of 1D ballistic FETs. This theory accurately describes the operation and properties of highly scaled FET for both digital and high-frequency applications. The I-V characteristics of such devices will be derived in detail, taking into account quasi-ballistic transport, multiple subbands, parasitic resistances, oxide scaling and the influence of oxide defects.

Chapter 3 describes MOSFETs suitable for high-frequency operation as well as high-frequency characterization of such devices, including small-signal modeling and performance metrics. Particular features of 1D quasi-ballistic devices will also be highlighted.

Chapter 4 covers the design and fabrication of InGaAs MOSFETs. This includes the selective area growth process, as well as characterization of the nanowires used as the channel in the devices of this work. Several schemes of contact formation are examined, including both regrown contacts and silicide-like processes. Various gate oxide choices are considered, as well as metallization options for both source, drain and gate. Finally, different schemes of T-gate formation are considered.

### **Transistor Theory**

#### 2.1 BENCHMARKING MOSFETS FOR DIGITAL APPLICATIONS

Digital applications, i.e. CMOS logic, impose strict requirements on device architecture and performance. A primary metric is the drive current delivered by the transistor in the on-state,  $I_{ON}$ . The on-state is defined as the bias point  $V_{DS} = V_{DD}$ ,  $V_{GS} = V_{OFF} + V_{DD}$ , where  $V_{OFF}$  is  $V_{GS}$  such that  $I_{DS} = I_{OFF}$ .  $I_{OFF}$  typically takes one of three values: 1, 10 or 100 nA/µm, corresponding respectively to low-power, general purpose and high performance applications, as defined by the international technology roadmap for semiconductors (ITRS). For III-V MOSFETs,  $V_{DD} = 0.5$  V is often intended.

A large  $I_{ON}$  is desireable in CMOS in order to reduce the propagation delay of the CMOS inverter, which is described as

$$t_p = \frac{C_L V_{DD}}{2I_{ON}} \tag{2.1}$$

where  $C_L$  is the load capacitance. A small propagation delay allows for logic operation at higher clock frequencies [3].

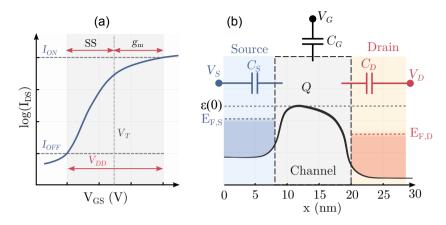

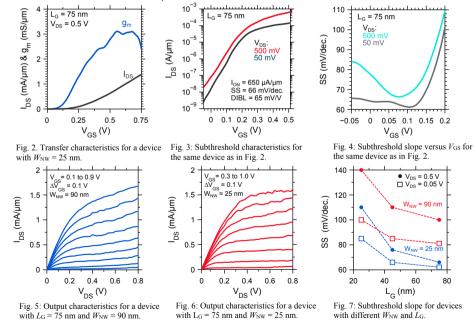

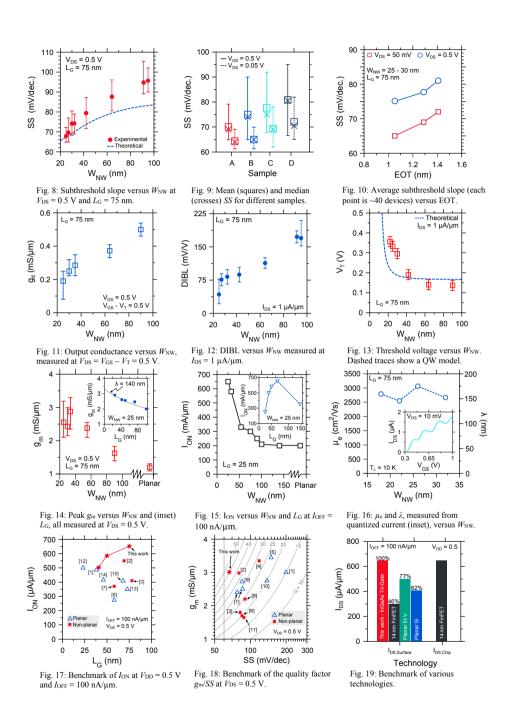

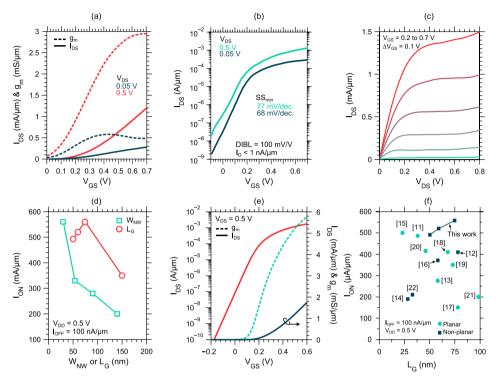

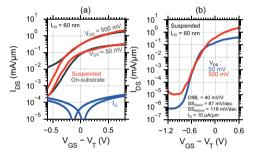

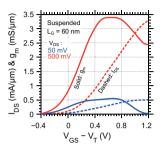

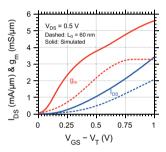

$I_{ON}$  is determined by the inverse subthreshold swing, SS, and the transconductance,  $g_m$ , as shown in Figure 2.1a. The SS is the  $V_{GS}$  change required for the change of one decade of current below threshold. Similarly,  $g_m$  is number of amperes delivered per volt of  $V_{GS}$  above threshold. Together they determine the required  $V_{GS}$  change for a full swing from  $I_{OFF}$  to  $I_{ON}$ .

A path to achieve small SS and large  $g_m$  is to implement a non-planar channel, such as a FinFET, Tri-gate FET or nanowire FET in a short- $L_G$  device structure. This kind of device will exhibit 1D transport characteristics if the channel is small enough, and operate in the quasi-ballistic regime, if  $L_G$  is short enough. Thus, an ideal MOSFET for digital applications can be described by the theory of ballistic 1D MOSFETs, developed by Lundstrom and others [34,35].

#### 2.2 THEORY OF BALLISTIC 1D MOSFETS

The I-V characteristics of a ballistic and quasi-balistic 1D MOSFET at  $T_L = 0$  K will now be derived [36]. A ballistic MOSFET can be understood as two electron

Figure 2.1: (a) A schematic figure of the subthreshold characteristics of a MOSFET. The drive bias  $V_{DD}$  determines the swing from on-state to off-state, thus  $I_{OFF}$  and  $I_{ON}$ . The subthreshold slope sets the current swing per voltage below the threshold voltage, while the transconductance does so above threshold. (b) Band diagram of conduction band of a MOSFET in the top of the barrier model. The transistor is here modeled as a system consisting of three capacitors modulating the channel charge Q.

reservoirs separated by an energy barrier. The Fermi level of one side, the source, is  $E_{F,S}$ , and the Fermi level of the other, the drain, is  $E_{F,D} = E_{F,S} - qV_{DS}$  under an applied bias,  $V_{DS}$ . Carriers from each side will be injected into the other, forming two oppositely directed currents,  $I^+$  and  $I^-$ . The total current is  $I_{DS} = I^+ - I^-$ .

$$I^{+} = \frac{2q^2}{h} \frac{\Psi}{q} \Theta(\Psi) \tag{2.2}$$

$$I^{-} = \frac{2q^2}{h} \frac{\Psi - qV_{DS}}{q} \Theta(\Psi - qV_{DS})$$

$$\tag{2.3}$$

where  $\Psi = E_F - \varepsilon(0)$ , the difference between the source Fermi energy and the energy at the top of the barrier. The bias-dependencies of  $I_{DS}$  can be determined from the top-of-the-barrier model, illustrated in Figure 2.1b.

In the top-of-the-barrier model, the transistor is modeled as a three-capacitor system with three terminals,  $V_G$ ,  $V_S$  and  $V_D$ .  $\varepsilon(0)$  is then determined from the solution of the Poisson equation representing this system, including a bias-induced charge, Q, corresponding to the mobile charge in the channel, at their common terminal.

$$-\varepsilon(0) = \frac{C_G}{C_{\Sigma}} q V_G + \frac{C_D}{C_{\Sigma}} q V_D + \frac{C_S}{C_{\Sigma}} q V_S - q \frac{Q}{C_{\Sigma}}$$

(2.4)

where  $Q = q(n_{1D} - n_0)$ ,  $n_{1D}$  is the total 1-D carrier density under bias, and  $n_0$  is the carrier density under zero bias.  $C_{\Sigma}$  is a parallel coupling of the capacitors,  $C_S + C_D + C_G$ .  $n_{1D}$  is understood as the total directed moments in both directions,  $n^+ + n^-$ , at the top of barrier energy. From a ballistic transport model, they are evaluated as [36]

$$n^{+} = \frac{\sqrt{2m^{*}\Psi}}{\pi\hbar}\Theta(\Psi) \tag{2.5}$$

$$n^{-} = \frac{\sqrt{2m^{*}(\Psi - qV_{DS})}}{\pi\hbar}\Theta(\Psi - qV_{DS})$$

(2.6)

The  $V_{GS}$  and  $V_{DS}$  dependence of  $I_{DS}$  can be determined by solving equations (2.4), (2.5) and (2.6) self-consistently, but simple equations can be obtained for  $I_{DS}$  by observing three regions of operation.

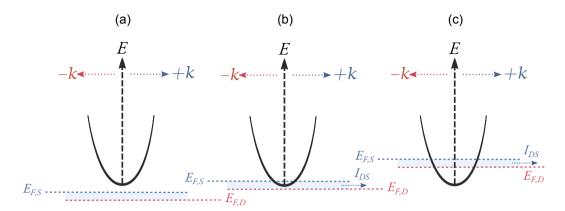

Region 1:  $\varepsilon(0) > E_{F,S}$ , as shown in Figure 2.2a. There are no states in the channel below  $E_{F,S}$ , thus both  $I_{DS}$  and  $n_{1D} = 0$ . If we assume perfect electrostatic gate control,  $C_S/C_\Sigma = 0$ ,  $C_D/C_\Sigma = 0$  and  $C_G/C_\Sigma = 1$ , then (2.4) simplifies to

$$\varepsilon(0) = -qV_{GS} \tag{2.7}$$

A current will begin to flow when  $E_{F,S}$  lines up with  $\varepsilon(0)$ , thus we may define the threshold voltage as  $V_T \equiv V_{GS} = E_{F,S}/q$ .

Region 2:  $E_{F,D} < \varepsilon(0) < E_{F,S}$ , as shown in Figure 2.2b. Here, the bottom of the barrier is below  $E_{F,S}$ , but above  $E_{F,D}$ . The channel states are therefore occupied only by carriers travelling in the positive direction,  $I^- = 0$  and  $n^- = 0$ , while  $I^+$  and  $n^+$  follow equations (2.2) and (2.5), respectively, with the step function  $\Theta(\Psi) = 1$ .  $I_{DS}$  is obtained from equations (2.2), (2.4) and (2.5) as

$$I_{DS} = \frac{2q}{h} \left[ -\frac{\sqrt{2m^*q^2}}{hC_{OX}} + \sqrt{\frac{2m^*q^4}{h^2C_{OX}^2} + q(V_{GS} - V_T)} \right]^2$$

(2.8)

$I_{DS}$  is therefore independent of  $V_{DS}$  in this region. This is also clear from the band structure. There are no occupied states below  $E_{F,D}$ , therefore, as  $V_{DS}$  is increased, the number of occupied states in the channel remains constant. Similarly, the  $V_{GS}$ -dependence is understood qualitatively as follows: As  $V_{GS}$  increases, the number of positive states below  $E_{FS}$  increases, thus  $I_{DS}$  increases.

Region 3:  $\varepsilon(0) < E_{F,D}$ , as shown in Figure 2.2c. Here, the bottom of the barrier is below both  $E_{F,S}$  and  $E_{F,D}$ .

$$I_{DS} = I^{+} - I^{-} = \frac{2q^{2}}{h} \frac{\Psi}{q} - \frac{2q^{2}}{h} \frac{\Psi - qV_{DS}}{q} = \frac{2q^{2}}{h} V_{DS}$$

(2.9)

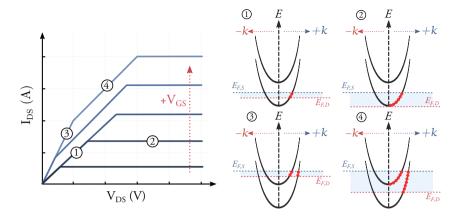

Figure 2.2: Schematic illustration of the conduction band edge in a 1D channel, i.e. the energy of lowest quantized subband, indicating three regions of behavior of the current versus the applied biases. (a) In region 1, the drain current is zero. (b) In region 2, the current is dependent on  $V_{GS}$ , but independent of  $V_{DS}$ . (c) In region 3, the current is dependent on  $V_{DS}$ , but independent of  $V_{GS}$ .

Thus,  $I_{DS}$  becomes independent of  $V_{GS}$ . This simply follows from that lowering  $\varepsilon(0)$  does not change the number of carriers in the channel, while lowering  $E_{F,D}$  lowers  $I^-$ , therefore increases  $I_{DS}$ . From the band diagram, it is also clear that as  $V_{DS}$  is increased, the system will eventually re-enter region 2 by satisfying its condition  $E_{F,D} < \varepsilon(0) < E_{F,S}$ . This will happen when  $\varepsilon(0) = E_{F,D} = E_{F,S} - qV_{DS,sat}$ .  $V_{DS,sat}$  is the saturation voltage, the value of  $V_{DS}$  which constitutes the boundary between region 2 and region 3. If  $V_{DS} < V_{DS,sat}$ , then equation (2.8) is true and  $I_{DS}$  is independent of  $V_{DS}$ . If  $V_{DS} > V_{DS,sat}$ , then equation (2.9) is true and  $I_{DS}$  is independent of  $V_{GS}$ .

The band diagram also shows that  $V_{DS,sat}$  must depend on  $V_{GS}$ . The exact expression for  $V_{DS,sat}$  when  $V_{DS} > V_{DS,sat}$  can be obtained by

$$qV_{DS,sat} = E_{F,S} - \varepsilon(0) = \left[ -\frac{\sqrt{2m^*q^2}}{hC_{OX}} + \sqrt{\frac{2m^*q^4}{h^2C_{OX}^2} + q(V_{GS} - V_T)} \right]^2$$

(2.10)

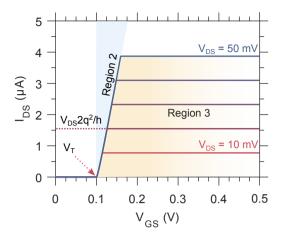

Figure Figure 2.3 shows a calculation of  $I_{DS}$  using equations (2.8) and (2.9), with  $m^* = 0.04$  and  $C_{OX} = 1.3 \cdot 10^{-9}$  F/m, with  $V_{DS} = 10$  to 50 mV. According to equation (2.9), the saturation current is  $V_{DS}2q^2/h$ , and therefore the conductance  $I_{DS}/V_{DS}$  is constant at a value of  $2q^2/h$ , which is called the quantum conductance.

Figure 2.3: Ideal transfer characteristics of a 1D ballistic MOSFET with a single occupied subband, at different values of  $V_{DS}$ . Regions 2 and 3, correlating with those in Figure 2.2, are indicated. Region 1 is below  $V_T$  but is not indicated.

#### 2.2.1 BALLISTIC TRANSCONDUCTANCE

The transconductance  $g_m = dI_{DS}/dV_{GS}$  is zero in regions 1 and 3. In region 2, it is obtained by derivating equation (2.8). Equation (2.8) can be simplified by identifying the quantum capacitance

$$C_Q = -q^2 \frac{\partial n_{1D}}{\partial \varepsilon(0)} = \frac{\sqrt{2m^* q^2 / \pi \hbar}}{-(\sqrt{2m^* q^2 / h C_{OX}}) + \sqrt{(2m^* q^4 / h^2 C_{OX}^2) + q(V_{GS} - V_T)}}$$

(2.11)

which gives

$$I_{DS} = \frac{2q^2}{h} \frac{C_{OX}}{C_{OX} + C_O} (V_{GS} - V_T)$$

(2.12)

$g_m$  can now be examined in the quantum capacitance limit (QCL),  $C_{OX} \gg C_Q$ ,

$$g_m = \frac{2q^2}{h} \tag{2.13}$$

and in the classical limit  $(C_{OX} \ll C_Q)$

$$g_m = \frac{h}{2m^*q} C_{OX}^2 (V_{GS} - V_T) \tag{2.14}$$

As seen in (2.14), in the classical limit,  $g_m$  has a dependence on the effective mass. In MOSFETs operating in the drift-diffusion regime,  $g_m$  is indirectly dependent on the effective mass, through the mobility, which is typically higher for lower effective mass. In a fully ballistic device, the dependence instead comes from the density of states. However, truly ballistic transistors are not currently achievable. It is therefore useful to model quasi-ballistic devices, i.e. devices with small amounts of scattering in the channel [37, 38].

#### 2.2.2 QUASI-BALLISTIC DEVICES

Consider again equation (2.9), where  $I_{DS}$  is described by a forward, and a backward current as [39]

$$I_{DS} = I^{+} - I^{-} \tag{2.15}$$

Assume now that  $I^+ = I_B^+$  is the ballistic forward current, and that a portion T of  $I^-$  scatters in the opposite direction.  $I^-$  is then constituted by a component from the scattered ballistic forward current,  $(1-T)I_B^+$ , and a component from the non-scattered ballistic backward current,  $TI_B^-$

$$I^{-} = TI_{B}^{-} + (1 - T)I_{B}^{+} \tag{2.16}$$

Inserting equation (2.16) into equation (2.15) gives

$$I_{DS} = T(I_B^+ - I_B^-) = TI_B (2.17)$$

When scattering is present in the channel, the ballistic current  $I_B$  is thus reduced by a factor T, called the transmission.

To determine an expression for T, consider a channel with the length L (corresponding to the gate length of a quasi-ballistic device), and the current fluxes  $J_{DS}(x) = J^+(x) - J^-(x)$ . It is clear that the forward flux at x = L is reduced by scattering by a factor T compared to the forward flux at x = 0 and that  $J^-(L) = 0$

$$J_{DS}(L) = J^{+}(L) = TJ^{+}(0)$$

(2.18)

The probability of a scattering event at an arbitrary distance x into the channel is  $x/\lambda$ , where  $\lambda$  is the mean free path, the average distance traveled between scattering events. Therefore, the forward flux at x is the difference between the forward flux at x = 0 and the portion of scattered total flux at x

$$J(x)^{+} = J^{+}(0) - J_{DS}(x)\frac{x}{\lambda}$$

(2.19)

Inserting equation (2.19) into equation (2.18) gives

$$T = \frac{J^{+}(L)}{J^{+}(0)} = \frac{1}{1 + L/\lambda} = \frac{\lambda}{\lambda + L}$$

(2.20)

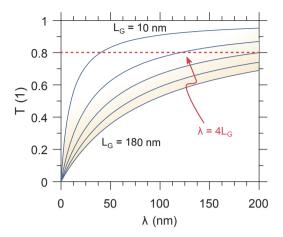

Figure 2.4: The transmission coefficient versus the mean free path at different gate lengths. The required mean free path to obtain 0.8 transmission follows the simple relationship  $\lambda = 4L_G$  and is indicated.

The current in a quasi-ballistic device then becomes

$$I_{DS} = \frac{\lambda}{\lambda + L_G} \frac{2q^2}{h} \frac{C_{OX}}{C_{OX} + C_O} (V_{GS} - V_T)$$

(2.21)

Figure 2.4 shows T versus  $\lambda$  for  $L_G=10$  to 180 nm. A transmission of 0.8 may be a reasonable target for high-performance III-V MOSFETs, this gives the simple formula

$$\lambda_{T=0.8} = 4L_G \tag{2.22}$$

An expression for  $\lambda$  in terms of material parameters can be obtained for nondegenerate conditions by considering Fick's law of diffusion

$$J_{DS} = -D\frac{dn}{dx} = -\frac{\lambda v_T}{2} \tag{2.23}$$

where  $v_T$  is the thermal velocity and D is the diffusion constant, which relates to the electron mobility  $\mu$  through the Einstein relation

$$D = \frac{k_B T_L \mu}{q} = \frac{\lambda v_T}{2} \tag{2.24}$$

where  $T_L$  is the lattice temperature. Thus, high mobility correlates with long mean free path.

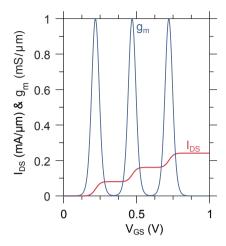

Figure 2.5: Simulated transfer characteristics of a device with three equidistant subbands.

#### 2.2.3 MULTIPLE SUB-BANDS

With M number of sub-bands below  $E_{F,S}$ , the total current in region 3 becomes [36]

$$I_{DS} = \sum_{n=1}^{M} I_{DS,n} = MT \frac{2q^2}{h} V_{DS}$$

(2.25)

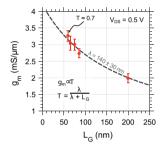

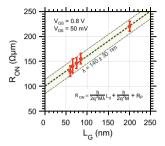

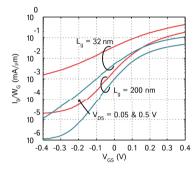

The transfer and output characteristics of a device with multiple subbands are shown in Figure 2.5 and Figure 2.6, respectively. The linear region exhibits multiple slopes, or values of  $R_{ON}$  according to  $MT\frac{2q^2}{h}$ , where M now indicates the number of subbands below  $E_{F,D}$ , which depends on both  $V_{GS}$  and  $V_{DS}$ . At high  $V_{GS}$  and low  $V_{DS}$ , a minimum value of  $R_{ON}$  is obtained, the ballistic on-resistance 12.9 k $\Omega/M$ . The measured  $R_{ON}$  of a quasi-ballistic device, with access resistance  $R_{DS}$  can then be described as

$$R_{ON} = \frac{h}{2q^2MT} + R_{DS} = \frac{h}{2q^2M} \left(1 + \frac{L_G}{\lambda}\right) + R_{DS} = L_G \frac{h\lambda}{2q^2M} + \frac{h}{2q^2M} + R_{DS} \quad (2.26)$$

M can be determined from the linear function  $R_{ON}(L_G)$ , by estimating and subtracting  $R_{DS}$  from the y-axis intercept. With knowledge of M,  $\lambda$  can subsequently be calculated from the slope.

A first order approximation of the energy separation E between sub-bands is

provided by a simple symmetric quantum well model

$$E = \frac{k^2 \hbar^2}{2m^*} \tag{2.27}$$

where k is the wave vector. Clearly, a small  $m^*$  results in a large energy separation.

#### 2.2.4 NON-PARABOLICITY

The effective mass approximation used here is valid only for low energies. At high energies, the dispersion relationship is no longer parabolic, but approaches a material-dependent linear slope. Using  $k \cdot p$  theory, this can be modeled as [40,41]

$$E(1 + \alpha E) = \frac{k^2 \hbar^2}{2m^*} \tag{2.28}$$

where  $\alpha$  determines the degree of non-parabolicity and can be approximated as [41]

$$\alpha \approx \frac{1}{E_G} (1 - \frac{m^*}{m_0})^2$$

(2.29)

Thus, the effective mass in a non-parabolic model increases at higher energies.

#### 2.2.5 THE DENSITY OF STATES BOTTLENECK

In a 2D, i.e. quantum well FET, the current is

$$I_{DS,2D} \propto \left(\frac{C_{OX}}{C_{OX} + C_Q}\right)^{3/2} \sqrt{m^*}$$

(2.30)

where the 2D quantum capacitance is

$$C_Q = \frac{q^2 m^*}{\pi \hbar^2} \tag{2.31}$$

The optimization of  $I_{DS,2D}$  with respect to  $m^*$  gives an optimum at  $C_Q = 2C_{OX}$ , which means that a lower  $m^*$  is beneficiary only up to a certain degree. For large  $m^*$ ,  $I_{DS,2D}$  is limited by low carrier velocity, while for small  $m^*$  it is limited by a low density of states (DOS). This effect is called the DOS bottleneck [42].

For a 1D channel, the optimization of  $I_{DS}$  with respect to  $m^*$ , i.e. using equations (2.11) and (2.21), implies no limit to the increase of  $I_{DS}$  with the reduction of  $m^*$ . Nevertheless, a DOS bottleneck-like effect is present in the fact that  $E \propto 1/m^*$  as shown in equation (2.27). Essentially, at a fixed  $V_{GS}$ , a reduction of  $m^*$  will reduce

Figure 2.6: Ideal output characteristics of a 1D ballistic MOSFET with up to two occupied subband, at different values of  $V_{GS}$ . The numbers and the corresponding schematic figures indicate the band alignment at the various biasing conditions. The red dots in the band diagram denote k-states that contribute to the drain current.

the number of sub-bands below  $E_{F,S}$  and thus the current according to equation (2.25). These considerations are valid for nanowires with radii of approximately above 10 nm, in which M > 1 under normal bias conditions. When M = 1, E does not influence  $I_{DS}$ , and so this effect is not present.

#### 2.2.6 INTERFACE TRAPS

The influence of charging of interface traps on the electrostatics of the device can be modeled by including the trapped charges  $n_{trap}$  in the total total bias-induced charge Q in equation (2.4)

$$-\delta\varepsilon(0) = q\delta V_G - q^2 \frac{n_{1D} - n_0 + \delta n_{trap}}{C_{OX}}$$

(2.32)

The trapped charges are described as  $\delta n_{trap} = D_{it} \delta \varepsilon(0)$ , where  $D_{it}$  is the density of interface traps.

$$-\delta\varepsilon(0) = q\delta V_G - q^2 \frac{n_{1D} - n_0}{C_{OX}} - \frac{q}{C_{OX}} D_{it} \delta\varepsilon(0)$$

(2.33)

Calculating the current as before, now gives

$$I_{DS} = T \frac{2q^2}{h} \frac{C_{OX}}{C_{OX} + C_O + q^2 D_{it}} (V_{GS} - V_T)$$

(2.34)

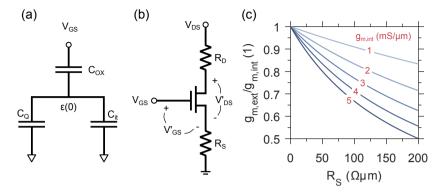

Figure 2.7: (a) A capacitative model of the channel in a MOSFET, assuming ideal electrostatics. The quantum capacitance, and the capacitance due to interface charge have a similar detrimental effect on device performance. (b) Circuit of a MOSFET including extrinsic resistance, source and drain access resistance. (c) Calculated degradation of the transconductance at increasing values of source resistance for different values of intrinsic transconductance. This effect is most severe in devices with large intrinsic transconductance.

The influence of trap charging can thus be described through the addition of a capacitor  $C_{it}$  in parallel with  $C_Q$  according to Figure 2.7(a), which degrades  $I_{DS}$ .

#### 2.3 DEVICE CHARACTERISTICS

#### 2.3.1 EXTRINSIC TRANSCONDUCTANCE

So far, the intrinsic transconductance  $g_m$ , or  $g_{m,int}$  has been derived, which does not include the effects of parasitic source and drain resistances,  $R_{DS} = R_D + R_S$ . The measured transconductance is the extrinsic transconductance,  $g_{m,ext}$ . The relationship between  $g_{m,ext}$  and  $g_{m,int}$ , assuming symetric resistances  $R_D = R_S$ , was derived by Chou et al. as follows [43]. Define  $g_{m,int}$  and the intrinsic output conductance  $g_{d,int}$  as

$$g_{m,int} = \frac{\delta I_{DS}}{\delta V_{GS}'} \tag{2.35}$$

$$g_{d,int} = \frac{\delta I_{DS}}{\delta V_{DS}'} \tag{2.36}$$

According to Figure 2.7(b), a change in the drain current can then be described as

$$\delta I_{DS} = g_{m.int} \delta V_{GS}' + g_{d.int} \delta V_{DS}' \tag{2.37}$$

with

$$V'_{DS} = V_{DS} - (R_D + R_S)I_{DS} = V_{DS} - R_{DS}I_{DS}$$

(2.38)

$$V'_{GS} = V_{GS} - R_S I_{DS} (2.39)$$

Transconductance is measured at constant  $V_{DS}$ , i.e.  $\delta V_{DS} = 0$ . The differentials of the intrinsic voltages are then

$$\delta V_{DS}' = -R_{DS}\delta I_{DS} \tag{2.40}$$

$$\delta V_{GS}' = \delta V_{GS} - R_S \delta I_{DS} \tag{2.41}$$

Combining (2.37) with (2.40) and (2.41) gives

$$\delta I_{DS} = g_{m,int}(\delta V_{GS} - R_S \delta I_{DS}) - g_{d,int} R_{DS} \delta I_{DS}$$

(2.42)

Solving (2.42) for  $g_{m,int}$  and using  $g_{m,ext} = \delta I_{DS}/\delta V_{GS}$  gives

$$g_{m,int} = \frac{\delta I_{DS}(1 + g_{d,int}R_{DS})}{\delta V_{GS} - R_S \delta I_{DS}} = \frac{g_{m,ext}(1 + g_{d,int}R_{DS})}{1 - R_S g_{m,ext}}$$

(2.43)

This means that a large output conductance will cause a drop in the measured transconductance, which is a well-known short-channel effect. For a long-channel device, with  $g_d \ll g_m$ , (2.43) simplifies to

$$g_{m,int} = \frac{g_{m,ext}}{1 - R_S g_{m,ext}} \Leftrightarrow g_{m,ext} = \frac{g_{m,int}}{1 + R_S g_{m,int}}$$

(2.44)

Figure 2.7(c), shows the reduction of  $g_{m,ext}$  as a function of  $R_S$  and  $g_{m,int}$ . High  $g_{m,int}$  devices are more severely degraded by access resistance, but e.g. at  $R_S = 50 \ \Omega \, \mu m$  and  $g_{m,int} = 3 \ mS/\mu m$ , similar to the values reported in this work, the degradation is only about 10%.

#### 2.3.2 OXIDE CAPACITANCE

As shown in equation (2.34), increasing the oxide capacitance by gate oxide scaling offers an improvement of  $I_{DS}$  and  $g_m$ , but the gain is limited by the quantum capacitance [44]. In a 1D gate-all-around (GAA) cylindrical geometry, the oxide capacitance is calculated from

$$C_{OX} = \frac{2\pi\epsilon_r\epsilon_0}{\ln(\frac{t_{OX} + r}{r})} \tag{2.45}$$

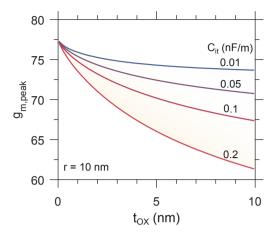

Figure 2.8: Peak transconductance versus gate oxide thickness in gate-all-around geometry and with nanowire radius of 10 nm, at different levels of interface trap-induced capacitance. It is clear that gate oxide scaling effectively counteracts the detrimental effects of interface traps, but for already low interface trap densities, oxide scaling provides only a minor enhancement of transconductance.

where  $t_{OX}$  is the gate oxide thickness, and r is the radius of the 1D channel. Figure 2.8 shows peak  $g_m$  versus  $t_{ox}$  at different values of  $C_{it}$ . At low values of  $C_{it}$ ,  $t_{OX}$  scaling offers minimal improvement to  $g_m$ . As shown, with regards to  $g_m$ ,  $t_{ox}$  scaling is primarily a means to compensate for the effects of interface traps.

In a rectangular gate-all-around geometry, the oxide capacitance instead is approximated as [45]

$$C_{OX} \approx \frac{2\epsilon_r \epsilon_0 (W + H)}{t_{OX}} + 2.232\epsilon_r \epsilon_0$$

(2.46)

where W and H are the width and height of the channel, respectively, and the condition  $t_{OX} \ll W, H$  is true. Similarly, if the rectangular channel is gated on three sides (tri-gate), the oxide capacitance can be approximated as

$$C_{OX} \approx \frac{\epsilon_r \epsilon_0 (W + 2H)}{t_{OX}} + 1.116 \epsilon_r \epsilon_0$$

(2.47)

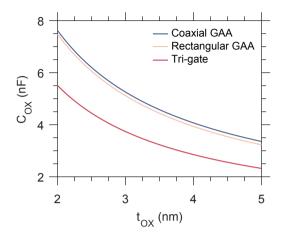

Figure 2.9 shows a comparison of the oxide capacitance for the three geometries, calculated using channel dimensions with the same circumference, and  $\epsilon_r = 20$ . In the gate-all-around geometry, cylindrical and rectangular channels have approximately equivalent oxide capacitance.

Figure 2.9: Oxide capacitance for three different geometries: Cylindrical gate-all-around, rectangular gate-all-around and tri-gate. Here, 20 nm is used for the rectangular channels, and a radius of 12.7 nm is used for the cylindrical, which give the same channel circumference for all three cases, and the same gated circumference for the first two cases.

#### 2.3.3 NATURAL LENGTH SCALE

As  $L_G$  is scaled down in order to increase the transmission  $T = \frac{\lambda}{\lambda + L_G}$  and reduce the size of the transistor, the oxide thickness and channel dimensions must also be reduced in order to avoid short channel effects [40, 46–48]. In particular, short-channel effects are caused by the source/drain potential influencing the channel potential. The length at which the source/drain influences the channel is described in terms of the natural length scale of the transistor,  $\lambda_n$  [48]. To avoid degradation of the subthreshold slope, the DIBL, as well as the transconductance through increased output conductance,

$$L_G \ge 5\lambda_n \tag{2.48}$$

should be maintained [46].

For gate-all-around cylindrical geometry and assuming extremely scaled nanowires,  $t_{OX} \gg r$ ,  $\lambda_n$ , can be approximated as

$$\lambda_n \approx \pi \frac{t_{OX} + r}{2.4} \tag{2.49}$$

For an ultra-thin-body planar FET with the channel thickness  $t_c$ , this expression instead becomes [48]

$$\lambda_n \approx \pi (t_{OX} + \frac{\epsilon_r}{\epsilon_c} t_c) \tag{2.50}$$

where  $\epsilon_c$  is the relative permeability of the channel material. Using the condition in equation (2.48), the required dimensions become  $L_G \geq 6.5(t_{OX} + r)$  and  $L_G \geq 16(t_{OX} + t_c)$  (assuming  $\epsilon_r \approx \epsilon_c$ ), for gate-all-around and planar geometry, respectively [40]. Gate-all-around geometry therefore allows approximately 2.5 times thicker oxide and channel thickness, as compared to planar geometry, at a fixed  $L_G$ . Any other non-planar geometry, such as FinFETs and Tri-gates, will have a natural length scale in between those described by equations (2.50) and (2.49). This is the primary motivation for the use of non-planar geometries.

### **RF-Transistors**

The response of transistors under an AC input bias is examined here. First, S-parameter measurements are described, followed by small-signal modeling of the devices presented in this work. Finally, key high-frequency performance metrics are analyzed.

#### 3.1 HIGH-FREQUENCY CHARACTERIZATION

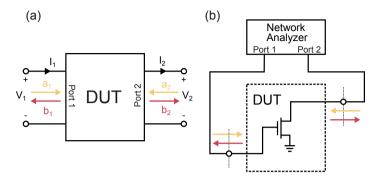

High frequency properties regard the response of the current through a device under test (DUT) to an input AC signal. The circuit that describes the electrical response of the DUT is called the small-signal model. The components of the small-signal model are determined by measurements of the matrix of the transfer function S for electromagnetic power waves, called the scattering parameters. As the MOSFET has two ports, i.e. where  $V_{\rm GS}$  and  $V_{\rm DS}$  are applied, the transfer function becomes

$$\begin{bmatrix}

b_1 \\

b_2

\end{bmatrix} = \begin{bmatrix}

S_{11} & S_{12} \\

S_{21} & S_{22}

\end{bmatrix} \begin{bmatrix}

a_1 \\

a_2

\end{bmatrix}$$

(3.1)

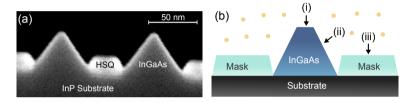

where  $a_1$  and  $a_2$  are incident power waves at port one and two. Similarly,  $b_1$  and  $b_2$  are reflected power waves. Figure 3.1a shows a schematic figure of the S-parameter measurement, and Figure 3.1b shows the measurement setup. The related transfer function Y, the admittance matrix, describing  $I \to V$  can be analytically derived from S, and from it, the elements of the small-signal model can be derived.

The S-parameters, rather than the Y-parameters, are measured because when measuring AC signals, a termination for the signal at the measurement station must be supplied in order to suppress reflection back to the DUT. For Y-parameters, the ports carry electrical current in and out of the DUT. For current signals, short-circuit and open-circuit terminations are necessary, but these are difficult to provide in a high-frequency setting. For S-parameters, termination by impedance matching is sufficient, and this is supplied by the 50  $\Omega$  impedance of the measurement system, following calibration, as seen from the DUT.

Figure 3.1: (a) Schematic figure of a two-port S-parameter measurement, with the incoming and reflected power waves a and b, respectively, as well as the associated currents and voltages of the system. (b) The S-parameter measurement setup, using a network analyzer.

#### 3.2 THE SMALL-SIGNAL MODEL

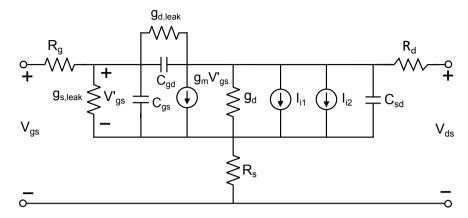

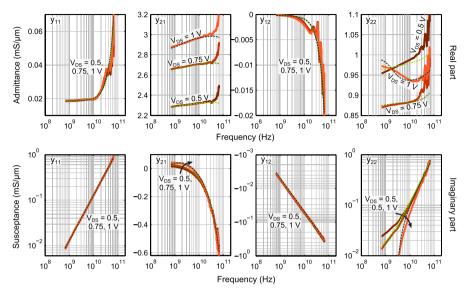

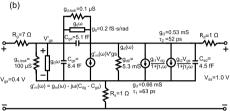

The small-signal model is a circuit representing the small-signal, i.e. the RF-signal, response of the DUT. It aims to capture the gain provided by the transistor at arbitrary frequencies. A hybrid- $\pi$  small signal model is typically used to model MOSFETs (Figure 3.2). The measured Y-parameter response of the transistor can be described in terms of the elements of the small-signal model [49]:

$$Y_{11} = \frac{I_1}{V_1} \Big|_{V_2 = 0} = \frac{\omega^2 (C_{gs} + C_{gd})^2 R_g + j\omega (C_{gs} + C_{gd})}{1 + \omega^2 (C_{gs} + C_{gd})^2 R_g^2}$$

(3.2)

$$Y_{12} = \frac{I_1}{V_2}\Big|_{V_1 = 0} = \frac{-\omega^2 C_{gd}(C_{gs} + C_{gd})R_g - j\omega C_{gd}}{1 + \omega^2 (C_{gs} + C_{gd})^2 R_g^2}$$

(3.3)

$$Y_{21} = \frac{I_2}{V_1} \Big|_{V_2 = 0} = \frac{g_m - j\omega g_m R_g (C_{gs} + C_{gd})}{1 + \omega^2 (C_{gs} + C_{gd})^2 R_q^2}$$

(3.4)

$$Y_{22} = \frac{I_2}{V_2} \Big|_{V_1 = 0} = g_{ds} + j\omega C_{sd} + j\omega C_{gd} + \frac{\omega^2 g_m R_g^2 C_{gd} (C_{gs} + C_{gd}) + j\omega g_m R_g C_{gd}}{1 + \omega^2 (C_{gs} + C_{gd})^2 R_g^2}$$

(3.5)

Here,  $C_{dg}$ ,  $R_D$ ,  $R_S = 0$  is assumed. The elements of the hybrid- $\pi$  small signal model are determined from the measured S-parameters, transformed to Y-parameters, by first setting  $R_S = R_D = 0$ . To do this,  $R_S$  and  $R_D$  are first estimated,

then subtracted from the measured impedence parameters Z [49]. The small-signal model elements are then calculated as follows [50]:

$$g_m = \text{Re}[Y_{21}]|_{\omega^2 = 0}$$

(3.6)

$$g_d = \text{Re}[Y_{22}]|_{\omega^2 = 0}$$

(3.7)

$$R_g = \frac{\text{Re}[Y_{21}]}{(\text{Im}(Y_{11}))^2} \tag{3.8}$$

$$C_{gd} = \frac{-\text{Im}[Y_{12}]}{\omega} \tag{3.9}$$

$$C_{dg} = \frac{-\text{Im}[Y_{21}]}{\omega} - g_m R_g (C_{gs} + C_{gd})$$

(3.10)

$$C_{gs} = \frac{\text{Im}[Y_{11}] + \text{Im}[Y_{12}]}{\omega} \tag{3.11}$$

$$C_{sd} = \frac{\text{Im}[Y_{22}]}{\omega} - C_{gd} - g_m R_g C_{gd} + \omega^2 C_{gd} C_{dg} (C_{gd} + C_{gs}) R_g^2$$

(3.12)

Subsequently, the modeled Y-parameters are determined from above equations. Finally,  $R_S$  and  $R_D$  are added to the modeled Z-parameters, which now give the response of the DUT at arbitrary frequencies. This allows predicting high-frequency metrics such as the cut-off frequency  $f_t$  and the maximum oscillation frequency  $f_{max}$  while measuring response at relatively low frequencies, e.g. up to 67 GHz.

Impact ionization becomes important at high  $V_{DS}$ . This effect is modeled by the inclusion of the two current sources  $I_{i1}$  and  $I_{i2}$ , that reflect the voltage dependencies of the impact ionization generation rate [51]

$$I_{i1} = \frac{g_{i1}V_{dg}}{1 + i\tau_1\omega} \tag{3.13}$$

$$I_{i2} = \frac{g_{i2}V'_{gs}}{1 + j\tau_2\omega} \tag{3.14}$$

$I_{i1}$  describes carrier generation from a strong drain electric field, i.e. the dependence on the carrier energy.  $I_{i2}$  describes the dependence on the number of carriers, i.e. the drain current. Impact ionization occurrs during a finite time, and therefore exhibits a frequency-dependence. In particular, at high frequencies, impact ionization is unable to follow the signal, and is therefore suppressed.  $j\tau\omega$  in the above expressions captures this effect, with  $\tau$  being an associated time constant.

**Figure 3.2:** A small-signal model accurately describing the frequency response of devices measured and characterized in this work.

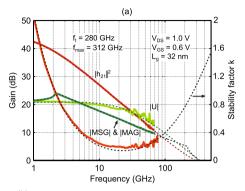

#### 3.3 HIGH-FREQUENCY PERFORMANCE

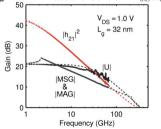

The cut-off, or transition, frequency  $f_T$  is a common figure of merit for high-frequency transistors.  $f_T$  is the frequency at which the transistor delivers unity current gain. The current gain is described in terms of the h-parameter  $h_{21}$

$$h_{21} = \frac{i_2}{i_1}|_{V_1 = 0} = \frac{Y_{21}}{Y_{11}} \tag{3.15}$$

$f_T$  is then obtained either from extrapolating  $|h_{21}|^2$  linearly at high frequencies with a slope of -20 dB/decade, or from a small-signal model with a good fit to the measured S-parameters. Assuming  $R_S = R_D = 0$   $\Omega$ ,  $h_{21}$  in terms of the small-signal elements is

$$|h_{21}| = \frac{\sqrt{g_m^2 - \omega^2 C_{gd}^2}}{\omega (C_{gs} + C_{gd})}$$

(3.16)

which for  $\omega \gg g_m/C_{gd}$  simplifies to

$$|h_{21}| \approx \frac{g_m}{\omega(C_{gs} + C_{qd})} \tag{3.17}$$

and gives  $f_T$  at unity

$$\omega_T = 2\pi f_T \approx \frac{g_m}{C_{qs} + C_{qd}} \Leftrightarrow f_T \approx \frac{g_m}{2\pi (C_{qs} + C_{qd})}$$

(3.18)

In a traditional transistor, i.e. one operating in the drift-diffusion regime, with minimal parasitic gate capacitance operating in the classical limit,  $C_{gs} + C_{gd} \approx \frac{2}{3}WL_GC_{OX}$ , equation (3.18) simplifies to

$$f_T \approx \frac{g_m}{2\pi (C_{gs} + C_{gd})} = \frac{\mu C_{OX} \frac{W}{L_G} (V_{GS} - V_T)}{2\pi \frac{2}{3} L_G W C_{OX}} = \frac{3\mu (V_{GS} - V_T)}{4\pi L_G^2}$$

(3.19)

where  $\mu$  is the carrier mobility and W the channel width. While  $C_{OX}$  increases  $g_m$ , it also adds a delay due to charging of the capacitance, and so the overall  $C_{OX}$  dependence cancels out. The quadratic dependence on  $L_G$  is due to a simultaneous increase of  $g_m$  and reduction of  $C_{OX}$ . However, parasitic capacitances may often dominate the gate capacitance, which strongly affects these scaling characteristics.

A quasi-ballistic device can be analyzed by using the ballistic expression for  $g_m$ . In the classical limit, equation (3.18) becomes

$$f_T \approx \frac{\frac{hTC_{OX}^2}{2m^*q}(V_{GS} - V_T)}{2\pi \frac{2}{3}C_{OX}L_G} = \frac{3hTC_{OX}}{8\pi m^*qL_G}(V_{GS} - V_T)$$

(3.20)

Here, the dependence on  $C_{OX}$  does not cancel out, but  $C_{OX}$  can be increased in order to improve  $f_T$ , which relates to a reduction of an intrinsic delay in the channel.

For very large  $C_{OX}$  the device enters the quantum capacitance limit,  $C_{gs} + C_{gd} \approx \frac{2}{3}WL_GC_Q$ , and equation (3.18) becomes

$$f_T \approx \frac{q^2 T}{\pi h_2^2 L_G C_O} = \frac{3T}{4\pi L_G} \sqrt{\frac{q(V_{GS} - V_T)}{2m^*}}$$

(3.21)

A reduced  $m^*$  gives a smaller density of states, and thus a lower  $C_Q$ , while  $g_m$  is independent of  $m^*$ . This explains the overall dependence of  $f_T$  on  $m^*$  in this regime.

With  $R_S, R_D > 0$   $\Omega$ , the expression for  $f_T$  is obtained by adding the resistances to the Z-parameters, which gives

$$\frac{1}{2\pi f_T} = \frac{C_{gs} + C_{gd}}{g_m} + \frac{C_{gs} + C_{gd}}{g_m} (R_S + R_D)g_d + (R_S + R_D)C_{gd}$$

(3.22)

The maximum oscillation frequency,  $f_{max}$ , is another figure of merit for high-frequency applications, and is defined as the frequency at which the power gain is unity.  $|\mathbf{U}|$  is the power gain of a unilateral transistor, i.e. one whose reverse transmission parameter, for instance  $h_{12}$ , is zero. It represents the maximum unilateral power gain achievable by the transistor, and is obtained by the addition of

a lossless feedback network. It has the benefit of being independent of the transistor configuration, e.g. common-source and common-gate configurations. It is expressed in Z-parameters as [49]

$$U = \frac{|Z_{21} - Z_{12}|^2}{4[\operatorname{Re}(Z_{11})\operatorname{Re}(Z_{22}) - \operatorname{Re}(Z_{12})\operatorname{Re}(Z_{21})]}$$

(3.23)

One of the significances of U is that the device is passive when U < 1 and active when U > 1. The frequency associated with this transition is  $f_{max}$  [49]

$$f_{max} = \sqrt{\frac{f_T}{8\pi R_G C_{gd} \left[1 + \frac{2\pi f_T}{C_{gd}}\right] \Psi}}$$

(3.24)

where  $\Psi$  is

$$\Psi = (R_D + R_S) \frac{(C_{gs} + C_{gd})^2 g_d^2}{g_m^2} + (R_D + R_S) \frac{(C_{gs} + C_{gd}) C_{gd} g_d}{g_m} + \frac{(C_{gs} + C_{gd})^2 g_d}{g_m^2}$$

(3.25)

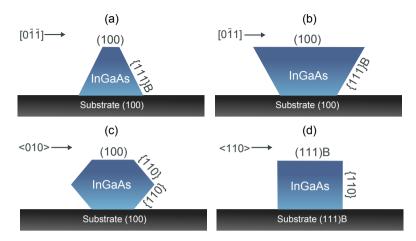

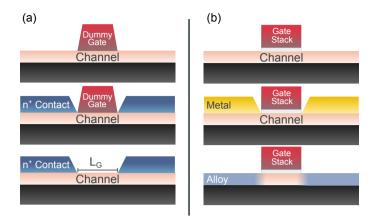

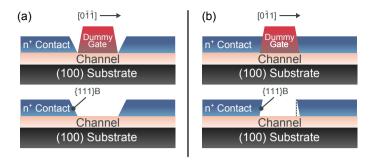

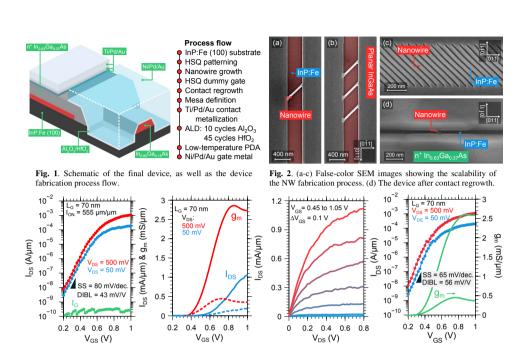

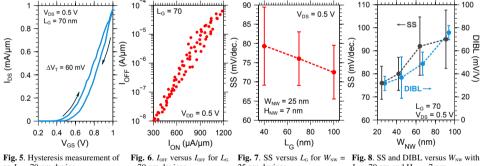

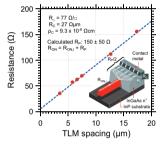

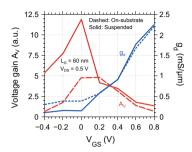

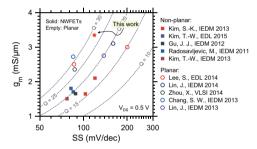

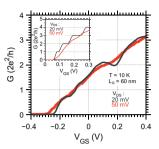

### **Transistor Design & Fabrication**