# LUND UNIVERSITY

InGaAs nanowire MOSFETs with I<sub>ON</sub> = 555  $\mu$ a/ $\mu$ m at I<sub>OFF</sub> = 100 nA/ $\mu$ m and V<sub>DD</sub> = 0.5 v

Zota, Cezar B.; Lindelöw, Fredrik; Wernersson, Lars Erik; Lind, Erik

Published in:

2016 IEEE Symposium on VLSI Technology, VLSI Technology 2016

DOI:

10.1109/VLSIT.2016.7573418

2016

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA):

Zota, C. B., Lindelöw, F., Wernersson, L. E., & Lind, E. (2016). InGaAs nanowire MOSFETs with I = 555 μa/μm at I = 100 nA/μm and V = 0.5 v. In 2016 IEEE Symposium on VLSI Technology, VLSP Technology 2016 Article 7573418 IEEE - Institute of Electrical and Electronics Engineers Inc.. https://doi.org/10.1109/VLSIT.2016.7573418

Total number of authors: 4

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

PO Box 117 221 00 Lund +46 46-222 00 00

Download date: 17. Dec. 2025

# InGaAs Nanowire MOSFETs with $I_{ON}$ = 555 $\mu A/\mu m$ at $I_{OFF}$ = 100 nA/ $\mu m$ and $V_{DD}$ = 0.5 V

Cezar B. Zota, Lars-Erik Wernersson and Erik Lind

Department of Electrical and Information Technology, Lund University, Box 118, Lund, Sweden E-mail: cezar.zota@eit.lth.se. Phone: +46462228062

#### **Abstract**

We report on  $In_{0.85}Ga_{0.15}As$  nanowire MOSFETs (NWFETs) with record performance in several key metrics for VLSI applications. These devices exhibit  $I_{\rm ON} = 555~\mu{\rm A/\mu m}$  (at  $I_{\rm OFF} = 100~{\rm nA/\mu m}$  and  $V_{\rm DD} = 0.5~{\rm V}$ ),  $I_{\rm ON} = 365~\mu{\rm A/\mu m}$  (at  $I_{\rm OFF} = 10~{\rm nA/\mu m}$  and  $V_{\rm DD} = 0.5~{\rm V}$ ) and a quality factor  $Q \equiv g_{\rm m}/{\rm SS}$  of 40, all of which are the highest reported for a III-V as well as silicon transistor. Furthermore, a highly scalable, self-aligned gate-last fabrication process is utilized, with a single nanowire as the channel. The devices use a 45° angle between the nanowire and the contacts, which allows for up to a 1.4 times longer gate length at a given pitch.

# Introduction

In<sub>x</sub>Ga<sub>x-1</sub>As MOSFETs are expected to deliver high on-currents at a reduced  $V_{\rm DD}$  of 0.5 V, making them suitable for VLSI applications. This is due to their high mobility, which enables increased transconductance  $g_{\rm m}$  at a given  $L_{\rm G}$ . For instance, we have recently demonstrated  $In_{0.85}Ga_{0.15}As$  NWFETs with  $g_m =$ 3.3 mS/µm, surpassing that of all other III-V and silicon transistors, including HEMTs [4]. However, to achieve high  $I_{\rm ON}$  at a specified  $I_{\rm OFF}$  and  $V_{\rm DD}=0.50~{\rm V}$  (an important VLSI metric) comparable to state-of-the-art silicon technology, the subthreshold slope must be near 60 mV/decade. This is challenging in III-V technology due to the oxide interface quality and small band causing gap, band-to-band-tunneling in the off-state. Recently, planar InAs MOSFETs with  $I_{ON}$  matching or surpassing that of silicon technology were reported [12]. In this work, we report on NWFETs with a new record of  $I_{ON} = 555 \mu A/\mu m$  at  $I_{OFF} = 100$  $nA/\mu m$  and  $V_{DD} = 0.5 \text{ V}$ .

## **Device Fabrication**

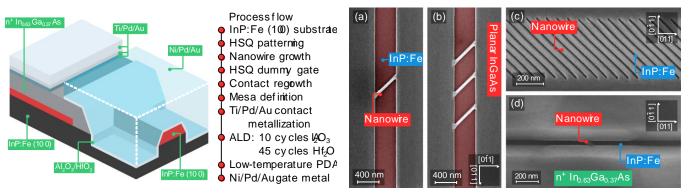

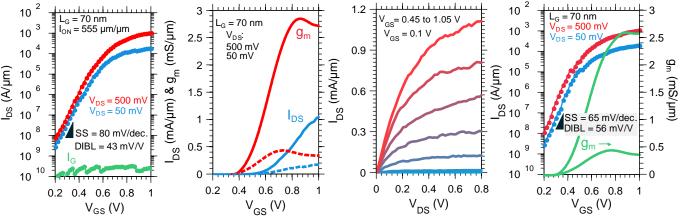

Fig. 1 shows a schematic of the fabricated device, and the process flow. The nanowires are formed by selective area growth, using hydrogen silsesquioxane (HSQ) as the MOCVD growth mask. The composition of the nanowire layer is In<sub>0.63</sub>Ga<sub>0.37</sub>As, while the nanowire is In<sub>0.85</sub>Ga<sub>0.15</sub>As, determined by EDX. Fig. 2(a)-(c) demonstrate the scalability of the selective growth process. A high-density nanowire-cluster with nanowire spacing of <10 nm is shown in fig. 2c. In this work, we characterize single-nanowire devices. The highly doped In<sub>0.63</sub>Ga<sub>0.37</sub>As ( $N_D = 5 \times 10^{19} \text{ cm}^{-3}$ ) contact layer is formed from a subsequent MOCVD growth step using HSQ as a dummy gate [Fig. 2(d)]. A 45° angle between the nanowire and the contacts is chosen in order to obtain optimal crystal facets. At a given pitch, this will also improve electrostatic control by allowing a longer gate length. After mesa isolation, Ti/Pd/Au is patterned and evaporated as the contact metal. The InP in the channel region is etched by HCl (1:1), in order for the metal to properly cover the sides of the nanowire. Several cycles of surface oxidation by ozone and diluted HCl etching is performed in order to reduce the dimensions of the nanowire. Surface passivation, by (NH4)<sub>2</sub>S (1:1) for 20 min, is followed by deposition of  $Al_2O_3/HfO_2$  (EOT = 1.5 nm) by ALD at 300/100°C. Subsequently, an in-situ 12 hour post-deposition annealing step at 100°C in N<sub>2</sub> atmosphere is performed. Ni/Pd gate metal patterning and evaporation completes the process.

#### Results

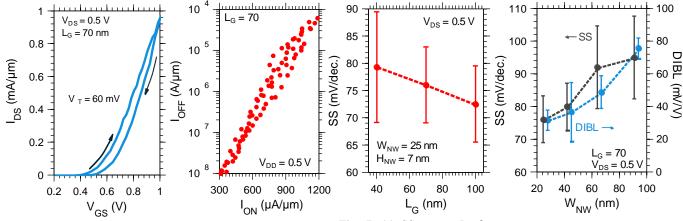

Fig. 3(a)-(c) show subthreshold, transfer and output characteristics of an  $L_{\rm G}=70$  nm NWFET with nanowire width and height  $W_{\rm NW}/H_{\rm NW}=25/7$  nm. Peak transconductance is  $g_{\rm m,peak}=2.85$  mS/ $\mu$ m. The subthreshold characteristics for the same device are shown in Fig. 4. The subthreshold slope (SS) is 80 mV/decade at both  $V_{\rm DS}=0.5$  V and 50 mV. The drain-induced barrier-lowering (DIBL) is 43 mV/V at  $I_{\rm DS}=1$   $\mu$ A/ $\mu$ m. The device exhibits  $I_{\rm ON}=555$   $\mu$ A/ $\mu$ m at  $I_{\rm OFF}=100$  nA/ $\mu$ m and  $V_{\rm DD}=0.5$  V, which is the highest reported value for a MOSFET. The quality factor  $Q\equiv g_{\rm m}/{\rm SS}$  is 35 for this device. The on-resistance is  $R_{\rm ON}=177$   $\Omega\mu$ m at  $V_{\rm GS}>1.4$  V. The specific contact resistivity is  $\rho_{\rm C}=7\times10^{-8}$   $\Omega$ cm<sup>-2</sup> and the sheet resistance of the n<sup>+</sup>  $I_{\rm 10,63}Ga_{0.37}As$  contact layer is  $R_{\rm L}=70$   $\Omega$ / $\rm L_{\odot}$ , both calculated from TLM measurements.

Fig. 4 shows transfer characteristics for another  $L_{\rm G}=70$  nm device with  $g_{\rm m,peak}=2.65$  mS/ $\mu$ m at  $V_{\rm DS}=0.5$  V. The average SS over one, two and three decades is 65, 69 and 73 mV/decade, respectively, all at  $V_{\rm DS}=0.5$  V. This device shows  $I_{\rm ON}=535~\mu{\rm A}/\mu{\rm m}$  at  $I_{\rm OFF}=100~{\rm nA}/\mu{\rm m}$  and  $I_{\rm ON}=365~\mu{\rm A}/\mu{\rm m}$  at  $I_{\rm OFF}=10~{\rm nA}/\mu{\rm m}$ ,  $V_{\rm DD}=0.5$  V. This is the highest reported  $I_{\rm ON}$  at  $I_{\rm OFF}=10~{\rm nA}/\mu{\rm m}$ . DIBL is 56 mV/V at  $I_{\rm DS}=1~\mu{\rm A}/\mu{\rm m}$ . The quality factor Q =  $g_{\rm m}/{\rm SS}$  is 40 for this device, which is the highest reported Q-factor for a MOSFET. The difference in SS between these devices may be explained by the discrete nature of traps in the small channel area  $(2\times10^{-3}~\mu{\rm m}^2)$ .

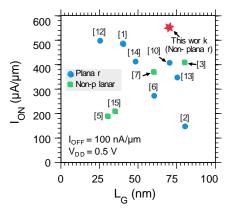

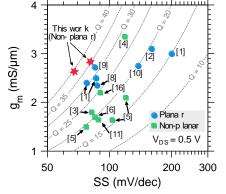

The hysteresis (Fig. 5) is  $\Delta V_{\rm T} = 60$  mV for  $V_{\rm GS} = 0.2$ -1.0 V, indicating high-quality oxide and oxide interface.  $I_{\rm OFF}$  versus  $I_{\rm ON}$  for several devices with  $L_{\rm G} = 70$  nm and  $W_{\rm NW}/H_{\rm NW} = 25/7$  nm is shown in Fig. 6, measured at a swing of  $V_{\rm DD} = 0.5$  V. Fig. 7 shows SS versus  $L_{\rm G}$ . Error bars show the standard deviation. SS and DIBL versus nanowire width  $W_{\rm NW}$  is shown in Fig. 8 ( $H_{\rm NW} = 7$  nm). Data points are offset for clarity. Improved electrostatic control from use of smaller nanowires can clearly be observed. The trend indicates that SS can be further reduced by additional scaling down of  $W_{\rm NW}$ . Fig. 9 and 10 show benchmarks of  $I_{\rm ON}$  and Q for various planar and non-planar MOSFETs.

### **Conclusions**

We have demonstrated highly scalable nanowire MOSFETs with record high performance in several key VLSI metrics. We have shown a device with  $g_{\rm m}=2.85$  mS/ $\mu$ m, SS = 80 mV/decade and  $I_{\rm ON}=555$   $\mu$ A/ $\mu$ m at  $I_{\rm OFF}=100$  nA/ $\mu$ m and  $V_{\rm DD}=0.5$  V. We have also shown a device with  $g_{\rm m}=2.65$  mS/ $\mu$ m and SS = 65 mV/decade, which gives a quality factor Q = 40.

#### Acknowledgements

This work was supported in part by the Swedish Research Council, in part by the Knut and Alice Wallenberg Foundation, in part by the Swedish Foundation for Strategic Research, and in part by the European Union H2020 program INSIGHT (Grant Agreement No. 688784).

Fig. 1. Schematic of the final device, as well as the device fabrication process flow.

Fig. 2. (a-c) False-color SEM images showing the scalability of the NW fabrication process. (d) The device after contact regrowth.

Fig. 3. (a) Subthreshold, (b) transfer and (c) output characteristics of the same  $L_G = 70$  nm,  $W_{\rm NW}/H_{\rm NW} = 25/7$  nm device.  $I_{\rm ON} = 555~\mu{\rm A}/\mu{\rm m}$  at  $I_{\rm OFF} = 100~{\rm nA}/\mu{\rm m}$  and  $V_{\rm DD} = 0.5~{\rm V}$ .

**Fig. 4**. (a)  $I_{DS}$ - $V_{GS}$  for an  $L_G$  = 70 nm,  $W_{\rm NW}/H_{\rm NW} = 25/7$  nm device.

Fig. 5. (a) Hysteresis measurement of an  $L_G = 70$  nm device

**Fig. 6**. (a)  $I_{OFF}$  versus  $I_{OFF}$ for  $L_G = 70$  nm devices.

Fig. 7. (a) SS versus  $L_{\rm G}$  for Fig. 8. (a) SS and DIBL versus  $W_{\rm NW}$  for  $W_{\rm NW} = 25$  nm devices.

$L_G = 70$  nm and  $H_{NW} = 7$  nm devices.

**Fig. 9**. Benchmark of  $I_{ON}$  at  $I_{OFF} = 100$  $nA/\mu m$  and  $V_{DD} = 0.5 \text{ V}$ .

Fig. 10. Benchmark of  $Q = g_m/SS$  at  $V_{DS} = 0.5 \text{ V}$ for various planar and non-planar III-V FETs.

- [1] S. Lee et al., EDL, p. 621 (2014).

- [2] J. Lin et al., IEDM, p. 574 (2014).

- [3] T.-W. Kim et al., EDL, p. 223 (2015).

- [4] C. B. Zota et al., IEDM, p. 811 (2015).

- [5] S.-H. Kim et al., IEDM, p. 432 (2013).

- [6] Radosavljevic et al., IEDM, p. 765 (2011).

- [7] T.-W. Kim et al., IEDM, p. 425 (2013).

- [8] X. Zhou et al., VLSI, p. 1 (2014).

- [9] P. Chang et al., IEDM, p. 418 (2013).

- [10] J. Lin et al., IEDM, p. 424 (2013).

- [11] J. J. Gu et al., IEDM, p. 634 (2012).

- [12] S. Lee et al., VLSI, p. 1 (2014).

- [13] Radosavljevic et al., IEDM, p. 319 (2009).

- [14] C. Huang et al., IEDM, p. 589 (2014).

- [15] D.-H. Kim et al., IEDM, p. 761 (2012).

- [16] N. Waldron et al., IEDM, p. 800 (2015).