# InGaAs tri-gate MOSFETs with record on-current

Zota, Cezar B.; Lindelow, Fredrik; Wernersson, Lars Erik; Lind, Erik

Published in:

2016 IEEE International Electron Devices Meeting, IEDM 2016

DOI:

10.1109/IEDM.2016.7838336

2017

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA):

Zota, C. B., Lindelow, F., Wernersson, L. E., & Lind, E. (2017). InGaAs tri-gate MOSFETs with record on-current. In *2016 IEEE International Electron Devices Meeting, IEDM 2016* (pp. 3.2.1-3.2.4). Article 7838336 IEEE - Institute of Electrical and Electronics Engineers Inc.. https://doi.org/10.1109/IEDM.2016.7838336

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 17. Dec. 2025

# InGaAs Tri-gate MOSFETs with Record On-Current

Cezar B. Zota, Fredrik Lindelow, Lars-Erik Wernersson and Erik Lind Department of Electrical and Information Technology, Lund University, Lund, Sweden E-mail: cezar.zota@eit.lth.se. Phone: +46462228062

Abstract—We demonstrate InGaAs tri-gate MOSFETs with an on-current of  $I_{\rm ON}=650~\mu{\rm A/\mu m}$  at  $V_{\rm DD}=0.5~{\rm V}$  and  $I_{\rm OFF}=100~{\rm nA/\mu m}$ , enabled by an inverse subthreshold slope of  $SS=66~{\rm mV/decade}$  and transconductance of  $g_{\rm m}=3~{\rm mS/\mu m}$ , a Q-factor of 45. This is the highest reported  $I_{\rm ON}$  for both Si-based and III-V MOSFETs. These results continue to push III-V MOSFET experimental performance towards its theoretical limit. We find an improvement in SS from 81 to 75 mV/dec. as the effective oxide thickness (EOT) is scaled down from 1.4 to 1 nm, as well as improvements in SS,  $g_{\rm d}$  and DIBL from reducing the nanowire width. We also find that electron mobility remains constant as the width is scaled to 18 nm.

#### I. INTRODUCTION

An important path for reducing the power density in CMOS technology has been to lower the supply voltage  $V_{\rm DD}$ . To maintain sufficient drive current, innovations are required, such as strained channels, novel channel materials and 3D device architectures [1]-[14]. For this purpose, high indium In<sub>x</sub>Ga<sub>1-x</sub>As is an attractive channel material due to its excellent electron transport properties, i.e. high electron mobility  $\mu_e$  and long mean free path  $\lambda$  [6]. While the relatively low DOS of indium-rich In<sub>x</sub>Ga<sub>1-x</sub>As is predicted to limit  $I_{DS}$  in highly scaled devices, compared to competing technologies such as Si and Ge, this may be offset by the gain from the long  $\lambda$  and high  $\mu_e$  of In<sub>x</sub>Ga<sub>1-x</sub>As [15]. Since this technology likely will be implemented in a 3D channel architecture, such as FinFETs or NWFETs, a further question concerns the dependence of  $\lambda$  on the channel dimensions, i.e. the influence of surface roughness on device performance.

In this work, we demonstrate tri-gate MOSFETs utilizing an  $In_{0.85}Ga_{0.15}As$  nanowire (NW) as the channel. By gate oxide scaling, improvements of the surface passivation process and optimization of device dimensions, we achieve a drive current of  $I_{\rm ON}=650~\mu{\rm A}/\mu{\rm m}$  at  $V_{\rm DD}=0.5~{\rm V}$  and  $I_{\rm OFF}=100~{\rm nA}/\mu{\rm m}$ . This is a record value for both III-V and Si MOSFETs. We also show that, as the NW width,  $W_{\rm NW}$ , is scaled down, electrostatic properties significantly improve, while  $g_{\rm m}$  and  $\lambda$  do not degrade. These results continue to push the limits, as well as explore the potential, of III-V FETs.

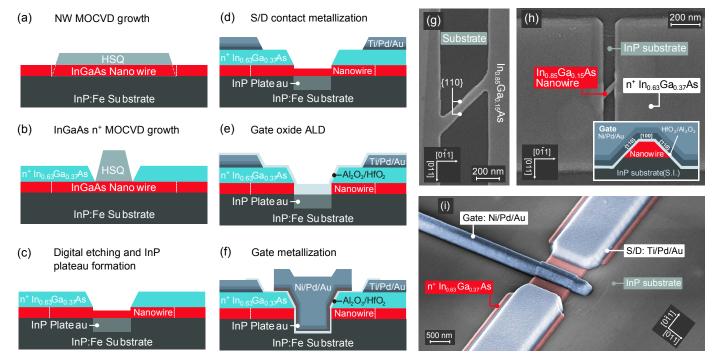

### II. DEVICE FABRICATION

The process flow and schematic images of the device are shown in Fig. 1(a)-(f). The nanowires are formed by selective area growth, using hydrogen silsesquioxane (HSQ) as the MOCVD growth mask, as described elsewhere [4]. Each device consists of a single NW. The composition of the NW is  $In_{0.85}Ga_{0.15}As$ , as determined by optical characterization [15]. Fig. 1(g) shows an SEM image of an NW with  $W_{NW}$  =

90 nm, with the {110} sidewall facets denoted [15]. The inset of Fig. 1(h) shows a schematic figure of the NW crosssection. 30 nm highly doped  $In_{0.63}Ga_{0.37}As$  ( $N_D = 5 \times 10^{19}$  cm<sup>-1</sup> 3) is subsequently grown by MOCVD as the contact layer, utilizing HSQ as a dummy gate [Fig. 1(h)]. After mesa isolation, the InP in the channel is etched by HCl (10%) in order to form a ~30 nm tall plateau, with the purpose of improving the gate coverage along the bottom of the sides of the NW. 4 cycles of surface oxidation by ozone and diluted HCl etching (digital etching) are performed to reduce the dimensions of the NW. The final height of the NW is  $H_{NW} =$ 8 nm, as determined from AFM. Subsequently, Ti/Pd/Au contact metal is evaporated and patterned by lift-off. Surface passivation, by ozone cleaning and (NH4)<sub>2</sub>S (10%) for 20 min, is followed by deposition of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> gate oxide (5/35 cycles and EOT  $\approx 1$  nm, unless otherwise stated). A 12 hour post-deposition anneal step at 100 °C in N<sub>2</sub> atmosphere is performed in-situ. Thermal evaporation and patterning by lift-off of 30/10/150 nm Ni/Pd/Au as the gate metal complete the process [Fig. 1(i)].

#### III. RESULTS

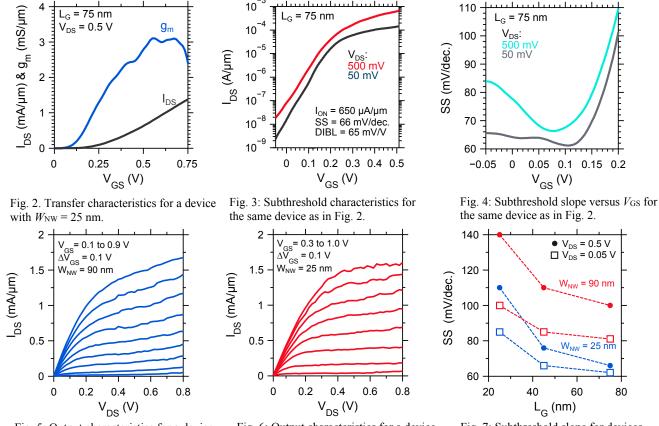

Fig. 2 shows transfer characteristics of a tri-gate MOSFET with  $L_G = 75$  nm and  $W_{NW} = 25$  nm. All normalization is done to the total gated NW periphery, i.e. the three sides of the tri-gate. Peak transconductance is  $g_{\rm m} \approx 3.0$  mS/ $\mu$ m at  $V_{\rm DS}$ = 0.5 V. Subthreshold characteristics of the same device are shown in Fig 3. At  $V_{\rm DD} = 0.5$  V and  $I_{\rm OFF} = 100$  nA/ $\mu$ m,  $I_{\rm ON} =$ 650  $\mu$ A/ $\mu$ m. The gate current is  $I_G < 1$  nA/ $\mu$ m. Minimum inverse subthreshold slope SS reaches 66 mV/decade (Fig. 4) at  $V_{\rm DS} = 0.5$  V, and 61 mV/decade at  $V_{\rm DS} = 0.05$  V. The drain-induced barrier-lowering (DIBL) is 65 mV/V, measured at  $I_{DS} = 1 \mu A/\mu m$ . The on-resistance of this device is  $R_{\rm ON} = 175~\Omega \cdot \mu \rm m$  at  $V_{\rm GS} = 1~V$ . Output characteristics for  $W_{\rm NW} = 90$  and  $W_{\rm NW} = 25$  nm devices with  $L_{\rm G} = 75$  nm are shown in Fig. 5 and 6, respectively. The output conductance of these devices is  $g_d = 0.45$  and 0.25 mS/ $\mu$ m (voltage gain is 5.5 and 10) at  $V_{GS} - V_T = V_{DS} = 0.5 \text{ V}$ .

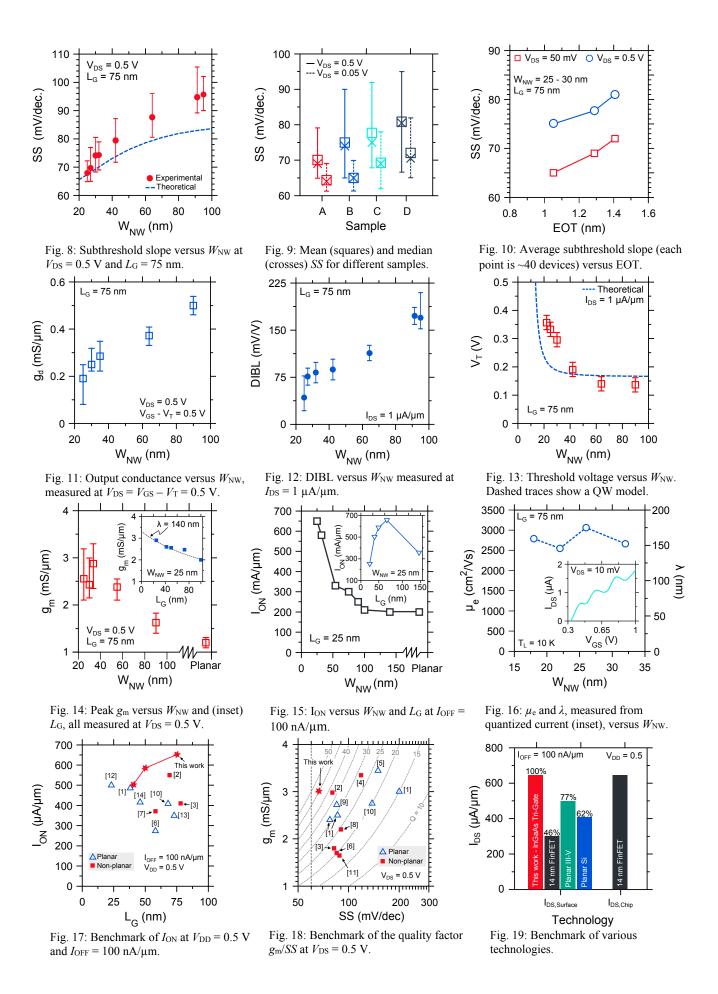

Minimum SS versus  $L_{\rm G}$  is shown for  $W_{\rm NW}=25$  nm and  $W_{\rm NW}=90$  nm devices at  $V_{\rm DS}=0.05$  and 0.5 V (Fig. 7). The reduced  $W_{\rm NW}$  offers improved resilience against short channel effects (SCEs), but at  $L_{\rm G}=25$  nm, SS is degraded (110 mV/decade) even at  $W_{\rm NW}=25$  nm. Minimum SS versus  $W_{\rm NW}$  is shown in Fig. 8 for  $L_{\rm G}=75$  nm devices at  $V_{\rm DS}=0.5$  V. Average minimum SS improves from approximately 95 mV/dec. for  $W_{\rm NW}>90$  nm to SS < 70 mV/dec. for  $W_{\rm NW}<30$  nm due to enhanced electrostatic control. The lowest SS of a device at this bias is 64 mV/dec. The theoretical values

indicate SS obtained from a solution of Laplace's equation modeling the full 3D structure of the nanowire using COMSOL. To improve performance at short  $L_G$ ,  $W_{NW}$  must be further reduced. Scaling of  $H_{NW}$  will improve SS but reduce the aspect ratio (AR), which is undesirable. Moreover, the implementation of a wider band gap back-barrier, such as InAlAs or a BOX layer, is also expected to improve resilience to SCEs. Fig. 9 shows median (crosses) and mean (squares) minimum SS for four samples with  $L_G = 75$  nm and  $W_{\rm NW} = 25-30 \text{ nm}$  at both  $V_{\rm DS} = 0.05 \text{ and } 0.5 \text{ V}$  (~40 devices each). Sample D has 5/50 cycles Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>. Sample C has 5/45 cycles Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>. Sample B and A have 5/35 cycles Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>. In addition, samples D, C and B where passivated with (NH<sub>4</sub>)<sub>2</sub>S (10%) produced by Merck, while sample A was passivated with (NH<sub>4</sub>)<sub>2</sub>S (10%) produced by Sigma-Aldrich. Fig. 10 shows mean minimum SS of samples D to B versus EOT (1 cycle = 1.1 Å,  $\kappa$  = 18 and 9 for HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>). These results indicate an improvement both from oxide scaling (average SS improves from 81 to 75 mV/dec. for EOT from ~1.4 nm to ~1 nm), and from optimization of the surface passivation parameters (mean SS improves from 75 to 70 mV/dec. for sample B to A). The trend indicates that SS may be further improved by scaling of the EOT. We do not observe a clear trend of  $g_m$  versus EOT.

Fig. 11 shows  $g_d$  versus  $W_{NW}$  at  $V_{DS} = 0.5$  V and  $V_{GS} - V_T$ = 0.5 V for  $L_G$  = 75 nm devices. Average  $g_d$  is reduced from  $0.5 \text{ mS/}\mu\text{m}$  at  $W_{\text{NW}} = 90 \text{ nm}$  to  $\sim 0.2 \text{ mS/}\mu\text{m}$  at  $W_{\text{NW}} = 25 \text{ nm}$ . The DIBL measured at 1  $\mu$ A/ $\mu$ m is shown in Fig. 12. It is similarly reduced from 170 mV/V at  $W_{\text{NW}} = 90$  nm, to 38 mV/V at  $W_{\rm NW} = 25$  nm. The threshold voltage ( $V_{\rm T}$ ) defined at  $I_{\rm DS} = 1~\mu {\rm A}/\mu {\rm m}$  increases in narrow NWs (Fig. 13). The trend approximately follows calculated values from an effective mass quantum wire model, indicating that the  $V_{\rm T}$  increase is due to quantum confinement.

Fig. 14 shows  $g_{\rm m}$  versus  $W_{\rm NW}$ . The highest  $g_{\rm m}$  observed in these devices is  $\sim 3.3$  mS/ $\mu$ m (SS<sub>sat</sub> = 90 mV/dec.) at  $V_{DS}$  = 0.5 V and  $L_G = 50$  nm.  $g_m$  increases as  $W_{NW}$  is scaled down to approximately 35 nm from planar architecture ( $W_{NW} = 1 \mu m$ ). This may be explained by that narrow NWs are more Indiumrich, due to interactions with the HSQ mask during MOCVD growth, which may improve mobility as well as change the  $D_{\rm it}$  distribution [15]. This shows that the improvement of  $g_{\rm d}$ with  $W_{\rm NW}$ , is in fact due to improved electrostatics. The inset of Fig. 15 shows average values of  $g_{\rm m}$  versus  $L_{\rm G}$  for  $W_{\rm NW}$  = 25 nm. Dashed traces show an analytical quasi-ballistic model with  $\lambda = 140$  nm fitted to the measured data.

$I_{\rm ON}$  at  $V_{\rm DD} = 0.5$  V and  $I_{\rm OFF} = 100$  nA/ $\mu$ m is shown in Fig. 15 versus both  $W_{\rm NW}$  and  $L_{\rm G}$  (inset).  $I_{\rm ON}$  increases from 200 to 650  $\mu$ A/ $\mu$ m as  $W_{NW}$  goes from 1 um (planar) to 25 nm, due to the simultaneous improvements of SS (100 to 66 mV/dec.) and  $g_{\rm m}$  (1.1 to 3 mS/ $\mu$ m).  $I_{\rm ON}$  peaks at  $L_{\rm G}$  = 75 nm, which is explained by the degraded SS (Fig. 7) and that g<sub>m</sub> only improves slightly (Fig. 14) for shorter  $L_{\rm G}$ .

These devices exhibit quantized conductance at 10 K due to subband splitting in a 1D channel (inset of Fig. 16). From the conductance steps, the transmission is obtained. The device in Fig. 3 shows a transmission of T = 0.67, which indicates quasi-ballistic transport. Fig. 16 shows electron mobility  $\mu_e$  and  $\lambda$  for NWs with  $W_{NW} = 18 - 32$  nm calculated from quantized conductance. To obtain  $\mu_{e_2}$  we use the Einstein relation and a correction factor of 1.6 to account for degeneracy [15]. We note that this method is not strongly influenced by  $D_{it}$ . No dependency versus  $W_{NW}$  is observed, which correlates with  $g_{\rm m}$  versus  $W_{\rm NW}$  with  $W_{\rm NW} < 35$  nm, explained by small surface scattering. Since g<sub>m</sub> is temperature-independent, the same is true for  $\mu_e$ .

A benchmark of the  $I_{ON}$  (at  $V_{DD} = 0.5$  V and  $I_{OFF} = 100$ nA/μm) for state-of-the-art III-V planar and non-planar MOSFETs is shown in Fig. 17. The value of 650 μA/μm presented in this work is the record value of both categories. The same is true for the quality factor  $Q = g_m/SS$ , which is 45 in this work (Fig. 18). Fig. 19 compares  $I_{ON}$  at  $V_{DD} = 0.5$  V and  $I_{OFF} = 100 \text{ nA/}\mu\text{m}$  for various technologies.  $I_{DS,surface}$  is  $I_{\rm ON}$  normalized to the gated channel periphery, while  $I_{\rm DS,chip}$  is normalized to the chip surface width including the specified pitch size. I<sub>ON,chip</sub> in our devices is lower than that of 14 nm FinFET (570 compared to 650 μA/μm for a pitch of 42 nm), which demonstrates the importance of high AR in 3D channels, but we observe a two-fold increase in  $I_{ON,surface}$  over 14 nm FinFET technology, which is due primarily to the high  $\mu_e$  of In<sub>x</sub>Ga<sub>1-x</sub>As [16].

#### IV. CONCLUSION

We have demonstrated In<sub>x</sub>Ga<sub>1-x</sub>As tri-gate MOSFETs with a record on-current of 650  $\mu$ A/ $\mu$ m at  $V_{DD} = 0.5$  V and  $I_{ON} =$ 100 nA/ $\mu$ m, SS = 66 mV/decade and  $g_m$  = 3.0 mS/ $\mu$ m. From data versus NW width, we observed improvements in SS, DIBL and g<sub>d</sub> for scaled down NWs. Furthermore, we observed improvements both from oxide scaling the surface passivation process. From low-temperature measurements we obtain  $\mu_e$  and  $\lambda$ , which remain high, 2750 cm<sup>2</sup>/Vs and 150 nm, respectively, even in scaled NWs.

This work was supported in part by the Swedish Research Council, in part by the Knut and Alice Wallenberg Foundation, in part by the Swedish Foundation for Strategic Research and in part by the European Union H2020 program INSIGHT (Grant Agreement No. 688784).

## V. REFERENCES

- [1] S. Lee et al., EDL, p. 621 (2014).

- [2] C. B. Zota et al., VLSI, (2016).

- [3] T.-W. Kim et al., EDL, vol. 36, p. 223 (2015).

- [4] C. B. Zota et al., IEDM, p. 811 (2015).

- [5] J. Lin et al., EDL, vol 37, p. 381 (2016).

- [6] Radosavljevic et al., IEDM, p. 765 (2011).

- [7] T.-W. Kim et al., IEDM, p. 425 (2013).

- [8] N. Waldron et al., IEDM, p. 800 (2015).

- [9] P. Chang et al., IEDM, p. 418 (2013). [10] J. Lin et al., IEDM, p. 424 (2013).

- [11] J. J. Gu et al., IEDM, p. 634 (2012).

- [12] S. Lee et al., VLSI (2014).

- [13] Radosavljevic et al., IEDM, p. 319 (2009).

- [14] C. Huang et al., IEDM, p. 589 (2014).

- [15] C. B. Zota et al., ACS Nano, vol. 9, p. 9892 (2015).

- [16] S. Natarajan et al., IEDM, p. 71 (2014).

Fig. 1: Schematic figures SEM images of the device fabrication process. (a) NW formation utilizes selective area MOCVD growth with an EBL-defined HSQ hard mask. (b) Contacts are defined using an HSQ dummy gate and MOCVD regrowth of  $n^+$  In<sub>0.63</sub>Ga<sub>0.37</sub>As. (c) NW is scaled down using "digital etching". (d) S/D metal is deposited by evaporation and lift-off. (e) A bilayer of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> is used as the gate oxide. (f) Ni/Pd/Au is evaporated as the gate metal. (g) SEM image of a 90 nm wide NW with the {110} side facets denoted. (h) The device after contact regrowth. Inset shows a schematic cross-section of the NW in the finished device. (i) False-color SEM image of the finished device. The NW is located at the center of the 1  $\mu$ m wide mesa.

Fig. 5: Output characteristics for a device with  $L_G = 75$  nm and  $W_{NW} = 90$  nm.

Fig. 6: Output characteristics for a device with  $L_G = 75$  nm and  $W_{NW} = 25$  nm.

Fig. 7: Subthreshold slope for devices with different  $W_{\rm NW}$  and  $L_{\rm G}$ .