# High-Performance Lateral Nanowire InGaAs MOSFETs with Improved On-Current

Zota, Cezar B.; Wernersson, Lars Erik; Lind, Erik

Published in:

**IEEE Electron Device Letters**

DOI:

10.1109/LED.2016.2602841

2016

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA):

Zota, C. B., Wernersson, L. E., & Línd, E. (2016). High-Performance Lateral Nanowire InGaAs MOSFETs with Improved On-Current. *IEEE Electron Device Letters*, *37*(10), 1264-1267. Article 7552490. https://doi.org/10.1109/LED.2016.2602841

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

PO Box 117 221 00 Lund +46 46-222 00 00

Download date: 16. Dec. 2025

# High-Performance Lateral Nanowire InGaAs MOSFETs with Improved On-Current

Cezar B. Zota, Lars-Erik Wernersson and Erik Lind, Member, IEEE

Abstract—We report on  $In_{0.85}Ga_{0.15}As$  MOSFETs utilizing selectively grown lateral nanowires as the channel. These devices exhibit on-current of  $I_{ON}=565~\mu A/\mu m$  at  $I_{OFF}=100~nA/\mu m$  and  $V_{DD}=0.5~V$ , which is higher than all other reported values for III-V FETs. This is enabled by a transconductance of 2.9 mS/ $\mu m$  and a minimum SS $_{sat}$  of 77 mV/decade. A ballistic top-of-the-barrier model is used to model these devices and to predict their ultimate performance, which is approximately twice that of the fabricated devices.

### Index Terms—MOSFET, III-V, InGaAs, Nanowire

#### I. INTRODUCTION

Indium-rich III-Vs have been considered as a replacement **▲** for silicon as the channel in CMOS technology [1]. This is due to their excellent electron transport properties, such as high mobility, which enables increased transconductance  $g_{\rm m}$  at a given  $L_G$  and may allow a reduction of the supply voltage  $V_{\rm DD}$  to 0.5 V. For instance, there have recently been several reports on In<sub>x</sub>Ga<sub>1-x</sub>As MOSFETs with g<sub>m</sub> of above 3 mS/μm [2]-[3]. However, to achieve high  $I_{ON}$  at a specified  $I_{OFF}$  and  $V_{\rm DD} = 0.5$  V, which is a primary metric for CMOS applications, the subthreshold slope must be near the thermal limit of 60 mV/decade. This is a challenge in III-V technology due to e.g. the high-k oxide interface quality. Moreover, the narrow band gap of In<sub>x</sub>Ga<sub>1-x</sub>As causes, for instance, band-toband-tunneling in the off-state which makes reaching lower  $I_{\rm OFF}$  such as 1 and 10 nA/ $\mu$ m (low-power and general purpose limits, respectively) difficult. For this reason, 3D channel architectures, such as various implementations of FinFETs and Tri-gate devices, are promising to improve electrostatic integrity at scaled down gate-lengths [4].

In this work, we report on  $In_{0.85}Ga_{0.15}As$  nanowire MOSFETs with a tri-gate architecture and a record  $I_{\rm ON}$  of 565  $\mu A/\mu m$  at  $I_{\rm OFF}=100$  nA/ $\mu m$  and  $V_{\rm DD}=0.5$  V, together with a combination of  $g_{\rm m}=2.9$  mS/ $\mu m$  and minimum SS of 77 mV/decade. Compared to our previous work, we have here

Manuscript received June XX, 2016, revised June XX, 2016; accepted June XX, 2016. Date of publication June, 2016; date of current version June, 2016. This work was supported in part by the Swedish Foundation for Strategic Research, in part by the Knut and Alice Wallenberg Foundation, in part by the Swedish Research Council and in part by the European Union H2020 program INSIGHT (Grant Agreement No. 688784).

The authors are with the Department of Electrical and Information Technology, Lund University, Lund 221 00, Sweden (e-mail: cezar.zota@eit.lth.se).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

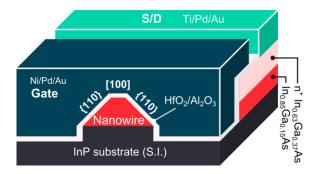

Fig. 1. Schematic figure of the fabricated device. The crystal facet are deduced from facet angels and the NW orientation.

TABLE I

COMPARISON OF THEORETICAL PERFORMANCE WITH RECORD FABRICATED

III-V DEVICES

| Metric                                                      | Experimental  | Theoretical |

|-------------------------------------------------------------|---------------|-------------|

| $I_{\rm ON}$ ( $I_{\rm OFF} = 100 \text{ nA/}\mu\text{m}$ ) | 565 μA/μm     | 1200 μA/μm  |

| $I_{\rm ON}$ ( $I_{\rm OFF} = 10 \text{ nA/}\mu\text{m}$ )  | 360 μA/μm [5] | 930 μA/μm   |

| $I_{\rm ON} (I_{\rm OFF} = 1 \text{ nA/}\mu\text{m})$       |               | 670 μA/μm   |

| $g_{\text{m,peak}}$ (V <sub>DS</sub> = 0.5 V)               | 2.9 mS/µm     | 6 mS/μm     |

| $SS_{\min}$ (V <sub>DS</sub> = 0.05 V)                      | 68 mV/dec.    | 60 mV/dec.  |

| $SS_{\min}$ (V <sub>DS</sub> = 0.5V)                        | 77 mV/dec.    | 60 mV/dec.  |

optimized the nanowire dimensions, as well as examined the influence of gate length scaling [5]. We also explore the ultimate potential of these devices by comparing with a modeled fully ballistic device.

## II. DEVICE FABRICATION

Lateral In<sub>0.85</sub>Ga<sub>0.15</sub>As nanowires (NWs) are formed on semiinsulating InP:Fe (100) by selective area growth using hydrogen silsequioxane (HSQ) as a hard mask, as described elsewhere [6]. The composition of the NWs is determined by optical characterization [7]. The direction of the NW is (010). The main focus of this work is on devices consisting of a single NW with width,  $W_{NW}$ , and height of 28 and 8 nm, respectively, and with gate length, L<sub>G</sub>, of 75 nm. To explore the scaling properties, devices with  $L_G = 50 - 150$  nm, and  $W_{NW} = 28 - 140$  nm are also fabricated. A 30 nm highly doped  $In_{0.63}Ga_{0.37}As$  (N<sub>D</sub> = 5 × 10<sup>19</sup> cm<sup>-3</sup>) raised contact layer is regrown using an HSQ dummy gate hard mask. The direction of the dummy gate is (110). Subsequently, the InP in the channel is etched down by HCl solution. This is to ensure proper gating of the lower edge of the nanowire. The dimensions of the nanowire are reduced by 4 cycles of Ozone oxidation and diluted HCl oxide etch. 50 nm Ti/Pd/Au

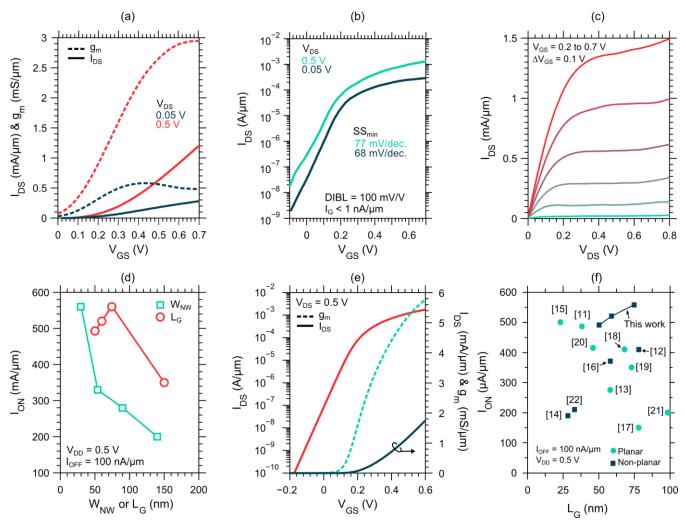

Fig. 2. (a) Transfer, (b) subthreshold and (c) output characteristics of the same  $L_G = 75$  nm device. (d)  $I_{ON}$  at  $I_{OFF} = 100$  nA/ $\mu$ m and  $V_{DD} = 0.5$  versus  $W_{NW}$  (squares) and  $L_G$  (circles). Squares have a fixed  $L_G = 75$ , and circles have a fixed  $W_{NW} = 28$  nm. (e) Transfer and subthreshold performance of a fully ballistic ideal device using a top-of-the-barrier model. (f) A benchmark of  $I_{ON}$  at  $I_{OFF} = 100$  nA/ $\mu$ m and  $V_{DD} = 0.5$  V for state-of-the-art III-V planar and non-planar MOSFETs.

source/drain metal is deposited by thermal evaporation. Prior to ALD deposition of  $Al_2O_3/HfO_2$  (10/40Å, EOT  $\approx 1.5$  nm) at 300/100°C, sulphur passivation in (NH<sub>4</sub>)<sub>2</sub>S (10%) is performed for 20 min. Following, an in-situ post-deposition annealing step is performed at 100°C for 12 hours in N<sub>2</sub> atmosphere, which is found to improve the subthreshold slope. Finally, 150 nm Ni/Pd/Au is patterned and thermally evaporated as the gate-metal and gate pad using lift-off. Since the gate was defined in the contact regrowth step, gate metallization is self-aligned. Fig. 1 shows a schematic image of the fabricated device, and the facets of the NW, which have 45° facet angles, as we have previously shown [7]. The distance between S/D contact metal and the gate is 700 nm. The width of the contacts is 1 µm.

## III. RESULTS

Fig. 2(a)-(b) show transfer and subthreshold characteristics for a device with  $L_G=75$  nm. The data is normalized to the gated perimeter according to the shape in Fig. 1. The peak transconductance is  $g_m=2.9$  mS/ $\mu$ m at  $V_{DS}=0.5$  V.

Minimum inverse subthreshold slope (SS<sub>sat</sub>) is 77 mV/decade, and the drain-induced barrier lowering (DIBL), measured at  $I_{\rm DS}=1~\mu{\rm A}/\mu{\rm m}$ , is 100 mV/V. The gate-leakage current  $I_{\rm G}$  is below 1 nA/ $\mu{\rm m}$ . At V<sub>DS</sub> = 50 mV, minimum SS is 68 mV/decade. The on-current, measured as  $I_{\rm DS}$  at a fixed voltage swing of 0.5 V from  $I_{\rm OFF}=100~{\rm nA}/\mu{\rm m}$  and  $V_{\rm DS}=0.5~{\rm V}$ , is  $I_{\rm ON}=565~\mu{\rm A}/\mu{\rm m}$ . The output characteristics of an  $L_{\rm G}=75~{\rm m}$  device is shown in Fig. 2(c). The on-resistance is  $R_{\rm ON}=180~{\rm Cm}$ , and the contact resistance is approximately  $R_{\rm C}=20~{\rm Cm}$ , as determined from transmission line measurements.

Fig. 2(d) shows  $I_{\rm ON}$  at  $I_{\rm OFF}=100$  nA/ $\mu$ m and  $V_{\rm DD}=0.5$  versus both the width of the nanowires,  $W_{\rm NW}$  (with  $L_{\rm G}=75$  nm for all devices) and  $L_{\rm G}$  (with  $W_{\rm NW}=28$  nm for all devices).  $I_{\rm ON}$  significantly improves as  $W_{\rm NW}$  is scaled down from 140 nm to 28 nm, which is primarily due to an improvement of SS, from > 100 mV/decade to approximately 80 mV/decade, as an effect of improved electrostatic control. The optimal  $I_{\rm ON}$  is found at  $L_{\rm G}=75$  nm for these devices. At shorter  $L_{\rm G}$ , short-channel effects begin to degrade performance through a degradation of the subthreshold slope. This can be offset by, e.g. further scaling of the NW. The peak transconductance is

weakly increasing with the reduction of gate length.

The ideal device performance was calculated using a fully ballistic top-of-the-barrier model and is shown in Fig. 2(e). The gate length is assumed long enough to suppress any short channel effects. For the evaluation of device density of states, a 2-band non parabolic quantum wire model was used [8]. Quantum well band bending was approximately taken into account through a first order perturbation scheme.

The nanowire was modeled as a  $28 \times 8$  nm rectangular wire (which is more voluminous than the fabricated NWs, due to their  $45^{\circ}$  facet angles), with a bulk effective mass m<sup>\*</sup> =  $0.027 m_0$  and a bulk bandgap of  $E_{\rm g} = 0.44$  eV, roughly corresponding to  ${\rm In_{0.9}Ga_{0.1}As}$ . The oxide capacitance was calculated from the tri-gate configuration, with  $t_{\rm ox} = 4.7$  nm and  $\varepsilon_{\rm r,ox} = 15.9$  [9]. Extrinsic resistances are  $0 \Omega$ .

Ideal nanowire device performance is compared to that of fabricated III-V MOSFETs with record  $I_{ON}$  in table 1. Currently,  $I_{OFF} = 1$  nA/ $\mu$ m has not been demonstrated experimentally in non-planar InGaAs MOSFETs. The  $g_{\rm m}$  and SS values are those reported in this work. Ideal  $g_{\rm m}$  and  $I_{\rm ON}$  (at 100 nA/μm) are 6 mS/μm and 1200 μA/μm, respectively. The difference of about a factor 2 compared to our devices is explained mainly by quasi-ballistic transport, e. g. a transmission less than 1, as well as non-ideal electrostatics partly due to traps (D<sub>it</sub>), in the fabricated devices [10]. We have previously shown that the transmission, T, in devices similar to those reported here is approximately 70% [7]. Therefore, to improve device performance, device dimensions,  $W_{\rm NW}$  and  $L_{\rm G}$  must be optimized, EOT must be reduced and the oxide interface quality improved. T is inversely proportional to  $L_G$ , and  $W_{NW}$  also influences T since smaller  $W_{NW}$  typically correlates to lower mobility and mean free path.

Finally, we benchmark our results with state-of-the art III-V planar and non-planar MOSFETs [Fig. 1(f)] [11]–[22]. The  $I_{\rm ON}$  (at 100 nA/ $\mu$ m) of 565  $\mu$ A/ $\mu$ m reported in this work is the record value for both planar and non-planar devices.

#### IV. CONCLUSION

We have reported  $In_{0.85}Ga_{0.15}As$  nanowire MOSFETs with record  $I_{ON}$  at 100 nA/ $\mu$ m. This was enabled by a transconductance of 2.9 mS/ $\mu$ m and minimum SS of 77 mV/decade. We also compared record III-V MOSFET performance to an ideal fully ballistic device using a top-of-the-barrier model. Fabricated device performance was found to have reached approximately half of that of the ideal device.

#### REFERENCES

- [1] H. Riel, L.-E. Wernersson, M. Hong, and J. A. del Alamo, "III–V compound semiconductor transistors—from planar to nanowire structures," *MRS Bull.*, vol. 39, no. 08, pp. 668–677, Aug. 2014. DOI: 10.1557/MRS.2014.137

- [2] J. Lin, X. Cai, Y. Wu, D. A. Antoniadis, and J. A. Del Alamo, "Record maximum transconductance of 3.45 mS/µm for III-V FETs," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 381–384, 2016. DOI: 10.1109/LED.2016.2529653

- [3] C. B. Zota, L. E. Wernersson, and E. Lind, "Single suspended InGaAs nanowire MOSFETs," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2015, pp. 31.4.1–31.4.4. DOI: 10.1109/IEDM.2015.7409808

- [4] N. Waldron, S. Sioncke, J. Franco, L. Nyns, A. Vais, X. Zhou, H. C. Lin, G. Boccardi, J. W. Maes, Q. Xie, M. Givens, F. Tang, X. Jiang,

- E. Chiu, A. Opdebeeck, C. Merckling, F. Sebaai, D. Van Dorp, L. Teugels, A. S. Hernandez, K. De Meyer, K. Barla, N. Collaert, and Y. V. Thean, "Gate-all-around InGaAs nanowire FETS with peak transconductance of 2200  $\mu$ S/ $\mu$ m at 50 nm Lg using a replacement Fin RMG flow," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2015, pp. 3111–3114. DOI: 10.1109/IEDM.2015.7409805

- [5] C. B. Zota, F. Lindelow, L.-E. Wernersson, and E. Lind, "InGaAs Nanowire MOSFETs with  $I_{on}=555~\mu\text{A}/\mu\text{m}$  at  $I_{off}=100~\text{nA}/\mu\text{m}$  and  $V_{DD}=0.5~\text{V}$ ," in Symp. VLSI Technol. Dig. Tech., Jun. 2016.

- [6] C. B. Zota, L. Wernersson, and E. Lind, "In<sub>0.53</sub>Ga<sub>0.47</sub>As Multiple-Gate Field-Effect Transistors With Selectively Regrown Channels," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 342–344, 2014. DOI: 10.1109/LED.2014.2301843

- [7] C. B. Zota, D. Lindgren, L. E. Wernersson, and E. Lind, "Quantized Conduction and High Mobility in Selectively Grown In<sub>x</sub>Ga<sub>1-x</sub>As Nanowires," ACS Nano, vol. 9, no. 10, pp. 9892–9897, 2015. DOI: 10.1021/acsnano.5b03318

- [8] G. Zerveas, E. Caruso, G. Baccarani, L. Czornomaz, N. Daix, D. Esseni, E. Gnani, A. Gnudi, R. Grassi, M. Luisier, T. Markussen, P. Osgnach, P. Palestri, A. Schenk, L. Selmi, M. Sousa, K. Stokbro, and M. Visciarelli, "Comprehensive comparison and experimental validation of band-structure calculation methods in III-V semiconductor quantum wells," *Solid. State. Electron.*, vol. 115, pp. 92–102, 2016. DOI: 10.1016/j.sse.2015.09.005

- [9] T.-S. Chen, "Determination of the Capacitance, Inductance, and Characteristic Impedance of Rectangular Lines," *IEEE Trans. Microw. Theory Tech.*, vol. 8, no. 5, pp. 510–519, 1960. DOI: 10.1109/TMTT.1960.1124779

- [10] A. Rahman, S. Datta, and M. S. Lundstrom, "Theory of ballistic nanotransistors," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1853–1864, Sep. 2003. DOI: 10.1109/TED.2003.815366

- [11] S. Lee, C. Huang, D. Cohen-elias, B. J. Thibeault, W. J. Mitchell, V. Chobpattana, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "Highly Scalable Raised Source/Drain InAs Quantum Well MOSFETs Exhibiting  $I_{om}=482~\mu\text{A}/\mu\text{m}$  at  $I_{off}=100~\text{nA}/\mu\text{m}$  and  $V_{DD}=0.5~\text{V}$ ," *IEEE Electron Device Lett.*, vol. 35, no. 6, pp. 621–623, 2014. DOI: 10.1109/LED.2014.2317146

- $[12] \qquad T. \text{ Kim, D. Koh, C. Shin, W. Park, T. Orzali, C. Hobbs, W. P.} \\ \text{Maszara, and D. Kim, "}L_g = 80\text{-nm Trigate Quantum-Well} \\ \text{In}_{0.53}\text{Ga}_{0.47}\text{As Metal-Oxide-Semiconductor Field-Effect Transistors} \\ \text{With Al}_2\text{O}_3/\text{HfO}_2 \text{ Gate-Stack,"} \\ \text{IEEE Electron Device Lett., vol. 36,} \\ \text{no. 3, pp. 223–225, 2015. DOI: } 10.1109/\text{LED.2015.2393554} \\ \end{aligned}$

- [13] M. Radosavljevic, G. Dewey, D. Basu, J. Boardman, B. Chu-Kung, J. M. Fastenau, S. Kabehie, J. Kavalieros, V. Le, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, H. W. Then, and R. Chau, "Electrostatics improvement in 3-D tri-gate over ultra-thin body planar InGaAs quantum well field effect transistors with high-K gate dielectric and scaled gate-to-drain/gate-to-source separation," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2011, pp. 33.1.1–33.1.4. DOI: 10.1109/IEDM.2011.6131661

- [14] S. Kim, M. Yokoyama, R. Nakane, O. Ichikawa, T. Osada, M. Hata, M. Takenaka, and S. Takagi, "High performance sub-20-nm-channel-length extremely-thin body InAs-on-insulator Tri-gate MOSFETs with high short channel effect immunity and V<sub>th</sub> tunability," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2013, pp. 429–432. DOI: 10.1109/IEDM.2013.6724642

- [15] S. Lee, V. Chobpattana, C.-Y. Huang, B. J. Thibeault, W. Mitchell, S. Stemmer, a C. Gossard, and M. J. W. Rodwell, "Record  $I_{on}$  (0.50 mA/ $\mu$ m at  $V_{DD}=0.5$  V and  $I_{off}=100$  nA/ $\mu$ m) 25 nm-gate-length ZrO<sub>2</sub>/InAs/InAlAs MOSFETs," in Symp. VLSI Technol. Dig. Tech., Jun. 2014. DOI: 10.1109/VLSIT.2014.6894363

- [16] T. Kim, D. Kim, D. H. Koh, H. M. Kwon, R. H. Baek, D. Veksler, C. Huffman, K. Matthews, S. Oktyabrsky, A. Greene, Y. Ohsawa, A. Ko, H. Nakajima, M. Takahashi, T. Nishizuka, H. Ohtake, S. K. Banerjee, S. H. Shin, D. H. Ko, C. Kang, D. Gilmer, R. J. W. Hill, M. W, C. Hobbs, and P. D. Kirsch, "Sub-100 nm InGaAs Quantum-Well (QW) Tri-Gate MOSFETs with Al2O3 /HfO2 (EOT < 1 nm) for Low-Power Logic Applications," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2013, pp. 425–428, 2013. DOI: 10.1109/IEDM.2013.6724641

- [17] J. Lin, D. A. Antoniadis, and J. A. del Alamo, "Novel intrinsic and extrinsic engineering for high-performance high-density self-aligned InGaAs MOSFETs: Precise channel thickness control and sub-40-

- nm metal contacts," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2014, pp. 25.1.1–25.1.4. DOI: 10.1109/IEDM.2014.7047104

- [18] J. Lin, X. Zhao, T. Yu, D. A. Antoniadis, and J. A. del Alamo, "A new self-aligned quantum-well MOSFET architecture fabricated by a scalable tight-pitch process," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2013, pp. 16.2.1–16.2.4. DOI: 10.1109/IEDM.2013.6724640

- [19] M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, "Advanced high-K gate dielectric for high-performance short-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistors on silicon substrate for low power logic applications," in *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Dec. 2009, pp. 1–4. DOI: 10.1109/IEDM.2009.5424361

- [20] C. Y. Huang, S. Lee, V. Chobpattana, S. Stemmer, A. C. Gossard, B. Thibeault, W. Mitchell, and M. Rodwell, "Low Power III-V

- InGaAs MOSFETs Featuring InP Recessed Source/Drain Spacers with  $I_{on}=120~\mu A~/\mu m$  at  $I_{off}=1~nA/\mu m$  and  $V_{DS}=0.5~V,"$  in Proc. IEEE Int. Electron Device Meeting (IEDM), Dec. 2014, pp. 586–589. DOI: <math display="inline">10.1109/IEDM.2014.7047107

- [21] T. Kim, R. J. W. Hill, C. D. Young, D. Veksler, L. Morassi, S. Oktybrshky, J. Oh, C. Y. Kang, D. Kim, J. A. Alamo, C. Hobbs, P. D. Kirsch, and R. Jammy, "InAs Quantum-Well MOSFET ( $L_g = 100$  nm) with Record High  $g_m$ ,  $f_T$  and  $f_{max}$ ," in *Symp. VLSI Technol. Dig. Tech.*, Jun. 2012, pp. 179–180. DOI: 10.1109/VLSIT.2012.6242520

- [22] D.-H. Kim, J. A. del Alamo, D. A. Antoniadis, J. Li, J.-M. Kuo, P. Pinsukanjana, Y.-C. Kao, P. Chen, A. Papavasiliou, C. King, E. Regan, M. Urteaga, B. Brar, and T.-W. Kim, " $L_g = 60$  nm recessed  $In_{0.7}Ga_{0.3}As$  metal-oxide-semiconductor field-effect transistors with  $Al_2O_3$  insulator," *Appl. Phys. Lett.*, vol. 101, no. 22, p. 223507, 2012. DOI: 10.1063/1.4769230