## Vertical InAs nanowire MOSFETs with IDS = 1.34 mA/µm and gm = 1.19 mS/µm at VDS = 0.5 V

Persson, Karl-Magnus; Berg, Martin; Borg, Mattias; Wu, Jun; Sjöland, Henrik; Lind, Erik; Wernersson, Lars-Erik

Published in:

**IEEE Electron Device Letters**

10.1109/DRC.2012.6256966

2012

#### Link to publication

Citation for published version (APA):

Persson, K.-M., Berg, M., Borg, M., Wu, J., Sjöland, H., Lind, E., & Wernersson, L.-E. (2012). Vertical InAs nanowire MOSFETs with IDS = 1.34 mA/µm and gm = 1.19 mS/µm at VDS = 0.5 V. *IEEE Electron Device* Letters, 195-196. https://doi.org/10.1109/DRC.2012.6256966

Total number of authors:

### General rights

Unless other specific re-use rights are stated the following general rights apply: Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights

- Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

Download date: 17. Dec. 2025

# Vertical InAs Nanowire MOSFETs with $I_{DS} = 1.34$ mA/ $\mu$ m and $g_m = 1.19$ mS/ $\mu$ m at $V_{DS} = 0.5$ V

Karl-Magnus Persson, Martin Berg, Mattias Borg, Jun Wu, Henrik Sjöland, Erik Lind and Lars-Erik Wernersson

Department of Electrical- and Information Technology, Lund University, SE-223 63 Lund, Sweden phone: +46704804486, email: karl-magnus.persson@eit.lth.se

III-V MOSFETs are currently considered for extension of, or as an add-on to, the Si CMOS technology. Following the Si-technology evolution, it is attractive to consider advanced III-V transistor architectures with non-planar geometry and improved electrostatic control [1]. We report on vertical InAs single nanowire FETs with diameter of 45 nm diameter, integrated on Si substrates with  $L_G=200$  nm. The devices demonstrate normalized extrinsic  $g_m$  and  $I_{DS}$  of 1.34 S/mm and 1.19 A/mm, respectively, at a  $V_{DS}$  of 0.5 V, and with an onresistance of 321  $\Omega$ µm, all values normalized to the circumference. The improvements in  $g_m$  and  $I_{DS}$  as related to previous work [2] are attributed to the improved higk- $\kappa$  interface consisting of  $Al_2O_3/HfO_2$ , as well as to the nanowire source resistance, which is reduced by applying an inorganic spacer layer. The main performance limitation is identified as the drain resistance in the ungated top part of the wire. By scaling the NW diameter to 28 nm, we also observe subthreshold swing down to 80 mV/decade at 50 mV  $V_{DS}$ . However, the onresistance increases for the narrow wires to 75  $k\Omega$ µm, and the normalized current level is reduced as compared to the larger diameter wires.

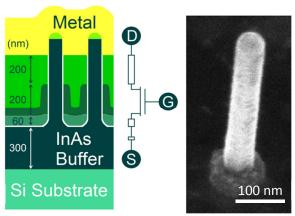

A 4" highly resistive Si wafer, which is overgrown with a 300-nm-thick InAs buffer layer, serves as sample substrates [3]. Electron-beam-lithography defined gold particles placed in arrays prior to epitaxial growth are made on  $2x2 \text{ cm}^2$  pieces. Each sample has 160 FETs, both single- and multi-wire devices, with RF compatible layout. High- $\kappa$  gate oxides are deposited with an ALD process consisting of 0.5 nm  $Al_2O_3$  at 250 °C and 6.5 nm  $HfO_2$  at 100 °C, directly after epitaxial nanowire growth. For device isolation and stray capacitance minimization, source mesas are etched out from the buffer layer. In a novel fabrication procedure, the first spacer layer, separating source and gate, is formed by plasma-enhanced-chemical-vapor-deposition of 60 nm  $Si_3N_4$ . The sputtered tungsten gate is defined using an etch mask and a dry-etch procedure. The top spacer layer separating gate and drain is made of a spin-coated organic film and has a thickness of 150-250 nm, making the ungated top part of the wire the largest fraction of the series resistance that limit the performance.

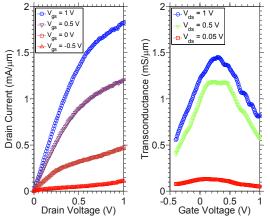

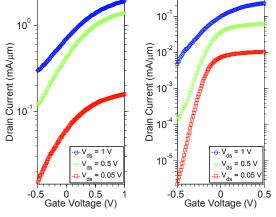

DC characterization is performed for single and multi NW InAs NW FETs, where the best single NW device of 45 nm diameter shows a normalized  $I_{DS}$  of 1.82 mA/ $\mu$ m and 1.34 mA/ $\mu$ m at a  $V_{GS}$  of 1.0 V and a  $V_{DS}$  of 1.0 V and 0.5 V, respectively. These devices also show a corresponding  $g_m$  of 1.45 mS/ $\mu$ m and 1.19 mS/ $\mu$ m at a  $V_{DS}$  of 1.0 V and 0.5 V, respectively. The  $V_t$  is extrapolated using the maximum transconductance method and determined to -0.27 at  $V_{ds}$  = 0.5 V. The device shows a low hysteresis of less than 5 mV at a  $V_{DS}$  of 0.5 V, most likely due to a low trap concentration within the low temperature deposited HfO<sub>2</sub> film. Devices scaled in diameter to 28 nm, with a 5.0-nm-thick Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> film, and with 96 wires in parallel show a normalized  $I_{DS}$  of 0.112 mA/ $\mu$ m, a transconductance of 0.154 mS/ $\mu$ m, and a  $V_t$  of -0.23 V at a  $V_{DS}$  of 0.5 V and within 0.5 V  $V_{GS}$ . While the performance is lower in the on-state, the subthreshold swing is greatly improved down to 80 mV/decade at a  $V_{DS}$  of 50 mV. Data for both samples is benchmarked in Table 1 [4], demonstrating good performance as compared to alternative implementations. S-parameter measurements of our RF devices with 45 nm in diameter, show that FETs consisting of 192 wires in parallel, operate with  $f_t$  = 18.5 GHz and  $f_{max}$  = 32.2 GHz. Although these values represent a two fold increase to previous published data for InAs NW FETs [5], the performance is still limited by parasitic contact pad capacitances, originating from the limitations of the optical lithography used.

- [1] J. A. del Alamo, Nature, vol. 479, no. 7373, pp. 317-323, Nov. 2011

- [2] C. Thelander et al., IEEE Electron Device Lett., vol. 29, no. 3, pp. 206-208, Mar. 2008

- [3] S. Gorji Ghalamestani et al., J. Crystal Growth., vol. 332, no. 1, pp. 12-16, Oct. 2011

- [4] A. Dey et al., IEEE Electron Device Lett., (Accepted for publication 2012)

- [5] S. Johansson et al., IEEE Trans. Microw. Theory Tech., vol. 59, no 10, Oct. 2011

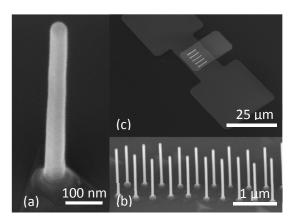

Fig 1. SEM images (30° tilt angle) of a single NW (a) and an array of NWs (b) after ALD as well as a 192 NW array with etched-out source mesa and sputtered W-gate-pad (c).

Fig 2. Schematic crosssection showing the different layer thicknesses in the fabricated device.

Fig 3. SEM image (30° tilt angle) of a single NW after the gate length definition.

Fig 4. Normalized  $I_{DS}$  vs  $V_{DS}$  for a single 45 nm NW FET. Fig 5. Normalized  $g_m$  vs  $V_{GS}$  for a single 45 nm NW FET.

Fig 6. Normalized  $I_{DS}$  vs  $V_{GS}$  for a single 45 nm NW FET. Fig 7. Normalized  $I_{DS}$  vs  $V_G$  for a 28 nm NW array FET.

| 0.25<br>V <sub>gs</sub> = 0.5 V<br>V <sub>gs</sub> = 0.5 V<br>0.2 | 0.5                                                                                                      |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Drain Current (mA/μm)  0.15- 0.15- 0.01- 0.05-                    | Lauscoonductance (mS/m)  1.0 ausconductance (mS/m)  1.0 ausconductance (mS/m)  1.0 ausconductance (mS/m) |

| 0<br>0 0.5 1<br>Drain Voltage (V)                                 | -0.5 0 0.5<br>Gate Voltage (V)                                                                           |

Fig 8. Normalized  $I_{DS}$  vs  $V_{DS}$  for a 28 nm NW array FET. Fig 9. Normalized  $g_m$  vs  $V_{GS}$  for a 28 nm NW array FET.

| D<br>(nm | L <sub>G</sub> (nm) |       | g <sub>m,max</sub><br>(mS/µm) | SS<br>(mV/dec) | Tech        | Reference                              |

|----------|---------------------|-------|-------------------------------|----------------|-------------|----------------------------------------|

| 28       | 200                 | 0.058 | 0.15                          | 140            | vertical NW | This work                              |

| 45       | 200                 | 0.67  | 1.19                          | 560            | vertical NW | This work                              |

| 15       | 100                 | 0.6   | 1.23                          | 140            | lateral NW  | A. Dey et al<br>EDL 2012               |

| 10       | 30                  | 0.7   | 1.9                           | 80             | HEMT        | DH. Kim et al<br>EDL 2008              |

| 30       | 250                 | 0.12  | 0.56                          | 120            | FinFET      | J. J. Gu et al<br>APL 2011             |

| 10       | 75                  | 0.55  | 1.75                          | 95             | QWFET       | M. Radosavljevic et<br>al<br>IEDM 2009 |

| 25       | 170                 | 0.4   | 0.8                           | 260            | radial NW   | X. Jiang et al<br>Nano Lett 2007       |

| 13       | 230                 | 0.9   | 1.72                          | 180            | XOI         | K. Takei et al<br>APL 2011             |

Table 1. Data benchmark for this work and other high performance technologies at a  $V_{DS}$  of 0.5 V and a  $V_{OD}$  of 0.5 V