# Low-frequency noise in vertical InAs nanowire FETs

Persson, Karl-Magnus; Lind, Erik; Dey, Anil; Thelander, Claes; Sjöland, Henrik; Wernersson, Lars-Erik

Published in:

**IEEE Electron Device Letters**

DOI:

10.1109/LED.2010.2043637

2010

## Link to publication

Citation for published version (APA):

Persson, K.-M., Lind, E., Dey, A., Thelander, C., Sjöland, H., & Wernersson, L.-E. (2010). Low-frequency noise in vertical InAs nanowire FETs. *IEEE Electron Device Letters*, *31*(5), 428-430. https://doi.org/10.1109/LED.2010.2043637

Total number of authors:

## General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 19. Dec. 2025

# Low-Frequency Noise in Vertical InAs Nanowire FETs

Karl-Magnus Persson<sup>1</sup>, Erik Lind<sup>2</sup>, Anil W Dey<sup>1</sup>, Claes Thelander<sup>2</sup>, Henrik Sjöland<sup>1</sup>, and Lars-Erik Wernersson<sup>1</sup>

Abstract— This paper presents DC characteristics and low-frequency noise (LFN) measurements on single vertical InAs nanowire MOSFETs with 35 nm gate length and HfO<sub>2</sub> high- $\kappa$  dielectric. The average normalized transconductance for three devices is 0.16 S/mm with a subthreshold slope of 130 mV/decade. At 10 Hz the normalized noise power  $S_I/I_d^2$  measures  $7.3 \times 10^{-7}$  Hz<sup>1</sup>. Moreover, the material dependent Hooge's parameter at room-temperature is estimated to  $4.2 \times 10^{-3}$ .

Index Terms—FET, flicker noise, InAs, nanowire (NW).

#### I. INTRODUCTION

O increase the drive currents in scaled MOSFETs, A alternatives to the Si technology are considered. A vertical MOSFET based on InAs nanowires (NWs) is one example of a promising extension, or add-on, to the Si CMOS platform. InAs has a high electron mobility, a high saturation velocity, and low contact resistance [1]. The nanowire geometry also offers electrostatic advantages using a wrap-around gate, providing better control of the channel potential. Good DC performance of vertical InAs NW transistors based on arrays of nanowires with 50 nm gate length has been demonstrated [2], with  $g_m = 0.5$  S/mm and a subthreshold slope of 90 mV/decade. We have recently also investigated the radio frequency (RF) performance of similar InAs nanowire FETs [3]. Here we present data of the DC and 1/f characteristic for FETs based on individual vertical InAs NWs. Up to now, several papers of FETs based on individual lateral NWs have been published [4][5], but only a few in the vertical geometry.

In recent years, much effort has been put into characterization of low-frequency noise (LFN) of MOSFETs as the noise spectral density tends to increase linearly with the scaling factor [6], making it a major concern for analog and RF applications. Ultra-scaled devices not only suffer from high noise levels, but also large disparity between devices processed in parallel [6][7]. In MOS structures, flicker noise, also known as 1/f-noise, has been shown to dominate the noise at low frequencies. Flicker noise stems from trapping and

Manuscript received on 10 November 2009. This work has been supported by the Swedish Foundation for Strategic Research, the Swedish Research Council, the Knut and Alice Wallenberg Foundation, and EU through the NODE project, No. 015783.

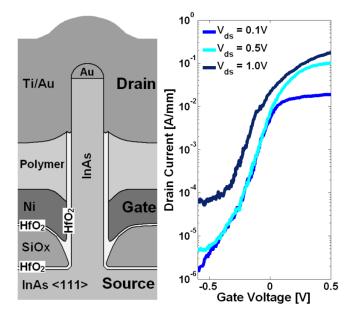

Fig. 1. (a) Schematic cross-section of a NW FET. (b) Device transfer characteristics of an individual NW FET (40 nm diameter, 35 nm gate length) at  $V_{ds}=0.1~\rm{V}, 0.5~\rm{V},$  and  $1.0~\rm{V}.$

detrapping events related to the channel, the oxide and the interface. This paper presents, to the best of our knowledge, the first 1/f noise characterization of a III-V MOSFET including high-κ integration in a non-planar geometry. It is demonstrated that similar noise performance can be achieved as in advanced Si device architectures. Compared to previous LFN studies of InAs NW FETs [8], our study incorporate wires with high-κ dielectric. The study also differs as the wires have shorter gate length and include characterization of the subthreshold regime.

## II. DEVICE FABRICATION

The NW FETs are fabricated from epitaxially grown InAs nanowires with a diameter of 40 nm, grown on an <111>-B InAs substrate [2, 9]. The wires are Sn-doped with a molar fraction of 3.49x10<sup>-8</sup>. The source to gate spacer layer consists of evaporated SiO<sub>x</sub>. During evaporation, the sample is rotated and the wires are slightly tilted to the material source to avoid shadowing of the base. The buildup of small quantitys of porous SiO<sub>x</sub> on the side facets of the wires is removed in a following wet-etch step, leaving the profile shown in the

Department of Electrical- and Information Technologies, Lund University, Box 118 S-221 00, Lund, Sweden.

Department of Solid State Physics, Lund University, Box 118 S-221 00, Lund, Sweden (email: karl-magnus.persson@eit.lth.se).

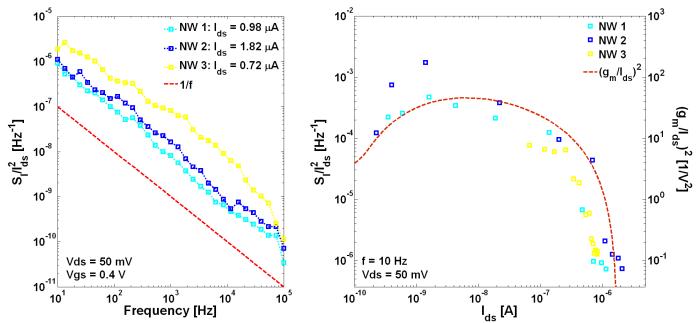

Fig. 2. (a) CNSD for three individual NW FETs. 1/f is plotted for reference. (b) CNSD (squares) for three devices and  $g_m^2/I_{ds}^2$  (line) for NW 2 at  $V_{ds} = 50$  mV, plotted versus the drain current for f = 10 Hz.

schematic cross-section of the device in Figure 1a. A dielectric film (HfO<sub>2</sub>) is deposited both before and after the  $SiO_x$ , utilizing atomic layer deposition, for total a thickness of 7 nm. The Ni gate is evaporated in a similar fashion as the  $SiO_2$  and the gate length is set by the thickness of the evaporated film. When spin-coating the sample to fabricate the gate to drain separation layer, the film gets thicker around the wires. The final thickness of the polymer is set by a following dry-etch procedure with a typical variation in the range of 100-200 nm, making the structure more or less asymmetrical. We here present data for a gate length of 35 nm.

## III. MEASUREMENTS

DC characteristics for one device is shown in Figure 1b. The maximum on-current at  $V_{ds}=0.5$  V reaches 0.1 A/mm (where the width is set as the NW circumference) for  $V_g=0.5$  V. For three different individual NW FETs, values for the threshold voltage,  $V_T$ , was determined to be between -0.1 and 0.0 V for  $V_{ds}=0.5$  V. At the same bias, the subthreshold slope, averaged over two decades, are 149, 119, and 121 mV/decade. The maximum transconductance for each wire was 157, 257, and 67 mS/mm, respectively.

The LFN measurement setup consisted of a Stanford SR830 lock-in amplifier measuring the noise current spectrum from the source terminal of the NW FET. To increase the sensitivity, the source current was pre-amplified through a Stanford SR570 low noise amplifier (LNA). The measurements were performed in the range of 10 Hz to 100 kHz at room temperature. The drain-source voltage was set to 50 mV in the presented data, but we also conducted measurements with various  $V_{ds}$ , however without observing any significant differences.

#### IV. RESULTS AND DISCUSSION

As compared to previously published data [2, 9], we note a larger subthreshold slope in these devices, 120 mV/decade as compared to 80 mV/decade. This can mainly be attributed to insufficient scaling of the wire diameter for this gate length, but also a high  $D_{it}$ . The threshold shift seen at high bias voltage is caused by a combination of impact ionization and band to band tunneling due to the narrow bandwidth of InAs, and band bending related to the comparably wide wire diameter [10]. While there is room for optimization of the structure, this study is one of the first on the properties of high- $\kappa$  on non-planar III/V structures [11].

LFN was measured for single NW FETs and the normalized current noise spectral density (CNSD),  $S_{l}/I_{ds}^{2}$ , for three different FETs is shown in Figure 2a at  $V_{gs} = 0.4$  V. We note a 1/f' dependence with the frequency exponent  $\gamma$  being equal to 1.05, 0.99, and 1.03 for NW 1, NW 2, and NW 3, respectively. The exponent being close to unity indicates an even distribution of slow and fast traps [12]. The 1/f behavior was unchanged for  $V_{gs}$  smaller than 0.4 V, even in the subthreshold region ( $V_{gs} = -0.2$ V), with  $\gamma$  kept close to unity. This indicates that several traps are involved in the noise process. We also note that the noise level uniformity is fairly good with a variation, averaged over frequency, within a factor of 5. Other studies on advanced structures with comparable gate length, though including more measured devices, show up to five orders of magnitude in variation [7]. As a reference, we also measured the LFN for devices with varying number of nanowires (7-19), where we observed the CNSD level to decrease slightly as the number of wires was increased.

In Figure 2b, CNSD for NW 1 and 2 is plotted versus the drain current at a constant frequency of 10 Hz. It can be seen that the CNSD has strong dependence on the square of the normalized transconductance,  $g_m^2/I_{ds}^2$ , which is in line with the

number fluctuation theory, pointing towards domination of trapping/detrapping events at the InAs/HfO<sub>2</sub> interface [12]. The CNSD reaches down to 7.3x10<sup>-7</sup> Hz<sup>-1</sup> at a drain current of 1.2 µA. As a comparison, a study of LFN in Si NWs, with a 55 nm gate length and SiO<sub>2</sub> gate oxide, show a normalized CNSD at 10 Hz (above threshold and at roughly 6 µA) in the order of 1x10<sup>-7</sup> Hz<sup>-1</sup> [7]. A more recent study of similar Si NWs show values of about  $5 \times 10^{-10} \text{ Hz}^{-1}$  for  $L_g = 350 \text{ nm}$  at 10 Hz and 1 μA [13]. From a LFN temperature study of lateral InAs NWs with SiO<sub>2</sub> gate oxide (back-gated) and 2 µm gate length, we extrapolated the minimum normalized CNSD at 10 Hz (data taken at 250 K), to be about 1x10<sup>-7</sup> Hz<sup>-1</sup> [8]. Another study of an AlSb/InAs HEMT show, for  $L_g = 100$  nm, by us extrapolated value at 10 Hz, a minimum of  $3x10^{-10}$  Hz<sup>-1</sup> [14]. While our device is not matching the planar heterostrucutre FET in noise level, our InAs NW MOSFETs have similar noise level as advanced Si transistors with comparable gate length or long-gated InAs NW FETs. For optimized and integrated devices, each transistor will likely consist of several parallel wires to ensure sufficient drive current, and a similar noise-behavior in a lateral and a vertical geometry may be expected.

Neither number nor mobility fluctuations perfectly describe the noise over the entire bias range [12]. Mobility fluctuations or correlated mobility-number fluctuations may however be considered at high gate overdrive voltages. Using the measured data above threshold, Hooge's prarameter,  $\alpha_H$ , can be determined. Hooge's parameter depends on material and crystal quality and is a good measure to evaluate the properties of advanced structures and exotic materials [6]. The parameter is found from Eq. (1)-(3).

$$S_1/I_{ds}^2 = \alpha_H/(N * f^{\gamma})$$

(1)

$$N = |V_{\sigma s} - V_{T}| *C_{\sigma} L_{\sigma} / e$$

(2)

$$C_{g} = 2\pi\varepsilon_{r}\varepsilon_{0}/\ln\left((r + t_{ox})/r\right)$$

(3)

Here, N is the total number of charge carriers in the channel,  $C_g$  is the gate capacitance per unit length,  $L_g$  is the gate length, e is the electronic charge, r is the NW radius,  $t_{ox}$  is the gate oxide thickness,  $\varepsilon_0$  is the permittivity of vacuum, and  $\varepsilon_r$  is the relative permittivity of HfO<sub>2</sub>. Using (1)-(3), the average for device 1 and 2 in Figure 2b, (for  $V_{gs}=0.2$  and 0.4 V at 10 Hz) the Hooge's parameter is determined to  $4.2 \times 10^{-3}$ . This can be compared with the minimum obtained room temperature value for the study of a lateral InAs NW FET device [8], corresponding to  $8.4 \times 10^{-3}$ . This indicates that the addition of a high- $\kappa$  oxide on an InAs surface does not seriously degrade the LFN performance

# V. CONCLUSION

We report DC characteristics and low frequency noise of vertical InAs NW MOSFETs with HfO2 high-κ oxide based on individual nanowires. It can be determined that the *1/f*-noise at low current levels is caused by number fluctuations due to trapping and detrapping events at the gate oxide interface. The exponent of the *1/f*-curve being close to unity

suggests an even distribution between slow and fast traps. There is also a relatively small deviation between samples. Comparing our values to other studies of advanced structures and/or materials, the noise level presented is in the same order. Evaluating the Hooge's parameter, which accounts for the quality in the channel material and gate length, we deduce a value of  $4.2 \times 10^{-3}$ .

#### ACKNOWLEDGEMENT

The authors would like to thank Philippe Caroff and Linus E. Fröberg for growth respectively pregrowth of the samples.

#### REFERENCES

- A. M. Crook, et al., "Low resistance, nonalloyed Ohmic contacts to InGaAs," Appl. Phys., vol. 91, no. 19, pp. 192114-192114-3, Nov. 2007.

- [2] C. Thelander, L. E. Froberg, C. Rehnstedt, L. Samuelson, and L.-E. Wernersson, "Vertical Enhancement-Mode InAs Nanowire Field-Effect Transistor With 50-nm Wrap Gate," *IEEE Electron Device Lett.*, vol. 29, no. 3, pp. 206-208, Mar. 2008.

- [3] M. Egard, et al., "InAs Nanowire Wrap Gate Transistors With ft > 7 GHz and fmax > 20 GHz," Nano Lett, 2009 (accepted).

- [4] K. Blekker, Q. T. Do, A. Matiss, W. Prost, and F. J. Tegude, "High Frequency Characterization of Single InAs Nanowire Field-Effect Transistors," 20th International Conference on Indium Phosphide and Related Materials, pp. 1-3, 2008.

- [5] Y. Tian, et al., "New Self-Aligned Silicon Nanowire Transistors on Bulk Substrate Fabricated by Epi-Free Compatible CMOS Technology: Process Integration, Experimental Characterization of Carrier Transport and Low Frequency noise," *IEEE International Electron Devices Meeting*, pp. 895-898, 2007.

- [6] E. Simoen and C. Claeys, "On the flicker noise in submicron silicon MOSFETs," Solid-State Electronics, vol. 43, no. 5, pp. 865-882, 1999.

- [7] J. Zhuge, et al., "Investigation of Low-Frequency Noise in Silicon Nanowire MOSFETs," *IEEE Electron Device Lett.*, vol. 30, no. 1, pp. 57-60, Jan. 2009.

- [8] M. R. Sakr and X. P. A. Gao, "Temperature dependence of the low frequency noise in indium arsenide nanowire transistors," *App. Phys.*, vol. 93, no. 20, pp. 203503-203503-3, Oct. 2008.

- [9] C. Thelander, et al., "Development of a Vertical Wrap-Gated InAs FET," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 3030-3036, Nov. 2008.

- [10] L. E. Froberg, et al., "Heterostructure Barriers in Wrap Gated Nanowire FETs," *IEEE Electron Device Lett*, vol. 29, no. 9, pp. 981-983, Sep. 2008.

- [11] S. Roddaro, et al., "InAs nanowire metal-oxide-semiconductor capacitors," Appl. Phys., vol. 92, no. 25, pp. 253509-253512, June 2008.

- [12] M. von Haartman and M. Östling, Low-Frequency Noise in Advanced MOS Devices. Springer, 2007.

- [13] C. Wei, et al., "Impact of Gate Electrodes on 1/f Noise of Gate-All-Around Silicon Nanowire Transistors," *IEEE Electron Device Lett.*, vol. 30, no. 10, pp. 1081-1083, Oct. 2009.

- [14] W. Kruppa, et al., "Low-Frequency Noise in AlSb/InAs and Related HEMTs," *IEEE Trans. Electron Devices*, vol. 54, no. 5, pp. 1193-1202, May 2007.