# High-Current GaSb/InAs(Sb) Nanowire Tunnel Field-Effect Transistors

Dey, Anil; Borg, Mattias; Ganjipour, Bahram; Ek, Martin; Dick Thelander, Kimberly; Lind, Erik; Thelander, Claes; Wernersson, Lars-Erik

Published in:

**IEEE Electron Device Letters**

DOI:

10.1109/LED.2012.2234078

2013

# Link to publication

Citation for published version (APA):

Dey, A., Borg, M., Ganjipour, B., Ek, M., Dick Thelander, K., Lind, E., Thelander, C., & Wernersson, L.-E. (2013). High-Current GaSb/InAs(Sb) Nanowire Tunnel Field-Effect Transistors. *IEEE Electron Device Letters*, *34*(2), 211-213. https://doi.org/10.1109/LED.2012.2234078

Total number of authors:

# General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 18. Dec. 2025

1

# High Current GaSb/InAs(Sb) Nanowire Tunnel Field-Effect Transistors

Anil W. Dey, B. Mattias Borg, Bahram Ganjipour, Martin Ek, Kimberly A. Dick, Erik Lind, Claes Thelander and Lars-Erik Wernersson

Abstract—We present electrical characterization of GaSb/InAs(Sb) nanowire tunnel field-effect transistors. The broken band alignment of the GaSb/InAs(Sb) heterostructure is exploited to allow for inter-band tunneling without a barrier, leading to high on-current levels. We report a maximum drive current of 310  $\mu$ A/ $\mu$ m at  $V_{DS}=0.5$  V. Devices with scaled gate oxides display transconductances up to  $g_m=250$  mS/mm at  $V_{DS}=300$  mV, normalized to the nanowire circumference at the axial heterojunction.

Index Terms—Tunnel field-effect transistors (TFET), broken gap, InAs, GaSb, III-V

### I. INTRODUCTION

HE rapid development of semiconductor technology during the last few decades has resulted in high-performance transistors in both Si and III-V semiconductor technologies [1], [2]. However, MOSFETs suffer from a fundamental lower limit of 60 mV/decade subthreshold swing (SS) at room temperature, and a corresponding lower limit of the power dissipation at a given threshold voltage and on-current level. There is a demand for devices with very steep inverse subthreshold slopes in order to maintain a high  $I_{ON}/I_{OFF}$  ratio while lowering the supply voltage. For this reason, steep-slope devices, such as tunnel field-effect transistors (TFETs), are now being studied in great detail in different material systems. Recent reports on devices with SS below 60 mV/decade [3]-[5], however show that the devices suffer from low on-current levels. Furthermore, there are often difficulties in integrating high- $\kappa$  dielectrics with III-Vs to achieve optimized device electrostatics [6]. Since the current in a p-i-n TFET device relies on charge carriers tunneling through a barrier at a given limited probability, the on-current is invariably lower than for a corresponding MOSFET device [7], [8]. As an alternative to conventional designs, we here focus on the GaSb/InAs(Sb) heterostructure, which forms a broken type II band alignment, and thus allows for inter-band tunneling without a barrier.

Based on highly doped  $p^+/n^+$  junctions of this particular heterostructure, we have recently demonstrated Esaki diodes with reverse-bias current densities up to  $I_{reverse} = 3.6$  MA/cm<sup>2</sup> [9]. Here we investigate the TFET properties of such heterostructures, with a  $p^+/n$  doping profile and it is found that such devices exhibit correspondingly high on-current levels. Furthermore, we report on the temperature behavior of such devices as well as the effect of various device geometries.

## II. MATERIALS AND DEVICE FABRICATION

GaSb/InAs(Sb) nanowires were grown from Au aerosols on a GaAs substrate by means of metalorganic vapor phase epitaxy. A short GaAs stem was first grown in order to facilitate

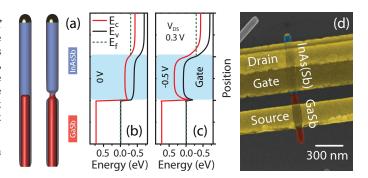

Fig. 1. (a) Schematics of the two types of nanowires used in the study. (b, c) Simulated band structures of an ideal device at 300 K including an exponentially graded Sb composition from 0.4 to 0.1 over 10 nm at the interface at  $V_{DS}=300$  mV and at (b)  $V_{GS}=0$  V and (c)  $V_{GS}=-0.5$  V. Note that applied gate voltage and semiconductor potential do not follow as 1:1 in the measured devices. (d) A colorized scanning electron microscopy image of a completed device. Note that the apparent nanowire diameter is here increased by the HfO<sub>2</sub> film, and that gate overlap/underlap varies between devices as discussed in the text below.

the nucleation of the GaSb segment [10], into which Zn (Zn/Ga molar flow fraction = 0.56) is also introduced to reduce the series resistance [9]. Subsequently, an unintentionally doped axial InAs(Sb) segment is grown which also forms a thin,  $\sim$ 5 nm, shell around the GaSb segment. This shell aids in reducing the series resistance to the source electrode and allows for a one-step fabrication process for the source and drain electrodes. In order to minimize a potential leakage current in the shell, and to reduce the cross-sectional area of the conducting channel, the nanowires were annealed in H<sub>2</sub> during the final stage of the growth, forming a constriction at the axial GaSb/InAs(Sb) heterointerface [11]. As a reference, nanowires were also grown where the Zn-doping and H<sub>2</sub> annealing were omitted. Assuming a hole mobility between 70 cm<sup>2</sup>/Vs (calculated from [12]) and 700 cm<sup>2</sup>/Vs [1], and a measured resistivity of 7.1 m $\Omega$  · cm [9], we estimate the carrier concentration in the GaSb segment to be in the range  $1.3 \cdot 10^{18}$  -  $1.3 \cdot 10^{19}$  cm<sup>-3</sup>. A corresponding estimate for the InAs(Sb) segments yields a carrier concentration of  $6 \cdot 10^{17}$  $cm^{-3}$  [13].

After the growth, the nanowires were dry-deposited onto prepatterned Si chips with a 100-nm-thick thermally grown SiO<sub>2</sub>. Source and drain electrodes were defined by electron beam lithography (EBL) followed by thermal evaporation of Ni and Au. A lift-off window for the high- $\kappa$  dielectric was defined by EBL, followed by an atomic layer deposition of an Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bi-layer (2/70 cycles) both deposited at 100 °C corresponding to an EOT of 2 nm, assuming  $\epsilon_r$  = 15. As a final step, a Ni/Au top-gate was formed. All room temperature

measurements were carried out in darkness and vacuum.

## III. RESULTS AND DISCUSSION

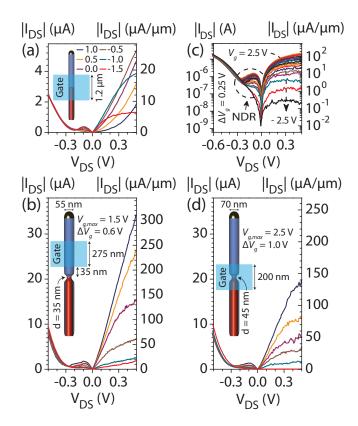

Fig. 2a presents the output characteristic for a reference device without a constriction at the axial heterointerface (as displayed in the schematics in Fig. 1a) and without Zn doping in the GaSb segment. In this device, carrier transport can occur along the InAs(Sb) shell and across the GaSb/InAs(Sb) heterojunction simultaneously due to the ambipolarity of the core-shell system [12]. At negative gate bias, the InAs(Sb) is depleted of electrons and the majority of the current is forced through the heterojunction. At positive gate bias, electrons accumulate at the surface, enabling n-type conduction along the shell with reduced tunneling. It is not possible to turn this device off.

Fig. 2b displays the output characteristic for a device with a Zn-doped GaSb segment and where a constriction has been formed at the axial heterointerface (d = 35 nm  $\pm$  5 nm). We calculate an on-current of 91  $\mu$ A/ $\mu$ m  $\pm$  13  $\mu$ A/ $\mu$ m at  $V_{DS}$  =  $V_{GS}$ - $V_T$  = 0.5 V (normalized to the nanowire circumference,  $\pi \cdot d$ ), and a maximum on-current of 310  $\mu$ A/ $\mu$ m  $\pm$  45  $\mu$ A/ $\mu$ m ( $V_{DS}$  = 0.5 V,  $V_{GS}$ - $V_T$  = 2 V), corresponding to  $R_{ON}$  = 1.57  $\Omega$  · mm, exceeding the drive currents of e.g. staggered AlGaSb-InAs TFETs [6].

As illustrated, the device in Fig. 2b has a 35 nm gate underlap to the heterojunction. In an ideal case, this would constitute a tunnel junction integrated in series with an InAs(Sb) MOS-FET. Such a tunnel junction is normally open for conduction due to the broken gap, and the current is modulated by the gate-action imposed on the InAs(Sb) segment. In the off-state, the device will suffer from the ungated segment, allowing tunneling across the heterostructure. Minority carriers (holes) injected from the drain may also accumulate and become trapped under the gate due to a barrier in the valence band to the GaSb.

The output characteristics of a device where the gate overlaps the heterojunction is included in Fig. 2c & d. The better off-state device performance we attribute to two effects; (i) the improved electrostatics at the heterojunction, gating the constriction rather than the thicker InAs(Sb), in agreement with the results of Tomioka et al. [5] and (ii) the device design layout itself as discussed next. For the device in Fig 2c & d, where the gate overlaps the heterointerface, we argue that in the on-state, the bands in the GaSb and the InAs(Sb) bend downwards. The bands are likely more easily modulated in the InAs(Sb) segment but some modulation of the GaSb is also expected. This may compromise the on-state by forming a barrier in the valence band in the GaSb segment, and reduce the probability of inter-band tunneling. However, Fermi level movement in GaSb-based MOS-structures is typically difficult due to the high number of acceptor-like interface traps  $(D_{it})$ between GaSb and high- $\kappa$  dielectrics [14]. In addition, the high Zn-doping level of the GaSb should lead to a limited movement of the bands on the GaSb side. For this reason, we argue that a device with a gate overlap better cuts off the tunneling path at the source heterojunction, which is otherwise open for an underlapping device (Fig. 2b). Furthermore, the

Fig. 2. Room temperature output characteristics of different TFET structures (reverse biased with GaSb grounded) with data normalized with respect to the circumference of the constriction. (a)  $I_{DS}$ - $V_{DS}$  sweep for an undoped nanowire without a constriction (d = 65 nm). (b-d) Output characteristics for TFET structures with a constriction and Zn-doped GaSb segment. (b) 35 nm gate underlap and 35 nm diameter at the GaSb/InAs(Sb) heterointerface. (c-d) 120 nm gate overlap and 45 nm diameter at the heterointerface constriction.

improved electrostatics at the constriction may lead to a better gate response. However, the devices are sensitive to measurement history, charging and hysteresis effects which makes the analysis somewhat challenging, e.g. determining a well-defined threshold voltage. The devices presented above show the extremes of a number of devices studied.

Evaluating the negative differential resistance region in the underlapping device, we calculate a maximum peak-to-valley current ratio of 3 with a maximum peak-current of 240 kA/cm<sup>2</sup> (forward biased with the InAs(Sb) segment grounded). We observe that  $V_P$  remains constant, or moves to *slightly higher*  $V_{DS}$  bias with increasing gate bias. In the ideal case of a gated resistance (MOSFET) integrated in series with a passive tunnel junction we expect  $V_P$  to move to lower  $V_{DS}$  values with increasing gate bias. The lack thereof indicates that the band alignment at the tunnel junction is affected by the gate.

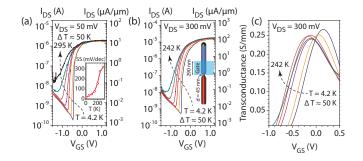

Fig. 3a & b display the transfer characteristic of a device where the EOT is scaled to 1.3 nm and the gate has been aligned to the heterointerface ( $\sim$  5nm overlap), with  $L_G$  = 290 nm. We calculate an on-current of 62  $\mu$ A/ $\mu$ m at  $V_{DS}$  = 0.3 V and  $V_{GS}$ - $V_T$  = 0.5 V,  $V_T$  = -0.51 V, and a maximum oncurrent of 130  $\mu$ A/ $\mu$ m ( $V_{DS}$  = 0.3 V,  $V_{GS}$ - $V_T$  = 1.75 V). The drain-induced barrier lowering was determined between  $V_{DS}$  = 0.05 and 0.3 V to be 280 mV/V. The maximum  $I_{ON}/I_{OFF}$  ratio increases from 143 at RT to 10<sup>4</sup> at 4.2 K and the SS decreases with temperature from 320 mV/decade at 295 K

Fig. 3. Electrical data for a nanowire TFET, d = 45 nm, where the gate oxide thickness is scaled to 5 cycles of Al<sub>2</sub>O<sub>3</sub> and 50 cycles of HfO<sub>2</sub>. The data is normalized to the constriction circumference. (a) Temperature dependent  $I_{DS}$ - $V_{GS}$  characteristics at  $V_{DS}$  = 50 mV from 4.2 K up to 295 K in increments of approximately 50 K. The inset shows the subthreshold swing as a function of temperature. (b) Temperature dependent  $I_{DS}$ - $V_{GS}$  characteristics and (c) transconductance at  $V_{DS}$  = 300 mV from 4.2 K to 242 K,  $\Delta$ T  $\approx$  50 K.

to 17 mV/decade at 4.2 K as seen in the inset of Fig. 3a. Similar values have been reported in other III-V TFET devices [15]. The temperature dependent SS is likely a result of trapassisted tunneling via the high  $D_{it}$  at the high- $\kappa$ /semiconductor interface. The determined activation energy, when reverse-biased, in the off-state from Fig. 3a (not shown) corresponds to the band gap of  $InAs_{0.9}Sb_{0.1}$  (0.27 eV). Furthermore, the onset of a temperature-independent ambipolar current is also evident in Fig. 3a & b, most likely due to band-to-band tunneling at the gate-drain junction related to the narrow band gap of the InAs(Sb). The temperature dependence of the valley current (forward-biased with InAs(Sb) grounded, not shown) suggests activation energies well-below  $E_g/2$  of InAs(Sb) indicating that trap-assisted tunneling is limiting the off-state performance.

Fig. 3c displays the temperature dependent transconductance at  $V_{DS}$  = 300 mV and the maximum extrinsic transconductance is extracted at 250 mS/mm ( $V_{GS}$ - $V_T$  = 0.5 V). The transconductance is nearly temperature independent, suggesting that the temperature dependent scattering mechanisms are not limiting the on-state of the device. In order to improve the off-state characteristics we propose two approaches; (i) increasing the band gap of the material in the drain by replacing InAs(Sb) with e.g. InGaAs to decrease the bandto-band tunneling at the gate-drain junction, (ii) reducing trap assisted tunneling by surface pretreatment/passivation and/or further improving the high- $\kappa$  quality, by e.g. higher deposition temperatures, to lower the SS. To increase the on-current further we suggest a higher doping of Zn in the GaSb to maintain a low-ohmic junction when gating the heterointerface as well as reducing the series resistance.

## IV. CONCLUSIONS

In this paper, experimental data for GaSb/InAs(Sb) tunnel field-effect transistors are presented, demonstrating high current densities attributed to the broken type II band alignment. These devices show on-currents of 310  $\mu$ A/ $\mu$ m ( $R_{ON}=1.6~\Omega$ · mm). Devices with a scaled gate oxide display a maximum extrinsic transconductance of 250 mS/mm at  $V_{DS}=300$  mV. The inverse subthreshold slope at room temperature is 320 mV/decade at  $V_{DS}=50$  mV and is likely limited by a high  $D_{it}$  at the high- $\kappa$ /semiconductor interface. At this point, the

minimum value of the off-current is limited by the narrow band gap of InAs(Sb).

### ACKNOWLEDGEMENTS

This work was supported in part by the Swedish Foundation for Strategic Research (SSF), by the Swedish Research Council (VR), by VINNOVA, by The Nanometer Structure Consortium at Lund University, and by the Knut and Alice Wallenberg Foundation.

#### REFERENCES

- J. A. del Alamo, "Nanometre-scale electronics with III-V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317–323, 2011.

H. J. Cho et al., "Bulk planar 20nm high-k/metal gate CMOS technology

- [2] H. J. Cho et al., "Bulk planar 20nm high-k/metal gate CMOS technology platform for low power and high performance applications," in *IEDM Tech. Dig.*, pp. 15.1.1–15.1.4, 2011.

- [3] G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, "Fabrication, characterization, and physics of III-V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing," in *IEDM Tech. Dig.*, pp. 33.6.1–33.6.4, 2011.

- [4] F. Mayer, C. Le Royer, J. F. Damlencourt, K. Romanjek, F. Andrieu, C. Tabone, B. Previtali, and S. Deleonibus, "Impact of SOI, Si<sub>1-x</sub>Ge<sub>x</sub>OI and GeOI substrates on CMOS compatible Tunnel FET performance," in *IEDM Tech. Dig.*, pp. 1–5, 2008.

- [5] K. Tomioka, M. Yoshimura, and T. Fukui, "Steep-slope tunnel field-effect transistors using III-V nanowire/Si heterojunction," in *Symposium on VLSI Technology*, pp. 47–48, 2012.

- [6] L. Rui, L. Yeqing, Z. Guangle, L. Qingmin, C. Soo Doo, T. Vasen, H. Wan Sik, Z. Qin, P. Fay, T. Kosel, M. Wistey, X. Huili, and A. Seabaugh, "AlGaSb/InAs Tunnel Field-Effect Transistor With On-Current of 78 μA/μm at 0.5 V," *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 363–365, 2012.

- [7] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329–337, 2011.

- [8] K. E. Moselund, H. Schmid, C. Bessire, M. T. Björk, H. Ghoneim, and H. Riel, "InAs-Si Nanowire Heterojunction Tunnel FETs," *IEEE Electron Device Lett.*, vol. PP, no. 99, pp. 1–3, 2012.

- [9] B. M. Borg, M. Ek, B. Ganjipour, A. W. Dey, K. A. Dick, L.-E. Wernersson, and C. Thelander, "Influence of doping on the electronic transport in GaSb/InAs(Sb) nanowire tunnel devices," *Appl. Phys. Lett.*, vol. 101, no. 4, p. 043508, 2012.

- [10] M. Jeppsson, K. A. Dick, J. B. Wagner, P. Caroff, K. Deppert, L. Samuel-son, and L.-E. Wernersson, "GaAs/GaSb nanowire heterostructures grown by MOVPE," *Journal of Crystal Growth*, vol. 310, no. 18, pp. 4115–4121, 2008.

- [11] B. M. Borg, M. Ek, K. A. Dick, B. Ganjipour, A. W. Dey, C. Thelander, and L.-E. Wernersson, "Diameter reduction of nanowire tunnel heterojunctions using in situ annealing," *Appl. Phys. Lett.*, vol. 99, no. 20, p. 203101, 2011.

- [12] B. Ganjipour, M. Ek, B. M. Borg, K. A. Dick, M.-E. Pistol, L.-E. Wernersson, and C. Thelander, "Carrier control and transport modulation in GaSb/InAsSb core/shell nanowires," *Appl. Phys. Lett.*, vol. 101, no. 10, p. 103501, 2012.

- [13] C. Thelander, P. Caroff, S. Plissard, and K. A. Dick, "Electrical properties of InAs<sub>1-x</sub>Sb<sub>x</sub> and InSb nanowires grown by molecular beam epitaxy," *Appl. Phys. Lett.*, vol. 100, no. 23, p. 232105, 2012.

- [14] X. Min, W. Runsheng, and P. D. Ye, "GaSb Inversion-Mode PMOS-FETs With Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> as Gate Dielectric," *IEEE Electron Device Lett.*, vol. 32, no. 7, pp. 883–885, 2011.

- [15] S. Mookerjea, D. Mohata, T. Mayer, V. Narayanan, and S. Datta, "Temperature-Dependent I-V Characteristics of a Vertical In<sub>0.53</sub>Ga<sub>0.47</sub>As Tunnel FET," *IEEE Electron Device Lett.*, vol. 31, no. 6, pp. 564 –566, 2010.