## LUND UNIVERSITY

Scaling of Vertical InAs-GaSb Nanowire Tunneling Field-Effect Transistors on Si

Memisevic, Elvedin; Svensson, Johannes; Hellenbrand, Markus; Lind, Erik; Wernersson, Lars-Erik

Published in:

**IEEE Electron Device Letters**

DOI:

10.1109/LED.2016.2545861

2016

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA):

Memisevic, E., Svensson, J., Hellenbrand, M., Lind, E., & Wernersson, L.-E. (2016). Scaling of Vertical InAs–GaSb Nanowire Tunneling Field-Effect Transistors on Si. *IEEE Electron Device Letters*, *37*(5), 549 - 552. https://doi.org/10.1109/LED.2016.2545861

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

EDL-2016-02-0225.R1

# Scaling of Vertical InAs-GaSb Nanowire Tunneling Field-Effect Transistors on Si

Elvedin Memišević, Johannes Svensson, Markus Hellenbrand, Erik Lind, and Lars-Erik Wernersson

Abstract— We demonstrate improved performance due to enhanced electrostatic control achieved by diameter scaling and gate placement in vertical InAs-GaSb Tunneling Field-Effect Transistors integrated on Si substrates. The best subthreshold swing, 68 mV/dec at  $V_{\rm DS}=0.3$  V, was achieved for a device with 20 nm InAs diameter. The on-current for the same device was 35  $\mu A/\mu m$  at  $V_{\rm GS}=0.5$  V and  $V_{\rm DS}=0.5$  V. The fabrication technique used allow downscaling of the InAs diameter down to 11 nm with a flexible gate placement.

Index Terms— HSQ, Nanowire, III-V, TFET, transistor, InAs-GaSb

#### I. INTRODUCTION

Scaling Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) has led to an increased transistor density that constrains the power consumption [1], [2]. It is hence desirable to scale the drive voltage. To maintain the offstate leakage, the subthreshold swing (SS) needs to be as low as possible, where the limit is 60 mV/dec for MOSFETs. Further voltage scaling beyond that of MOSFETs optimally requires devices that can reach a subthreshold swing below 60 mV/dec. One promising technology is the Tunneling Field-Effect Transistor (TFET), which uses quantum mechanical tunneling to filter the thermal injection [3], [4]. A challenge is to fabricate TFETs with a steep slope and large on-currents (I<sub>on</sub>). We here present highly scaled, vertical InAs/GaSb nanowire TFETs utilizing a gate all-round (GAA) geometry for good electrostatic control [5], [6]. The broken bandgap of the InAs/GaSb junction and low channel effective mass provides a high on-current [7], [8], [9] demonstrated previously on lateral nanowire devices [10]. In this paper, we study the effects of nanowire diameter scaling and gate-metal

This paragraph of the first footnote will contain the date on which you submitted your paper for review. This work was supported in part by the Swedish Foundation for Strategic Research and in part by the European Union Seventh Framework Program E2SWITCH under Grant 619509. The authors are with the Department of Electrical and Information Technology, Lund University, Lund 221 00, Sweden (elvedin.memisevic@eit.lth.se)

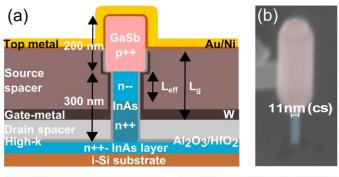

Fig. 1. (a) Schematic illustration of the vertical nanowire TFETs. Given lengths of the InAs and GaSb segments are applicable on the nanowires with HSQ drain spacer. (b) A colorized SEM image of the InAs-GaSb nanowire after digital etching. (c, d) SEM images of two devices with HSQ as drain spacer and gate-metal. Placement of the gate-metal is controlled using HSQ with different thicknesses. The gate-metal on the nanowires is colorized with green on the right half. In c) the gate is perfectly aligned with the heterojunction while in d) it is overlapping the junction.

placement on the TFET performance. We show that the InA/GaSb nanowire heterostructure can provide TFET performance capable to staggered heterostructure [11], [12].

#### II. DEVICE FABRICATION

InAs/GaSb nanowires were grown using vapor-liquid-solid growth method on an 200-nm-thick n<sup>+</sup>-InAs layer integrated on a highly resistive Si (111) substrate (p=5.5 k $\Omega$ -cm) [13]. The placement and diameter of the gold catalyst particles were defined using Electron Beam Lithography (EBL) and lift-off [14]. The Au-seed particles defining the nanowire diameters were 40 or 45 nm with spacing between 0.5 to 1.5  $\mu$ m, in arrays with 1-200 wires. The growth of the InAs/GaSb nanowires was subsequently performed using metal-organic vapor phase epitaxy (MOVPE). The GaSb source segment was p-doped to  $10^{19}$  cm<sup>-3</sup> using diethlyzinc (DeZn). The bottom ~1/2 of the total InAs length, was n-doped to a concentration

EDL-2016-02-0225.R1

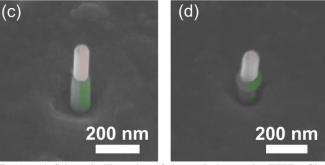

Fig. 2. (a) Output data of the devices with 40 nm and 15 nm InAs diameter, respectively. (b) Transfer data for the same devices as represented in figure a. (c) Temperature dependent transfer data from device with 15-nm-thick InAs. (d The Figure shows the best differential subthreshold swing,  $I_{\rm off}$  and  $I_{\rm on}$  as a function of temperature. Dots represents  $I_{\rm off}$  and  $I_{\rm on}$  current at  $V_{\rm GS} = -0.24$  V and  $V_{\rm GS} = 0.5$  V, respectively. Squares, enhanced by a dotted line, represent subthreshold swing values.

of 10<sup>18</sup> cm<sup>-3</sup>, by usage of tetraethyltin (TESn). The channel of the device was not intentionally doped with an estimated background carrier concentration of 10<sup>17</sup> cm<sup>-3</sup>. After growth, the nanowire diameter of the InAs was reduced trough a number of digital etching cycles without any noticeable etching of the GaSb resulting in InAs diameters between 11 to 40 nm on different set of samples. Directly after etching, a high-k layer of 1 nm Al<sub>2</sub>O<sub>3</sub> and 4 nm HfO<sub>2</sub> was applied using atomic layer deposition (ALD) at temperatures of 300 °C and 120 °C, respectively. The estimated EOT for this layer was 1.4 nm. Two methods were applied for formation of gate-drain spacer layer. For thick (100-400 nm) spacer layers, an organic layer was spun on and etched back using O2 plasma. For controlled fabrication of variable drain spacer (0-80 nm) thickness, a hydrogen silsesquioxane (HSQ) layer was formed using EBL exposure with exact dose control [15]. A 60-nmthick tungsten (W) film was conformally deposited by reactive sputtering to form the gate electrode. The physical gate-length (Lg) was set by spin on and etchback of an organic film, followed by O<sub>2</sub>-plasma ashing, yielding L<sub>g</sub> between 200 to 300 nm, as indicated in Fig 1a. UV- lithography was used to define the gate-pads. An organic gate-source spacer was formed using a spin on organic layer followed by etchback. Nickle and gold top-metals were sputtered and pads were defined using UV-lithography followed by wet-etching of the metals. The fabrication results in two types of samples, one with organic drain spacer used to study the effects of nanowire diameter scaling, and one sample with HSO drain spacer for study of the gate-placement. A schematic image of the final

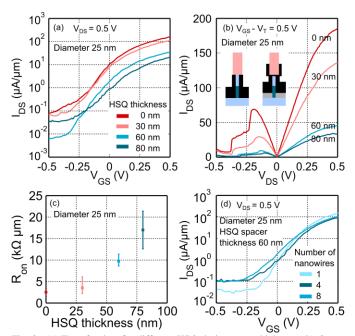

Fig. 3. (a) Transfer data for different HSQ drain spacer thickness. (b) Output data for the same devices as in Figure a. The inset schematically shows the placement of the gate on the devices with different drain spacer. (c)  $R_{\rm on}$  as function of the HSQ thickness. (d) Effects of the scaling of the number of the nanowire in the device for a HSQ thickness of 60 nm.

device is shown in Figure 1a. A TFET with an InAs diameter of 11 nm prior to high-k deposition is shown in Figure 1b. The effective gate-length ( $L_{\rm eff}$ ), is determined from unintentionally-doped (UID) channel thickness, as shown in Figure 1a, with an approximate length of 100 nm to 200 nm for devices with InAs diameter of 11 nm to 40 nm, respectively. Although the fabrication techniques allowed us to manufacture working transistors with InAs diameter of 11 nm, the highest yield and most data presented in this article was obtained from devices with thicker diameters.

### III. EFFECTS OF DIAMETER AND GATE PLACEMENT ON THE ELECTROSTATICS

Figure 2a-c shows the effect of diameter scaling, strongly improving the electrostatics of the devices as the diameter is scaled from 40 down to 15 nm. Both SS taken at  $V_{\rm DS} = 50 \text{ mV}$ improves from 243 mV/decade to 100 mV/decade as the diameter is scaled. Further, the drain-induced barrier lowering (DIBL) is greatly improved by the diameter scaling. Both device show similar  $I_{on}$ , around 6 - 9  $\mu$ A/ $\mu$ m, taken at  $V_{GS}$  =  $V_{\rm DS} = 0.5$  V. The gate current was two to three orders of magnitude lower than  $I_{DS}$  for all devices presented. Figure 2c shows the temperature dependence of the transfer characteristics for the 15 nm diameter device. As shown in the Figure 2d, the minimum SS shows different dependence, with a constant SS about 50 mV/dec for low temperatures and temperature dependent SS for higher temperature for which small activation energy of about 50 meV was extracted above the measurement noise floor at  $V_{GS} = -0.24$  V. The low activation energy indicates that the off-current is limited by trap-assisted tunneling, and not by back-injection over the valence band edge. The effect of gate placement relative to the

EDL-2016-02-0225.R1 3

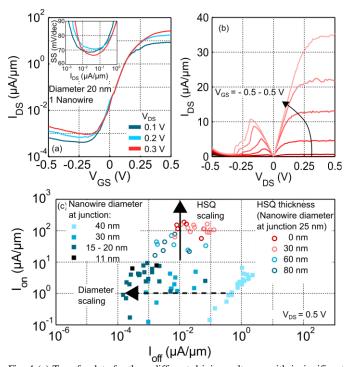

Fig. 4 (a) Transfer data for three different driving voltages, with insignificant DIBL. The HSQ drain spacer thickness for this device is 60 nm and the InAs diameter is 20 nm. The inset shows SS for three different drive voltages where the lowest differential SS achieved is 68 to 71 mV/dec. (b) Output data for the same device as a). (c)  $I_{\rm on}$  and  $I_{\rm off}$  current for devices with different InAs diameters and HSQ drain spacer thicknesses. The observed trends of improved electrostatics by general scaling.

channel/source junction, as well as the gate-drain overlap was studied on the sample with different HSQ drain spacers. In Figure 3a and b, the transfer data and output data from four devices with different drain spacer thickness between 0 to 80 nm are compared.  $I_{\text{on}}$  at  $V_{\text{DS}} = V_{\text{GS}} = 0.5 \text{ V}$  is increasing from  $21 \mu A/\mu m$  to  $160 \mu A/\mu m$ , as the thickness was decreased. The peak current in the NDR region was scaling with the spacer thickness, with the largest currents for the devices with thinnest HSQ reaching 1.09 mA/µm<sup>2</sup> and a peak-to-valley ratio of 10 at  $V_{\rm DS} = 0.5$  V. The inset in Figure 3b shows schematically the gate-placement on different devices. Due to the constant  $L_{\text{eff}}$ , as the gate-drain overlap is decreased, the gate-source overlap increases at a similar rate. In Figure 3c, the effect of the spacer thickness on  $R_{on}$  is shown. This trend corresponds well with observations for the output characteristics. Ron increases with spacer thickness, indicating an increase mainly in drain access resistance as the gate-drain overlap decreases although the increase of the gate-source overlap on the source side could affect the electrostatics as well. The lowest  $R_{\rm on}$  achieved was 1.6 kΩ · μm and 21.4 kΩ · µm for the devices with 0 nm and 80 nm spacer thickness, respectively. The subthreshold swing is decreasing when the spacer thickness is increased from 0 to 60 nm with an average value of 157 mV/dec to 133 mV/dec. In Figure 3d, the transfer data from devices with different numbers of nanowires are presented showing similar performance. In Figure 4a the transfer data is shown for the device with a 60- nm-thick HSQ drain spacer and a 20-nm-diameter InAs-channel, achieving a

TABLE I BENCHMARKING

|                                                               | BEI (CIII)II II (III)     |                      |

|---------------------------------------------------------------|---------------------------|----------------------|

| Parameter                                                     | Best device in this paper | Dewey IEDM 2011 [11] |

| Minimum point SS                                              | 66                        | 58                   |

| $(V_{\rm DS}=50~{\rm mV})$                                    |                           |                      |

| Current for lowest SS                                         | 9.2 nA/μm                 | 0.8 nA/μm            |

| $(V_{\rm DS} = 50 \text{ mV})$                                |                           |                      |

| On-current                                                    | 11.28 μA/μm               | 1.3 μA/μm            |

| $(I_{\rm off} = 10 \text{ nA/}\mu\text{m}, V_{\rm DS} =$      |                           |                      |

| $0.3 \text{ V}, \text{ V}_g\text{-V}_{goff} = 0.3 \text{ V})$ |                           |                      |

minimum differential SS of 68 mV/dec at  $V_{DS} = 0.3$  V and 82 mV/dec at  $V_{DS} = 0.5$  V. The improvement in subthreshold swing as compared with organic spacers can in part be explained by omission of O2 plasma during the processing of the drain spacer. The electrostatics of this device is excellent, which is shown by the insignificant (4.6 mV/V) DIBL and comparable SS values for drive voltages of 100 mV to 300 mV, shown in the inset in Figure 4a. The same device is benchmarked, in Table 1, against a TFET with a staggered InGaAs heterostructure demonstrating operation at higher current levels. The output data in Figure 4b shows that the  $I_{DS}$ current saturates well achieving currents of 35  $\mu$ A/ $\mu$ m for  $V_{GS}$ = 0.5 V and  $V_{DS}$  = 0.5 V. Figure 4c compares  $I_{on}$  and  $I_{off}$ performance of the devices from different samples. Diameter scaling clearly improves  $I_{\text{off}}$  while keeping  $I_{\text{on}}$  fairly constant due to an improved electrostatic control. Scaling down the drain spacer thickness improves the  $I_{on}$ . Thus the device geometry to a large degree affects the device performance.

#### IV. CONCLUSION

In this paper, we have demonstrated the importance of scaling the diameter and gate-placement in vertical InAs/GaSb TFETs. The fabrication technique used allows us to manufacture devices with the InAs diameter down to 11 nm and to position the gate-metal at an exact distance from the junction. The results show that diameter and gate-placement influences the electrostatics and on-current of the devices. The reduction of the diameter improves the electrostatics and on-current increases with decreasing drain spacer thickness. The lowest subthreshold swing was 68 mV/dec at  $V_{\rm DS}=0.3$  V and 82 mV/dec at  $V_{\rm DS}=0.5$  V measured on a device with 60-nm-thick drain spacer and 20 nm InAs-diameter, with the  $I_{\rm on}$  of 13  $\mu$ A/ $\mu$ m for  $V_{\rm GS}=0.5$  V and  $V_{\rm DS}=0.3$  V, and 35  $\mu$ A/ $\mu$ m for  $V_{\rm GS}=0.5$  V and  $V_{\rm DS}=0.5$  V.

#### REFERENCES AND FOOTNOTES

- [1] H. Riel, L.-E. Wernersson, M. Hong, J. A. del Alamo, "III-V compound semiconductor transistors-from planar to nanowire structures", MRS bull, Vol. 39, No. 8, pp. 668–677, August 2014, DOI: 10.1557/mrs.2014.137

- [2] S. Datta, H. Liu, V. Narayanan, "Tunnel FET technology: A reliability perspective", *Microelectron Reliab.*, Vol. 54, No. 8, pp. 861–874, March 2014, DOI: 10.1016/j.microrel.2014.02.002

- [3] A. M. Ionescu, H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches", *Nature*, Vol. 479, No. 7373, pp. 329–337, November 2011, DOI: 10.1038/nature10679

EDL-2016-02-0225.R1

[4] A. C. Seabaugh, Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic", *Proc. IEEE*, Vol. 98, No. 12, pp. 2095–2110, December 2010, DOI: 10.1109/JPROC.2010.2070470

- [5] E. Lind, E. Memišević, A. W. Dey, L.-E. Wernersson, "III-V Heterostructure Nanowire Tunnel FETs", *IEEE J. Electron Devices Soc.*, Vol. 3, No. 3, pp. 96–102, May 2015, DOI: 10.1109/JEDS.2015.2388811

- [6] K. J. Kuhn, "Considerations for Ultimate CMOS Scaling", *IEEE Trans. Electron Devices*, Vol. 59, No. 7, pp. 1813–1822, July 2012, DOI: 10.1109/TED.2012.2193129

- [7] D. Mohata, B. Rajamohanan, T. Mayer, M. Hudait, J. Fastenau, D. Lubyshev, A. W. K. Liu, S. Datta, "Barrier Engineered Arsenide-Antimonide Heterojunction Tunnel FETs with Enhanced Drive Current", *IEEE Electron Device Lett.*, Vol. 33, No. 11, pp. 1568–1570, November 2012, DOI: 10.1109/LED.2012.2213333

- [8] U. E. Avci, I. A. Young, "Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9 nm gate-length", *Proc. IEEE Int. Electron Device Meeting (IEDM)*, Washington, DC, USA, 2013, pp. 4.3.1–4.3.4, DOI: 10.1109/IEDM.2013.6724559

- [9] G. Zhou, R. Li, T. Vasen, M. Qi, S. Chae, Y. Lu, Q. Zhang, H. Zhu, J.-M. Kuo, T. Kosel, M. Wistey, P. Fay, A. Seabaugh, and H. Xing, 'Novel gate-recessed vertical InAs/GaSb TFETs with record high I<sub>ON</sub> of 180 μA/μm at V<sub>DS</sub> = 0.5 V', *IEEE Int. Electron Devices Mtg.*, San Francisco, CA, USA, 2012, pp. 32.6.1–32.6.4, DOI: 10.1109/IEDM.2012.6479154

- [10] A. W. Dey, B. M. Borg, B. Ganjipour, M. Ek, K. A. Dick, E. Lind, C. Thelander, L.-E. Wernersson, "High-current GaSb/InAs (Sb) nanowire tunnel field-effect transistors.", *IEEE Electron Device Lett.*, Vol. 34, No. 2, pp. 211–213, February 2013, DOI: 10.1109/LED.2012.2234078

- [11] G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M, Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, R. Chau, "Fabrication, Characterization, and Physics of III-V Heterojunction Tunneling Field Effect Transistors (H-TFET) for Steep Sub-Threshold Swing", Proc. IEEE Int. Electron Device Meeting (IEDM), Washington, DC, USA, 2011, pp. 33.6.1–33.6.4, DOI: 10.1109/IEDM.2011.6131666

- [12] B. Rajamohanan, R. Pandey, V. Chobpattana, C. Vaz, D. Gundlach, K. P. Cheung, J. Suehle, S. Stemmer, and S. Datta, "0.5 V Supply Voltage Operation of In<sub>0.65</sub>Ga<sub>0.35</sub>As/GaAs<sub>0.4</sub>Sb<sub>0.6</sub> Tunnel FET", *IEEE Electron Device Lett.*, Vol. 36, No. 1, pp. 20–22, January 2015, DOI: 10.1109/LED.2014.2368147

- [13] S. G. Ghalamestani, M. Berg, K. A. Dick, L.-E. Wernersson, 'High quality InAs and GaSb thin layers grown on Si (111)', J. Cryst. Growth, Vol. 332, No. 1, pp. 12–16, October 2011, DOI: 10.1016/j.jcrysgro.2011.03.062

- [14] S. G. Ghalamestani, S. Johansson, B. M. Borg, E. Lind, K. A. Dick, L.-E. Wernersson, "Uniform and position-controlled InAs nanowires on 2" Si substrates for transistor applications", *Nanotechnology*, vol. 23, no. 1, pp. 015302-1–015302-7, January 2012, DOI: 10.1088/0957-4484/23/1/015302

- [15] E. Memišević, E. Lind, L.-E. Wernersson, "Thin electron beam defined hydrogen silsesquioxane spacers for vertical nanowire transistors", J. Vac. Sci. Technol. B, Vol. 32, No. 5, pp. 051211-1-051211-6, September 2014, DOI:10.1116/1.4895112