## Vertical InAs/GaSb Nanowire Axial TFETs Integrated on Si-substrates

#### By E. Memisevic, J. Svensson, E. Lind, and L.-E. Wernersson

Swedish Foundation for Strategic Research

Lund University/ Faculty of Engineering/ Electrical and Information Technology/ Nano Electronics Group/ E. Memisevic

1

# Outline

- General about the TFETs

- Fabrication of the transistors

- DC-data

- Benchmarking

- Conclusions

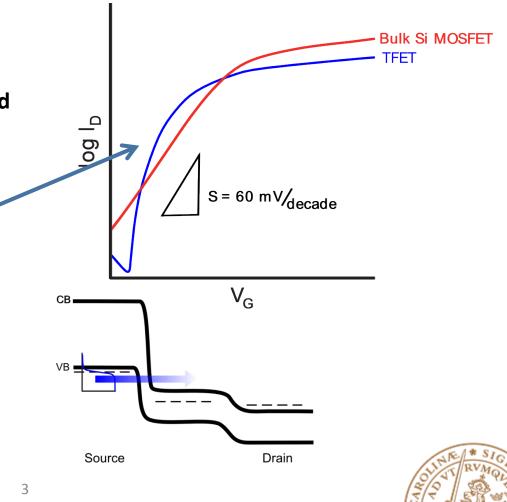

### General about the TFETs

- Traditional MOSFET are limited to lowest SS of 60 mV/dec at RT.

- With TEFT that limit can be evaded due to usage of electrons outside the tail in the Fermi-Dirac distribution.

- Higher current can be achivied at lower voltages.

Drain

CB

Source

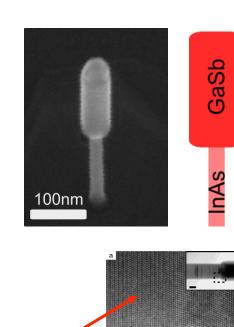

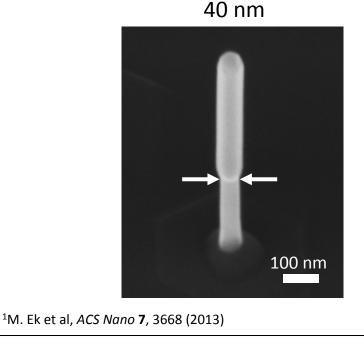

# The InAs/GaSb nanowires

- Combine materials with a large lattice mismatch

- Good electrostatic control

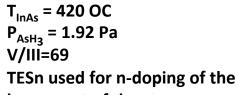

- Growth conditions for nanowires with InAs diameter of 25-30 nm :

- high enough  $P_{TMSb}$

- and high enough growth T

Because the growth of the GaSb on InAs stem is highly sensitive to TMSb partial pressure. <sup>1</sup>

20

60 nm

From: <sup>1</sup>M. Ek et al, ACS Nano 7, 3668 (2013)

$T_{GaSb} = 500 \ ^{O}C$  $P_{TMSb} = 0.6 \ Pa$ V/III = 1.1 DeZn used for p-doping

lower part of the stem

Lund University/ Faculty of Engineering/ Electrical and Information Technology/ Nano Electronics Group/ E. Memisevic

Δ

InGaSb segment (Approx. 3.5 nm)

InAs (WZ)

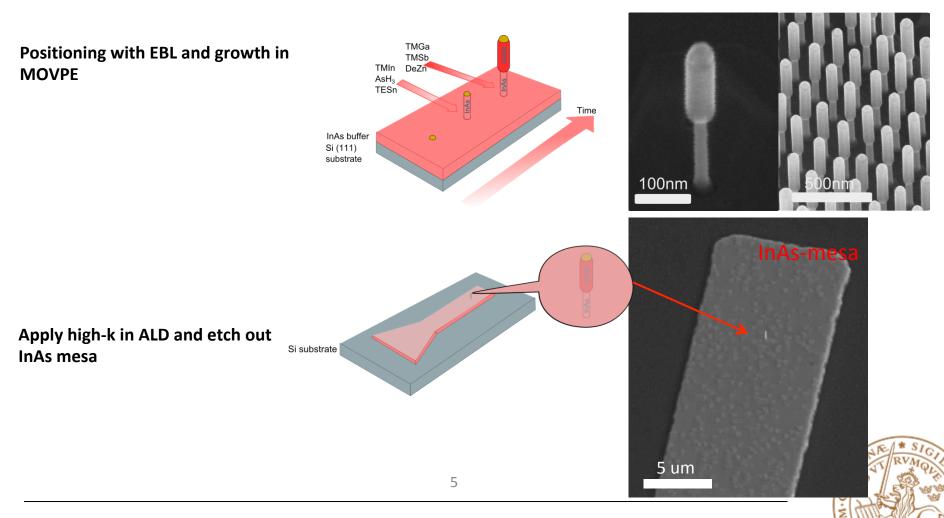

# Fabrication of the transistors

NANO

**ELECTRONICS**

GROUP

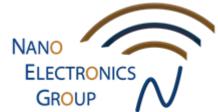

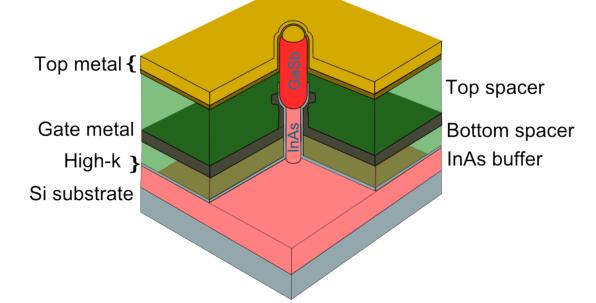

# Fabrication of the transistors

Definition of the spacers bottom/top using RIE and photo resist

Gate fabrication with sputtering of W and gate-length definition with RIE/photo resist.

### Gate metal High-k } Si substrate 6

# Fabrication of the transistors

Top-metal is defined using evaporation or sputtering.

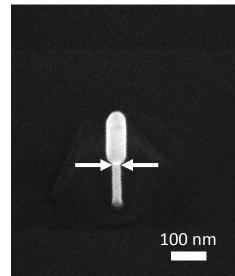

#### Controlling the InAs diameter: Digital etching

• To thin down the diameter of InAs we have used digital etching with Citric acid/Ozone, without any noticeable etching of GaSb.

15 nm

Lund University/ Faculty of Engineering/ Electrical and Information Technology/ Nano Electronics Group/ E. Memisevic

8

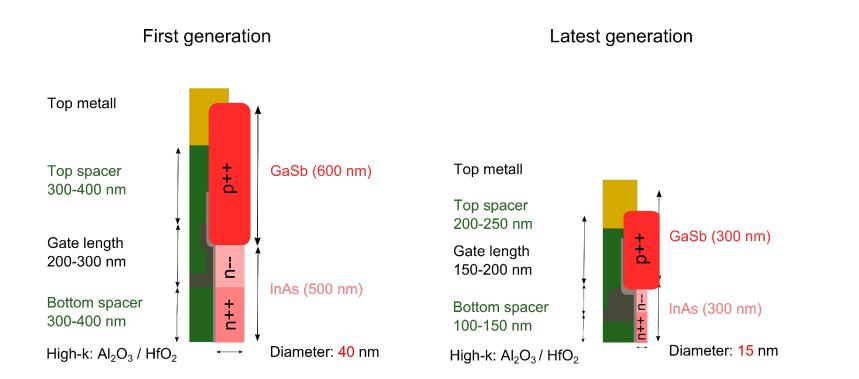

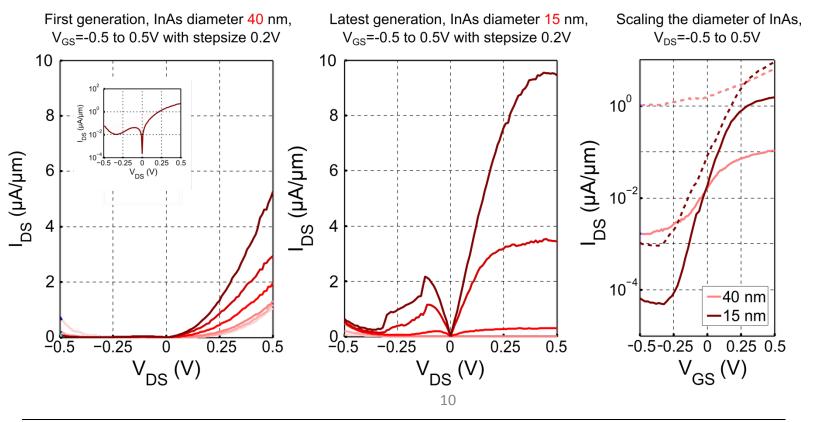

## Downscaling of the devices

9

### Effects of scaling

- Improved electrostatic control

- Lower I<sub>off</sub>

- Higher I<sub>on</sub>

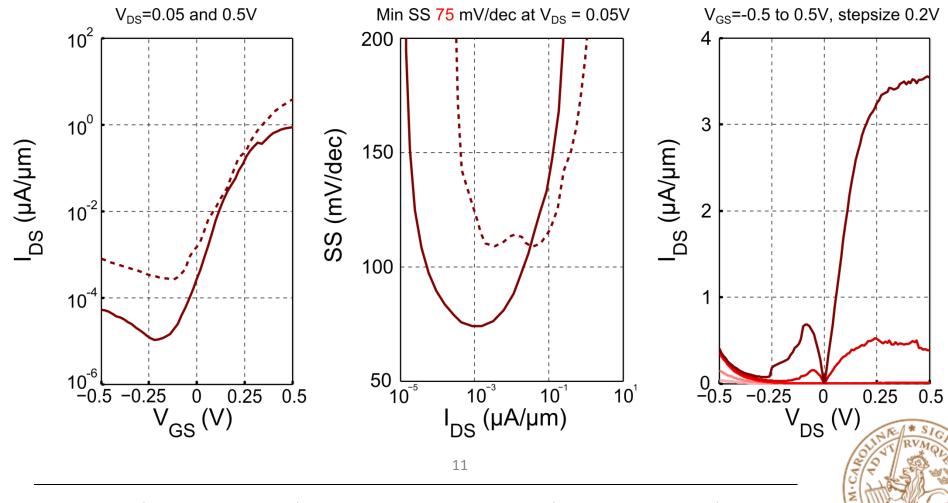

### **Device with lowest SS**

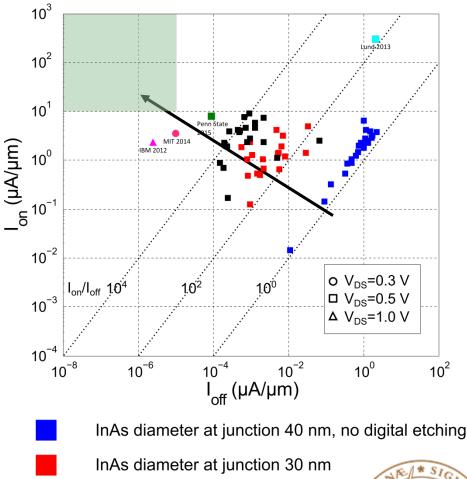

### Benchmarking

|                    |                     |                               |                              |                               | , 1                 |

|--------------------|---------------------|-------------------------------|------------------------------|-------------------------------|---------------------|

| Ref.               | Type of<br>geometry | Min SS (mV/dec)               | lon (μΑ/μm)                  | Peak<br>to<br>valley<br>ratio | 1                   |

| Lund 2013          | Lateral             | 250 (V <sub>DS</sub> = 0.3V)  | 310 (V <sub>DS</sub> = 0.5V) | 3                             | 1                   |

| Penn State<br>2015 | Vertical            | 97 (V <sub>DS</sub> = 0.05V)  | 8.4 (V <sub>DS</sub> = 0.5V) | -                             | (un 1               |

| IBM 2012           | Vertical            | 120 (V <sub>DS</sub> = 0.75V) | 2.4 (V <sub>DS</sub> = 1V)   | -                             | A                   |

| MIT 2014           | Vertical            | 75 (V <sub>DS</sub> = 0.3V)   | 2.5 (V <sub>DS</sub> = 0.5V) | 6.2                           | ן <u>ר</u><br>נכ    |

| From this<br>work  | Vertical            | 75 (V <sub>DS</sub> = 0.05V)  | 3.4 (V <sub>DS</sub> = 0.5V) | 8.4                           | _ <sup>0</sup><br>1 |

InAs diameter at junction 15-20 nm/

Lund University/ Faculty of Engineering/ Electrical and Information Technology/ Nano Electronics Group/ E. Memisevic

12

### Conclusions

We have shown following

- Vertical III-V Nanowire TFETs integrated on Si

- Possibilty to make devices with InAs diameters of 15 nm

- Achieving currents up to 9.5 uA/um

- SS down to 75 mV/dec at 0.05mV

### Thanks for your attention

Swedish Foundation for Strategic Research