# LUND UNIVERSITY

# A Self-aligned Gate-last Process applied to All-III-V CMOS on Si

Jonsson, Adam; Svensson, Johannes; Wernersson, Lars Erik

Published in: **IEEE Electron Device Letters**

DOI: 10.1109/LED.2018.2837676

2018

Document Version: Peer reviewed version (aka post-print)

Link to publication

Citation for published version (APA): Jonsson, A., Svensson, J., & Wernersson, L. E. (2018). A Self-aligned Gate-last Process applied to All-III-V CMOS on Si. IEEE Electron Device Letters, 39(7), 935-938. https://doi.org/10.1109/LED.2018.2837676

Total number of authors: 3

General rights

Unless other specific re-use rights are stated the following general rights apply: Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

· Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

· You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

# A Self-aligned Gate-last Process applied to All-III-V CMOS on Si

Adam Jönsson, Johannes Svensson, and Lars-Erik Wernersson

Abstract—Vertical nanowire n-type (InAs) and p-type (GaSb) transistors are co-processed and co-integrated using a gate-last process, enabling short gate-lengths ( $L_g$ =40 nm) and allowing selective digital etching of the channel. Two different common gate-stacks, including various pre-treatments, were compared and evaluated. The process was optimized to achieve high n-type performance while demonstrating p-type operation. The best n-type device is scaled down to 12 nm diameter and has a peak transconductance of 2.6 mS/µm combined with a low  $R_{0n}$  of 317  $\Omega$ ·µm while the p-type exhibit 74 µS/µm. In spite of increased complexity due to co-integration, our n-type InAs transistors demonstrate increased drive-current, 1.8 mA/µm, compared to earlier publications.

Index Terms—Vertical, nanowire, III-V, MOSFET, CMOS, InAs, GaSb

### I. INTRODUCTION

COMPLEMENTARY metal-oxide-semiconductor (CMOS) circuits based on all-III-V channel materials require further development to achieve competitive p-type performance [1], [2]. Although antimonide-based materials such as GaSb have demonstrated high hole mobility [3], transistor performance is, in part, limited by the gate-stacks [4]–[6]. It has been suggested that combinations of a more conventional p-type SiGe channel combined with n-type III-V InGaAs channel is a viable alternative to current CMOS technology [7], [8]. This type of material integration is, however, not straightforward, mainly due to strong material selectivity during processing.

With continued transistor scaling, deteriorated electrostatics leads to various short channel effects [9]. Vertical nanowires with a gate-all-around (GAA) geometry is one alternative with beneficial performance at the 5 nm node [10]. The vertical nanowire geometry in particular decouples the gate length and contact geometry from the footprint area [11].

In this paper, GaSb p-type and InAs n-type MOSFETs are co-integrated in a vertical nanowire gate-all-around structure, utilizing a common gate-stack. The process uses hydrogen silsequioxane (HSQ) spacers with adjustable thickness for development of a self-aligned, gate-last, process compatible with vertical antimonide-based structures.

This work was supported in part by the Swedish Research Council, and in part by the Swedish Foundation for Strategic Research, and the European Union H2020 Program INSIGHT (Grant Agreement No. 688784).

All authors were with the Department of Electrical and Information Technology, Lund University, SE-221 00 Lund, Sweden (e-mail: adam.jonsson@eit.lth.se). All presented devices are scaled to sub-100 nm gate lengths and, for the n-type devices, nanowire diameters down to 12 nm are demonstrated. Improved drive-currents are also realized as compared to previous iterations of vertical InAs transistors, namely a 400% (gate-last) [12] and 150% (doped channel) [13] increase is shown with  $I_{\rm DS} = 1.8$  mA/µm (V<sub>ds</sub> and V<sub>gs</sub> = 0.7 V).

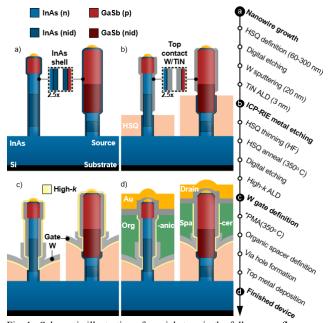

Fig. 1. Schematic illustration of crucial steps in the full process flow attached with an overview of fabrication. The illustrations show nidchannel devices, notice that the process allows for varying gate placement along the nanowire. \*Post metal anneal (PMA) is performed only on specific samples.

#### II. DEVICE FABRICATION

Fig. 1 schematically illustrates the process flow for cointegration of p-type GaSb and n-type InAs MOSFETs. The devices are fabricated on  $1 \text{ cm}^2$  p-type silicon (111) substrates with a 260 nm epitaxially grown InAs layer [14].

InAs-GaSb nanowires are subsequently grown from 15-nmthick Au seed particles defined by electron beam lithography (EBL). Sections of the InAs segment is n-doped by Sn and the top of the GaSb segment is p-doped by Zn, see Fig. 1. In the case of GaSb growth, significant background doping is present attributed to point defects ( $\sim 10^{16}$ ) [15]. By utilizing the Gibbs-Thomson effect during VLS growth, the GaSb growth rate can be significantly reduced for smaller gold particle sizes [16] (diameter < 30 nm) which enables length control of the two separate materials in the heterojunction nanowires [17]. Therefore, 24 nm and 28 nm diameter Au dots are used for growing n-type wires and 44 nm for p-type wires. The Au dots

| TABLE I<br>SAMPLE DESCRIPTION      |                                                                                     |                                                                           |

|------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Sample                             | Sample A                                                                            | Sample B                                                                  |

| Top contact formation <sup>1</sup> | Ozone oxidation + citric<br>acid 60 s + W/TiN                                       | Ozone oxidation + citric<br>acid 60 s + 1:500 +<br>$(NH_4)_2S:H_2O 3 min$ |

| Gate-stack                         | HCL:IPA + 5x TMA1                                                                   | Citric acid + 8x {TMAl                                                    |

| Pre-treatment                      | pulses                                                                              | pulse and H <sub>2</sub> plasma}                                          |

| High-k                             | $^{2}6/36$ cycles Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub><br>EOT = 0.85 nm | $^{3}40$ cycles HfO2 (+PMA)<br>EOT = 0.76 nm                              |

| n-type                             |                                                                                     |                                                                           |

| doping                             | nid-channel                                                                         | n-channel                                                                 |

| $L_{g}$                            | 50 nm                                                                               | 40 nm                                                                     |

| diameter                           | 20 nm                                                                               | 12 nm                                                                     |

| $g_{ m m,peak}$                    | 1.2 mS/µm                                                                           | 2.6 mS/μm                                                                 |

| $SS_{lin}$                         | 74 mV/dec                                                                           | 191 mV/dec                                                                |

| $R_{\rm on}$                       | 1039 <b>Ω</b> ·μm                                                                   | 317 <b>Ω</b> ·μm                                                          |

| p-type                             |                                                                                     |                                                                           |

| $L_{\rm g}$                        | 70 nm                                                                               | 100 nm                                                                    |

| diameter                           | 40 nm                                                                               | 38 nm                                                                     |

| $g_{ m m,peak}$                    | 74 μS/μm                                                                            | 11 μS/μm                                                                  |

| $SS_{lin}$                         | 273 mV/dec                                                                          | 622 mV/dec                                                                |

| $R_{ m on}$                        | 5.9 kΩ·µm                                                                           | 20 kΩ·µm                                                                  |

Description of processing variations for two different samples highlighting the critical steps involved. An overview is given for the important performance metrics.  $g_{m,peak}$  is extracted at drain bias  $|V_{ds}|=0.5$  V and  $SS_{lin}$  at  $|V_{ds}|=0.05$  V.

<sup>1</sup>Contact annealing, post top metal definition, has been performed at 350 degrees C for 60 minutes (Fig. 1). <sup>2</sup>Al<sub>2</sub>O<sub>3</sub> (TMAl) and HfO<sub>2</sub> (TDMAHf) is deposited at 300 °C and 120°C respectively. <sup>3</sup>In situ remote plasma treatment of the surface is carried out inside the ALD chamber and HfO<sub>2</sub> (TDMAHf) is deposited at 250°C. Additional post metal anneal (PMA) at 350°C is also performed after gate-definition on sample B.

are patterned in structures with a pitch of about 300 nm.

In the first step, the top contact is defined with an HSQ mask, whose thickness is determined by the dose in an EBL process [9]. The thicknesses of the HSQ is gradually varied from 60 to 300 nm to define gate position in separate devices. The InAs shell on the protruding part of the nanowires, that will later constitute the top contact, is digitally etched by oxidation and citric acid treatment. An ammonium sulfide treatment is also used for some of the samples, to passivate the III-V surface [18], processing differences are outlined in Table I. Subsequently, 20 nm tungsten (W) is sputtered followed by a 3 nm TiN atomic-layer-deposited (ALD) film. The metal is removed from all planar surfaces by an ICP-RIE SF<sub>6</sub>:C<sub>4</sub>F<sub>8</sub> based dry-etch process leaving metal on the nanowire sidewalls defining the top metal contact.

The same HSQ mask is also used as a bottom spacer by thinning it with a diluted HF (1:1000) wet etch so that the nanowire part that constitutes the channel protrudes. This method allows for sub-100 nm gate-length definition. The exposed semiconductor surface is digitally etched by oxidation followed by either citric acid or an HCL:IPA (1:30) treatment. The number of digital etch cycles are adjusted to remove the overgrown doped InAs shell, restoring the core channel material for the p- and n-type wires, that finishes the gate recess.

To optimize the processing conditions, two types of high-k

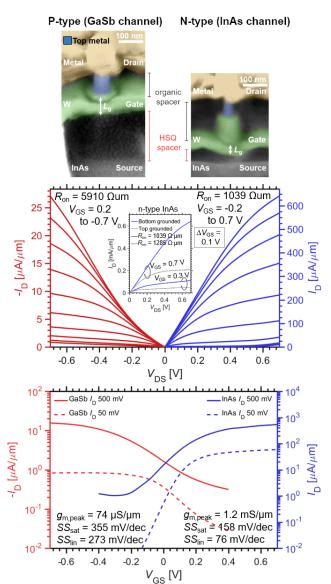

Fig. 2. Falsely colored SEM-images depicting single nanowires inside a p-type and n-type structure for Sample A (Table I), highlighting the different HSQ thickness. Combined transfer and output characteristics is presented for a selected p- and n-type device. The n-type (nid-channel) device consists of 184 nanowire array with a pitch of 300 nm, diameter of 20 nm, and  $L_g = 50$  nm. The p-type consists of 144 nanowires with a pitch of 350 nm, diameter of 40 nm, and  $L_g = 70$  nm. Increased resistance is shown in  $R_{on}$  by switching drain and source to realize a top grounded configuration.

are compared, a conventional bi-layer  $Al_2O_3/HfO_2$  [19] and a pure  $HfO_2$  dielectric. The  $HfO_2$  only gate-stack is preferred for aggressive EOT scaling [20]. High temperature ( $\geq 250^{\circ}C$ ) is necessary when forming the interface layers for more effective self-cleaning [19], [21]. The different high-*k* with corresponding pre-treatments are described further in Table I, representing the best optimization for GaSb p-type (Sample A) and InAs n-type (Sample B) device performance.

The gate metal is defined by sputtering 60 nm W followed by a back-etched S1813 spacer as mask for an SF<sub>6</sub> dry-etch process to remove the top of the gate W and vertically align the gate to the top contact. An organic spacer is then deposited, followed by sputtering of the top metal electrode consisting of W/Ni/Au.

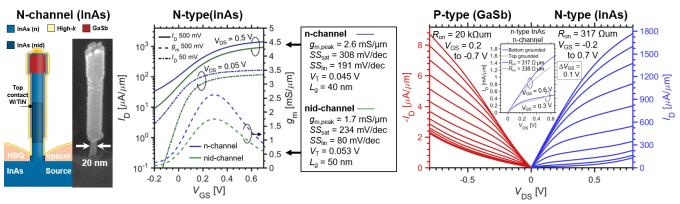

Fig. 3. Comparison between 184 nanowire arrays with  $L_g = 40$  and  $L_g = 50$  nm from sample B (Table I). Output characteristics of the p-type device in Sample B is also included. The SEM image is showing a 12 nm diameter nanowire, with doped channel (n-channel) after in-situ hydrogen plasma and highk ALD comprised of 40 cycles HfO<sub>2</sub> corresponding to 4 nm thickness, . The lower curve of each curve-pair (n-type InAs) corresponds to a, not intentionally doped, nid-channel. The HSQ spacer thicknesses for n- and nid-channel devices are 10 and 50 nm, respectively. Contact resistance behaves symmetrically with closely matched  $R_{on}$  values for switched bias conditions, due to improved contact processing.

Notice that the InAs-GaSb combination introduces a tunneling source contacts with broken bandgap, for the p-type device, where reported values suggest that it may have sufficiently low resistivity (axial Esaki diodes: ~260  $\Omega$ ·µm) [22], [23]. Thus the InAs-GaSb structure, due to resemblance with state-of-the-art Tunnel-FETs [24], [25], lends itself for future CMOS Tunnel-FET implementations including co-integration of MOSFETs and Tunnel-FETs.

#### III. DEVICE CHARACTERIZATION

Transfer and output characteristics for sample A with a bilayer gate-stack is presented in Fig. 2. Transconductance  $g_{m,peak}$ values of 1.2 mS/µm for n-type and 74 µS/µm for p-type was achieved with minimum subthreshold slope  $SS_{\text{lin}}$  of 74 and 271 mV/dec. Both devices exhibit enhancement mode operation with  $V_{\text{T}} = 0.08$  and -0.02 V. The limited n-type off-state performance is partly caused by drain tunneling due to the narrow bandgap of InAs [26]. However, for the p-type GaSb device the large diameter of the gate-segment in conjunction with a non-optimal high-*k* interface degrades the off-state. The 24 times higher drive current for the n-type as compared to the p-type MOSFET is expected due to the large difference in charge carrier mobility [2]. Further, significant gate-length scaling and strained GaSb channels are needed to enable the ptype MOSFET semi-ballistic operation [27], [28].

The resistance originating from the top contact is reduced for the n-type device in sample B (Table I) by adding a sulfur passivation step during the top contact definition, which increases the on-state performance,  $g_{m,peak} = 2.6 \text{ mS/}\mu\text{m}$  (nchannel), Fig. 3. This is further quantified by switching the source and drain electrodes during measurement that displays a symmetrical behavior with low  $R_{on}$  values of 317 and 338  $\Omega$ ·µm, in contrast to the n-type device in sample A (Fig. 2 inset). This device also utilizes a pure HfO<sub>2</sub> gate-stack with low EOT of 0.76 nm, see Table I. The off-state and electrostatics are limited, which can be attributed to a doped channel and a hightemperature deposition of HfO<sub>2</sub> at 250°C [29]. The hysteresis window corresponding to the gate-stack is evaluated to 20 mV, on a representative device, at the minimum SS point ( $V_{ds}$ =-0.2 to 0.7 V). An additional device with nid-channel, based on the same type of nanowire that has a gate shifted upwards along the nanowire, is also available on the same sample and is presented in Fig. 3. Here, improved electrostatics is shown with SS<sub>lin</sub> decreased from 191 (n-channel) to 80 mV/dec (nid channel). Even though H<sub>2</sub>-plasma on InAs may result in increased surface roughness we find that high transconductance values still can be obtained. The n-type devices, on sample B, with peak transconductance  $g_{m,peak}$  of 2.6 (n-channel) and 1.7 mS/ $\mu$ m (nid-channel), at  $V_{ds}$ =0.5 V, indicate added source resistance due to varied HSQ spacer thickness. The spacer is varied from 10 (n-channel) up to 50 nm (nid-channel), see Fig. 3. Notably the saturation current for the device with doped n-channel is 1.8 mA/ $\mu$ m at  $V_{gs} = 0.7$  V. The improved drive current, compared to previous InAs transistor iterations, can be attributed to the addition of doping at the bottom nanowire-segment [12] and ndoped shell growth [13]. The p-type device is demonstrated although with reduced performance and electrostatics as compared to the n-type device quantified by  $g_{m,peak} = 11 \ \mu S/\mu m$  $(V_{\rm ds} = -0.5 \text{ V})$  and  $SS_{\rm lin} = 622 \text{ mV/dec}$ , see Table I.

### IV. CONCLUSIONS

A new process for n-type (InAs) and p-type (GaSb) MOSFET co-integration compatible with highly sensitive antimonide-based materials has been developed. Aggressively scaled devices with sub-100 nm gate-lengths and n-type diameters down to 12 nm have been demonstrated using gatestack variation, giving a highest  $g_{m,peak}$  of 2.6 mS/um, see Table I. P-type devices, demonstrating  $g_{m,peak}$  of 74 and 11 uS/um, are also co-integrated on the same samples. Further optimization of the GaSb gate-stacks combined with aggressive diameter scaling will increase the balance for the III-V CMOS. The HSQ-spacer utilization allows for future integration of p- and n-type on the same nanowire, ultimately reducing the diameter difference between the devices. The process also enables possibilities for co-integrating MOSFETs with state-of-the-art Tunnel-FETs.

#### V. ACKNOWLEDGEMENTS

I extend my gratitude to Dr. Peralagu at The University of Glasgow for helpful feedback regarding process development.

#### REFERENCES

- K.-H. Goh, K.-H. Tan, S. Yadav, Annie, S.-F. Yoon, G. Liang, X. Gong, and Y.-C. Yeo, "Gate-all-around CMOS (InAs n-FET and GaSb p-FET) based on vertically-stacked nanowires on a Si platform, enabled by extremely-thin buffer layer technology and common gate stack and contact modules," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, p. 15.4.1-15.4.4, DOI: 10.1109/IEDM.2015.7409704.

- [2] A. W. Dey, J. Svensson, B. M. Borg, M. Ek, and L.-E. Wernersson, "Single InAs/GaSb Nanowire Low-Power CMOS Inverter," *Nano Lett.*, vol. 12, no. 11, pp. 5593–5597, Nov. 2012, DOI: 10.1021/nl302658y.

- [3] Z. X. Yang, S. Yip, D. Li, N. Han, G. Dong, X. Liang, L. Shu, T. F. Hung, X. Mo, and J. C. Ho, "Approaching the Hole Mobility Limit of GaSb Nanowires," *ACS Nano*, vol. 9, no. 9, pp. 9268–9275, 2015, DOI: 10.1021/acsnano.5b04152.

- [4] W. Lu, I. P. Roh, D. Geum, S. Kim, J. D. Song, L. Kong, and J. A. Alamo, "10-nm Fin-Width InGaSb p-Channel Self-Aligned FinFETs Using Antimonide-Compatible Digital Etch," in 2017 IEEE International Electron Devices Meeting (IEDM), 2017, pp. 433–436, DOI: 10.1109/IEDM.2017.8268412.

- [5] D. Cutaia, K. E. Moselund, H. Schmid, M. Borg, A. Olziersky, and H. Riel, "Complementary III–V heterojunction lateral NW Tunnel FET technology on Si," in 2016 IEEE Symposium on VLSI Technology, 2016, pp. 1–2, DOI: 10.1109/VLSIT.2016.7573444.

- [6] V. Deshpande, V. Djara, E. O'Connor, P. Hashemi, K. Balakrishnan, M. Sousa, D. Caimi, A. Olziersky, L. Czornomaz, and J. Fompeyrine, "Advanced 3D Monolithic hybrid CMOS with Sub-50 nm gate inverters featuring replacement metal gate (RMG)-InGaAs nFETs on SiGe-OI Fin pFETs," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, p. 8.8.1-8.8.4, DOI: 10.1109/IEDM.2015.7409658.

- J. A. del Alamo, "Nanometre-scale electronics with III–V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317– 323, Nov. 2011, DOI: 10.1038/nature10677.

- [8] P. Hashemi, Kam-Leung Lee, T. Ando, K. Balakrishnan, J. A. Ott, S. Koswatta, S. U. Engelmann, Dae-Gyu Park, V. Narayanan, R. T. Mo, and E. Leobandung, "Demonstration of record SiGe transconductance and short-channel current drive in High-Ge-Content SiGe PMOS FinFETs with improved junction and scaled EOT," in 2016 IEEE Symposium on VLSI Technology, 2016, pp. 1– 2, DOI: 10.1109/VLSIT.2016.7573370.

- [9] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fullydepleted, surrounding-gate MOSFET's," *IEEE Electron Device Lett.*, vol. 18, no. 2, pp. 74–76, Feb. 1997, DOI: 10.1109/55.553049.

- [10] D. Yakimets, G. Eneman, P. Schuddinck, Trong Huynh Bao, M. G. Bardon, P. Raghavan, A. Veloso, N. Collaert, A. Mercha, D. Verkest, A. Voon-Yew Thean, and K. De Meyer, "Vertical GAAFETs for the Ultimate CMOS Scaling," *IEEE Trans. Electron Devices*, vol. 62, no. 5, pp. 1433–1439, May 2015, DOI: 10.1109/TED.2015.2414924.

- [11] M. Berg, K.-M. Persson, O.-P. Kilpi, J. Svensson, E. Lind, and L.-E. Wernersson, "Self-aligned, gate-last process for vertical InAs nanowire MOSFETs on Si," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, p. 31.2.1-31.2.4, DOI: 10.1109/IEDM.2015.7409806.

- [12] K.-M. Persson, M. Berg, M. B. Borg, J. Wu, S. Johansson, J. Svensson, K. Jansson, E. Lind, and L.-E. Wernersson, "Extrinsic and Intrinsic Performance of Vertical InAs Nanowire MOSFETs on Si Substrates," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2761–2767, Sep. 2013, DOI: 10.1109/TED.2013.2272324.

- [13] M. Berg, O.-P. Kilpi, K.-M. Persson, J. Svensson, M. Hellenbrand, E. Lind, and L.-E. Wernersson, "Electrical Characterization and Modeling of Gate-Last Vertical InAs Nanowire MOSFETs on Si," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 966–969, Aug. 2016, DOI: 10.1109/LED.2016.2581918.

- S. Gorji Ghalamestani, M. Berg, K. A. Dick, and L.-E. Wernersson, "High quality InAs and GaSb thin layers grown on Si (1 1 1)," J. Cryst. Growth, vol. 332, no. 1, pp. 12–16, Oct. 2011, DOI: 10.1016/J.JCRYSGRO.2011.03.062.

- [15] A. S. Babadi, J. Svensson, E. Lind, and L.-E. Wernersson, "Impact of doping and diameter on the electrical properties of GaSb nanowires," *Appl. Phys. Lett.*, vol. 110, no. 5, p. 53502, Jan. 2017, DOI: 10.1063/1.4975374.

- [16] M. Ek, B. M. Borg, J. Johansson, and K. A. Dick, "Diameter Limitation in Growth of III-Sb-Containing Nanowire Heterostructures," ACS Nano, vol. 7, no. 4, pp. 3668–3675, Apr. 2013, DOI: 10.1021/nn400684p.

- [17] J. Svensson, A. W. Dey, D. Jacobsson, and L.-E. Wernersson, "III– V Nanowire Complementary Metal–Oxide Semiconductor Transistors Monolithically Integrated on Si," *Nano Lett.*, vol. 15, no. 12, pp. 7898–7904, Dec. 2015, DOI: 10.1021/acs.nanolett.5b02936.

- [18] L. Zhao, Z. Tan, R. Bai, N. Cui, J. Wang, and J. Xu, "Effects of sulfur passivation on GaSb metal-oxide-semiconductor capacitors with neutralized and unneutralized (NH4)2S solutions of varied concentrations," *Appl. Phys. Express*, vol. 6, no. 5, 2013, DOI: 10.7567/APEX.6.056502.

- [19] T. Gougousi, "Atomic layer deposition of high-k dielectrics on III– V semiconductor surfaces," *Prog. Cryst. Growth Charact. Mater.*, vol. 62, no. 4, pp. 1–21, Dec. 2016, DOI: 10.1016/J.PCRYSGROW.2016.11.001.

- [20] S. Sioncke, J. Franco, A. Vais, V. Putcha, L. Nyns, A. Sibaja-Hernandez, R. Rooyackers, S. C. Ardila, V. Spampinato, A. Franquet, J. W. Maes, Q. Xie, M. Givens, F. Tang, X. Jiang, M. Heyns, D. Linten, J. Mitard, A. Thean, D. Mocuta, N. Collaert, "First demonstration of ~3500 cm 2 /V-s electron mobility and sufficient BTI reliability (max Vov up to 0.6V) InGaAs nFET using an IL/LaSiO/HfO," in 2017 Symposium on VLSI Technology, 2017, pp. T38–T39, DOI: 10.23919/VLSIT.2017.7998192.

- [21] A. S. Babadi, E. Lind, and L.-E. Wernersson, "ZrO<sub>2</sub> and HfO<sub>2</sub> dielectrics on (001) n-InAs with atomic-layer-deposited *in situ* surface treatment," *Appl. Phys. Lett.*, vol. 108, no. 13, p. 132904, Mar. 2016, DOI: 10.1063/1.4945430.

- [22] K. Vizbaras, M. Törpe, S. Arafin, and M.-C. Amann, "Ultra-low resistive GaSb/InAs tunnel junctions," *Semicond. Sci. Technol.*, vol. 26, no. 7, p. 75021, Jul. 2011, DOI: 10.1088/0268-1242/26/7/075021.

- [23] A. W. Dey, J. Svensson, M. Ek, E. Lind, C. Thelander, and L.-E. Wernersson, "Combining Axial and Radial Nanowire Heterostructures: Radial Esaki Diodes and Tunnel Field-Effect Transistors," *Nano Lett.*, vol. 13, no. 12, pp. 5919–5924, Dec. 2013, DOI: 10.1021/nl4029494.

- [24] E. Memisevic, J. Svensson, E. Lind, and L.-E. Wernersson, "InAs/InGaAsSb/GaSb Nanowire Tunnel Field-Effect Transistors," *IEEE Trans. Electron Devices*, vol. 64, no. 11, pp. 4746–4751, Nov. 2017, DOI: 10.1109/TED.2017.2750763.

- [25] A. W. Dey, B. M. Borg, B. Ganjipour, M. Ek, K. A. Dick, E. Lind, C. Thelander, and L.-E. Wernersson, "High-Current GaSb/InAs(Sb) Nanowire Tunnel Field-Effect Transistors," *IEEE Electron Device Lett.*, vol. 34, no. 2, pp. 211–213, Feb. 2013, DOI: 10.1109/LED.2012.2234078.

- [26] N. D. Chien and C.-H. Shih, "Short channel effects in tunnel fieldeffect transistors with different configurations of abrupt and graded Si/SiGe heterojunctions," *Superlattices Microstruct.*, vol. 100, pp. 857–866, Dec. 2016, DOI: 10.1016/J.SPMI.2016.10.057.

- [27] A. Nainani, D. Kim, T. Krishnamohan, and K. Saraswat, "Hole mobility and its enhancement with strain for technologically relevant III-V semiconductors," *Int. Conf. Simul. Semicond. Process. Devices, SISPAD*, pp. 4–7, 2009, DOI: 10.1109/SISPAD.2009.5290251.

- [28] A. Nainani, B. R. Bennett, J. Brad Boos, M. G. Ancona, and K. C. Saraswat, "Enhancing hole mobility in III-V semiconductors," *J. Appl. Phys.*, vol. 111, no. 10, p. 103706, May 2012, DOI: 10.1063/1.4718381.

- [29] D. M. Hausmann and R. G. Gordon, "Surface morphology and crystallinity control in the atomic layer deposition (ALD) of hafnium and zirconium oxide thin films," *J. Cryst. Growth*, vol. 249, no. 1–2, pp. 251–261, Feb. 2003, DOI: 10.1016/S0022-0248(02)02133-4.